# BATTERY-SOURCED SWITCHED-INDUCTOR MULTIPLE-OUTPUT CMOS POWER-SUPPLY SYSTEMS

A Dissertation Presented to The Academic Faculty

by

Carlos J. Solis

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology May 2018

Copyright © 2018 by Carlos J. Solis

# BATTERY-SOURCED SWITCHED-INDUCTOR MULTIPLE-OUTPUT CMOS POWER-SUPPLY SYSTEMS

# Approved by:

Dr. Gabriel A. Rincón-Mora School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Maysam Ghovanloo School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Thomas G. Habetler School of Electrical and Computer Engineering Georgia Institute of Technology Dr. John D. Cressler School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Sung Ha Kang School of Mathematics Georgia Institute of Technology

Date Approved: April 3, 2018

## **ACKNOWLEDGEMENTS**

I would like to first thank my advisor, Dr. Gabriel Alfonso Rincón-Mora, whose drive and passion for excellence, technical guidance, and advise made this research possible.

Also, I want to thank my proposal and committee members, Dr. Maysam Ghovanloo, Dr. Thomas G. Habetler, Dr. John D. Cressler, and Dr. Sung Ha Kang for their invaluable technical feedback and support for my research.

I am tremendously grateful to Bryan Legates, Tony Bonte, JD Morris, and Analog Devices, Inc. for their technical and financial support for this research.

I am also very thankful for my colleagues at the Georgia Institute of Technology, Andres Blanco, Rajiv Damodaran Prahba, Orlando Lazaro, Karl Peterson, Luke Milner, Dongwon Kwon, Suhwan Kim, Joshua Cowan, Jun-Yang Lei, Kowshik Murali, Amy C Wilson, Nan Xing, Siyu Yang, and Devon Janke, for the priceless technical discussions, guidance, and their support through this journey.

A very special thanks to family and friends especially to my parents, Lydia E. Ramírez-Santiago and Carlos D. Solis-Orria, for their unconditional support and encouragement.

Finally, I am extremely grateful for my loving wife, Ivonne M. Matos-Guerra, without whose endless love, support, sacrifice and encouragement none of this journey would had been possible.

# TABLE OF CONTENTS

|   |        |                                                                           | Page |

|---|--------|---------------------------------------------------------------------------|------|

| A | CKNO   | OWLEDGEMENTS                                                              | iii  |

| L | IST O  | F TABLES                                                                  | vii  |

| L | IST O  | F FIGURES                                                                 | viii |

| S | UMM    | ARY                                                                       | xvi  |

| C | НАРТ   | TER                                                                       |      |

| 1 | Pov    | wering Multifunctional Microsystems                                       | 1    |

|   | 1.1    | Emerging Applications                                                     | 1    |

|   | 1.2    | Power Management Requirements                                             | 3    |

|   | 1.3    | Power Supplies                                                            | 5    |

|   | 1.4    | Challenges                                                                | 9    |

|   | 1.5    | Summary                                                                   | 14   |

| 2 | Sin    | gle-Inductor Multiple-Output Converters                                   | 17   |

|   | 2.1    | SIMO Operation                                                            | 17   |

|   | 2.2    | SIMO Control                                                              | 24   |

|   | 2.3    | Context and Comparison                                                    | 29   |

|   | 2.4    | Summary                                                                   | 32   |

| 3 | Sta    | bility Analysis of Hysteretic Current-Mode Control for Switched-Inductors |      |

| C | Conver | ters                                                                      | 36   |

|   | 3.1    | Hysteretic Control                                                        | 36   |

|   | 3.2    | Single-Output Hysteretic Current-Mode Design                              | 37   |

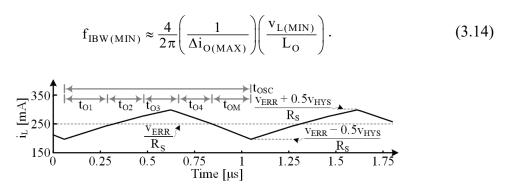

|   | 3.3 | Multiple-Output Hysteretic Current-Mode Design                    | 47  |

|---|-----|-------------------------------------------------------------------|-----|

|   | 3.4 | Summary                                                           | 56  |

| 4 | Pro | posed Fully Hysteretic Single-Inductor Dual-Output Buck Converter | 59  |

|   | 4.1 | Dual-Output Power Supply                                          | 59  |

|   | 4.2 | Design Implementation                                             | 64  |

|   | 4.3 | Measured Performance                                              | 73  |

|   | 4.4 | State-of-the-Art Comparison                                       | 85  |

|   | 4.5 | Limitations                                                       | 87  |

|   | 4.6 | Summary                                                           | 88  |

| 5 | Pro | posed Single-Inductor Triple-Output Buck-Boost Power Supply       | 90  |

|   | 5.1 | Power-Supply System                                               | 90  |

|   | 5.2 | Design and Implementation                                         | 96  |

|   | 5.3 | Measured Performance                                              | 104 |

|   | 5.4 | State-of-the-Art Comparison                                       | 116 |

|   | 5.5 | Summary                                                           | 117 |

| 6 | Bal | ancing Speed and Accuracy with Proposed Hysteretic-PWM Control    | 120 |

|   | 6.1 | PWM-Hysteretic Power Supply System                                | 120 |

|   | 6.2 | Load Regulation Cross–regulation                                  | 122 |

|   | 6.3 | PWM Independent Loop Control                                      | 124 |

|   | 6.4 | Implementation                                                    | 129 |

|   | 6.5 | SIDO Measured Performance                                         | 140 |

|   | 6.6 | SIDO Comparison to Similar Single-Output                          | 142 |

|   | 6.7 | Summary                                                           | 146 |

| 7 Coi | nclusions                                         | 149 |

|-------|---------------------------------------------------|-----|

| 7.1   | Applications                                      | 149 |

| 7.2   | Single-Inductor Multiple-Output Converters (SIMO) | 150 |

| 7.3   | Research Objective                                | 152 |

| 7.4   | Research Contributions                            | 152 |

| 7.5   | Design Considerations                             | 159 |

| 7.6   | Publications                                      | 162 |

| 7.7   | Technological Challenges                          | 163 |

| 7.8   | Future SIMO Research                              | 164 |

| 7.9   | Conclusions                                       | 171 |

| 7.10  | SIMOs in the Future                               | 173 |

| 7.11  | Summary                                           | 174 |

| REFER | ENCES                                             | 176 |

| VITA  |                                                   | 189 |

# LIST OF TABLES

| Table 2.1. SoA Comparison of Mixed-Output (Buck & Boost) SIMO Converters. | 31  |

|---------------------------------------------------------------------------|-----|

| Table 2.2. SoA Comparison of Control schemes for SIMO Converters.         | 32  |

| Table 4.1. SoA Comparison of Control schemes for SIMO Converters.         | 86  |

| Table 5.1. SoA Comparison of Mixed Output (Buck & Boost) SIMO Converters. | 117 |

# LIST OF FIGURES

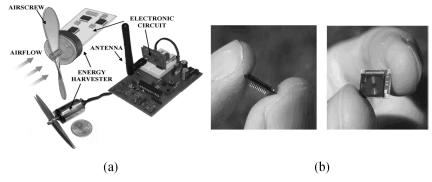

| Figure 1.1. Wireless microsystem examples: (a) air temperature and velocity monitor  |    |

|--------------------------------------------------------------------------------------|----|

| for industrial applications [3] © 2010 IEEE and (b) implantable neural recorder for  |    |

| biomedical applications [4] © 2009 IEEE.                                             | 1  |

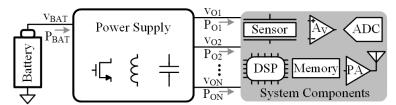

| Figure 1.2. Power management for wireless microsystems.                              | 2  |

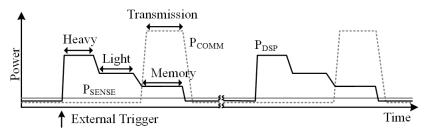

| Figure 1.3. Sample power profile of their function in a wireless microsystem.        | 4  |

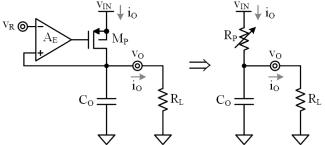

| Figure 1.4. Linear regulator for regulating a supply.                                | 6  |

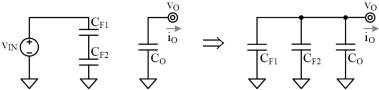

| Figure 1.5. Sample switched-capacitor converter with a series to parallel sequence.  | 7  |

| Figure 1.6. Switch-inductor converters in the buck (a) and boost (b) configuration.  | 8  |

| Figure 1.7. Power density of single-output supplies as a function of frequency [43]. | 10 |

| Figure 1.8. Quality vs energy density for integrated and external inductor [43].     | 11 |

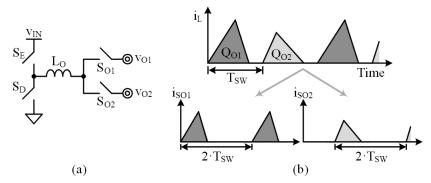

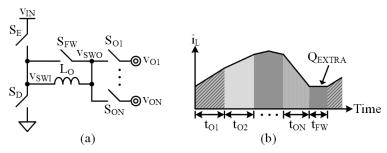

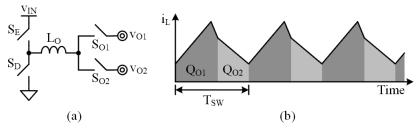

| Figure 2.1. A sample two-output SIMO (a) and dedicated energizing operation (b).     | 18 |

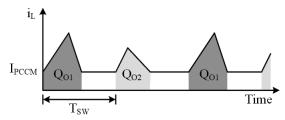

| Figure 2.2. Pseudo CCM operating mode to increase power delivery.                    | 19 |

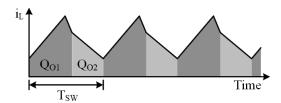

| Figure 2.3. Inductor current waveform during shared energy packet operation.         | 20 |

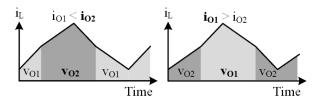

| Figure 2.4. Matching load to inductor current level reduces load-disparity cross     |    |

| regulation [69].                                                                     | 21 |

| Figure 2.5. Freewheeling period as an energy buffer based on [78].                   | 22 |

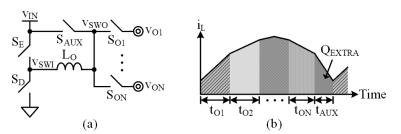

| Figure 2.6. Auxiliary output to reduce cross-regulation [73].                        | 22 |

| Figure 2.7. Power paths for mixed output generation on a SIMO.                       | 23 |

| Figure 2.8. Peak current control for SIMO converters (a) and operating waveforms     |    |

| (b).                                                                                 | 25 |

| Figure 2.9. PWM control for the independent voltage loops.                           | 26 |

| Figure 2.10. PWM control with current feed forward on independent loops.             | 26 |

| Figure 2.11. Peak voltage control for independent outputs.                                      | 27 |

|-------------------------------------------------------------------------------------------------|----|

| Figure 2.12. (a) Switching-linear hybrid converter with dedicated linear regulator on           |    |

| each output (a) and (b) PWM control scheme that multiplex between outputs [55].                 | 28 |

| Figure 2.13. Switching-linear hybrid converter with single linear shunt regulator for           |    |

| all outputs [82].                                                                               | 29 |

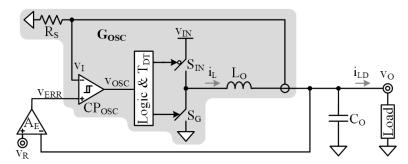

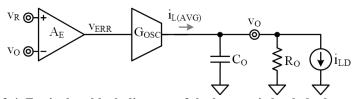

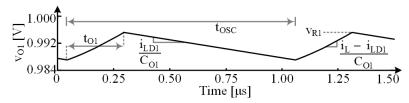

| Figure 3.1. Hysteretic current-mode switched-inductor buck dc-dc converter.                     | 37 |

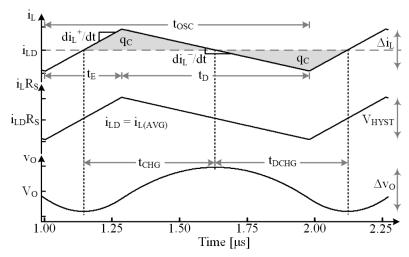

| Figure 3.2. Single-output steady-state waveforms of the hysteretic buck converter.              | 38 |

| Figure 3.3. Step response of inductor current $i_L$ and its $R_{EQ}C_{EQ}$ equivalent $i_L^*$ . | 40 |

| Figure 3.4. Equivalent block diagram of the hysteretic buck dc-dc converter.                    | 41 |

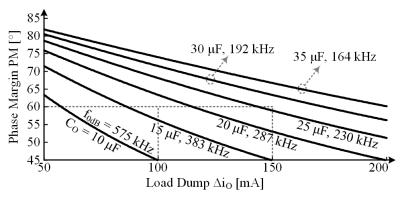

| Figure 3.5. Stability curves for a given capacitance and load dump size.                        | 43 |

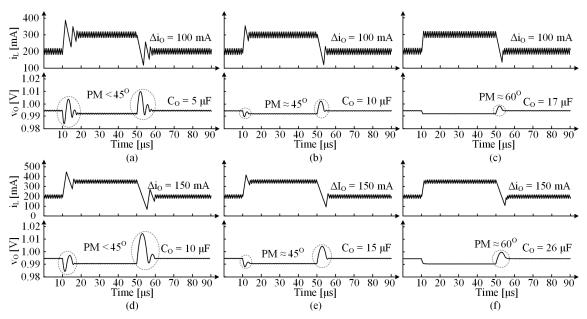

| Figure 3.6. Simulation of load dump response across various capacitance and load                |    |

| dump sizes                                                                                      | 43 |

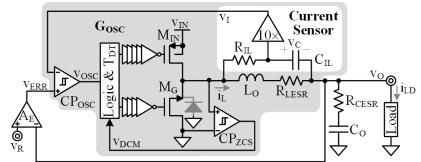

| Figure 3.7. Implemented hysteretic current-mode switched-inductor converter.                    | 45 |

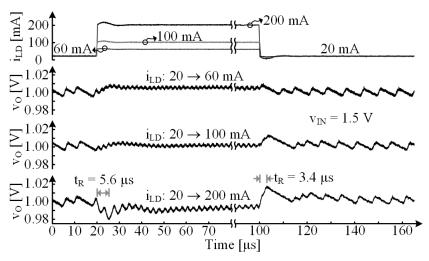

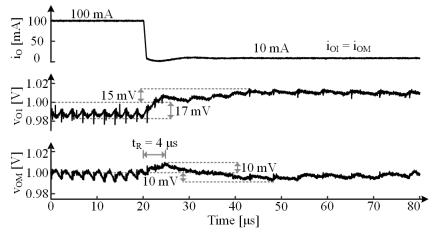

| Figure 3.8. Measured response to 40-, 80-, and 180-mA load dumps when input                     |    |

| voltage $v_{IN}$ is 1.5 V.                                                                      | 46 |

| Figure 3.9. Measured response to 180-mA load dump when input voltage $v_{\rm IN}$ is 1.4 $$     |    |

| and 1.8 V.                                                                                      | 46 |

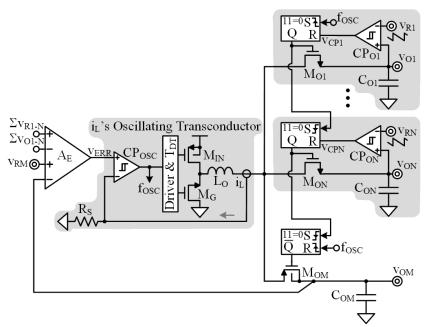

| Figure 3.10. Hysteretic current-mode SIMO buck converter.                                       | 47 |

| Figure 3.11. Simulated inductor current waveform for an evenly loaded 5-output                  |    |

| SIMO.                                                                                           | 48 |

| Figure 3.12. Simulated waveform of the first independent output in a 5-output SIMO.             |    |

|                                                                                                 | 49 |

|                                                                                                 |    |

| outputs.                                                                                | 49 |

|-----------------------------------------------------------------------------------------|----|

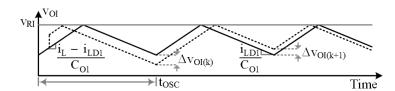

| Figure 3.14. Simulated peak-voltage control showing sub-harmonics oscillations and      |    |

| compensated waveform.                                                                   | 50 |

| Figure 3.15. Equivalent small-signal model of peak-voltage control of independent       |    |

| outputs.                                                                                | 50 |

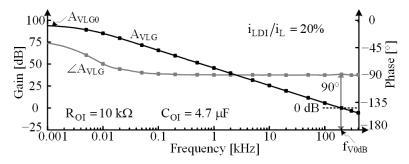

| Figure 3.16. Simulated Bode response of peak-voltage control.                           | 51 |

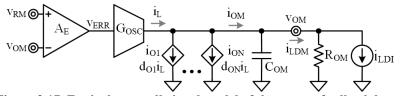

| Figure 3.17. Equivalent small-signal model of the master feedback loop.                 | 52 |

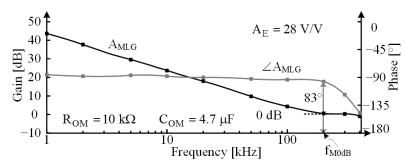

| Figure 3.18. Simulated small-signal master feedback's loop gain for a 5-output          |    |

| SIMO.                                                                                   | 54 |

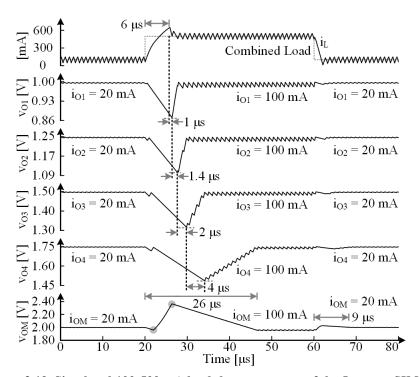

| Figure 3.19. Simulated 100-500 mA load-dump response of the 5-output SIMO.              | 55 |

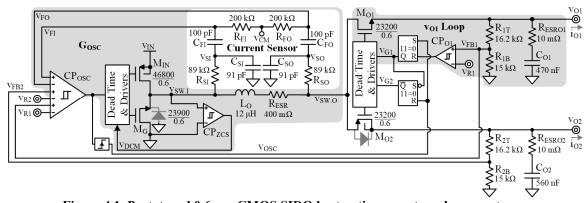

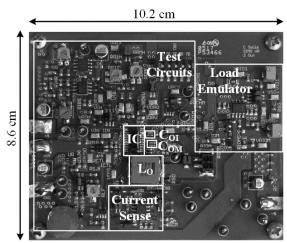

| Figure 4.1. Prototyped 0.6-μm CMOS SIDO hysteretic current-mode converter.              | 60 |

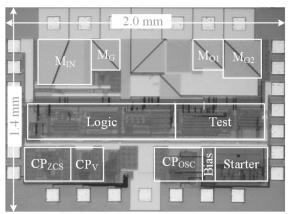

| Figure 4.2. Die of prototyped 0.6-μm CMOS SIDO converter.                               | 61 |

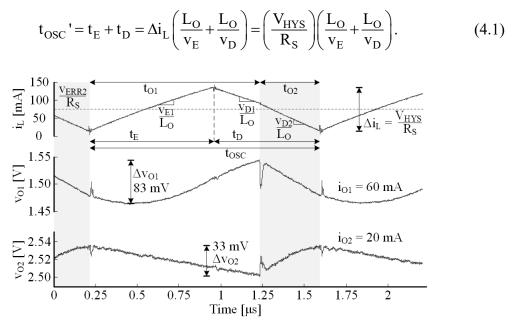

| Figure 4.3. Measured steady-state waveform in continuous-conduction mode.               | 62 |

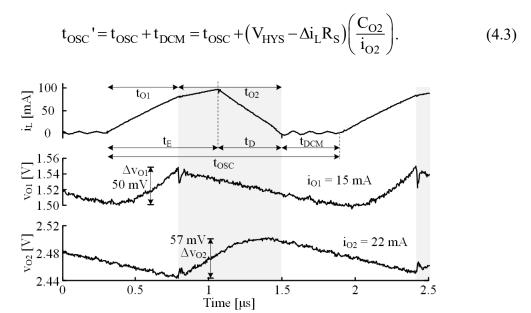

| Figure 4.4. Measured steady-state waveform discontinuous-conduction mode.               | 63 |

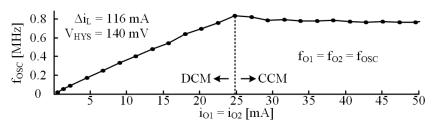

| Figure 4.5. Measured oscillating frequency with balanced loads                          | 64 |

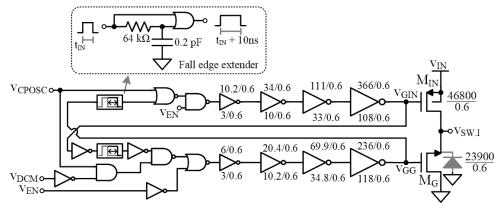

| Figure 4.6. Implementation of dead time generator and drivers for the input side        |    |

| switches.                                                                               | 65 |

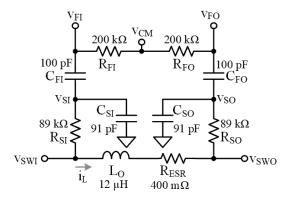

| Figure 4.7. Current sensing and filter circuit.                                         | 66 |

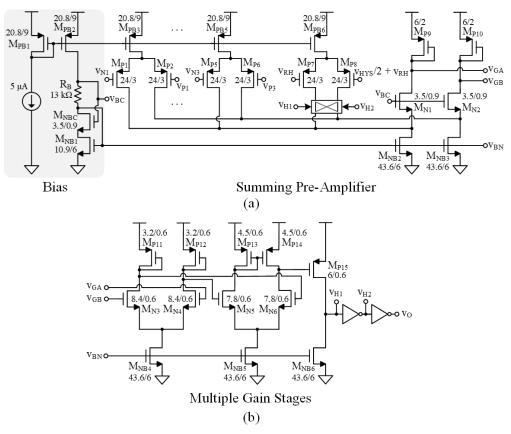

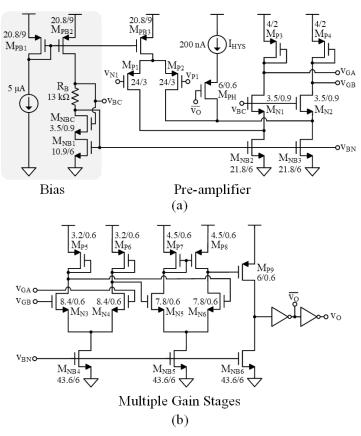

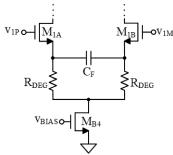

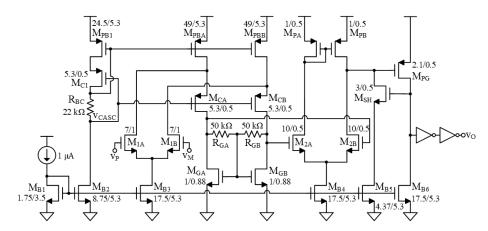

| Figure 4.8. (a) Summing pre-amplifier stage and its bias, and (b) multiple stages       |    |

| afterwards of summing comparator CP <sub>OSC</sub> .                                    | 69 |

| Figure 4.9. (a) Pre-amplifier stage and its bias, and (b) multiple stages afterwards of |    |

| comparator CP <sub>O1</sub> .                                                           | 71 |

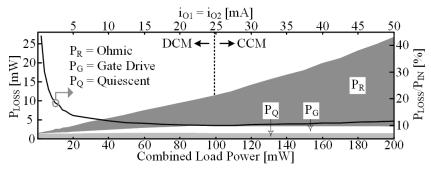

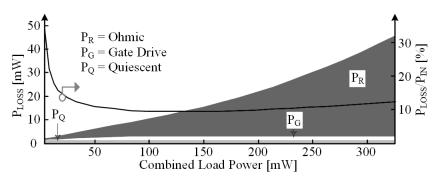

| Figure 4.10. Simulated power losses with balanced losses.                               | 73 |

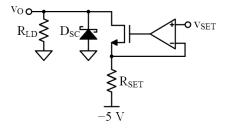

| Figure 4.11. Flexible high-bandwidth load emulation circuit.                  | 74 |

|-------------------------------------------------------------------------------|----|

| Figure 4.12. Two-layer board for prototype testing.                           | 75 |

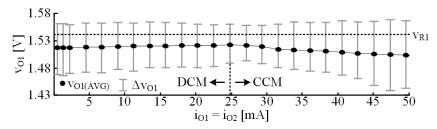

| Figure 4.13. $v_{O1}$ 's measured load regulation with balanced loads.        | 76 |

| Figure 4.14. v <sub>O2</sub> 's measured load regulation with balanced loads. | 77 |

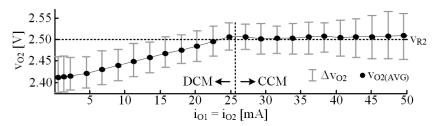

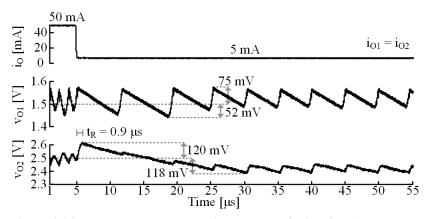

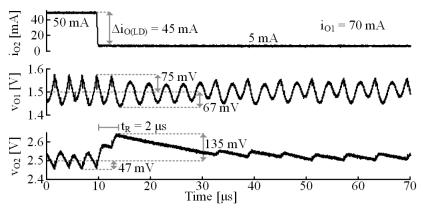

| Figure 4.15. Measured response to simultaneous rising 45-mA load steps.       | 78 |

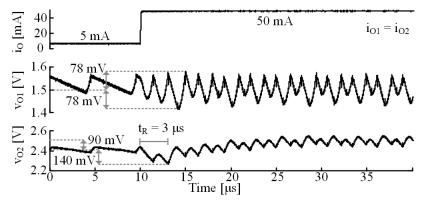

| Figure 4.16. Measured response to simultaneous falling 45-mA load step.       | 78 |

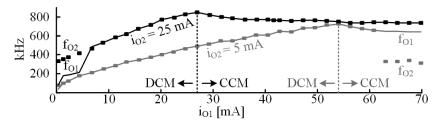

| Figure 4.17. Outputs' switching frequencies across unbalanced load levels.    | 80 |

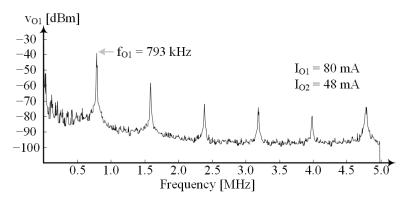

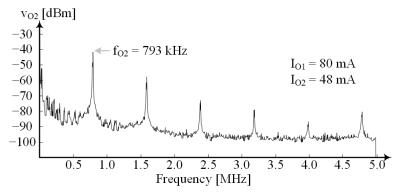

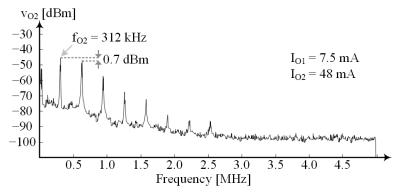

| Figure 4.18. Frequency spectrum of output $v_{\rm O1}$ with balanced loads.   | 81 |

| Figure 4.19. Frequency spectrum of output $v_{\rm O2}$ with balanced loads.   | 81 |

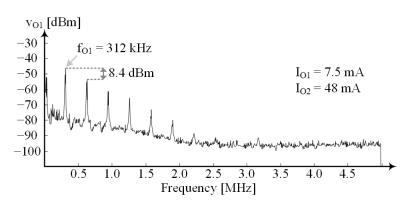

| Figure 4.20. Frequency spectrum of output $v_{\rm O1}$ with unbalanced loads. | 82 |

| Figure 4.21. Frequency spectrum of output $v_{\rm O2}$ with unbalanced loads. | 82 |

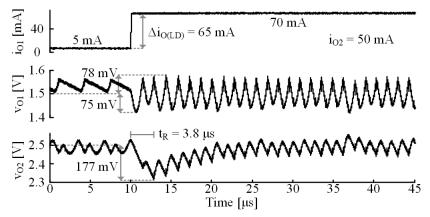

| Figure 4.22. Measured response to a rising 65-mA load step at $v_{\rm O1}$ .  | 83 |

| Figure 4.23. Measured response to a falling 65-mA load step at $v_{\rm O1}$ . | 83 |

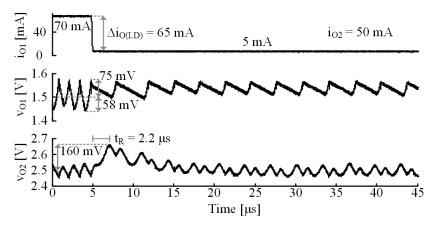

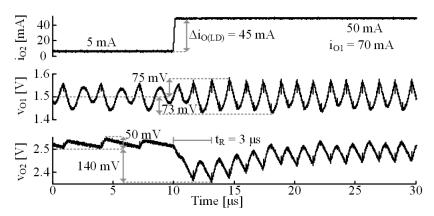

| Figure 4.24. Measured response to a rising 45-mA load step at $v_{\rm O2}$ .  | 84 |

| Figure 4.25. Measured response to a falling 45-mA load step at $v_{\rm O1}$ . | 85 |

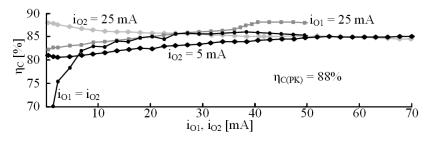

| Figure 4.26. Measured power-conversion efficiency across load levels.         | 85 |

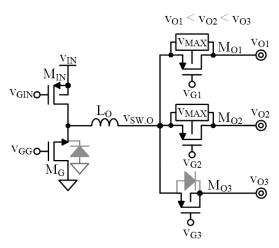

| Figure 5.1. One-inductor triple-output buck-boost power supply.               | 92 |

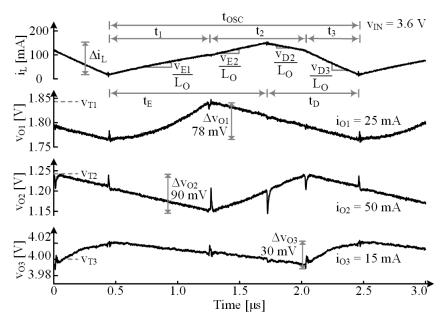

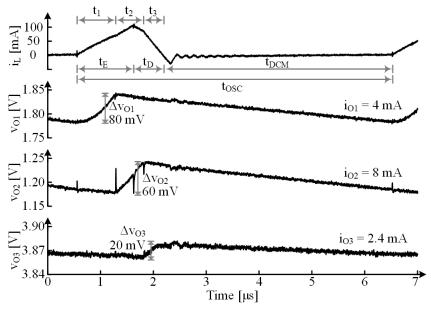

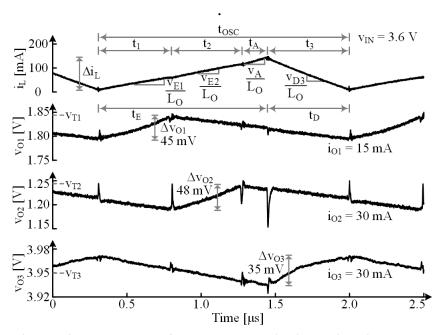

| Figure 5.2. Measured waveforms when operating in the five-switch mode.        | 93 |

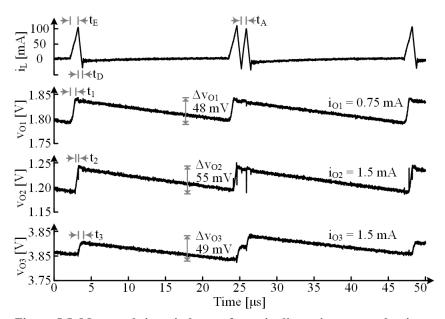

| Figure 5.3. Measured waveforms in discontinuous conduction.                   | 94 |

| Figure 5.4. Measured waveforms when operating in the six-switch mode.         | 94 |

| Figure 5.5. Measured six-switch waveforms in discontinuous conduction.        | 95 |

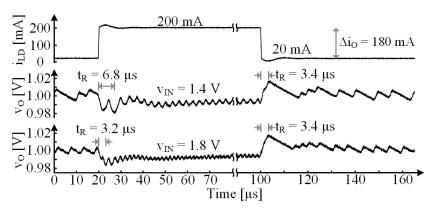

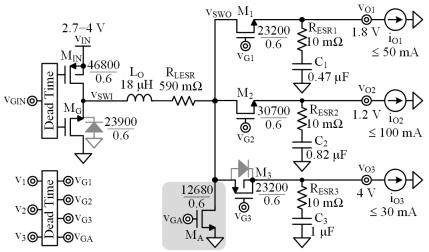

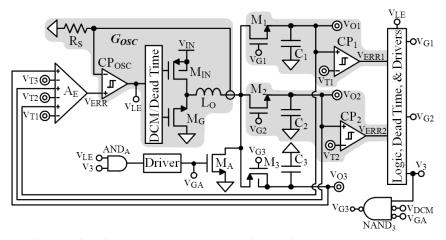

| Figure 5.6. Triple-output buck-boost switched-inductor supply system.         | 97 |

| Figure 5.7. Logic to engage and turn off output v <sub>O1</sub> .             | 98 |

| Figure 5.8. Logic to engage and turn off output $v_{O2}$ .                         | 98  |

|------------------------------------------------------------------------------------|-----|

| Figure 5.9. Logic to engage and turn off output $v_{\rm O3}$ .                     | 99  |

| Figure 5.10. Drivers and dead-time generator for outputs' switches.                | 100 |

| Figure 5.11. Simulated losses of the triple-output buck-boost converter.           | 102 |

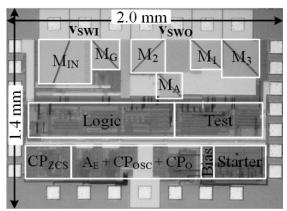

| Figure 5.12. Prototyped 0.6-μm CMOS die.                                           | 104 |

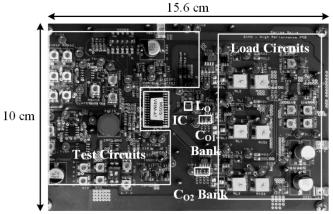

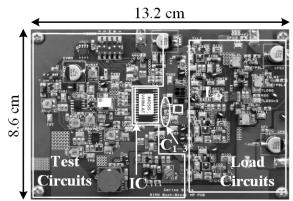

| Figure 5.13. Two-layer board for testing buck-boost prototype.                     | 105 |

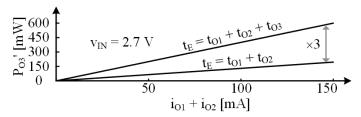

| Figure 5.14. Theoretical and measured maximum boost power with five switches       |     |

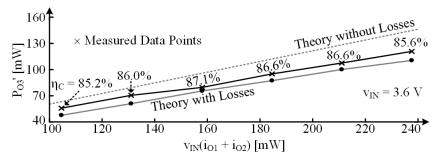

| when $v_{IN}$ is 3.6 V.                                                            | 107 |

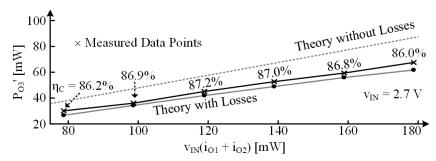

| Figure 5.15. Theoretical and measured maximum boost power with five switches       |     |

| when $v_{IN}$ is 2.7 V.                                                            | 107 |

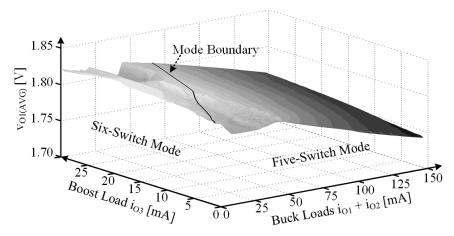

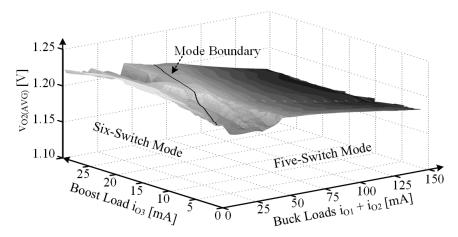

| Figure 5.16. Measured load regulation for output v <sub>O1</sub> .                 | 108 |

| Figure 5.17. Measured load regulation for output $v_{\rm O2}$ .                    | 109 |

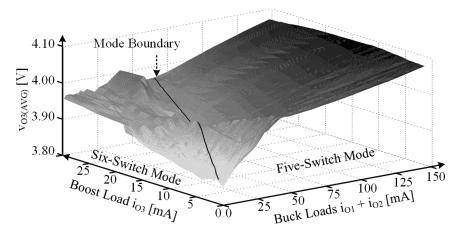

| Figure 5.18. Measured load regulation for output $v_{\rm O3}$ .                    | 109 |

| Figure 5.19. Loss comparison of simulated and measured efficiency during five-     |     |

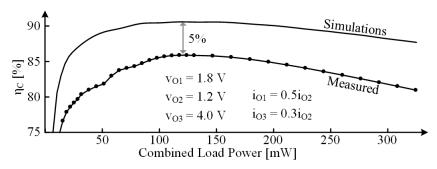

| switch operation.                                                                  | 110 |

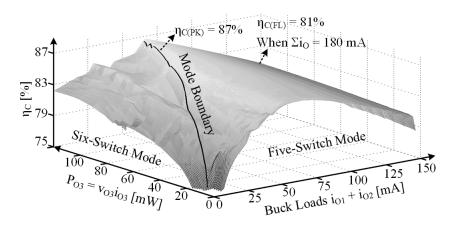

| Figure 5.20. Measured power-conversion efficiency across load power.               | 111 |

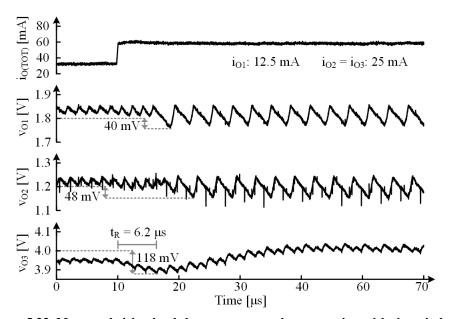

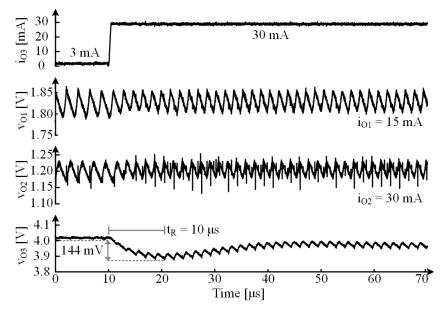

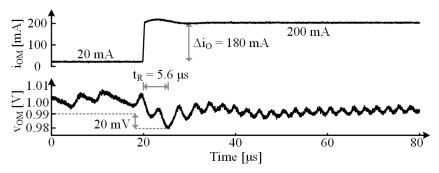

| Figure 5.21. Measured rising load-dump response when operating with five switches. |     |

|                                                                                    | 112 |

| Figure 5.22. Measured falling load-dump response when operating with five          |     |

| switches.                                                                          | 112 |

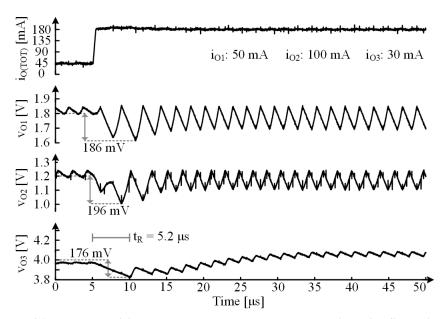

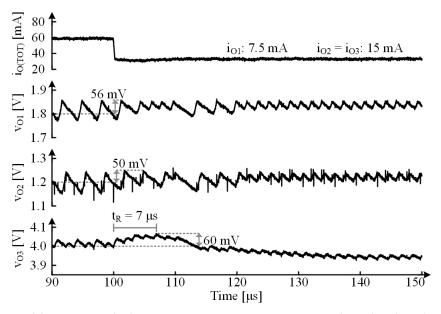

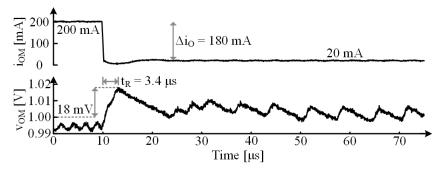

| Figure 5.23. Measured rising load-dump response when operating with six switches.  |     |

|                                                                                    | 113 |

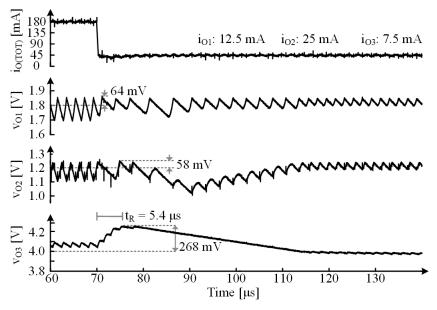

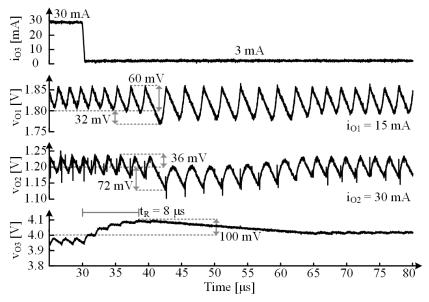

Figure 5.24. Measured falling load-dump response when operating with six switches.

|                                                                                                        | 114 |

|--------------------------------------------------------------------------------------------------------|-----|

| Figure 5.25. Measured rising load-dump response across switching modes.                                | 115 |

| Figure 5.26. Measured falling load-dump response across switching modes.                               | 115 |

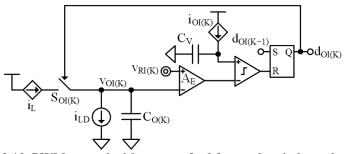

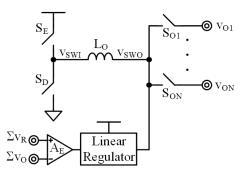

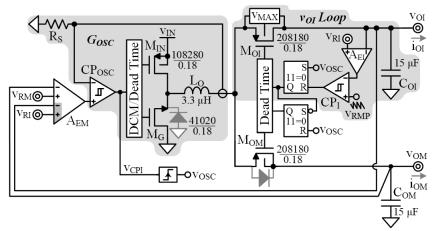

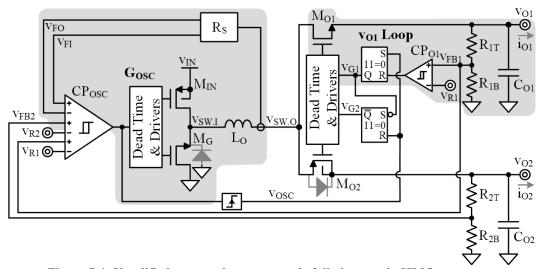

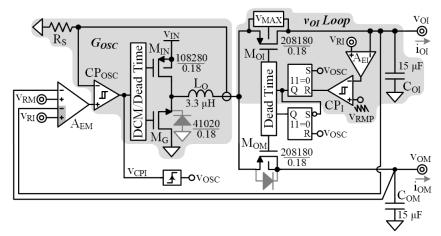

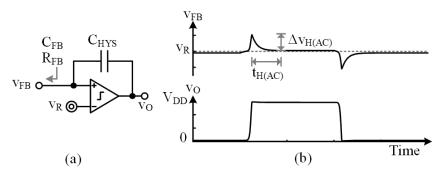

| Figure 6.1. Proposed PWM-Hysteretic dual-output power supply system.                                   | 121 |

| Figure 6.2. Measured waveforms of proposed PWM-hysteretic dual-supply.                                 | 121 |

| Figure 6.3. Simulated load regulation of $v_{\text{OI}}$ and cross–regulation to $v_{\text{OM}}$ while |     |

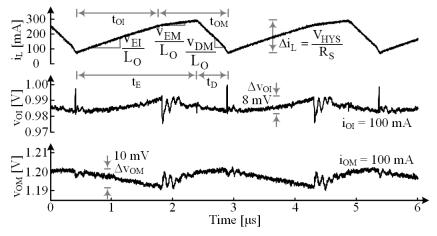

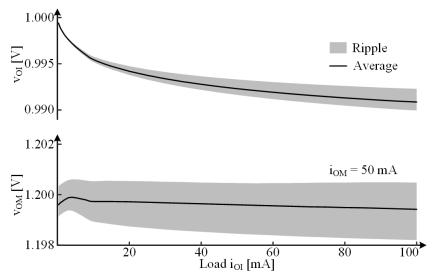

| summing all frequency components of $v_{\text{OI}}$ in the current loop.                               | 123 |

| Figure 6.4. Simulated load regulation of $v_{\text{OI}}$ and cross–regulation to $v_{\text{OM}}$ while |     |

| summing all frequency components higher than $8kHz$ of $v_{OI}$ in the current loop.                   | 124 |

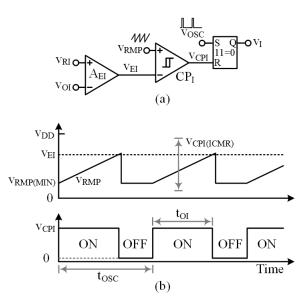

| Figure 6.5. PWM control for independent output $v_{OI}\left(a\right)$ schematic and (b) operating      |     |

| waveforms.                                                                                             | 125 |

| Figure 6.6. Measured response to simultaneous rising 90-mA load dumps.                                 | 128 |

| Figure 6.7. Measured response to simultaneous falling 90-mA load dumps.                                | 128 |

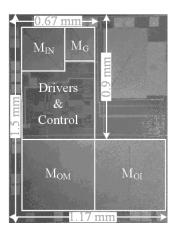

| Figure 6.8. Die of proposed PWM-hysteretic controller in 0.18 $\mu m$ CMOS process.                    | 129 |

| Figure 6.9. Testing PCB to measure performance of the dual-supply system.                              | 130 |

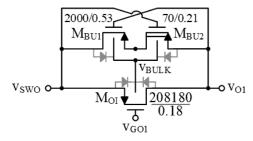

| Figure 6.10. Circuit to bias bulk of power switch of independent output $v_{\rm OI}$ .                 | 131 |

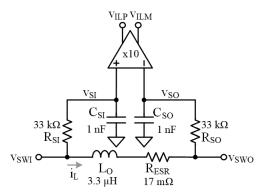

| Figure 6.11. Current sensor implementation for low voltage converters.                                 | 133 |

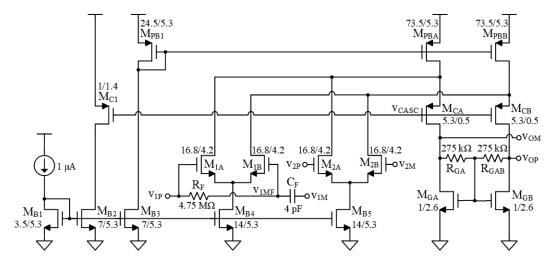

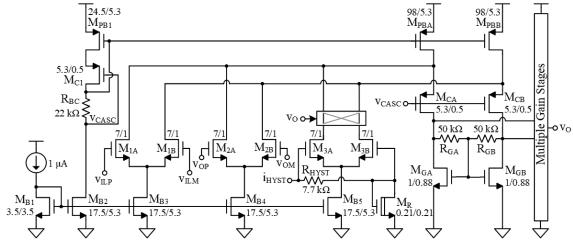

| Figure 6.12. Summing amplifier $A_{EM}$ implementation in 0.18 $\mu m$ CMOS process.                   | 133 |

| Figure 6.13 Filtered summing implementation alternative.                                               | 135 |

| Figure 6.14. Pre–amplification of hysteretic comparator CP <sub>OSC</sub> of the current loop.         | 135 |

| Figure 6.15. PWM loop's A <sub>EI</sub> implementation.                                                | 137 |

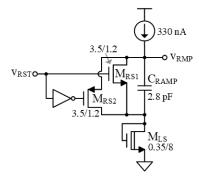

| Figure 6.16. Modulating ramp for PWM control of independent voltage $v_{\rm OI}$ .                     | 137 |

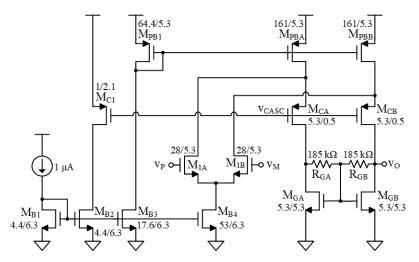

| Figure 6.17. PWM loop's CP <sub>I</sub> CMOS implementation.                                           | 138 |

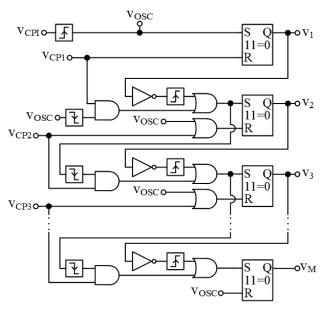

| Figure 6.18. Scalable output logic that sequences the output by priority.           | 139 |

|-------------------------------------------------------------------------------------|-----|

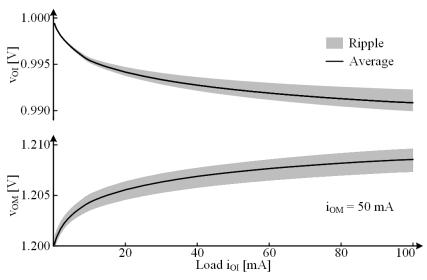

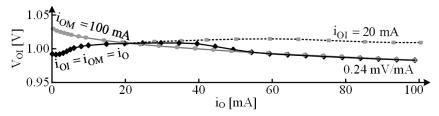

| Figure 6.19. Measured load regulation of independent output $v_{\text{OI}}$ .       | 140 |

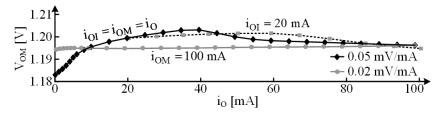

| Figure 6.20. Load regulation of master output $v_{\rm OI}$ .                        | 141 |

| Figure 6.21. Efficiency of PWM-hysterteic SIDO supply system.                       | 142 |

| Figure 6.22. Conversion efficiency comparison between single and dual supplies.     | 143 |

| Figure 6.23. Ripple comparison between single and dual supplies.                    | 144 |

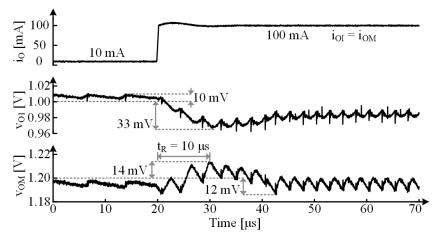

| Figure 6.24. Measured dynamic response for a rising load dump in the dual-supply    |     |

| system.                                                                             | 145 |

| Figure 6.25. Measured dynamic response for a falling load dump in the dual-supply   |     |

| system.                                                                             | 145 |

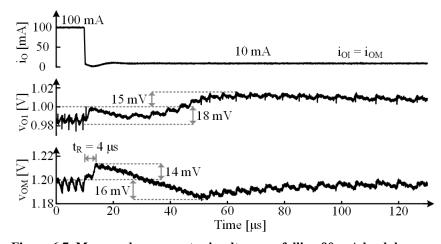

| Figure 6.26. Measured dynamic response for a rising load dump in the single-supply  |     |

| system.                                                                             | 146 |

| Figure 6.27. Measured dynamic response for a falling load dump in the single-supply |     |

| system.                                                                             | 146 |

| Figure 7.1. (a) A dual-output converter and (b) its operating waveform when sharing |     |

| the energy packet.                                                                  | 150 |

| Figure 7.2. (a) Current-mode PWM control to regulate energy in inductor and (b) its |     |

| operation waveform; and (c) PWM control to regulate voltage on the independent      |     |

| loops.                                                                              | 151 |

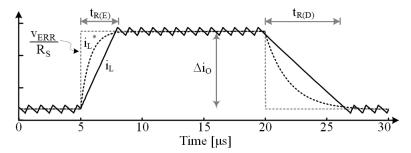

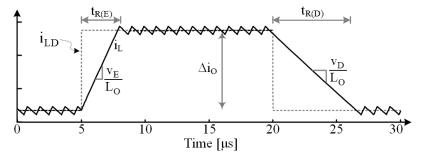

| Figure 7.3. Slew response of inductor current with hysteretic control.              | 153 |

| Figure 7.4. Simplified proposed current-mode fully hysteretic SIMO converter.       | 154 |

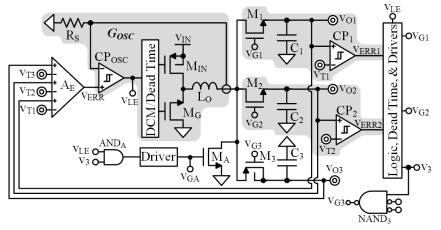

| Figure 7.5. Proposed current-mode fully hysteretic buck-boost SIMO converter.       | 157 |

| Figure 7.6. Hysteretic current-mode SIMO with independent PWM loops.                | 158 |

| Figure                                                                         | 7.7.    | Single-inductor      | multiple-input    | multiple-output     | converter     | for   |

|--------------------------------------------------------------------------------|---------|----------------------|-------------------|---------------------|---------------|-------|

| microsy                                                                        | stems   | applications.        |                   |                     |               | 165   |

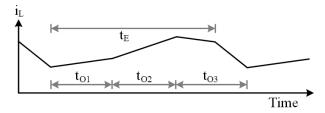

| Figure 7                                                                       | 7.8. Co | nverter operation    | by extending ene  | rgizing time to boo | osted output. | . 166 |

| Figure 7                                                                       | '.9. Ma | aximum deliverable   | e boosted power v | when energizing or  | nly through b | ouck  |

| outputs and extended comparison.                                               |         |                      |                   |                     |               | 167   |

| Figure 7.10. Power stage for output switches zero-voltage switching technique. |         |                      |                   |                     |               | 168   |

| Figure 7.11. Operating waveform for output switches with zero-volt switching.  |         |                      |                   |                     |               | 169   |

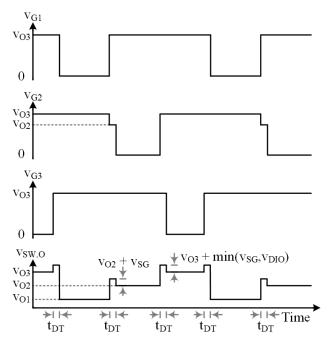

| Figure 7                                                                       | '.12. A | .C hysteresis (a) sc | hematic and (b)   | operating waveform  | ms for hyster | retic |

| control                                                                        | on ind  | ependent outputs.    |                   |                     |               | 171   |

# **SUMMARY**

Portable electronics such as wireless microsystems incorporate functions such as sensing, data processing, and transreceiver that allows adding intelligence, improve use of resources and even saves lives. These systems are powered by tiny batteries to achieve a small overall solution to reduce costs and allow a large deployment of microsystems. These various functionalities in these systems require different supply levels optimized for their respectively technology used and performance requirements. Moreover, as battery depletes and for transmitting signals with enough power over large distances, regulating a boosted supply from the battery becomes necessary. In addition, the voltage levels can be dynamic to optimize for the instantaneous workload of the function and the system might duty cycle blocks when not in use to conserve energy. These system designs impose stricter requirements on the power-supply system on board since it must quickly react to load dumps and changes in supply levels in a compact and cheap solution. The incorporated tiny battery exacerbates the challenges as power losses must be minimized to prevent a costly battery replacement.

The objective of this research is to investigate, develop, test and evaluate a compact and efficiency power converter capable of regulating buck and boost voltages while quickly responding to load dumps. Among power converter topologies, switched-inductor converters achieve the highest efficiency across operating conditions. However, inductors are bulky and difficult to integrate and therefore limiting the power converter to a single inductor while regulating multiple outputs balances size and efficiency. The fundamental challenge is in the operation and sharing of the single inductor to generate buck and boost voltages, increase regulation bandwidth and reduce cross-regulation between outputs.

Literature commonly uses the well-understood PWM to accurately regulate multiple supplies in a SIMO; however, its takes multiple switching cycles to respond and correct the output after a load dump. Luckily, hysteretic current-mode control achieves good dynamic performance but literature has not analyzed its stability and applied it to SIMO converters. A fully hysteretic control for SIMO achieves a fast response closest to the fast but inefficient linear regulators.

A boosted output from a buck power stage is possible without changing operation. Fundamentally, as long inductor energizes through buck outputs, it can energize through any buck and boost outputs without changing operation. However, a limited quantity power can be boosted, and therefore an auxiliary switch is proposed when a higher boosted power must be delivered. Although hysteretic control has good dynamic response, it is noise sensitive as it regulates instantaneous signal. Therefore, a novel PWM—hysteretic hybrid control is proposed for applications that have stricter noise requirements that balances the good dynamic performance of hysteretic control with accuracy of a PWM control.

This dissertation starts by discussion motivation, and benefits and challenges of switched-inductor converters in Chapter 1. Chapter 2 reviews the literature and discusses the state-of-the-art control and operation of single-inductor multiple-output (SIMO) converters with their benefits and disadvantages for portable electronics. Chapter 3 analyses the stability and discusses the design of hysteretic current-mode control for single-output converter at first; and then expand it for SIMOs. Chapter 4 presents the proposed fully hysteretic control for SIMOs that achieves a fast response time while having a low silicon real state per output. Chapter 5 elaborates on how to generate a boosted output from a buck power stage without altering its operation under certain restrictions. Therefore, this

allows to conserve the efficiency by avoiding using a buck-boot power stage operation unless necessary. Chapter 6 discusses the noise sensitivity challenge of the hysteretic control and then proposes a hybrid PWM-hysteretic control that balances response time while having lower noise sensitivity. Finally, Chapter 7 summarizes the resulting contributions of this research along with the technical challenges and future research directions.

# CHAPTER 1

# POWERING MULTIFUNCTIONAL MICROSYSTEMS

# 1.1 Emerging Applications

Current trends in portable electronics increases the integrated functionalities and capabilities in products such as laptops, tablets, phones, and networked microsystems. Specifically, networked (or wireless) microsystems can sense, process, store, transmit, and receive information in hospitals, factories, farms, and homes and can save lives, energy, and money [1–9]. As an example, Figure 1.1 (a) shows an air quality monitor for industrial applications by sensing temperature and velocity [3]. Also, Figure 1.1 (b) shows an implantable wireless neural recorder that circumvent limitations of wired versions during brain studies [4]. These wireless microsystems have the advantage on reaching tough places like the inside of walls or the human body for monitoring and reporting. Therefore, it is imperative for microsystems to be as small as possible to be non-intrusive and avoid frequent, if any, battery replacement by extending battery life.

Figure 1.1. Wireless microsystem examples: (a) air temperature and velocity monitor for industrial applications [3] © 2010 IEEE and (b) implantable neural recorder for biomedical applications [4] © 2009 IEEE.

These microsystems generally have three main functionalities: sensing, data processing, and communication. Sensing has an analog interface to the real world and commonly an analog-to-digital converter (ADC) for a digital-signal processor (DSP) to process the information. These can be implemented in a low-cost CMOS technology and either on the same or separate dies. Finally, wireless communication for these microsystems requires a power amplifier (PA) which can output enough power to communicate over the required distance required.

Unfortunately, higher cost technologies, such as GaAs and InP, implement the PA to transmit high enough power at fast communication speeds [10]. These technologies achieve high performance in a PA because they can tolerate higher voltages in the range of 4–5 V [11]. These high voltages reduces current levels during transmission and therefore losses [12], while maintaining high mobility in transistors for higher bandwidth. In the other hand, DSPs are low voltage and noise tolerant, so noisy 0.5–1-V power supplies can drive them to conserve energy [13–14]. Sensors and ADCs, on the other hand, usually require higher supplies with lower noise content to keep a high signal to noise ratio [15]. Efficient power-supply systems, like Figure 1.2 illustrates, must therefore supply and regulate several outputs for all these functions [16–17].

Figure 1.2. Power management for wireless microsystems.

A battery provides energy and portability for these systems but different chemistries provide a wide range of voltages to regulate from. Also, as the battery drains and its state of charge changes, so is their voltage. For example, a high energy-density chemistry as lithium-ion batteries can have a voltage between 2.7–4.2 V depending of its state of charge [18]. This would require the power supply to boost a voltage for the PA to use, while regulating a supply lower than the battery voltage for the other functions. Hence, the power supply must supply a mix of buck (step-down) and boost (step-up) voltages.

The overall size of these networked microsystems need to be compact and non-intrusive, and thus battery is often small with limited energy storage which makes battery lifetime becomes a challenge. In despite work to harvest ambient energy to extend battery lifetime [19–22], ambient energy is limited or often not continuously abundant; therefore, an efficient power converter is imperative to preserve energy regardless if the system harvests ambient energy. Plus, tiny batteries cannot sustain power for long, so even though DSPs, ADCs, and power amplifiers (PAs) can tolerate higher voltages, they (for the sake of saving energy) should not as long as they meet performance requirements [23].

## 1.2 Power Management Requirements

To conserve the limited energy in wireless microsystems, there exists two main approaches at the system level: block duty-cycling and dynamic voltage scaling (DVS). Block duty-cycling turns off or idle blocks when they are unnecessary for the proper operation of the system [24–26]. For instance, while the system waits for an external trigger, the digital processing and communication blocks can be turned off, until they are necessary to process and transfer data like Figure 1.3 shows. On the other hand, DVS minimizes the power

consumption without sacrificing required throughput by adjusting supply voltage [27–29]. Figure 1.3 displays voltage scaling on the digital signal processor power profile P<sub>DSP</sub> that during heavy processing it has the highest supply voltage and decreases when the computation demand reduces. Moreover, process variation can affect the optimal supply power efficient throughput such as in multi-core applications [14], [30]. Hence a higher supply granularity provides more flexibility for a more efficient system as long as the performance degradation does not overwhelms energy loss reduction given the added complexity [31].

Figure 1.3. Sample power profile of their function in a wireless microsystem.

These system-level energy-savings techniques imposes tougher efficiency and accuracy requirements on the power supply. Since the maximum to idle power consumption ratio can be large, the converter must be efficient across the wide load range. Otherwise, battery can excessively discharge during short operation at maximum capacity or long idling (or standby) periods. Thus, the converter must have high power conversion efficiency across a wide output load range. This means that besides a power converter having a high peak conversion efficiency  $\eta_{C(PK)}$ , it should also have a high average efficiency  $\eta_{C(AVG)}$  across the power range, or a high full-load efficiency  $\eta_{C(FL)}$  depending on the most likely power profile for a given application.

Regulation accuracy become more constrained since either block-duty cycle or DVS also requires the converter to quickly provide energy demanded to the corresponding function. When waking up from an idling state, for instance, latency reduces efficient use of energy resources and functions as they wait for the supply to settle [32]. Moreover, the supply regulator should follow the optimum target, under DVS operation, to minimize losses as long as energy savings outweighs losses from increasing tracking speed [33]. Hence, each output of the power converter needs a high bandwidth to handle fast full-load transients while maintaining a high efficiency across a wide range of loads.

## 1.3 Power Supplies

Potential power converters topologies include non-switching options such as linear regulator that is a simple linear system and produces negligible noise. Another set of option are switching topologies like the switched-capacitor and switched-inductor variations, although noisy they are more efficient. Each has their own advantages and disadvantages that must be weighted in for each microsystems application.

## 1.3.1 Linear Regulators

A linear regulator consist of a pass transistor M<sub>P</sub> which resistance is modulated to regulate the output voltage to the target like Figure 1.4 depicts. Deploying dedicated linear regulators to each block is a compact solution and can accurately regulate at a high bandwidth [34–35]. Also, since linear regulators is a linear system, they tend to have a simpler design and stabilization for high bandwidth contrary to switching converters.

Figure 1.4. Linear regulator for regulating a supply.

Unfortunately, linear regulators tend to be lossy since the modulated resistance  $R_P$  absorbs considerable ohmic losses by sitting across input voltage  $v_{IN}$  and output voltage  $v_{O}$ . Its conversion efficiency  $\eta_{C(LR)}$  depends linearly on the output power  $P_{O}$  or  $v_{O}i_{O}$  divided by the input power  $P_{IN}$ . Since all output current  $i_{O}$  flows through the pass transistor  $M_P$  and originates at  $v_{IN}$ ,  $P_{IN}$  depends on output load  $i_{O}$ . In addition, quiescent power  $P_{Q}$  from the control also comes from the input supply  $v_{IN}$ . In the ideal case where there is no quiescent power  $P_{Q}$ ,  $\eta_{C(LR)}$  is theoretically limited by the output voltage  $v_{O}$  to input voltage  $v_{IN}$  ratio:

$$\eta_{C(LR)} = \frac{P_O}{P_{IN}} = \frac{v_O i_O}{v_{IN} (i_O + i_Q)} < \frac{v_O}{v_{IN}}.$$

(1.1)

For applications where input to output voltage spread is large, their low efficiency will shorten battery life as operating condition changes. In addition, linear regulators can only regulate voltages below the battery voltage, or in other words, can only buck. These drawbacks limit their use among applications requiring high efficiency and at least one boosted supply such as in wireless microsystems.

# 1.3.2 Switched-Capacitor Converters

Switching converters incorporate switches with low voltage across when closed to reduce conduction losses. Therefore, switched capacitor supplies have higher efficiency than

linear regulators and although they occupy a larger silicon real estate than linear regulators, they can be fully integrated [36–37]. Switched capacitors can either buck or boost supplies depending how its flying capacitor is charge and discharged. For instance, Figure 1.5 depicts a series to parallel sequence that downconverters a supply from the input.

Figure 1.5. Sample switched-capacitor converter with a series to parallel sequence.

For every state in the sequence, the converter will charge each capacitance to a certain voltage as a function of the input and output voltages. This means that every switching sequence has an associated voltage gain, e.g. Figure 1.5 has a voltage input-to-output translation of 0.5 V/V. The converter regulates the output by replenishing the flying capacitor(s), C<sub>F1</sub> and C<sub>F2</sub> in Figure 1.5, and the output capacitor more frequently or reconfiguring gain stages in between cycles [38]. As load increases, so is ripple voltage and thus the charge to be replenished on the capacitors. This will slightly increase the voltage across switches during charge redistribution because capacitor's voltages will be farther apart, hence increasing losses.

When the power-stage gain does not match input to output voltage vo, irrespective of load level, the converter regulates by allowing more ripple voltage. This decreases efficiency as the required voltage conversion mismatches the power stage gain [38–39]. Therefore, efficiency will be dependent on the output to input voltage although to a much lesser degree than linear regulators. Topologies with modifiable gain stages moderately increase efficiency at the expense of design complexity and more switches [38]. Also,

integrated switched capacitors have an additional loss due to their bottom plate capacitance, which further degrades the efficiency unless expensive technologies or manufacturing steps are used such as deep trench capacitors [40–42].

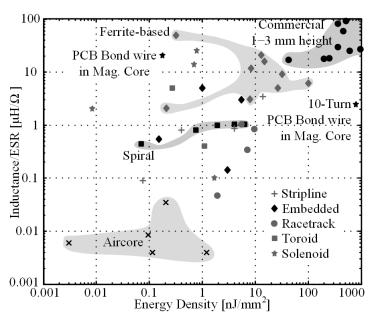

#### 1.3.3 Switched-Inductor Converters

Switched-inductor converters adjust the inductor current to satisfy the output demand and replenish the output capacitor. It does so by switching the voltage across the inductor in alternating cycles by engaging and disengaging switches. The voltage across engaged switches can be minimum unlike a switched-capacitor converter, hence switched-inductor converter can achieve a higher efficiency among the power topologies considered for a wider range of operating conditions such as input and output voltages, and load currents. The switched-inductor converter can either buck or boost depending in the switch configuration like in Figure 1.6.

Figure 1.6. Switch-inductor converters in the buck (a) and boost (b) configuration.

The switched-inductor converter is the most suitable power topology for power management in a wireless microsystem. Minimizing losses is imperative when operating from a tiny battery with a wide range of battery voltage and regulation voltages which switched-inductors can provide. However, as Figure 1.6 shows, it requires two passives which present some challenges due to the required compactness on the overall system

specially if multiple regulated supplies are required in microsystem applications or portable electronics in general.

#### 1.4 Challenges

Although switched-inductor converters provide high efficiency, they have integration challenges. Since they require at least two passives, i.e. a capacitor and inductor, it is difficult to integrate both on the same die at a reasonable cost. Also, generating a multiple-output solution based in a switched-inductor converter add more technical challenges to be addressed such as the optimum way to share the inductor.

#### 1.4.1 Miniaturization

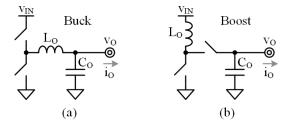

Unfortunately, integration of a switched-inductor converter is challenging. Research has been conducted to integrate the passives, i.e. inductor and capacitor, in the same integrated circuit (IC). Figure 1.7 summarizes state of the art switching converter using the literature survey reported in [43]. There are 4 main categories of integration: product modules (PCB), system-in-package (SiP), and system-on-chip (SoC) solutions. Products modules tend to have a lower power density because they require external passives. Increasing the switching frequency decreases the size of the required passives until the point they are possible to co-package in a SiP solution and hence, more power density. There is active research as well as products in a SiP solution (or SiPP), like in Figure 1.7 (b), that shows performance close to product modules. However, increasing switching frequency beyond 10 MHz allows passives to be small enough to be integrated in the same die in a SoC design and ultimately improving power density; however, it is at the expense of higher switching

losses. The efficiency drop can be in the order of 10–30% due to the increased switching-related losses of switches and quiescent power [44–46].

Figure 1.7. Power density of single-output supplies as a function of frequency [43].

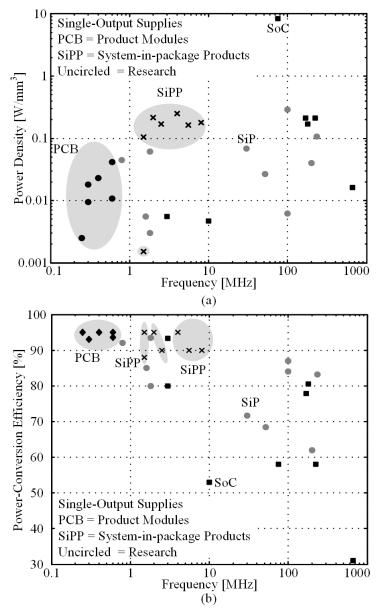

On the passive integration, the inductor is the most challenging element to integrate [47–49]. Figure 1.8 shows a summary of state-of-the-art inductors, compiled from data surveyed at [43], which shows quality, or inductance per resistance, versus energy density

for a given volume and saturation current. Inductors with no magnetic materials, such as air-core [44] or spiral-shaped inductors, tend to have low energy density and quality due to the low permeability of air. Inductor with magnetic materials, on the other hand, can store more energy per length, hence better quality due to lower series parasitic resistance. The magnetic material increases the magnetic flux the inductance can store for a given current flowing through because of a higher permeability [50]. However, this magnetics materials are not readily available in all processes and can increase manufacturing fabrication steps and challenges [51]. Because external inductors have better quality and large energy density by more than an order of magnitude compared to the state of the art, this research will concentrate on solving the generation of multiple supplies in a lower cost and size without adding the challenges of an integrated inductor. However, inductor integration should ultimately be part of the solution in the future.

Figure 1.8. Quality vs energy density for integrated and external inductor [43].

# 1.4.2 Multiple Outputs

A simple alternative to efficiently generate various regulated supplies from a battery or unregulated supply is to dedicate a whole switched-inductor converter for each. In despite of being an efficient option, using multiple inductors increase the size of the solution as well as the cost. Therefore, generating multiple supplies using a single inductor balances efficiency and size (and cost) [52].

A single-inductor multiple-output converter (SIMO) will present its own set of technical and design challenges. Most of them stem from the fact that the inductor is shared among the outputs in alternating cycles and the increased complexity of the design. The principal challenges are:

- 1. Insightful stability analysis

- 2. Accuracy of individual outputs

- 3. Output cross-regulation

- 4. Efficient buck-boost supplies

## 1.4.2.1 <u>Insightful Stability Analysis</u>

The switching nature of SIMOs makes them a non-linear system which complicates the analysis and design to ensure a fast and stable converter. Despite work to simplify design and analysis for the single-output switching converters, analysis for the SIMO is seldom. The multiple regulating loops in SIMOs complicates the analysis as they can interact and affect others. This adds complexity in the design because heavy simulations or mathintensive approaches are needed to ensure stability.

# 1.4.2.2 Accuracy

While in a single output switched-inductor buck converter the output will continuously receive energy, it will be duty-cycle irrespective if it is a buck or boosted output in a SIMO. In other words, a SIMO replenishes each output for less time and less often and it has an inherent increased delay when responding to load transients/dumps. This increases output voltage deviations from the target because the output capacitor must provide all the energy for a fraction of the switching period. Therefore, accuracy will degrade as compared to the single-output counterpart by increasing voltage ripple and voltage deviations from load dumps.

## 1.4.2.3 <u>Cross Regulation</u>

Another challenge with SIMOs is that a change in one output's energy needs will affect the energy remaining for distribution among the rest of the outputs. This is known as cross-regulation because the outputs are coupled through the energy stored in the inductor. There are two main types of cross-regulation: transient and load disparity. Transient-induced cross-regulation is when a load step or dump on an output suddenly disturb the energy in the inductor to cause an undershoot or overshoot on the other outputs due to excessive or lack of energy received.

Load-disparity cross-regulation occurs when the load between the outputs is considerable large. During steady-state, the inductor must carry enough energy to satisfy all outputs, and since one output is heavily loaded the inductor must carry at least this current. When a lightly-loaded output connects to the inductor and quickly receives a lot of energy, control must react almost immediately to prevent an overshoot. However,

limitations on minimum on-time in the light-loaded output's switch, its driver, and control would make the output receive more energy than consumed every cycle. This can create a run-away condition with the lightly-loaded voltage as it keeps increasing that must be prevented.

# 1.4.2.4 Efficient Buck-Boost Supplies

Single-output switched-inductor converters can only generate a buck or boost supply unless a four-switch buck-boost topology is used. A single-inductor multiple-output inherently has a higher number of switches to connect the output supplies. Fortunately, this also provides flexibility in the control to adapt the switching sequences to generate a mix of buck and boost supplies. However, this must be done with the minimum number of switching transitions to reduce power losses and design complexity.

# 1.5 Summary

Portable electronics, such as wireless microsensors, incorporate many features and functions that improve our quality life, save energy and money, and can save lives. These microsystems, powered by a small battery, incorporate blocks that often include sensing and converting sensed signals to a digital domain, a digital signal processor and communications to a central location for reporting. Each of these functions have their own specific supply and power requirements to optimize energy usage and performance which includes step-down and step-up regulation. Also, at the system level, blocks are duty-cycled when not in use and their supplies adaptively adjusted depending on their workload to minimize power consumption. Regulators, besides supplying a mix of buck and boosted

supplies, must be efficient and quick responding to this energy optimizing techniques to leverage their impact.

Linear regulators are fast and compact, but can only buck and are energy inefficient. Meanwhile, switched-capacitor circuits can be integrated and are more efficient, however they can only transfer limited energy per cycle and therefore have limited accuracy and their efficiency is still dependent on voltage conversion. Luckily, switched-inductor converters are the most efficient, but inductor are difficult to integrate. Even though research is being conducted to reduce the size of the passive to allow integration, tradeoffs with efficiency and manufacturing cost prohibits such implementation for wireless microsystems. Fortunately, using a single-inductor to regulate and supply several outputs balances efficiency and size, and hence costs.

Single-inductor multiple-output (SIMO) converters present their own challenges: analysis, accuracy, and cross-regulation. SIMO is multi-loop and non-linear system that increases complexity in the analysis and design. Accuracy degrades in a SIMO because each output is duty cycled and forces the output capacitor to solely provide the output's energy for a longer period compared to the single-output counterpart. Also, during transient events such as load dumps, outputs must wait for their turn to receive the energy necessary to replenish the output capacitor and adjustment of energy delivered. Because the inductor is shared, a sudden energy change in an output affects what other receives, therefore causing transient cross-regulation. During steady-state, load disparity between outputs also causes cross-regulation when an output receives much more energy than it needs. If left uncontrolled, this can continuously charge lightly loaded outputs and loose regulation.

Also, a SIMO will inherently have a higher number of switches and switches events. Regulating a mix of buck and boost outputs can make them advantageous given their flexibility on switching sequences; however, it must be done efficiently. In conclusion, SIMO converters can greatly improve the form factor for microsystems, or more generally portable electronics, with high efficiency to prevent excessive battery drain. Research groups has been focusing on understanding and solving the challenges with SIMO during operation and control. Bridging the performance gap between single-output and multiple-output switched-inductor converters will propel a cost reduction and miniaturization that will help to deploy more microsystems to leverage their benefits.

# **CHAPTER 2**

# SINGLE-INDUCTOR MULTIPLE-OUTPUT CONVERTERS

# 2.1 SIMO Operation

The control scheme in a single-inductor multiple-output (SIMO) allocates time to each output to receive energy from the inductor and adjust their on-time to achieve regulation against variations. There are two basic approaches for time allocation: dedicated energy packets or shared energy packets [52–53]. This section discusses the advantages and shortcomings for both operations used in the state of the art.

# 2.1.1 Dedicated Energy Packets

A dedicated energy transfer allocates a full inductor energizing and de-energizing sequence to each output [54–58]. This means that the SIMO behaves like independent single-output switching converters that shares the inductor after each switching period. Figure 2.1 (a) shows a buck power stage with the output shared by two outputs while Figure 2.1 (b) shows its operation with dedicated energy packets. From the beginning of a cycle, output  $v_{01}$  receives energy until the inductor current  $i_L$  completely de-energizes and stays deenergized until the end of the next period. Similarly, output  $v_{02}$  will receive energy on the following cycle. Equivalently, each output operates at a higher switching period, which for the example in Figure 2.3 will be at twice the switching period for two outputs.

Figure 2.1. A sample two-output SIMO (a) and dedicated energizing operation (b).

Since there is no sharing of the energy packet that inductor transfers, its main advantage is no output interferences in the regulation of other outputs, or in other words, minimum cross-regulation. However, for minimum cross-regulation, the converter requires that inductor completely de-energizes before the end of the period otherwise known as discontinuous conduction mode (DCM) operation. This way, the current will always start from a known value independent of load conditions among the outputs. However, this imposes a maximum deliverable output power with a given time allocation [58]. For instance, in the SIMO from Figure 2.1, the maximum power  $P_{O1(MAX)}$  for output  $v_{O1}$  is when the energy packet occupies the entire allocation period  $T_{SW}$ . By calculating the maximum charge  $Q_{O1}$  that can be delivered,  $P_{O1(MAX)}$  can be expressed as:

$$P_{O1(MAX)} = \frac{Q_{O1(MAX)}V_{O1}}{T_{SW}} = \frac{(V_{IN} - V_{O1})V_{O1}^2T_{SW}}{4L_OV_{IN}}.$$

(2.1)

To increase the maximum output power, the inductance should be low at the expense of higher conduction losses due to the current ripple increase. Alternatively, switching period can be high to increase output power but regulation suffers because each output receives energy less frequently compromising dynamic and voltage ripple performance [52].

To circumvent the power limitation, the inductor current  $i_L$  can stop de-energizing before it reaches zero and operate in a pseudo continuous-conduction mode (PCCM) [56]. As Figure 2.2 shows, instead of the inductor current  $i_L$  starting from zero, it starts from a fixed value  $I_{PCCM}$ , which allows the outputs to receive more energy from the beginning of the cycle. Unfortunately, an additional switch is necessary to circulate the  $I_{PCCM}$  current around the inductor when no output receives energy. This extra switch introduces more power losses that are more noticeable at higher load currents that can limit the full-load efficiency  $\eta_{C(FL)}$ . The dedicated energy packet scheme, irrespective of DCM or PCCM operation, has either higher current ripples or more switching losses that limits the power conversion efficiency at full load  $\eta_{C(FL)}$  to below 80% [55–56], [58].

Figure 2.2. Pseudo CCM operating mode to increase power delivery.

# 2.1.2 Shared Energy Packet

The other energy transferring scheme is to share the energy packet in the inductor among outputs in a single switching cycle [59–78], as Figure 2.3 shows the corresponding inductor current i<sub>L</sub> waveform under this scheme. The main advantage is that there is no output power limitation since it can operate in continuous conduction mode (CCM) unlike the dedicated energy packets scheme. Another benefit is that every output receives energy every switching cycle, or in other words, every output refresh rate is the switching frequency. This keeps accuracy high compared to the dedicated energy packet scheme [52].

Figure 2.3. Inductor current waveform during shared energy packet operation.

However, the fact that the outputs share the same energy packet results in cross-regulation. If a single output requires more energy, it can deprive subsequent outputs of energy and thus affecting their regulation. For instance, in a two-output buck power stage, when inductor ripple is very small, the duty cycle, or fraction of the period that connects to the inductor, of an output voltage  $v_{O1}$  is a function of the ratio between its load  $i_{O1}$  to the total load:

$$d_{Ol} = \frac{i_{Ol}}{i_{Ol} + i_{O2}}.$$

(2.2)

This means that duty cycle of one output has a load dependence on the other making them susceptible to interaction, and therefore cross-regulation.

#### 2.1.2.1 Cross Regulation

There are two ways to mitigate the cross-regulation with a shared energy packet scheme: matching output and inductor current [69], and having a freewheeling period or auxiliary output as an energy buffer [63], [72], [78]. Matching output current io to the closest level of inductor current i<sub>L</sub> reduces cross regulation when there is a load disparity among outputs. It achieves so by connecting the output with the lightest load at the beginning and near the end of the switching period when inductor current is low. The disadvantage of this technique is the control complexity for comparing and sorting output loads for more than

two outputs. Also, the benefit reduces as inductor current ripple is very small compared to the DC value because the current discrepancy between  $i_L$  and  $i_O$  is reduced only slightly after sorting.

Figure 2.4. Matching load to inductor current level reduces load-disparity cross regulation [69].

A limitation to matching current levels of the load to inductor is that it still does not address transient cross regulation as when one output's energy demand suddenly change. An alternative to mitigate this cross regulation is to add an energy buffer through a freewheeling period [78] or an auxiliary output [63], [73]. Since cross regulation propagates towards the last output in the sequence, an energy buffer at the end of the period provides or absorbs energy require to recover from a sudden load change. Figure 2.5 shows the power stage and operation with an extra switch that circulates a regulated fixed current across the inductor toward the end of the switching period [78]. This forces the inductor to store more and prevent energy starvation if any or multiple outputs suddenly need more energy. Likewise, if outputs need less energy, it prevents the last output in the sequence, e.g. von in Figure 2.5, to receive excess energy and allow the excess to flow in the freewheeling period t<sub>FW</sub>. The control eventually readjusts energy in the inductor to compensate for the excess. Since the regulation target of the current during the freewheeling period can be relatively high during heavy loads, it represents an additional power loss when flowing through the additional free-wheeling switch S<sub>FW</sub>.

Figure 2.5. Freewheeling period as an energy buffer based on [78].

Alternatively, an auxiliary output can act as the energy buffer. It can either be stored in another temporary output and then transferred back to the supply with an auxiliary switched-inductor converter [63], or connect the input supply as the auxiliary output to reduce component count [73]. Figure 2.6 shows the respective power stage (a) and operating waveforms (b) to use the input supply  $v_{IN}$  as an auxiliary output. This is slightly more efficient than recirculating the extra energy through the inductor because the energy is recovered and store back at the input capacitor or battery. Nevertheless, the extra switch and switching events can limit the peak efficiency  $\eta_{C(PK)}$  to below 85% [63], [73].

Figure 2.6. Auxiliary output to reduce cross-regulation [73].

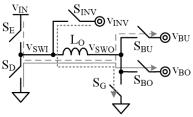

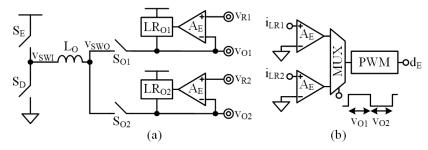

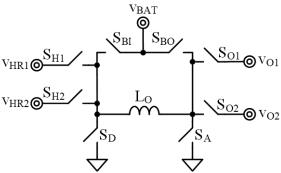

# 2.1.2.2 Mixed Output

Fortunately, a major benefit of the shared energy packet operation is the opportunity to create a mix of buck, boost and inverting supplies. Figure 2.7 shows a generic power stage with possible power flows to generate buck, boost and inverting supplies. Initial inductor energizing can occur from supply to ground (S<sub>E</sub> & S<sub>G</sub> engages) or from supply to a buck

output  $v_{BU}$  ( $S_E$  &  $S_{BU}$  engages). Afterwards, because the inductor still carries current, a boost output can de-energize the inductor by engaging  $S_{BO}$  and the supply  $S_E$  or input-side ground  $S_D$  switch. Moreover, if inductor still carries current, an inverting output  $v_{IN}$  can connect on the input switching node  $v_{SWI}$  by closing  $S_{INV}$  to generate a negative voltage. Fundamentally, the inductor can only energize through buck outputs or a ground path but can be de-energize with either buck or boost outputs if the input switching node  $v_{SWI}$  is connected to ground; otherwise, if the input side is connected to the supply, it can only deenergize through a boosted output.

Figure 2.7. Power paths for mixed output generation on a SIMO.

Literature shows various configurations to generate a mix of output voltages including buck & boost outputs [57], [64], [67], [68], [70], [75], and [78]. For the portable microsystem applications, the majority of outputs are buck and few or one needs to be a boosted voltage. When using a boost-derived topology such as in [64] or [67], boost power must dominate the total buck power to prevent overcharging boost outputs. Otherwise, control bypasses inductor and transfer energy directly to the outputs to prevent the runaway condtion, and doing so reduces power conversion efficiency between 5-10%. Therefore, a buck-derived boost is more compatible with the targeted application to avoid unnecesary switching events and minimize losses.

Other work uses single energy packet scheme which as previously discussed limit efficiency [78]. Work at [70] avoids such extra losses with adaptively adjusting the switch sequence to generate buck and boost outputs; however, its extended-PWM, which compares the ramps for each output, to generate such control adds higher complexity for more than two outputs. Therefore, a scalable, simple implementation and efficient mixed output converter able to generate buck and boost supplies is neccesary for microsystems applications.

#### 2.2 SIMO Control

The shared energy packet scheme increases control complexity because it needs to regulate both the stored energy in the inductor as well as the distribution among the outputs. Although voltage-mode control is possible [59], [61]; it often limits the control bandwidth due to the complex conjugate pole of the power stage that must be compensated for. A current loop that regulates inductor current effectively transforms the inductor in a current source up to the loop's bandwidth. This eliminates the pole that the inductor contributes in the system or main loop leading to a simpler compensation, design and higher bandwidth [79]. Most of the state of the art uses a pulse width modulation (PWM) approach with few variations on the control that distributes the energy among outputs.

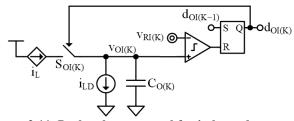

#### 2.2.1 Current-Mode PWM Variations

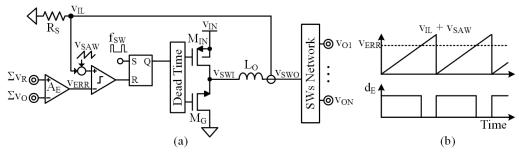

When implementing the current loop, state-of-the-art SIMOs commonly uses peak current control [60], [63], [64], [67], [69], [72], [73], [76], and [77]. Figure 2.8 (a) shows the control structure that includes a sampling point for the inductor current i<sub>L</sub>, a conversion to

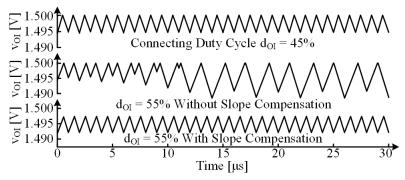

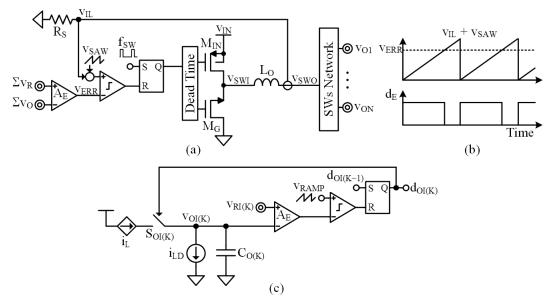

voltage  $v_{IL}$  through equivalent resistor  $R_S$  and a comparator. When a cycle begins, a clock engages the inductor  $L_O$  into energizing until its peak equates a reference point  $v_{ERR}$ . The reference  $v_{ERR}$  set by an amplified total error among outputs, or alternatively only the last output in the sequence, dictates how long energizing time  $t_E$ , or duty cycle  $d_E$ , lasts as Figure 2.8 (b) shows. This control provides a simple and robust control; however, it needs a saw tooth voltage  $v_{SAW}$  added to the sensed current to compensate for sub-harmonics oscillations when energizing duty cycle  $d_E$  is higher than 50% as the single-output counterpart requires [80].

Figure 2.8. Peak current control for SIMO converters (a) and operating waveforms (b).

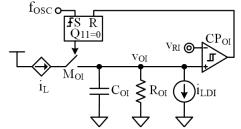

The current loop will store enough energy in the inductor to satisfy all outputs; but additional loops are required to distribute this energy. Because one output can be connected for the reminder of the switching period until a new cycle begins, an additional N-1 loops are required for an N-output SIMO converter. These loops are local to each output, which makes them independent of the of the current loop, or in other words independent voltage loops. There are two main approaches for the independent voltage loops in literature: PWM and peak-voltage control.

#### 2.2.1.1 Fully PWM

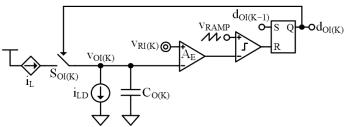

The independent voltage  $v_{OI(K)}$  loops, i.e. all outputs except the last in the sequence, can be controlled using a simple PWM loop [69], [77]. Under this scheme, an output starts to receive energy, and when ramp voltage  $v_{RAMP}$  reaches the amplified error of the controlled output, it disconnects from the inductor like implementation in Figure 2.9. This control provides good accuracy for a simple implementation.

Figure 2.9. PWM control for the independent voltage loops.

The incorporation of the inductor current in the modulation while the output receives energy improves accuracy and cross-regulation specially when there is load disparity among outputs [64], [67], [73]. Figure 2.10 shows such implementation by replacing the modulation from a constant-slope ramp to a ramp with slope proportional to the sensed current through the switch. As an example, if an output receives a large current through its switch, the modulation ramp increases faster. This effectively increases the loop gain and the comparator can resolve finer duty cycles that helps reduce load-disparity cross regulation.

Figure 2.10. PWM control with current feed forward on independent loops.

Although any of the discussed PWM methods can regulate independent outputs accurately, they are slow responding to load dumps. They require multiple cycles to recover from a load dump because they control an average quantity of the output voltage [81]. Because portable microsystems must react and regulate supplies to a moving target or after a waking up a block, bandwidth is an important requirement for the control.

# 2.2.1.2 Peak Voltage

Direct regulation of an instantaneous signal is faster because it bypasses any filtering or intermediate block. A simple implementation, as shown in Figure 2.11, is to regulate the voltage of the independent outputs to a reference directly with a comparator to determine the on-time. This control effectively regulates the output's peak voltage [60], [63], [66], [72], [76]. The direct regulation of the outputs creates a challenging aspect of this simple control since it is noise sensitive due to the lack of filtering. Also, because this control is often combined with a current-mode PWM approach, the total response of the converter is limited by the PWM bandwidth of the current regulation.

Figure 2.11. Peak voltage control for independent outputs.

# 2.2.2 Linear Regulator Hybrids

An alternative power stage topology and control combines the high efficiency of a switched-inductor converter with the high bandwidth of a linear regulator. Figure 2.12 (a) shows a power stage that adds a linear regulator to each output while Figure 2.12 (b) shows

the switched-inductor control's block diagram [55]. Each linear regulator directly corrects any error in the output while the SIMO drives the current in each linear regulator to zero. This allows the converter to react to a rising load dump in less than 50 ns, while achieving a peak efficiency of 83% at steady-state. However, since the linear regulators can only supply currents, the benefits are less for a falling load step, increasing to a 2 µs response time. Also, since the linear regulator has high bandwidth, it will try to regulate against the output voltage ripple at steady-state. This means that its current will be non-zero and will reduce efficiency specially at high current levels as noted by the 72% reported in [55].

Figure 2.12. (a) Switching-linear hybrid converter with dedicated linear regulator on each output (a) and (b) PWM control scheme that multiplex between outputs [55].

Despite the integrability of a linear regulator, dedicating one per out increases silicon real estate and hence cost. An alternative is to allocate one linear regulator available for all outputs from the switching node [54]. Figure 2.13 shows the concept where the linear regulator sources or sink current from the output switching node  $v_{SWO}$  according to the total error among outputs. This implementation results in a higher power conversion efficiency because the steady-state current the linear regulator provides is closer to zero due to ripple cancelation because of the error summation. In addition, because it is a shared linear regulator, its quiscent power is less. This results in a peak efficiency  $\eta_{C(PK)}$  of 88.7% but can drop to 82% at full load conditions [82]. Leveraging a single linear regulator for

many outputs can be very challenging because no independent loop regulate the output voltages directly. Using an error-based approach, in which only the output with the largest error receives energy in a given cycle, is possible but it can result in cross-regulation and unregular switching at steady-state [82].

Figure 2.13. Switching-linear hybrid converter with single linear shunt regulator for all outputs [82].

# 2.3 Context and Comparison

A quantitative comparison among proposed supplies is necessary to evaluate the merits of control and operation techniques given a certain context and application. For a fairer comparison, the approach would be divided between control approaches and mixed-output (buck and boost) operation to account for the inherent design tradeoffs of the later. Nevertheless, the same figure of merit (FoM) will compare both as it is focused on the SIMO performance for wireless microsystem applications.

# 2.3.1 Figure of Merit

Comparing the state of the art (SoA) is difficult because too many metrics describe the performance of a switched-inductor power supply. Plus, the significance and relative weight of each parameter can vary widely from one application to the next. Still, comparing

under equivalent conditions and uniform weights can be useful. So, for the purposes of the following discussion, all independent parameters carry equal weight.

A multiple-output inductor is more appealing when it supplies higher total current  $i_{O(MAX)}$  and more outputs  $N_O$  with higher power-conversion efficiency  $\eta_C$ . Although  $\eta_C$  can be more important at one level, peak and full-load efficiencies  $\eta_{C(PK)}$  and  $\eta_{C(FL)}$  reflect what is possible when optimized and stretched to output as much power as possible. And although maximum output-voltage variation  $\Delta v_{O(MAX)}$  is important,  $\Delta v_{O(MAX)}$  ultimately depends on output capacitance  $C_O$ , maximum load dump  $\Delta i_{O(MAX)}$ , and response time  $t_R$ .  $t_R$ , however, is largely independent of the others. Plus, given  $t_R$  and any of the other two, the third is simply their consequence. Hence,  $t_R$  is arguably the one that represents the rest.

A power supply is also more attractive when it costs less and occupies less space. In this respect, fewer off-chip components  $N_{OC}$  and smaller silicon die size  $A_{SI}$  cost and occupy less, and longer channel-length technologies  $L_{MIN}$  cost less. Plus, longer  $L_{MIN}$  technologies can sustain higher voltages. Assuming all these parameters are equally significant, an all-encompassing figure of merit (FoM) should rise with higher  $i_{O(MAX)}$ ,  $N_{O}$ ,  $\eta_{C(PK)}$ ,  $\eta_{C(FL)}$ , and  $L_{MIN}$  and lower  $t_R$ ,  $N_{OC}$ , and  $A_{SI}$ . Normalizing the FoM to one point of reference PoR reveals a relative FoM or RFoM that is useful when comparing devices:

$$RFoM = \frac{FoM}{PoR} = \frac{i_{O(MAX)}N_{O}\eta_{C(PK)}\eta_{C(FL)}L_{MIN}}{t_{R}N_{OC}A_{SI}PoR},$$

(2.3)

where PoR is the FoM of the best SoA in each comparison.

# 2.3.2 Mixed-Output SIMO Comparison

The mixed-output SoA, summarized in Table 2.1, commonly uses a PWM control approach. This control consistently has a peak efficiency  $\eta_{C(PK)}$  close or higher than 90%. However, [63] and [78] uses an energy buffer as an auxiliary output that increases losses as [78]'s full-load efficiency  $\eta_{C(FL)}$  of 74% shows. Also, Table 2.1 shows that the design has been focused on operation and steady-state performance given the lack of report for response time  $t_R$ .

Table 2.1. SoA Comparison of Mixed-Output (Buck & Boost) SIMO Converters.

|                  | Units           | [63]                         | [78]                    | [67]      | [64]      |  |

|------------------|-----------------|------------------------------|-------------------------|-----------|-----------|--|

| Notes            | _               | I-PWM, V-PK<br>Energy Buffer | Fully PWM Energy Buffer | Fully PWM | Fully PWM |  |

| L <sub>MIN</sub> | μs              | 0.5                          | 0.25                    | 0.25      | 0.25      |  |

| Ası              | mm <sup>2</sup> | 3.6                          | 10                      | 2.1       | 3.8       |  |

| VIN              | V               | 2.5–4.5                      | 2.7                     | 0.9–1.6   | 1.8–2.2   |  |

| Vo               | V               | 2–12                         | 1.8–3.3                 | 0.6, 1.8  | 1.25–2.25 |  |

| io(MAX)          | mA              | 145                          | 650                     | 240       | 400       |  |

| No               | #               | 5                            | 4                       | 2         | 4         |  |

| Noc              | #               | 10                           | 5                       | 3         | 5         |  |

| ПС(РК)           | %               | 83                           | 91                      | 92        | 93        |  |

| ηC(FL)           | %               | _1                           | 74                      | 92        | 92        |  |

| tr               | μs              | _1                           | $10^{2}$                | _1        | _1        |  |

| RFoM             | %               | 39 <sup>3</sup>              | 49                      | $90^{3}$  | $100^{3}$ |  |

<sup>&</sup>lt;sup>1</sup>Not reported. <sup>2</sup>Estimate. <sup>3</sup>assumes  $t_R = 10 \mu s$  for comparison.

# 2.3.3 Control Comparison

Table 2.2 compiles the state of the art (SoA) which reported almost all considered parameters and with the best control performance for wireless microsystem applications. The best performing technique using the discussed FoM in equation (2.3) is the hybrid with

dedicated linear regulators [55], thanks from its 2  $\mu$ s response time in despite its low 72% full-load efficiency  $\eta_{C(FL)}$ . Using a dedicated energy transfer scheme resulted in a low 72% full-load efficiency  $\eta_{C(FL)}$  and slow response time of 20  $\mu$ s [58]. A full PWM approach helps balance the response time to around 5 to 40  $\mu$ s while maintaining a full-load efficiency  $\eta_{C(FL)}$  above 80%. Using a peak voltage control can provide bandwidth benefits but the complexity of the particular implementation of [76] of a shared comparator and a time limit for any outputs increases response time to 200  $\mu$ s.

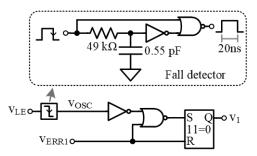

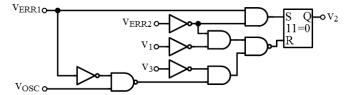

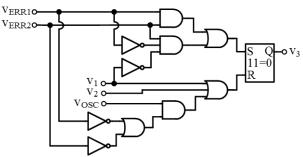

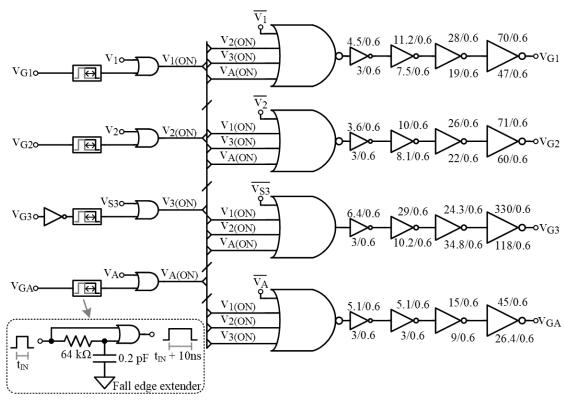

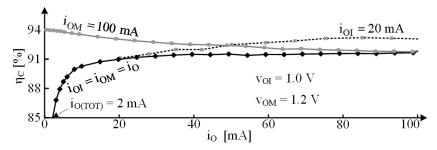

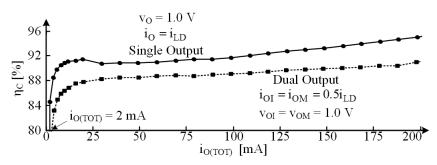

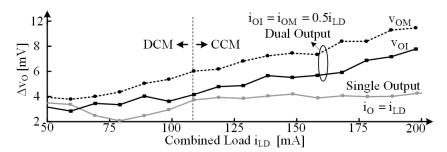

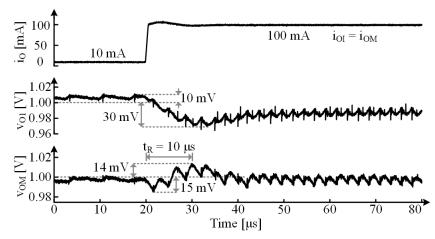

Table 2.2. SoA Comparison of Control schemes for SIMO Converters.