# Air-gap gating of MgZnO/ZnO heterostructures

Cite as: J. Appl. Phys. **116**, 084310 (2014); https://doi.org/10.1063/1.4894155 Submitted: 23 June 2014 . Accepted: 18 August 2014 . Published Online: 28 August 2014

T. Tambo, J. Falson, D. Maryenko, Y. Kozuka, A. Tsukazaki, and M. Kawasaki

#### ARTICLES YOU MAY BE INTERESTED IN

Electron scattering times in ZnO based polar heterostructures

Applied Physics Letters 107, 082102 (2015); https://doi.org/10.1063/1.4929381

Optical probing of MgZnO/ZnO heterointerface confinement potential energy levels Applied Physics Letters 106, 082102 (2015); https://doi.org/10.1063/1.4913313

Spontaneous polarization driven Mg concentration profile reconstruction in MgZnO/ZnO heterostructures

Applied Physics Letters 104, 242112 (2014); https://doi.org/10.1063/1.4884383

## Air-gap gating of MgZnO/ZnO heterostructures

T. Tambo, <sup>1</sup> J. Falson, <sup>1,a)</sup> D. Maryenko, <sup>2</sup> Y. Kozuka, <sup>1</sup> A. Tsukazaki, <sup>3,4</sup> and M. Kawasaki <sup>1,2</sup> <sup>1</sup>Department of Applied Physics and Quantum-Phase Electronics Center (QPEC), University of Tokyo, Tokyo 113-8656, Japan

<sup>2</sup>RIKEN Center for Emergent Matter Science (CEMS), Wako 351-0198, Japan

(Received 23 June 2014; accepted 18 August 2014; published online 28 August 2014)

The adaptation of "air-gap" dielectric based field-effect transistor technology to controlling the MgZnO/ZnO heterointerface confined two-dimensional electron system (2DES) is reported. We find it possible to tune the charge density of the 2DES via a gate electrode spatially separated from the heterostructure surface by a distance of  $5 \mu m$ . Under static gating, the observation of the quantum Hall effect suggests that the charge carrier density remains homogeneous, with the 2DES in the 3 mm square sample the sole conductor. The availability of this technology enables the exploration of the charge carrier density degree of freedom in the pristine sample limit. © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4894155]

#### I. INTRODUCTION

The development of a new material platform requires advances in both sample fabrication and means of experimentally controlling the systems parameters. In the case of two-dimensional electron systems (2DES) confined at heterointerfaces, molecular-beam epitaxy (MBE) has made tremendous contributions by suppressing scattering origins and hence improving the quality of the 2DES<sup>1-3</sup> while access to electrostatic gating then unlocks the carrier density (n)degree of freedom to be explored experimentally. For this, the prevailing technique ubiquitous in the semiconductor industry and fundamental research realms alike is the formation of metal-oxide-semiconductor field-effect transistors (MOSFET) and Schottky metal semiconductor FET, where by a thin dielectric or depletion layer between the conducting channel and gate electrode facilitates tuning of the system's Fermi energy. 4,5 Owing to such prevalence, many gate dielectric materials have now been studied to extract optimal transport properties. 6-8 However, the employment of such solid-state dielectrics inevitably has drawbacks including inducing disorder at the interface with the device under investigation as well the presence of trapped/mobile charges resulting in hysteretic electrostatic response. To circumvent such problems, a technique involving the use of an "air-gap" dielectric has recently emerged in fundamental research studies. First explored in the field of organic semiconductors, 9-12 the fruits of adapting such techniques to two-dimensional (2D) materials are now seen notably in state-of-the-art graphene devices. In separating the graphene flake from the solid-state dielectric of SiO<sub>2</sub> and mitigating the surface roughness and/or impurity potential disorder it imposes, so-called "suspended graphene" devices are now clean enough to reveal the previously masked fragile physical details. 13-15 The application of the "air-gap" structure hence possesses great potential for preserving pristine quality of a wide range of 2D materials and heterostructure confined 2DES.

In this letter, we report the adaptation of air-gap fieldeffect transistor (AFET) technology to controlling the electrical characteristics of a MBE grown solid-state 2DES. The prototype system we explore is the MgZnO/ZnO heterointerface which has emerged in recent years as the host of a high mobility 2DES. 16,17 Since this 2DES is on the order of 200 nm below the sample surface, this study may seem rather removed from the AFET reports on 2D materials which are inherently exposed, and hence susceptible to the surrounding environment. However, it is acutely obvious that even in buried 2DES, long-range Coulombic disorder can severely affect fragile electronic ground states observed at low temperatures. 18,19 Hence, this technology is aimed at superseding the standard MOSFET devices which have been previously reported, <sup>20,21</sup> enabling access to the charge carrier density degree of freedom in the pristine sample limit by eliminating unnecessary sample processing steps and surface disorder. The device we present is measured in van der Pauw geometry which enhances the simplicity of design, while simultaneously acting as a particularly useful tool in evaluating the uniformity of transport. Using the AFET technology, we find it experimentally possible at low temperature to tune the 2DES across the wide range of  $\Delta n = 3 \times 10^{11} \, \mathrm{cm}^{-2}$ within  $\pm 200 \,\mathrm{V}$  gate voltages  $(V_{\mathrm{G}})$  while retaining electron mobility values close to that of a raw piece of the same wafer. Simultaneously, the electric-field controlled *n* remains homogeneous as illustrated through the observation of the integer and fractional quantum Hall effects.

## **II. AIR-GAP FET**

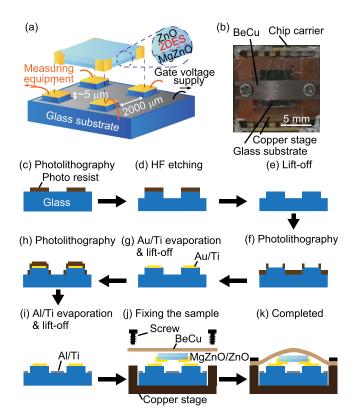

Figure 1(a) shows a schematic representation of the AFET device, which consists of two components. One is the MBE-grown sample to be measured and the other is the stage on which the sample is placed, resulting in the gate electrode being spatially separated from the sample surface. Based on

<sup>&</sup>lt;sup>3</sup>Institute for Materials Research (IMR), Tohoku University, Sendai 980-8577, Japan

<sup>&</sup>lt;sup>4</sup>PRESTO, Japan Science and Technology Agency (JST), Tokyo 102-0075, Japan

a)Electronic mail: falson@kwsk.t.u-tokyo.ac.jp

FIG. 1. (a) A bird's-eye view of the MgZnO/ZnO heterostructure placed upside down on a stage with four Au/Ti capped pillars, contacting the ohmic contacts on the sample, and hence the 2DES. The gate electrode is isolated by an air-gap dielectric. Both the pillars and the gate are then wire bonded individually. The distance between pillars is 2 mm and their height  $\approx 5 \,\mu\text{m}$ . (b) A microscope image of the air-gap device from the top after fixing the MgZnO/ZnO sample to the glass stage with the BeCu spring, which is placed on a copper stage. (c)-(k) Flow of the air-gap device fabrication. The dimensions are not accurately drawn in (c)-(k).

this design, the sample itself requires few processing steps and the gating structure is an independent, reusable unit, thus allowing efficient characterization by exchanging only the sample. These units are fabricated independently as detailed below and combined just before measurements are performed. In order to keep the distance between the ohmic electrodes and gate electrode constant from room to low temperatures, a BeCu flat spring is used to fix the sample. As shown in Fig. 1(b), the 0.3 mm thick BeCu is cut to roughly the same size as the sample, and then screwed to the copper stage, which is fixed to the chip carrier by varnish. In this geometry, the difference of thermal expansions between the glass substrate and other parts (ZnO, BeCu, screws, etc.) is buffered by the BeCu spring, which keeps pressing the MgZnO/ZnO sample to the glass substrate with an appropriate pressure. As introduced above, the conducting channel in this structure is found at the MgZnO/ZnO heterointerface, some 200 nm below the sample surface. This necessitates the 2DES being contacted at the sample edges and results a macroscopic size device at the current technological level. This potentially has the following negative drawbacks: increased leakage currents and non-uniformity in the gate-induced electric field. To mitigate such risks, we have designed the air-gap thickness to be 5  $\mu$ m, much thicker than other reports which typically utilize  $\approx 100 \, \text{nm.}^{10,12}$

To begin with, the gate unit is made of a glass substrate with four pillars defined by optical lithography (Fig. 1(c)) and then etched by hydrofluoric acid (Fig. 1(d)). This etching is performed at room temperature by immersing the glass substrate in 47% concentration hydrofluoric acid for 70 s, resulting in 5  $\mu$ m high pillars. A short etching time is desirable as the sticking of the photoresist to the glass substrate deteriorates with time, leading to poorly defined pillars. After etching, the stage is then washed in acetone to remove the photoresist (Fig. 1(e)). Without this step, acid which penetrates beneath the photoresist remains resilient to rinsing, resulting in non-uniformity in the etched depth. After the pillars are defined, 100 nm Au/10 nm Ti is evaporated on the top of these pillars to form the bonding pads and to make contacts to the electrodes on the sample (Figs. 1(f) and 1(g)), while 20 nm Al/10 nm Ti is evaporated on the remaining surface area, to form the gate electrode (Figs. 1(h) and 1(j)). Finally, the ohmic electrodes of the MgZnO/ZnO 2DES sample are contacted to the Au/Ti electrodes of the glass stage by fixing the sample down with the BeCu spring and two screws.

The sample, a 3 mm square chip, is cut from a wafer of MgZnO/ZnO grown on a single crystal ZnO substrate. Four ohmic contacts consisting of 100 nm Au/10 nm Ti and roughly 0.5 mm square in size are evaporated at the edge of the sample on its surface using a metal mask, contacting the 2DES and yielding a device measurable in van der Pauw geometry. Finally, the heterostructure is exposed to O<sub>2</sub> plasma for 30 s. This treatment has the effect of reducing the 2DES charge carrier density, which may be later compensated by gating, presumably through the formation of charged defects at the surface. This is a commonly used method to improve rectification behavior in ZnO Schottky junctions and empirically without such a treatment the gating efficiency was observed to be poor.

## **III. RESULTS AND DISCUSSIONS**

Electrical measurements are performed at  $T = 500 \,\mathrm{mK}$ in a 15 T superconducting magnet equipped <sup>3</sup>He cryostat. At such low temperatures, the ZnO bulk substrate is insulating leading to the 2DES being the sole conducting channel. Two measurement techniques are utilized. First, direct current measurements performed using a semiconductor parameter analyser (4156C and 41501B, Agilent Technologies) with 1 mV drain voltage establish the  $V_{\rm G}$  dependence of the device. To explore the effect of static gating on magnetotransport, alternating current lock-in measurements were performed with a current of  $100\,\mathrm{nA}$ ,  $(14\,\mathrm{Hz})$  after the  $V_\mathrm{G}$ dependence is characterized. During each magnetic field sweep, V<sub>G</sub> is fixed. Leakage current is negligibly small (<50 pA) for all measurements. In order to evaluate the carrier modulation efficiency, a LCR meter (4284 A, Agilent Technologies) is used to measure the capacitance between the gate and 2DES.

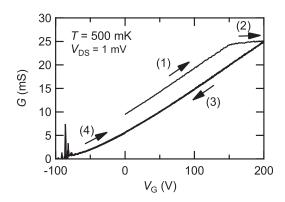

The conductance, G, of the 2DES as a function of gate voltage  $V_G$  is shown in Fig. 2. Note that the G in Fig. 2 is only for one pair of contacts in the van der Pauw geometry. With increasing  $V_G$ , G increases linearly along the line

FIG. 2. The transfer characteristics of conductance (G) between one set of contacts in the van der Pauw geometry as a function of gate voltage  $(V_{\rm G})$  for the MgZnO/ZnO AFET device. (1) At first, G linearly increases with positive  $V_{\rm G}$ . (2) Saturation occurs above  $V_{\rm G}=150$  V from which (3) G reduces linearly with decreasing  $V_{\rm G}$ , ultimately returning (4) to  $V_{\rm G}=0$  V from -100 V.

labelled (1). At a positive bias of 150 V, G is seen to saturate as shown in region (2). From here, when decreasing  $V_G$ , we observe a reduction in G, not along the original trace, but immediately, as shown in region (3). Finally, while going back to  $V_G = 0 \text{ V}$  (4), G increases along same trace on (3) with no hysteresis. Once this loop is established, it is reproducible over multiple sweeps along same trace on (3) and (4). In region (2) where saturation in G occurs, it is evident that the electric-field no longer acts to accumulate electrons into the 2DES. Rather, immobile charges are likely formed near the surface of MgZnO capping layer, which in turn screen the gate induced electric-field, effectively weakening its effect on the 2DES.<sup>26</sup> In fact, we observe a similar saturation of G also in the case of conventional MOSFETs using  $Al_2O_3$ gate dielectric.<sup>21</sup> While this concisely explains the shift in the required  $V_{\rm G}$  after saturation, entering such a regime should be avoided in final device operation. In any case, the sample may be "reset" by heating to room temperature, resulting in a return to the original conductivity behavior.

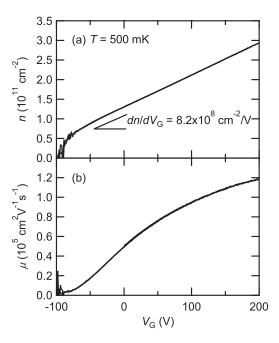

As G is a product of both the charge density n and mobility  $\mu$  of the 2DES, the respective contributions are quantified in Fig. 3 for the section corresponding to (3) of Fig. 2. Working under the assumption that at each  $V_G$  the Hall resistance  $R_{xy}(B)$  is linearly dependent at low magnetic field B as given below

$$n = \frac{1}{e(R_{xy}(+0.5T) - R_{xy}(-0.5T))},$$

(1)

where e is the elementary charge, n is deduced. This is then used to calculate  $\mu = G_{\rm sheet}/ne$ . From being completely depleted at around  $V_{\rm G} = -100\,{\rm V}$ , n increases linearly above  $-50\,{\rm V}$  to  $200\,{\rm V}$ , ultimately saturating at  $n = 2.9 \times 10^{11}\,{\rm cm}^{-2}$ . This is the maximum number of charge carriers which may be accommodated by the spontaneous polarization mismatch at the heterointerface. The carrier density modulation constant is  $8.2 \times 10^8\,{\rm cm}^{-2}/{\rm V}$ . This value is about one-third of the expected value of  $2.3 \times 10^9\,{\rm cm}^{-2}/{\rm V}$  calculated from the measured capacitance of the device  $C = 370\,{\rm pF/cm}^2$ . This reduced modulation ratio may be related with charged defects at the MgZnO surface screening the electric field. If fact, conductivity cannot be modulated at all without the O<sub>2</sub> plasma

FIG. 3. Gate voltage dependence of the device. (a) Carrier density n and (b) electron mobility  $\mu$  as a function of  $V_{\rm G}$ . (a) n is seen to increase linearly as a function of  $V_{\rm G}$  above -50 V at a rate of  $8.2 \times 10^8 {\rm cm}^{-2}/{\rm V}$ . Carriers in the heterostructure are completely depleted around -100 V. (b) Mobility  $\mu$  as a function of  $V_{\rm G}$ . The maximum  $\mu$  of  $120\,000~{\rm cm}^2{\rm V}^{-1}{\rm s}^{-1}$  is achieved at maximum accumulation of n.

treatment as noted above, and the modulation ratio much depends on sample to sample. This observation indicates that, while an air-gap transistor is defect-free in the gate dielectric, the operation is still susceptible to the defects at the surface of the channel or capping layer. In the measurements, the largest mobility of  $120,000\,\mathrm{cm^2V^{-1}s^{-1}}$  is achieved at  $200\,\mathrm{V}$  with carrier density of  $2.9\times10^{11}\,\mathrm{cm^{-2}}$ . These values are limited by the saturation in G as discussed above and are close to the values observed in a separately measured raw chip of the same wafer without gate unit.

Finally, we explore the techniques compatibility with typical magnetotransport measurements performed on low dimensional systems. Figure 4 displays the magnetotransport data at T = 500 mK of the device under applied static gate voltages, corresponding to a range of  $n = 0.87 \times 10^{11} \, \text{cm}^{-2}$ to  $2.9 \times 10^{11} \, \text{cm}^{-2}$ . In these traces, we follow the filling factor  $(\nu)$ , given by  $\nu = nh/eB$ , where h is the Planck constant, indicating how many Landau levels are populated at a certain B. Prominent integer and fractional quantum Hall states are seen at  $\nu = 2$  (circle),  $\nu = 1$  (triangle), and  $\nu = 2/3$ (square) and are observed to shift systematically as described by the relationship above. The most robust state,  $\nu = 1$ , is noted to remain zero resistance throughout the voltages applied. This non-dissipative transport confirms the two dimensional nature of the conducting channel without any parasitic conduction, even when the sample surface is exposed to high voltages. In the dilute limit of the measurement ( $n = 0.87 \times 10^{11} \,\mathrm{cm}^{-2}$ ), we begin to encounter the limitations of the technique application to this sample. As seen in the red curve of Fig. 4(b), the  $R_{xy}$  displays non-monotonic behavior with increasing B. While mixing in this van der Pauw geometry likely plays a role as the  $R_{xx}$  and  $R_{xy}$  become

FIG. 4. Magnetotransport at T=500 mK of the 2DES under static gating. (a) The longitudinal resistance  $R_{\rm xx}$  curves correspond to carrier density of 0.87, 1.3, 1.6, 1.9, 2.3,  $2.9 \times 10^{11} \, {\rm cm}^{-2}$ , respectively, from top to bottom with offset of 0.5 k $\Omega$ . (b) The Hall resistance  $R_{\rm xy}$  curves for the same carrier densities. Notable quantum Hall states of  $\nu=2$ , 1, and 2/3 are identified by closed circles, triangles and squares in (a), respectively.

similar in magnitude, such dramatic behavior beyond  $\nu = 1$  suggests that depletion around the ohmic contacts affects the contact to 2DES edge channels. Further optimization of contacts is therefore likely to be a generic but crucial requirement for material systems adopting this design to enhance the versatility of the gate unit described.

Despite this limitation, the AFET has the advantage over conventional MOSFET devices in maintaining clear signals of the quantum Hall effect into the dilute regime. In Refs. 20 and 21, the quantum Hall effects were observed with varying the carrier density via gating across an  $Al_2O_3$  dielectric. However, under slight depletion fractional states rapidly were degraded already at carrier densities of  $3.7 \times 10^{11}$  cm<sup>-2</sup> in a sample of comparable quality to the one in the current study. Even with a higher quality sample in Ref. 21, the fractional states suffer significantly by  $n = 1.6 \times 10^{11}$  cm<sup>-2</sup>. As we describe here, the current AFET structure allows us to maintain clear fractional quantum Hall features to carrier densities as low as  $10^{11}$  cm<sup>-2</sup>.

### **IV. SUMMARY**

In conclusion, we have developed the technology which enables the use of an air-gap dielectric to electrostatically tune the electrical characteristics of a solid state 2DES

confined in MgZnO/ZnO heterostructures in van der Pauw geometry. The method has the advantage of using a reusable gating unit separate from the sample under investigation, providing relatively easy and fast turn-around between experiments. We find tunability of n over an order of magnitude while retaining  $\mu$  values close to that of a raw pristine sample from the same wafer. This technique is therefore complimentary to the ability to tune the charge density through controlled doping regimes, for example the Mg content in MgZnO. Under static gating, the electric field acting on the 2DES in MgZnO/ZnO remains homogenous enough to allow the observation of zero resistance quantum Hall states when applying a large perpendicular magnetic field and evidences that compared to previous studies which utilized solid-state gating, 20,21 disorder is suppressed in the magnetotransport data approaching  $n \approx 1.0 \times 10^{11} \, \mathrm{cm}^{-2}$ . Future efforts to realize more contacts while reducing the thickness of air-gap itself to increase the electrostatic tuning efficiency will yield a versatile technique for enabling the exploration of the carrier density degree of freedom in various heterostructures, surfaces and 2D materials.

#### **ACKNOWLEDGMENTS**

We wish to thank to Y. Nakamura, R. Yamazaki, and R. Goto for helpful advice. This work was partly supported by JSPS Grant-in-Aid for Scientific Research(S) No.24226002 and for Young Scientist (A) No. 23686008 and the Japan Society for the Promotion of Science through "Funding Program for World-Leading Innovative R&D on Science and Technology (FIRST Program)," initiated by the Council for Science and Technology Policy (CSTP).

<sup>1</sup>L. Pfeiffer and K. West, Physica E 20, 57 (2003).

<sup>2</sup>H. L. Stormer, Rev. Mod. Phys. **71**, 875 (1999).

<sup>3</sup>D. G. Schlom and L. N. Pfeiffer, Nature Mater. 9, 881 (2010).

<sup>4</sup>S. Sze, *Physics of Semiconductor Devices*, 2nd ed. (John Wiley and Sons, Inc., New York, 1981).

<sup>5</sup>P. Y. Yu and M. Cardona, *Fundamentals of Semiconductors*, 4th ed. (Springer, Berlin, 2010).

<sup>6</sup>G. D. Wilk, R. M. Wallace, and J. M. Anthony, J. Appl. Phys. **89**, 5243

<sup>7</sup>J. Robertson, Rep. Prog. Phys. **69**, 327 (2006).

<sup>8</sup>L. Niinistö, J. Nieminen, M. Päiväsaari, J. Niinistö, M. Putkonen, and M. Nieminen, Phys. Status Solidi A **201**, 1443 (2004).

<sup>9</sup>V. Podzorov, E. Menard, A. Borissov, V. Kiryukhin, J. A. Rogers, and M. E. Gershenson, Phys. Rev. Lett. 93, 086602 (2004).

<sup>10</sup>E. Menard, V. Podzorov, S.-H. Hur, A. Gaur, M. Gershenson, and J. Rogers, Adv. Mater. 16, 2097 (2004).

<sup>11</sup>Y. Xia, V. Kalihari, C. D. Frisbie, N. K. Oh, and J. A. Rogers, Appl. Phys. Lett. **90**, 162106 (2007).

<sup>12</sup>M. Uno, T. Uemura, Y. Kanaoka, Z. Chen, A. Facchetti, and J. Takeya, Org. Electron. 14, 1656 (2013).

<sup>13</sup>K. Bolotin, K. Sikes, Z. Jiang, M. Klima, G. Fudenberg, J. Hone, P. Kim, and H. Stormer, Solid State Commum. 146, 351 (2008).

<sup>14</sup>B. E. Feldman, B. Krauss, J. H. Smet, and A. Yacoby, Science 337, 1196

<sup>15</sup>D.-K. Ki and A. F. Morpurgo, Nano Lett. **13**, 5165 (2013).

<sup>16</sup>J. Falson, D. Maryenko, Y. Kozuka, A. Tsukazaki, and M. Kawasaki, Appl. Phys. Express 4, 091101 (2011).

<sup>17</sup>Y. Kozuka, A. Tsukazaki, and M. Kawasaki, Appl. Phys. Rev. 1, 011303 (2014).

<sup>18</sup>W. Pan, N. Masuhara, N. S. Sullivan, K. W. Baldwin, K. W. West, L. N. Pfeiffer, and D. C. Tsui, Phys. Rev. Lett. **106**, 206806 (2011).

<sup>19</sup>G. Gamez and K. Muraki, Phys. Rev. B **88**, 075308 (2013).

- $^{20}\mathrm{A}.$ Tsukazaki, S. Akasaka, K. Nakahara, Y. Ohno, H. Ohno, D. Maryenko, A. Ohtomo, and M. Kawasaki, Nature Mater. 9, 889 (2010).

- <sup>21</sup>Y. Kozuka, A. Tsukazaki, D. Maryenko, J. Falson, S. Akasaka, K. Nakahara, S. Nakamura, S. Awaji, K. Ueno, and M. Kawasaki, Phys. Rev. **B 84**, 033304 (2011).

- <sup>22</sup>Y. Dong, Z.-Q. Fang, D. C. Look, D. R. Doutt, G. Cantwell, J. Zhang, J. J. Song, and L. J. Brillson, J. Appl. Phys. 108, 103718 (2010).

- <sup>23</sup>B. J. Coppa, R. F. Davis, and R. J. Nemanich, Appl. Phys. Lett. 82, 400

- <sup>24</sup>U. Özgür, Y. I. Alivov, C. Liu, A. Teke, M. A. Reshchikov, S. Dorgan, V.

- 25M. W. Allen and S. M. Durbin, Appl. Phys. 98, 041301 (2005).

25M. W. Allen and S. M. Durbin, Appl. Phys. Lett. 92, 122110 (2008).

26R. Vetury, N.-Q. Zhang, S. Keller, and U. K. Mishra, IEEE Trans. Electron Devices 48, 560 (2001).