University of Nevada, Reno

# **Boost Matrix Converters in Clean Energy Systems**

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

by

Ekrem Karaman

Prof. Andrzej Trzynadlowski/ Dissertation Advisor

May, 2014

## THE GRADUATE SCHOOL

UNIVERSITY OF NEVADA RENO

We recommend that the dissertation prepared under our supervision by

## EKREM KARAMAN

entitled

## **Boost Matrix Converters in Clean Energy Systems**

Be accepted in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Andrzej M. Trzynadlowski, Ph.D., Advisor

Mehdi Etezadi-Amoli, Ph.D., Committee Member

M. Sami Fadali, Ph.D., Committee Member

Xiaoshan Zhu, Ph.D., Committee Member

Murat Yuksel, Ph.D., Graduate School Representative

Marsha H. Read, Ph. D., Dean, Graduate School

May, 2014

### ABSTRACT

This dissertation describes an investigation of novel power electronic converters, based on the ultra-sparse matrix topology and characterized by the minimum number of semiconductor switches. The Z-source, Quasi Z-source, Series Z-source and Switched-inductor Z-source networks were originally proposed for boosting the output voltage of power electronic inverters. These ideas were extended here on three-phase to three-phase and three-phase to single-phase indirect matrix converters.

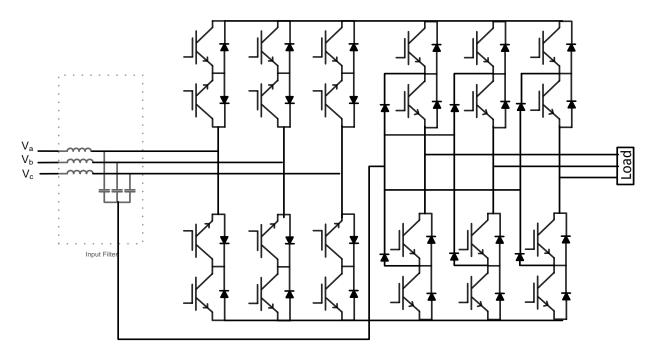

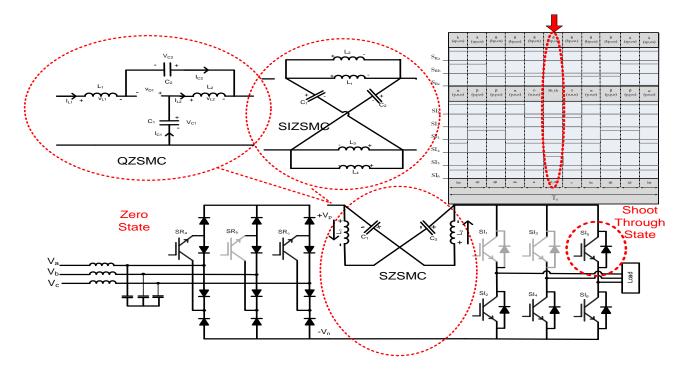

For the three-phase to three-phase matrix converters, the Z-source networks are placed between the three-switch input rectifier stage and the output six-switch inverter stage. A brief shoot-through state produces the voltage boost. An optimal pulse width modulation technique was developed to achieve high boosting capability and minimum switching losses in the converter.

For the three-phase to single-phase matrix converters, those networks are placed similarly. For control purposes, a new modulation technique has been developed. As an example application, the proposed converters constitute a viable alternative to the existing solutions in residential wind-energy systems, where a low-voltage variable-speed generator feeds power to the higher-voltage fixed-frequency grid.

Comprehensive analytical derivations and simulation results were carried out to investigate the operation of the proposed converters. Performance of the proposed converters was then compared between each other as well as with conventional converters. The operation of the converters was experimentally validated using a laboratory prototype.

To my beloved wife Maria and my son Ersan...

### ACKNOWLEDGMENT

I would like to express my heartfelt gratitude to Dr. Trzynadlowski for his inspiring guidance and encouragement throughout my graduate studies at UNR. I am fortunate to have worked with him and witnessed his dedication to research.

I express my sincere appreciation to the other members of committee; Dr. Etezadi, Dr. Fadali, Dr. Yuksel and Dr. Zhu. My thanks are also extended to the PhD candidate Mehdi Farasat for his help in setting the laboratory prototype and to the former MS student Fen Niu for her help in the initial simulations of the converters.

Finally and most importantly, I would like to thank my parents Sohret-Ibrahim Karaman and my sister and brother in law Dr. Gulzade – Dr. M. Emin Ozyalvacli and my mother in law Dr. Elena Derbeneva for their continuous support and love.

## **Table of Contents**

| ABS   | STRACT    | `i                                            |

|-------|-----------|-----------------------------------------------|

| ACI   | KNOWL     | EDGMENTiii                                    |

| List  | of Table  |                                               |

| List  | of Figur  | es x                                          |

| Cha   | pter 1    |                                               |

| Intro | oduction  |                                               |

| 1.1   | Backgro   | ound1                                         |

| 1.2   | Disserta  | tion Objectives                               |

| 1.3   | Content   | of the Dissertation                           |

| Cha   | pter 2    |                                               |

| Тор   | ologies a | nd Modulation Techniques of Matrix Converters |

| 2.1   | Matrix (  | Converter Topologies                          |

|       | 2.1.1     | Direct Matrix Converters                      |

|       | 2.1.2     | Indirect Matrix Converters                    |

| 2.2   | Modula    | tion Techniques for Matrix Converters         |

|       | 2.2.1     | Space Vector Rectifier Control                |

|       | 2.2.2     | Space Vector Inverter Control                 |

|     | 2.2.3     | Indirect Modulation of Matrix Converter         | 35 |

|-----|-----------|-------------------------------------------------|----|

| 2.3 | Conclus   | sion                                            | 41 |

| Cha | pter 3    |                                                 | 42 |

| Boo | ost Netwo | ork Topologies                                  | 42 |

| 3.1 | Z-sourc   | e Network                                       | 43 |

|     | 3.1.1     | Operation Principle                             | 46 |

|     | 3.1.2     | Circuit Analysis                                | 46 |

|     | 3.1.3     | Boost Factor and Voltage Gains                  | 49 |

|     | 3.1.4     | Design Guideline                                | 50 |

| 3.2 | Series Z  | Z-source Network                                | 51 |

|     | 3.2.1     | Operation Principle                             | 55 |

|     | 3.2.2     | Circuit Analysis                                | 56 |

| 3.3 | Quasi Z   | -source Network                                 | 58 |

|     | 3.3.1     | Circuit Analysis                                | 59 |

| 3.4 | Switche   | d Inductor Z-source Network                     | 61 |

|     | 3.4.1     | Circuit Analysis                                | 63 |

| 3.5 | Conclus   | sion                                            | 64 |

| Cha | pter 4    |                                                 | 65 |

| Thr | ee Phase  | to Three Phase Matrix Converters with Z-sources | 65 |

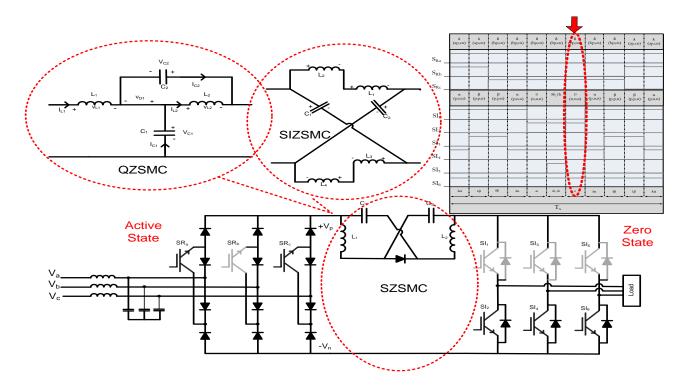

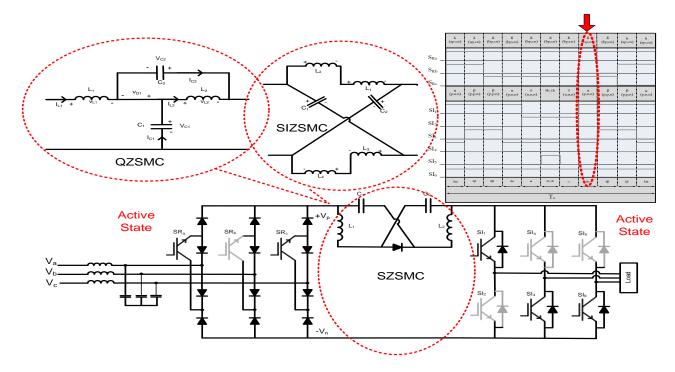

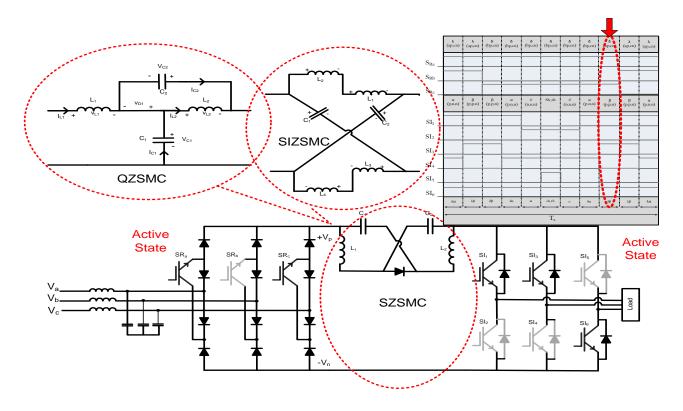

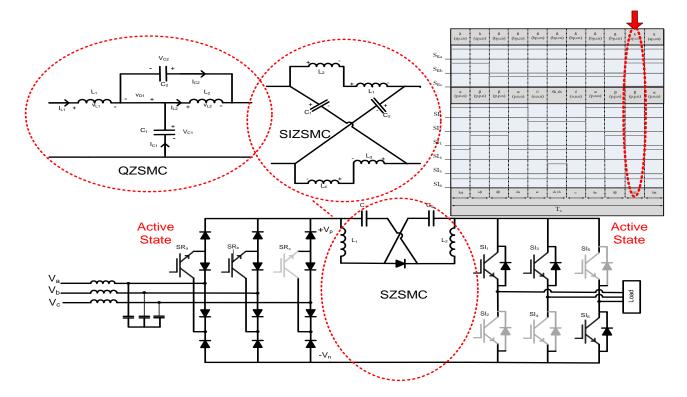

| 4.1 | Topolog   | gies                                            | 67 |

|     | 4.1.1     | Series Z-source Matrix Converter                                    | 67  |

|-----|-----------|---------------------------------------------------------------------|-----|

|     | 4.1.2     | Quasi Z-source Matrix Converter                                     | 68  |

|     | 4.1.3     | Switched Inductor Z-source Matrix Converter                         | 68  |

| 4.2 | Operatio  | Dn                                                                  | 69  |

|     | 4.2.1     | Series Z-source Matrix Converter                                    | 69  |

|     | 4.2.2     | Quasi Z-source Matrix Converter                                     | 70  |

|     | 4.2.3     | Switched Inductor Z-source Matrix Converter                         | 71  |

| 4.3 | Circuit A | Analysis                                                            | 73  |

|     | 4.3.1     | Series Z-source Matrix Converter                                    | 73  |

|     | 4.3.2     | Quasi Z-source Matrix Converter                                     | 75  |

|     | 4.3.3     | Switched Inductor Matrix Converter                                  | 77  |

| 4.4 | Design    | of Passive Components                                               | 78  |

|     | 4.4.1     | Input Current Filter                                                | 78  |

|     | 4.4.2     | Network Components                                                  | 80  |

| 4.5 | Switchin  | ng Strategy                                                         | 82  |

| 4.6 | Results   |                                                                     | 95  |

|     | 4.6.1     | Series and Cascaded Z-source Matrix Converters – Simulation Results | 95  |

|     | 4.6.2     | Series Z-Source Matrix Converter - Experimental Results             | 106 |

|     | 4.6.3     | Quasi Z-Source Matrix Converter - Simulation Results                | 110 |

|     | 4.6.4     | Quasi Z-Source Matrix Converter – Experimental Results              | 114 |

|      | 4.6.5     | Switched Inductor Z-Source Matrix Converter - Simulation Results   | 118 |

|------|-----------|--------------------------------------------------------------------|-----|

|      | 4.6.6     | Switched Inductor Z-Source Matrix Converter - Experimental Results | 123 |

| 4.7  | FFT An    | alysis of Input and Output Currents                                | 126 |

| 4.8  | Conclusi  | on                                                                 | 131 |

| Cha  | pter 5    |                                                                    | 133 |

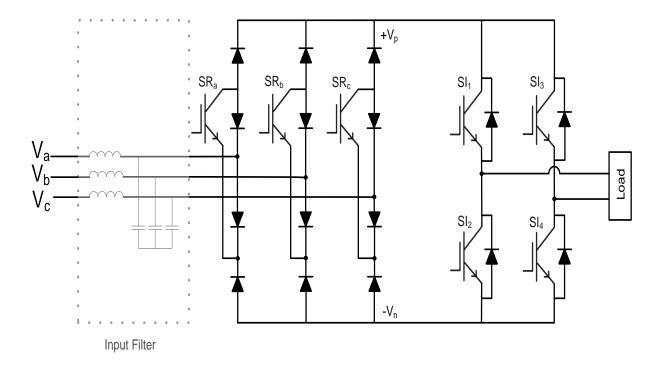

| Sing | gle-Phase | e Boost Matrix Converters                                          | 133 |

| 5.1  | Introd    | uction                                                             | 133 |

| 5.2  | Topol     | ogies                                                              | 133 |

| 5.3  | Contro    | ol Strategy                                                        | 136 |

| 5.4  | Circui    | t Analysis                                                         | 141 |

|      | 5.4.1     | Z-source Circuit                                                   | 141 |

|      | 5.4.2     | Switched Inductor Z-source Circuit                                 |     |

| 5.5  | Simula    | tion Results                                                       | 143 |

| 5.6  | Concl     | usion                                                              | 148 |

| Cha  | pter 6    |                                                                    | 149 |

| 6.1  | Introduc  | ction                                                              | 149 |

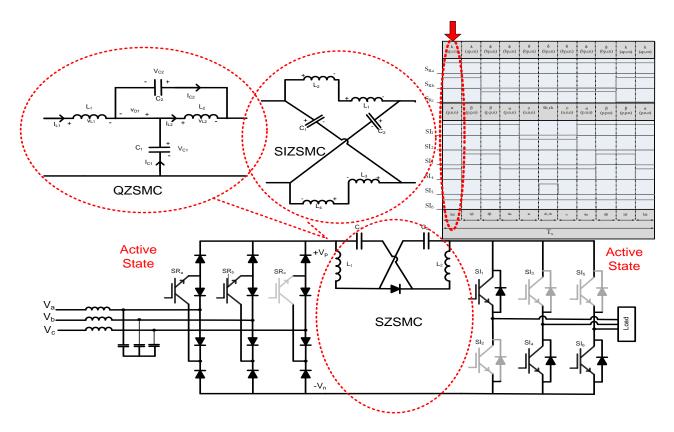

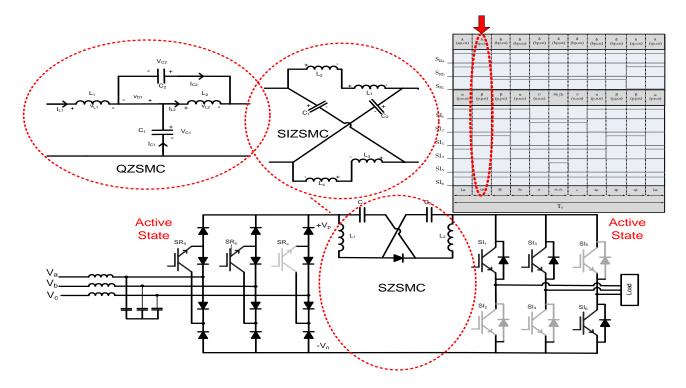

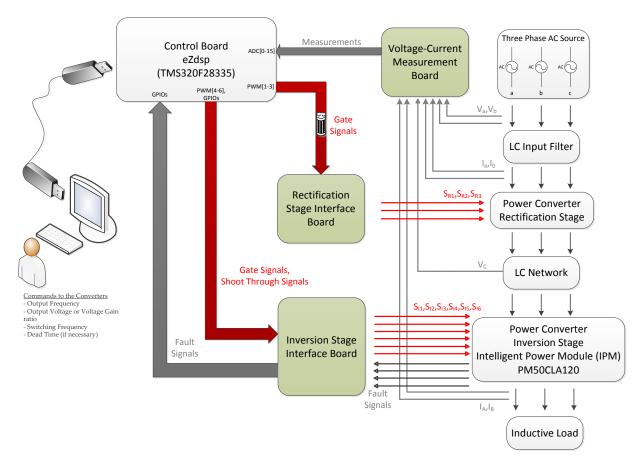

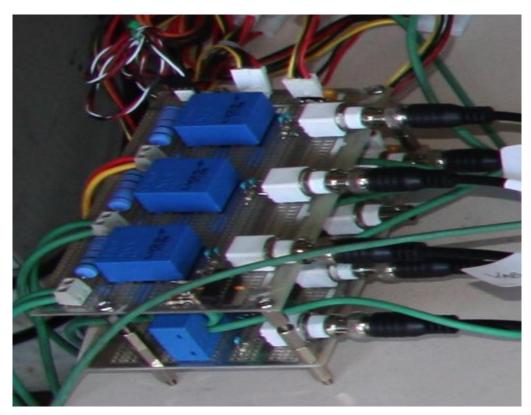

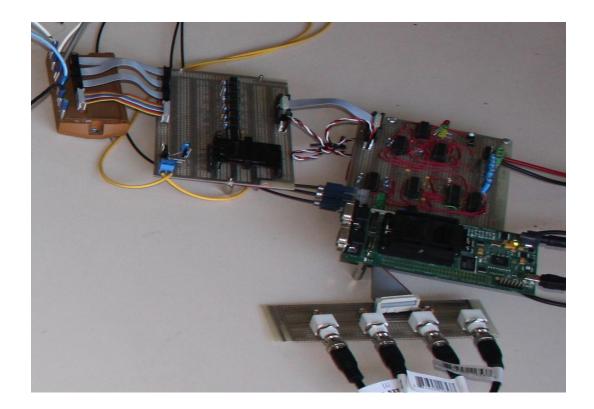

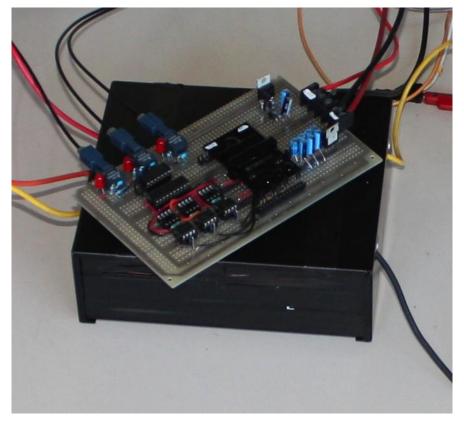

| 6.2  | Hardwa    | re Implementation                                                  | 149 |

|      | 6.2.1     | Structure of the Prototype Converters                              | 149 |

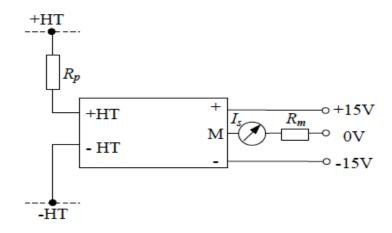

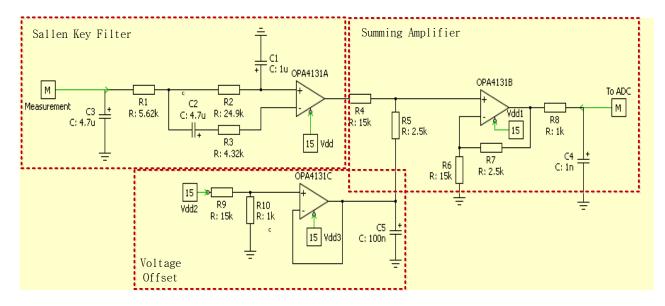

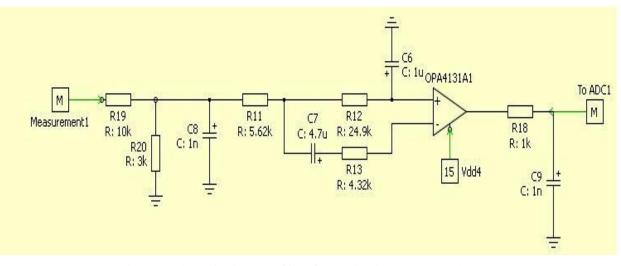

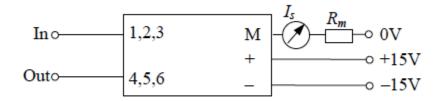

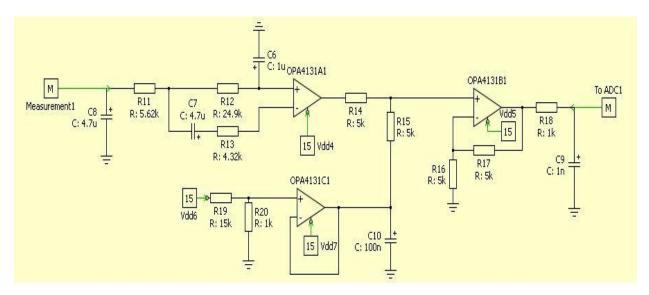

|      | 6.2.2     | Voltage – Current Measurement Board                                | 151 |

|      | 6.2.3     | Control Board – eZDSP controller (TMS320F28335)                    | 155 |

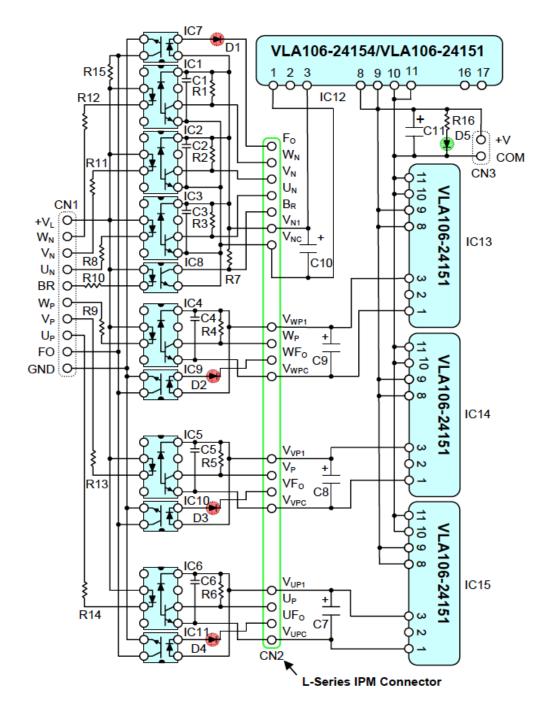

|     | 6.2.4    | Inversion Stage Power Converter – Powerex Intelligent Power Module (IPM) | 156 |

|-----|----------|--------------------------------------------------------------------------|-----|

|     | 6.2.5    | Inversion Stage Interface Circuit                                        | 157 |

|     | 6.2.6    | Rectification Stage Interface Circuit                                    | 161 |

| 6.3 | Softwar  | re Implementation                                                        | 162 |

|     | 6.3.1    | ADC Module                                                               | 163 |

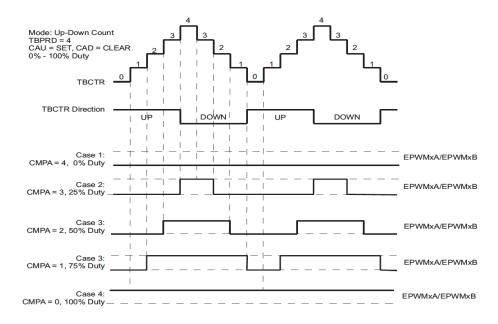

|     | 6.3.2    | PWM Module                                                               | 164 |

| 6.4 | Conclus  | sion                                                                     | 169 |

| Cha | pter 7   |                                                                          | 170 |

| Sun | nmary an | d Conclusion                                                             | 170 |

| 7.1 | Summa    | ry of the Dissertation                                                   | 171 |

| 7.2 | Conclus  | sion                                                                     | 172 |

| 7.3 | Future V | Work                                                                     | 173 |

| Ref | erences  |                                                                          | 175 |

## List of Tables

| Chapter 2 |                                                                                     |   |

|-----------|-------------------------------------------------------------------------------------|---|

| Table 2.1 | Comparison of the back-to-back converters and conventional MCs [36]                 | 8 |

| Table 2.2 | Comparison of MC topologies                                                         | 5 |

| Table 2.3 | Switching vector states for rectification stage                                     | 9 |

| Table 2.4 | Switching vector states of the inversion stage                                      | 3 |

| Chapter 3 | 3                                                                                   |   |

| Table 3.1 | Governing functions of ZSI                                                          | 0 |

| Table 3.2 | Governing equations of series Z-source inverter                                     | 7 |

| Table 3.3 | Governing equations of quasi Z-source inverter [12]                                 | 1 |

| Table 3.4 | Governing equations of switched inductor Z-source inverter                          | 4 |

| Chapter 4 |                                                                                     |   |

| Table 4.1 | System 1 parameters                                                                 | 6 |

| Table 4.2 | System 2 parameters 10                                                              | 1 |

| Table 4.3 | System parameters                                                                   | 1 |

| Table 4.4 | System parameters                                                                   | 8 |

| Chapter 5 |                                                                                     |   |

| Table 5.1 | System parameters. Top to bottom: super-sparse, Z-source, and switched-inductor 14- | 4 |

| Chapter 6 |                                                                                     |   |

| Table 6.1 | AQCTLA register coding                                                              | 6 |

| Table 6.2 | AQCTLA register coding for the rectification space vector                           | 5 |

| Table 6.3 | AQCTLA register coding for the inversion space vector                               | 7 |

| Table 6.4 | CMPA registers values for the rectification stage                                   | 8 |

| Table 6.5 | CMPA and CMPB registers values for the rectification stage                          | 8 |

## List of Figures

| Chapter 1                                                                                  |             |

|--------------------------------------------------------------------------------------------|-------------|

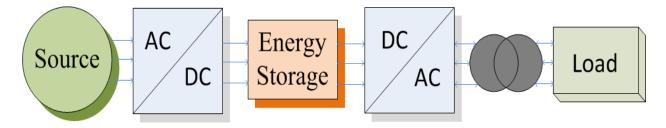

| Fig. 1.1 Ac-dc-ac conversionin a back-to-back converter                                    |             |

| Fig. 1.2 Transformerless direct ac-ac conversion                                           |             |

| Chapter 2                                                                                  |             |

| Fig. 2.1 Classification of matrix converters                                               | 6           |

| Fig. 2.2 Direct matrix converter                                                           | 9           |

| Fig. 2.4 Indirect matrix converter ( $\pi/6$ displacement angle)                           |             |

| Fig. 2.5 Indirect matrix converter (full range displacement angle).                        |             |

| Fig. 2.6 Circuit diagram of the indirect matrix converter                                  |             |

| Fig. 2.7 Indirect matrix converter to direct matrix converter transformation               |             |

| Fig. 2.8 Sparse matrix converter                                                           |             |

| Fig. 2.9 Very sparse matrix converter                                                      |             |

| Fig. 2.10 Ultra sparse matrix converter.                                                   |             |

| Fig. 2.11 Legs of the front-end rectifier. Left: sparse matrix converter, right: ultra spa | arse matrix |

| converter                                                                                  |             |

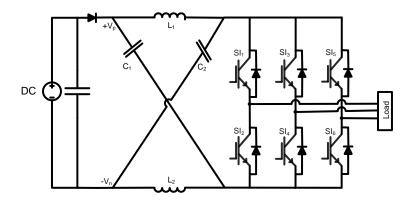

| Fig. 2.12 Z source ultra sparse matrix converter.                                          |             |

| Fig. 2.13 IMC with a three-level PWM output stage                                          |             |

| Fig. 2.14 IMC with additional single stage three-level PWM output stage                    |             |

| Fig. 2.15 Unidirectional IMC with a three-level PWM output stage                           |             |

| Fig. 2.16 Major specification of modulation techniques for matrix converters               |             |

| Fig. 2.17 Diagram of input-current space vectors                                           |             |

| Fig. 2.18 Reference input current space vector with the adjacent vectors                   |             |

| Fig. 2.19 Diagram of output-voltage space vectors.                                            | 34  |

|-----------------------------------------------------------------------------------------------|-----|

| Fig. 2.20 Reference output voltage space vector with the adjacent vectors                     | 34  |

| Fig. 2.21 Step 1: $T_{\lambda\alpha}$ where $\lambda$ =ca and $\alpha$ =010,                  | 38  |

| Fig. 2.22 Step 2: $T_{\lambda\beta}$ where $\lambda$ =ca and $\beta$ =011                     | 38  |

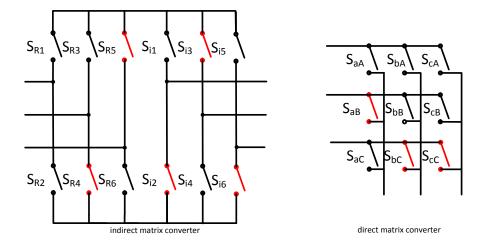

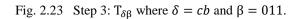

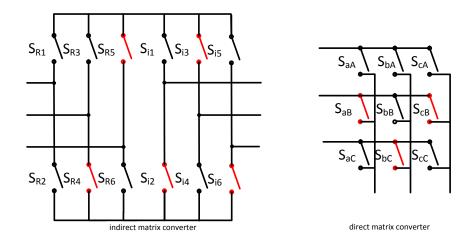

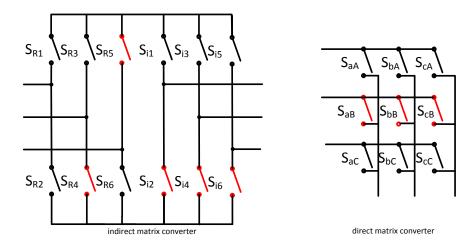

| Fig. 2.23 Step 3: $T_{\delta\beta}$ where $\delta$ =cb and $\beta$ =011                       | 39  |

| Fig. 2.24 Step 4: $T_{\delta\alpha}$ where $\delta$ =cb and $\alpha$ =010                     | 39  |

| Fig. 2.25 Step 5: $T_0$ where $\delta$ =cb and $\alpha$ =000.                                 | 39  |

| Fig. 2.26 Step 6: $T_{\delta\alpha}$ where $\delta$ =cb and $\alpha$ =010                     | 40  |

| Fig. 2.27 Step 7: $T_{\delta\beta}$ where $\delta$ =cb and $\beta$ =01.1                      | 40  |

| Fig. 2.28 Step 8: $T_{\lambda\beta}$ where $\lambda$ =ca and $\beta$ =011                     | 40  |

| Fig. 2.29 Step 9: $T_{\lambda\alpha}$ where $\lambda$ =ca and $\alpha$ =010                   | 41  |

| Chapter 3                                                                                     |     |

| Fig. 3.1 Z-source inverter                                                                    | 43  |

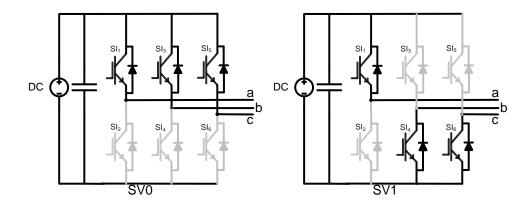

| Fig. 3.2 States of the VSI (dark power switches are on, grey switches are off)                | 44  |

| Fig. 3.3 Instances of shoot-through states. From top to bottom (a) three legs shoot-through ( | (b) |

| two legs shoot-through (c) one leg shoot-through                                              | 45  |

| Fig. 3.4 Equivalent-circuits of the Z-source: (a) non-shoot-through states, (b) shoot-throu   | gh  |

| states                                                                                        | 46  |

| Fig. 3.5 Series Z-source inverter                                                             | 52  |

| Fig. 3.6 Derivation stage 1 of series Z-source inverter                                       | 53  |

| Fig. 3.7 Derivation stage 2 of series Z-source inverter                                       | 53  |

| Fig. 3.8 Derivation stage 3 of series Z-source inverter                                       | 54  |

| Fig. 3.9 Derivation stage 4 of series Z-source inverter                                       | 54  |

| Fig. 3.10 Derivation stage 5 of series Z-source inverter                                      | 54  |

| Fig. 3.11 Derivation stage 5 of series Z-source inverter                                       | . 55 |

|------------------------------------------------------------------------------------------------|------|

| Fig. 3.12 From left to right (a) non-shoot-through states (b) shoot-through states             | . 55 |

| Fig. 3.13 Quasi Z-source inverter                                                              | . 58 |

| Fig. 3.14 From top to bottom (a) shoot-through states (b) non-shoot-through states             | . 59 |

| Fig. 3.15 Switched inductor Z-source                                                           | . 61 |

| Fig. 3.16 Equivalent circuits of the switched-inductor Z-source: (a) non-shoot-through states, | (b)  |

| shoot-through states.                                                                          | . 62 |

| Chapter 4                                                                                      |      |

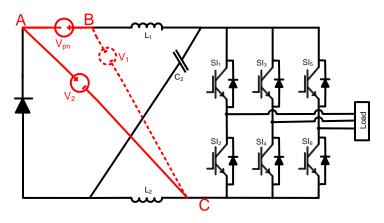

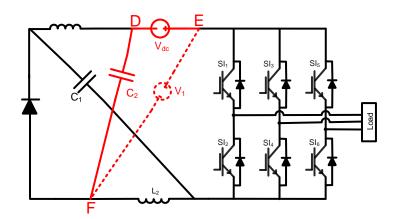

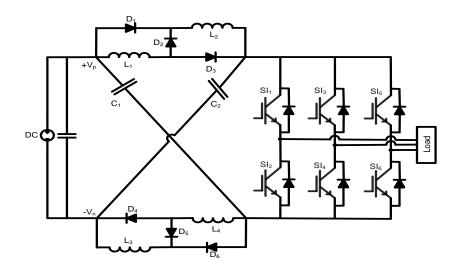

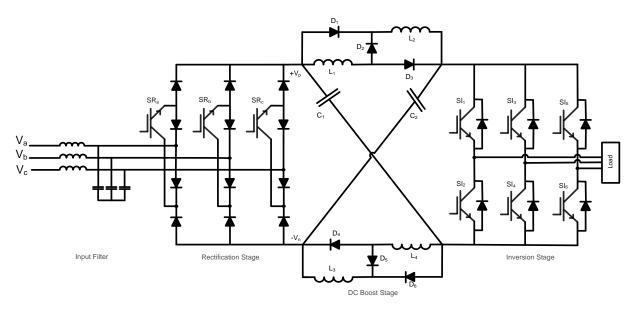

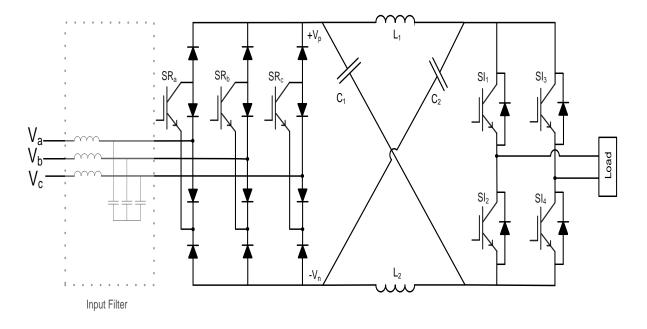

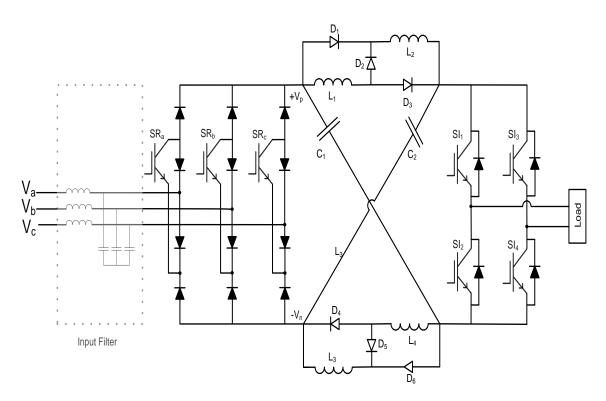

| Fig. 4.1 Series Z-source matrix converter                                                      | . 67 |

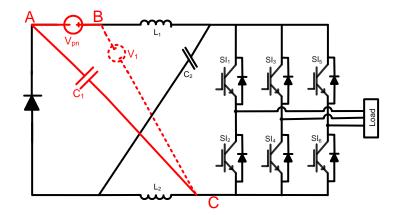

| Fig. 4.2 Quasi Z-source matrix converter.                                                      | . 68 |

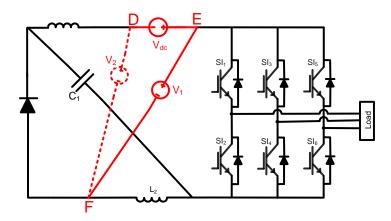

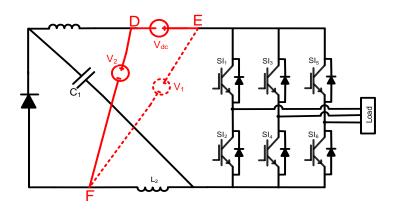

| Fig. 4.3 Switched inductor Z-source matrix converter.                                          | . 69 |

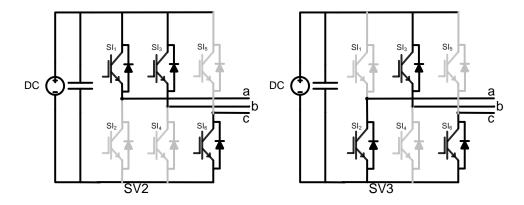

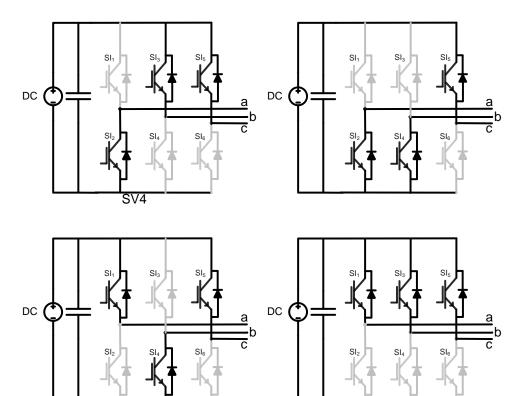

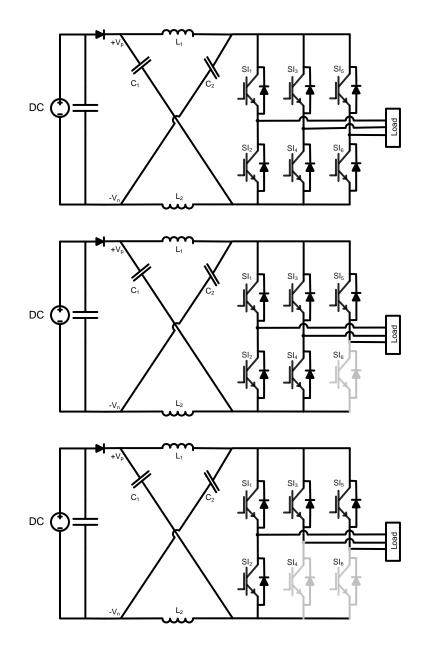

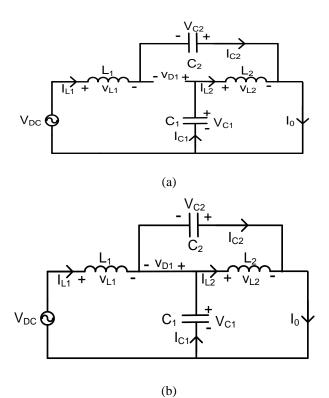

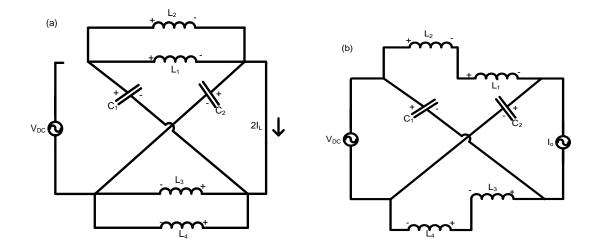

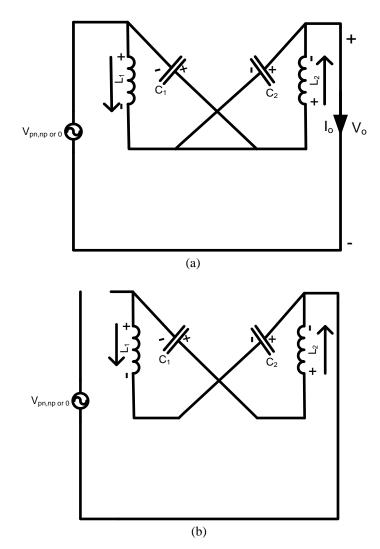

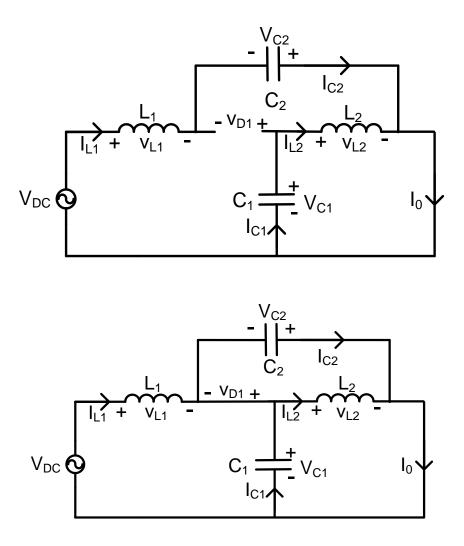

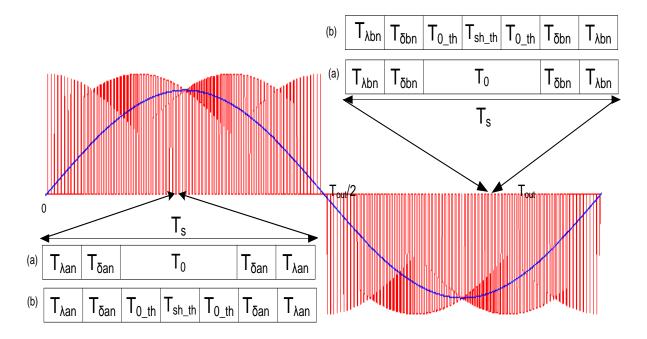

| Fig. 4.4 Top to bottom (a) non-shoot-through states (b) shoot-through states.                  | . 70 |

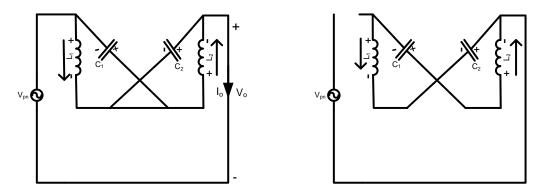

| Fig. 4.5 Top to bottom (a) shoot-through states (b) non-shoot-through states.                  | . 71 |

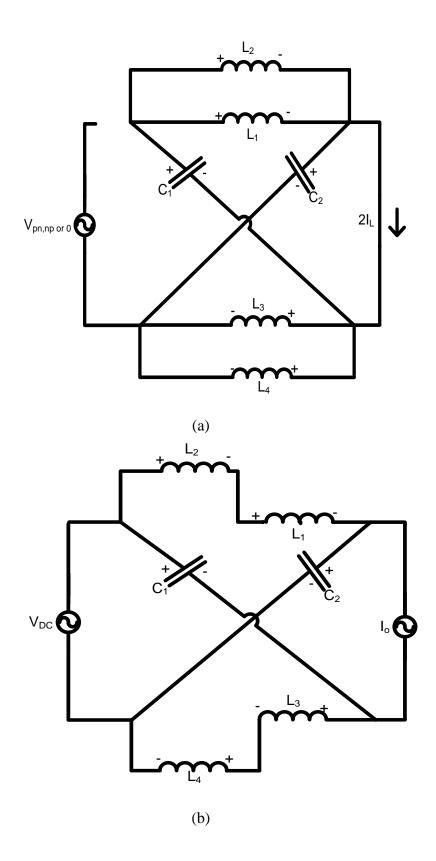

| Fig. 4.6 Top to bottom (a) shoot-through states (b) non-shoot-through states.                  | . 72 |

| Fig. 4.7 Diagram of input-current space vectors                                                | . 82 |

| Fig. 4.8 Reference input-current space vector with the adjacent vectors.                       | . 83 |

| Fig. 4.9 Diagram of input-current space vectors                                                | . 84 |

| Fig. 4.10 Reference output voltage space vector with the adjacent vectors.                     | . 84 |

| Fig. 4.11 Switching signals and sequences. Top to bottom: rectification stage (input-cur       | rent |

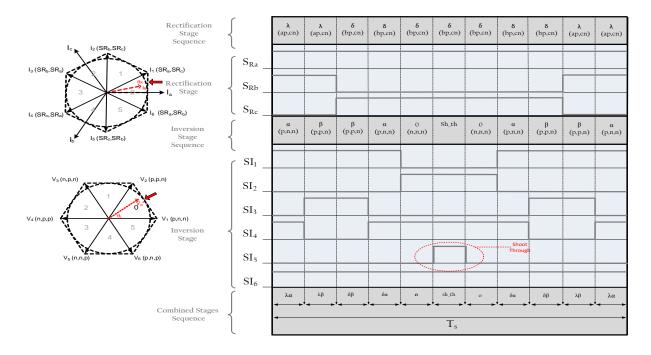

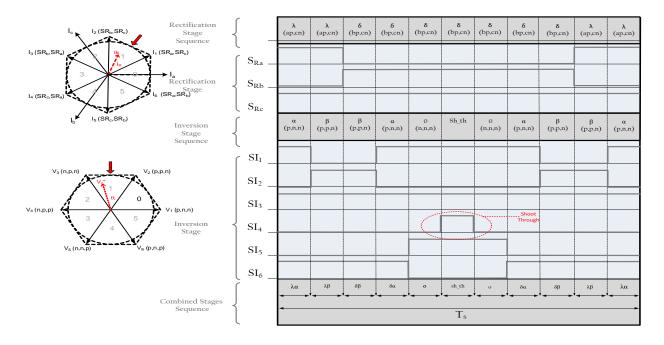

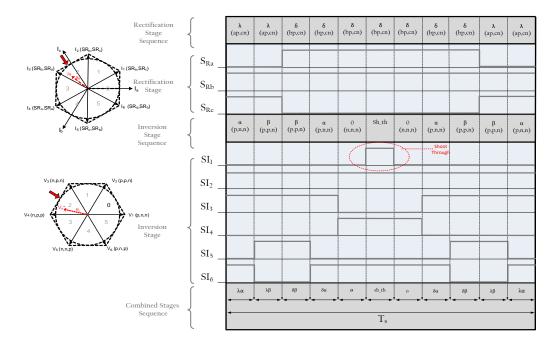

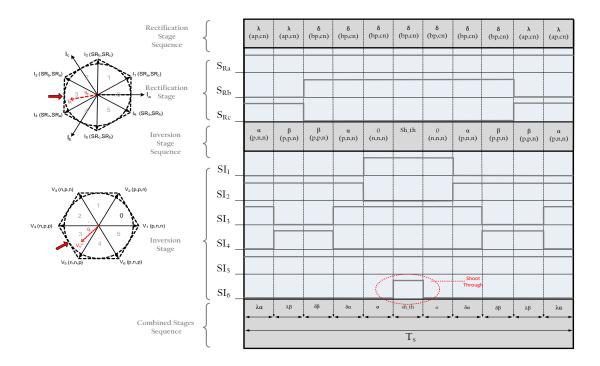

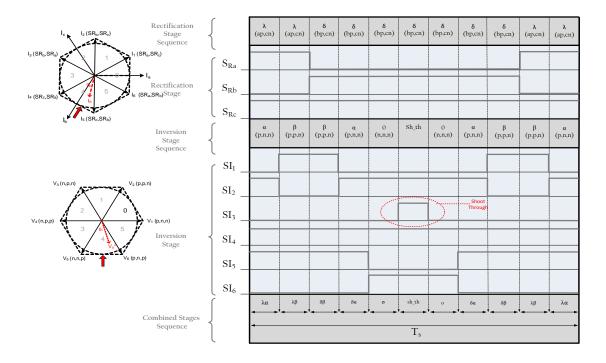

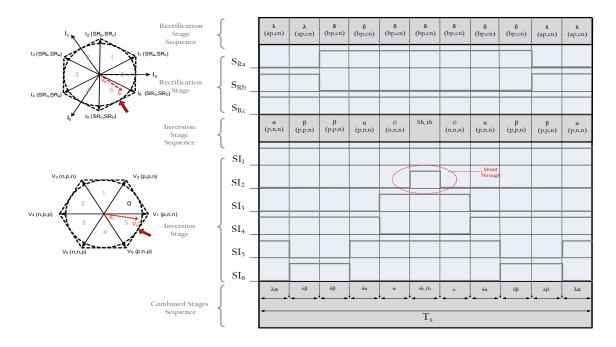

| space vector in sector 0), inversion stage (output voltage space vector in sector 0)           | . 87 |

| Fig. 4.12 Switching signals and sequences. Top to bottom: rectification stage (input-cur       | rent |

| space vector in sector 1), inversion stage (output voltage space vector in sector 1)           | . 87 |

| Fig. 4.13 Switching signals and sequences. Top to bottom: rectification stage (input-cur       | rent |

| space vector in sector 2), inversion stage (output voltage space vector in sector 2)           | . 88 |

| Fig. 4.14 Switching signals and sequences. Top to bottom: rectification stage (input-current                                      |

|-----------------------------------------------------------------------------------------------------------------------------------|

| space vector in sector 3), inversion stage (output voltage space vector in sector 3)                                              |

| Fig. 4.15 Switching signals and sequences. Top to bottom: rectification stage (input-current                                      |

| space vector in sector 4), inversion stage (output voltage space vector in sector 4)                                              |

| Fig. 4.16 Switching signals and sequences. Top to bottom: rectification stage (input-current                                      |

| space vector in sector 5), inversion stage (output voltage space vector in sector 5)                                              |

| Fig. 4.17 Boost matrix converter's switching sequence. Step 1: During $T_{\lambda\alpha}$ . $\theta_R$ and $\theta_i$ are both in |

| zero sector                                                                                                                       |

| Fig. 4.18 Boost matrix converter's switching sequence. Step 2: During $T_{\lambda\beta}$ . $\theta_R$ and $\theta_i$ are both     |

| in zero sector                                                                                                                    |

| Fig. 4.19 Boost matrix converter's switching sequence. Step 3: During $T_{\delta\beta}$ . $\theta_R$ and $\theta_i$ are both in   |

| zero sector                                                                                                                       |

| Fig. 4.20 Boost matrix converter's switching sequence. Step 4: During $T_{\delta\alpha}$ . $\theta_R$ and $\theta_i$ are both in  |

| zero sector                                                                                                                       |

| Fig. 4.21 Boost matrix converter's switching sequence. Step 5: During $T_o$ . $\theta_R$ and $\theta_i$ are both in               |

| zero sector                                                                                                                       |

| Fig. 4. 22 Boost matrix converter's switching sequence. Step 6: During $T_{(sh-th)}$ . $\theta_R$ and $\theta_i$ are              |

| both in zero sector                                                                                                               |

| Fig. 4.23 Boost matrix converter's switching sequence. Step 7: During $T_o$ . $\theta_R$ and $\theta_i$ are both in               |

| zero sector                                                                                                                       |

| Fig. 4.24 Boost matrix converter's switching sequence. Step 8: During $T_{\delta \alpha}$ . $\theta_R$ and $\theta_i$ are both in |

| zero sector                                                                                                                       |

| Fig. 4.25 Boost matrix converter's switching sequence. Step 9: During $T_{\delta\beta}$ . $\theta_R$ and $\theta_i$ are both in   |

| zero sector                                                                                                                       |

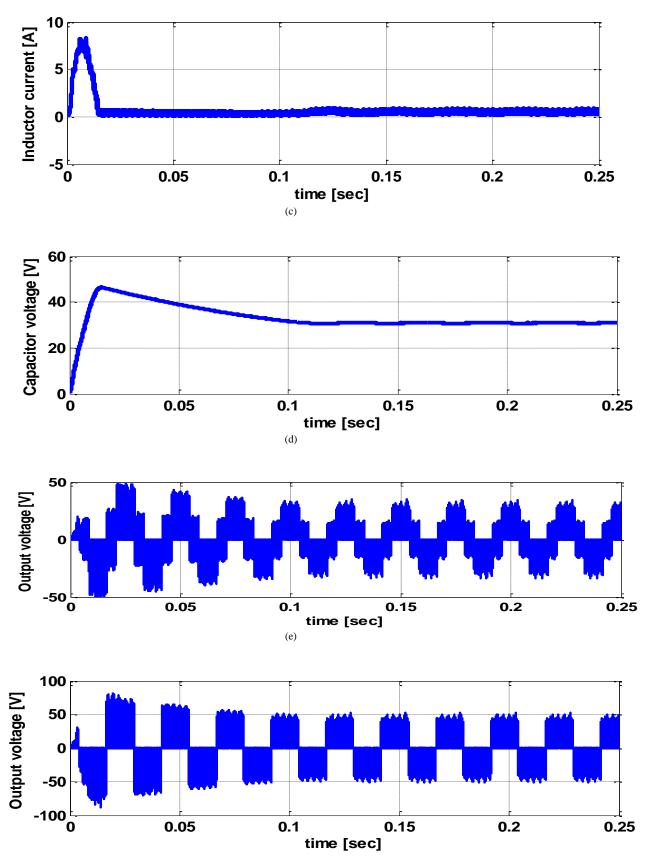

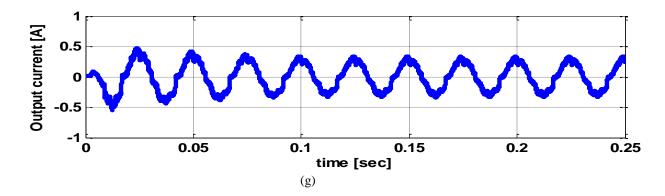

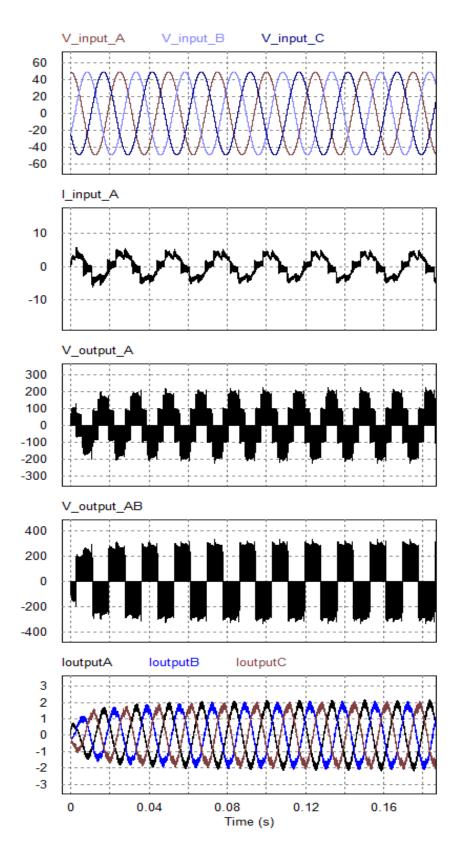

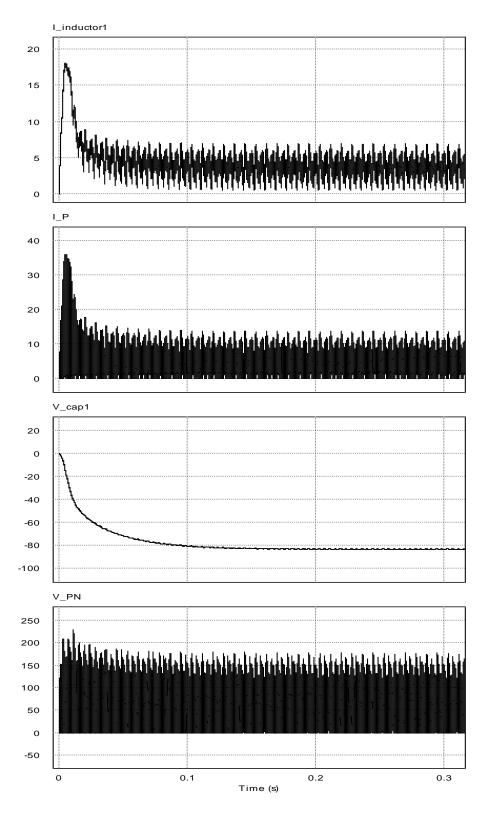

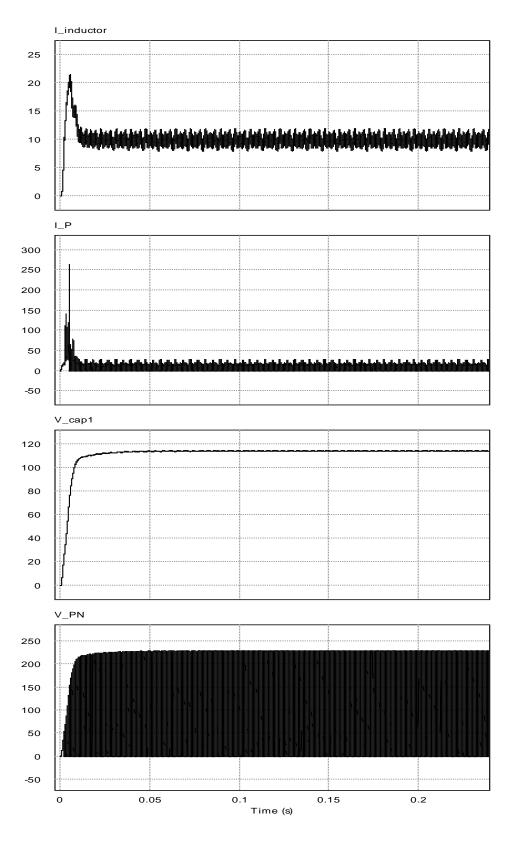

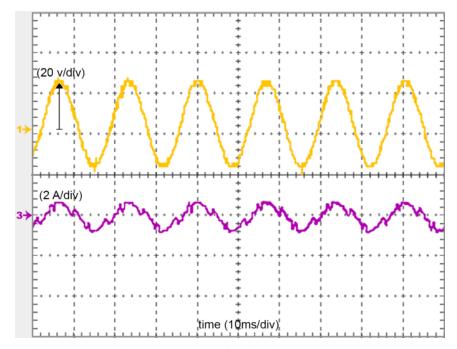

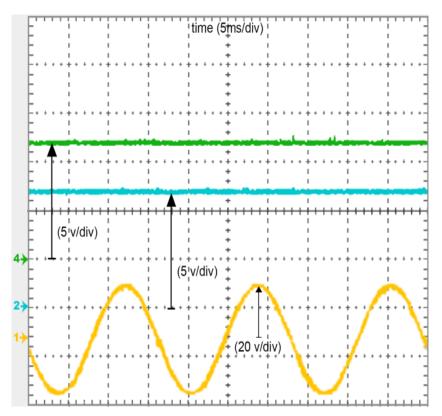

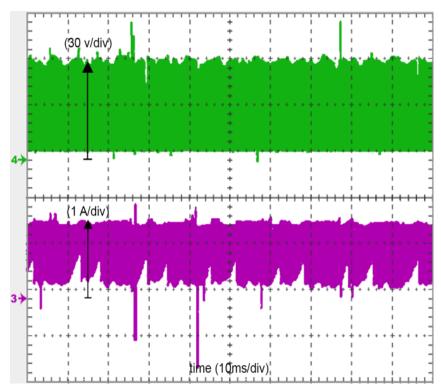

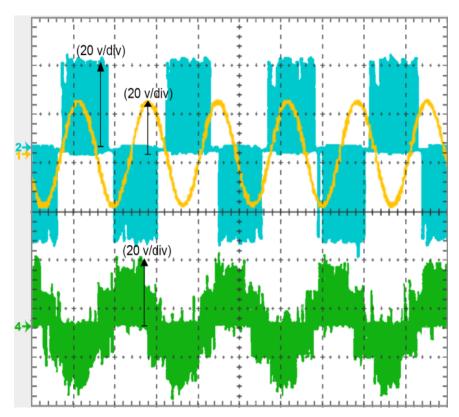

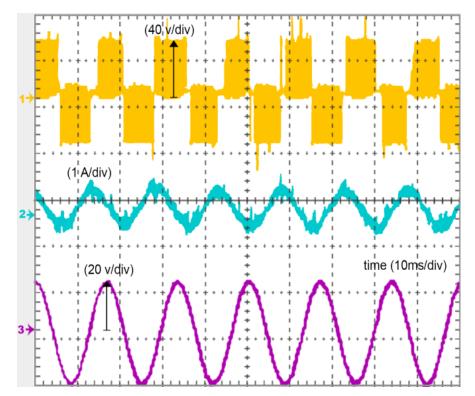

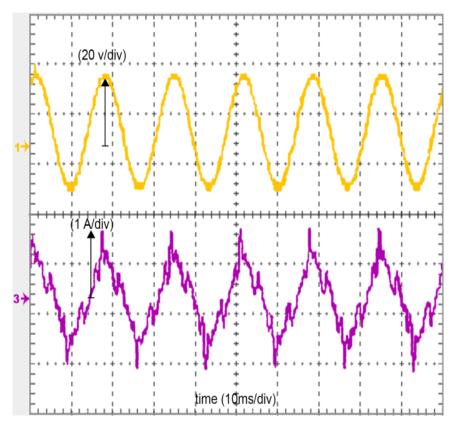

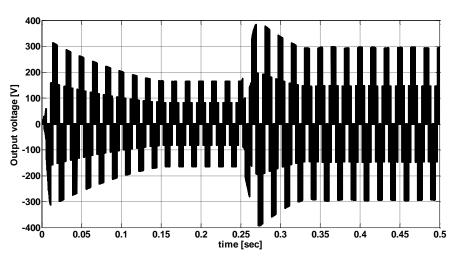

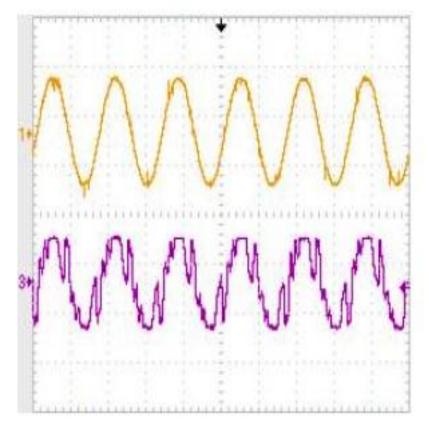

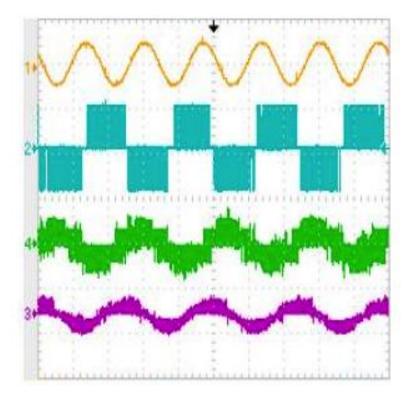

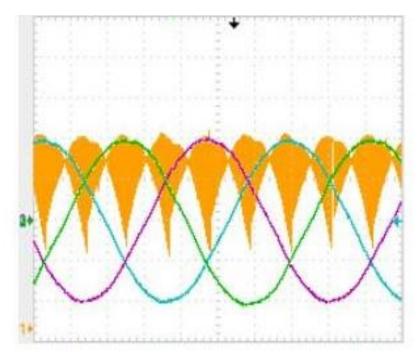

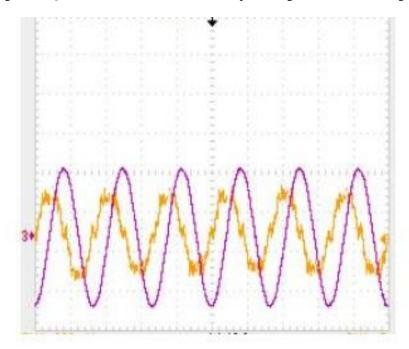

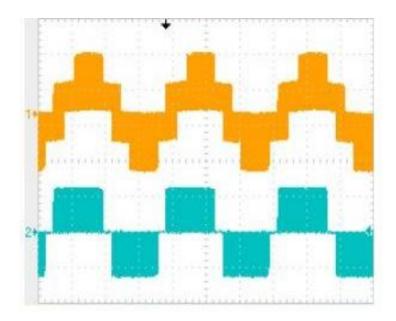

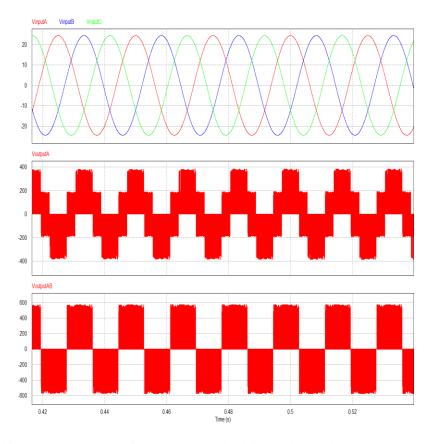

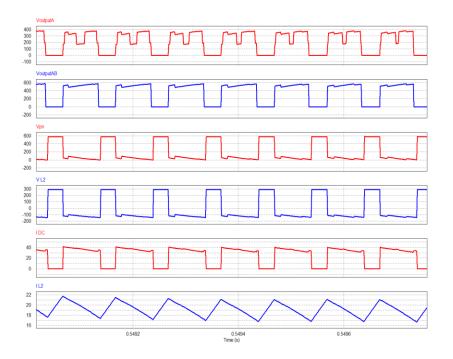

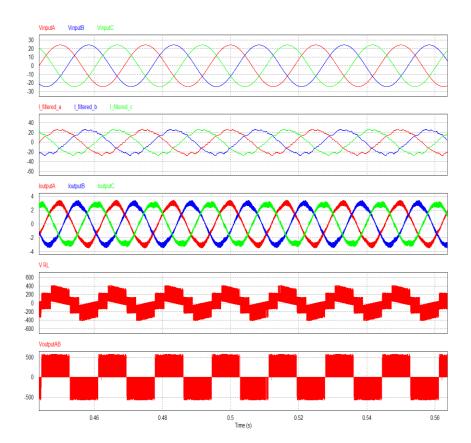

Fig. 4.26 Boost matrix converter's switching sequence. Step 10: During  $T_{\lambda\beta}$ .  $\theta_R$  and  $\theta_i$  are both Fig. 4.27 Boost matrix converter's switching sequence. Step 11: During  $T_{\lambda\alpha}$ .  $\theta_R$  and  $\theta_i$  are both Fig. 4.28 Series Z-source matrix converter: (a) input phase current, (b) dc link current, (c) series Z-source inductor current, (d) series Z-source capacitor voltage, (e) output phase voltage, (f) Fig. 4.29 Cascaded Z-source matrix converter: (a) input phase current, (b) dc link current, (c) series Z-source inductor current, (d) series Z-source capacitor voltage, (e) output phase voltage, Fig. 4.30 Series Z-source, top to bottom: input phase voltages, input phase A current, output Fig. 4.31 Cascaded Z-source, top to bottom: input phase voltages, input phase A current, output Fig. 4.32 Series Z-source, top to bottom: Series Z-source inductor (L1) current, dc link current, Fig. 4.33 Cascaded Z-source, top to bottom: Z-source inductor (L1) current, dc link current, Zsource capacitor (C1) voltage, dc link voltage...... 105 Fig. 4.34 Series Z-source matrix converter. Top: line-line input voltage, bottom: phase input Fig. 4.35 Series Z-source matrix converter. Top: Z-source network capacitor voltages, bottom: Fig. 4.36 Series Z-source matrix converter. Top: Z-source network output voltage, bottom: Z-

| Fig. 4.37 Series Z-source matrix converter. Top: line-line input and output voltages, bottom:     |

|---------------------------------------------------------------------------------------------------|

| output phase voltage                                                                              |

| Fig. 4.38 Series Z-source matrix converter. Top to bottom: line-line output voltage, output phase |

| current, line-line input voltage                                                                  |

| Fig. 4. 39 Cascaded Z-source matrix converter. Top: line-line input voltage, bottom: phase input  |

| current                                                                                           |

| Fig. 4.40 Cascaded Z-source matrix converter: line-line input and output voltages 109             |

| Fig. 4.41 Cascaded Z-source matrix converter. Top: line-line output voltage, bottom: output       |

| phase current                                                                                     |

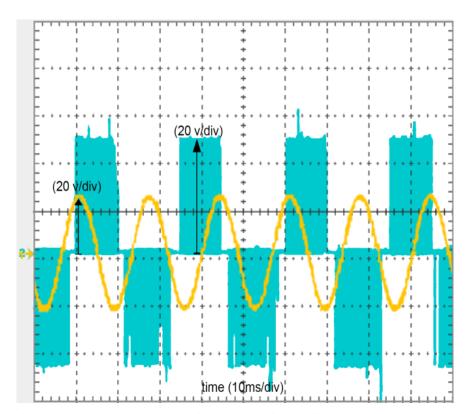

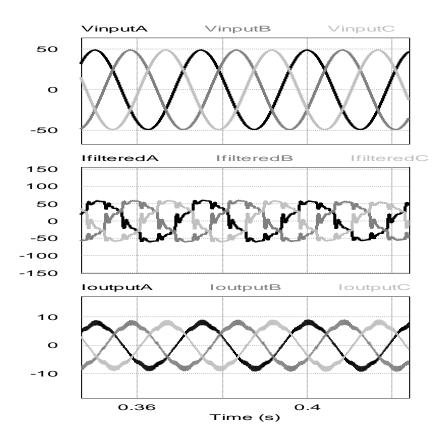

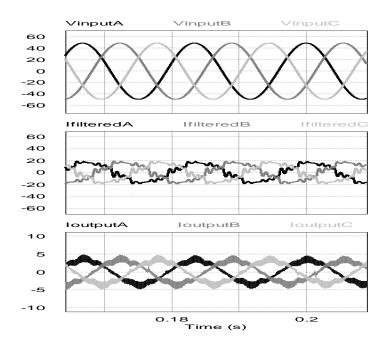

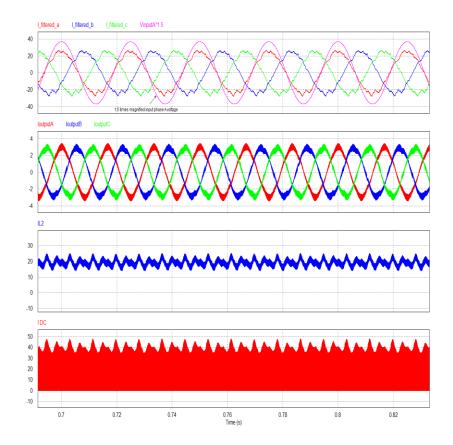

| Fig. 4.42 RL load. Top to bottom: input phase voltages, filtered input currents, output currents. |

|                                                                                                   |

| Fig. 4.43 RL load. Top to bottom: output phase voltage, output line-to-line voltage, capacitor-1  |

| voltage                                                                                           |

| Fig. 4.44 Grid-connected converter. Top to bottom: input phase voltages, filtered input currents, |

| output currents                                                                                   |

| Fig. 4.45 Grid-connected converter. Top to bottom: voltage across the interface inductor, output  |

| line-to-line voltage, capacitor-1 voltage                                                         |

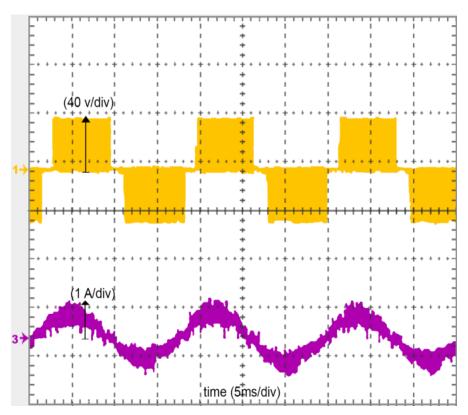

| Fig. 4.46 Quasi Z-source matrix converter: phase A input voltage and current                      |

| Fig. 4.47 Quasi Z-source matrix converter: phase A output current                                 |

| Fig. 4 48 Quasi Z-source matrix converter: phase A output voltage                                 |

| Fig. 4.49 Quasi Z-source matrix converter. Top: line-line input voltage, bottom: phase input      |

| current                                                                                           |

| Fig. 4.50 Quasi Z-source matrix converter. Top to bottom: line-line input voltage, line-line      |

| output voltage, phase output voltage, output phase current                                        |

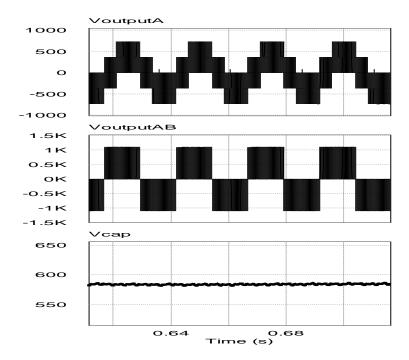

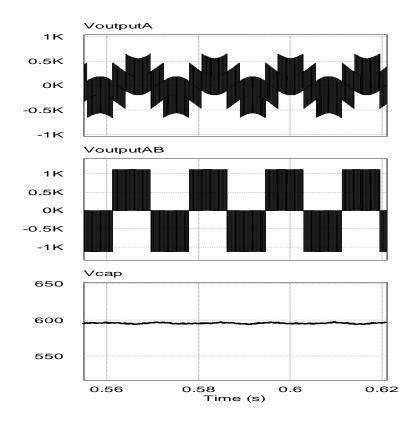

| Fig. 4.51 Quasi Z-source inverter: line-line input voltages and dc-link voltage                 |

|-------------------------------------------------------------------------------------------------|

| Fig. 4.52 Quasi Z-source inverter: line-line input voltages and input phase current 117         |

| Fig. 4.53 Quasi Z-source inverter: Top to bottom: output phase voltage, output line to line     |

| voltage                                                                                         |

| Fig. 4.54 Switched inductor Z-source matrix converter. Top to bottom RL load: input phase       |

| voltages, output phase voltage, output line to line voltage                                     |

| Fig. 4.55 RL load. Top to bottom: filtered input currents and the input phase A voltage, output |

| currents, inductor 2 current, dc-link current                                                   |

| Fig. 4.56 RL load – zoom-in. Top to bottom: output phase voltage, output line-to-line voltage,  |

| dc-link voltage, inductor 2 voltage, dc-link current, inductor 2 current                        |

| Fig. 4.57 Grid connected switched inductor Z-source matrix converter. Top to bottom: input      |

| phase voltages, input phase currents, output currents, phase-A voltage across the interface     |

| inductor, converter output voltage before the inductor                                          |

| Fig. 4.58 Switched inductor Z-source matrix converter: phase A input voltage and current 122    |

| Fig. 4.59 Switched inductor Z-source matrix converter: phase A output current 122               |

| Fig. 4.60 Switched inductor Z-source matrix converter: phase A output voltage 123               |

| Fig. 4.61 Switched inductor Z-source matrix converter. Top: line-line input voltage, bottom:    |

| phase input current                                                                             |

| Fig. 4.62 Switched inductor Z-source matrix converter. Top: Z-source network capacitor          |

| voltages, bottom: line-line input voltage                                                       |

| Fig. 4.63 Switched inductor Z-source matrix converter. Top: Zoomed Z-source network             |

| capacitor voltages, bottom: line-line input voltage                                             |

| Fig. 4.64 Switched inductor Z-source matrix converter. Top: Line to line output voltage and     |

| input voltage, bottom: phase output current                                                     |

xvi

| Fig. 4.65 Switched inductor Z-source matrix converter. Top: Line to line output voltage and        |

|----------------------------------------------------------------------------------------------------|

| input voltage, bottom: phase output current                                                        |

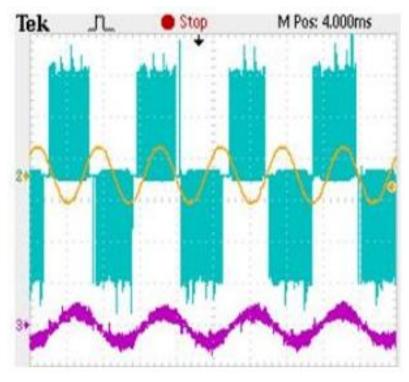

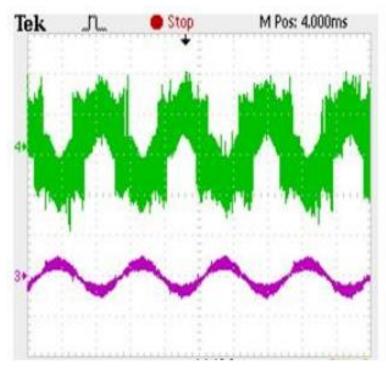

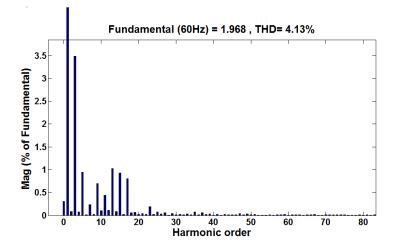

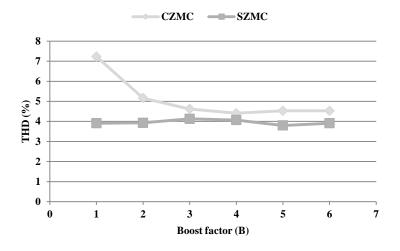

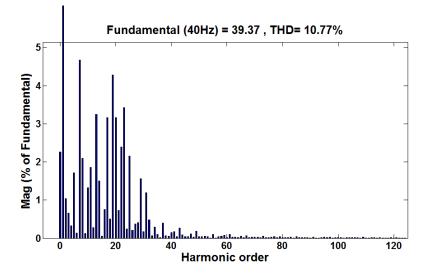

| Fig. 4.66 Harmonic spectrum of the output current of series Z-source matrix converter with $B =$   |

| 3, $m = 0.7$ and $f_{out} = 60$ Hz                                                                 |

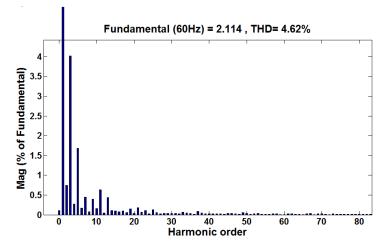

| Fig. 4.67 Harmonic spectrum of the output current of cascaded Z-source matrix converter with $B$   |

| = 3, $m = 0.7$ and $f_{out} = 60$ Hz                                                               |

| Fig. 4.68 THD of the output current of cascaded Z-source and series Z-source matrix converters     |

| vs. the boost factor                                                                               |

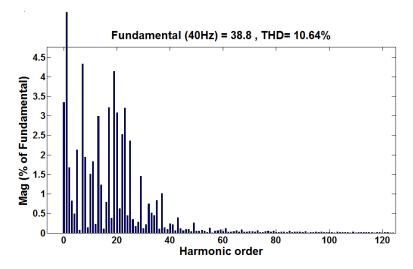

| Fig. 4.69 Harmonic spectrum of the input current of switched inductor Z-source matrix              |

| converter with $B = 3$ , $m = 0.7$ and $f_{in} = 40$ Hz                                            |

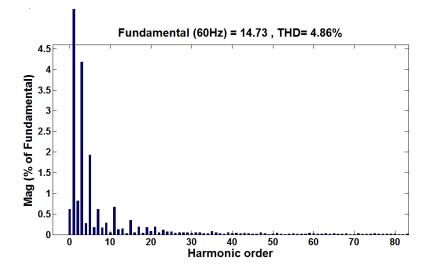

| Fig. 4.70 Harmonic spectrum of the output current of switched inductor Z-source matrix             |

| converter with $B = 3$ , $m = 0.7$ and $f_{in} = 40$ Hz                                            |

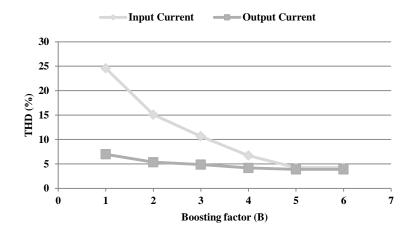

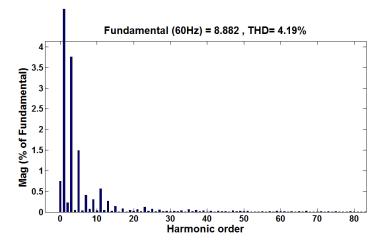

| Fig. 4.71 THD of input and output currents in the switched inductor Z-source matrix converter      |

| with $B = 3$ , $m = 0.7$ and $f_{in} = 40$ Hz                                                      |

| Fig. 4.72 Harmonic spectrum of the input current of quasi Z-source matrix converter with $B = 3$ , |

| $m = 0.7$ and $f_{in} = 40$ Hz                                                                     |

| Fig. 4.73 Harmonic spectrum of the output current of quasi Z-source matrix converter with $B =$    |

| 3, $m = 0.7$ and $f_{out} = 60$ Hz                                                                 |

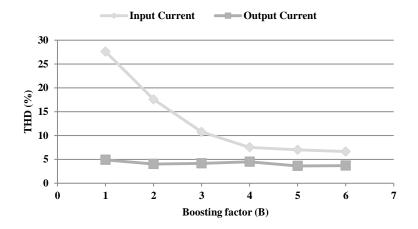

| Fig. 4.74 Total harmonic distortion of the quasi Z-source matrix converter's input and output      |

| currents                                                                                           |

| Chapter 5                                                                                          |

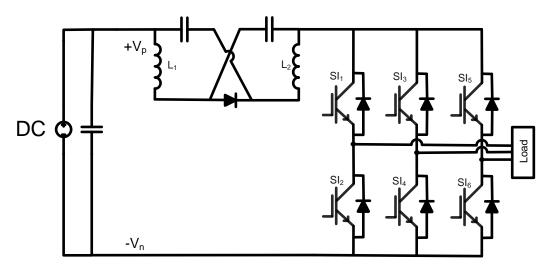

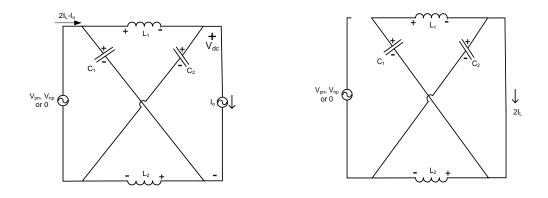

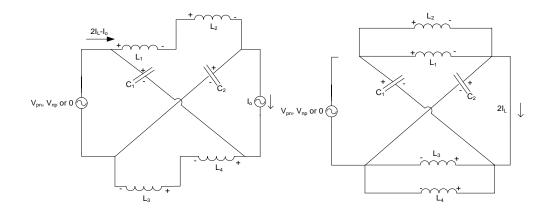

| Fig. 5.1 Three-phase to single-phase super-sparse matrix converter                                 |

| Fig. 5.2 Three-phase to single-phase super-sparse Z-source matrix converter                        |

| Fig. 5.3 Three-phase to single-phase super-sparse switched-inductor Z-source matrix converter.      |

|-----------------------------------------------------------------------------------------------------|

|                                                                                                     |

| Fig. 5.4 Legs of the front-end rectifier. Left: sparse matrix converter, right: ultra-sparse matrix |

| converter                                                                                           |

| Fig. 5.5 Input current vectors                                                                      |

| Fig. 5.6 State sequences within one switching cycle: (a) super-sparse matrix converter, (b) Z-      |

| source and switched-inductor Z-source matrix converters                                             |

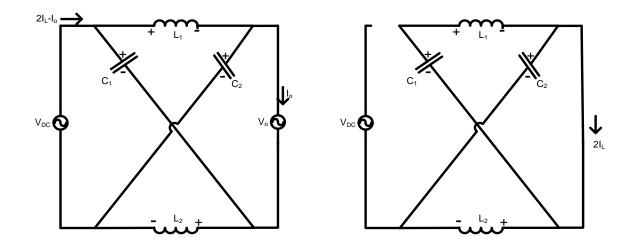

| Fig. 5.7 Equivalent-circuits of the Z-source: left to right: non-shoot-through states, shoot-       |

| through states                                                                                      |

| Fig. 5.8 Equivalent circuits of the switched-inductor Z-source, left to right: non-shoot-through    |

| states, shoot-through states                                                                        |

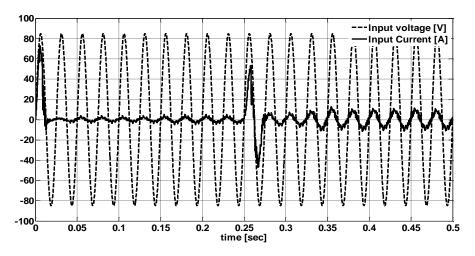

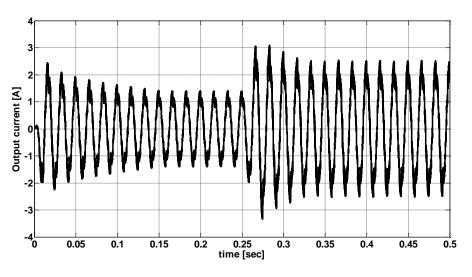

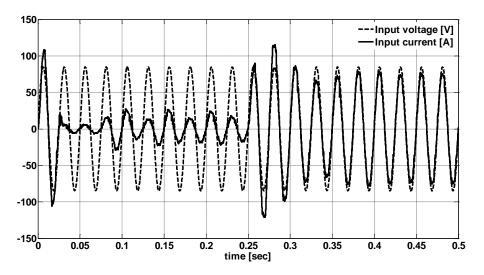

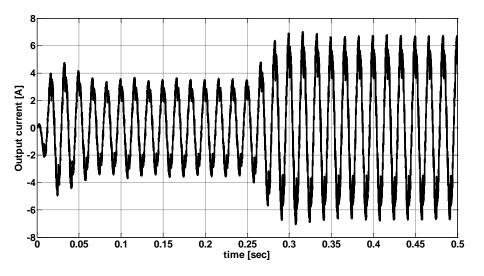

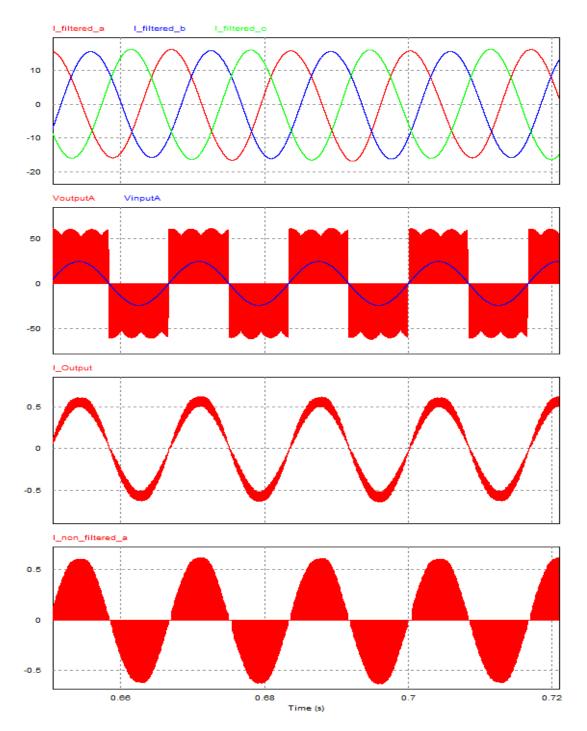

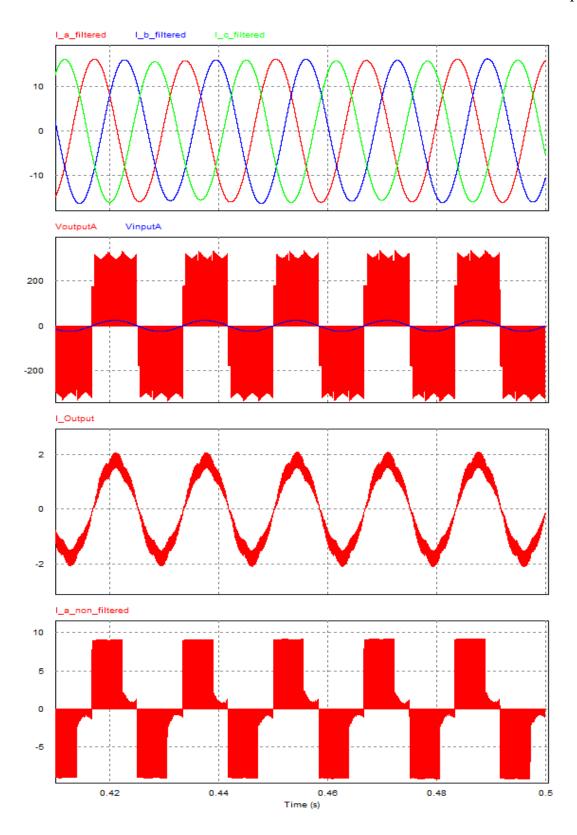

| Fig. 5.9 Super-sparse matrix converter. Top to bottom: filtered input phase currents, output and    |

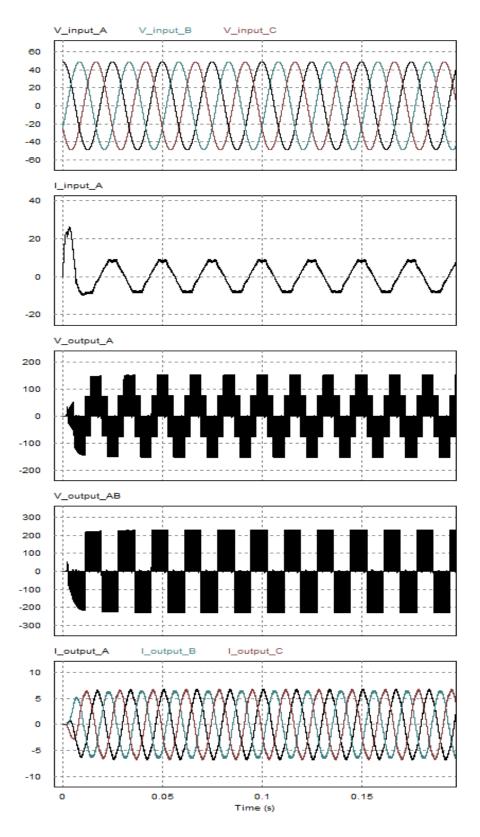

| input voltages, output current, unfiltered input currents                                           |

| Fig. 5.10 Z-source matrix converter. Top to bottom: filtered input phase currents, output and       |

| input voltages, output current, unfiltered input currents                                           |

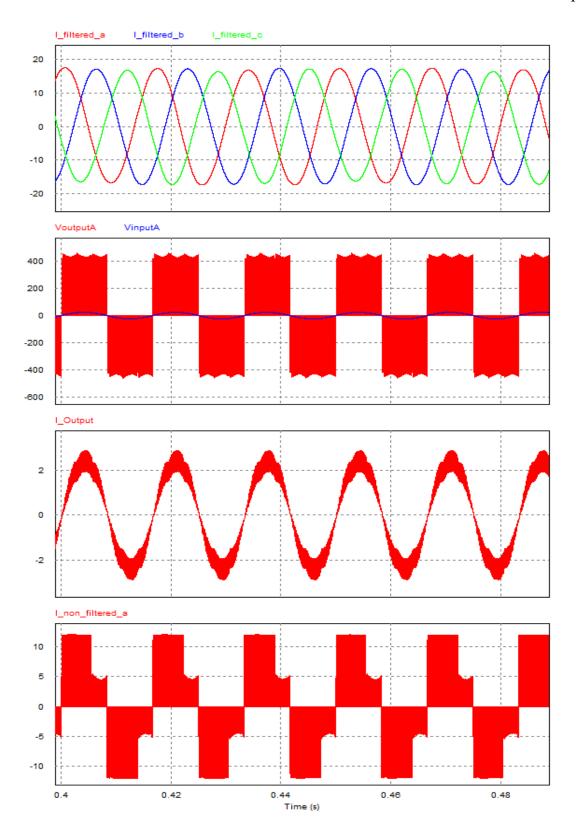

| Fig. 5.11 Switched inductor Z-source matrix converter. Top to bottom: filtered input phase          |

| currents, output and input voltages, output current, unfiltered input currents                      |

| Chapter 6                                                                                           |

| Fig. 6.1 Structure of the implemented boost matrix converter                                        |

| Fig. 6.2 Schematic diagram of a voltage transducer                                                  |

| Fig. 6.3 Schematic diagram of an interface to the ac voltage transducers                            |

| Fig. 6.4 The voltage and current measurement board                                                  |

| Fig. 6.5 Schematic diagram of interface to the dc voltage transducers                               |

| Fig. 6.6 Schematic diagram of a current transducer                                                  |

| Fig. 6.7 S  | chematic diagram of an interface to the ac current transducers | 155 |

|-------------|----------------------------------------------------------------|-----|

| Fig. 6.8 S  | chematic diagram of the IPM interface circuit                  | 158 |

| Fig. 6.9 Ir | nversion stage interface                                       | 160 |

| Fig. 6.10   | Rectification stage interface and converter.                   | 162 |

| Fig. 6.11   | An example up-down mode (courtesy of Texas Instruments)        | 165 |

### Introduction

### 1.1 Background

Penetration of clean energy, mainly the wind and photovoltaic (PV) generated electrical energy, in the power grid is increasing exponentially. Both the wind and PV power plants are connected to the grid through converters, transferring the generated DC power in PV applications and AC power in wind power (WP) applications to the AC grid. The aim of the dissertation is to propose new topologies, modulation techniques, and control of grid converters for WP applications. Throughout the various types of proposed topologies, non-grid cases are explained and then followed by grid applications.

Parameters of the output voltage of most renewable energy sources tend to fluctuate with the varying supply of input power. A wind turbine driving a synchronous generator represents a typical example of the disparity between the voltage of the generator and that of the utility grid, and an appropriate power electronic interface is needed to reconcile that disparity. The required ac-ac power conversion is usually performed indirectly as ac-dc-ac conversion in a back-to-back converter, shown in Fig. 1.1.

Fig. 1.1 Ac-dc-ac conversion in a back-to-back converter.

In recent years, matrix converters have awakened the interest of researchers as an alternative solution. Aside of small LC filters, direct matrix converters do not need the high-capacitance dc link typical for the back-to-back converters, provide a unity input power factor and sinusoidal input and output currents, but their voltage gain is inherently limited to 0.866 with direct ac-ac conversion as shown in Fig. 1.2. Having several bidirectional switches increases the cost of the converter as well as the conduction losses.

Fig. 1.2 Transformerless direct ac-ac conversion.

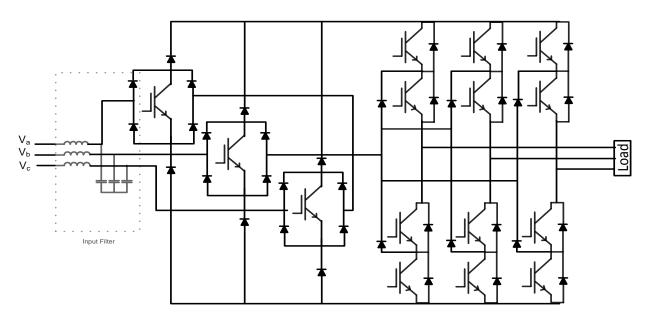

A classic three-phase to three-phase matrix converter is based on nine bidirectional switches. Each switch is composed of two unidirectional switches and two diodes or a single switch and four diodes although certain manufacturers, e.g., Fuji Electric, have developed integrated bidirectional switches for their products [1]. Recently, sparse and ultra-sparse matrix converter topologies have been introduced to reduce the switch count [2].

High reliability and power density are important features of power electronic converters, affecting the total cost of many applications [3]. This issue is particularly relevant in the context of residential wind energy systems, whose popularity has been hampered by real and perceived expenses. A typical wind-energy system consists of a turbine, a gearbox, a three-phase ac generator, a power converter, and an optional step-up transformer connecting the system to the grid. The gearbox/transformer tradeoff is necessary, as slow-motion generators tend to produce low voltages. The gearbox or the transformer increase the cost, weight, and volume of the

system, and reduce its overall reliability. Therefore, a possibly simple matrix converter with voltage-boosting capability would represent a promising solution.

Because of the limited voltage gain and complex control algorithms, matrix converters have not yet been commonly used in industry [4]. To overcome these drawbacks various control algorithms and topologies have been proposed. In [5] application of a direct matrix converter connected to a step up-down transformer is proposed for a wind-turbine system. Alas, the use of transformer increases the system's weight, volume, and cost, and reduces the reliability system. Another solution for increasing the voltage gain to unity and beyond is the indirect matrix topology, where a voltage-boosting network is inserted between the input rectifier and output inverter stages. The recently popular Z-source network, first proposed in [6], is well-suited for that role [7]-[9]. Current modulation techniques for indirect Z-source matrix converters are investigated in [10]. An optimal modulation approach provides high buck-boost flexibility, minimum commutation count, and ease of implementation. In [11], a grid interface for wind turbine generators based on an ultra-sparse matrix converter is described. The system integrates a generator-side three-switch buck-type rectifier and a grid-side Z-source inverter. The Z-source network allows boosting the voltage two to three times. Expansions of the Z-source dc link for buck-boost inverters, called Quasi Z-source network, Series Z-source network and Switchedinductor Z-source, were recently proposed in [12-14].

In practical applications, in order to provide a high boost factor for a low-voltage dc power source, the Z-source converter would have to operate under extreme conditions of long shoot-through zero states. The constraints of a low modulation index and a long shoot-through state cause a conflict between the output power quality and system boost ability. Therefore, the practical boost factor of Z-source impedance network is restricted. The Quasi Z-source network,

Series Z-source network and Switched-inductor Z-source networks aim at a solution of that problem.

### **1.2** Dissertation Objectives

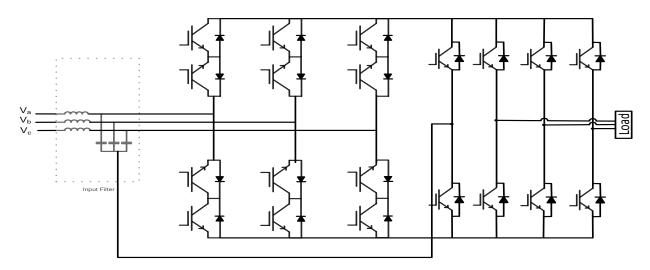

This dissertation proposes a number of converters, all based on the ultra-sparse matrix topology characterized by the minimum number of semiconductor switches. Z-source network, quasi Z-source network, series Z-source network and switched-inductor Z-source network were originally developed for boosting the output voltage of power electronic inverters. These ideas are extended here on a three-phase indirect matrix converters and three-phase to single-phase indirect matrix converters. For three-phase matrix converters, these circuits are placed between the three-switch input rectifier stage and the output six-switch inverter stage. A brief shootthrough state produces the voltage boost. An optimal pulse width modulation technique was developed to achieve high boosting flexibility and minimum switching losses in the converter. Similarly, for three-phase to single-phase matrix converters, these networks are placed between the three-switch input rectifier stage and the output four-switch inverter stage. To control them, a new modulation technique has been developed. As an example application, the proposed converters constitute a viable alternative to the existing solutions in residential wind-energy systems, where a low-voltage variable-speed generator feeds power to the higher-voltage fixedfrequency grid.

### **1.3** Content of the Dissertation

This dissertation contains seven chapters, which address different aspects of the project objectives:

*Chapter 1* is the introduction to the dissertation. It describes research motivation and the outlines of the project.

*Chapter 2* gives a technology overview of the matrix converter topologies and their control methods. It discusses in detail the concept of the direct matrix converter, indirect matrix converter, sparse matrix converter, and boost matrix converter topologies. A combined space vectors based indirect modulation technique is widely discussed.

*Chapter 3* gives a technology overview of the boost type inverter networks that include Z-source inverter, series Z-source inverter, quasi Z-source inverter, and switched inductor Z-source inverter. The circuit analysis and operation principle are discussed with analytical derivations.

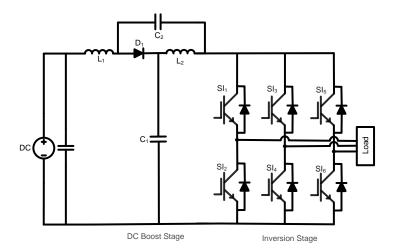

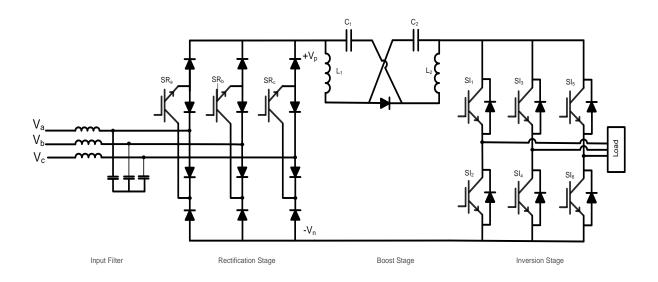

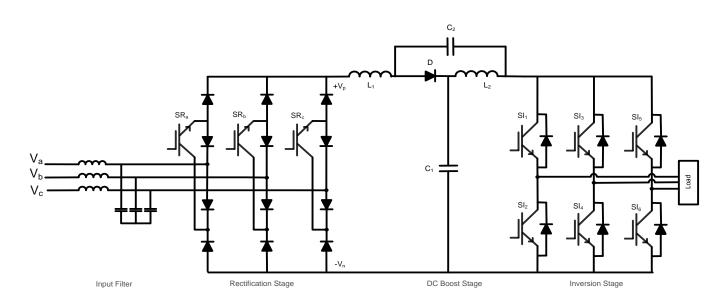

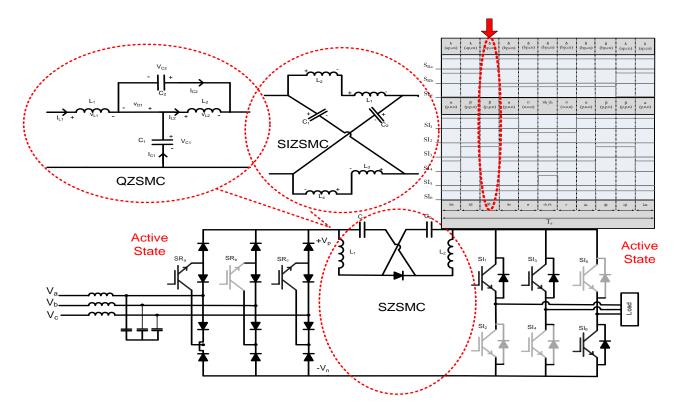

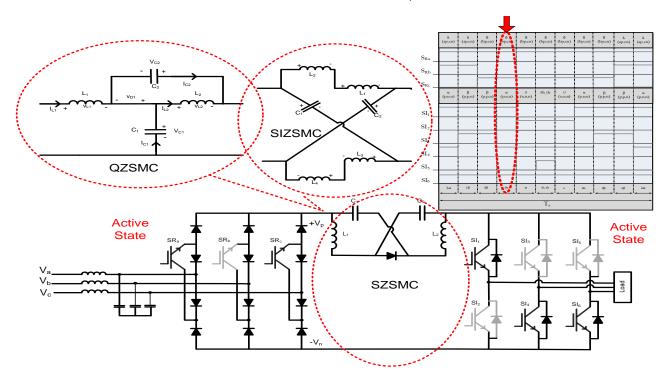

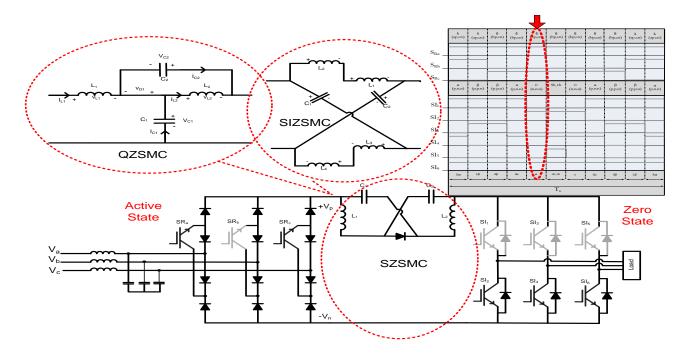

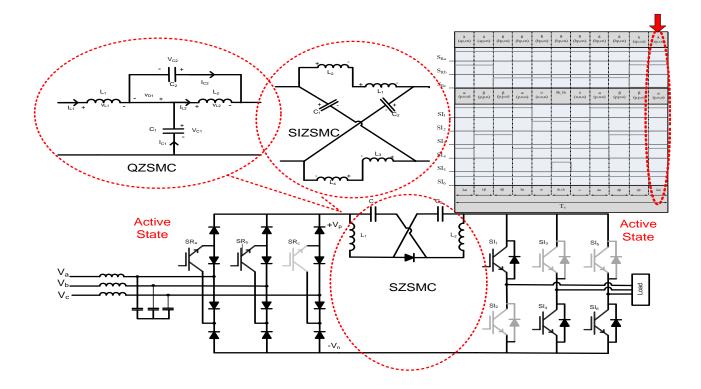

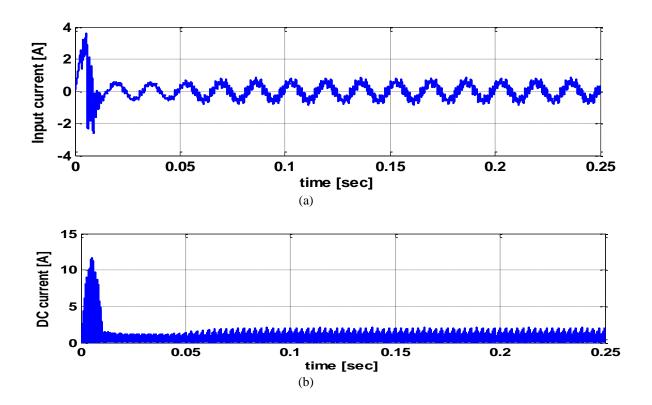

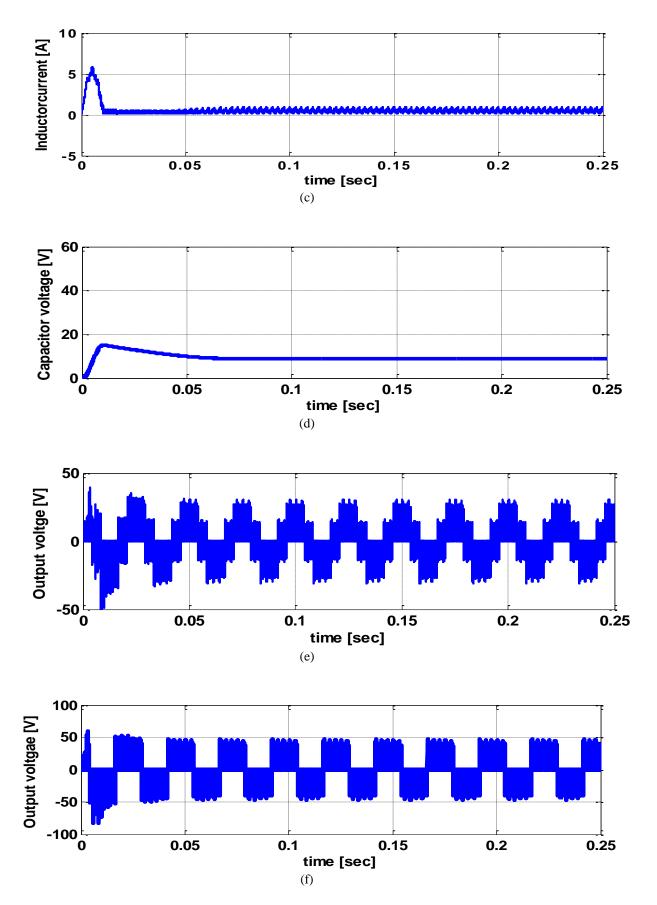

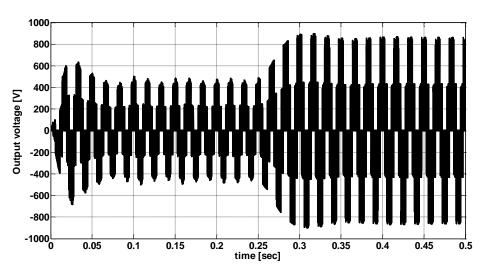

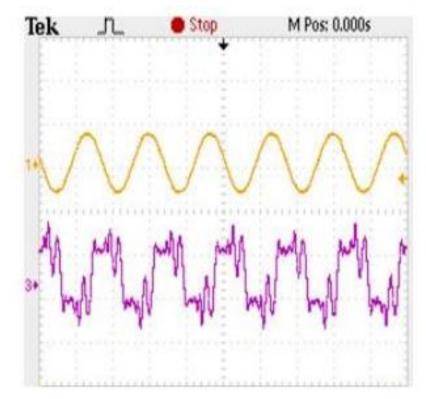

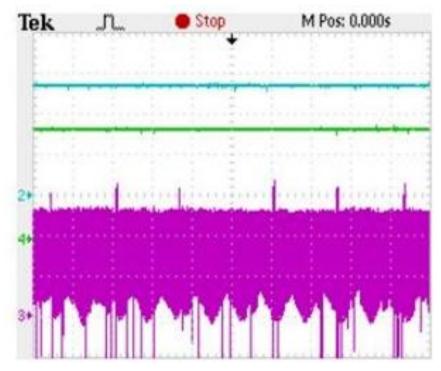

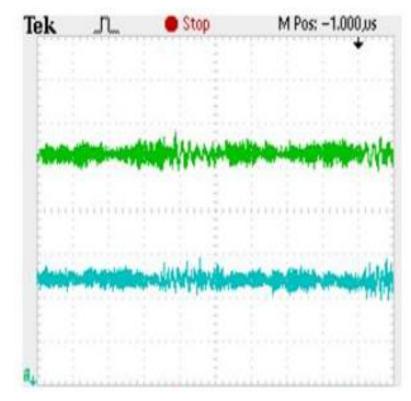

*Chapter 4* proposes three different types of three-phase boost matrix converters based on ultra-sparse matrix converters and series Z-source, quasi Z-source, and switched inductor Z-source networks. A new control technique is provided to maximize the efficiency of these converters. Experiment and simulation results are shown to confirm the ability of the converters to overcome the voltage gain disadvantage of the classic matrix converters.

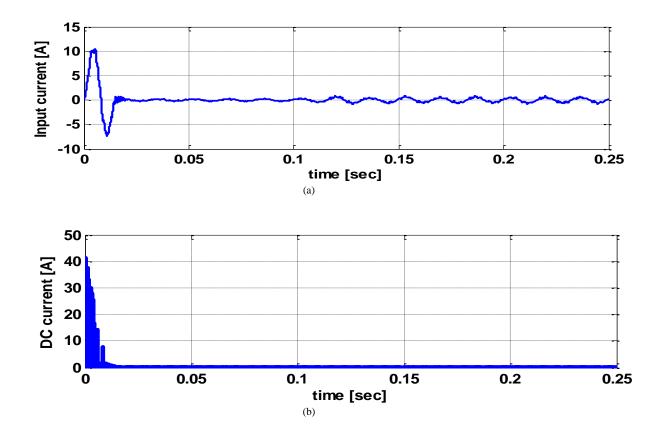

*Chapter 5* extends above considerations on single-phase boost matrix converters. Simulation results are provided to illustrate capabilities of those converters.

*Chapter 6* presents the hardware implementation and experimental setups for the boost matrix converters. Structures of the prototype converters are described and design of each circuit is explained in detail. Control firmware based on Texas Instruments microprocessor is discussed.

*Chapter 7* contains the conclusion of the dissertation. It summarizes the work done and the main findings of the PhD research. Possibilities for improving the investigated topologies are outlined for future work.

## **Topologies and Modulation Techniques of Matrix Converters**

### 2.1 Matrix Converter Topologies

Matrix converter (MC) topologies are based on semiconductor, usually bidirectional, power switches. In most cases, an MC consists of nine bi-directional switches. The name of the converter comes from the arrangement of these switches in a matrix pattern. Gate signals are modulated to achieve sinusoidal input and output currents.

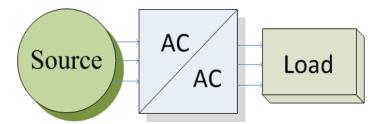

Matrix converters first appeared in a book by Gyugui and Pelly [15] and in a journal publication by Daniels and Slatery in 1976 [16]. The concept was presented as AC-AC direct power conversion [17]. Since then various types of MC topologies have been studied. Classification of MCs is shown in Fig. 2.1.

Fig. 2.1 Classification of matrix converters [18].

As no energy is present in the MC, the output voltages have to be generated from the input voltages. Output voltages need to fit in the envelope curve. The minimum envelope curve

is the 0.866 times the peak input balanced line voltages. Thus the minimum envelope curve is 0.866 times the peak input balanced line voltages. This is a gain limitation of most matrix converters.

Another aspect of the output voltage is the harmonic content. Compared to two level voltage source inverters, matrix converters can be considered as three level converters since the input three-phase voltages appears at the output with varying levels. This reduces the harmonic loss [18]. The input current of the MC is directly related to the switching control of the converter and MC can control the phase angle of the input currents. Besides the fundamental component, the input current has a high harmonic content around the switching frequency. A filter is therefore used to average the chopped current [19].

One of the critical issues when investigating a converter topology is efficiency. An analysis of the efficiency is carried out in Table 2.1 that shows the semiconductor loss in the matrix converter compared back-to-back converters. The analysis demonstrates that the MC has lower switching loss and larger conduction loses than the back-to-back converter. Back-to-back converters are hard commutated, but with proper selection of bi-directional switches and commutation strategy MCs can be semi-soft commutated [20] or semi-natural commutated [21].

It is necessary to place filter capacitors at the input of the MCs to draw sinusoidal input currents. To avoid a short circuit of the impressed input voltages, a simultaneous connection of two input phases to the same output phase must be avoided. On the other hand, due to the load currents, one output phase must, be connected to one input phase. It is also permissible to connect all outputs to the same input.

|                                | Back-to-back<br>Converter | Conventional Matrix<br>Converter |

|--------------------------------|---------------------------|----------------------------------|

| Commutation                    | Hard Switch               | Semi-Soft Switch                 |

| Switch Voltage                 | 1x                        | (2/π)x                           |

| Switch Current                 | 1x                        | (2/√3)x                          |

| # Switching                    | 4x                        | 8x                               |

| Switch Losses                  | 4x                        | 2.94x                            |

| Semiconductors in current path | 4x                        | 4x                               |

| Conduction Losses              | 4x                        | 4.61x                            |

Table 2.1 Comparison of the back-to-back converters and conventional MCs [36].

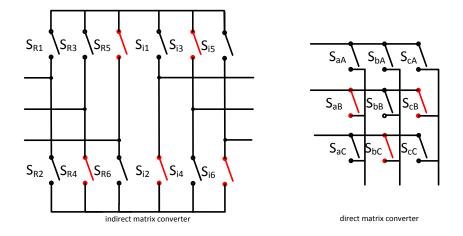

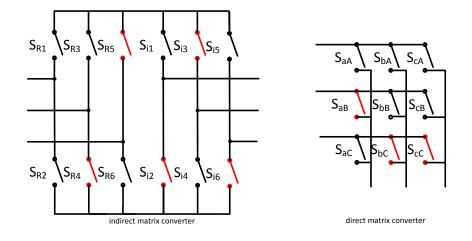

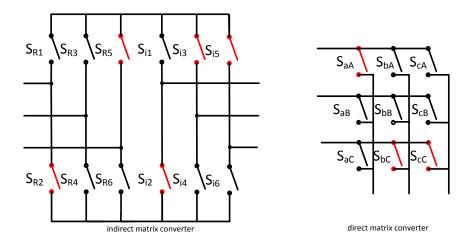

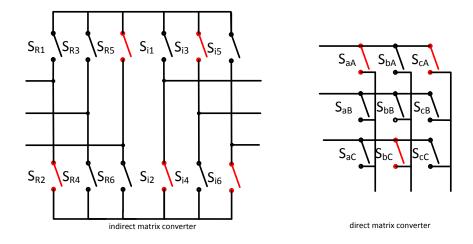

#### 2.1.1 Direct Matrix Converters

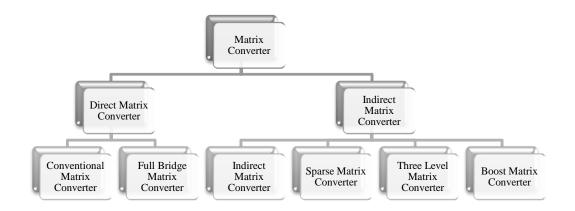

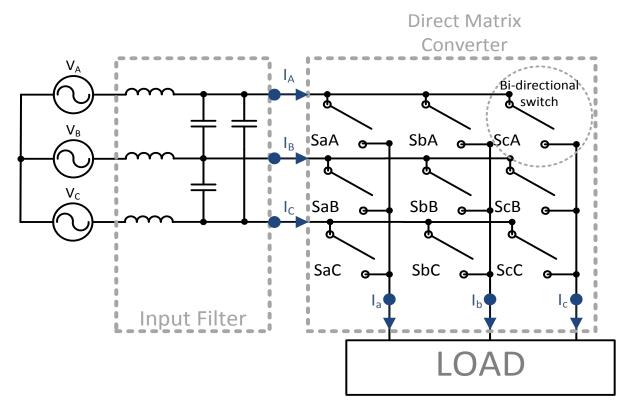

Each of the input phases of the conventional, direct MC, can be directly connected with each output phase. It can therefore be represented as a switching matrix. A four-quadrant switch can be implemented by a regular power switch with anti-parallel freewheeling diodes as the input stage of the MC as shown on Fig. 2.2. A functional representation of the direct MC is depicted in Fig. 2.3. With respect to the conduction losses, an even better solution is to use an anti-parallel connection of RB-IGBTs [22]-[24].

Full bridge matrix converter (for open motor winding) was presented in [25]-[27] which is suitable for variable speed AC drives, because it generates no sub-harmonic components in the output voltage and hence the output frequency is limited.

Fig. 2.2 Direct matrix converter.

As there is direct connection with voltage sources, the input phase shall never be shorted. If the switches cause a short circuit between the input voltage sources, a large current flows through the switches and damages the phase in which the short circuit occurs. Also, due to the inductive nature of typical loads, the output terminals must not be open-circuited. If any output terminal is open-circuited, the voltage across the inductor (and consequently across the switches) is infinite and switches will be damaged due to the over-voltage. Switches for each output phase must be controlled based on the following expression:

$$S_{jA} + S_{jB} + S_{jC} = 1, \quad j \in \{a, b, c\}$$

(2.1)

where

$$S_{jk} \begin{cases} 1 \ closed \\ 0 \ open \end{cases}, j \in \{a, b, c\}, k \in \{A, B, C\}$$

$$(2.2)$$

Fig. 2.3 Connection diagram of the direct matrix converter.

Power switches in the converter are divided into two groups. There are 27 allowable converter states including active states and zero states. Instantaneous values of the output voltages and the input currents produced by each switching combination can be determined using

the instantaneous transfer matrices, where  $T_{LL}$  is the instantaneous input phase to output line-toline transfer matrix and  $T_{ph}$  is the instantaneous input phase to output phase matrix:

$$T_{LL} = \begin{bmatrix} S_{aA} - S_{bA} & S_{aB} - S_{bB} & S_{aC} - S_{bC} \\ S_{bA} - S_{cA} & S_{bB} - S_{cB} & S_{bC} - S_{cC} \\ S_{cA} - S_{aA} & S_{cB} - S_{aB} & S_{cC} - S_{aC} \end{bmatrix}, \ T_{ph} = \begin{bmatrix} S_{aA} & S_{aB} & S_{aC} \\ S_{bA} & S_{bB} & S_{bC} \\ S_{cA} & S_{cB} & S_{cC} \end{bmatrix}$$

(2.3)

From the line to line transfer matrix the instantaneous output voltages,  $V_{LL}$  and input phase currents,  $i_{ph}$  can be determined:

$$V_{LL} = \begin{bmatrix} V_{ab} \\ V_{bc} \\ V_{ca} \end{bmatrix} = T_{LL} \begin{bmatrix} V_A \\ V_B \\ V_C \end{bmatrix} = T_{LL} V_i , \quad i_{ph} = \begin{bmatrix} i_A \\ i_B \\ i_C \end{bmatrix} = T_{LL}^T \begin{bmatrix} i_{ab} \\ i_{bc} \\ i_{ca} \end{bmatrix}$$

(2.4)

To generate balanced and sinusoidal input and output waveforms with variable input displacement angle, matrix converters are controlled using modulation techniques. Over each switching period, the modulation strategy controls duty cycles of the switches so that the input voltages and output currents are applied to the output and input terminals, respectively, that generates reference voltages and currents.

$$0 \le m_{jk} = \frac{t_{jk}}{T_S} \le 1, \ j \in \{a, b, c\}, \ k \in \{A, B, C\}$$

(2.5)

where  $m_{jk}$  and  $t_{jk}$  denote the duty cycle and on-time of switch  $S_{jk}$ , respectively, and  $T_S$  is the switching period. Then,

$$\begin{bmatrix} v(t)_{o,a} \\ v(t)_{o,b} \\ v(t)_{o,c} \end{bmatrix} = \begin{bmatrix} m(t)_{aA} & m(t)_{aB} & m(t)_{aC} \\ m(t)_{bA} & m(t)_{bB} & m(t)_{bC} \\ m(t)_{cA} & m(t)_{cB} & m(t)_{cC} \end{bmatrix} \begin{bmatrix} v(t)_{in,A} \\ v(t)_{in,B} \\ v(t)_{in,C} \end{bmatrix}$$

$$\begin{bmatrix} i(t)_{in,A} \\ i(t)_{in,B} \\ i(t)_{in,C} \end{bmatrix} = \begin{bmatrix} m(t)_{aA} & m(t)_{aB} & m(t)_{aC} \\ m(t)_{bA} & m(t)_{bB} & m(t)_{bC} \\ m(t)_{cA} & m(t)_{cB} & m(t)_{cC} \end{bmatrix} \cdot \begin{bmatrix} i(t)_{o,a} \\ i(t)_{o,b} \\ i(t)_{o,c} \end{bmatrix}$$

(2.6)

$$\begin{bmatrix} i(t)_{in,A} \\ i(t)_{in,C} \\ m(t)_{cA} & m(t)_{cB} & m(t)_{cC} \end{bmatrix} \cdot \begin{bmatrix} i(t)_{o,a} \\ i(t)_{o,b} \\ i(t)_{o,c} \end{bmatrix}$$

(2.7)

For balanced input lines,

$$\begin{bmatrix} m(t)_{aA} & m(t)_{aB} & m(t)_{aC} \\ m(t)_{bA} & m(t)_{bB} & m(t)_{bC} \\ m(t)_{cA} & m(t)_{cB} & m(t)_{cC} \end{bmatrix} = \begin{bmatrix} 1 \\ 1 \\ 1 \end{bmatrix}$$

(2.8)

while  $\frac{V_0}{V_{in}} \le \frac{\sqrt{3}}{2}$ ;

$$\begin{bmatrix} v(t)_{o,a} \\ v(t)_{o,b} \\ v(t)_{o,c} \end{bmatrix} = \begin{bmatrix} V_o \cos(w_o t + \theta_o) \\ V_o \cos\left(w_o t + \theta_o - \frac{2\pi}{3}\right) \\ V_o \cos\left(w_o t + \theta_o + \frac{2\pi}{3}\right) \end{bmatrix}$$

(2.9)

$$\begin{bmatrix} v(t)_{in,A} \\ v(t)_{in,B} \\ v(t)_{in,C} \end{bmatrix} = \begin{bmatrix} V_{in} \cos(w_{in}t) \\ V_{in} \cos\left(w_{in}t - \frac{2\pi}{3}\right) \\ V_{in} \cos\left(w_{in}t + \frac{2\pi}{3}\right) \end{bmatrix}$$

(2.10)

$$\begin{bmatrix} i(t)_{in,A} \\ i(t)_{in,B} \\ i(t)_{in,C} \end{bmatrix} = \begin{bmatrix} I_{in} \cos(w_{in}t + \varphi_{in}) \\ I_{in} \cos\left(w_{in}t + \varphi_{in} - \frac{2\pi}{3}\right) \\ I_{in} \cos\left(w_{in}t + \varphi_{in} + \frac{2\pi}{3}\right) \end{bmatrix}$$

(2.11)

$$\begin{bmatrix} i(t)_{o,a} \\ i(t)_{o,b} \\ i(t)_{o,c} \end{bmatrix} = \begin{bmatrix} I_o \cos(w_o t + \theta_o + \varphi_o) \\ I_o \cos\left(w_o t + \theta_o + \varphi_o - \frac{2\pi}{3}\right) \\ I_o \cos\left(w_o t + \theta_o + \varphi_o + \frac{2\pi}{3}\right) \end{bmatrix}$$

(2.12)

where,  $V_o$  is the output voltage,  $V_{in}$  is the input voltage,  $\theta_o$  is the output reference angle,  $w_{in}$  is the input angular frequency,  $w_o$  is the output angular frequency,  $\varphi_{in}$  is the input displacement angle and  $\varphi_o$  is the output displacement angle. To obtain the maximum voltage transfer ratio, third harmonic components of input and output signals are injected into the output voltages and the output voltage becomes as in Eq. (2.13) and the extended voltage transfer ratio is in Eq. (2.14):

$$\begin{bmatrix} v(t)_{o,a} \\ v(t)_{o,b} \\ v(t)_{o,c} \end{bmatrix} = V_o \begin{bmatrix} \cos(w_o t + \theta_o) \\ \cos\left(w_o t + \theta_o - \frac{2\pi}{3}\right) \\ \cos\left(w_o t + \theta_o + \frac{2\pi}{3}\right) \end{bmatrix} + \frac{v_{in}}{4} \begin{bmatrix} \cos(3w_{in}t) \\ \cos(3w_{in}t) \\ \cos(3w_{in}t) \end{bmatrix} - \frac{v_o}{6} \begin{bmatrix} \cos(3w_o t + 3\theta_o) \\ \cos(3w_o t + 3\theta_o) \\ \cos(3w_o t + 3\theta_o) \end{bmatrix}$$

(2.13)

$$\begin{bmatrix} v(t)_{o,a} \\ v(t)_{o,b} \\ v(t)_{o,c} \end{bmatrix} = V_o \begin{bmatrix} \cos(w_o t + \theta_o) \\ \cos\left(w_o t + \theta_o - \frac{2\pi}{3}\right) \\ \cos\left(w_o t + \theta_o + \frac{2\pi}{3}\right) \end{bmatrix} + \frac{V_o}{2\sqrt{3}} \begin{bmatrix} \cos(3w_{in}t) \\ \cos(3w_{in}t) \\ \cos(3w_{in}t) \end{bmatrix} - \frac{V_o}{6} \begin{bmatrix} \cos(3w_o t + 3\theta_o) \\ \cos(3w_o t + 3\theta_o) \\ \cos(3w_o t + 3\theta_o) \end{bmatrix}$$

(2.14)

The solution of the matrix of the low-frequency modulation function is

$$[m(t)] = \frac{1}{3}[I] + [X] + [Y] + [Z]$$

(2.15)

where,

$$[I] = \begin{bmatrix} 1 & 1 & 1 \\ 1 & 1 & 1 \\ 1 & 1 & 1 \end{bmatrix}$$

(2.16)

$$[X] = \frac{\beta_1}{3} \begin{bmatrix} m_+(1) & m_+(2) & m_+(3) \\ m_+(2) & m_+(3) & m_+(1) \\ m_+(3) & m_+(1) & m_+(2) \end{bmatrix} + \frac{\beta_2}{3} \begin{bmatrix} m_-(1) & m_-(2) & m_-(3) \\ m_-(2) & m_-(3) & m_-(1) \\ m_-(3) & m_-(1) & m_-(2) \end{bmatrix}$$

(2.17)

$$[Y] = \frac{\gamma_1}{3} \begin{bmatrix} n_+(1) & n_+(2) & n_+(3) \\ n_+(2) & n_+(3) & n_+(1) \\ n_+(3) & n_+(1) & n_+(2) \end{bmatrix} + \frac{\gamma_2}{3} \begin{bmatrix} n_-(1) & n_-(2) & n_-(3) \\ n_-(2) & n_-(3) & n_-(1) \\ n_-(3) & n_-(1) & n_-(2) \end{bmatrix}$$

(2.18)

$$[\mathbf{Z}] = \frac{\delta_1}{3} \begin{bmatrix} q_+(1) & q_+(2) & q_+(3) \\ q_+(2) & q_+(3) & q_+(1) \\ q_+(3) & q_+(1) & q_+(2) \end{bmatrix} + \frac{\delta_2}{3} \begin{bmatrix} q_-(1) & q_-(2) & q_-(3) \\ q_-(2) & q_-(3) & q_-(1) \\ q_-(3) & q_-(1) & q_-(2) \end{bmatrix}$$

(2.19)

where,

$$m_{+}(i) = \cos[(w_{o} + w_{in})t + \theta_{o} - (i - 1)\frac{2\pi}{3}]$$

(2.20)

$$m_{-}(i) = \cos[(w_o - w_{in})t + \theta_o - (i - 1)\frac{2\pi}{3}]$$

(2.21)

$$\beta_1 = \frac{V_o}{V_{in}} \left[ 1 - \frac{\tan(\varphi_{in})}{\tan(\varphi_{in})} \right]$$

(2.22)

$$\beta_2 = \frac{V_o}{V_{in}} \left[ 1 + \frac{\tan(\varphi_{in})}{\tan(\varphi_{in})} \right]$$

(2.23)

$$n_{+}(i) = \cos[4w_{in}t - (i-1)\frac{2\pi}{3}]$$

(2.24)

$$n_{-}(i) = \cos[2w_{in}t - (i-1)\frac{2\pi}{3}]$$

(2.25)

$$\gamma_1 + \gamma_2 = \frac{1}{\sqrt{3}} \frac{V_0}{V_{in}}$$

(2.26)

$$q_{+}(i) = \cos[(3w_{o} + w_{in})t + 3\theta_{o} - (i-1)\frac{2\pi}{3}]$$

(2.27)

$$q_{-}(i) = \cos[(3w_o - w_{in})t + 3\theta_o - (i-1)\frac{2\pi}{3}]$$

(2.28)

$$\delta_1 + \delta_2 = \frac{1}{3} \frac{V_o}{V_{in}} \tag{2.29}$$

The coefficients  $\gamma$  and  $\delta$  not violating the "0.866" maximum voltage transfer ratio are

$$\gamma_1 = \frac{-1}{6\sqrt{3}} \frac{V_o}{V_{in}}, \quad \gamma_2 = \frac{7}{6\sqrt{3}} \frac{V_o}{V_{in}}, \quad \delta_1 = \delta_2 = \frac{-1}{6} \frac{V_o}{V_{in}}$$

(2.30)

### 2.1.2 Indirect Matrix Converters

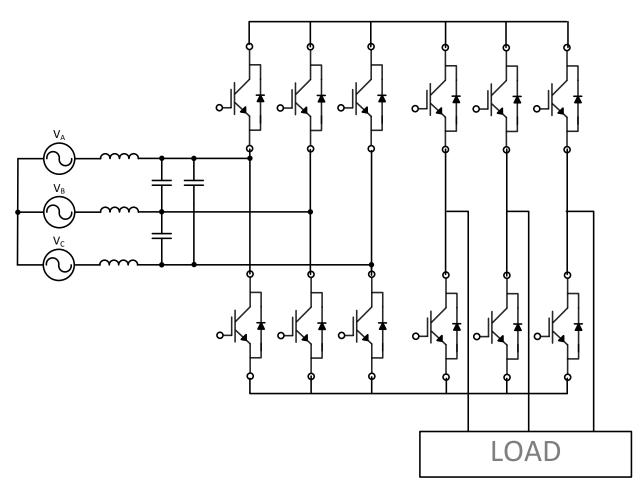

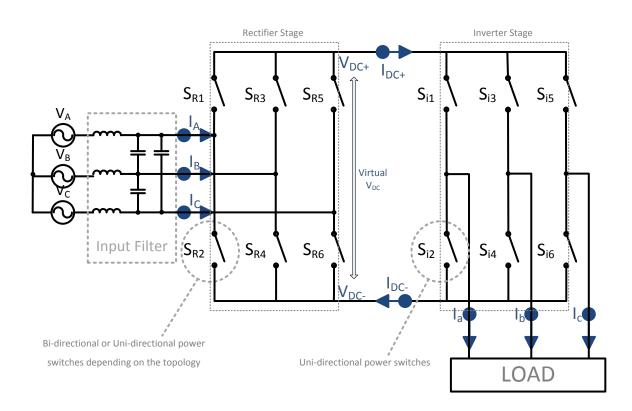

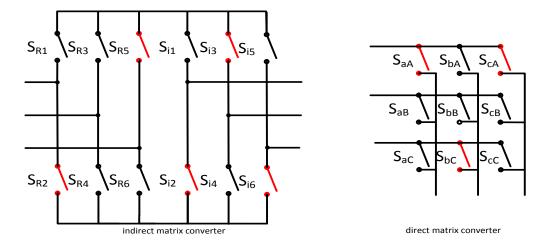

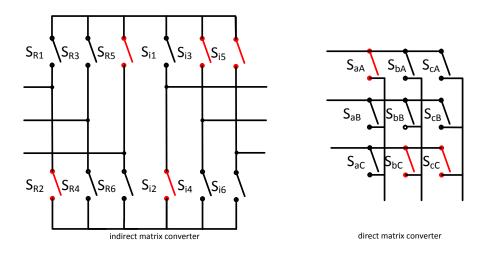

An alternative MC exists as the indirect matrix converter (IMC). The IMC has two separate stages, the front end and the back end, but without any energy storage in the intermediate link. The analysis of MC circuits is based on the basic functionality and modulation of the ac–dc converter with impressed output current and the dc–ac converter with impressed input voltage. The IMC is based on the current source rectifier and voltage source inverter topologies [18].

Fig. 2.4 Indirect matrix converter ( $\pi/6$  displacement angle).

In order to derive a MC topology from the ac–ac converter with a dc-link capacitor, Fig.2.4 is considered first as the indirect ac–ac converter with an intermediate link where the energy-storage dc-link capacitor is omitted. Such a converter system was suggested in [28] and investigated in more detail in [29]–[31]. The input filter capacitors are required to provide impressed voltages at the input due to the impressed load currents at the output. The input stage of the converter system represents a synchronous three-phase rectifier. Its conductive state is directly defined by the mains voltage, and it cannot be influenced through the control. The load line current segments in the link, which are generated by the PWM output stage, are supplied by the input stage through the diodes with the highest instantaneous mains line-to-line voltage across them. This type of matrix converters allows only  $\pi/_6$  degrees of displacement angle [18].

Fig. 2.5 Indirect matrix converter (full range displacement angle).

The further presented indirect matrix converters provide a full range of the displacement angle, shown in Fig.2.5. It is essential to place a power switch in series with each diode, to maintain the front end conductivity. However, when this series switch is blocking, a forward voltage can occur, which must not appear across the anti-parallel switches and which is mainly desirable for the reverse power flow. The input stage now consists of two anti-parallel connected

Fig. 2.6 Circuit diagram of the indirect matrix converter.

As in direct matrix converters, short circuit of two main phases would result from simultaneously turning on two power switches of the upper or lower bridge legs and must therefore be avoided. The fundamental of IMC is based on decoupling the control of the rectifier and inverter stages. The instantaneous input phase to output phase matrix,  $T_{ph}$ , from Eq. 2.3 can be divided into rectifier and inverter transfer functions:

$$T_{ph} = I * R \tag{2.31}$$

$$\begin{bmatrix} S_{aA} & S_{aB} & S_{aC} \\ S_{bA} & S_{bB} & S_{bC} \\ S_{cA} & S_{cB} & S_{cC} \end{bmatrix} = \begin{bmatrix} S_{i1} & S_{i2} \\ S_{i3} & S_{i4} \\ S_{i5} & S_{i6} \end{bmatrix} * \begin{bmatrix} S_{R1} & S_{R3} & S_{R5} \\ S_{R2} & S_{R4} & S_{R6} \end{bmatrix}$$

(2.32)

where the matrix I is the inverter transfer function and the matrix R is the rectifier transfer function. The resultant transfer function allows combining current source PWM rectifier with voltage source PWM inverter without any energy storage components between the positive and negative rails.

By combining Eq. (2.4) and Eq. (2.32), we obtain

$$\begin{bmatrix} V_A \\ V_B \\ V_C \end{bmatrix} = \begin{bmatrix} S_{i1} & S_{i2} \\ S_{i3} & S_{i4} \\ S_{i5} & S_{i6} \end{bmatrix} * \begin{bmatrix} S_{R1} & S_{R3} & S_{R5} \\ S_{R2} & S_{R4} & S_{R6} \end{bmatrix} * \begin{bmatrix} V_a \\ V_b \\ V_c \end{bmatrix}$$

(2.33)

$$\begin{bmatrix} V_A \\ V_B \\ V_C \end{bmatrix} = \begin{bmatrix} (S_{i1} * S_{R1} + S_{i2} * S_{R2}) & (S_{i1} * S_{R3} + S_{i2} * S_{R4}) & (S_{i1} * S_{R5} + S_{i2} * S_{R6}) \\ (S_{i3} * S_{R1} + S_{i4} * S_{R2}) & (S_{i3} * S_{R3} + S_{i4} * S_{R4}) & (S_{i3} * S_{R5} + S_{i4} * S_{R6}) \\ (S_{i5} * S_{R1} + S_{i6} * S_{R2}) & (S_{i5} * S_{R3} + S_{i6} * S_{R4}) & (S_{i5} * S_{R5} + S_{i6} * S_{R6}) \end{bmatrix} * \begin{bmatrix} V_a \\ V_b \\ V_c \end{bmatrix}$$

(2.34)

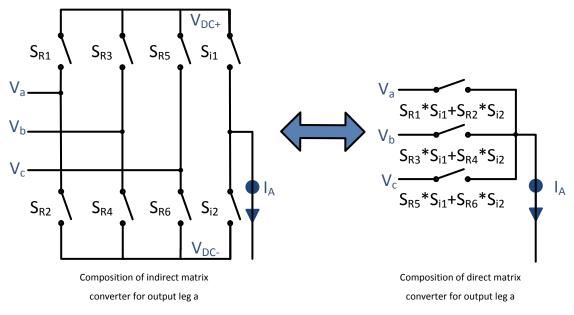

Eq. (2.34) shows that the output phases represent the product and sum of the input phases through inverter switches and rectifier switches. If the equivalent circuit is seen from the inverter's output phase *a*, two switches  $S_{i1}$  and  $S_{i2}$  of phase *a* half bridge are directly connected to input phases *a*, *b* and *c* through six rectifier switches  $S_{R[1,6]}$ . Fig.2.7 shows the transformation of an indirect matrix converter into the direct matrix converter by realizing Eq. (2.34).

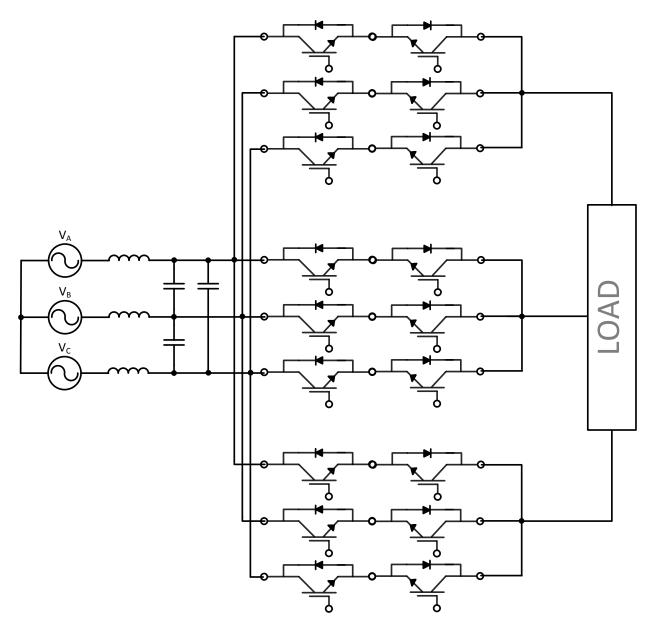

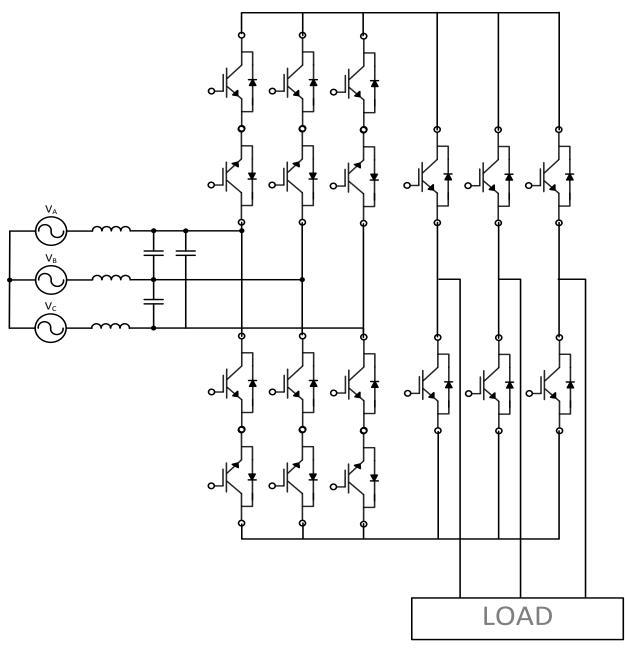

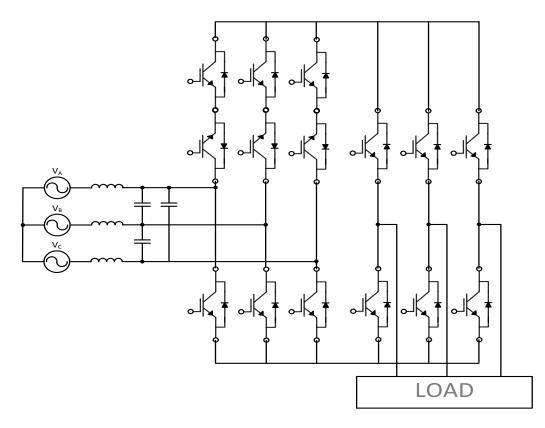

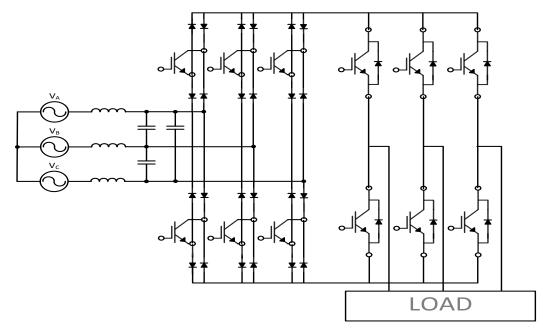

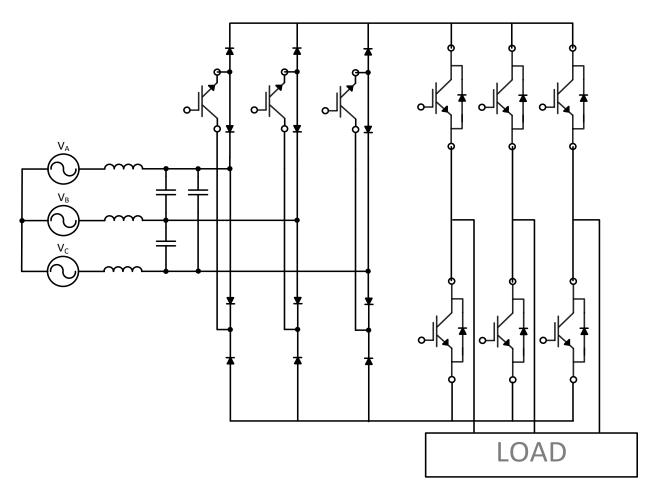

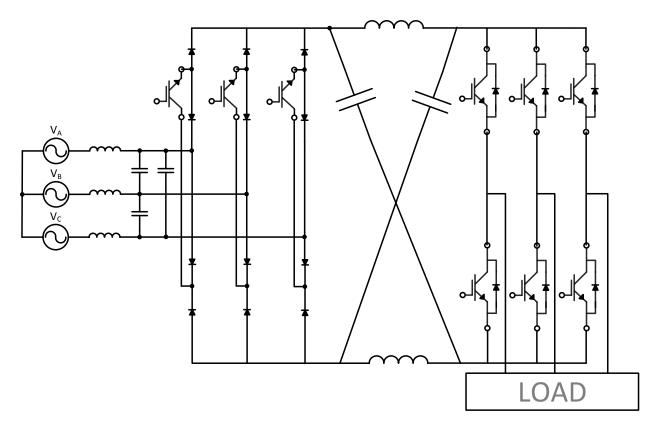

In [32] sparse matrix-equivalent three-phase ac-dc-ac converter topologies are developed based on the structure of an IMC. The converter topologies exhibit a reduced number of power transistors compared to the CMC or IMC and are therefore designated as (a) sparse matrix converter (SMC), shown in Fig.2.8, (b) very sparse matrix converter (VSMC), shown in Fig.2.9, and (c) ultra sparse matrix converter (USMC), shown in Fig.2.10. SMC employs 15 IGBTs, compared to 18 IGBTs of the IMC, and therefore the converter topology is called a sparse converter. The functional equality of the CMC/IMC and SMC is proven in [33], where the CMC

and SMC line-to-line output voltages and input phase currents resulting for the different switching state combinations are composed.

Fig. 2.7 Indirect matrix converter to direct matrix converter transformation.

If simple functionality of a unidirectional buck-type PWM rectifier system, as described in [34] and [35], is desired, then SMC can be reduced by omitting the power switches in each bridge leg. This causes blocking the reverse flow of the dc-link current and restricts the circuit operation to a unidirectional power flow. Controllability of the phase displacement of input voltage and input current fundamental is also limited, while the phase displacement of load current and load voltage fundamental is not allowed to exceed  $\pi/_6$ . Down to the lowest number of power switches (nine IGBTs), this circuit topology is called the USMC. Converters that are presented in Chapters 4 and 5 are based on the USMC type converters.

Since the USMC has a unidirectional power flow, the load must not be allowed to feed energy back into the dc-link since there are no energy storage capacitors, and excessive dc-link voltages would be generated. Therefore, an addition of a clamp circuit to the USMC is needed. The clamp can be as simple as a series connection of a diode and capacitor across the dc-link [36], [37] and/or as a braking resistor with a series connected controllable switch, which provides braking capability in case of a mains failure [32].

Fig. 2.8 Sparse matrix converter.

Fig. 2.9 Very sparse matrix converter.

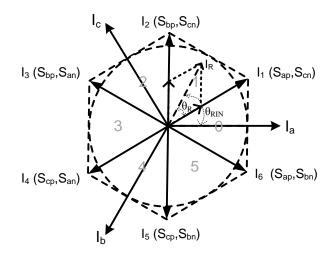

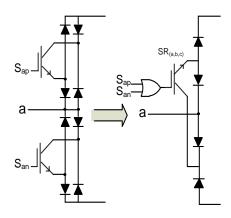

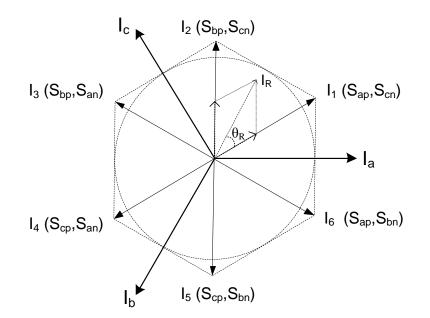

The front-end rectifier, whose one leg is depicted in Fig.2.11, draws sinusoidal input currents and controls the input displacement angle. For a unity input power factor, the reference input phase current vector is aligned with that of the input phase voltage. For example,  $(S_{ap}, S_{cn})$  indicates that the input phase "a" is connected to the positive (top) rail "p" and phase "c" is connected to the negative (bottom) rail "n".

Fig. 2.10 Ultra sparse matrix converter.

To avoid short circuit of a dc link voltage in a given switching period of the rectifier input stage, the commutation of the inverter output stage must be performed in a way identical to the commutation of a traditional IMC. There, a dead time between the turn-on of the power switches of a bridge leg must be implemented. Control design must ensure that there is no bidirectional connection between any two input lines, i.e., no short-circuiting of an input line-toline voltage terminal. Additionally a current path must be continuously provided. Therefore multistep commutation schemes are required, using voltage independent and current independent commutation as known for the CMC [38].

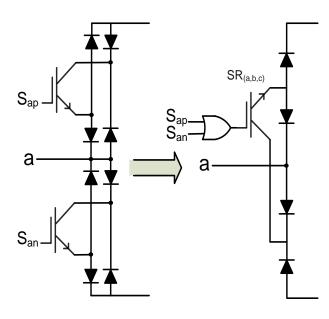

Fig. 2.11 Legs of the front-end rectifier. Left: sparse matrix converter, right: ultra sparse matrix converter.

Multi-step commutation is demanding on the microprocessor, but on the other hand indirect matrix converters can provide a degree of control freedom that is not available in the CMC. Complex commutation problems can be avoided. For instance, as proposed in [39], the inverter stage could be switched into a free-wheeling state and then the rectifier stage could commutate with zero dc-link current. This has the additional benefit of a reduction of switching losses of the input stage. By employing the zero dc-link current commutation strategy the topology of the IMC can be reduced to that of the very sparse matrix converter [32].

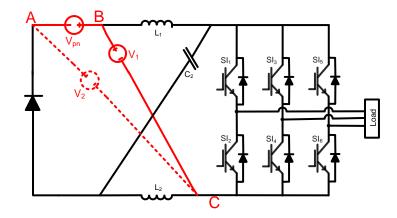

The maximum voltage gain of MCs is limited to 0.866 due to its buck conversion characteristic. To overcome this limitation, various modulation techniques, such as overmodulation methods, have been investigated for improvement in the output voltage quality and voltage transfer ratio. However, these methods tend to compromise system input or output operating performance [41]-[43]. To avoid such deterioration, a hybrid direct power converter that incorporates an auxiliary voltage source in the DC-link of the IMC was presented in [44]. Auxiliary power devices can support the unity voltage transfer ratio of the IMC. However, these additional switches increase the complexity of control and size and weight of the converter, which is a major disadvantage. A Z-source AC-DC matrix converter was studied in [45]. The Z-source provides a buck-boost conversion from the low DC battery voltage to an AC motor load, and exhibits good line-side current modulation. In [42] and [46] Z-source MC shown in Fig.2.12 was shown to boost the input voltage up to 2.35 times.

Fig. 2.12 Z source ultra sparse matrix converter.

Usually, the output stage of the IMC is a two-level PWM inverter. A three-level inverter can be employed at the back end of the MC, as shown in Fig.2.13, to reduce the switching

frequency harmonics of the output voltage. Such a topology, in which the center point for the output stage is provided by the star point of the input filter capacitors, was proposed in [47]. It enables formation of the output voltage by the phase and line-to-line input voltages. As the input stage of an SMC can be used, this topology was later designated as three-level SMC (USMC3).

Fig. 2.13 IMC with a three-level PWM output stage.

The same functionality can be achieved with the topology shown in Fig.2.14, which has the advantage of having a reduced number of switches [48]. Instead of using additional diodes to generate the fifth voltage level, using these two extra switches to move the voltage on positive rail, neutral point (star cap center) and negative rail achieves the same attribute. It can thus be called a three level indirect matrix converter (IMC3).

Fig. 2.14 IMC with additional single stage three-level PWM output stage.

Significant simplification of the indirect three-level MC circuits can be achieved by assuming the unidirectional power flow shown in Fig.2.15 [49]. The front end of this topology reveals the structure of a Vienna rectifier [50]. The main attribute of such converters is that the front end power switches are turning on and off only two times the fundamental frequency. This leads to high efficiency due to low switching losses in the corresponding power switches.

Fig. 2.15 Unidirectional IMC with a three-level PWM output stage.

There are other topologies related to matrix converters in the literature that can be considered as basic classes of MCs. Table 2.2 shows the number of transistors, diodes and gate driver sources are needed for such topologies. It is hard to tell which converter is better than the others, and the selection must be based on the specific application.

|             | СМС | IM<br>C | SPMC | VSMC | USMC | ZSMC | SMC3 | IMC3 | USMC3 |

|-------------|-----|---------|------|------|------|------|------|------|-------|

| Transistors | 18  | 18      | 15   | 12   | 9    | 9    | 24   | 20   | 15    |

| Diodes      | 18  | 18      | 18   | 30   | 18   | 18   | 30   | 20   | 36    |

| Gate drives | 9   | 8       | 7    | 19   | 7    | 7    | 8    | 8    | 7     |

Table 2.2 Comparison of MC topologies.

# 2.2 Modulation Techniques for Matrix Converters

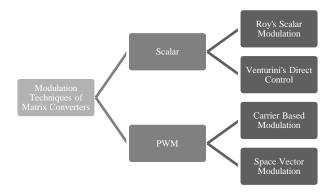

Venturini and Alesina in [51] provided the rigorous mathematical background and introduced the name "matrix converter," elegantly describing how the low frequency behaviors of the voltages and currents are generated at the load and the input [52]. Fig.2.16 shows the summary of the popular modulation techniques of matrix converters. Besides those shown, there are many other application specific techniques, which can be found in [55]-[64].

Fig. 2.16 Major specification of modulation techniques for matrix converters.

The first versatile modulation method is called direct control is also known as Venturini's modulation. Output voltages are formed from the fixed amplitude and fixed frequency input voltages. However, as a golden rule to matrix converters, output voltages have variable amplitude and variable frequency. Venturini's first technique had the voltage transfer ratio (VTR) of 0.5 only. He then proposed the third harmonic technique to reach the value of 0.866 [53].

A scalar method was proposed by Roy in the late 1980s. The main difference of the Roy's method from Venturini's is the scalar comparison of input voltages and the instantaneous value of output voltage. This technique is similar to Venturini's third harmonic insertion technique but fails at low switching frequencies. In both techniques, adjusting the power factor reduces the VTR.

Carrier based modulation method is commonly used in many applications and is based on the sinusoidal pulse width modulation (PWM). The high frequency carrier signal (triangle or sawtooth) with an offset voltage and fixed amplitude is compared with a sinusoidal reference signal. The amplitude of the reference signal specifies the modulation index and the frequency specifies the frequency of output voltages. The same process can be employed for either the three-phase or single-phase applications. In [54], a variable displacement angle for the power factor is applied to a carrier based method. The main drawback of this method is generation of high frequency reference signals are generated in hardware and this brings extra cost, complexity and space issues.

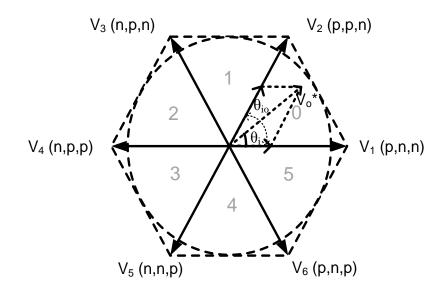

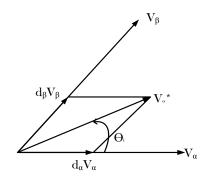

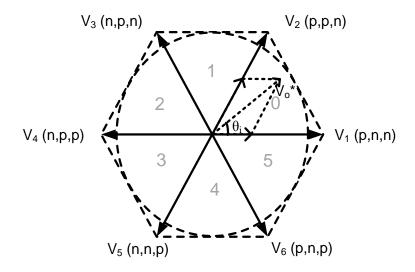

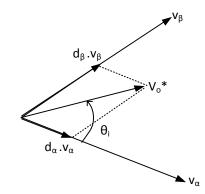

Space vector modulation (SVM) is a very popular method for matrix converters. This method features full control of frequency, amplitude and phase angle of the output voltage, as well as a controllable phase angle displacement of the input line currents. This type of modulation technique was first presented in [55] and has since acquired many extensions. The control method is based on rectification and inversion: the rectification stage forms the input sinusoidal currents and the inversion stage generates output voltages. The control method proposed in Chapter 4 is based on such cascaded SVM stages.

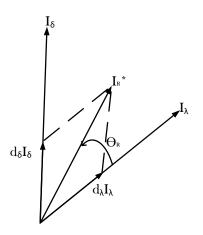

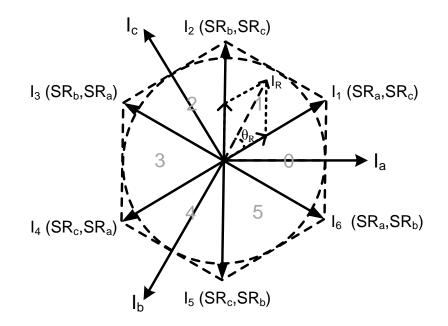

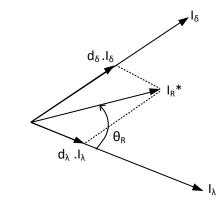

#### 2.2.1 Space Vector Rectifier Control

Active and zero states of the rectifier are utilized in the space vector modulation. The control algorithm must result in input currents that are sinusoidal with a controllable displacement angle with respect to the input voltages. To get unity power factor, input voltage has to be synchronized with input currents. A virtual dc link is formed by the chopped input voltages. The input currents are represented as the virtual dc-link current,  $I_{DC}$ , multiplied by the switch states of the rectifier stage with a transfer function described by Eq. (2.32).

$$\begin{bmatrix} I_A \\ I_B \\ I_C \end{bmatrix} = \begin{bmatrix} S_{R1} & S_{R2} \\ S_{R3} & S_{R4} \\ S_{R5} & S_{R6} \end{bmatrix} * \begin{bmatrix} I_{DC+} \\ I_{DC-} \end{bmatrix}$$

(2.34)

$$\begin{bmatrix} V_{DC+} \\ V_{DC-} \end{bmatrix} = \begin{bmatrix} S_{R1} & S_{R3} & S_{R5} \\ S_{R2} & S_{R4} & S_{R6} \end{bmatrix} * \begin{bmatrix} V_A \\ V_B \\ V_C \end{bmatrix}$$

(2.35)

Space vector modulation is based on transformation of the time-varying values of input currents and output voltages. The three-phase systems are transformed into two phase systems.

$$V_{out} = \frac{2}{3} \left( V_A + V_B e^{\frac{j2\pi}{3}} + V_C e^{j4\pi/3} \right)$$

(2.36)

$$I_{in} = \frac{2}{3} \left( I_a + I_b e^{\frac{j2\pi}{3}} + I_c e^{j4\pi/3} \right)$$

(2.37)

$$V_{in} = \frac{2}{3} \left( V_a + V_b e^{\frac{j2\pi}{3}} + V_c e^{j4\pi/3} \right)$$

(2.38)

$$I_{out} = \frac{2}{3} (I_A + I_B e^{\frac{j2\pi}{3}} + I_C e^{j4\pi/3})$$

(2.39)

Only nine states are allowed to avoid the open circuit of the dc links. Six of these are active states and three are zero states. The nine combinations can be divided into active vectors  $I_{[1,6]}$  and three zero vectors  $I_0$ . These discrete vectors can be associated with the dc link current value. For example,  $I_{2,ac}$  can be derived as:

$$I_2 = \frac{2}{3} (I_a + I_b e^{\frac{j2\pi}{3}} + I_c e^{j4\pi/3})$$

(2.40)

$$I_2 = \frac{2}{3} (I_{DC} + I_{DC} e^{j4\pi/3})$$

(2.41)

$$I_2 = \frac{2}{\sqrt{3}} I_{DC} e^{j\pi/6}$$

(2.42)

| State  | Vector                          | $\begin{bmatrix} \boldsymbol{S}_{R1} & \boldsymbol{S}_{R3} & \boldsymbol{S}_{R5} \\ \boldsymbol{S}_{R2} & \boldsymbol{S}_{R4} & \boldsymbol{S}_{R6} \end{bmatrix}^T$ | Ia                | I <sub>b</sub>    | I <sub>c</sub>    | <i>I<sub>in</sub></i>      | ∠I <sub>in</sub> | V <sub>out</sub>           | V <sub>DC</sub>  |

|--------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|----------------------------|------------------|----------------------------|------------------|