Aalborg Universitet

### Thermal Characterization of Silicon Carbide MOSFET Module Suitable for High-**Temperature Computationally-Efficient Thermal-Profile Prediction**

Chen, Mengxing; Wang, Huai; Pan, Donghua; Wang, Xiongfei; Blaabjerg, Frede

Published in: IEEE Journal of Emerging and Selected Topics in Power Electronics

DOI (link to publication from Publisher): 10.1109/JESTPE.2020.2984586

Publication date: 2020

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

*Citation for published version (APA):* Chen, M., Wang, H., Pan, D., Wang, X., & Blaabjerg, F. (2020). Thermal Characterization of Silicon Carbide MOSFET Module Suitable for High-Temperature Computationally-Efficient Thermal-Profile Prediction. *IEEE* Journal of Emerging and Selected Topics in Power Electronics, 1-12. https://doi.org/10.1109/JESTPE.2020.2984586

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

? You may not further distribute the material or use it for any profit-making activity or commercial gain

? You may freely distribute the URL identifying the publication in the public portal ?

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Thermal Characterization of Silicon Carbide MOSFET Module Suitable for High-Temperature Computationally-Efficient Thermal-Profile Prediction

Mengxing Chen, Student Member, IEEE, Huai Wang, Senior Member, IEEE, Donghua Pan, Member, IEEE, Xiongfei Wang, Senior Member, IEEE, and Frede Blaabjerg, Fellow, IEEE

Abstract—This paper characterizes the thermal behavior of a commercialized silicon carbide (SiC) power MOSFET module with special concerns on high-temperature operating conditions as well as particular focuses on SiC MOSFET dies. A temperature-dependent Cauer-type thermal model of the SiC MOSFET is proposed and extracted based on offline finiteelement simulations. This Cauer model is able to reveal the temperature-dependent thermal property of each packaging layer and it is suitable for the high-temperature thermal-profile prediction with sufficient computational efficiency. Due to the temperature-dependent thermal properties of the SiC die and ceramic material, the junction-heatsink thermal resistance can be raised by more than 10% under high-temperature conditions (up to 200 °C), which can considerably worsen thermal estimations of the SiC die and its packaging materials. Furthermore, the experimental measurement of transient thermal impedance was conducted under operating temperature variations (with virtual junction temperature ranging from 60.5  $^\circ C$  to 199.6  $^\circ C)$ , and the effectiveness of the proposed temperature-dependent Cauer model was fully validated.

*Index Terms*—Finite-element method (FEM), high operating temperature, computational efficiency, SiC power MOSFET module, temperature-dependent Cauer model.

#### I. INTRODUCTION

The power electronic system based on wide bandgap (WBG) devices is by far one of the most promising technologies in order to achieve a large energy efficiency improvement and a potential power-loss reduction by more than 50% [1], [2]. As one of the most popular WBG devices, the silicon carbide (SiC) MOSFET features several superiorities in comparison with the conventional silicon (Si) IGBT [2], e.g., the enhanced electric field, the enhanced thermal conductivity, the high-temperature operation capability, and etc.

Over recent years, the high-temperature capability of SiC MOSFET has always been an active research topic, as it enables new application areas such as automotive, aircraft, and deep-space exploration [3], [4]. It has been demonstrated that

the SiC die is capable of operating with junction temperatures being above 200 °C [5]–[8]. Although the rated junction temperatures of commercialized SiC modules are still constrained by conventional die-attach and encapsulation technologies (as lower than 150 °C) [9]–[11], novel materials for die-attach and encapsulation are promising to enable a practical virtual-junction-temperature up to 250 °C [12]–[15].

1

Nevertheless, the wide utilization of SiC MOSFETs for high-temperature applications is still dramatically prohibited. One of the most significant limiting factors is its reliability uncertainty under such high-temperature conditions, as the lifetime of the power semiconductor is closely related to its thermal profile [16], [17]. Compared to the Si IGBT, the SiC MOSFET is more fragile to transient-overloading or short-circuit events, as it features a more compact die area and thinner gate oxide [18]. On the other hand, if suffered from a long-term high-temperature profile, the SiC MOSFET can be deteriorated by issues such as the interlayer dielectric erosion, electrode delamination, and timedependent gate-oxide breakdown [19]. Besides, the long-term thermal cycling with escalated temperature magnitude can easily accelerate the wear-out processes, such as the bondwire lift-off and solder crack [16], [17]. In order to ensure a reliable operation of the SiC MOSFET throughout its targeted lifespan, a computationally-efficient thermal model suitable for the high-temperature thermal-profile prediction is highly demanded. Then, a mission-profile based reliability assessment methodology can be applied to translate the thermal-profile to a series of quantified reliability metrics [20], [21].

For the present-day thermal-profile prediction of power semiconductors, one of the most prevailing methodologies with a high computational efficiency is to perform thermal simulations using compact resistor-capacitor (RC) lumped thermal models [22], [23], i.e., the Foster-type and the Cauertype. Specifically, the Foster-type RC-lumped thermal model (the Foster model) can be extracted from experimental measurements of the transient thermal impedance, which is usually accessible from the device datasheet. It has been utilized for the evaluation of long-term thermal profiles of SiC MOSFETs in [24]–[26]. The other Cauer-type RC-lumped thermal model (the Cauer model) is attainable based on the knowledge of device geometry and material property. A conventional yet straightforward method to extracted the RC parameters in the

Manuscript received December 6, 2019; revised February 21, 2020; accepted March 16, 2020. This work was supported by Innovation Fund Denmark under Grant 5185-00006B (HER-SiC). This paper was presented in part at the IEEE 4th Southern Power Electronics Conference (IEEE SPEC-2018), Singapore, Dec. 10-13, 2018, and was awarded the best paper award. (Corresponding author: Donghua Pan)

The authors are with the Department of Energy Technology, Aalborg University, Aalborg 9220, Denmark (e-mail: mec@et.aau.dk; hwa@et.aau.dk; pan.dh@outlook.com; xwa@et.aau.dk; fbl@et.aau.dk).

Cauer model is based on two analytical equations, as it is discussed in [27]. The applications of Cauer model for the thermal-profile prediction of SiC MOSFET can be found in several works. In [28], a Cauer network of a multi-chip SiC MOSFET module was studied with a special concern on the heat path. Moreover, a measurement method of the Cauer-type thermal model of SiC MOSFETs was proposed in [29].

However, the Foster-type and Cauer-type thermal models discussed above are generally obtained for a specific temperature condition with fixed thermal resistance and capacitance, while their accuracy for the high-temperature thermal prediction is still unknown. Especially, the thermal properties of the SiC die as well as its packaging materials can shift considerably due to effects of free electrons and lattice vibrations [30]. In consideration of this issue, [31] characterized the temperature-dependent thermal performance of a Si IGBT module. It was validated that omitting the temperature effect can lead to unrealistic thermal-profile predictions. Moreover, an electro-thermal model with a special focus on the SiC die was proposed in [32], and the temperature effect of SiC thermal properties was taken into account, which made the proposed model suitable for short-circuit thermal predictions.

Concerning the above mentioned issues, this paper characterizes the high-temperature thermal performance of the SiC power MOSFET module with special focus on SiC MOSFET dies, and a temperature-dependent Cauer model is proposed accordingly. Without losing the generality, a commercialized SiC MOSFET module is utilized as the study case and the high-temperature thermal behavior of SiC MOSFET is fully revealed. The thermal properties of packaging materials (including SiC) are investigated in Section II to demonstrate the physical reason of the temperature effect on thermal performance. In order to be compatible for the long-term thermalprofile prediction, a temperature-dependent Cauer model is extracted based on offline FEM simulations in Section III. The proposed Cauer model fully characterizes the temperature effect on each packaging layer and is suitable for hightemperature thermal profile predictions with sufficient computational efficiency. Furthermore, multiple experimental measurements of the transient thermal impedance were conducted under virtual junction temperature variations from 60.5 °C to 199.6 °C, and the results are given in Section IV. It is concluded that neglecting the temperature-dependency of thermal properties may cause 10% error on the magnitude of thermal resistance. Although experimental validations were conducted up to 199.6 °C on the commercialized SiC MOSFET module, the Cauer model as well as its modeling methodology can also be applied to SiC MOSFET modules with higher operating temperatures. In Section V, the FEM extracted Cauer model is benchmarked with the conventional analytical Cauer model obtained by [27], and it is found that the FEM extracted Cauer model can provide the higher prediction accuracy.

Compared to [31], which studied the temperature effect on thermal models of the Si IGBT, this work characterizes the SiC MOSFET module for a higher junction temperature range as it is driven by the high-temperature capability of SiC. Furthermore, the temperature-dependent thermal property of the ceramic layer is modeled to give a more comprehensive

2

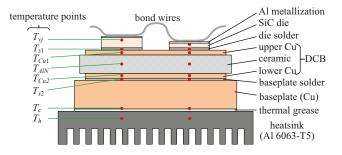

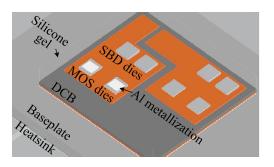

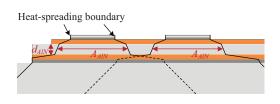

Fig. 1. Vertical view of the studied SiC MOSFET module interfacing with an Al-extrude heatsink.

understanding of the temperature effect on SiC thermal modeling. Compared to [32], which focused only on the thermal modeling of SiC die, the whole SiC MOSFET module (from the die to the heatsink) is studied in this work.

#### II. REVIEW OF STRUCTURE AND THERMAL PROPERTIES OF COMMERCIALIZED SIC MOSFET MODULE

#### A. Structure of SiC MOSFET Module

The vertical structure of a commercialized SiC MOSFET module is typically made of multiple layer stacks with various packaging materials, which resembles its Si counterparts. The vertical view of a commercialized SiC MOSFET module is depicted in Fig. 1. The SiC dies are soldered on a direct copper bonded (DCB) substrate, which consists of double copper layers and a ceramic layer sandwiched in between. Likewise, the DCB substrate is fixed on the copper baseplate via the baseplate solder, and the baseplate is mounted on the cooling system via the thermal interface material. Moreover, several temperature measurement points are depicted in Fig. 1, which will be discussed in the following section.

It is noted that the ceramic layer is typically made of from aluminum oxide (Al<sub>2</sub>O<sub>3</sub>), aluminum nitride (AlN), or silicon nitride (Si<sub>3</sub>N<sub>4</sub>). Compared with Al<sub>2</sub>O<sub>3</sub>, the AlN and Si<sub>3</sub>N<sub>4</sub> feature higher thermal conductivity, but reduced coefficient of thermal expansion, which are more preferable in high-performance power semiconductor modules.

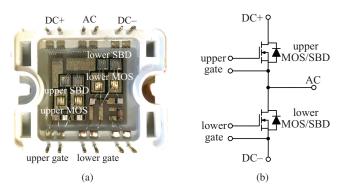

In this work, a commercialized half-bridge SiC MOSFET module rated at 1200 V and 55 A (APTMC120AM55CT1AG by Microsemi) is adopted as the study case. The top view as well as the circuit diagram of the module are detailed in Fig. 2(a) and Fig. 2(b), respectively. Each SiC switch consists of dual MOSFET dies connected in parallel. In addition, one pair of SiC Schottky-barrier diode (SBD) dies is applied in anti-parallel with each pair of MOSFET dies to mitigate the reverse-recovery current during the switching transient. The geometry dimensions of the SiC MOSFET module under study are listed in Table I. The AlN is utilized in this module as the ceramic material, which features the lowest thermal conductivity among the aforementioned ceramic materials.

## *B. Temperature-Dependent Thermal Properties of Packaging Materials*

For the thermal-profile prediction of power semiconductors, it is generally assumed that the power module is adiabatic from

Authorized licensed use limited to: Aalborg Universitetsbibliotek. Downloaded on April 02,2020 at 11:47:59 UTC from IEEE Xplore. Restrictions apply.

Fig. 2. Half-bridge SiC MOSFET module from Microsemi. (a) Top view. (b) Circuit diagram.

TABLE I DIMENSIONS OF DIFFERENT LAYERS INSIDE THE STUDIED SIC MODULE (MICROSEMI APTMC120AM55CT1AG).

| Layers                | Size $(mm^2)$                | Thickness (mm) |  |

|-----------------------|------------------------------|----------------|--|

| MOSFET die            | $2.80 \times 3.00$ (per die) | 0.18           |  |

| SBD die               | $3.08 \times 3.08$ (per die) | 0.377          |  |

| MOSFET solder         | $2.80 \times 3.00$ (per die) | 0.09           |  |

| SBD solder            | $3.08 \times 3.08$ (per die) | 0.09           |  |

| Upper copper          | $28.2 \times 25.54$          | 0.3            |  |

| Ceramic (AlN)         | $28.2 \times 25.54$          | 0.63           |  |

| Lower copper          | $28.2 \times 25.54$          | 0.3            |  |

| Baseplate solder      | $28.2 \times 25.54$          | 0.2            |  |

| Baseplate             | $49.46 \times 40.8$          | 2.5            |  |

| TIM (silicone grease) | $49.46 \times 40.8$          | 0.1            |  |

the top and lateral sides. The heat generated from the SiC die propagates through the solder layers, the DCB substrate, and the baseplate and eventually reaches the cooling system, where it is dissipated to the ambient. Therefore, the thermal properties of packaging materials, i.e., the thermal conductivity and specific heat capacity, will significantly affect the heat propagation process and the thermal performance of the SiC MOSFET module.

Specifically, the thermal conductivity measures the ability to conduct heat, which correlates to the thermal resistance in the RC lumped thermal model. The specific heat capacity, on the other hand, defines the quantity of heat required to raise the temperature per unit mass, as it can be characterized as the thermal capacitance in the RC lumped thermal model. Predicting the material temperature based on fixed thermal conductivity and specific heat capacity is regularly straightforward and easily accessible. However, the thermal properties of packaging layers can be considerably affected by material local temperatures due to effects of free electrons and lattice vibrations, which may lead to a significant discrepancy on thermal-profile estimation.

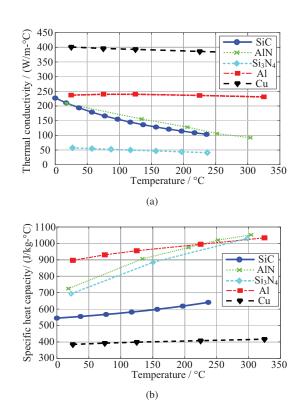

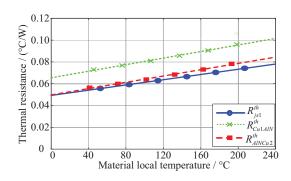

According to [31], [33]–[35], the thermal conductivities and specific heat capacities of various packaging materials (i.e., SiC, AlN,  $Si_3N_4$ , Cu, and Al) in correspondence with temperature are exhibited in Fig. 3(a) and Fig. 3(b), respectively. It can be obtained that the thermal conductivities of SiC and AlN feature an intensive temperature dependency, which

Fig. 3. Temperature-dependent thermal properties of packaging materials of the SiC MOSFET module. (a) Thermal conductivity. (b) Specific heat capacity.

decline with the increase of temperature. Moreover, the Cu and  $Si_3N_4$  also exhibit a non-neglectable temperature dependency, though not comparable with that of the SiC and AlN. In Fig. 3(b), the specific heat capacities of SiC, AlN,  $Si_3N_4$ , and Al can be characterized as positively related with the material temperature. Especially, the ceramic materials of AlN and  $Si_3N_4$  exhibit similar and more significant temperature dependencies, whereas other materials of the SiC, Cu, and Al are characterized by less temperature dependencies.

Consequently, neglecting the temperature-dependency of thermal properties of packaging materials may lead to unrealistic temperature estimations. Especially for the case of high-temperature operation, the actual junction temperature of the SiC die can be critically higher than the theoretical estimation without considering the temperature effect, as the thermal conductivities of SiC, AlN, Si<sub>3</sub>N<sub>4</sub>, and Cu are all negatively related with temperature.

#### III. EXTRACTION OF TEMPERATURE-DEPENDENT CAUER MODEL BASED ON FEM SIMULATION

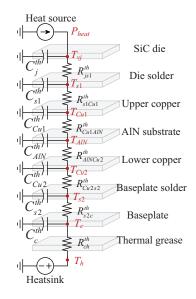

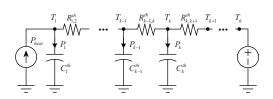

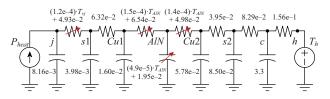

For the high-temperature thermal modeling of the SiC MOSFET module, the Cauer-type thermal model is applied in this work, as it is illustrated in Fig. 4. Each packaging layer of the SiC MOSFET module is represented by a thermal capacitance in connection with a thermal resistance. Accordingly, the temperature-dependent thermal properties of each packaging layer can be characterized in this Cauer model.

In order to extract the RC parameters in the Cauer model, FEM based simulations were performed on a threedimensional (3D) CAD model including geometry and mate-

Authorized licensed use limited to: Aalborg Universitetsbibliotek. Downloaded on April 02,2020 at 11:47:59 UTC from IEEE Xplore. Restrictions apply.

IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS

Fig. 4. Equivalent Cauer model of the SiC MOSFET module including structural information.

rial details (especially temperature-dependent thermal properties) of the SiC MOSFET module.

#### A. Implementation of FEM Simulation

The basic concept of FEM can be considered as subdividing the entire computational domain into separated smallscale parts and calculating local solutions of the diffusionconvection-reaction problem. For the analysis of heat-transfer process, multiple FEM based softwares are available, and the ANSYS/ICEPAK was utilized in this work.

As a study case, a 3D CAD model of the SiC MOSFET module under study was constructed in SOLIDWORKS, and was simulated in ANSYS/ICEPAK (as depicted in Fig. 5). The stacked multi-layer structure of the SiC module (as illustrated in Fig. 1 and Table I) was replicated in the model. The aforementioned thermal conductivities and specific heat capacities with temperature dependency were also programmed in ANSYS/ICEPAK. Then, multiple transient FEM simulations were conducted under different heatsink temperatures (i.e., 20 °C, 50 °C, 80 °C, 110 °C, and 140 °C). The upper-third volume of each MOSFET die was assumed as the heat source, since the generated heat is not uniformly distributed among the die volume but becomes more concentrated towards the upperthird volume of the die [32], [36]. Letting the upper-third die volume to be the heat source helps to better mimic the thermal behaviors inside the die and obtain the more realistic thermal impedance. Basic parameter settings of the FEM simulation are listed in Table II. A minimum time step of 10  $\mu$ s is selected to fully reveal the transient thermal response, and the maximum value of iterations-per-step is established to be 100 to ensure that the convergence criteria is fulfilled for each time step. The procedures for performing each simulation trial are demonstrated as follows:

1) The external conditions (i.e., the heatsink temperature and the heating power) and material thermal properties are defined prior to the simulation trial.

4

Fig. 5. Geometry overview of the 3D CAD model of the SiC MOSFET module in ANSYS/ICEPAK.

TABLE II

PARAMETER SETTINGS USED FOR THE FEM SIMULATION

| Parameters                    | Values                    |  |

|-------------------------------|---------------------------|--|

| Minimum time step             | 10 µs                     |  |

| Simulation duration           | 190 s                     |  |

| Maximum iterations/step       | 100                       |  |

| Convergence criteria (energy) | $\leq 10^{-10} \text{ J}$ |  |

| Minimum mesh size             | 30 µm                     |  |

| Heating power per die         | 30 W                      |  |

| Heatsink temperature          | 20-140 °C                 |  |

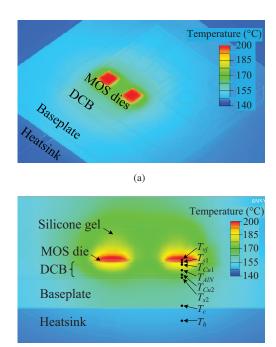

- 2) During the starting stage of the simulation, a constant heating power  $P_{heat} = 30$  W is applied to each MOSFET die until a thermal equilibrium is reached. The temperature distribution of the thermal equilibrium with heatsink temperature of 140 °C is depicted in Fig. 6. The steadystate temperatures at points of measurements [as indicated in Fig. 6(b)] under the thermal equilibrium are recorded. As the module is filled with silicone gel for insulation purpose (with thermal conductivity of 0.2 W/mK), a small portion of the generated heat can expand towards the top and lateral sides of the power stack at a pretty slow velocity [as can be seen from Fig. 6(b)]. Nevertheless, this effect will not degrade the modeling accuracy, given that the thermal conductivities of power-stack materials are in the range of 100–400 W/mK.

- 3) After the thermal equilibrium is reached, the heating power is removed and the cooling stage starts. Simultaneously, the transient temperature responses at the points of measurement are then monitored.

Given that the thermal distribution is significantly dependent on geometry and material, the temperature measurement points should be defined in individual layers, and aligned with the center point of the MOSFET die (i.e.,  $T_{s1}$  on die solder,  $T_{Cu1}$ on upper copper,  $T_{AlN}$  on AlN ceramic,  $T_{Cu2}$  on lower copper,  $T_{s2}$  on baseplate solder,  $T_c$  on baseplate case, and  $T_h$  on heatsink). Specifically, the virtual junction temperature of  $T_{vj}$ is recognized as the mean temperature of heated die volume, as the temperature values also become much higher towards the upper-third part of the die [36]. Otherwise, an optimistic thermal expectation shall be obtained if  $T_{vj}$  is assumed as the average temperature of the whole die-volume. It is noted that the thermal response of lower MOSFET should be identical with that of the upper MOSFET, since uniform packaging

#### IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS

Fig. 6. FEM-simulated steady-state temperature distribution of the SiC MOSFET module under the case of heatsink temperature of 140  $^\circ$ C. (a) Top view. (b) Vertical view.

(b)

structures and materials are involved. Moreover, the thermal profile of the SiC MOSFET in FEM simulation shall not be affected by conditions of other power devices.

#### B. Extraction of Thermal Resistance and Capacitance

Knowing both the steady-state and transient temperature responses at the defined measurement points, the parameters of thermal resistance and capacitance components in the Cauer model can be extracted accordingly.

The aforementioned multi-layer Cauer model is generalized in Fig. 7 for the ease of illustration. First, the thermal resistances of the Cauer model can be obtained according to the steady-state temperature measurements:

$$\begin{cases} R_{k-1,k}^{th} = (T_{k-1,steady} - T_{k,steady})/P_{heat} \\ R_{k,k+1}^{th} = (T_{k,steady} - T_{k+1,steady})/P_{heat} \end{cases}$$

(1)

where  $T_{k-1,steady}$ ,  $T_{k,steady}$ , and  $T_{k+1,steady}$  designate the steady-state temperatures of the  $(k-1)^{th}$ ,  $k^{th}$ , and  $(k+1)^{th}$  measurement points under the thermal equilibrium, respectively. Then, the thermal capacitance of the  $k^{th}$  layer,  $C_k^{th}$ , can be extracted by:

$$C_{k}^{th} = P_{k}\left(t\right) \left/ \frac{dT_{k}\left(t\right)}{dt} \right. \tag{2}$$

$$\begin{cases} P_k(t) = \frac{T_{k-1}(t) - T_k(t)}{R_{k-1,k}^{th}} - \frac{T_k(t) - T_{k+1}(t)}{R_{k,k+1}^{th}}, k \neq 1\\ P_k(t) = -\frac{T_k(t) - T_{k+1}(t)}{R_{k,k+1}^{th}}, k = 1 \end{cases}$$

(3)

where  $T_{k-1}(t)$ ,  $T_k(t)$ , and  $T_{k+1}(t)$  denote the transient temperature responses of the  $(k-1)^{th}$ ,  $k^{th}$ , and  $(k+1)^{th}$  measurement points obtained from the FEM simulation. Additionally,

5

Fig. 7. The generalized multi-layer Cauer model for the extraction of thermal resistance and capacitance parameters.

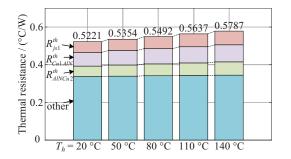

Fig. 8. Bar graph of FEM-extracted thermal resistance values with special emphasises on  $R_{is1}^{th}$ ,  $R_{Cu1AlN}^{th}$ , and  $R_{AlNCu2}^{th}$ .

$P_k(t)$  denotes the transient power flowing through the  $k^{th}$  thermal capacitor branch.

#### C. Temperature-Dependent Cauer Model

Using the aforementioned methodology, the thermal resistance and capacitance under heatsink-temperature variations can be obtained accordingly, as listed in Table III. As the heatsink temperature increases from 20 °C to 140 °C, the thermal resistance values related to the SiC die  $(R_{js1}^{th})$  and AlN ceramic  $(R_{Cu1AlN}^{th} \text{ and } R_{AlNCu2}^{th})$  are increased by 26%, 24%, and 29%, respectively. In contrast, the values of  $R_{s1Cu1}^{th}$ ,  $R_{Cu2s2}^{th}$ ,  $R_{s2c}^{th}$ , and  $R_{ch}^{th}$  are increased by 0.9%, 2.0%, 3.3%, and 2.2%, respectively. Therefore, the temperature-dependency of  $R_{s1Cu1}^{th}$ ,  $R_{Cu2s2}^{th}$ ,  $R_{s2c}^{th}$ , and  $R_{ch}^{th}$  can be omitted as they will not cause significant error to the thermal prediction. The bargraph demonstrating the thermal resistance values is depicted in Fig. 8. The overall junction-heatsink thermal resistance  $R_{jh}^{th}$  is raised by more than 10%, from 0.5221 °C/W to 0.5787 °C/W.

As the heatsink temperature increases from 20 °C to 140 °C, the thermal capacitance values of  $C_{s1}^{th}$ ,  $C_{Cu1}^{th}$ ,  $C_{AlN}^{th}$ ,  $C_{Cu2}^{th}$ ,  $C_{s2}^{th}$  are increased by 15%, 11%, 29%, 16%, and 0.6% respectively, which is caused by the positive temperature dependency of specific heat capacities [illustrated in Fig. 3(b)]. On the other hand, the values of  $C_{j}^{th}$  and  $C_{c}^{th}$  feature a negative temperature-dependency, as they are decreased by 0.9% and 1.5% respectively. Because, for thermal capacitance with greater layer-thickness but less temperature dependency, i.e.,  $C_{j}^{th}$  and  $C_{c}^{th}$ , the effect of heat-flux concentration may dominate under a high-temperature-gradient condition [23].

In order to reveal this thermal-resistance-temperature relationship in the Cauer model, curve fittings were performed using linear polynomials. In consideration of easy implementation, only the thermal components with parametric variance higher than 20% throughout the testing range are characterized

6

TABLE III PARAMETERS OF THERMAL RESISTANCE AND CAPACITANCE OF THE MULTI-LAYER CAUER MODEL OBTAINED BY FEM SIMULATION. (UNIT:  $R^{th} - °C/W$ ,  $C^{th} - J/°C$ )

|                   | Heatsink Temperature |                      |                      |                      |                       |

|-------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|

|                   | 20 °C                | 50 °C                | 80 °C                | 110 °C               | 140 °C                |

| $R^{th}_{js1}$    | 0.0557               | 0.0592               | 0.0629               | 0.0665               | 0.0704                |

| $C_j^{th}$        | $8.20\times10^{-3}$  | $8.18\times10^{-3}$  | $8.16\times10^{-3}$  | $8.16\times 10^{-3}$ | $8.13 \times 10^{-3}$ |

| $R^{th}_{s1Cu1}$  | 0.0628               | 0.0630               | 0.0632               | 0.0633               | 0.0634                |

| $C^{th}_{s1}$     | $3.63 	imes 10^{-3}$ | $3.76\times10^{-3}$  | $3.90\times 10^{-3}$ | $4.04\times 10^{-3}$ | $4.19 	imes 10^{-3}$  |

| $R_{Cu1AlN}^{th}$ | 0.0730               | 0.0767               | 0.0809               | 0.0857               | 0.0905                |

| $C_{Cu1}^{th}$    | $1.50\times 10^{-2}$ | $1.54\times 10^{-2}$ | $1.58\times 10^{-2}$ | $1.62\times 10^{-2}$ | $1.67 \times 10^{-2}$ |

| $R^{th}_{AlNCu2}$ | 0.0564               | 0.0599               | 0.0639               | 0.0684               | 0.0730                |

| $C^{th}_{AlN}$    | $2.14\times 10^{-2}$ | $2.30\times 10^{-2}$ | $2.46\times 10^{-2}$ | $2.62\times 10^{-2}$ | $2.75 	imes 10^{-2}$  |

| $R_{Cu2s2}^{th}$  | 0.0390               | 0.0393               | 0.0395               | 0.0397               | 0.0398                |

| $C_{Cu2}^{th}$    | $5.26\times10^{-2}$  | $5.44\times10^{-2}$  | $5.65\times10^{-2}$  | $5.89\times10^{-2}$  | $6.12 \times 10^{-2}$ |

| $R^{th}_{s2c}$    | 0.0811               | 0.0820               | 0.0827               | 0.0832               | 0.0838                |

| $C^{th}_{s2}$     | $8.46\times 10^{-2}$ | $8.49\times10^{-2}$  | $8.51\times 10^{-2}$ | $8.50\times 10^{-2}$ | $8.51 	imes 10^{-2}$  |

| $R^{th}_{ch}$     | 0.1542               | 0.1552               | 0.1561               | 0.1569               | 0.1577                |

| $C_c^{th}$        | 3.34                 | 3.33                 | 3.32                 | 3.31                 | 3.29                  |

| $R^{th}_{jh}$     | 0.5221               | 0.5354               | 0.5492               | 0.5637               | 0.5787                |

Fig. 9. Temperature-dependent thermal resistances and curve fitting results of  $R_{js1}^{th}$ ,  $R_{Cu1AlN}^{th}$ , and  $R_{AlNCu2}^{th}$ .

by linear polynomials (i.e.,  $R_{js1}^{th}$ ,  $R_{Cu1AlN}^{th}$ , and  $R_{AlNCu2}^{th}$ ). This selecting criteria also applies for the characterization of thermal capacitances, and only  $C_{AlN}^{th}$  with a parametric variance of 29% is modeled using the linear polynomial. As depicted in Fig. 9, the curve fitting results match well with discrete data points and reflect a rising tendency of  $R_{js1}^{th}$ ,  $R_{Cu1AlN}^{th}$ , and  $R_{AlNCu2}^{th}$ . Then, the temperature-dependent Cauer model can be concluded accordingly. As illustrated in Fig. 10, the thermal resistance and capacitance components of  $R_{js1}^{th}$ ,  $R_{Cu1AlN}^{th}$ ,  $R_{Cu1AlN}^{th}$ ,  $R_{Cu1AlN}^{th}$ ,  $R_{AlNCu2}^{th}$ , and  $C_{AlN}^{th}$  are characterized as temperature dependent by linear polynomial equations, whereas other components can be regarded as temperature-constant as discussed above.

It is noted that the SiC SBD dies may also operate in applications and generate considerable amount of heat, which may also affect the thermal profiles of MOSFET dies [37]. In this situation, a module-level thermal characterization integrating thermal models of both the MOSFET and SBD shall be required. For that module-level thermal modeling, it is generally assumed that thermal models of the MOSFET and SBD are coupled through either the heatsink or baseplate [36].

Fig. 10. The FEM-extracted Cauer model with temperature-dependent RC components.

Hence, the junction-heatsink (or junction-baseplate) thermal impedances of SiC MOSFET and SBD can be studied independently and integrated together via the heatsink or baseplate node as the module-level thermal model. Moreover, the FEM based modeling method discussed above can also be utilized for the thermal modeling of SiC SBD.

#### D. Application for Transient Thermal Simulation

As  $R_{js1}^{th}$ ,  $R_{Cu1AlN}^{th}$ ,  $R_{AlNCu2}^{th}$ , and  $C_{AlN}^{th}$  are dependent on material local temperatures, the values of these thermal components should be calibrated prior to the transient thermal simulation. An implementation flowchart of the Cauer-model simulation with a calibration process is depicted in Fig. 11. An iteration process with steady-state thermal calculations (iteration of mean  $T_{vj}$  and  $T_{AlN}$  and update of  $R_{js1}^{th}$ ,  $R_{Cu1AlN}^{th}$ ,  $R_{AlNCu2}^{th}$ , and  $C_{AlN}^{th}$ ) is utilized to calibrate these temperaturedependent components until the convergence condition of  $|T_{vj,n} - T_{vj,n}| \leq 1^{\circ}$ C is satisfied. In normal cases, it takes three times of iteration in maximum to reach the convergence condition. Thereafter, the transient thermal simulation can be conducted using the calibrated thermal resistance and capacitance values. A specific application example is demonstrated as follows.

One of the typical heating conditions of SiC power MOS-FETs can be considered as a periodic power in a dc/ac inverter

IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS

Fig. 11. Implementation flowchart of the Cauer-model simulation with a calibration process.

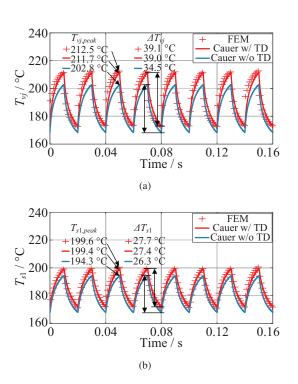

application, which comes from switching and conduction losses per half ac-cycle. By simulating the Cauer model in a circuit simulator (MATLAB/Simulink), the virtual junction temperature of  $T_{vj}$  under a periodic heating power (square wave with 180 W magnitude, 50% duty cycle, and 50 Hz frequency) is obtained as depicted in Fig. 12(a), and the heatsink temperature is set to be 140 °C. For comparison, the  $T_{vj}$  simulated by the FEM simulation (ANSYS/ICEPAK) as well as by the Cauer model without temperature dependency are plotted in Fig. 12(a).

It can be seen that the  $T_{vi}$  obtained from the temperaturedependent Cauer model matches satisfactorily with that simulated by ANSYS/ICEPAK in Fig. 12(a). The temperature peaks  $T_{vj,peak}$  obtained by the FEM simulation and temperature-dependent Cauer model are observed as 212.5 °C and 211.7 °C respectively (with 0.3% error). Additionally, the amplitudes of temperature swing  $\Delta T_{vi}$  calculated by the two methods are exhibited as 39.1 °C and 39.0 °C (with 0.2% error). Nevertheless, a significant discrepancy is witnessed if the temperature-dependency of the thermal model is neglected. The maximum disparity of  $T_{vj}$  between Cauer-model calculations with and without the temperature dependency counts to be 8.9 °C (with 4.4% error), which occurs at peak points  $T_{vj,peak}$  in Fig. 12(a). Moreover, a considerable discrepancy on  $\Delta T_{vi}$  (with error up to 4.5 °C, 13%) can be observed from Fig. 12(a). Additionally, another reliability-critical variable, the die-solder temperature of  $T_{s1}$ , can also be obtained from the temperature-dependent Cauer model, as it is depicted in Fig. 12(b). Similar conclusions can also be drawn.

#### IV. EXPERIMENTAL CHARACTERIZATION OF TRANSIENT THERMAL IMPEDANCE

#### A. Introduction to Experimental Setup

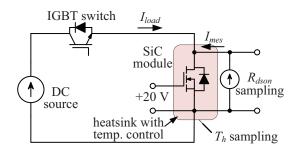

In order to validate the temperature-dependent Cauer model, an experimental setup was built in laboratory and the junction-

7

Fig. 12. Temperature profile of the SiC MOSFET module. (a) Cauersimulated virtual junction temperature of  $T_{vj}$  with (w/) and without (w/o) the temperature dependency (TD), as well as the  $T_{vj}$  recorded from the FEM simulation. (b) Cauer-simulated die-solder temperature of  $T_{s1}$  w/ and w/o the TD, as well as the  $T_{s1}$  recorded from the FEM simulation.

Fig. 13. Main circuit diagram of the experimental setup for the transientthermal-impedance measurement of SiC MOSFET.

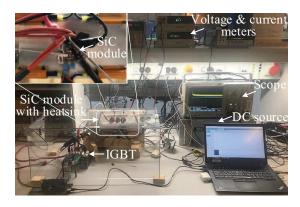

heatsink transient thermal impedance of the SiC MOSFET was measured. As demonstrated in Fig. 13, the main circuit of the experimental setup consists of a DC power source, an auxiliary IGBT, and a SiC module APTMC120AM55CT1AG with its peripheral circuits. It is noted that the circuit diagram illustrated above is only valid for the thermal characterization of the SiC MOSFET, not for that of the external SBD. A photograph of the experimental setup is exhibited in Fig. 14. The SiC module was mounted on a Al-extrude heatsink with temperature-control functionality, and a layer of silicone grease (*Dow Corning 340*) was applied in between.

Doing so, the experimental measurement of transient thermal impedance was able to be conducted under temperature variations. The heatsink temperature  $T_h$  was sampled via an optic fiber temperature sensor, which was inserted into the heatsink plate. Meanwhile, the on-state resistance of  $R_{dson}$ was acquired by external voltage and current probes.

IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS

Fig. 14. Photograph of the experimental setup for the transient-thermalimpedance measurement of SiC MOSFET.

Fig. 15. Virtual junction temperature of  $T_{vj}$  in correspondence with the on-state resistance of  $R_{dson}$  of the SiC MOSFET module APTMC120AM55CT1AG.

### B. Experimental Measurement of Transient Thermal Impedance

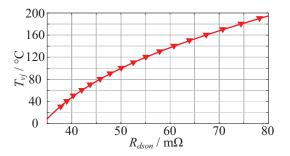

As the  $R_{dson}$  of the SiC MOSFET features an intensive sensitivity to the temperature, the virtual junction temperature of  $T_{vj}$  in time domain can be indirectly obtained by the measured  $R_{dson}$  profile [38]. This is also noted as the temperaturesensitive electrical parameter based methodology for junction temperature monitoring.

Without generating heating power from the MOSFET die, the  $T_{vj}$  can be assumed identical to the heatsink temperature of  $T_h$  once a thermal equilibrium is reached. Then, multiple sets of  $T_{vj}$  -  $R_{dson}$  data was able to be experimentally measured with the temperature-controlled heatsink. Then, the  $T_{vj}$  - $R_{dson}$  function can be acquired as a fractional equation by means of curve fitting:

$$T_{vj}(R_{dson}) = \frac{n_1 \cdot R_{dson}^2 + n_2 \cdot R_{dson} + n_3}{R_{dson} + d_1}$$

(4)

where  $n_1 = 1.842$ ,  $n_2 = 66.95$ ,  $n_3 = -4427$ , and  $d_1 = -14.67$ , which can be obtained by the curve-fitting tool of MATLAB. The calibrated  $T_{vj}$  -  $R_{dson}$  function with the data points are depicted in Fig. 15.

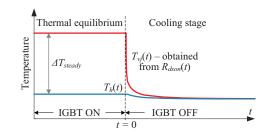

The implementation procedure as well as the temperature responses of the transient thermal impedance measurement are illustrated in Fig. 16. During the initial stage of the experiment, both the auxiliary IGBT and the SiC MOSFET maintained conducted with load current of  $I_{load} = 30$  A supplied by a programmable DC source. The SiC MOSFET works in its ohmic region and its junction temperature was

Fig. 16. Implemented test procedure and temperature response of the transient thermal impedance measurement.

heated up by the on-state resistance of  $R_{dson}$ . After the thermal equilibrium was reached and the junction temperature was in steady state, the gate voltage of the auxiliary IGBT was removed and the load current was switched-off. Then, the cooling stage starts and a measurement current of  $I_{mes} =$ 1 A was injected into the SiC MOSFET die by an external current source in parallel with the device. Meantime, the SiC MOSFET maintained conduction and still worked in the ohmic region. The transient  $R_{dson}$  indicating  $T_{vj}$  can be sampled by external voltage and current probes. It is noted that the resistive heating power generated by  $I_{mes}$  is in the range of tens of miliwatt ( $I_{mes}^2 R_{dson}$ ), therefore the  $I_{mes}$  will not affect the accuracy of the measurement.

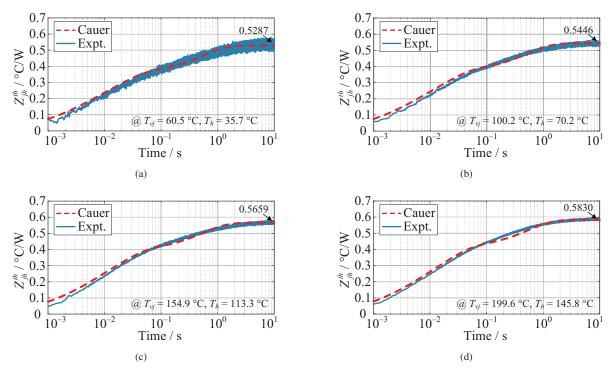

Multiple experimental measurements were conducted with different heatsink temperatures, i.e.,  $T_h = 37$  °C, 70.2 °C, 113.3 °C, and 145.8 °C. The load current of  $I_{load} = 30$  A was applied and a broad range of junction temperature was reached during the experiment (see Table IV). It is noted that the transient thermal impedance under the  $T_{vj}$  of 199.6 °C was successfully tested, which is 50 °C higher than its rated junction temperature.

Once the transient virtual junction temperature of  $T_{vj}(t)$ and the heatsink temperature of  $T_h(t)$  were obtained from the cooling stage of the experiment, the transient thermal impedance from junction to heatsink can be calculated by:

$$Z_{jh}^{th}(t) = \frac{-\left[T_{vj}(t) - T_{h}(t)\right] + \Delta T_{steady}}{P_{heat}}$$

(5)

where  $\Delta T_{steady}$  and  $P_{heat}$  denote the steady-state junctionheatsink temperature difference and the die loss, respectively.

#### C. Experiment Results and Comparison

The measured junction-heatsink transient thermal impedance of  $Z_{jh}^{th}(t)$  under heatsink conditions of  $T_h =$  37 °C, 70.2 °C, 113.3 °C, and 145.8 °C are depicted in Fig. 17(a)–(d), respectively. The thickness variations of  $Z_{jh}^{th}(t)$  curves in Fig. 17(a)–(d) are induced by the noise-level differences under various  $P_{heat}$  conditions, as a higher  $P_{heat}$  value also helps to attenuate the measurement noises of  $T_{vj}(t)$  according to (5). In order to do validation, the  $Z_{jh}^{th}(t)$  simulated by the temperature-dependent Cauer model are also studied as exhibited in dashed curves, and identical external conditions. A steady-state error of lower than 0.9% between the Cauer-model simulation and experimental

IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS

9

TABLE IV

External Condition and Steady-State Results of Multiple Experiments under Thermal Equilibrium.

|                                       | Experiment No. |          |          |          |

|---------------------------------------|----------------|----------|----------|----------|

|                                       | Expt 1         | Expt 2   | Expt 3   | Expt 4   |

| Heatsink temperature $T_h$            | 35.7 °C        | 70.2 °C  | 113.3 °C | 145.8 °C |

| Load current Iload                    | 30 A           | 30 A     | 30 A     | 30 A     |

| Junction loss $P_{heat}$              | 46.3 W         | 55.4 W   | 73.2 W   | 91.9 W   |

| Virtual junction temperature $T_{vj}$ | 60.5 °C        | 100.2 °C | 154.9 °C | 199.6 °C |

Fig. 17. Junction-heatsink transient thermal impedance obtained by both experimental measurements and the temperature-dependent Cauer model with different temperature conditions. (a)  $T_h = 35.7$  °C,  $I_{load} = 30$  A. (b)  $T_h = 70.2$  °C,  $I_{load} = 30$  A. (c)  $T_h = 113.3$  °C,  $I_{load} = 30$  A. (d)  $T_h = 145.8$  °C,  $I_{load} = 30$  A.

measurement applies for all of the conditions studied. It can be concluded that the proposed temperature-dependent Cauer model can characterize transient thermal behaviors of a real SiC MOSFET with limited error-band under both the normal and high-temperature conditions. Furthermore, the amplitude of the measured thermal impedance, i.e., the  $R_{jh}^{th}$ , is raised by more than 10% (from 0.5287 °C/W to 0.5830 °C/W) as  $T_{vj}$ increases from 60.5 °C to 199.6 °C, as indicated in Fig. 17.

#### V. BENCHMARKING OF MODELING METHODOLOGIES OF CAUER-TYPE THERMAL MODELS

As validated in Section IV, the FEM-extracted Cauer model is able to predict the high-temperature thermal performance of the SiC MOSFET module under both the transient- and steady-state. Other than conducting parameter extractions by FEM simulations, the conventional method studied in [27] can also be a promising solution for the establishment of the Cauer model, by which the temperature dependencies of thermal behaviors can be modeled using two analytical equations. This section will give an introduction to this method and provide a performance benchmarking of these two approaches.

#### A. Introduction to the Analytical Methodology

According to the Fourier's Law for heat conduction, the thermal resistance of each packaging layer can be calculated from the thermal conductivity of its forming material:

$$R^{th} = \frac{1}{k} \cdot \frac{d}{A} \tag{6}$$

where k is the material thermal conductivity, d is the heatdissipation distance, and A is the effective cross-sectional area for heat spreading. An example for  $d_{AlN}$  and  $A_{AlN}$ identifications is demonstrated in Fig. 18. More analysis on the calculation of effective heat-spreading area can be found in [39].

Additionally, the thermal capacitance of single layer is able to be attained from its specific heat capacity:

$$C^{th} = c_h \cdot \rho \cdot d \cdot A \tag{7}$$

where  $\rho$  is the mass density of material, and  $c_h$  is the specific heat capacity. By applying (6) and (7), it is noted that the heat flux and temperature distribution of each physical layer are

Fig. 18. Vertical view of the heat-spreading boundary and identifications of heat-dissipation distance d and effective cross-sectional area A of the AlN layer.

TABLE V PARAMETER VALUES UTILIZED FOR ANALYTICAL CALCULATION OF THERMAL RESISTANCE AND CAPACITANCE

| Component                                                           | Related layer | $ ho (g/cm^3)$ | d (mm) | $A \\ (mm^2)$ |

|---------------------------------------------------------------------|---------------|----------------|--------|---------------|

| $R^{th}_{js1}$                                                      | j             | _              | 0.12   | 16.8          |

| $\begin{array}{c} R^{th}_{Cu1AlN} + \\ R^{th}_{AlNCu2} \end{array}$ | Cu1           | _              | 0.15   | 20.5          |

|                                                                     | AlN           | —              | 0.63   | 34.1          |

|                                                                     | Cu2           | _              | 0.15   | 51.2          |

| $C_j^{th}$                                                          | j             | 3.10           | 0.18   | 16.8          |

| $C^{th}_{AlN}$                                                      | AlN           | 3.26           | 0.63   | 34.1          |

simplified as uniformly distributed within the defined crosssectional area of A.

As the temperature dependencies of thermal conductivities and specific heat capacities can be obtained from Fig. 3, the temperature-dependent thermal resistance and capacitance are also able to be modeled according to (6) and (7).

#### B. Performance Benchmarking of Modeling Methodologies

In order to benchmark their ability to model the temperature-dependent thermal resistance, the values of  $R_{js1}^{th}$  and  $R_{Cu1AlN}^{th} + R_{AlNCu2}^{th}$  obtained from both the FEM extraction and what is derived by (6) are detailed in Fig. 19(a). The values of heat-dissipation distance d and effective cross-sectional area A utilized for analytical derivations are listed in Table V for reference. It is observed in Fig. 19(a) that the temperature dependency is able to be characterized by (6), as comparable resistance-temperature slew rates are exhibited from both methods. Nonetheless, the analytical method shows relatively lower thermal resistance values, since (6) assumes an equalized distribution of the heat flux among the effective cross-sectional area. In contrast, the heat flux can be more concentrated beneath the center of the SiC die in FEM simulations, which better imitates the real heat-spreading scenario.

Moreover, the parameters of  $C_{j}^{th}$  and  $C_{AlN}^{th}$  calculated by (7) are compared with FEM extractions in Fig. 19(b), where an analogous explanation also applies. The values of  $\rho$ , d, and A used in (7) are also given in Table V for reference. As the temperature-field assumed in (7) is regarded as homogeneous among the effective heat-spreading area, more Joules of energy are to be calculated in (7) to heat up the whole area per Celsius degree, i.e., more thermal capacitance compared to FEM extractions. Consequently, a significant discrepancy on  $C_{AlN}^{th}$  can be observed in Fig. 19(b). In spite of this, the

10

Fig. 19. Benchmarking of temperature-dependent thermal resistances and capacitances obtained from both the FEM extraction and the analytical equations. (a)  $R_{js1}^{th}$  and  $(R_{Cu1AlN}^{th} + R_{AlNCu2}^{th})$ . (b)  $C_j^{th}$  and  $C_{AlN}^{th}$ .

calculation on  $C_j^{th}$  exhibits a satisfactory match with its FEM extraction since the heat-spreading area of the SiC die is not comparable with that of the AlN ceramic layer and less computational error shall be incurred.

Overall, as featured by lower thermal resistances and higher thermal capacitances, the conventional method [by analytical equations (6) and (7)] will expect a relatively more optimistic thermal-profile estimation when compared with the FEM based method studied in this work. Nevertheless, it should also be pointed out that these two methods summarized in this work are currently unable to characterize the thermal degradation induced by the aging process of power device.

#### VI. CONCLUSION

This paper characterizes the thermal performance of a commercialized SiC MOSFET module with special concerns on high-temperature operating conditions as well as a particular focus on SiC MOSFET dies. It is found that the temperaturedependent thermal properties of the SiC die and AlN ceramic can considerably worsen the thermal performance under high operating temperature. Then, a temperature-dependent Cauertype thermal model of the SiC MOSFET is extracted in this work based on FEM simulations, which is able to reveal the temperature-dependent thermal properties of packaging layers and it is suitable for high-temperature thermal-profile prediction with sufficient computational efficiency.

It is concluded from the proposed Cauer model that the overall thermal resistance can be raised by more than 10% under high-temperature conditions (up to 200 °C). An application case with periodic heating power has demonstrated

that the predicted virtual junction temperature of  $T_{vj}$  can be raised by 8.9 °C with the consideration of temperature dependency. Additionally, the junction temperature swing of  $\Delta T_{vj}$  is elevated by 4.5 °C using the extracted Cauer model.

Furthermore, the accuracy of the extracted temperaturedependent Cauer model was validated through experiments. Multiple experimental measurements of thermal impedances were conducted under both normal- and high-temperature conditions (60.5-199.6 °C), and their transient thermal impedance curves match satisfactorily for a broad temperature range. A steady-state error of lower than 0.9% between the Cauer-model simulation and experimental measurement applies for all of the conditions studied. Additionally, the accuracy of the FEMextracted Cauer model is proven to be more superior through the benchmarking with an analytical Cauer model.

#### REFERENCES

- J. Millán, P. Godignon, X. Perpiñà, A. Pérez-Tomás, and J. Rebollo, "A survey of wide bandgap power semiconductor devices," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2155–2163, May 2014.

- [2] X. She, A. Q. Huang, O. Lucía, and B. Ozpineci, "Review of silicon carbide power devices and their applications," *IEEE Trans. Ind. Electron.*, vol. 64, no. 10, pp. 8193–8205, Oct. 2017.

- [3] J. Rabkowski, D. Peftitsis, and H. Nee, "Silicon carbide power transistors: A new era in power electronics is initiated," *IEEE Ind. Electron. Mag.*, vol. 6, no. 2, pp. 17–26, Jun. 2012.

- [4] A. O. Adan, D. Tanaka, L. Burgyan, and Y. Kakizaki, "The current status and trends of 1,200-v commercial silicon-carbide mosfets: Deep physical analysis of power transistors from a designer's perspective," *IEEE Power Electron. Mag.*, vol. 6, no. 2, pp. 36–47, Jun. 2019.

- [5] Z. Wang, X. Shi, L. M. Tolbert, F. Wang, Z. Liang, D. Costinett, and B. J. Blalock, "A high temperature silicon carbide mosfet power module with integrated silicon-on-insulator-based gate drive," *IEEE Trans. Power Electron.*, vol. 30, no. 3, pp. 1432–1445, Mar. 2015.

- [6] D. P. Hamilton, M. R. Jennings, A. Pérez-Tomás, S. A. O. Russell, S. A. Hindmarsh, C. A. Fisher, and P. A. Mawby, "High-temperature electrical and thermal aging performance and application considerations for sic power dmosfets," *IEEE Trans. Power Electron.*, vol. 32, no. 10, pp. 7967–7979, Oct. 2017.

- [7] N. Tega, S. Sato, and A. Shima, "Comparison of extremely hightemperature characteristics of planar and three- dimensional sic mosfets," *IEEE Trans. Power Electron.*, vol. 40, no. 9, pp. 1382–1384, Sep. 2019.

- [8] C. Unger and M. Pfost, "Thermal stability of sic-mosfets at high temperatures," *IEEE Trans. Electron Devices*, vol. 66, no. 11, pp. 4666– 4672, Nov. 2019.

- [9] APTMC120AM55CT1AG Datasheet, Microsemi, Jun. 2013, rev. 1.

- [10] CAS120M12BM2 1.2-kV, 13-mΩ, All-Silicon Carbide, Half-Bridge Module, Cree, Inc., Aug. 2015.

- [11] FF11MR12W1M1\_B11 Datasheet, Infineon Technologies AG, Jul. 2018, rev. 2.2.

- [12] R. Khazaka, L. Mendizabal, D. Henry, and R. Hanna, "Survey of hightemperature reliability of power electronics packaging components," *IEEE Trans. Power Electron.*, vol. 30, no. 5, pp. 2456–2464, May 2015.

- [13] F. Yu, J. Cui, Z. Zhou, K. Fang, R. W. Johnson, and M. C. Hamilton, "Reliability of ag sintering for power semiconductor die attach in hightemperature applications," *IEEE Trans. Power Electron.*, vol. 32, no. 9, pp. 7083–7095, Sep. 2017.

- [14] K. Sugiura, T. Iwashige, K. Tsuruta, C. Chen, S. Nagao, T. Funaki, and K. Suganuma, "Reliability evaluation of sic power module with sintered ag die attach and stress-relaxation structure," *IEEE Trans. Compon.*, *Packag., Manuf. Technol.*, vol. 9, no. 4, pp. 609–615, Apr. 2019.

- [15] A. Streibel, M. Becker, O. Muehlfeld, B. Hull, S. Sabri, D. J. Lichtenwalner, and J. Casady, "Reliability of sic mosfet with danfoss bond buffer technology in automotive traction power modules," in *Proc. PCIM Europe 2019; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management*, May 2019, pp. 1–7.

- [16] H. Wang, M. Liserre, F. Blaabjerg, P. de Place Rimmen, J. B. Jacobsen, T. Kvisgaard, and J. Landkildehus, "Transitioning to physics-of-failure as a reliability driver in power electronics," *IEEE J. Emerging Sel. Topics Power Electron.*, vol. 2, no. 1, pp. 97–114, Mar. 2014.

- [17] H. Wang, M. Liserre, and F. Blaabjerg, "Toward reliable power electronics: Challenges, design tools, and opportunities," *IEEE Ind. Electron. Mag.*, vol. 7, no. 2, pp. 17–26, Jun. 2013.

- [18] H. Du, P. Diaz Reigosa, L. Ceccarelli, and F. Iannuzzo, "Impact of repetitive short-circuit tests on the normal operation of sic mosfets considering case temperature influence," *IEEE J. Emerging Sel. Topics Power Electron.*, vol. 8, no. 1, pp. 195–205, Mar. 2020.

- [19] S. Tanimoto and H. Ohashi, "Reliability issues of sic power mosfets toward high junction temperature operation," *Physica Status Solidi A*, vol. 206, pp. 2417–2430, 2009.

[20] K. Ma, H. Wang, and F. Blaabjerg, "New approaches to reliability

- [20] K. Ma, H. Wang, and F. Blaabjerg, "New approaches to reliability assessment: Using physics-of-failure for prediction and design in power electronics systems," *IEEE Power Electron. Mag.*, vol. 3, no. 4, pp. 28– 41, Dec. 2016.

- [21] Y. Shen, A. Chub, H. Wang, D. Vinnikov, E. Liivik, and F. Blaabjerg, "Wear-out failure analysis of an impedance-source pv microinverter based on system-level electrothermal modeling," *IEEE Trans. Ind. Electron.*, vol. 66, no. 5, pp. 3914–3927, May 2019.

- [22] A. S. Bahman, K. Ma, P. Ghimire, F. Iannuzzo, and F. Blaabjerg, "A 3d-lumped thermal network model for long-term load profiles analysis in high-power igbt modules," *IEEE J. Emerging Sel. Topics Power Electron.*, vol. 4, no. 3, pp. 1050–1063, Sep. 2016.

- [23] A. S. Bahman, K. Ma, and F. Blaabjerg, "A lumped thermal model including thermal coupling and thermal boundary conditions for highpower igbt modules," *IEEE Trans. Power Electron.*, vol. 33, no. 3, pp. 2518–2530, Mar. 2018.

- [24] A. S. Bahman, F. Blaabjerg, A. Dutta, and A. Mantooth, "Electrical parasitics and thermal modeling for optimized layout design of high power sic modules," in *Proc. 2016 IEEE Applied Power Electronics Conference and Exposition (APEC)*, Mar. 2016, pp. 3012–3019.

- [25] L. Ceccarelli, R. M. Kotecha, A. S. Bahman, F. Iannuzzo, and H. A. Mantooth, "Mission-profile-based lifetime prediction for a sic mosfet power module using a multi-step condition-mapping simulation strategy," *IEEE Trans. Power Electron.*, vol. 34, no. 10, pp. 9698–9708, Oct. 2019.

- [26] S. Acharya, X. She, M. H. Todorovic, R. Datta, and G. Mandrusiak, "Thermal performance evaluation of a 1.7-kv, 450-a sic-mosfet based modular three-phase power block with wide fundamental frequency operations," *IEEE Trans. Ind. Appl.*, vol. 55, no. 2, pp. 1795–1806, Mar. 2019.

- [27] J. Lutz, H. Schlangenotto, U. Scheuermann, and R. D. Doncker, Semiconductor Power Devices: Physics, Characteristics, Reliability. Berlin, Germany: Springer, 2011.

- [28] J. Li, A. Castellazzi, M. A. Eleffendi, E. Gurpinar, C. M. Johnson, and L. Mills, "A physical rc network model for electrothermal analysis of a multichip sic power module," *IEEE Trans. Power Electron.*, vol. 33, no. 3, pp. 2494–2508, Mar. 2018.

- [29] S. Zheng, X. Du, J. Zhang, Y. Yu, and P. Sun, "Measurement of thermal parameters of sic mosfet module by case temperature," *IEEE J. Emerging Sel. Topics Power Electron.*, vol. 8, no. 1, pp. 311–322, Mar. 2020.

- [30] M. Chen, H. Wang, F. Blaabjerg, X. Wang, and D. Pan, "A temperaturedependent thermal model of silicon carbide mosfet module for longterm reliability assessment," in *Proc. 2018 IEEE 4th Southern Power Electronics Conference (SPEC)*, Dec. 2018, pp. 1–7.

- [31] R. Wu, H. Wang, K. B. Pedersen, K. Ma, P. Ghimire, F. Iannuzzo, and F. Blaabjerg, "A temperature-dependent thermal model of igbt modules suitable for circuit-level simulations," *IEEE Trans. Ind. Appl.*, vol. 52, no. 4, pp. 3306–3314, Jul. 2016.

- [32] A. Tsibizov, I. Kovačević-Badstübner, B. Kakarla, and U. Grossner, "Accurate temperature estimation of sic power mosfets under extreme operating conditions," *IEEE Trans. Power Electron.*, vol. 35, no. 2, pp. 1855–1865, Feb. 2020.

- [33] R. Wei, S. Song, K. Yang, Y. Cui, Y. Peng, X. Chen, X. Hu, and X. Xu, "Thermal conductivity of 4h-sic single crystals," *J. Appl. Phys.*, vol. 113, no. 5, p. 1–4, Feb. 2013.

- [34] T. B. Jackson, K. Y. Donaldson, and D. P. H. Hasselman, "Temperature dependence of the thermal diffusivity/conductivity of aluminum nitride," *J. Am. Ceram. Soc.*, vol. 73, no. 8, pp. 2511–2514, 1990.

- [35] D. de Faoite, D. J. Browne, F. R. Chang-Díaz, and K. T. Stanton, "A review of the processing, composition, and temperature-dependent mechanical and thermal properties of dielectric technical ceramics," *J. Mater. Sci.*, vol. 47, no. 10, pp. 4211–4235, May 2012.

- [36] R. Schnell, M. Bayer, and S. Geissmann, "Thermal design and temperature ratings of igbt modules," ABB Switzerland Ltd. Semiconductors, Fabrikstrasse 3, CH-5600 Lenzburg, Switzerland, Tech. Rep. 5SYA 2093-00, Aug. 2013.

- [37] B. Yang, J. Yuan, and Z. J. Shen, "Evaluation of lateral power mosfets in a synchronous buck converter using a mixed-mode device and circuit simulation," *IEEE Trans. Electron Devices*, vol. 58, no. 11, pp. 4004– 4010, Nov. 2011.

- [38] A. Griffo, J. Wang, K. Colombage, and T. Kamel, "Real-time measurement of temperature sensitive electrical parameters in sic power mosfets," *IEEE Trans. Ind. Electron.*, vol. 65, no. 3, pp. 2663–2671, Mar. 2018.

- [39] N. B. Nguyen, "Properly implementing thermal spreading will cut cost while improving device reliability," in *Proc. The International Symposium on Microelectronics*, 1996, pp. 383–388.

**Mengxing Chen** (S'16) received his B.E. and M.E. degrees in electrical engineering from Shandong University, Jinan, China, in 2014 and 2017, respectively. He is currently working toward the Ph.D. degree with the Department of Energy Technology, Aalborg University, Aalborg, Denmark. He was a Visiting Scientist with the Fraunhofer Institute for Reliability and Microintegration IZM, Berlin, Germany, from Jan. to Mar. 2020.

His research interests include the reliability of power electronics, Silicon Carbide (SiC) based

power converters, and multilevel converters. Mengxing Chen was the recipient of the IEEE Southern Power Electronics Conference (SPEC) 2018 Best Paper Award.

Huai Wang (M'12, SM'17) received the B.E. degree in electrical engineering, from Huazhong University of Science and Technology, Wuhan, China, in 2007 and the Ph.D. degree in power electronics, from the City University of Hong Kong, Hong Kong, in 2012. He is currently Professor with the Center of Reliable Power Electronics (CORPE), Department of Energy Technology at Aalborg University, Denmark. He was a Visiting Scientist with the ETH Zurich, Switzerland, from Aug. to Sep. 2014, and with the Massachusetts Institute of Technology (MIT), USA,

from Sep. to Nov. 2013. He was with the ABB Corporate Research Center, Switzerland, in 2009. His research addresses the fundamental challenges in modelling and validation of power electronic component failure mechanisms, and application issues in system-level predictability, condition monitoring, circuit architecture, and robustness design.

Dr. Wang received the Richard M. Bass Outstanding Young Power Electronics Engineer Award from the IEEE Power Electronics Society in 2016, and the Green Talents Award from the German Federal Ministry of Education and Research in 2014. He is currently the Chair of IEEE PELS/IAS/IES Chapter in Denmark. He serves as an Associate Editor of IET Electronics Letters, IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS, and IEEE TRANSACTIONS ON POWER ELECTRONICS.

**Donghua Pan** (S'12-M'15) received the B.S. and Ph.D. degrees in electrical engineering from Huazhong University of Science and Technology, Wuhan, China, in 2010 and 2015, respectively.

Since September 2017, he has been with Aalborg University, Aalborg, Denmark, where he is currently a Postdoctoral Fellow with the Department of Energy Technology. His research interests include magnetic integration techniques, modeling and control of grid-connected converters, and wide bandgap power conversion systems.

He was the recipient of the Outstanding Reviewer Award of IEEE TRANS-ACTIONS ON POWER ELECTRONICS in 2017 and the Best Paper Award at IEEE SPEC 2018.

Xiongfei Wang (S'10-M'13-SM'17) received the B.S. degree from Yanshan University, Qinhuangdao, China, in 2006, the M.S. degree from Harbin Institute of Technology, Harbin, China, in 2008, both in electrical engineering, and the Ph.D. degree in energy technology from Aalborg University, Aalborg, Denmark, in 2013.

12

Since 2009, he has been with the Department of Energy Technology, Aalborg University, where he became an Assistant Professor in 2014, an Associate Professor in 2016, a Professor and Research Program

Leader for Electronic Power Grid (eGrid) in 2018, and the Director of Aalborg University-Huawei Energy Innovation Center in 2020. His current research interests include modeling and control of grid-interactive power converters, stability and power quality of converter-based power systems, active and passive filters.

Dr. Wang was selected into Aalborg University Strategic Talent Management Program in 2016. He has received six IEEE Prize Paper Awards, the 2016 Outstanding Reviewer Award of IEEE TRANSACTIONS ON POWER ELECTRONICS, the 2018 IEEE PELS Richard M. Bass Outstanding Young Power Electronics Engineer Award, the 2019 IEEE PELS Sustainable Energy Systems Technical Achievement Award, and the 2019 Highly Cited Researcher by Clarivate Analytics (former Thomson Reuters). He serves as a Member at Large for Administrative Committee of IEEE Power Electronics Society in 2020-2022, and as an Associate Editor for the IEEE TRANSACTIONS ON POWER ELECTRONICS, the IEEE TRANSACTIONS ON INDUSTRY AP-PLICATIONS, and the IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS.

**Frede Blaabjerg** (S'86–M'88–SM'97–F'03) was with ABB-Scandia, Randers, Denmark, from 1987 to 1988. From 1988 to 1992, he got the PhD degree in Electrical Engineering at Aalborg University in 1995. He became an Assistant Professor in 1992, an Associate Professor in 1996, and a Full Professor of power electronics and drives in 1998. From 2017 he became a Villum Investigator. He is honoris causa at University Politehnica Timisoara (UPT), Romania and Tallinn Technical University (TTU) in Estonia.

His current research interests include power electronics and its applications such as in wind turbines, PV systems, reliability, harmonics and adjustable speed drives. He has published more than 600 journal papers in the fields of power electronics and its applications. He is the co-author of four monographs and editor of ten books in power electronics and its applications.

He has received 32 IEEE Prize Paper Awards, the IEEE PELS Distinguished Service Award in 2009, the EPE-PEMC Council Award in 2010, the IEEE William E. Newell Power Electronics Award 2014, the Villum Kann Rasmussen Research Award 2014, the Global Energy Prize in 2019 and the 2020 IEEE Edison Medal. He was the Editor-in-Chief of the IEEE TRANSACTIONS ON POWER ELECTRONICS from 2006 to 2012. He has been Distinguished Lecturer for the IEEE Power Electronics Society from 2005 to 2007 and for the IEEE Industry Applications Society from 2010 to 2011 as well as 2017 to 2018. In 2019-2020 he serves a President of IEEE Power Electronics Society. He is Vice-President of the Danish Academy of Technical Sciences too. He is nominated in 2014-2019 by Thomson Reuters to be between the most 250 cited researchers in Engineering in the world.