Aalborg Universitet

# Impact of Repetitive Short-Circuit Tests on the Normal Operation of SiC MOSFETs Considering Case Temperature Influence

Du, He; Reigosa, Paula Diaz; Ceccarelli, Lorenzo; Iannuzzo, Francesco

Published in: IEEE Journal of Emerging and Selected Topics in Power Electronics

DOI (link to publication from Publisher): 10.1109/JESTPE.2019.2942364

Publication date: 2020

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Du, H., Reigosa, P. D., Ceccarelli, L., & lannuzzo, F. (2020). Impact of Repetitive Short-Circuit Tests on the Normal Operation of SiC MOSFETs Considering Case Temperature Influence. *IEEE Journal of Emerging and Selected Topics in Power Electronics*, 8(1), 195-205. [8844745]. https://doi.org/10.1109/JESTPE.2019.2942364

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

? You may not further distribute the material or use it for any profit-making activity or commercial gain

? You may freely distribute the URL identifying the publication in the public portal ?

### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

He Du, Student Member, IEEE, Paula Diaz Reigosa, Member, IEEE, Lorenzo Ceccarelli, Student Member, IEEE, and Francesco Iannuzzo, Senior Member, IEEE

Abstract—This paper presents the impact of repetitive shortcircuit tests on the normal operation of a commercial Silicon Carbide (SiC) MOSFET and the influence of different case temperatures on the short-circuit degradation process. To ensure repeatable short-circuit test conditions, the maximum shortcircuit withstanding time is studied at three different case temperatures, and the critical energy is identified. In order to investigate the effect of short-circuit stress on the normal operation, the static and dynamic characteristics are periodically measured along with repetitive short-circuit activity. The turn-on switching loss increases gradually with the increasing number of repetitive short-circuit tests. This is associated with the increase of the gate leakage current during the short circuit tests, which shows a reduction of the on-state gate voltage because of the gate oxide degradation. Then, since the case temperature of the device is subject to the operating condition in the application, the degradation process of repetitive short-circuit tests with respect to different case temperatures are investigated, and the relationship between the number of repetitions to failure and the initial case temperature is established. Finally, the case temperature influence is explained by a 1-D transient thermal model based on the shortcircuit condition.

*Index Terms*—Temperature, degradation, power MOSFET, short circuit, Silicon Carbide, switching characteristics.

#### I. INTRODUCTION

**S** ILICON Carbide (SiC) power semiconductor devices are becoming more and more attractive in power electronics applications, e.g., electric vehicles, railway traction, and power grids, thanks to their superior physical properties over siliconbased devices [1] [2]. The higher breakdown electric field strength, thermal conductivity and carrier velocity provide the capability for SiC devices in faster switching, higher voltage and higher temperature operations [3] [4]. Therefore, the reliability of SiC MOSFETs becomes critical in order to meet the long-term application requirement, especially the reliability under abnormal operating conditions, such as overcurrent, overvoltage, Unclamped Inductive Switching (UIS) [5] and Short Circuit (SC) [6]. Among these, the SC conditions receive extensive attention since the device withstands both high voltage and high current at the same time.

Due to the smaller chip size and thinner gate oxide, the robustness of SiC MOSFETs regarding the SC condition is lower than their Si counterparts [7] [8]. So far, two chip-related failure mechanisms under SC conditions have been found [9]. Thermal instability is one of them; during a single SC event, a high-energy pulse is dissipated in a relatively short time, and the internal temperature increases well above the rated limits. The drain leakage current, caused by the drift of thermally generated carriers, could trigger positive temperature feedback when it achieves a considerable value and eventually leads to the thermal runaway [10] [11]. The other main observed failure mechanism is the gate oxide damage. The gate oxide thickness needs to be thinner due to the larger bandgap of the SiC material, and therefore the gate structure is fragile [12]. The leakage current from gate to source, generated by the creation of conductive paths, is increased by the high electric field and high temperature [7] [13]. In [14], four possible different conductive paths have been identified.

On the other hand, the failure mechanism is dependent on the amount of dissipated SC energy [10]. The influence of the gatesource voltage, DC-link voltage, gate resistance, and pulse time duration on the SC energy have been investigated in [15]. Since an undesirable SC fault may occur in a variety of ways during the lifetime of the devices and at least 2 µs is needed for the commercial drivers to react, the repetitive SC tests could reflect the impact of a single SC event and also provide more insights about the degradation process [16] [17]. With the aid of repetitive SC tests, aging indicators can be explored comprehensively. The shift of the gate threshold voltage, the reduction of the gate-drain capacitance and the increase of the gate leakage current, drain leakage current and on-state resistance [7] [18]-[21] have been proposed as the indicators to evaluate the degradation after repetitive SC events. However, the effect of SC events on the normal operation of SiC MOSFETs, especially on switching performance, needs to be taken into account.

At the same time, the case temperature of the device, which is subject to the operating conditions or real application scenarios, needs to be considered. In [10] and [22], the temperature-dependent SC capability and robustness are

Manuscript received May 29, 2019; revised August 31, 2019; accepted September 7, 2019.

He Du, Lorenzo Ceccarelli and Francesco Iannuzzo are with the Department of Energy Technology, Aalborg University, Aalborg 9220, Denmark (e-mail:

hdu@et.aau.dk; lce@et.aau.dk; fia@et.aau.dk). Paula Diaz Reigosa is with the University of Applied Sciences Northwest Switzerland (e-mail: paula.diazreigosa@fhnw.ch).

analyzed, which is limited by the heat-generated leakage current and related to thermal runaway [23]. The gate-oxide damage is also observed by the failure analysis after SC test at 150 °C [24]. However, the impact of different case temperatures on the SC degrading process still needs to be investigated.

In this context, the aim of this paper is to analyze the effect of repetitive SC tests on the electrical performances of 1000 V/22 A discrete SiC MOSFETs at different case temperatures with 3<sup>rd</sup>-generation planar technology. This work mainly focuses on the variation of static and dynamic characteristics and the influence of case temperature on the number of SC repetitions until failure. The paper is organized as follows:

After an introduction, in Section II, the SC test setup for SiC MOSFETs is presented and the maximum SC withstanding time with respect to different initial case temperatures are presented. In Section III, the repetitive SC tests are performed at room temperature combined with static and dynamic characterizations. Several aging indicators, including gate leakage current and on-state resistance, have been analyzed in detail. The relationship between the on-state gate-source voltage during SC tests and the gate leakage current measured is verified. The switching waveforms and losses are obtained by the standard Double Pulse Tests (DPT). Section IV presents the repetitive SC tests at different initial case temperatures. The gate-source voltage, which is related to the gate leakage current, is used as an aging indicator. A relationship between the number of SC repetitions  $(N_{\rm SC})$  and the case temperature is presented in the same section as well. Finally, in order to understand the impact of case temperature on the gate degradation, the chip temperature evolution during SC tests are simulated. Section IV draws the conclusions.

#### II. SHORT-CIRCUIT AGING TEST

# A. Configuration of Experimental Setup

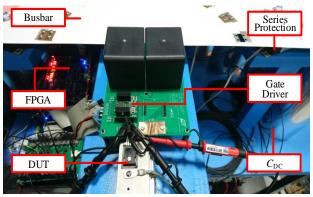

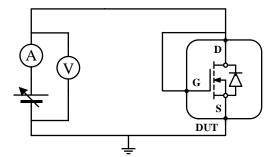

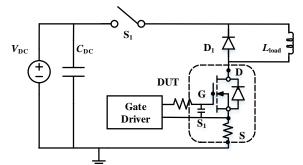

A Non-Destructive Tester (NDT) has been built for the SC tests with DC-bus voltage and current limits of 2.4 kV and 10 kA [25]. The basic schematic of the NDT and its appearance are shown in Fig. 1 and Fig. 2, respectively. The needed energy for SC tests is provided by a high voltage power supply  $(V_{DC})$  and a high-power capacitor bank ( $C_{\rm DC}$ ). The series protection consists of four paralleled IGBT power modules to ensure high current capability and at the same time interrupt the SC current immediately after the pulse in order to avoid the device destruction and allow for post-failure analysis. The busbar is custom-designed for even current distribution and the stray inductance is about 10 nH. The control signals to the gate drivers for both series protection and the Device Under Test (DUT) are provided by a 100 MHz Field-Programmable Gate Array (FPGA) board. A commercial SiC MOSFET isolated gate driver by CREE is used and the gate-source voltage is set to +15 V/-4 V. During the SC tests, drain-source voltage, drain current and gate-source voltage waveforms are measured by means of the HDO6054-MS oscilloscope with the high voltage probe (LeCroy PPE 2 kV), Rogowski coil current probe (PEM CWT6), and the passive voltage probe (LeCroy PP018), respectively.

The DUT is a 1000 V/ 22A discrete SiC MOSFET with 3<sup>rd</sup> generation planar technology (CREE C3M0120100K) [26] and it has separate Kelvin source pin (TO-247-4) to ensure low

2

Fig. 1. Principle schematic of the Non-Destructive Tester (NDT).

Fig. 2. Appearance of NDT with DUT and PCB adaptor.

common-source inductance package. Initially, the matched fresh devices, which have similar initial static characteristics, especially threshold voltage ( $V_{\text{th}}$ ) and output characteristics ( $I_{\text{D}}V_{\text{DS}}$ ), are selected to ensure the similar SC energies under the same SC conditions. Then, they are used as the DUTs and numbered from S<sub>1</sub> to S<sub>9</sub>. Besides, a temperature controller and electrical heater are used to investigate the impact of different initial case temperatures and an isolated Thermal Interface Material (TIM) is used between the DUT and heating plate during the SC tests. Since the drain-source voltage ( $V_{\text{DS}}$ ) is clamped to the DC-bus voltage during the SC test, the impact of output capacitance ( $C_{\text{OSS}}$ ), which is always charged, could be negligible.

# B. Temperature-Dependent Maximum SC Withstanding Time

The maximum SC withstanding time is experimentally investigated at different initial case temperatures for the three fresh devices, which have similar static characteristics ( $S_1$ ,  $S_2$ , and  $S_3$ ). The results help to identify the critical energy and make sure that the selected testing conditions for the repetitive aging SC tests are below critical SC energy.

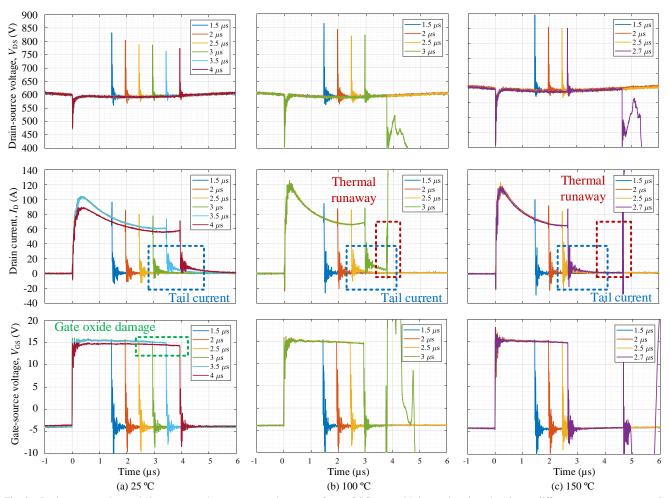

The SC waveforms under a bias voltage of 600 V with increasing pulse time duration at three case temperatures (i.e.  $T_{\rm C} = 25$  °C, 100 °C, and 150 °C) are shown in Fig. 3. At 25 °C case temperature, the reduction of the gate-source voltage appears when the pulse time duration increases to 4 µs, indicating a gate oxide damage. On the other hand, it can be observed in the blue dotted boxes that a tail current appears at turn-off for the SC pulse durations larger than 2.5 µs at each case temperature. This phenomenon is in agreement with previous work [9], and its mechanism is also confirmed in [11] and [20]. The high temperature within the depletion region

#### JESTPE-2019-05-0427.R1

leads to a thermal generation current flowing across the device junction. If the leakage current is high enough, a thermal runaway mechanism might be triggered [22]. As can be seen in the red dotted boxes in Fig. 3 (b) and (c), the devices fail after turning off, which confirms the thermal runaway mechanism.

The SC withstanding time duration decreases from 4  $\mu$ s to 3  $\mu$ s and then 2.7  $\mu$ s when the initial case temperature increases from 25 °C to 100 °C and 150 °C. The SC energy is calculated when the failure is observed, being 0.15 J, 0.13 J to 0.12 J with increasing case temperature. The summary of the SC tests with increasing time duration at different case temperatures is listed in Table I.

#### III. STATIC AND DYNAMIC CHARACTERISTICS VARIATIONS

# A. Static Characteristics Variations

In order to evaluate the impact of repetitive SC tests on the static characteristics in the normal operation, another fresh DUT ( $S_4$ ) is firstly investigated with the static characterization between repetitive SC tests by means of the Power Device Analyzer (Keysight B1506A).

With the aim of performing the repetitive SC tests below the maximum SC critical energy, the testing conditions are set to  $V_{DC} = 600 \text{ V}$ ,  $t_{SC} = 2.2 \text{ } \mu \text{s}$  and  $T_C = 25 \text{ }^\circ\text{C}$ . The output voltage of the gate driver is fixed to +15 V/ -4 V during the repetitive SC

TABLE I

SUMMARY OF SC TESTS WITH INCREASING TIME DURATION AT DIFFERENT

| _ |                | CASE TEMPERATURES |              |          |                   |  |

|---|----------------|-------------------|--------------|----------|-------------------|--|

| _ |                | Case              | SC           | Critical |                   |  |

|   | No.            | temperat          | withstanding | energy   | Failure mode      |  |

| _ |                | ure (°C)          | time (µs)    | (J)      |                   |  |

|   | $S_1$          | 25                | 4            | 0.15     | Gate oxide damage |  |

|   | $\mathbf{S}_2$ | 100               | 3            | 0.13     | Thermal runaway   |  |

| _ | $S_3$          | 150               | 2.7          | 0.12     | Thermal runaway   |  |

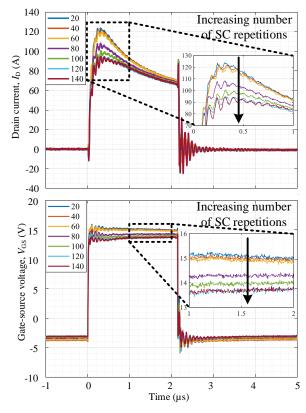

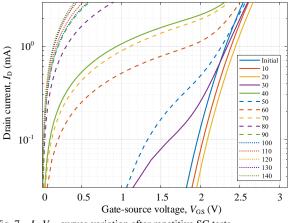

tests, and the gate resistance is equal to 20  $\Omega$ , which dampens the oscillation when the device turns off. Initially, the static characteristics, including threshold voltage ( $V_{\text{th}}$ ), gate leakage current ( $I_{\text{GSS}}$ ), drain leakage current ( $I_{\text{DSS}}$ ) and on-state resistance ( $R_{\text{DS,on}}$ ) are measured on the fresh device. Then, the repetitive SC tests are performed, and the drain-source voltage ( $V_{\text{DS}}$ ), gate-source voltage ( $V_{\text{GS}}$ ) and drain current ( $I_{\text{D}}$ ) waveforms are recorded during SC tests. Every 10 SC repetitions, the static characterizations are performed again. The drain current and gate-source voltage waveforms from the 20<sup>th</sup> to 140<sup>th</sup> repetition are shown in Fig. 4. A reduction of the on-state gate-source voltage and on-state drain current are observed with the increasing number of repetitions. This phenomenon could be explained by the gate oxide degradation mechanism; the conductive paths, which are formed through the

Fig. 3. Drain-source voltage, drain current and gate-source voltage waveform of SC tests with increasing time duration at different case temperatures. In the blue dotted boxes, tail currents are highlighted. The gate oxide damage and thermal runway are marked in the green and red dotted boxes, respectively.

4

JESTPE-2019-05-0427.R1

gate oxide during the SC tests lead to a gradually increasing gate leakage current ( $I_{GSS}$ ) and eventually cause a permanent gate oxide damage. At the same time, the considerable  $I_{GSS}$ forms a voltage drop across the gate resistance, which decreases the effective gate voltage on the device during on-state operation. It is shown as the reduction of on-state  $V_{GS}$  during the SC tests and leads to the SC drain current  $I_D$  decrease. Therefore, the effective gate voltage ( $V_{GS}$ ) can be expressed by the output voltage of the gate driver ( $V_{driver}$ ), external gate resistance ( $R_G$ ) and gate leakage current ( $I_{GSS}$ ) as (1).

$$V_{\rm GS} = V_{\rm driver} - R_{\rm G} \times I_{\rm GSS} \tag{1}$$

The variation of on-state  $V_{GS}$  and  $I_D$  during SC test is also in agreement with the results in [27], which is related to the degradation of the gate structure.

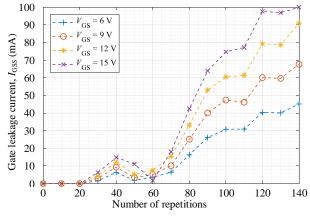

The results of the gate leakage current measured with the power device analyzer in Fig. 5 confirm the gate degradation. After 30 SC repetitions, the gate leakage current jumps from 4.87 pA (after 20 SC repetitions) to 6.33 mA when the  $V_{GS}$  is equal to 15 V. The  $I_{GSS}$  increases significantly after 40 SC repetitions and decreases again after 50 SC repetitions, which might be affected by the electrons de-trapping mechanism [28] [29]. Thereafter, it increases gradually from the 50<sup>th</sup> repetition, and the SC tests stopped after 140 repetitions when the maximum gate leakage current reaches 100 mA.

The threshold voltage ( $V_{\text{th}}$ ) is measured with the power device analyzer (Keysight B1506A), and the connection diagram is shown in Fig. 6. Since the gate and drain terminals are connected together internally while measuring  $V_{\text{th}}$ , the effect

Fig. 4. Drain current and gate voltage waveforms of repetitive SC tests from 20<sup>th</sup> to 140<sup>th</sup> repetition at room temperature.

of the gate leakage current needs to be considered.

Fig. 7 shows the variation of  $I_{\rm D}$ - $V_{\rm GS}$  curves every 10 repetitions, and it can be divided into three stages. From the initial state to the 20<sup>th</sup> repetition, the threshold voltage shifts positively. This phenomenon can be explained by the electrons trapping. When a positive bias is applied to the gate, the electric field stress across the oxide is very high because of the small gate oxide thickness. The electrons at the strongly inverted surface tunnel into or through the gate oxide (i.e. the SiO<sub>2</sub> layer between substrate and polysilicon). This mechanism is named Fowler-Nordheim tunnelling, and it is explored in detail in [7] [30]. Therefore, an increase in the net negative charge (i.e. electron trapping) could result in a positive shift of the threshold voltage and the threshold voltage can be expressed as [31]:

Fig. 5. Gate leakage current increases after repetitive SC tests.

Fig. 6. The connection diagram of  $V_{\rm th}$  measurement by Keysight B1506A.

Fig. 7. ID-VGS curves variation after repetitive SC tests.

JESTPE-2019-05-0427.R1

$$\begin{cases} Q_{\text{ox}} = Q_{\text{T}} + Q_{\text{m}} + Q_{\text{I}} + Q_{\text{F}} \\ V_{\text{th}} = V_{\text{thi}} - \frac{Q_{\text{ox}}}{c_{\text{ox}}} \end{cases}$$

(2)

Where  $V_{\text{thi}}$  is the initial threshold voltage,  $Q_{\text{ox}}$  is the charges in gate oxide, and  $C_{ox}$  is the specific capacitance of the gate oxide layer. The oxide contains four types of positive charges: trapped oxide charge ( $Q_{\text{T}}$ ), mobile charge ( $Q_{\text{m}}$ ), fixed oxide charge ( $Q_{\text{F}}$ ) and interface state charge ( $Q_{\text{I}}$ ).

In the second stage of Fig. 7, the drain current increases gradually with the increasing  $V_{GS}$  after 30 repetitions. Since the gate and drain terminals are connected together, this phenomenon shows that a conductive path inside the gate oxide has been formed. In this case, a small current going through the gate oxide contributes to the  $I_D$  and the threshold voltage cannot be obtained accurately in this way. The last stage starts from the 80<sup>th</sup> repetition to the 140<sup>th</sup> repetition and the curves indicate that the gate oxide conductivity increases gradually.

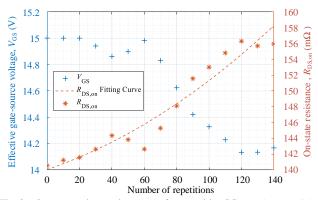

The on-state resistance is calculated by the output characteristics ( $I_{\rm D}$ - $V_{\rm DS}$ ) when the  $V_{\rm GS,set}$  is set to 15 V and  $I_{\rm D}$  is equal to 15 A. In Fig. 8, the  $R_{\rm DS,on}$  increases with the increasing number of repetitions and this could be explained by the positive threshold voltage shift and the effective gate-source voltage reduction as mentioned above. From the initial state to the 20<sup>th</sup> repetition, the effective  $V_{\rm GS}$  remains as 15 V and  $R_{\rm DS,on}$  increases owing to the positive  $V_{\rm th}$  shift. Thereafter, the effective  $V_{\rm GS}$  applied on the device becomes lower than its settings value (i.e.  $V_{\rm GS} < V_{\rm GS,set} = 15$  V), which could lead to further increase in  $R_{\rm DS,on}$ . Besides, the reduced mobility from increased oxide charge scattering might be another factor, and it needs to be further investigated.

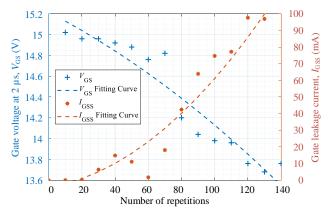

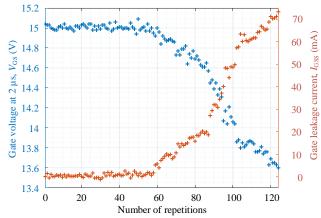

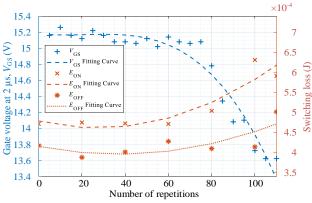

An obvious correlation between the on-state gate-source voltage during SC tests and the gate leakage current is obtained. Fig. 9 shows the reduction of the on-state gate-source voltage at 2  $\mu$ s and the increase of the gate leakage current, measured by means of static characterization, with the number of SC repetitions increasing. The SC tests are stopped at 140<sup>th</sup> repetition when the maximum gate leakage current increases up to 100 mA, and in this case, the minimum gate-source voltage at 2  $\mu$ s is equal to 13.6 V, which is decreased by 9.3 % if compared to 15 V. Since the gate oxide degradation has also been observed on the other types of commercial SiC MOSFETs [7] [15], the reduction of  $V_{GS}$  could be considered as an aging indicator and the reduced value needs to be further confirmed for the other devices.

Furthermore, another fresh DUT (S<sub>5</sub>) is used to monitor the  $I_{\rm G}$  variation during repetitive SC tests in order to confirm the increasing gate leakage current during repetitive SC tests and ensure the gate oxide degradation at the same time. In this case, another voltage probe is placed before the external  $R_{\rm G}$  (20  $\Omega$ ) and the voltage drop on the  $R_{\rm G}$  can be measured during SC tests. Then the gate current  $I_{\rm G}$  during SC tests can be calculated with the  $R_{\rm G}$  and the measured voltage drop across the  $R_{\rm G}$ . Fig. 10 shows the relationship between the average  $I_{\rm GSS}$  (from  $t = 1 \,\mu$ s to 2  $\mu$ s) and the on-state  $V_{\rm GS}$  at 2  $\mu$ s. When the  $V_{\rm GS}$  at 2  $\mu$ s decreases to 13.6 V, the repetitive SC tests are stopped after 124 SC repetitions, and the  $I_{\rm GSS}$  is equal to 73.34 mA. Thereafter, the  $I_{\rm GSS}$  is also measured with the power device analyzer, and it reaches 100 mA when the  $V_{\rm GS}$  is 12.3 V. Therefore, the on-state

Fig. 8. On-state resistance increases after repetitive SC tests ( $V_{GS,set} = 15$  V and  $I_D = 15$  A) and the effective gate-source voltage ( $V_{GS}$ ) decreases, measured at the same time by static characterization.

Fig. 9. Correlation between the on-state gate voltage ( $t = 2 \mu s$ ) during SC tests and the gate leakage current, measured by static characterization ( $V_{GS,set} = 15 V$ ) (S<sub>4</sub>).

Fig. 10. Correlation between the on-state gate voltage ( $t = 2 \ \mu s$ ) and the average gate leakage current during SC tests (S<sub>5</sub>).

gate voltage at 2  $\mu$ s during SC tests (nearly at the end of the pulse time duration) is selected as the aging indicator in order to evaluate the degradation process in the following tests.

### **B.** Dynamic Characteristics Variations

The SC robustness of power semiconductor devices is typically assessed on fresh components; however, a SC event could occur several times along the life of the component

6

JESTPE-2019-05-0427.R1

during normal operation and its effect on the normal operation of the device can be quite different, depending on the level of degradation. Therefore, in this section, Double-Pulse Tests (DPT) are combined together with repetitive SC tests for the fresh DUT ( $S_6$ ) in order to investigate the degradation of the normal operation of the SiC MOSFET after repetitive SC tests.

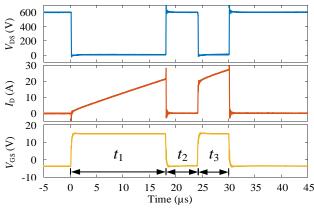

The schematic of the standard DPT is shown in Fig. 11 [32]. A 1.2 kV / 20 A SiC Schottky diode ( $D_1$ ) is used as the freewheeling diode and the inductance of load is equal to 620  $\mu$ H. The DUT is driven by a +15 V/ -4 V gate voltage, and the used gate resistance and capacitance are equal to 20  $\Omega$  and 4.7 nF in order to slow down the switching and mitigate the parasitic inductance in the gate loop, which might cause the oscillation during switching DPT and the first pulse time ( $t_1$ = 18  $\mu$ s) is used to increase the current to its rated value. Then, there is a delay of 6  $\mu$ s ( $t_2$ ) between the first and second pulse for the device to settle out. The second narrow pulse time ( $t_3$ ) is set to 6  $\mu$ s and the SC aging test condition is set the same as before ( $V_{DC} = 600 \text{ V}$ ,  $t_{SC} = 2.2 \ \mu$ s and  $T_C = 25 \ ^{\circ}C$ ).

Initially, the standard DPT is performed on a fresh device  $(S_6)$  and the drain-source voltage, gate-source voltage and drain current waveforms are measured. Then the repetitive SC tests are performed and after each 20 SC repetitions, the DPT is carried out again to analyze the impact of SC aging stress on the dynamic characteristics. The SC tests stop at 110<sup>th</sup> SC repetition when the on-state  $V_{GS}$  at 2 µs during SC test, i.e. the aging indicator, decreases to 13.6 V. Thereafter, the last DPT is performed on the degraded device after 110 repetitions.

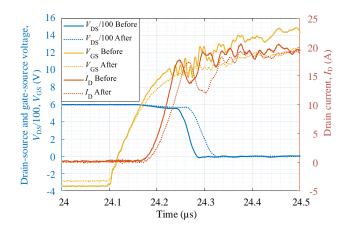

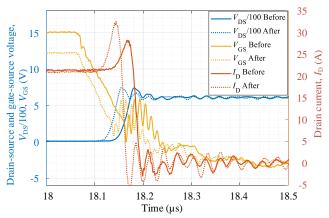

The  $V_{\text{DS}}$ ,  $V_{\text{GS}}$ , and  $I_{\text{D}}$  waveforms during turn-on and turn-off transitions before and after 110 repetitions of SC tests (i.e. the

Fig. 11. Principle schematic of the standard Double Pulse Test (DPT).

Fig. 12. Drain-source voltage, drain current and gate-source voltage waveform of Double Pulse Test.

initial and the last one) are shown in Fig. 13 and Fig. 14, separately. After repetitive SC aging tests, the device turns on slower and turns off faster than before. This phenomenon could be explained by the reduction of the effective gate-source voltage  $V_{\text{GS}}$ .

During turn-on transient, no  $I_D$  flows through the device until  $V_{GS}$  exceeds  $V_{th}$ . Due to the reduction of the effective  $V_{GS}$  after SC tests, it takes longer time to reach  $V_{th}$ , which leads to the increased delay of  $I_D$ . When  $V_{GS}$  is larger than  $V_{th}$ ,  $I_D$  is given by (3) [33].

$$I_{\rm D}(t) = g_{\rm m} [V_{\rm G}(t) - V_{\rm th}] = \frac{\mu_{\rm ni} C_{\rm ox} Z}{2L_{\rm CH}} [V_{\rm G}(t) - V_{\rm th}]^2 \quad (3)$$

Where  $g_m$  is the transconductance of the device,  $\mu_{ni}$  is the inversion layer mobility,  $C_{OX}$  is the specific capacitance of the gate oxide,  $L_{CH}$  is the channel length, and Z is the equivalent channel width. At the same time *t*, the lower effective  $V_{GS}$  results in the lower  $I_D$ , which is in agreement with the waveform in Fig. 13. On the other hand, the reduction of mobility and the increased scattering from trapped charges might cause the reduction in transconductance. Further investigations are needed on this point. Similarly, during the turn-off transient, the effective  $V_{GS}$  after SC tests needs less time than before to decrease to  $V_{th}$ , and thus the  $I_D$  starts to decrease earlier in Fig. 14.

Fig. 13. Drain-source voltage and drain current waveforms during turnon time before and after 110 repetitions of SC tests.

Fig. 14. Drain-source voltage and drain current waveforms during turnoff time before and after 110 repetitions of SC tests.

#### JESTPE-2019-05-0427.R1

Fig. 15 shows the reduction of on-state gate-source voltage and the variation of switching loss with increasing number of SC repetitions. The turn-on loss increases after 80 SC repetitions because of the delay of turn-on  $V_{DS}$ , which is similar to [34], and it is in agreement with the reduction of the aging indicator ( $V_{GS}$  at 2 µs). Meanwhile, the turn-off loss variation induced by the SC stress is not obvious and it only increases slightly at the end of repetitions due to the higher current spike during turn-off transition.

# IV. IMPACT OF CASE TEMPERATURE ON SHORT-CIRCUIT AGING

# A. Repetitive SC Tests at Different Temperatures

The repetitive SC tests are performed with 600 V bias voltage and 2.2 µs pulse time duration at 25 °C, 100 °C, and 150 °C for the three fresh DUTs (S<sub>7</sub>, S<sub>8</sub>, and S<sub>9</sub>), which have matched static characteristics, in order to investigate the impact of different case temperatures. The gate resistance used on the driver board is equal to 6.67  $\Omega$ , and the output voltage of the gate driver is fixed as +15 V/-4 V.

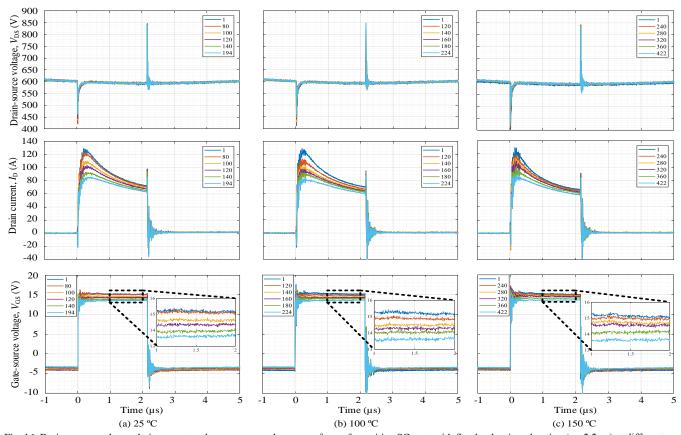

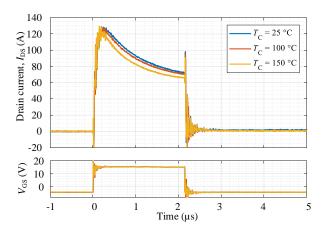

Fig. 16 presents the drain-source voltage, drain current, and gate-source voltage waveforms at different temperatures, and the gate oxide degradation similar to Fig. 4 is observed in each case; the on-state gate voltage and drain current decreases with the number of SC repetitions increasing, which indicates the increase of gate leakage current.

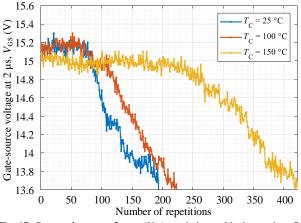

The experimental results obtained in Fig. 9 shows that when the on-stage gate-source voltage decreases from 15 V to 13.6

7

Fig. 15. The reduction of gate-source voltage and the variation of switching loss with the increasing number of repetitions.

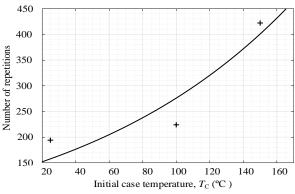

V, the device could be considered as a failed device; therefore, this criterion is considered for the following repetitive SC tests. The  $V_{\rm GS}$  variation (at 2 µs) with increasing repetitions at 25 °C, 100 °C, and 150 °C are shown in Fig. 17. The number of repetitive SC tests until failure ( $N_{\rm SC}$ ) increases from 194 repetitions (25 °C) to 224 repetitions (100 °C), and then to 422 repetitions (150 °C) with the case temperature increase. The relationship between the number of repetitions to failure and the initial case temperature is presented in Fig. 18, and it could be fitted as (4).

$$W_{\rm SC} = f(T_{\rm c}) = 130.9 \times \exp(0.007457 \times T_{\rm c})$$

(4)

Fig. 16. Drain-source voltage, drain current and gate-source voltage waveform of repetitive SC tests with fixed pulse time duration ( $t = 2.2 \ \mu s$ ) at different case temperatures.

Fig. 17. Gate voltage at 2  $\mu$ s ( $V_{GS}$ ) variation with increasing SC repetitions at different case tempeatures.

Fig. 18. Relationship between the number of repetitions to failure and the case temperature.

One may think that the increasing case temperature could lead to earlier failures; however, this is not the case for SiC MOSFETs, since the drain current decreases with temperature due to its negative temperature coefficient, leading to lower SC energies.

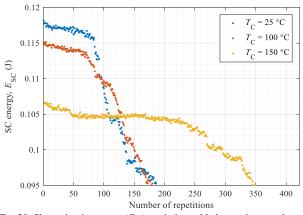

As can be seen in Fig. 19, the gate-source voltage during the first SC test at different case temperature keeps the same value. The drain current during the first SC test at 150 °C case temperature is the lowest one, and the drain current at 25 °C is higher than 100 °C. The SC energy from  $t = 0 \ \mu s$  to 2.2  $\mu s$  is also calculated for each repetition of SC tests with respect to different case temperatures, as shown in Fig. 20. In the first stage (SC tests within 100 repetitions), the SC energy at 25 °C case temperatures is higher than 100 °C and 150 °C, and all the calculated values are below 0.12 J, which is the critical energy at 150 °C. Thereafter, when more than 100 repetitions are performed, the SC energy reduction is mainly determined by the reduced drain current caused by gate degradation.

# B. Thermal Behavior Simulation of SC Tests

In order to investigate how the higher SC energy results in the less number of SC repetitions to failure, the thermal behavior during SC test is considered. Since the very fast temperature transient during SC operation (i.e.  $t = 2.2 \ \mu$ s) cannot be easily approached in measurement, a thermal simulation is performed to estimate the transient temperature. Therefore, a 1-D heat propagation model is used to analyze the

8

Fig. 19. Drain current and gate-source waveforms during the 1<sup>st</sup> repetition SC test at different case temperatures.

Fig. 20. Short-circuit energy ( $E_{SC}$ ) variation with increasing number of SC repetitions at different case temperatures (25 °C, 100 °C and 150 °C).

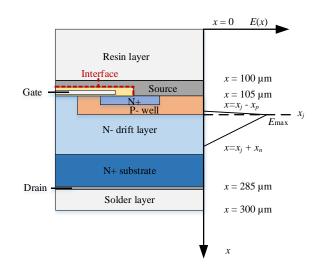

thermal behavior during SC test at different initial case temperatures as shown in Fig. 21.

The estimated doping concentration in the N- drift layer is 1 × 10<sup>16</sup> cm<sup>-3</sup> and the junction depth is 0.6  $\mu$ m ( $x_j = 105.6 \mu$ m). The depletion width in the P-well layer ( $x_p$ ) is omitted in the model due to the negligible thickness. The width in the N- drift layer ( $x_n$ ) can be calculated by (5) where  $\varepsilon_s$  is the dielectric constant of SiC,  $N_d$  is the doping concentration in the N-drift region,  $V_{ds}$  is the applied voltage during SC test and q is the electron charge [35].

$$x_n \approx \sqrt{\frac{2\varepsilon_{\rm s}}{qN_{\rm d}}} V_{\rm ds} \tag{5}$$

The distribution of the electric field density in this region  $(x_i \le x \le x_n)$  is calculated by (6).

$$E(x) = \frac{qN_{\rm d}}{\varepsilon_{\rm s}} \left( x_{\rm n} + x_{\rm j} - x \right) \tag{6}$$

During SC tests, the  $V_{DS}$  bias is applied, and the on-state drain current goes through the device at the same time. The SC current density J(t) is obtained by the active chip area A and the time-dependent SC current  $I_{SC}(t)$ , which is derived from the actual SC waveform. Since the  $V_{DS}$  changes slightly during the

JESTPE-2019-05-0427.R1

SC test, the heat generation rate Q(x, t) can be calculated by (7).

$$Q(x,t) = E(x) \cdot \frac{I_{SC}(t)}{A}$$

(7)

Therefore, the classical heat equation in (8) can be solved in the model to simulate the temperature distribution in terms of time.

$$\frac{\partial}{\partial x} \left( \lambda(T) \cdot \frac{\partial T}{\partial x} \right) + Q(x,t) = \rho \cdot c(T) \cdot \frac{\partial T}{\partial t}$$

(8)

$\lambda$ ,  $\rho$  and *c* are the thermal conductivity, physical density and specific heat of each material, respectively. Their settings in SiC material are listed as below (9)-(11) [36] and the parameters in other materials (i.e. resin, Al and solder layer) are included in Table II.

$$\lambda(T)_{\rm SiC} = (0.0003 + 1.05 \times 10^{-5}T)^{-1} \ (W/m \cdot K) \ (9)$$

$$\rho_{\rm SiC} = 3.211 \ (g/\rm{cm}^3) \tag{10}$$

$$c(T)_{\text{SiC}} = 925.65 + 0.3772T - 7.929 \times 10^{-5}T^2 - 3.1946 \times 10^7/T^2 \text{(J/kg \cdot K)}$$

(11)

During the simulation, the time (*t*) increases from 0 µs to 2.2 µs in step of 4 ns and  $V_{DS}$  is set to 600 V, which are the same as the actual test in part A. The active chip area A is estimated by the measured chip size. The experimental drain current waveform during the first repetitive SC test at different case temperatures in Fig. 19 are used as  $I_{SC}(t)$  in the model, in order to obtain an accurate heat generation rate. The temperature boundaries of both top ( $x = 0 \mu m$ ) and bottom sides ( $x = 300 \mu m$ ) in the 1-D model are set the same as the corresponding initial case temperatures due to the extreme short SC time duration.

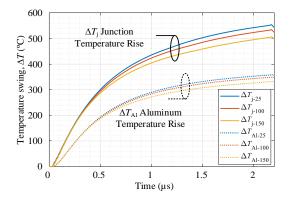

Fig. 22 shows the simulation results of the temperature variation ( $\Delta T = T$ -  $T_{case}$ ) at different initial case temperatures ( $T_{case} = 25$  °C, 100 °C, and 150 °C). The maximum junction temperature rise ( $\Delta T_j$ ) decreases from 554.1 °C to 534.8 °C and then to 506.7 °C when the case temperature increases from 25 °C to 100 °C and to 150 °C.

This result is coherent with the fact that at higher initial

TABLE II Thermal Behavior Simulation Specifications

| Parameter               | Value                                 | Unit              |

|-------------------------|---------------------------------------|-------------------|

| $\mathcal{E}_{s}$       | $9.66\times8.85\times10^{\text{-12}}$ | F/m               |

| A                       | 3.478                                 | cm <sup>2</sup>   |

| $\lambda_{	ext{Resin}}$ | 0.2                                   | $W/(m \cdot K)$   |

| $ ho_{ m Resin}$        | 1.8                                   | g/cm <sup>3</sup> |

| $c_{\text{Resin}}$      | 1000                                  | $J/(kg \cdot K)$  |

| $\lambda_{ m Al}$       | 167                                   | W/(m·K)           |

| $ ho_{ m Al}$           | 2.7                                   | g/cm <sup>3</sup> |

| $c_{\mathrm{Al}}$       | 900                                   | $J/(kg \cdot K)$  |

| $\lambda_{ m Solder}$   | 50                                    | W/(m·K)           |

| $ ho_{ m Solder}$       | 7.4                                   | g/cm <sup>3</sup> |

| C <sub>Solder</sub>     | 190                                   | $J/(kg \cdot K)$  |

Fig. 21. Heat propagation model (1-D) of the SiC MOSFETs.

Fig. 22. Simulated junction temprature rise and alumuinum temperature rise at three different case temperatures (25 °C, 100 °C and 150 °C).

temperatures, the drain current is lower, yielding a reduced SC energy and it indicates that the gate degradation under repetitive aging SC test is mainly related to the temperature variation rather than the maximum junction temperature. Due to the different Coefficient of Thermal Expansion (CTE) between the Aluminum and SiO<sub>2</sub> layer, there would be a mismatch on the interface between the materials, which is shown as the red dotted line in Fig. 21. With the number of short-circuit repetitions increasing, the cracks might appear through the SiO<sub>2</sub> layer. This hypothesis is in agreement with the crack measured by Magnified Focused-Ion-Beam (FIB) after short-circuit stress in [37].

Besides, the Coffin-Manson law is usually used for the temperature cycling condition in order to investigate the bond wire and solder pad degradation. The expected number of cycles to failure  $N_{\rm f}$  at a given temperature swing  $\Delta T_{\rm j}$  and an average temperature  $T_{\rm m}$  can be estimated with the equation

$$N_{\rm f} = A \cdot \Delta T_{\rm j}^{\alpha} \cdot \exp(\frac{E_{\rm a}}{K_{\rm B} \cdot T_{\rm m}}) \tag{7}$$

Where  $K_{\rm B}$  is the Boltzmann constant,  $E_{\rm a}$  is the activation energy, and  $\alpha$  and A are the parameters. If the Coffin-Manson law is used for the Al/SiO<sub>2</sub> interface with typical values of power semiconductor packaging (i.e.  $\alpha = -4$ ,  $\Delta T_{\rm j} = 20$  K and  $N_{\rm f}$ = 1×10<sup>6</sup>), the expected number of SC repetitions to failure is

equal to few units since the temperature swing is very high ( $\Delta T_j$  = 500 K). Therefore, during a SC transient, the higher drain current in terms of lower initial case temperature would lead to a larger temperature gradient and thus less number of repetitions to failure.

# V. CONCLUSIONS

In this paper, the impact of repetitive SC tests on the normal operation of 1000-V/22-A SiC MOSFETs are investigated, and the influence of case temperature on the SC degradation process is presented. The test conditions for repetitive SC tests are selected below the critical energy, which is also temperature-dependent and verified by increasing the SC pulse time duration step by step, and a gate oxide failure is observed with the increasing number of repetitions.

Both dynamic and static characteristics are combined together with repetitive SC aging tests, respectively, in order to investigate the impact on normal operation. The dynamic turnon and turn-off performance are affected, showing a delay and advance after repetitive SC tests. This phenomenon is caused by the reduction of the effective gate-source voltage on the device. Since the turn-on drain-source voltage delays gradually with the increase of SC repetitions, the turn-on loss increases correspondingly. With respect to static characteristics, the increase of the gate leakage current and on-state resistance are analyzed with increasing SC repetitions. A correlation between the on-state gate-source voltage during SC tests and the gate leakage current is confirmed, and in this case, a 9.3 % reduction of the on-state gate-source voltage is considered as the aging indicator for failure.

The impact of the case temperature on the repetitive SC is also taken into account. The results show that the number of repetitions until failure increases with increasing initial case temperature, which indicates the opposite trend compared to the SC robustness and the relationship between the case temperature and the number of repetitions is presented. This phenomenon can be explained by the lower SC energy due to the drain current reduction at higher case temperature. Thereafter, a 1-D heat propagation model together with experimental SC current waveforms is used to calculate the chip temperature evolution during the first repetitive SC test. The junction temperature rise decreases with the initial case temperature increase, which is in agreement with the fact that the SC energy is reduced at higher case temperature.

#### REFERENCES

- J. Millan, P. Godignon, X. Perpina, A. Perez-Tomas, and J. Rebollo, "A survey of wide bandgap power semiconductor devices," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2155–2163, 2014.

- [2] X. Wang, C. Jiang, B. Lei, H. Teng, H. K. Bai, and J. L. Kirtley, "Power-Loss Analysis and Efficiency Maximization of a Silicon-Carbide MOSFET-Based Three-Phase 10-kW Bidirectional EV Charger Using Variable-DC-Bus Control," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 4, no. 3, pp. 880–892, 2016.

- [3] S. Hazra *et al.*, "High Switching Performance of 1700-V, 50-A SiC Power MOSFET over Si IGBT/BiMOSFET for Advanced Power Conversion Applications," *IEEE Trans. Power Electron.*, vol. 31, no. 7, pp. 4742–4754, 2016.

- [4] P. Ning et al., "A High-Temperature SiC Three-Phase AC–DC Converter Design for >100 °C Ambient Temperature," IEEE Trans.

Power Electron., vol. 28, no. 1, pp. 555-572, 2012.

- [5] A. Fayyaz, L. Yang, M. Riccio, A. Castellazzi, and A. Irace, "Single pulse avalanche robustness and repetitive stress ageing of SiC power MOSFETs," *Microelectron. Reliab.*, vol. 54, no. 9–10, pp. 2185– 2190, 2014.

- [6] E. P. Eni et al., "Short-circuit degradation of 10-kV 10-A SiC MOSFET," *IEEE Trans. Power Electron.*, vol. 32, no. 12, pp. 9342– 9354, 2017.

- [7] T. T. Nguyen, A. Ahmed, T. V. Thang, and J. H. Park, "Gate Oxide Reliability Issues of SiCMOSFETs Under Short-Circuit Operation," *IEEE Trans. Power Electron.*, vol. 30, no. 5, pp. 2445–2455, 2015.

- [8] C. Ionita, M. Nawaz, K. Ilves, and F. Iannuzzo, "Comparative assessment of 3.3kV/400A SiC MOSFET and Si IGBT power modules," in 2017 IEEE Energy Conversion Congress and Exposition (ECCE), 2017, pp. 1343–1349.

- [9] L. Ceccarelli, P. D. Reigosa, F. Iannuzzo, and F. Blaabjerg, "A survey of SiC power MOSFETs short-circuit robustness and failure mode analysis," *Microelectron. Reliab.*, vol. 76–77, pp. 272–276, 2017.

- [10] G. Romano *et al.*, "A comprehensive study of short-circuit ruggedness of silicon carbide power MOSFETs," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 4, no. 3, pp. 978–987, 2016.

- [11] S. Mbarek, P. Dherbécourt, O. Latry, and F. Fouquet, "Short-circuit robustness test and in depth microstructural analysis study of SiC MOSFET," *Microelectron. Reliab.*, vol. 76–77, pp. 527–531, 2017.

- [12] T. Santini, M. Sebastien, M. Florent, L. V. Phung, and B. Allard, "Gate oxide reliability assessment of a SiC MOSFET for high temperature aeronautic applications," in 2013 5th IEEE Energy Conversion Congress and Exposition Asia (ECCE Asia), 2013, pp. 385–391.

- [13] F. Boige and F. Richardeau, "Gate leakage-current analysis and modelling of planar and trench power SiC MOSFET devices in extreme short-circuit operation," *Microelectron. Reliab.*, vol. 76–77, pp. 532–538, 2017.

- [14] F. Boige, F. Richardeau, D. Trémouilles, S. Lefebvre, and G. Guibaud, "Investigation on damaged planar-oxide of 1200 V SiC power MOSFETs in non-destructive short-circuit operation," *Microelectron. Reliab.*, vol. 76–77, pp. 500–506, 2017.

- [15] C. Ionita, M. Nawaz, K. Ilves, and F. Iannuzzo, "Short-circuit ruggedness assessment of a 1.2 kV/180 A SiC MOSFET power module," in 2017 IEEE Energy Conversion Congress and Exposition (ECCE), 2017, pp. 1982–1987.

- [16] D. Johannesson, "Assessment of 10 kV, 100 A Silicon Carbide MOSFET Power Modules," *IEEE Trans. Power Electron.*, vol. 33, no. 6, pp. 5215–5225, 2018.

- [17] B. Maxime, O. Remy, C. Thibault, B. Pierre, O. Sebastion, and T. Dominique, "Electrical performances and reliability of commercial SiC MOSFETs at high temperature and in SC conditions," in 2015 17th European Conference on Power Electronics and Applications (EPE'15 ECCE Europe), 2015, pp. 1-9.

- [18] S. Mbarek, F. Fouquet, P. Dherbecourt, M. Masmoudi, and O. Latry, "Gate oxide degradation of SiC MOSFET under short-circuit aging tests," *Microelectron. Reliab.*, vol. 64, pp. 415–418, 2016.

- [19] D. Pappis, L. de Menezes, and P. Zacharias, "Comparison of the Short Circuit Capability of Planar and Trench SiC MOSFETs," in 2017 International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management (PCIM Europe), 2017, pp. 1–9.

- [20] X. Zhou, H. Su, Y. Wang, R. Yue, G. Dai, and J. Li, "Investigations on the Degradation of 1.2-kV 4H-SiC MOSFETs under Repetitive Short-Circuit Tests," *IEEE Trans. Electron Devices*, vol. 63, no. 11, pp. 4346–4351, 2016.

- [21] H. Du, P. D. Reigosa, F. Iannuzzo, and L. Ceccarelli, "Investigation on the degradation indicators of short-circuit tests in 1.2 kV SiC MOSFET power modules," *Microelectron. Reliab.*, vol. 88–90, pp. 661–665, 2018.

- [22] Z. Wang *et al.*, "Temperature-Dependent Short-Circuit Capability of Silicon Carbide Power MOSFETs," *IEEE Trans. Power Electron.*, vol. 31, no. 2, pp. 1555–1566, 2016.

- [23] A. Marz, T. Bertelshofer, R. Horff, M. Helsper, and M. M. Bakran, "Explaining the short-circuit capability of SiC MOSFETs by using a simple thermal transmission-line model," in 2016 18th European Conference on Power Electronics and Applications (EPE'16 ECCE Europe), 2016, pp. 1-10.

- [24] P. D. Reigosa, F. Iannuzzo, and L. Ceccarelli, "Failure analysis of a degraded 1.2 kv sic mosfet after short circuit at high temperature," in

- Int. Symp. Phys. Fail. Anal. Integr. Circuits (IPFA), 2018, pp. 1–5.

[25] L. Smirnova, J. Pyrhonen, F. Iannuzzo, R. Wu, and F. Blaabjerg, "Round busbar concept for 30 nH, 1.7 kV, 10 kA IGBT nondestructive short-circuit tester," 2014 16th Eur. Conf. Power Electron. Appl. (EPE-ECCE Eur.), 2014, pp. 1–9.

- [26] Datasheet for CREE 1.0kV, 22A Silicon Carbide Power MOSFET, C3M0120100K, 2018.

- [27] D. Othman, S. Lefebvre, M. Berkani, Z. Khatir, A. Ibrahim, and A. Bouzourene, "Robustness of 1.2 kV SiC MOSFET devices," *Microelectron. Reliab.*, vol. 53, no. 9–11, pp. 1735–1738, 2013.

- [28] A. J. Lelis, R. Green, D. B. Habersat, and M. El, "Basic mechanisms of threshold-voltage instability and implications for reliability testing of SiC MOSFETs," *IEEE Trans. Electron Devices*, vol. 62, no. 2, pp. 316–323, 2015.

- [29] J. A. Ortiz Gonzalez and O. Alatise, "A Novel Non-Intrusive Technique for BTI Characterization in SiC MOSFETs," *IEEE Trans. Power Electron.*, 2018.

- [30] K. Roy, S. Mukhopadhyay, and H. Mahmoodi-Meimand, "Leakage current mechanisms and leakage reduction techniques in deepsubmicrometer CMOS circuits," *Proc. IEEE*, vol. 91, no. 2, pp. 305– 327, 2003.

- [31] H. Luo, F. Iannuzzo, and M. Turnaturi, "Role of Threshold Voltage Shift in Highly Accelerated Power Cycling Tests for SiC MOSFET Modules," *IEEE J. Emerg. Sel. Top. Power Electron.*, 2019.

- [32] L. Ceccarelli, A. S. Bahman, and F. Iannuzzo, "Impact of Device Aging in the Compact Electro-thermal Modeling of SiC Impact of Device Aging in the Compact Electro-thermal Modeling of SiC Power MOSFETs," *Microelectron. Reliab.* (in press), 2019.

- [33] B. J. Baliga, Fundamentals of power semiconductor devices, Second edition. 2018.

- [34] S. Pu, E. Ugur, and B. Akin, "Real-time degradation monitoring of SiC-MOSFETs through readily available system microcontroller," in 2017 IEEE 5th Work. Wide Bandgap Power Devices Appl. (WiPDA), 2017, pp. 378–382.

- [35] J. Sun, H. Xu, X. Wu, and K. Sheng, "Comparison and analysis of short circuit capability of 1200V single-chip SiC MOSFET and Si IGBT," in 2016 Int. Forum Wide Bandgap Semicond. China (IFWS), 2016, pp. 42–45.

- [36] L. L. Snead, T. Nozawa, Y. Katoh, T.-S. Byun, S. Kondo, and D. A. Petti, "Handbook of SiC properties for fuel performance modeling," *J. Nucl. Mater.*, vol. 371, no. 1–3, pp. 329–377, Sep. 2007.

- [37] P. D. Reigosa, F. Iannuzzo, and L. Ceccarelli, "Effect of short-circuit stress on the degradation of the SiO2dielectric in SiC power MOSFETs," *Microelectron. Reliab.*, vol. 88–90, pp. 577–583, 2018.

He Du (S'18) received the B.S. and M.S. degree from the Department of Electrical Engineering, North China Electric Power University, China in 2014 and 2017, respectively. He is currently a Ph.D. student in power electronics from the Department of Energy Technology, Aalborg University, Denmark, where he is also part of CORPE (Center of Reliable Power Electronics). He was a R&D assistant with ABB Corporate Research Center, Beijing, China from July to October 2015. From September 2019, he is a

Visiting Scholar with Fraunhofer Institute for Integrated Systems and Device Technology IISB, Erlangen, Germany. His research interests include the reliability of power electronic devices and especially SiC devices failures, assessment of devices under abnormal conditions.

**Paula Diaz Reigosa** (M'17, SM'14) received the B.S. degree in industrial engineering with a specialization in electrical engineering from the University of Oviedo, Spain, in 2012, and the M.S. degree in power electronics and drives from Aalborg University, Denmark, in 2014. She received the Ph.D. degree from Aalborg University, Denmark, in 2017. She has been a postdoctoral researcher with the University of Aalborg during 2018 and she is currently Associate Scientist with the University of Applied Sciences

Northwest Switzerland. Her current research interests include reliability of power devices, design of IGBTs and MOSFETs and their failure mechanisms, development of non-destructive testing facilities for assessment of high power modules under extreme conditions and emerging power electronics applications.

Lorenzo Ceccarelli (S'16) received the M.Sc. degree in electrical engineering from the University of Cassino and Southern Lazio, Cassino, Italy, in 2016. He carried out his Master Thesis activity with ABB Corporate Research Center, Västerås, Sweden, dealing with the modeling and characterization of megawatt-scale SiC power modules. He has recently finalized a Ph.D. degree in advanced electrothermal modeling and simulation of SiC mosfets for reliability with the Energy Technology Department, Aalborg

University, Aalborg, Denmark.

In 2018, he spent five months as a Visiting Graduate Scholar with the MSCAD Group, University of Arkansas, Fayetteville, USA. His research interests in Aalborg are included within the Center of Reliable Power Electronics and the Advanced Power Electronics Technology and Tools projects.

**Francesco Iannuzzo** (M'04-SM'12) received the M.Sc. degree in Electronic Engineering and the Ph.D. degree in Electronic and Information Engineering from the University of Naples, Italy, in 1997 and 2002, respectively. He is primarily specialized in power device modelling.

He is currently a professor in reliable power electronics at the Aalborg University, Denmark, where he is also part of CORPE, the Center of Reliable Power Electronics. His research interests are

in the field of reliability of power devices, including mission-profile based life estimation, condition monitoring, failure modelling and testing up to MW-scale modules under extreme conditions. He is author or co-author of more than 210 publications on journals and international conferences, three book chapters and four patents. Besides publication activity, over the past years he has been contributing 17 technical seminars about reliability at first conferences as ISPSD, EPE, ECCE, PCIM and APEC.

Prof. Iannuzzo is a senior member of the IEEE (Industry Application Society, Reliability Society, Power Electronic Society, and Industrial Electronic Society). He currently serves as Associate Editor for Transactions on Industry Applications, and is secretary elect of IAS Power Electronic Devices and Components Committee. In 2018, he was the general chair of the 29<sup>th</sup> ESREF, the first European conference on reliability of electronics.