## Aalborg Universitet

### Modeling and Design of a 1.2 pF Common-Mode Capacitance Transformer for Powering MV SiC MOSFETs Gate Drivers

Zhao, Hongbo; Dalal, Dipen Narendra; Wang, Xiongfei; Jørgensen, Jannick Kjær; Uhrenfeldt, Christian; Beczkowski, Szymon Michal; Munk-Nielsen, Stig Published in:

Proceedings of IECON 2019 - 45th Annual Conference of the IEEE Industrial Electronics Society

DOI (link to publication from Publisher): 10.1109/IECON.2019.8926673

Publication date: 2019

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Zhao, H., Dalal, D. N., Wang, X., Jørgensen, J. K., Uhrenfeldt, C., Beczkowski, S. M., & Munk-Nielsen, S. (2019). Modeling and Design of a 1.2 pF Common-Mode Capacitance Transformer for Powering MV SiC MOSFETs Gate Drivers. In *Proceedings of IECON 2019 - 45th Annual Conference of the IEEE Industrial* Electronics Society IEEE Press. Proceedings of the Annual Conference of the IEEE Industrial Electronics Society https://doi.org/10.1109/IECON.2019.8926673

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

? You may not further distribute the material or use it for any profit-making activity or commercial gain

? You may freely distribute the URL identifying the publication in the public portal ?

### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Modeling and Design of a 1.2 pF Common-Mode Capacitance Transformer for Powering MV SiC MOSFETs Gate Drivers

Hongbo Zhao, Dipen Narendra Dalal, Xiongfei Wang, Jannick Kjær Jørgensen, Christian Uhrenfeldt, Szymon Beczkowski, Stig Munk-Nielsen Department of Energy Technology Aalborg University, Aalborg, Denmark

hzh@et.aau.dk

*Abstract*— This paper proposes a physics-level modeling method for analyzing the primary to secondary-side (commonmode) parasitic capacitance of the transformer for the Mediumvoltage SiC MOSFETs gate drivers. The lumped circuit-based physics-model of the turn-to-turn capacitance, turn-to-core capacitance, and self capacitance of the core are derived, and it is found that the turn-to-core capacitance mainly contributes to the total equivalent parasitic common-mode capacitance. The measured common-mode impedance of the transformer shows high agreements with the calculated value, where the accuracy of the proposed modeling method can be proved based on the experimental results.

Keywords—common-mode capacitance, SiC MOSFETs gate drivers, lumped circuit-based physics-level model, turn-to-core capacitance.

### I. INTRODUCTION

Medium-voltage (MV) converters are getting increased attention as a grid interfaces to the MV power grids (1 kV- 35 kV) with typical line-to-line voltages of 3.3 kV, 4.16 kV, 6.6 kV, and 10 kV. Thanks to the recent advances in SiC Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET), the blocking voltage for the Wolfspeed  $3^{rd}$  generation SiC MOSFET dies have been increased to 10 kV and 15 kV [1] which makes it possible to design the MV converters by using the simple two-level voltage source converter (VSC) topology. However, due to the high dv/dt operations of SiC MOSFETs, the parasitic elements of active and passive components utilized in the converters should be considered and analyzed [2].

Gate drivers play an important role in providing reliable and continuous operation for the semiconductor switches. The high dv/dt switching transient causes the transient common-mode (CM) current to flow through the high side gate driver in a two-level VSC, which may result in the false turn-on switching instant and disturb the reliable operations of gate driver ICs and power supply controller [3].

It is known that the CM capacitance of the gate driver is majorly contributed by the parasitic primary to secondary side capacitance of the high voltage isolation transformer of the DC-DC power supply [3]. The peak amplitude of the CM current is in direct proportion to the transformer CM capacitance and therefore larger CM capacitance of the transformer will contribute to the increased transient CM current [4].

Several modeling methods are reported for modeling the CM capacitance of transformers. In [5] the authors proposed an accurate equivalent circuit model of the transformer by measuring the impedance between the terminals separately. In [6] the physics-based model of inductors for calculating the theoretical parasitic capacitance based on the energy conservation law was derived, where the electrical potential difference between the two analyzed terminals was assumed to be known. However, how to accurately and reasonably define the voltage drop between the two terminals of the analyzed capacitor is still a challenge for this type of modeling method [7].

Another popular physics-based modeling method is built on the lumped circuit-based modeling of the electromagnetic devices [8, 9]. This type of modeling method does not require any prior knowledge of the voltage potential difference between the analyzed terminals, but the disadvantage of this method is that the total equivalent capacitance is calculated by solving the complex lumped circuit models.

J. Biela et al. comprehensively review the physics-based modeling methods for calculating the stray capacitance of transformers and they indicate the CM capacitance of the transformer is majorly contributed by the primary-side layer to secondary-side layer capacitance [10]. However, for the transformers utilized in gate drivers, A. Anurag et al. in [4] point out that the CM capacitance is majorly contributed by the capacitance from the winding to the core. Since the derivations of the physics-based models are based on the geometrical structure, these models are useful for the optimized design of the transformer [7].

None of the known papers have physically modeled the parasitic CM capacitance of the transformer by considering the turn-to-core capacitance. In order to fill this gap, the geometrybased physics-level models of parasitic capacitances are derived in this paper, to develop the theoretical model for the transformer parasitic capacitances. Then, an efficient and simple method is proposed for calculating the total equivalent parasitic CM capacitance of the transformer by simplifying the complex lumped circuit model. The valid frequency range of the proposed method is also given in this paper. Finally, the experimentally measured impedance of the transformer is compared with the calculated equivalent parasitic CM capacitance to validate the accuracy of the proposed modeling method.

### II. MV SIC MOSFETS GATE DRIVER POWER SUPPLY

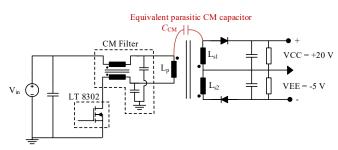

Fig. 1 shows the schematic of the designed gate driver power supply, which has been introduced in detail in [3]. A flyback converter is used for supplying the voltage to the gate driver IC. A high-frequency and high isolation voltage toroidal core transformer is used in the designed flyback converter.

It is known that one of the biggest challenges for designing the gate drivers prone to high dv/dt switching transients is the CM current due to the transformer primary to secondary side (CM) parasitic capacitance. Based on  $i = C \cdot dv/dt$ , the CM current will be smaller for the smaller value of the CM capacitance [3, 4]. Therefore, it is meaningful to have a physics-based model for calculating and optimizing the parasitic CM capacitance of the transformer.

Fig. 1 Schematic of the MV SiC MOSFET gate driver power supply [3]

### III. MODELING OF PARASITIC CAPACITANCE

The parasitic capacitances of the transformer include turnto-core capacitance  $C_{tc}$ , turn-to-turn capacitance  $C_{tt}$  and self capacitance of the core  $C_{core}$ . A toroid-type core transformer (primary side: 2 turns, secondary side: 2 turns) is selected as an example in this section. The equivalent circuit including the parasitic elements for the analyzed transformer is presented first, after which, the theoretical equations for the parasitic capacitances are derived.

### A. Key assumptions

Several key assumptions have been made for the modeling, which are the same assumptions as in [8, 9] and are summarized below:

1) The inductance and parasitic capacitance are linear, and not voltage and frequency-dependent. The reactance of the parasitic capacitance is infinite and doesn't affect the performance of the inductance at low frequency [8].

2) The elementary parasitic turn-to-turn, turn-to-core capacitances, and inductances in one turn can be represented as

a single equivalent turn-to-turn, turn-to-core capacitance, and inductance [8, 9].

3) The elementary capacitance between two adjacent turns or between the turn-to-core can be an equivalent series combination of several elementary capacitors, each with uniform dielectric material [9].

4) The lines of the electrical field are orthogonal to the conductor surfaces. The length of the electrical field in coatings and bobbins is considered to be equal to the thickness of the respective material. The length of the electrical field in the air gap is assumed to be the shortest distance between the two calculated points [8, 9].

5) The efficient angle range for integration is selected as  $-\pi/2$  to  $\pi/2$ , which is the same as Ref. [9].

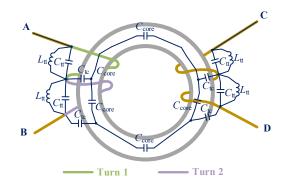

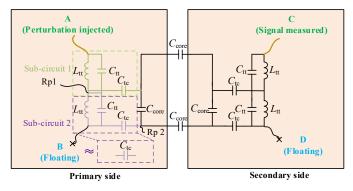

## *B.* The equivalent circuit for the toroidal core transformer with parasitic elements

A toroidal core transformer with two turns in each side is selected as an example in this section. The schematic of the researched transformer with parasitic elements is shown in Fig. 2, where  $L_{tt}$  and  $C_{tt}$  are the equivalent inductance and capacitance between the two neighbor turns,  $C_{tc}$  is the equivalent capacitance between the single turn and core, and  $C_{core}$  is the equivalent capacitance between the mapping points of the individual turn.

Fig. 2 Schematic of the transformer with parasitic elements

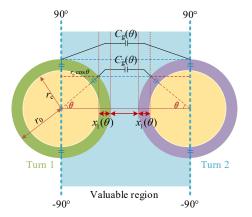

### C. Modeling of turn-to-turn capacitance

In a cross-sectional view as shown in Fig. 3, the capacitance between the two neighbor turns (Turn 1 and Turn 2) can be expressed as a series combination of several equivalent capacitances between the two conductors [8, 9].

Based on the [8, 9], the equations of  $C_{c}(\theta)$  which is the equivalent elementary capacitance between the conductor and insulated coating and  $C_{g1}(\theta)$  which is the equivalent elementary capacitor between the two turns contributed by the air gap with per unit angle can be given as

$$dC_{c}(\theta) = \varepsilon_{r}\varepsilon_{0}d\theta \int_{0}^{t_{r}} dl \int_{r_{0}}^{r_{c}} \frac{r}{dr} = \frac{\varepsilon_{r}\varepsilon_{0}l_{r}}{\ln\frac{r_{0}}{r_{c}}}$$

(1)

$$dC_{g1}(\theta) = \frac{\varepsilon_0 \int_0^{t_1} dl}{p_1 + 2x_1(\theta)} r_0 d\theta = \frac{\varepsilon_0 l_1 r_0}{p_1 + 2r_0 (1 - \cos \theta)}$$

(2)

where  $r_c$  is the diameter of the conductor,  $r_0$  is the diameter of the conductor with coating,  $p_1$  is the air gap between the two turns,  $l_t$  is the length of one turn,  $\varepsilon_r$  is the relative permittivity of the coating of turns, and  $\varepsilon_0$  is the vacuum permittivity. For any angle  $\theta$ , there exists a corresponding element equivalent capacitance.

The equivalent elementary capacitance  $C_{tt}(\theta)$  between the Turn 1 and Turn 2 can be presented as

$$dC_{\rm tt}(\theta) = dC_{\rm c}(\theta) / / dC_{\rm gl}(\theta) / / dC_{\rm c}(\theta)$$

(3)

where the symbol "//" represents the mathematical calculation symbol for the capacitances in series.

Fig. 3 Schematic of the two adjacent turns with parasitic elements in 2-Dimension

Integrating the Eq. (3) from  $-90^{\circ}$  to  $+90^{\circ}$  [9], the equivalent turn-to-turn capacitance can be expressed as

$$C_{\rm tt} = \int_{-\frac{\pi}{2}}^{\frac{\pi}{2}} dC_{\rm tt}(\theta) \tag{4}$$

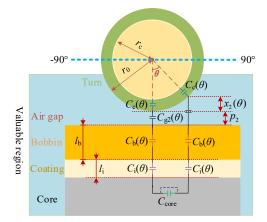

### D. Modeling of turn-to-core capacitance with bobbins

In [8], the turn-to-core capacitance is calculated to be twice of the measured capacitance, based on the assumption that there is no air gap between the turn and the core. For the modern power electromagnetic devices, bobbins, core coating, and even more complex structures are designed. In this section, the turnto-core capacitance models considering the impacts of bobbins and core coating are derived.

In practice, there is an insulated coating on the surface of the toroid core. The thickness of this coating is usually large so that its impact on capacitance cannot be neglected. Therefore, Case B is aimed to illustrate the parasitic turn-to-core capacitance with both bobbins and core coating. The turn-to-core capacitance, in this case, can be presented in a cross-sectional view as shown in Fig. 4.  $C_{g2}(\theta)$  is the equivalent elementary capacitor contributed by the airgap,  $C_b(\theta)$  is the equivalent

elementary capacitor contributed by the bobbins, and  $C_i(\theta)$  is the equivalent elementary capacitor contributed by the coating of the core.

The extra elementary capacitance contributed by the core coating and the bobbin with per unit angle can be presented as

$$dC_{i}(\theta) = \frac{\varepsilon_{i}\varepsilon_{0}\int_{0}^{l_{i}}dl}{l_{i}}r_{0}d\theta$$

(5)

$$dC_{\rm b}(\theta) = \frac{\varepsilon_{\rm b}\varepsilon_0 \int_0^{l_{\rm c}} dl}{l_{\rm b}} r_0 d\theta \tag{6}$$

$$dC_{g^{2}}(\theta) = \frac{\varepsilon_{0} \int_{0}^{t_{1}} dl}{p_{2} + x_{2}(\theta)} r_{0} d\theta = \frac{\varepsilon_{0} l_{1} r_{0}}{p_{2} + x_{2}(\theta)} d\theta = \frac{\varepsilon_{0} l_{1} r_{0}}{p_{2} + r_{0}(1 - \cos\theta)}$$

(7)

where  $l_i$  is the thickness of the core coating,  $\varepsilon_i$  is the relative permittivity of the coating of the core.

Therefore, the total elementary capacitance per angle can be expressed as

$$dC_{\rm tc}(\theta) = dC_{\rm c}(\theta) / / dC_{\rm g2}(\theta) / / dC_{\rm b}(\theta) / / dC_{\rm i}(\theta)$$

(8)

Fig. 4 Schematic representation of the turn-to-core capacitance in 2-Dimension considering bobbins and coating of the core elements (*C*<sub>core</sub> can be neglected in most situations)

Integrating the Eq. (6) from  $-90^{\circ}$  to  $+90^{\circ}$ , the equivalent turn-to-core capacitance can be obtained as

$$C_{\rm tc} = \int_{-\frac{\pi}{2}}^{\frac{\pi}{2}} dC_{\rm tc}(\theta) \tag{9}$$

### *E.* Modeling of the self-capacitance of the core

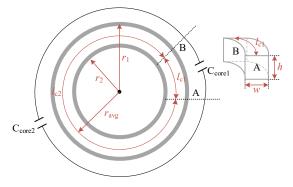

Considering the two cross-sections A and B of the toroid core is presented in Fig. 5, the total equivalent capacitance  $C_{\text{core}}$  can be expressed as a parallel combination of the two separate capacitors ( $C_{\text{core1}}$  and  $C_{\text{core2}}$ ).  $C_{\text{core1}}$  is the capacitor contributed by the minor circle, and  $C_{\text{core2}}$  is the capacitor contributed by the major circle on the core as shown in Fig. 5.

The total capacitance can be expressed as

$$C_{\rm core} = C_{\rm core1} + C_{\rm core2} \tag{10}$$

Ccore1 and Ccore2 can be approximately expressed as

$$C_{\text{corel}} \approx \frac{\varepsilon_0 \varepsilon_c w h}{l_{\text{cl}}}, \quad C_{\text{core2}} \approx \frac{\varepsilon_0 \varepsilon_c w h}{l_{\text{c2}}}$$

(11)

where  $\varepsilon_c$  is the relative permittivity of the core,  $l_{c1}$ , and  $l_{c2}$  are the average lengths from points A to B of the minor arc and major arc respectively.

Fig. 5 Schematic representation of the self-core capacitance between surface A and B

### IV. CALCULATION OF CM CAPACITANCE

In practice, one of the methods to obtain the CM capacitance of transformers is to measure the impedance between the primary and secondary side winding using an impedance analyzer.

In Fig. 2, A and B are the two ends of the primary winding, C and D are the two ends of the secondary winding. If the terminals A and C are connected to the impedance analyzer, and the terminals B and D are left floating, then the equivalent schematic can be represented as shown in Fig. 6.

While the signal is injected at the Terminal A, and the Terminal B is floating, the circuit of the primary side can be divided into the two identical sub-circuits.

For one of the sub-circuits shown in Fig. 6, the impedance between the Rp1 and Rp2 can be written as

Fig. 6 The equivalent CM impedance between the terminals A and C of the toroidal transformer

$$Z_{\text{RP1}_2} = (Z_{\text{Ltt}} / / Z_{\text{Ctt}}) + Z_{\text{Ctc}}$$

$$= \frac{j\omega L_{\text{tt}} \times \frac{1}{j\omega C_{\text{tt}}}}{j\omega L_{\text{tt}} + \frac{1}{j\omega C_{\text{tc}}}} + \frac{1}{j\omega C_{\text{tc}}}$$

(12)

If the frequency range of  $Z_{\text{RP1}_2}$  below  $0.1 \times w_{\text{tt}}$ , where  $w_{\text{tt}}$  is the characteristic frequency of the paralleled circuit of  $L_{\text{tt}}$  and  $C_{\text{tt}}$ , the  $Z_{\text{RP1}_2}$  can be rewritten as

$$Z_{\text{RP1}_2} \approx j\omega L_{\text{tt}} + \frac{1}{j\omega C_{\text{tc}}}, \quad \omega \le 0.1 \times \frac{1}{\sqrt{L_{\text{tt}}C_{\text{tt}}}}$$

(13)

In further, if the frequency range of  $Z_{\text{RP1}_2}$  is also below  $0.1 \times w_{\text{tc}}$ , where  $w_{\text{tc}}$  is the characteristic frequency of the  $L_{\text{tt}}$  and  $C_{\text{tc}}$  in series, the  $Z_{\text{RP1}_2}$  can be further simplified into

$$Z_{\text{RPI}_2} \approx \frac{1}{j\omega C_{\text{tc}}}, \quad \omega \le 0.1 \times \min(\frac{1}{\sqrt{L_{\text{tt}}C_{\text{tt}}}}, \frac{1}{\sqrt{L_{\text{tt}}C_{\text{tc}}}}) \quad (14)$$

Besides that, the relative permittivity of the core material is usually much higher than the relative permittivity of the insulating material and bobbins. According to the reference [10], the relative permittivity of the MnZn core is  $2 \times 10^5$  at 0.1 MHz, whereas the relative permittivity of the core enabled by NiZn core is 50 at 0.01 MHz.

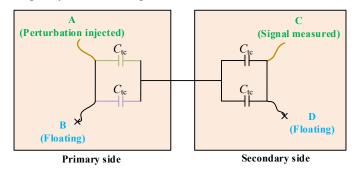

For the MnZn core, the capacitance  $C_{\text{core}}$  can be regarded as short since  $C_{\text{core}}$  is much larger than the  $C_{\text{tc}}$ . Then the simplified equivalent circuit of transformer for calculating the CM capacitance can be presented as Fig. 7.

Based on the simplifications, the CM capacitance calculated from terminal A to terminal C can be presented as

$$C_{\rm CM} = \frac{nm}{n+m} C_{\rm tc}, f \le 0.1 \times \min(\frac{1}{2\pi \sqrt{L_{\rm tt}C_{\rm tt}}}, \frac{1}{2\pi \sqrt{L_{\rm tt}C_{\rm tc}}}) (15)$$

where n is the number of turns of the primary winding, m is the number of turns of the secondary winding, f is the valid frequency range which is smaller than the minimal characteristic frequency of the windings.

Fig. 7 The simplified equivalent CM impedance between the terminal A and C of the transformer

According to the Eq. (13), for the certain frequency range, the value of CM capacitance of transformer is only related to the primary side and secondary side number of turns and the equivalent turn-to-core capacitance.

### V. CASE STUDY AND EXPERIMENTAL RESULTS

The key parameters of the designed transformers are listed in Table I.

Table I: Key parameters of the researched transformers

| Parameters                                      | Value                                          |  |

|-------------------------------------------------|------------------------------------------------|--|

| Core material [11]                              | 3F3                                            |  |

| Primary-side turns                              | 5                                              |  |

| Secondary-side turns                            | 10                                             |  |

| Relative permittivity of the turn coating [12]  | 3.3                                            |  |

| Relative permittivity of the core coating [13]  | 4.0                                            |  |

| Relative permittivity of the bobbins [14]       | 2.7                                            |  |

| Relative permittivity of core<br>@ 0.1 MHz [11] | $MnZn = 2 \times 10^5$                         |  |

| Size of core [11]                               | Dia. 32 mm<br>Inner Dia. 19 mm<br>Thick. 13 mm |  |

| Thickness of the core coating [11]              | 0.3 mm                                         |  |

| Diameter of the conductor                       | 0.65 mm                                        |  |

| Diameter of the conductor including insulation  | 0.85 mm                                        |  |

| Inductance factor (Al) [11]                     | 2270 nH/per turn                               |  |

The magnetizing inductance for primary and secondary side windings are calculated as 11.35 uH and 22.7 uH per turn respectively. The triple-insulated wire is used for winding the transformer, which has a breakdown voltage rating of 15 kV.

Since the relative permittivity of the core is much larger than the relative permittivity of the bobbin and coating, the equivalent capacitance of  $C_{\text{core}}$  is very high and can be regarded as a short based on the analysis presented Section IV.

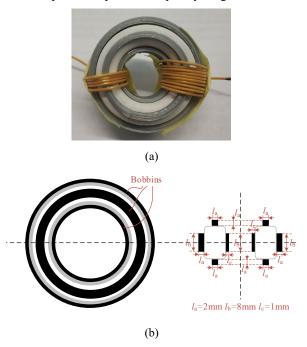

The CM impedance of the designed transformer is measured by the impedance analyzer E4990A using an adaptor 16047 from Keysight Technologies. The image of the test set up for experimental measurements is shown in Fig. 8.

Fig. 8 Image of the experimental test setup

The picture of the designed transformer with bobbins is shown in Fig. 9(a). The schematic diagram of the core with bobbins is shown in Fig. 9(b).

The measured average length of the single turn is 5.1 cm. The air gap length between the turn and core is measured using the caliper, and the average length is calculated as 0.36 mm. The theoretical CM capacitance can be obtained by calculating the several capacitors in series combination, due to the different thickness and width of bobbins.

Thus, according to Eq. (9), the theoretical turn-to-core capacitance  $C_{tc}$  can be calculated as

$$C_{\rm tc} = 0.32 \, \rm pF$$

(16)

For the frequency range of up to  $0.1 \times f_c$  (2.4 MHz), the calculated parasitic CM capacitance is shown in Eq. (17) based on Eq. (15).

$$C_{\rm CM} = 1.07 \ \rm pF$$

(17)

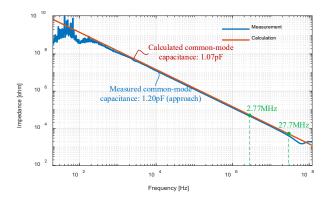

The measured and calculated impedance for the CM capacitance for the transformer with bobbins are compared in Fig. 10.

According to Fig. 10, the calculated impedance matches the measured impedance up to the frequency range of 2.4 MHz.

Fig. 9 (a) The image and (b) schematic for the transformer design with bobbins

Due to the capacitive coupling of the PCB, the total CM capacitance of the gate-driver is measured as 3 pF. For comparing, Table II gives the comparisons of the CM capacitance among the designed transformer and other commercial products with MV insulation. According to the comparisons, the designed low CM capacitance transformer helps to significantly reduce the total CM capacitance of the power supply for the gate driver.

Fig. 10 The measured impedance and calculated equivalent parasitic CM capacitance (with bobbins)

Table II: The comparisons of the CM capacitance among the designed transformer and commercial productions

|                                           | CM capacitance |

|-------------------------------------------|----------------|

| Designed transformer                      | 1.2 pF         |

| Gate driver with the designed transformer | 3 pF           |

| Concept ISO5125I DC-DC power supply[15]   | 4 pF           |

| RECOM REC6/R DC-DC power supply[16]       | 20 pF          |

| Concept Scale 2 1SC0450 gate driver[17]   | 8 pF           |

VI. SENSITIVITY ANALYSIS OF ASSUMPTIONS

In this paper, the permittivity and permeability of materials are found from the datasheet, technical report, and previous publications. However, none of them is constant, and most of them vary with frequency, temperature, current and voltage. The measured or estimated length of the geometrical structure may also introduce some error to the calculated results.

The sensitivity of two parameters is discussed in detail, which is the estimated length  $l_{tb}$  between the turn and bobbin and integrating angle range  $\theta$ .

Table III presents the calculated results with the fixed integrating angle (from  $-\pi/2$  to  $\pi/2$ ) and different estimated length  $l_{tb}$ . It can be found that there is a 16% difference between the calculated capacitance with  $l_{tb} = 0.1$  mm and  $l_{tb} = 0.36$  mm. The best fit results when  $l_{tb}$  is equal to around 0.2 mm.

Table III: The comparisons of the CM capacitance of transformer for a different turn-to-core length

|      | $l_{\rm tb} = 0.1\rm mm$ | $l_{\rm tb} = 0.2 {\rm mm}$ | $l_{\rm tb} = 0.36 {\rm mm}$ | Meas.  |

|------|--------------------------|-----------------------------|------------------------------|--------|

| Cap. | 1.27 pF                  | 1.18 pF                     | 1.07 pF                      | 1.2 pF |

Table IV presents the calculated results with fixed estimated length  $l_{\rm tb} = 0.22$  mm and different integrating range (from - $\pi/2$  to  $\pi/2$ , - $\pi/3$  to  $\pi/3$ , - $\pi/6$  to  $\pi/6$ ).

Table IV: The comparisons of the CM capacitance of transformer with different integrating angle ranges

|   |      | $-\pi/2$ to $\pi/2$ | $-\pi/3$ to $\pi/3$ | -π/6 to π/6 | Meas.  |

|---|------|---------------------|---------------------|-------------|--------|

| I | Cap. | 1.07 pF             | 0.75 pF             | 0.39 pF     | 1.2 pF |

It can be found that the calculated capacitance is smaller with the smaller angle range, which means the calculated capacitance is sensitive to the angle range. The best fit results when the integrating angle range is even wider than  $-\pi/2$  to  $\pi/2$ . It is worth noting that the integrating angle range might be different for different practical applications.

### VII. CONCLUSIONS

This paper proposes a complete modeling method for calculating the equivalent transformer CM mode parasitic for MV SiC MOSFETs gate drivers. The turn-to-turn, turn-to-core, and self- capacitance of the core are modeled considering several practical problems. A novel simplified method is used for calculating the equivalent parasitic CM capacitance in a certain frequency range, where the frequency range is determined based on the minimal characteristic frequency of the system. A transformer low CM capacitance is examined using the proposed modeling method, and it is found that the major CM capacitance of the transformer is contributed by the turn-tocore capacitance in the valid frequency range. The experimental results show good agreements with the theoretical analysis. The theoretical analysis and experimental results also prove that the transformers with bobbins have 1.1 pf-1.2 pF CM capacitance, which is a significant improvement compared to the previous research [3]. The total capacitance of gate driver with the designed transformer is 3 pF, respectively, which are considerably smaller compared to the commercial productions in 10 kV voltage class [15 - 17].

### REFERENCES

- J. Casady, V. Pala, D. Lichtenwalner, E. Brunt, B. Hull and et al., "New generation 10 kV SiC power MOSFET and diodes for Industrial Applications," *in Proc. 2015 PCIM Europe*, pp. 96-103, 2015.

- [2] N. Christensen, A. B. Jørgensen, D. N. Dalal, S. D. Sonderskov, S. Bęczkowski, C. Uhrenfeldt, and S. Munk-Nielsen, "Common mode current mitigation for medium voltage half bridge SiC modules," *in Proc. 2017 EPE'17 ECCE Europe*, pp. 1-8, 2017.

- [3] D. N. Dalal, N. Christensen, A. B. Jørgensen, S. D. Sønderskov, S. Bęczkowski, C. Uhrenfeldt, and S. Munk-Nielsen, "Gate driver with high common mode rejection and self-turn-on mitigation for a 10 kv SiC MOSFET enabled MV converter," *in Proc. 2017 EPE'17 ECCE Europe*, pp. 1-10, 2017.

- [4] A. Anurag, S. Acharya, Y. Prabowo, G. Gohil, and S. Bhattacharya, "Design considerations and development of an innovative gate driver for medium voltage power devices with high *dv/dt*," *IEEE Transactions on Power Electronics*, vol. 34, no. 6, pp. 5256–5267, Sep. 2018.

- [5] K. Fu and W. Chen, "Evaluation method of flyback converter behaviors on common-mode noise," *IEEE Access*, vol. 7, pp. 28019-28030, Mar. 2019.

- [6] Z. Shen, H. Wang, Y. Shen, Z. Qin and F. Blaabjerg. "Winding design of series AC inductor for dual active bridge converters", *in Proc. 2018 IEEE Applied Power Electronics Conference and Exposition*, pp. 565-570, 2018.

- [7] Z. Shen, H. Wang, Y. Shen, Z. Qin and F. Blaabjerg, "An improved stray capacitance model for inductors," *IEEE Transactions on Power Electronics*, early access, 2019.

- [8] A. Massarini and M. Kazimierczuk, "Self-capacitance of inductors," *IEEE Transactions on Power Electronics*, vol. 12, no. 4, pp. 671–676, Jul 1997.

- [9] A. Ayachit and K. Kazimierczuk, "Self-capacitance of single-layer inductors with separation between conductor turns," *IEEE Trans. Electromagn. Compat.*, vol. 59, no. 5, pp. 1642–1645, Sep. 2017.

- [10] J. Biela, J. W. Kolar, "Using Transformer Parasitics for Resonant Converters—A Review of the Calculation of the Stray Capacitance of Transformers," *IEEE Trans. Industry Applications*, vol. 44, no. 1, pp. 223-233, 2008.

- [11] Ferroxcube, "Soft ferrites and accessories," https://www.ferroxcube.com/en-global/download/download/11, Tech. Rep., Jul. 2013.

- [12] I. Kobayashi, K. Mori, N. Chida, A. Higashiura, T. Ishii and A. Taba, "Development of heat-resistant triple-insulated Winding Wire "Tex-F"", *Furukawa Review Archive*, no. 21, pp. 92-96, Nov. 2011.

- [13] AZoM, "Polyamide 11 Nylon 11- PA 11", [Online], Avaliable: https://www.azom.com/article.aspx?ArticleID=436

- [14] Ultimaker, "Technical datasheet PLA", [Online], Avaliable: https://ultimaker.com/download/74599/UM180821%20TDS%20PLA% 20RB%20V10.pdf

- [15] Power integrations, "1SC0450E2B0-45 and 1SC0450E2B0-65 Preliminary Data Sheet", [Online], Avaliable: <u>https://gatedriver.power.com/sites/default/files/product\_document/data\_sheet/1SC0 450E2B0-xx.pdf</u>

- [16] RECOM, "6 watt DIP24 reinforced single & dual output DC/DC converter", [Online], Available: <u>https://eu.mouser.com/datasheet/2/468/</u> REC6-S\_DRW\_R-958414.pdf

- [17] Concept, "ISO51251 Preliminary Data Sheet—High-Voltage Insulated DC/DC Power Supply for SCALE-2 Gate Drivers for 3.3kV, 4.5kV and 6.5kV IGBT modules", [Online], Available: <u>https://gatedriver.power.com/sites/default/files/product\_document/data\_sheet/ISO5\_1251.pdf</u>