Aalborg Universitet

## Packaging of Wide Bandgap Power Semiconductors using Simulation-based Design

Jørgensen, Asger Bjørn

Publication date: 2019

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Jørgensen, A. B. (2019). Packaging of Wide Bandgap Power Semiconductors using Simulation-based Design. Aalborg Universitetsforlag. Ph.d.-serien for Det Ingeniør- og Naturvidenskabelige Fakultet, Aalborg Universitet

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ?

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

## PACKAGING OF WIDE BANDGAP POWER SEMICONDUCTORS USING SIMULATION-BASED DESIGN

BY ASGER BJØRN JØRGENSEN

DISSERTATION SUBMITTED 2019

AALBORG UNIVERSITY DENMARK

# Packaging of Wide Bandgap Power Semiconductors using Simulation-based Design

Ph.D. Thesis Asger Bjørn Jørgensen

Thesis submitted April 2019

| Dissertation submitted:   | April, 2019                                                       |

|---------------------------|-------------------------------------------------------------------|

| PhD supervisor:           | Prof. Stig Munk-Nielsen<br>Aalborg University                     |

| Assistant PhD supervisor: | Assoc. Prof. Christian Uhrenfeldt<br>Aalborg University           |

|                           | Assoc. Prof. Szymon Beczkowski<br>Aalborg University              |

| PhD committee:            | Associate Professor Pooya Davari (chairman)<br>Aalborg University |

|                           | Professor Mark Johnson<br>University of Nottingham                |

|                           | Associate Professor Zhe Zhang<br>Technical University of Denmark  |

| PhD Series:               | Faculty of Engineering and Science, Aalborg University            |

| Department:               | Department of Energy Technology                                   |

|                           |                                                                   |

ISSN (online): 2446-1636 ISBN (online): 978-87-7210-426-3

Published by: Aalborg University Press Langagervej 2 DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Asger Bjørn Jørgensen

The thesis is types et using LATEX  $2\varepsilon$

Printed in Denmark by Rosendahls, 2019

in honor of my late father...

## Abstract

Power electronics are used for the conversion of electric energy in applications such as wind turbines, pumps, solar arrays and many industrial processes. The main unit of any power electronic device is the semiconductor die which traditionally has been made from silicon. For past decades wide bandgap semiconductors, such as silicon carbide and gallium nitride, have matured. They can be operated at higher voltages, higher frequencies and reduce losses by switching faster. To fully utilize these benefits the semiconductor die must be properly packaged and integrated with other parts of the power electronic converter.

The thesis initially presents a simulation framework for detailed modelling of electro-thermal behavior of 3D power module packaging and printed circuit board stackups used in integrated packaging. This enables rapid digital prototyping and accurate prediction of the performance, prior to manufacturing and testing of the real device.

The thesis studies several aspects related to packaging of wide bandgap semiconductor power semiconductors. The parasitic capacitive coupling in conventional power modules is analyzed with new medium voltage dies that switch at high dv/dt. A concept is investigated where the gate driver is integrated in the power module to enable fast switching and high power dissipation of the gate driver. The gate driver is operated at 2.5 MHz and its thermal resistance is reduced by 45 % compared with conventional placement on a printed circuit board outside the package. The experience gained from the two studies is combined to design and test the worlds first 10 kV SiC MOSFET power module driven in the MHz-range.

A new power module structure is proposed for new gallium nitride power devices, which is significantly easier to manufacture compared with other integrated structures. The package has a power loop inductance experimentally verified at 2.65 nH and switching transients of 64 V/ns without any overshoot. The new power module with gallium nitride devices is more expensive than conventional silicon power modules, but reduces switching losses up to 75 - 90 % and thus is regarded a viable choice for future power electronics applications.

# Dansk resumé

Effektelektronik benyttes til konvertering af elektrisk energi i applikationer som vindmøller, pumper, solpaneler og i mange industrielle processer. Hjertet i effektelektronikken er halvlederchips som de sidste mange årtier har været lavet af silicium. I de senere år er nye halvledermaterialer blevet modnet, herunder siliciumkarbid og galliumnitrid. De kan opereres ved højere spændinger, højere frekvenser eller sikre lavere skiftetab end traditionelle siliciumchips. Men disse fordele kan kun udnyttes hvis halvlederen indpakkes rigtigt og integreres med andre dele af effektelektronikken.

Indledningsvis præsenteres en simuleringsprocedure, som giver mulighed for en detaljeret beskrivelse af både elektriske og termiske aspekter af selv avancerede 3D strukturer og printlag i integreret effektelektronik. Det tillader hurtig udvikling af digitale prototyper og præcist design af elektronikkens opførsel, inden de fremstilles og testes fysisk.

I denne afhandling undersøges forskellige aspekter i forbindelse med indpakning af de nye halvlederchips til effektelektronik-formål. Problemer med kapacitiv kobling i traditionel elektronikindpakning undersøges med de nye højspændings-chips. Herefter indlejres styrekredsen tæt på halvlederchippen, hvilket sikrer hurtig tænd/sluk karakteristik, samtidig med at styrekredsens termiske modstand nedsættes med 45 %. Erfaringerne med højspændings-chips og indlejringsteknikken kombineres, og afhandlingen præsenterer verdens første forsøg på at drive en 10.000 V siliciumkarbid halvlederchip ved frekvenser i MHz-området.

Slutteligt præsenteres en helt ny indpakningsstruktur af galliumnitridbaserede chips, som er meget nemmere at fremstille end den nuværende førende teknologi. Indpakningen har lav induktans på 2.65 nH hvilket sikrer at chippen kan tænde/slukke med spændingshældninger på op til 64 V/ns helt uden oversving i blokeringsspændingen. Den nye indpakning baseret på galliumnitridhalvledere er dyrere end traditionel silicium-teknologi, men kan reducere skiftetab med op til 75 - 90 %. Derfor anses den nye teknologi som et realistisk valg i fremtidens effektelektroniske apparater.

| A                | bstra                  | t                                                                 | $\mathbf{v}$ |

|------------------|------------------------|-------------------------------------------------------------------|--------------|

| D                | ansk                   | esumé                                                             | vii          |

| $\mathbf{P}_{1}$ | reface                 | x                                                                 | ciii         |

| Ι                | $\mathbf{E}\mathbf{x}$ | ended summary                                                     | 1            |

| 1                | Intr                   | duction                                                           | 3            |

|                  | 1.1                    | State of the art packaging                                        | 5            |

|                  | 1.2                    | Research objectives                                               | 10           |

|                  | 1.3                    | List of publications                                              | 11           |

|                  | 1.4                    | Thesis outline                                                    | 12           |

| <b>2</b>         | $\mathbf{Sim}$         | lation tools & methods                                            | 15           |

|                  | 2.1                    | Electromagnetic finite element software                           | 16           |

|                  |                        | 2.1.1 SPICE lumped models from ANSYS Q3D Extractor $\therefore$   | 19           |

|                  | 2.2                    | Software framework                                                | 21           |

|                  | 2.3                    | Digital prototyping                                               | 23           |

| 3                | Wid                    | bandgap power module prototypes                                   | <b>25</b>    |

|                  | 3.1                    | Challenges in medium voltage operation of SiC MOSFETs             | 25           |

|                  |                        | B.1.1 Parasitic capacitance in conventional power modules         | 26           |

|                  |                        | B.1.2 Design and test of prototype with low parasitic capacitance | 28           |

|                  | 3.2                    | An integrated high frequency power module                         | 30           |

|                  |                        | 3.2.1 Analysis of gate driver dynamics for fast switching         | 32           |

|                  |                        | B.2.2 Design of power module with integrated gate driver          | 34           |

|                  |                        | 3.2.3 Thermal performance of gate driver IC                       | 35           |

|                  |                        | B.2.4 Experimental results at 2.5 MHz in Class E converter .      | 39           |

|                  | 3.3                    | Making vacuum tubes obsolete?                                     | 40           |

|                  |                        | 3.3.1 Power module design and manufacturing                       | 41           |

|    | 3.3.2Experimental results & discussion3.4Conclusion                                                                                                                                                                                                               | $\begin{array}{c} 43\\ 46\end{array}$                       |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

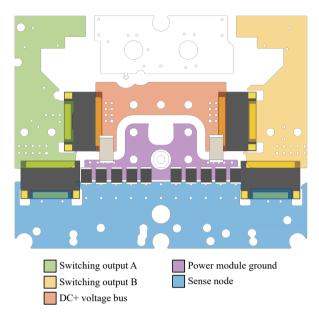

| 4  | Novel integrated packaging of GaN eHEMT devices         4.1       Power module design & layout                                                                                                                                                                    |                                                             |

| 5  | Conclusion & future work<br>5.1 Future work                                                                                                                                                                                                                       | <b>63</b><br>64                                             |

| 6  | References                                                                                                                                                                                                                                                        | 67                                                          |

| II | Appended papers                                                                                                                                                                                                                                                   | 81                                                          |

| Α  | Reduction of parasitic capacitance in 10 kV SiC MOSFET<br>power modules using 3D FEM<br>References                                                                                                                                                                | <b>83</b><br>93                                             |

| в  | A SiC MOSFET Power Module With Integrated Gate Drive         for 2.5 MHz Class E Resonant Converters         B.1 Introduction         B.2 Design of integrated module         B.3 Experimental tests         B.3.1 Estimation of gate driver junction temperature | <b>97</b><br>99                                             |

|    | B.3.1       Estimation of gate driver junction temperature         B.3.2       Class E electrical measurement         B.4       Conclusion         References                                                                                                     | 105<br>107<br>109<br>110                                    |

| С  | B.3.2 Class E electrical measurement                                                                                                                                                                                                                              | 107<br>109<br>110<br><b>113</b><br>115<br>117<br>119<br>121 |

|              |      | ast-Switching Integrated Full-Bridge Power Module Base<br>GaN eHEMT Devices | 137   |

|--------------|------|-----------------------------------------------------------------------------|-------|

|              | D.1  | Introduction                                                                | 139   |

|              | D.2  | Design of integrated GaN power module                                       | 143   |

|              |      | D.2.1 Gate driver $\ldots$                                                  | 143   |

|              |      | D.2.2 Board layout                                                          | 146   |

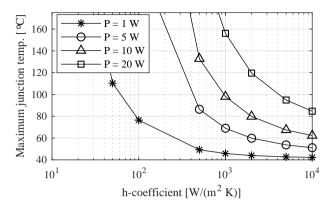

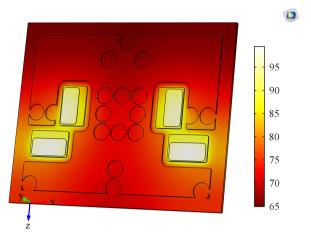

|              | D.3  | Thermal characteristics                                                     | 147   |

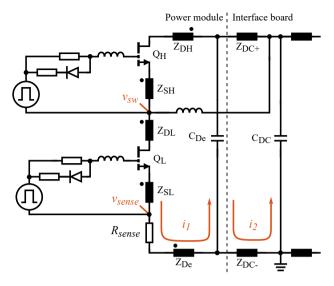

|              | D.4  | Electrical simulation model                                                 | 149   |

|              |      | D.4.1 Measurement of component parasitics                                   | . 151 |

|              |      | D.4.2 Simulation results                                                    | 152   |

|              | D.5  | Experimental results                                                        | 155   |

|              |      | D.5.1 Switching behavior                                                    | 156   |

|              | D.6  | Conclusion                                                                  | 158   |

|              | Refe | rences                                                                      | 159   |

| $\mathbf{E}$ | The  | rmal characteristics and simulation of an integrated GaN                    | V     |

|              | eHE  | CMT power module                                                            | 167   |

|              | Refe | rences                                                                      | 175   |

|              |      |                                                                             |       |

# Preface

This thesis is prepared at the Department of Energy Technology, Aalborg University as partial fulfillment of the PhD degree. The research was conducted in the time period between August 2016 and April 2019. The research is funded by the Intelligent and Efficient Power Electronics (IEPE) project, Advanced Power Electronics Technology and Tools (APETT) project and the Department of Energy Technology, Aalborg University.

The thesis was supervised by Professor Stig Munk-Nielsen and Associate Professors Christian Uhrenfeldt and Szymon Beczkowski. Part of the research was conducted at the FREEDM Systems Center at North Carolina State University, USA during Fall 2018 under supervision of Professor Douglas C. Hopkins, Head of the Packaging Research in Electronic Energy Systems (PREES) laboratory. I would like to express my gratitude to all of them for their trust and giving me the freedom to pursue new research ideas along the way. I would also like to thank the industrial partners of the IEPE and APETT projects for valuable discussions and feedback throughout the project period. I appreciate the discussions with Niels Høgholt Petersen and Søren Jørgensen from Grundfos A/S and their contributions to the research. I would like to thank my colleagues at the Department of Energy Technology, Aalborg University for making it a great and inspiring place to work.

Special thanks to my family for their support in times where some things in life are more important than research.

Asger Bjørn Jorgensu

Asger Bjørn Jørgensen

Preface

# Part I

# Extended summary

# Chapter 1 Introduction

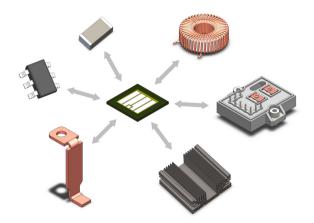

Power electronics is used in the conversion of electrical energy. It is employed for all power levels and includes applications such as wind turbines, photovoltaics, motor drives, pumps and lighting. Its main task is to control the flow of power from a source or to a load. This is done using a semiconductor die by switching it between its conducting and blocking state. At lower power levels (<1 kW) the semiconductor die is typically packaged as a single discrete device, and is then interfaced with other components to form a switch mode power supply (SMPS) unit [1]. At higher powers, typically several power semiconductor devices are packaged together in a standalone component called a power module. The interconnections between devices are then arranged inside the power module and only a few external terminals points are available for the end user. Achieving a good performance of the semiconductor die depends on how well it is interfaced with the other semiconductors as well as other parts of the SMPS, including gate driver integrated circuits (ICs), measurement circuitry, filter inductors and capacitors. In addition, the packaging must be designed to also ensure that the semiconductor die is cooled adequately and enclosed properly to avoid contaminants. These interactions of a semiconductor die with surrounding parts of the power electronic system are shown in Figure 1.1.

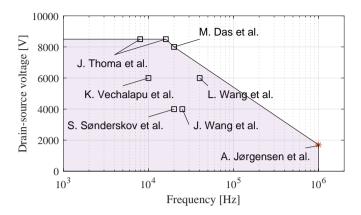

Traditionally the semiconductor die has been based on silicon (Si) material. Other advantageous wide bandgap (WBG) semiconductor materials such as silicon carbide (SiC) and gallium nitride (GaN) have been known for decades without significantly impacting the market of power semiconductor devices [2], [3]. However, in recent years new low voltage (typically 650-1200 V) WBG devices with advantageous properties have been introduced to the market at competitive prices [4], [5]. When compared to Si devices, some of the advantages highlighted for new available WBG devices are higher voltage breakdown strength, higher thermal conductivity and reduced on state resistance [6]–[9]. Some advantages of the WBG semiconductor materials and the trade offs in a

Fig. 1.1: Performance of the power semiconductor device depends on its interconnections with other parts of the power converter.

Table 1.1: Material properties for selected semiconductors [12], [13]

| Material                                                                                 | Si            | $\mathbf{SiC}$ | GaN            |

|------------------------------------------------------------------------------------------|---------------|----------------|----------------|

| Band gap [eV]                                                                            | 1.12          | 3.26           | 3.39           |

| $\epsilon$ , relative permittivity                                                       | 11.7          | 9.7            | 8.9            |

| $\mu$ , electron mobility $\left[\frac{\mathrm{cm}^2}{\mathrm{V}\cdot\mathrm{s}}\right]$ | 1360          | 900            | 2000           |

| $E_{\rm C}$ , critical electric field $\left[\frac{\rm V}{\rm cm}\right]$                | $2\cdot 10^5$ | $22\cdot 10^5$ | $15\cdot 10^5$ |

power semiconductor can be understood by studying the equation for the on resistance,  $R_{\rm on}$ , of a power semiconductor. The following equation is valid for the on resistance of the drift region in a unipolar device such as the Schottky diode, but also applies to MOSFETs, and is given by [10].

$$R_{\rm on} = \frac{4 \cdot V_{\rm br}^2}{\epsilon \cdot \mu \cdot E_{\rm C}^3 \cdot A} \tag{1.1}$$

where  $V_{\rm br}$  is the breakdown voltage, A is the cross sectional area.  $\epsilon$  is the relative permittivity,  $\mu$  the electron mobility and  $E_{\rm C}$  the critical electric field of the semiconductor material. The denominator  $(\epsilon \cdot \mu \cdot E_{\rm C}^3)$  is often referred to as the Baliga figure of merit (BFOM) of a semiconductor material [11].

For high voltage power electronics (1.1) shows that increasing the breakdown voltage of a device from 1 kV to 10 kV results in a 100x increase of  $R_{\rm on}$ . Using Si as semiconductor material, this would require an impractical large die area or result in a device with too high on resistance. In recent years, high voltage SiC devices with ratings of 10 and 15 kV have been developed and made available for research teams and universities [14], [15]. By using the higher BFOM of SiC,

Wolfspeed has developed a 10 kV 350 m $\Omega$  SiC MOSFET with a die area of 8.1 x 8.1 mm [16].

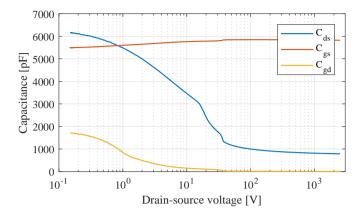

Increasing the die area results in a reduction in on resistance, but to achieve high frequency operation of the device it must also be appropriately sized. Increasing the die area results in larger capacitance of the devices, such as the input and output capacitance of the device. Generally the switching time for transitioning between the on and off states increases as the output capacitance of the device becomes larger [17]. Similarly, a larger input capacitance puts more demand on the gate driving circuit as more power is required to charge and discharge the gate of the device [18]. This balance between on resistance and input capacitance is depicted by Baligas high frequency figure of merit (BHFFOM) [19], given by

$$BHFFOM = \frac{1}{R_{\rm on} \cdot C_{\rm in}}$$

(1.2)

where  $C_{\rm in}$  is the input capacitance of the device. Due to the properties of WBG, these devices are smaller when compared with a Si device of similar voltage and current ratings. Due to the smaller die area, the WBG devices also have lower input capacitance which potentially allows operation at higher frequencies [19], [20].

Thus in summary the new WBG materials used for semiconductor devices, when compared with conventional Si devices, allows for higher voltage operation, faster switching performance and higher frequency driving. The balance between these attributes depends on the design of the semiconductor die itself. Furthermore, the benefits can only be utilized in the power electronics converter design if the semiconductor die is properly packaged and interfaced with the remaining power electronics system.

## **1.1** State of the art packaging

The following section reviews and presents a state of the art of packaging of power semiconductors, as packaging is identified as a key element to benefit from the advantages WBG power semiconductors potentially bring.

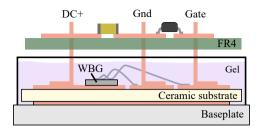

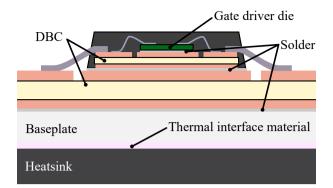

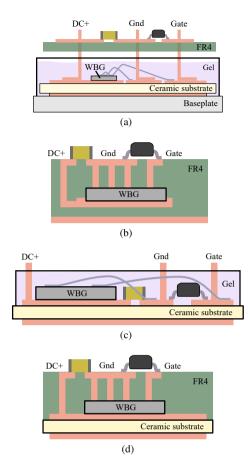

With Si being the dominant technology for the past decades, the most widely used power module structure is shown in Fig. 1.2. It is estimated to be used in 70 to 80 % of all power modules [4]. The assembly typically starts with a baseplate at the bottom. The baseplate ensures mechanical support and allows for mounting the power module to a heat sink, which is the reservoir used for dissipation of the generated power losses of the power module. Soldered to the baseplate is a direct bonded copper (DBC) substrate, which is a sandwich structure of a ceramic with copper on either side. The ceramic is typically aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) or aluminum nitride (AlN). The DBC ensures electrical

Fig. 1.2: Typical structure of a conventional power module. [Paper D]

insulation while allowing a relatively effective heat transfer from the top copper layers to the base plate [21]. The top copper layer of the DBC has tracks which routes the electrical signals and interconnects the different semiconductor dies, which are soldered to the top copper layer. For most Si power semiconductor dies, such as MOSFETs and IGBTs, the drain/collector-connection is at the bottom side and is soldered to the copper. Source/emitter and gate-connections are located on the top side of the die. The top side of the die is interconnected with the DBC top side copper using bond wires. The bond wires are typically attached to the die metallization and the DBC copper by ultrasonic welding and does not require soldering. Power terminals to interface with the external circuits are either soldered or ultrasonic welded to the top side copper. Following these steps the power module is encapsulated typically with epoxy or silicone gel. The encapsulation has a higher electric breakdown strength than air, and thus allows a more compact power module design with reduced risk of partial discharges or flashovers. Additionally, the encapsulation protects the semiconductor dies from humidity and other contaminants. Connected to the power module terminals on the outside is a printed circuit board (PCB), which holds the other important electrical components that is required to operate the power module, such as DC-link capacitors, gate driver circuit and voltage/current measurements. The advantage of this power module structure is its capability to dissipate high powers through the large baseplate and its attached heat sink. Also, the use of DBC and encapsulation enables for high voltage design [22]. Its disadvantage is its large parasitic inductances due to the long copper terminals, single-layer copper traces and the use of bond wires. This is a reported as an issue in terms of utilizing the fast switching speed of the new emerging WBG power devices. Power modules using this conventional structure typically has a parasitic inductance in the power loop of 10-30 nH [23]–[26]. Such high inductance results in large voltage overshoots and ringings when subjected to the high di/dt produced by the WBG power devices in some applications [27]. Similar noise issues may arise during fast switching of the gate-source loop because the gate driver is located outside the power module [28]. To fully utilize the fast switching capabilities of WBG power devices, research has been put into new power module packaging structures which minimize the

parasitic inductance in both the power and gate loop. From a theoretical point of view the optimum solution is to include the gate driver structure directly in the semiconductor switch structure. But such a solution is not economical, as the structure required to do the driver is more intensive than making the power structure [29]. For now the performance achieved by co-packing driver and switch is deemed good enough, with new packaging concepts to narrow the gap to the theoretical limit.

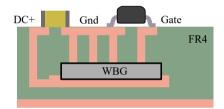

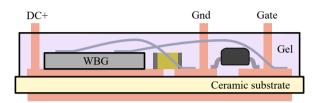

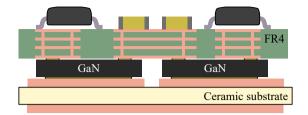

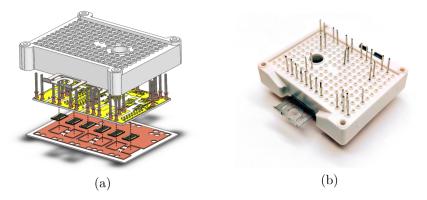

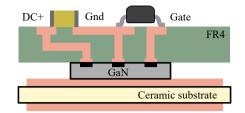

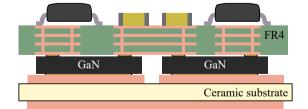

A proposed structure to minimize the parasitic inductance is by embedding the power semiconductor device inside the PCB and placing the gate driver and other circuitry on the outside layers, as shown in Fig. 1.3. First of all this eliminates the use of bond wires and secondly the gate driver is placed very close to the gate of the device which it has to drive. A prototype of this concept has been presented with a power loop having only 2.8 nH of parasitic inductance [25].

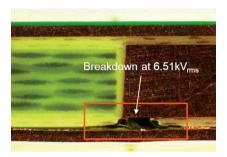

Fig. 1.3: Power module structure using PCB embedded die technology. [Paper D]

An issue of this structure is that the FR4 material has a relatively low thermal conductivity. To improve the thermal performance, designers might use larger copper planes and via arrays to distribute the generated losses to the outside copper layers. For further improvement of the thermal resistance the FR4 layers must be kept as thin as possible. However, as the FR4 layers become thinner it then may result in electrostatic issues such as partial discharge or sparking [30]. An example of this phenomenon is described by D. Kearney et al. during testing of a PCB embedded switching cell [31]. At 3.5  $\frac{kV_{rms}}{mm}$  partial discharges are detected, which for an insulation layer thickness of 130  $\mu m$  corresponds to 455  $V_{\rm rms}$ . The team experienced electric breakdown at approximately 14 times that voltage at an edge where field concentration occurred, as shown in Fig. 1.4. The geometry of the structure can be modified to reduce the peak electric field stress [32], but the critical dielectric field strength of the material must be obeyed. Thus while the embedded power module structure allows for a very low inductive design, it may cause difficulty in maintaining a good performance of both the thermal and electrostatic aspects simultaneously.

For good thermal performance it is advantageous to place the semiconductor device on a DBC, but it is often desired to achieve lower parasitic inductance than what is possible with the conventional power module structure. A proposed

Fig. 1.4: Electric breakdown in 130  $\mu$ m isolation layer of an embedded PCB solution [31].

Fig. 1.5: Diagram of integrated DBC power module structure. [Paper D]

power module structure [28], [33] utilizes more of the DBC by including most of the important components inside the power module, as the power module structure shown in Fig. 1.5. Here both the semiconductor device, DC-link and gate driver are soldered to the top side copper layer, and literature presents a power loop inductance in the range of 7-11 nH [34]. Good electrostatic performance can still be obtained as the module can be encapsulated in silicone gel. Additionally, if compared with the conventional power module structure, this technology does not require any new manufacturing steps. However, it is difficult to obtain the same level of integration and compactness as with the PCB technology because the circuit is limited to the single copper layer on the top side of the DBC. [26], [35] has proposed a solution to address this issue by using a printed copper thick-film approach. While more compact circuitry can be integrated in the power module by using this approach, it is still not as dense as what is possible with PCB technology.

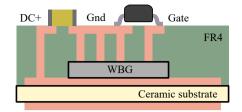

With the advantages and disadvantages observed from the PCB embedded and DBC integrated power module structures, a new proposed solution is to combine the two technologies [18], [36], [37]. It solves the problem of the weak thermal performance from the PCB embedded structure, while allowing a low inductive and compact design compared with the DBC. The structure is shown in Fig. 1.6. The PCB is molded directly on top of the DBC, which enables a very low inductive design reported at 1.5 nH for the power loop [38]. G. Feix *et al.* [37] have proven fast switching speeds of both gate and power loops, of the module shown in Figure 1.7(a). Using hybrid DBC and PCB technology is

Fig. 1.6: Diagram of a PCB/DBC hybrid power module structure. [Paper D]

an effective solution to achieve low electrical parasitics, high heat dissipation and good electrostatic performance. But in terms of manufacturability the complexity is increased significantly. An alternative solution is proposed by O. Kreutzer *et al.* [18], which decreases the complexity of manufacturing, but still combines the PCB and DBC as shown in Figure 1.7(b). Instead of molding the PCB layers on top of the DBC, bond wires are used to connect the chip to the PCB. Long copper planes and terminals are avoided compared with a conventional power module structure. The bond wires inevitably adds some inductance to both the power and gate loops. However, some inductance can be allowed as there is a limit to the switching speed of the gate structure, as discussed in Section 3.2.

**Fig. 1.7:** Two examples from Fraunhofer IZM Berlin of combinations of DBC and the PCB either (a) molded on top [37] or (b) connected by bond wires [18].

The literature review shows the various packaging approaches available to achieve high voltage operation and fast-switching of WBG power semiconductors. It has highlighted that research is put into the improvement of current power module packaging techniques. However, it also shows that packaging technology of the new WBG is far from as mature as the known silicon technology. When investigating the papers, various issues are encountered during experimental tests. The designs fail or are limited in performance due to weak electrostatic design [31], wrong gate design [18] or low thermal performance [33]. Some challenges found in literature is that the fast di/dt produced by the WBG devices increase the noise originating from the device source inductance, while high dv/dt may increase the displacement current of the Miller capacitance causing a false parasitic turn-on of a device [39], [40]. The issue is reinforced as the new WBG devices are decreasing in size meaning that they have lower input capacitance, which may make them more susceptible for noise issues such as the parasitic turn-on and ringing of the gate-source voltage. As devices become smaller and the packaging more compact it decreases parasitic inductance and capacitance in both power and gate loops. Especially reported in the case of GaN enhancement high electronic mobility transistors (eHEMTs), the result is that the resonance frequencies of power and gate loops move closer to one another, creating a scenario where it can cause for a continuous oscillatory triggering making the circuit unstable [41]–[44].

The risk of issues appearing in the experimental test phase can potentially be reduced by using a proper design method involving three-dimensional (3D) computer-aided design (CAD), multi-physics simulation, device modelling and circuit simulation. Limited usage of simulation methods prior to manufacturing may result that the performance of designs sometimes seem like a "hit" or "miss". Further discussion and reasoning for the use of simulation tools is elaborated further in Chapter 2.

## 1.2 Research objectives

The project has two main research objectives. The new emerging WBG power semiconductor devices offer benefits for designers of power electronic converters. To fully utilize the benefits it is necessary to package and properly integrate the semiconductor device to achieve robust operation. To close the gap between an ideal switch and a physical semiconductor die, a fast-switching WBG device must integrated with its peripheral components, including gate drivers and DC-link capacitors etc. The first research objective is

### To investigate and design packaging prototypes to push the operating range, improve the fast-switching or high voltage switching capabilities of WBG power semiconductors.

To achieve the first research goal, it is necessary to understand and use accurate simulation models of both the semiconductor devices and the influence of the packaging. The second research objective is

### To develop and build a digital design framework used for virtual prototyping of new integrated packaging solutions.

Gaining fidelity of the combined 3D multi-physics simulations, device modelling and circuit simulation will aid in the design of working prototypes and push the performance of new power modules based on WBG semiconductor devices.

## 1.3 List of publications

The thesis is based on the following papers, which have also been appended at the back of the thesis.

- A "Reduction of Parasitic Capacitance in 10 kV SiC MOSFET Power Modules using 3D FEM." Asger Bjørn Jørgensen, Nicklas Christensen, Dipen Narendrabhai Dalal, Simon Dyhr Sønderskov, Szymon Beczkowski, Christian Uhrenfeldt and Stig Munk-Nielsen. Published in "Proceedings of 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe)", Warsaw, Poland, 2017.

- B "A SiC MOSFET Power Module With Integrated Gate Drive for 2.5 MHz Class E Resonant Converters" Asger Bjørn Jørgensen, Unnikrishnan Raveendran Nair, Stig Munk-Nielsen and Christian Uhrenfeldt Published in "Proceedings of CIPS 2018; 10th International Conference on Integrated Power Electronics Systems", Stuttgart, Germany, 2018.

- C "High Frequency Resonant Operation of an Integrated Medium Voltage SiC MOSFET Power Module." Asger Bjørn Jørgensen, Thore Stig Aunsborg, Szymon Beczkowski, Christian Uhrenfeldt and Stig Munk-Nielsen. Submitted for publication in "IET Power Electronics", 2019.

- D "A Fast-Switching Integrated Full-Bridge Power Module Based on GaN eHEMT Devices" Asger Bjørn Jørgensen, Szymon Beczkowski, Christian Uhrenfeldt, Niels Høgholt Petersen, Søren Jørgensen and Stig Munk-Nielsen Published in "IEEE Transactions on Power Electronics, vol. 34, no. 3, pp. 2494-2504", March 2019.

- E "Thermal Characteristics and Simulation of an Integrated GaN eHEMT Power Module." Asger Bjørn Jørgensen, Tzu-Hsuan Cheng, Douglas Hopkins, Szymon Beczkowski, Christian Uhrenfeldt and Stig Munk-Nielsen Accepted for publication in "Proceedings of 2019 21th European Conference on Power Electronics and Applications (EPE'19 ECCE Europe)", Genoa, Italy, 2019.

In addition to the appended papers which are included in the thesis, there is a main authorship/co-authorship of the following papers which have been published during the PhD-project period.

"Novel Screening Techniques for Wind Turbine Power Converters." Asger Bjørn Jørgensen, Simon Dyhr Sønderskov, Nicklas Christensen, Kristian Linding Frederiksen, Eddy Iciragiye, Anders Eggert Maarbjerg, Stig Munk-Nielsen and Bjørn Rannestad. Published in "Proceedings of 18th European Conference on Power Electronics and Applications (EPE'16 ECCE Europe)", Karlsruhe, Germany, 2016.

- "Test Bench for Thermal Cycling of 10 kV Silicon Carbide Power Modules." Simon Dyhr Sønderskov, Asger Bjørn Jørgensen, Anders Eggert Maarbjerg, Kristian Linding Frederiksen, Stig Munk-Nielsen, Szymon Beczkowski and Christian Uhrenfeldt. Published in "Proceedings of 18th European Conference on Power Electronics and Applications (EPE'16 ECCE Europe)", Karlsruhe, Germany, 2016.

- "Switching Current Imbalance Mitigation in Power Modules with Parallel Connected SiC MOSFETs." Szymon Beczkowski, Asger Bjørn Jørgensen, Helong Li, Christian Uhrenfeldt, Xiaoping Dai and Stig Munk-Nielsen. Published in "Proceedings of 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe)", Warsaw, Poland, 2017.

- 4. "Performance Analysis of Commercial MOSFET Packages in Class E Converter Operating at 2.56 MHz" Unnikrishnan Raveendran Nair, Stig Munk-Nielsen and Asger Bjørn Jørgensen Published in "Proceedings of 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe)", Warsaw, Poland, 2017.

- 5. "Gate Driver with High Common Mode Rejection and Self Turn-on Mitigation for a 10 kV SiC MOSFET Enabled MV Converter" Dipen Narendrabhai Dalal, Nicklas Christensen, Asger Bjørn Jørgensen, Simon Dyhr Sønderskov, Szymon Beczkowski, Christian Uhrenfeldt and Stig Munk-Nielsen. Published in "Proceedings of 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe)", Warsaw, Poland, 2017.

- 6. "Common Mode Current Mitigation for Medium Voltage Half Bridge SiC Modules" Nicklas Christensen, Asger Bjørn Jørgensen, Dipen Narendrabhai Dalal, Simon Dyhr Sønderskov, Szymon Beczkowski, Christian Uhrenfeldt and Stig Munk-Nielsen. Published in "Proceedings of 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe)", Warsaw, Poland, 2017.

## 1.4 Thesis outline

The thesis is structured in the following way. Chapter 1 introduces the state of the art within packaging and defines the research objectives. Part of fulfilment of the research goals includes understanding the use of simulation software and tools. The simulation software and the design methodologies used throughout the thesis are presented in Chapter 2.

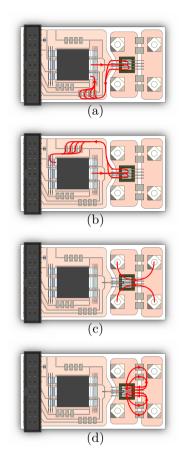

Chapter 3 presents several power module prototypes demonstrating packaging design changes to better utilize some benefits of the SiC devices. A 10 kV

### 1.4. Thesis outline

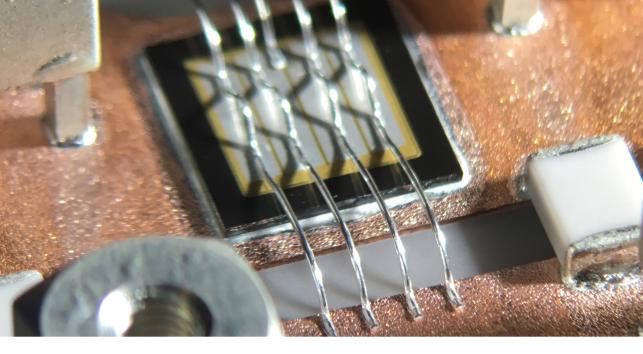

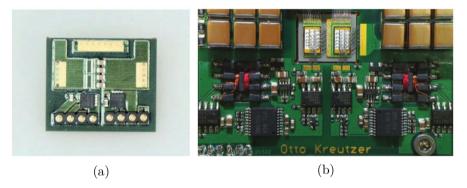

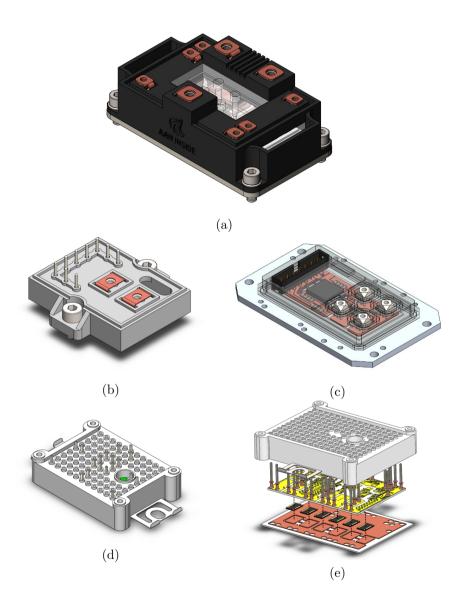

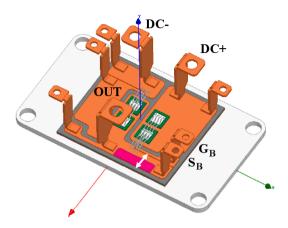

SiC MOSFET half bridge power module, as shown in Fig. 1.8(a), has been designed to study the influence of parasitic capacitances for high voltage and high dv/dt operation. The design of a power module with low parasitic capacitance is the topic of Section 3.1, and the design and experimental validation is published as the main content of Paper A. The work was carried out as part of the Intelligent and Efficient Power Electronics (IEPE) research project.

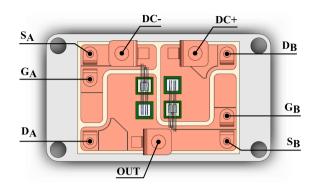

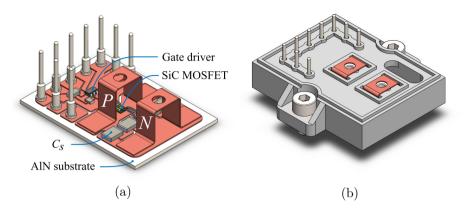

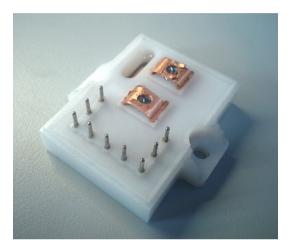

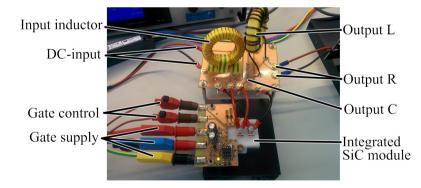

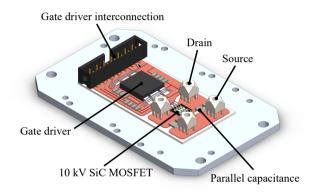

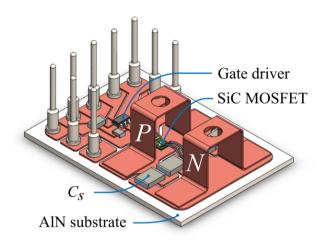

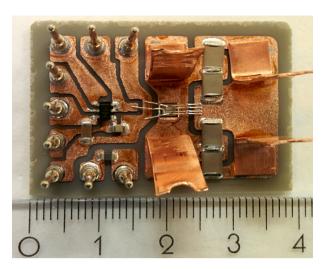

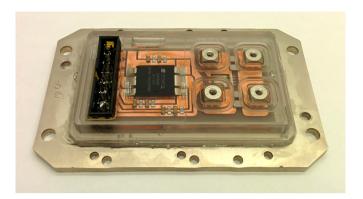

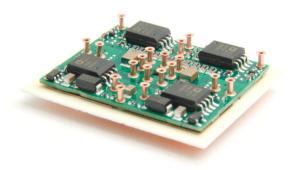

To study the design of high frequency power electronics, a SiC MOSFET power module with integrated gate driver circuit was designed, as shown in Fig. 1.8(b). The work was carried out as part of the Advanced Power Electronics Technology and Tools (APETT) project, as a contribution of how to achieve MHz-range switching using conventional gate driver ICs. The design, simulation and validation at 2.5 MHz in a Class-E converter of the designed power module is published in Paper B.

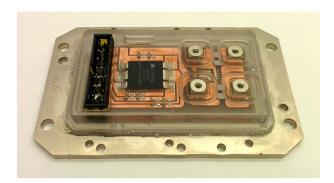

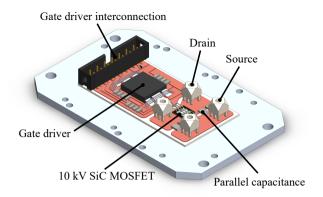

The experience gained from working with both the high voltage and the high frequency packaging is combined in Section 3.3. A medium voltage, high frequency power module based on a 10 kV SiC MOSFET die and integrated gate driver is designed as shown in Fig. 1.8(c) and tested. It is the first documented attempt of operating a 10 kV SiC MOSFET die in the MHz range, and the work is included in Paper C

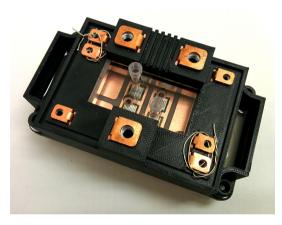

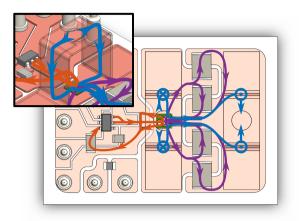

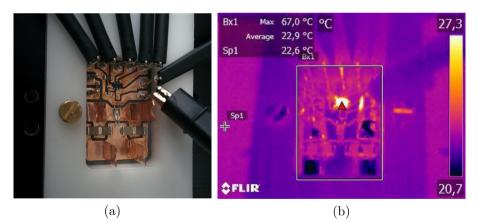

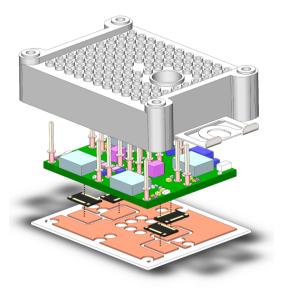

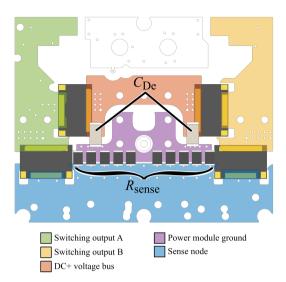

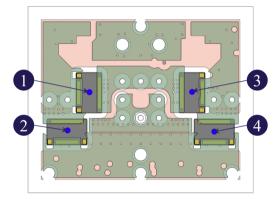

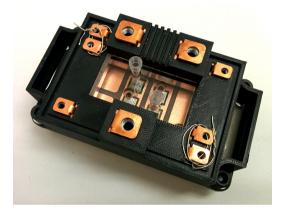

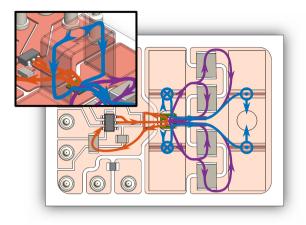

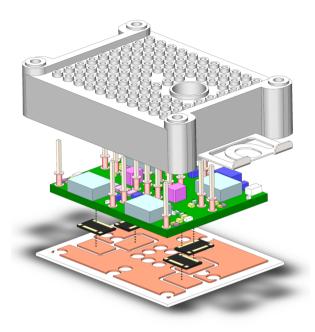

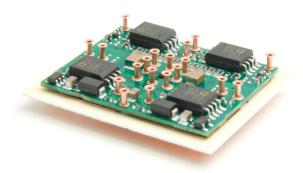

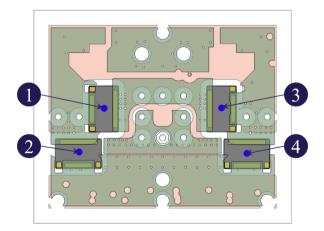

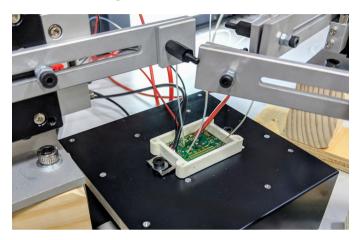

Chapter 4 presents the work on a fast-switching GaN eHEMT power module, which uses a new integrated packaging structure. The power module is shown in Fig. 1.8(d). Due to its compact form factor it is carefully simulated and tested for both its electrical and thermal performance, which is included as the main content of Paper D and E. The research is part of the APETT project. Due to the successful results a new three phase power module prototype, as shown in Fig. 1.8(e), is build and is currently being prepared for tests in a real pump application.

The thesis is concluded in Chapter 5 and the main research contributions are summarized. Future work is discussed in Section 5.1.

**Fig. 1.8:** 3D renderings of power module designs developed throughout the project, including: (a) 10 kV SiC MOSFET halfbridge power module (b) SiC MOSFET RF power module with integrated gate driver (c) integrated RF power module with 10 kV SiC MOSFET die (d) integrated GaN eHEMT full-bridge power module (e) exploded view of integrated GaN eHEMT three phase power module.

# Chapter 2 Simulation tools & methods

Simulation tools have been used extensively for the presented research and designs in this thesis. This chapter summarizes the motivation for using the simulation softwares and presents how they are used<sup>1</sup>. The chapter concludes with the presentation of an overall simulation framework, that has been used throughout the project period for the design of power modules. The simulation tools mainly include finite element method software suites to solve problems involving complex geometries exposed to physics such as electromagnetic fields, electrostatics, heat transfer and thermomechanical stress. The use of such simulations have become more valuable and more easily accessible due to a number of reasons.

**Computing power** The number of computations per second is continuously increasing, resulting in reductions of the simulation time. Combined with increasing memory available it allows for continuously larger and more complex geometries to be solved for. To increase simulation speed and being able to store the problem in memory, users have often been required to reduce and simplify the geometries to only small sections or cross-sectional 2D problems to study. The importance of having knowledge and understanding the physics on a simplified model cannot be understated. However, it also limits the trust a designer has of how well the simplified model represents the real-world behavior. With the availability of work stations with quad core computing power and memory of 32 GB/64 GB often allows for fast solving of the original geometry with only minor simplifications [45].

<sup>&</sup>lt;sup>1</sup>Some of the software is chosen as it is regarded the superior software for the specific problem to solve, while in other cases the choice of software is based solely on prior experience and what licenses are available. Note that the author has no personal interest or benefit in the promotion of any of software packages.

**Difficulty of measuring** Getting measurements on wide bandgap semiconductor devices which are encapsulated and integrated in compact power modules and packages is difficult. To utilize the fast-switching speeds of SiC and GaN, the inductance of commutation loops are as low as only a few nH. Most current sensing techniques are intrusive as they need to be inserted in or around the current path, which may add up to several nH of insertion inductance in the path and thus deteriorates the fast switching performance that was aimed for in the first place [46]–[49]. Due to the compactness of many power modules and integrated packages, measurement of internal voltages in the circuit such as gate-source voltages may be impossible. Likewise, prediction of issues such as cross-coupling between internal PCB layers, ground plane bounce etc. can be hard or impossible to measure [50], [51], in which case simulation of the original geometries is an important tool for designers.

Accuracy of measurements In the cases where measurement of the current and voltages is possible, the accuracy of such measurements is of concern. The reason is that the devices are switching so fast and has frequency content of hundreds of MHz. Voltage probes rated at several hundreds volts are typically limited by a bandwidth in the range of 100-200 MHz for differential probes [52]–[54] and 400-500 MHz for passive probes [55]–[57]. When measuring signals which are approaching this limit, designers may start to lose trust in their measurements [58]. For this reason, a second layer of validation through accurate simulation of the original geometry is useful to validate that the experimental measurements are correct.

**Digital prototyping** A simulation based design approach has been used to enable rapid digital prototyping, where several iterations of designs are quickly simulated and tested, before settling on a final design to manufacture. Silicon technology and power modules have been matured over decades, which provides a big pool of knowledge and many previous designs. However, when using new WBG semiconductors there is less experience and limited designs to build upon. Due to the duration of this PhD project, it was considered time inefficient to build several iterations of prototypes before landing the final design.

## 2.1 Electromagnetic finite element software

One of the main tasks for this thesis is to extract the electrical parasitics in terms of resistances, inductances and capacitances in the designed 3D power module structures. A widely used simulation software suite for extraction of electrical parasitics is the ANSYS Electronics Desktop. The ANSYS Electronics Desktop software suite includes three environments: ANSYS Maxwell, ANSYS Q3D Extractor and ANSYS HFSS - each specifically designed to speed up simulations

### 2.1. Electromagnetic finite element software

for different areas of electromagnetic problems encountered in power electronics. The difference is what approximations are used to ensure convergence and enabling faster solving without necessarily suffering significant reduction in accuracy for a type of problem. **ANSYS Maxwell** is designed for simulation of low frequency magnetics such as inductors, transformers or induction machines. It includes non-linear material properties and temperature dependencies [59]. **ANSYS Q3D Extractor** is used for higher frequencies, typically in range from DC to <1.5 GHz. It solves near-field magnetic and electric fields to calculate inductive and capacitive coupling between conductors. Material properties are linear and solving of magnetic and electric fields are decoupled problems. These simplifications allows calculation of RLC-parasitics for rather complex geometries often found in power modules and multilayer PCBs [60]. ANSYS **HFSS** is designed for very high frequencies, typically from MHz to hundreds of GHz, and solves the coupled magnetic and electric fields propagating into far field. It is well suited for simulating antenna structures or assess electromagnetic interference issues for different packages or casings [61].

For this PhD thesis the ANSYS Q3D Extractor has been used as the main software tool for computing the RLC parasitics encountered in power module packaging and PCBs. When reviewing literature using ANSYS Q3D Extractor [22], [62]–[67], it becomes apparent that different simulation approaches are employed within the ANSYS Q3D Extractor tool itself. The following paragraphs describe the different simulation methodologies used and discusses the advantages/disadvantages.

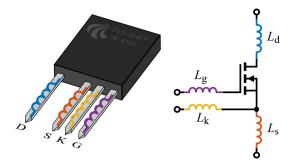

Method A In this method the inductances are calculated piece-wise for each conductor/trace on the circuit, as shown in Fig. 2.1. For the TO 247 4-pin device in this example, the model simply includes the extraction of the self-inductance for each individual lead. The advantage of this method is that setting up the simulation is simple and solving of the problem is fast, because it is reduced to single decoupled problems. The result is easily read and implemented as a lumped inductor in any circuit simulator such as PLECS, LTSpice, Saber or Simplorer. The disadvantage is that the result does not take into account the influence of cross-coupling due to flow of current in the other conductors of the net. There is no magnetic cancelling effects, or for instance how the gate-leads are influenced by a high current flowing in the drain-source path. Despite this fact, many SPICE component models of relatively compact packages only include lead self-inductances with no consideration to the coupling between.

Method A is the easiest to understand and to implement. It is useful in cases where it is not critical to fully model the magnetic field cancelling effects. Examples could be for single layered power electronic modules, especially if working at low di/dt where the contribution from inductances is less dominant.

Fig. 2.1: Simulation method A calculating single piece-wise inductance values excluding coupling.

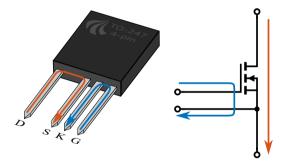

**Method B** To take into account the magnetic field cancelling effects, a method is to change the problem from a lumped element, into calculating a full current path, as shown in Fig. 2.2. When calculating the full loop during

Fig. 2.2: Simulation method B calculating entire loops including coupling.

a simulation cycle, it takes into account the magnetic coupling for that entire loop. In practice, this is then often achieved by shorting the terminals of the semiconductor die, so that it is a perfect conductor. The disadvantage of this method is that now the inductance is calculated for a full loop. It is not easy to implement in the circuit simulator, because the inductances are not split into lumped components that can be easily placed around the semiconductor model. The method can be advantageous in optimization problems as loops are quantified by a single loop value read from the software. For instance, if the main focus is to reduce the inductance of the power loop or gate loop. In such a case, it is easy to visualize and method B provides more accurate results of the effective inductance when compared to Method A.

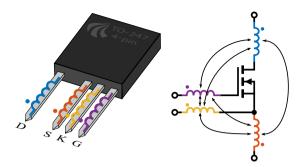

**Method C** This method uses the same self-inductances as in method A, with the addition of coupling between the self-inductances, as shown in Fig. 2.3. The

2.1. Electromagnetic finite element software

Fig. 2.3: Simulation method C calculating inductances and all couplings.

advantage is that the accuracy is similar to method B, because the magnetic field cancelling effects are included. In addition to that, when compared to method B, it now enables the designer to include the self-inductance and coupling into a circuit diagram. The disadvantage is that the effective inductance of a loop is not as easily available as in the case of method B, and thus during an initial design phase it is not as useful for design optimizations. For small systems, the couplings could be entered to a circuit simulator manually. However, for larger systems describing all couplings quickly approaches hundreds/thousand of entries. Thus, in practice ANSYS Q3D Extractor allows for the export of the full coupling matrix in a SPICE format. Thus to use the result, this method requires the use of a SPICE compatible circuit simulator, which may exclude a few circuit simulation softwares, such as PLECS. LTSpice, Saber and Simplorer are all compatible with this method. The definition of the coupled SPICE lumped circuit model of a power electronic component is described further in Section 2.1.1.

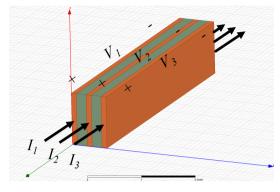

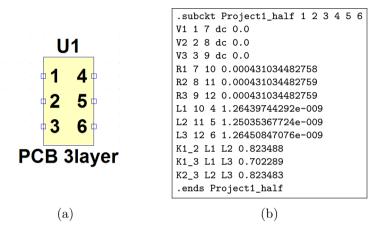

### 2.1.1 SPICE lumped models from ANSYS Q3D Extractor

For the case of three to four coupled nets it is easy to have an overview of how couplings are interconnected. However, for a case with 30-40 nets or more, extracting and keeping track of the interconnections manually is a tedious task prone to mistakes. Having at least 30-40 coupled impedances is not uncommon. In this case we need another way to describe the circuit dynamics in a more compact form. A three-layer PCB stack, as shown in Fig. 2.4, is used to describe how the SPICE lumped circuit model is interpreted. Each copper layer is defined as a net, which is all geometries of a conductive material type which is in contact with one another. Each net is separated by an isolating material type, either explicitly defined as the FR4 material layers included in Fig. 2.4 or just the surrounding air/vacuum. Each net has two terminals on its surface, a current input and current output, also known as a source and sink in ANSYS Q3D Extractor. The current sources and sink are indicated by the arrows in Fig. 2.4. Thus, for currents flowing through each net, they create a voltage drop, that we wish to solve for, and can be represented in matrix form as

Fig. 2.4: Example of a three layer stack coupled electromagnetically in ANSYS Q3D.

$$\begin{bmatrix} V_1 \\ V_2 \\ V_3 \end{bmatrix} = \begin{bmatrix} R_{11} & R_{12} & R_{13} \\ R_{21} & R_{22} & R_{23} \\ R_{31} & R_{32} & R_{33} \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \\ I_3 \end{bmatrix} + j\omega \begin{bmatrix} L_{11} & L_{12} & L_{13} \\ L_{21} & L_{22} & L_{23} \\ L_{31} & L_{32} & L_{33} \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \\ I_3 \end{bmatrix}$$

(2.1)

ANSYS Q3D Extractor solves the problem at two frequencies. At DC the problem is solved with the current distributed uniformly in the volume of the conductor, until convergence at the current path which results in the lowest resistance,  $R_{ij}$ . Based on this current distribution the magnetic couplings,  $L_{ij}$ are calculated. The second solution is obtained at high frequency AC with the assumption that skin effect is well developed, thus the current density is focused on the conductor surfaces. To speed up the solver the problem is regarded as a surface problem. When solving the high frequency AC part it is solved as a coupled problem, meaning that the current distribution is dependent on the inductive part. ANSYS Q3D Extractor also solves for the capacitive coupling between nets. This is done by assuming equipotential nets, and the capacitance values are calculated as an independent problem with no influence of frequency or the magnetic coupling.

The extracted resistance, inductances and capacitance values, are implemented in the SPICE circuit simulator as lumped circuit elements. The inductance and resistance values are halved and the capacitance is placed in between. Thus the parasitics are arranged symmetrically in terms of the defined input/output ports. This may of course not be the case in the real device where capacitance might be distributed differently. ANSYS Q3D Extractor allows for automatic export of the calculated RLC-matrices into a SPICE circuit model using the circuit diagram as depicted in Fig. 2.5.

Fig. 2.5: Equivalent lumped circuit model of Fig. 2.4.

Fig. 2.6: (a) the LTSpice circuit symbol and (b) part of the SPICE code used to describe the terminal.

For fast solving of a large netlist it is useful to use as few elements as possible, and solve a simplified set of equations to speed up the simulation. However, for systems of high frequencies and where it is required to achieve higher accuracy the ANSYS HFSS software package could be the simulation tool of choice. ANSYS Q3D Extractor enables the lumped circuit model of Fig. 2.5 to be directly exported into a SPICE circuit symbol as shown in Fig. 2.6(a). The symbol includes the SPICE code to define Fig. 2.5 and is partly shown in Fig. 2.6(b)

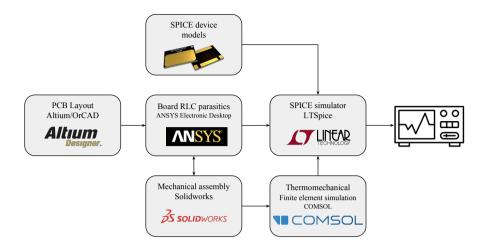

## 2.2 Software framework

The following section describes the main software packages which have been used for the research in this thesis. Additionally, some discussion is given in regard to which design tasks are being carried out at each step. A flow diagram shown in Fig. 2.7 depicts how the different software are interfaced with one another.

Fig. 2.7: The simulation software tool roadmap used for designed prototypes.

The simulation process starts out by setting up a model of the semiconductor. Almost all semiconductor manufacturers provide SPICE models of their devices, and thus a SPICE solver is required. For this thesis LTSpice has been used exclusively due to its accessibility and for being freeware. Alternatives could be Saber and Simplorer. Initially, just the main circuit elements and the die models are used to gain insight to the overall functionality of the circuit. It is important to insert some of the parasitic inductances and capacitances that are expected to be in the final power module. By changing the values of the parasitics, the designer gains some insight into what paths of the power module are critical. Some paths might allow hundreds of nH without significantly effect on the resulting switching waveforms, while 1-2 nH in the wrong path can seriously deteriorate the performance.

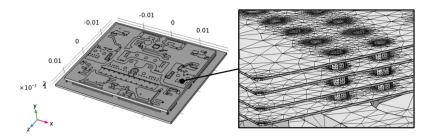

Once the circuit is understood, a draft of the 3D design power module is proposed. For a conventional power module structure it is mainly the traces of the DBC, which for this thesis is designed using Solidworks. For more integrated packaging the electrical design is done in a PCB editor, such as Altium or OrCAD. As a draft design is done, it is imported to ANSYS Electronics Desktop. The circuit is simulated using the ANSYS Q3D Extractor and an electrical parasitics model, as described in Section 2.1, is exported for use in LTSpice. If the electrical performance is satisfactory in LTSpice, the next step is to verify the power module in terms of other aspects in a multi-physics finite element method simulation software such as COMSOL Multiphysics, ANSYS workbench or Abaqus.

From ANSYS Electronics Desktop the full PCB layer stackup and its traces can be exported as a 3D model, which in this thesis is assembled in Solidworks

#### 2.3. Digital prototyping

with the 3D models of baseplates, DBCs and semiconductor die models. From Solidworks a full 3D model is now available to verify the electrostatic or thermal performance of the power module. From the electrical waveforms in LTSpice we may have obtained some critical information such as expected power losses and peak voltage that can be used as input information. Furthermore, the finite element method software can also be used for a transient simulation i.e. used for obtaining a thermal response for the power module. If the SPICE model of the component is temperature-dependent, the thermal characteristics can be implemented in LTSpice to finalize a full electro-thermal model.

Using this detailed simulation process allows the engineer to assess a design for several aspects before spending valuable time on manufacturing a prototype. Using the real 3D geometries and accurate SPICE die models provides more accurate results as opposed to rough calculations or simplified 2D structures to estimate semiconductor losses, thermal resistances and electric field strengths early in the design process. Additionally, having the 3D models and using finite element method simulations provides a visualization of phenomena such as current crowding, thermal spreading and electric field concentrations. This enables the engineer to make quick adjustments and digitally iterate on a design much faster.

## 2.3 Digital prototyping

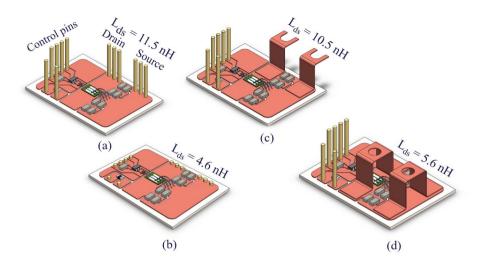

As an example of digital prototyping, some early versions of designs for an integrated RF power module are presented in this section. The design of the module is presented in more detail in Chapter 3.2. For now the focus is on a single inductance of the power module.

In this example an initial power module layout, shown in Fig. 2.8(a), has been designed in the 3D CAD software Solidworks. In ANSYS Q3D Extractor the inductance is calculated using Method B. The inductance is from the drain to the source terminals - thus the path is through the semiconductor die and its bondwires. For the initial design the inductance equals 11.5 nH. To understand the origin of the inductance, a new 3D model is designed in Fig. 2.8(b), where the lengths of the three pin terminals are reduced from 14 mm to 1 mm. The inductance is then reevaluated as 4.6 nH, revealing that more than 50 % of the inductance is caused by the terminals. By gaining inspiration from looking at some discrete RF packages [68] and high current power modules [69] that rely on low inductive packaging, a new set of power terminals based on wide flat copper terminals are designed. The drain-source inductance of the new design in Fig. 2.8(c) is then increased again to 10.5 nH. The new terminals are slightly better than the original design, but the main inductance was not caused by the shape of the terminals. It is noticed that the current must flow from the exterior of the DBC to the center before conducting through the semiconductor die.

Fig. 2.8: Rapid prototyping enable quick trial of design layouts, as (a), (b), (c) and (d) represents four different iterations of the design.

Additionally, the  $\sim$ 5-6 nH contributed from the height of the power terminals itself can be reduced by paralleling more conductors. The final power module layout, shown in Fig. 2.8(d), has achieved a drain-source inductance of 5.6 nH.

This example shows how the power module inductance in an important path of the power module has been reduced to half of its initial value. The four different designs have been designed and simulated in about a 1-2 days of work. Without the use of 3D CAD tools and finite element simulation software, there would have been limited information to assess the design before it was build.

This chapter has presented several simulation strategies when using the finite element method software. Some of the approaches have advantages during early design iterations and for parametric sweeps of design variables to optimize the layout. Some methods are more suited for accurate circuit modelling in later stages. The use of the simulation tools are an important part in the design of the power module packages presented in the following chapters of this thesis. The time required in experimental testing is reduced, because the prototype being manufactured has already been through extensive digital verification.

## Chapter 3

# Wide bandgap power module prototypes

The following chapter presents power module prototypes that each treats an issue related to the full utilization of WBG power semiconductor devices. Issues related to fast dv/dt in switching of medium voltage devices are presented in Section 3.1. Section 3.2 investigates the gate-driver circuit if WBG power devices are to be switched at potentially higher frequencies without the use of resonant gate drivers. The knowledge gained from the two first prototypes are combined in Section 3.3 to present the worlds first documented attempt of medium voltage, high frequency operation of a 10 kV SiC MOSFET.

## 3.1 Challenges in medium voltage operation of SiC MOSFETs

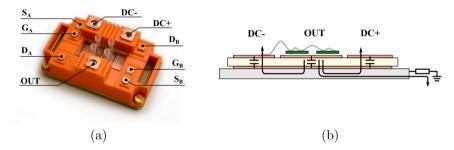

Medium voltage SiC devices have received increasing interest as the semiconductor technology is improving and samples are being released for engineers and research institutions. A potential application, once the medium voltage semiconductor technology has matured, is the wind turbine industry where power levels has scaled to several megawatts within a decade. For increasing power levels the typical method for increasing the power handling capability is to increase the current rating by paralleling converters [70]. Associated with the very high current levels is increasing joule losses and increasing size of the transformer required to step up the voltage for distribution [71]. An alternative solution to reach the required power is by removing the bulky transformer in the nacelle and increase the voltage at converter level [72], [73]. A proposal is to use the conventional two-level converter topology and increase the voltage rating by using 10 kV SiC MOSFETs instead of low voltage Si IGBTs. Currently, the packaging of medium voltage devices is not mature and this research is set out to investigate critical issues when designing packaging for such high voltage ratings.

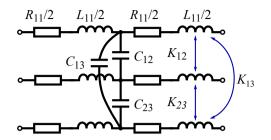

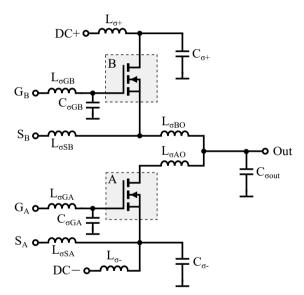

Conventional Si IGBT power modules have several hundreds or thousands of amperes in rating, meaning that they are experiencing a large di/dt during switching. For the medium voltage operation the di/dt stress is reduced, thus despite the faster switching of WBG devices the inductance of conventional packaging is not a limiting factor. As discussed in Section 1.1, the conventional packaging structure has advantageous properties in terms of electrostatics. The conventional packaging structure is deemed advantageous for medium voltage operation. However, in terms of medium voltage operation increased focus on the issues related to high dv/dt is critical, which is the parasitic capacitances shown in Fig. 3.1.

Fig. 3.1: Parasitics of a half-bridge conventional module structure. [Paper A]

### 3.1.1 Parasitic capacitance in conventional power modules

In early versions of a 10 kV SiC MOSFET half-bridge power module, as shown in Fig. 3.2, it is observed that during switching, the high dv/dt of the switching output causes current to flow in the heat sink due to the parasitic capacitance of the power module [74]. The copper layers of the DBC are only separated by a 0.63 mm thick aluminum nitride (AlN) ceramic, so the Cu-AlN-Cu sandwich structure makes a capacitance. For safety the heat sink is grounded and due

Fig. 3.2: Previous 10 kV SiC MOSFET power module layout.

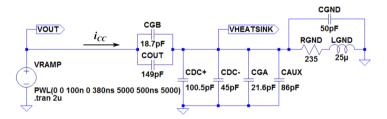

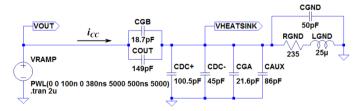

to the grounding impedance there is a voltage ringing on the heat sink as current flows [40]. The current conducts through critical gate driver circuitry of the power module, which causes electromagnetic interference issues limiting the achievable switching speed [74]. Rearranging the parasitic capacitances of Fig. 3.1 and including the grounding impedance and auxiliary parasitic capacitance of the experimental setup results in a SPICE simulation schematic as shown in Fig. 3.3. In this schematic the inductances have been neglected, because for the experimental tests the di/dt is relatively low and only slightly influences the result. The schematic highlights that the root cause of the

Fig. 3.3: SPICE model of the capacitive coupling to the heat sink. [Paper A]

currents are the capacitances  $C_{\sigma GB}$  and  $C_{\sigma out}$ . As the voltage  $(V_{out} - V_{heatsink})$  changes, a current flows given by

$$i_{\rm CC}(t) = (C_{\sigma\rm GB} + C_{\sigma\rm out}) \cdot \frac{\mathrm{d}(V_{\rm out} - V_{\rm heatsink})}{\mathrm{d}t}$$

(3.1)

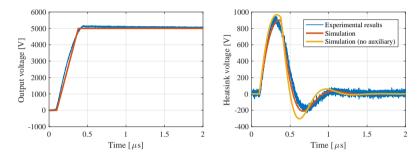

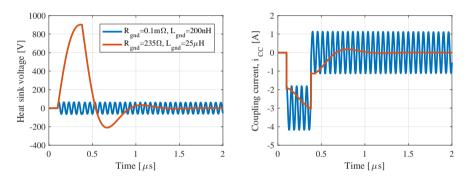

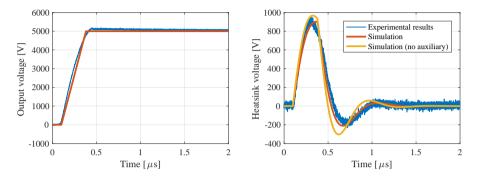

where  $C_{\sigma \text{GB}}$  is the parasitic capacitance of the gate plane for MOSFET B,  $C_{\sigma \text{out}}$  the parasitic capacitance of the output plane,  $V_{\text{out}}$  the voltage of the switching output plane and  $V_{\text{heatsink}}$  the voltage of the heat sink. It is not desirable to slow down the switching speed of the SiC MOSFET, as we wish to have as fast  $\frac{dV_{\text{out}}}{dt}$  as possible. We may limit the rate of change of voltage on the heat sink, by changing the grounding impedance. Having a very high resistance is dangerous as the heat sink is not properly grounded and can be dangerous when working with the test bench after a switching test if voltage is build up in the capacitance. On the other hand a very low resistance results in an undamped oscillation. In this experiment the resistor has been chosen such that it gives a nearly critically damped response of the heat sink voltage, ensuring that heat sink voltage oscillation diminishes fast. This is shown for a double pulse switching test in Fig. 3.4, which also demonstrates the validity of the SPICE model in Fig. 3.3. The simulation is run both with and without the influence of 86 pF from auxiliary circuitry on the experimental setup. This highlights how the parasitic capacitance can be indirectly verified by measurement of on the heat sink voltage.

Fig. 3.4: Heatsink voltage during a double pulse switching test. [Paper A]

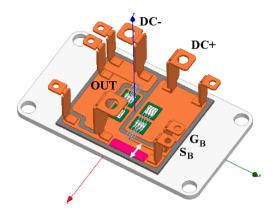

### 3.1.2 Design and test of prototype with low parasitic capacitance

The most effective way to solve the electromagnetic interference (EMI) issue is to decrease the common mode current by reducing the parasitic capacitances. The initial power module layout is shown in Fig. 3.2, which has a total output capacitance ( $C_{\sigma out} + C_{\sigma GB}$ ) of 168 pF. Some of the main changes for a new layout is that the ability for paralleling dies is removed. The gate driver connection points are kept in the same location, but the terminals are rotated such that the connection point is outside the perimeter of the DBC. This reduced the parasitic output capacitance to 98 pF.

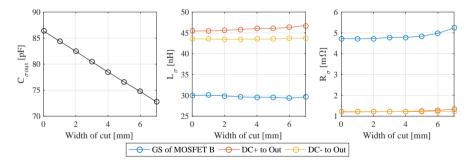

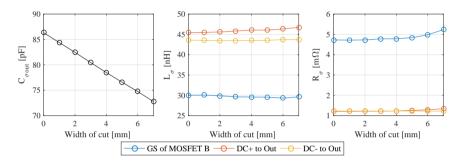

A relatively large part of the output copper plane is used for the connection to the source terminal,  $S_B$ . Floating copper planes are utilized to reduce the copper area of the output plane. When choosing the size of one of these floating planes, it is noted that it is close to the expected current paths, and thus might affect the parasitic inductances. An ANSYS Q3D Extractor simulation is setup, which includes a parametric sweep of the size of the area which is to be converted to a floating area, as indicated by the marked area in Fig. 3.5.

#### 3.1. Challenges in medium voltage operation of SiC MOSFETs

Fig. 3.5: The width of indicated area is swept using ANSYS Q3D Extractor. [Paper A]

The three paths which are considered are from DC+ to the output terminal, from DC- to the output and the gate-source loop of MOSFET B. The inductances are evaluated according to Method B of Section 2.1. While increasing the width of the removed area, the parasitic inductance, parasitic resistance and output capacitance are monitored. The results are shown in Fig. 3.6. The results show that the parasitic capacitance is linearly decreasing as the width of the region removed is increased, while the parasitic inductance and resistance are nearly unaffected.

**Fig. 3.6:** Simulated  $C_{\sigma out}$ ,  $L_{\sigma}$  and  $R_{\sigma}$  for three critical paths as the width of the floating area is increased. [Paper A]

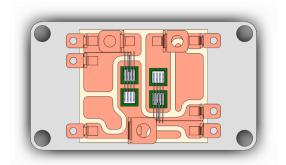

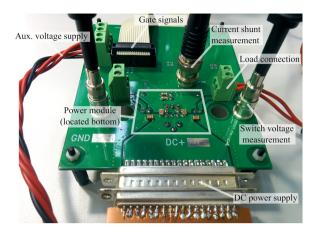

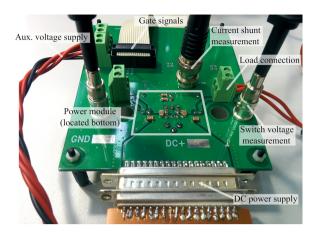

The final power module layout is shown in Fig. 3.7. An experimental setup is designed to perform a double-pulse test of the new power module. Gate driver boards and a medium voltage experimental test bench are designed and build by Nicklas Christensen, Dipen Narendrabhai Dalal and Simon Dyhr Sønderskov *et al.* as described in [40], [74].

The new power module is tested in the medium voltage test bench and

Chapter 3. Wide bandgap power module prototypes

Fig. 3.7: Updated 10 kV SiC MOSFET power module design with lowered parasitic capacitance.

Fig. 3.8: Picture of manufactured 10 kV SiC MOSFET power module.

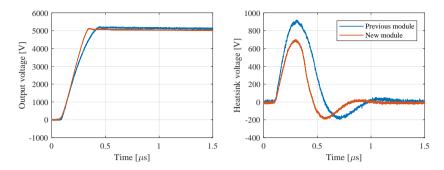

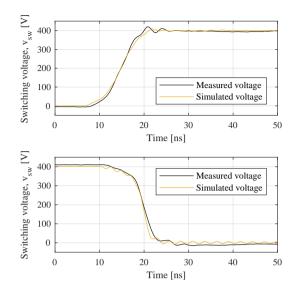

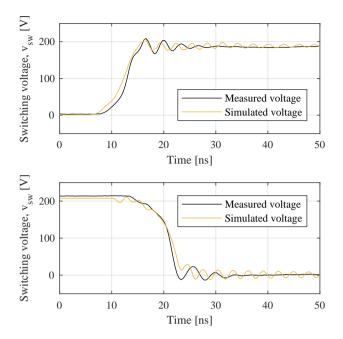

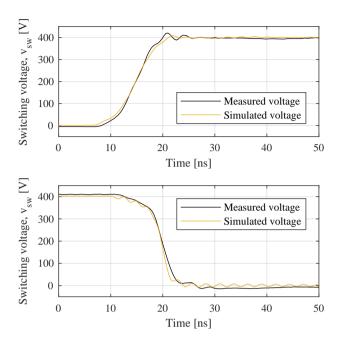

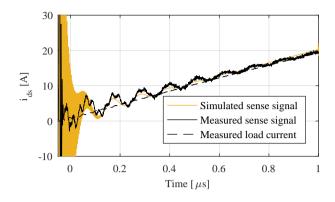

the switching output voltage and the generated heat sink voltage is compared with the previous module, as shown in Fig. 3.9. The results highlight that the reduction in total parasitic output capacitance from 167 pF to 85 pF (73 pF from  $C_{\sigma out}$  and 12 pF from  $C_{\sigma GB}$ ) results in a reduction in switching time of 15 %, while the amplitude of the heat sink voltage has been reduced by 26 %.

## 3.2 An integrated high frequency power module

One of the benefits of the WBG semiconductor devices, is the ability to be operated at higher frequencies. Smaller device area is required to obtain the same voltage and current ratings as a Si device, which results in reduced device capacitances. Often for high frequencies resonant gate driver circuits are used,

#### 3.2. An integrated high frequency power module

Fig. 3.9: Comparison of output voltage and generated heat sink voltage during 5 kV / 5 A switching of the previous and new 10 kV SiC MOSFET power modules.

as they enable recovery of some of the gate charge. Resonant gate drivers have less strict requirements of the gate-source loop inductance, as it is included as a part of the resonant oscillating loop [75]. Resonant gate drivers use more components, such as capacitors and inductors, which distribute the gate losses and reduces overheating of gate driver circuitry [76]. But it comes at the cost of resonant gate drivers being more complex to design. A hard switched gate driver IC is advantageous for many applications because of its increased control flexibility, increased power density and simpler implementation [77], [78]. But two main prerequisites for the solution is the capability of handling the increased gate losses of a hard-switched gate driver and strict requirements that the inductance is low enough to avoid oscillations due to a steep slope of the gate voltage input waveform.

S. Guo *et al.* [28], [33] have shown good performance of a 650 V SiC MOSFET power module with integrated gate driver. The gate driver is soldered to the DBC inside the power module, meaning it has a structure similar to what was shown in Fig. 1.5. Good switching performance of the SiC MOSFET device was demonstrated.

In this section, two aspects are further studied in detail. First of all it is analyzed how low inductance is required in the gate-source loop to achieve the clean switching. Secondly, the change in thermal performance of the gate driver IC is analyzed when placed on DBC inside the power module versus a typical placement on a PCB. Without these two assessments it could prove that the SiC MOSFETs perform very well on their own and that discrete packages are sufficient [79]. If relatively high inductance is allowed and the thermal performance is good enough on a PCB, it would mean that there is no requirement for integration of the gate-driver circuit inside the power module to achieve high switching frequencies of SiC MOSFETs.

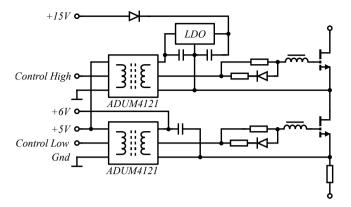

This is investigated using a platform of a Class E resonant converter to be operated at a frequency of 2.5 MHz. A custom SiC MOSFET power module with integrated gate driver IC is designed. The components to be integrated Chapter 3. Wide bandgap power module prototypes

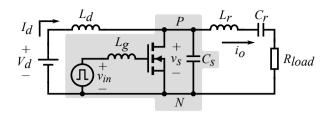

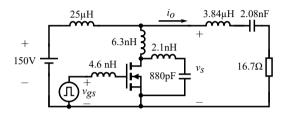

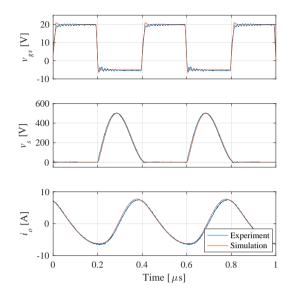

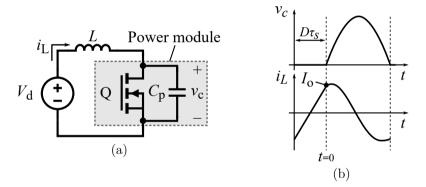

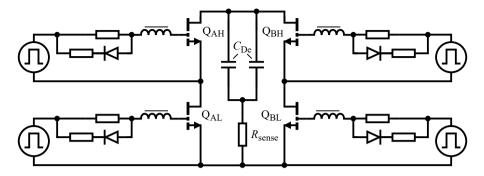

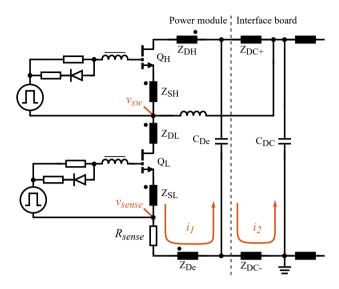

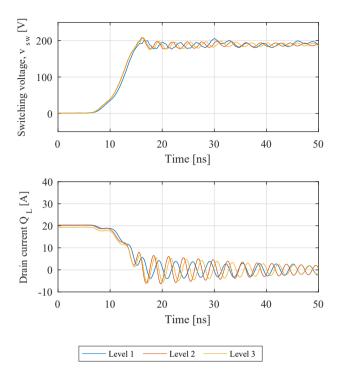

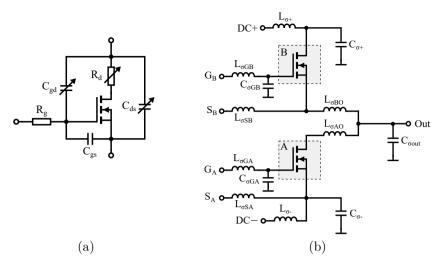

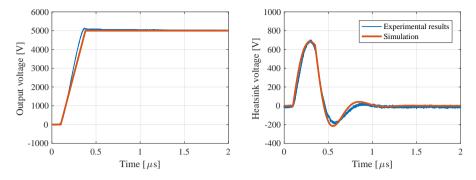

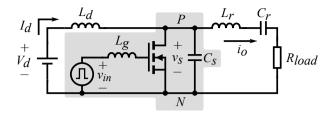

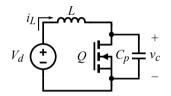

Fig. 3.10: Class E schematic with integrated components marked [Paper B].

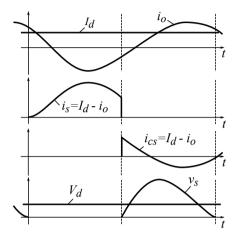

Fig. 3.11: Class E converter waveforms.

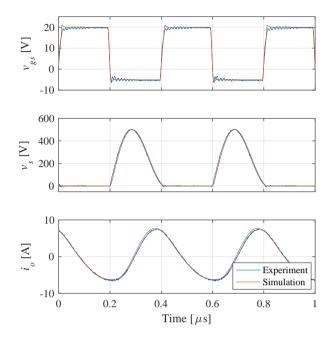

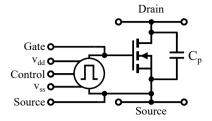

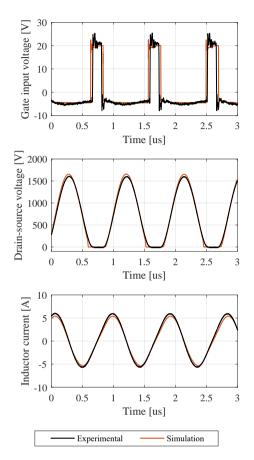

inside the power module are marked in Fig. 3.10. The ideal Class E resonant converter waveforms are shown in Fig. 3.11. When the switch turns on/off the current is abruptly shifted between the external parallel capacitance,  $C_s$  and the switch. Thus, to reduce the noise generated the external parallel capacitance is also included inside the package.

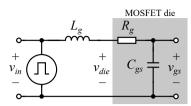

### 3.2.1 Analysis of gate driver dynamics for fast switching

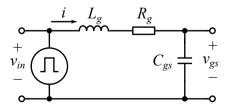

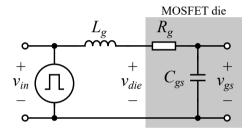

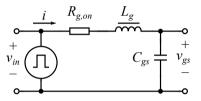

Part of achieving fast switching speeds, is to ensure the correct dynamics of the gate-source voltage. Often a gate resistor is placed between the gate driver IC and the MOSFET, which helps dampening the gate-source loop and results in a robust but slow transient of the gate-source voltage. If a too small resistance is used it leads to oscillations of the gate-source voltage, which may propagate as undesirable high frequency noise on the drain-source voltage of the MOSFET [18], [80]. The purpose of this section is to describe the dynamics of the gate-source loop, to achieve a fast and non-oscillating gate-source voltage. The parasitics included in the gate-source loop are shown in Fig. 3.12

#### 3.2. An integrated high frequency power module

Fig. 3.12: Parasitics included in the gate-driving loop [Paper C]

Kirchoffs voltage law is applied to the circuit in Fig. 3.12

$$v_{\rm in}(t) = L_{\rm g} \frac{{\rm d}i(t)}{{\rm d}t} + i(t)R_{\rm g} + v_{\rm gs}(t)$$

(3.2)

Taking the Laplace transform of (3.2) results in

$$V_{\rm in}(s) = L_{\rm g} \cdot s \cdot I(s) + I(s)R_{\rm g} + V_{\rm gs}(s)$$

$$(3.3)$$

By inserting  $I(s) = C_{\rm gs} \cdot s \cdot V_{\rm gs}(s)$  to (3.3) and rearranging

$$V_{\rm in}(s) = V_{\rm gs}(s)(L_{\rm g} \cdot C_{\rm gs} \cdot s^2 + C_{\rm gs} \cdot R_{\rm g} \cdot s + 1)$$

$$(3.4)$$

From (3.4) the transfer function becomes

$$\frac{V_{\rm gs}(s)}{V_{\rm in}(s)} = \frac{1}{L_{\rm g} \cdot C_{\rm gs} \cdot s^2 + C_{\rm gs} \cdot R_{\rm g} \cdot s + 1}$$

(3.5)

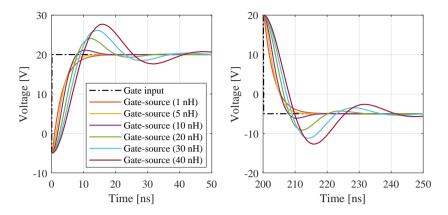

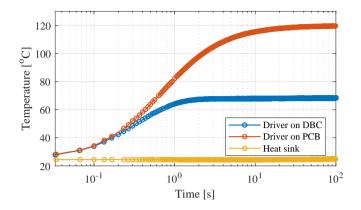

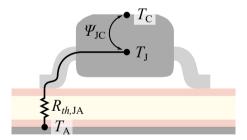

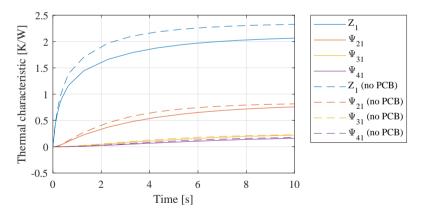

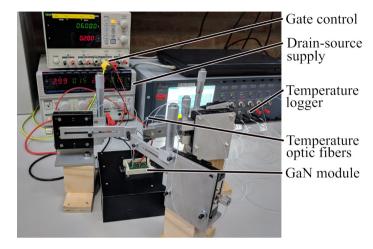

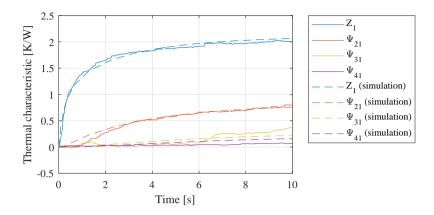

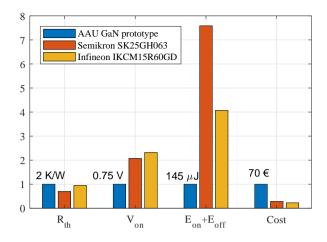

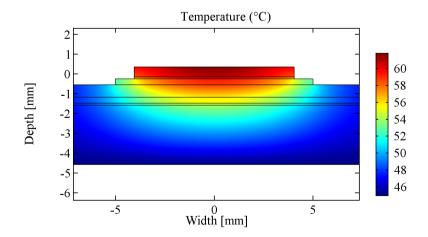

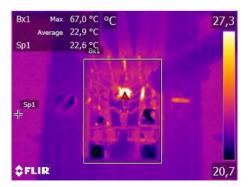

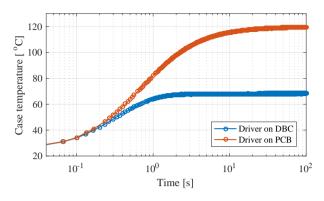

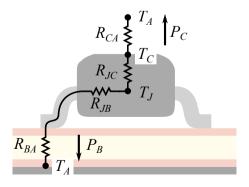

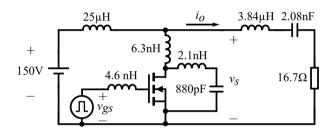

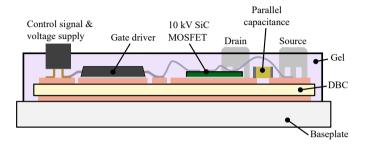

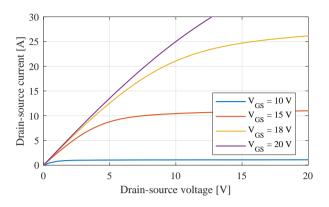

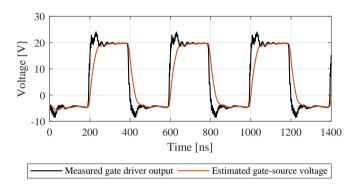

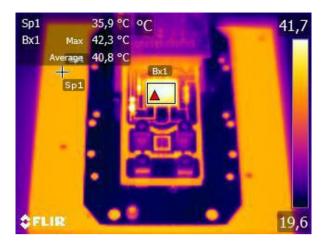

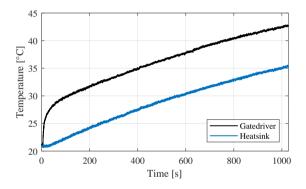

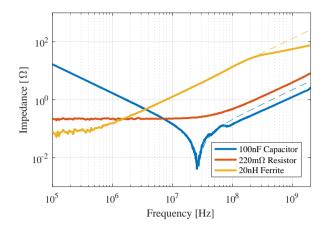

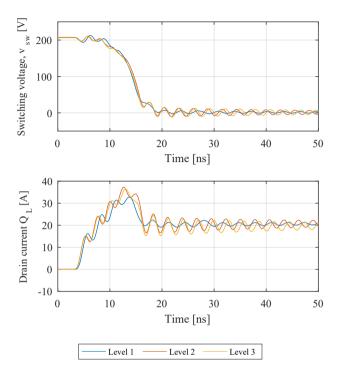

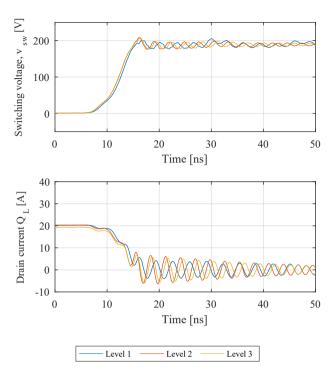

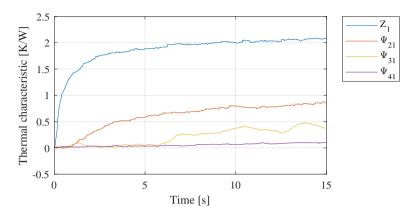

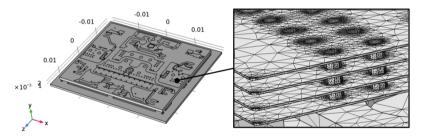

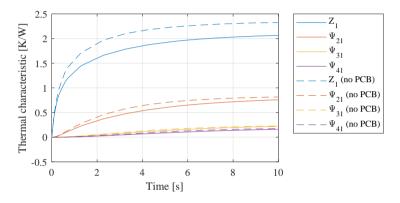

The standard form for a 2nd order system is shown in (3.6)