Aalborg Universitet

## Modeling of igbt with high bipolar gain for mitigating gate voltage oscillations during short circuit

Reigosa, Paula Diaz: Iannuzzo, Francesco: Corvasce, Chiara: Rahimo, Munaf

Published in: IEEE Journal of Emerging and Selected Topics in Power Electronics

DOI (link to publication from Publisher): 10.1109/JESTPE.2019.2913044

Publication date: 2019

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Reigosa, P. D., lannuzzo, F., Corvasce, C., & Rahimo, M. (2019). Modeling of igbt with high bipolar gain for mitigating gate voltage oscillations during short circuit. *IEEE Journal of Emerging and Selected Topics in Power Electronics*, 7(3), 1584 - 1592. [8698267]. https://doi.org/10.1109/JESTPE.2019.2913044

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

? You may not further distribute the material or use it for any profit-making activity or commercial gain

? You may freely distribute the URL identifying the publication in the public portal ?

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Modelling of IGBT with High Bipolar Gain for Mitigating Gate Voltage Oscillations during Short Circuit

Paula Diaz Reigosa<sup>a</sup>, Francesco Iannuzzo<sup>b</sup>, Chiara Corvasce<sup>c</sup> and Munaf Rahimo<sup>d</sup>

<sup>a</sup> University of Applied Sciences Northwestern Switzerland FHNW, Klosterzelgstrasse 2, CH-5210, Switzerland

<sup>b</sup> Department of Energy Technology, Aalborg University, Pontoppidanstraede 111 DK-9220, Denmark

<sup>c</sup>ABB Switzerland Ltd. Semiconductors, CH-5600, Lenzburg, Switzerland

<sup>d</sup> MTAL GmbH, Gnsbrunnen, Switzerland

Abstract—In this paper, the impact of the PNP bipolar transistor gain on the short-circuit behaviour of High Voltage Trench IGBTs is analysed. The short circuit ruggedness against highfrequency oscillations is strongly improved by increasing the hole current supplied by the collector. By doing so, the electric field at the emitter of the IGBT is increased and less influenced by the amount of the excess charge (i.e., the electric field is fixed). The charge-field interactions during the short circuit event, leading to a periodic charge storage and charge removal effect and provoking miller capacitance variations, can be mitigated. The effectiveness of using IGBTs with high bipolar gain is validated through both simulations and experiments, also a design rule to trade off the IGBT's losses and short-circuit robustness is provided.

*Index Terms*—Insulated gate bipolar transistor, bipolar gain, short circuit, gate oscillations, parametric oscillation, robustness, Kirk Effect, TCAD.

### I. INTRODUCTION

In the event of a short circuit, IGBTs have shown a good capability of withstanding high current and high voltage for a limited amount of time, named short-circuit withstanding time  $t_{sc}$  [1]. Some applications such as solar inverters, motor drives and wind converters have standard requirements for this parameter (i.e.,  $t_{sc} = 5 - 10 \ \mu$ s). During this period the protection circuit must succeed in turning off the IGBT, however, the IGBT may fail due to unstable operation, before the gate driver protection is able to turn-off the IGBT (i.e., failure in the range of nanoseconds) [2]. One of the instabilities occurring during short circuit is the occurrence of high-frequency gate oscillations [3]–[5], where the gate driver is no longer able to protect the converter from IGBT failures.

Many experimental works show that under adverse combinations (i.e., large circuit stray inductance and low gate resistance) and under certain operating conditions (i.e., low DC-link voltage), IGBTs exhibit high-frequency oscillations as it has been found in [3], [5], [6] for planar IGBTs and, recently, for trench-gate, field-stop IGBTs [4], [7]–[10]. This instability may cause the destruction of the gate-oxide, in the case that the oscillation amplitude runs out of control, as reported in [3], [11] for planar IGBTs and in [9] for trench IGBTs. In an attempt to solve the problem, the short-circuit robustness of IGBTs have been studied from three aspects: device design [12], package design [13], and gate driver design [14]. Although several measures have been implemented, short circuit failures as a consequence of high-frequency oscillations are still observed in practical applications. The problem was not fully understood until recently, where the complex behavior of the IGBT with both circuit and device analysis has been investigated in [6]. It has been proposed that the root cause of such oscillatory behaviour is a parametric oscillation involving the IGBT and the gate circuit. It has been discovered that the oscillations can only start when the electric field at the emitter side of the IGBT becomes weak. The low electric field is influenced by the amount of the excess charge at the emitter and therefore the field starts to fluctuate with time. The electric field fluctuations creates charge accumulation variations at the emitter of the IGBT, which in turn leads to Miller capacitance variations. Thanks to the results from TCAD simulations, it has been possible to associate the capacitance variation with charge-storage effects occurring at the surface of the IGBT, arising from the low carrier velocity. Therefore, the time-varying element during the parametric oscillation is the IGBT's Miller capacitance, leading to an amplification mechanism.

With the purpose of mitigating the oscillation phenomenon, care must be taken into the optimization of the carrier profile in IGBTs. The aim is to increase the electric field at the IGBT's surface and counteract the weak electric field. A sensitivity study has been performed in [6], [11], [15] and later in [10], varying different parameters and investigating its influence on the short-circuit oscillation behavior. Those studies have proven that the IGBT oscillations are more likely to be observed when the device is operated at low DC-link voltages, high positive gate voltages and low case temperatures, because the electric field becomes weaker at the emitter. There are several possibilities to achieve the desired carrier profile to make sure that the electric field at the surface is high; the most widely used are: a) high bipolar gains b) profiled lifetime control techniques c) increase of the drift region doping concentration and d) reduction of the electron injection from the MOS-channel. Among them, the increase of the IGBT collector efficiency (i.e., the PNP bipolar gain) has been selected in this work to mitigate the short-circuit oscillations in IGBTs. The impact of the collector dose concentration on the

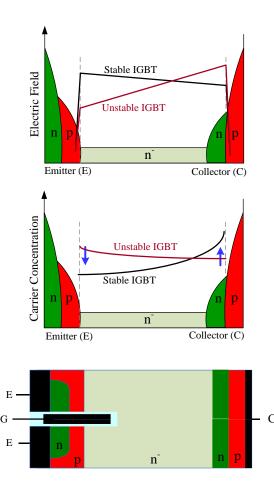

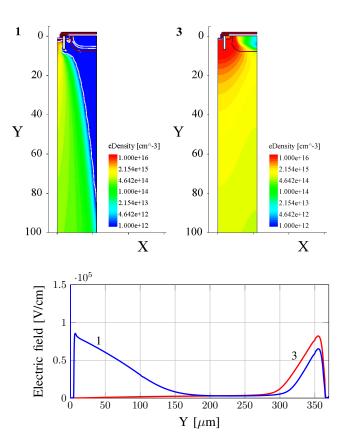

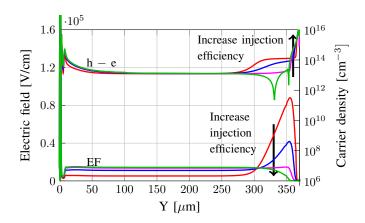

Fig. 1. Carrier profile distribution and electric field shape in Field Stop Trench IGBTs leading to stable and unstable operation during short-circuit events.

oscillation phenomenon will be investigated from both finiteelement simulations and experimental validation.

This paper is organized as follows: Section II presents the Kirk Effect phenomenon in IGBTs, typically observed under short circuit conditions. Section III introduces the IGBT model that is used for the finite-element simulations. Section IV demonstrates that the oscillation phenomenon can be mitigated with high bipolar gain. Section V shows that by adjusting the  $P^+$  collector dose of the IGBT, the oscillations are effectively mitigated through experimental tests. Section VI and Section VII discuss about possible design rules for robust short circuit operation and the final conclusions, respectively.

## II. KIRK EFFECT IN IGBTS UNDER SHORT CIRCUIT

One of the main problems of the Insulated-Gate Bipolar Transistor (IGBT) lies in the fact that under certain current densities, a low electric field is observed at the surface of the IGBT, which eventually leads to an electric field rotation [16]. This phenomenon is referred as the Kirk Effect, which is a very unstable condition that typically occurs in IGBTs under short circuit conditions. The Kirk Effect has been proven in [6] to be a necessary condition for driving the IGBT into an oscillatory mode, therefore, it is important to understand the limiting conditions that will lead to the initiation of oscillations. The gradient of the electric field strength dE/dy is function of the

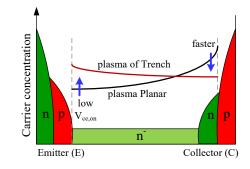

Fig. 2. Evolution of the IGBT technology depending on different vertical designs and its correlation with the electric field strength: NPT - Non-Punch-Through, SPT - Soft-Punch Through, FS - Field Stop.

Fig. 3. Evolution of the IGBT cell design for better trade-off between switching and conduction losses.

effective charge concentration in the n-base  $(N_{effective})$  and can be calculated with the Poisson's equation [1], given as:

$$\frac{dE}{dx} = \frac{q}{\epsilon_s}(N_D + h - e) \tag{1}$$

where  $\epsilon_s$  is the dielectric permittivity of the semiconductor, q is the electron charge,  $N_D$  is the drift doping concentration, h is the hole density and e is the electron density.

In Fig. 1 two IGBT designs are shown: one is prone to oscillations because the carrier distribution profile leads to a rotated electric field (unstable), and the other one presents a carrier distribution profile leading to a triangular-shape electric field, which is robust against oscillations (stable).

The carrier distribution can be shaped for preventing the electric field rotation; the impact of the carrier distribution is presented in the following:

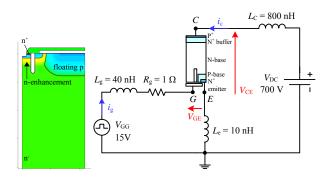

- Vertical IGBT design (i.e., Non-Punch Through NPT, Punch-Through PT, Soft-Punch Through SPT or Field Stop FS). As the cell structure becomes thinner from NPT or conventional PT to SPT technologies, the doping concentration in the drift layer is decreased to achieve similar blocking capability. This means that the gradient of the electric field becomes flatter and it may eventually rotate (see Fig. 2). Therefore, one must ensure that the back-side design does not bring the IGBT into an unstable situation where the electric field rotates.

- 2) IGBT cell topology (i.e., planar, trench, enhancement layers, Side Gate). As the cell evolves from planar to

trench designs, the trend is to reduce on-state losses by increasing the electron current density (majority carriers), as pointed out in Fig. 3. This, in turn, may set the conditions for having a rotated electric field. Furthermore, if the hole carrier density (minority carriers) is relatively small, for achieving a fast IGBT with low switching losses, the electric field would rotate even more (see Fig. 3). The optimization of IGBTs to have low on-state and low switching losses can be done up to a limit, which is related to the shape of the electric field under short circuit conditions.

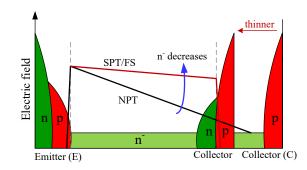

#### **III. IGBT SIMULATION MODEL**

Mixed-mode device simulations have been carried out using the TCAD Sentaurus simulation tool. The doping profile of the 3.3-kV Enhanced-Trench IGBT and the circuit model used to perform the short circuit simulations are shown in Fig. III. Only the emitter side is presented in Fig. III, showing that an n-enhancement layer and a lightly doped p-well region have been implemented. The collector side, which is not shown in Fig. III, has a Soft-Punch Through (SPT) buffer.

The IGBT model has been calibrated to match the real characteristics of the tested devices. The drift region thickness has been adjusted to achieve a blocking voltage of 3,300. The effective area of the IGBT is 0.4 cm<sup>2</sup>, yielding a nominal current of 50 A.

Short-circuit simulations have been carried out including the external circuit of Fig. III, whose values are selected to be in agreement with the experimental setup, but also favouring the occurrence of the oscillation phenomenon. Since the stray inductances are involved in the oscillation phenomenon, not being the main triggering mechanism but taking part of it, the dependence of the gate inductance and collector inductance in respect to the oscillation phenomenon is investigated in the following. The effect of the emitter inductance is a little complex because it takes part in both gate and commutation paths, therefore, this investigation is not presented for the trench IGBT. The effect of emitter inductance on the short circuit oscillations for planar IGBTs has been explained in [17], [18].

Fig. 4. The 3.3-kV enhanced-trench IGBT half cell (left) and the circuit to perform the short-circuit simulations with TCAD (right).

3

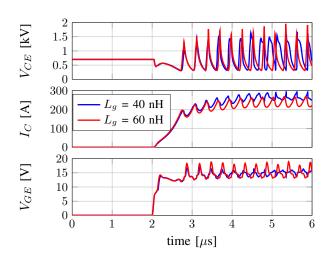

Fig. 5. Short-circuit simulation showing the oscillation dependency as a function of the gate inductance  $L_g$ . Conditions:  $L_C = 800 \ \mu$ H,  $L_e = 10 \ n$ H,  $R_g = 1 \ \Omega$ ,  $V_{GE} = 15 \ V$  and  $V_{DC} = 700 \ V$ .

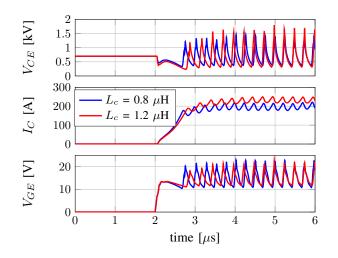

Fig. 6. Short-circuit simulation showing the oscillation dependency as a function of the collector inductance  $L_C$ . Conditions:  $L_g = 40$  nH,  $L_e = 10$  nH,  $R_g = 1 \Omega$ ,  $V_{GE} = 15$  V and  $V_{DC} = 700$  V.

## A. Effect of gate inductance, $L_g$

The variation of the gate stray inductance  $L_g$  and its impact on the short-circuit oscillation phenomenon for the 3,300 V Trench IGBT has been evaluated. The simulation results show a similar trend, as previously investigated for the planar IGBTs in [18]. In Fig. 5 is observed that the gate inductance,  $L_g$ , affects the IGBT short-circuit behaviour in two ways:

- 1) With higher gate inductance  $L_g$ , an increased oscillation amplitude on the gate voltage waveform can be observed.

- 2) The oscillation frequency increases with decreasing  $L_q$ .

The observed oscillation amplification with higher gate inductance is related to the parametric oscillation phenomenon. The energy transferred between the gate inductance and the IGBT's miller capacitance is now larger because the gate inductance is also bigger and more energy can be transferred.

4

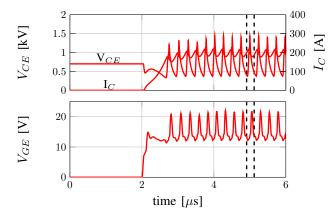

Fig. 7. Simulated voltage and current waveforms of the 3.3-kV IGBT with  $p^+$  collector doping of  $1\cdot 10^{17}$  cm<sup>-3</sup>.

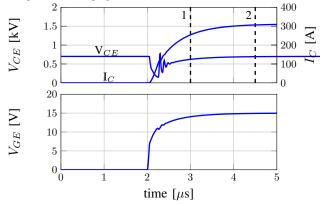

Fig. 8. Simulated voltage and current waveforms of the 3.3-kV IGBT with  $p^+$ collector doping of  $3 \cdot 10^{17}$  cm<sup>-3</sup>.

## B. Effect of collector inductance, $L_C$

The impact of the collector stray inductance  $L_C$  variation on the short-circuit oscillation phenomenon for the 3,3-kV Trench IGBT has also been evaluated. The implication of the collector inductance to the short-circuit oscillation phenomenon is similar as for the planar IGBTs in [18]. As observed in Fig. 6, the collector inductance,  $L_C$ , affects the IGBT short-circuit behaviour in three ways:

- 1) The gate oscillation amplitude does not change with  $L_C$ .

- 2) The oscillation frequency increases with decreasing  $L_C$ .

- 3) With higher  $L_C$ , an increased undershoot across the collector-emitter voltage can be observed.

The oscillation amplitude does not change with the value of the collector inductance because the  $L_C$  is not involved in the gate oscillation path. Nevertheless, an increased collector inductance leads to a greater undershoot across the collectoremitter voltage leading to a lower electric field, thus, favoring the Kirk effect onset.

## IV. EFFECT OF HIGH BIOLAR GAIN

## A. Effect of collector doping concentration

The charge-field interactions can be counteracted by increasing the electric field at the emitter of the IGBT, in this way, the electric field becomes strong and not influenced by the excess

Fig. 9. Time-zoom of Fig.7.

of carriers in this region. One option to achieve a stronger electric field is to increase the hole injection, for example, by increasing the bipolar current gain  $\alpha_{pnp}$  [15]. This can be done by selecting a higher doping concentration of the p<sup>+</sup> collector layer.

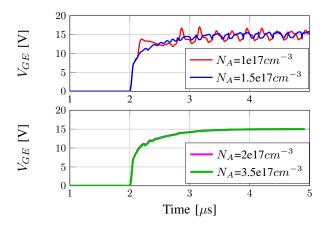

Figs. 7 and 8 show the short-circuit simulations of the 3.3kV enhanced trench IGBT, having the same doping profiles but employing different collector doping concentrations of  $1 \cdot 10^{17}$  cm<sup>-3</sup> and  $3 \cdot 10^{17}$  cm<sup>-3</sup>, respectively. It is clear that the adjustment of the doping concentration at the collector brings the benefit of improving the stability of the device during short circuit. By adopting this strategy, oscillations are mitigated with high bipolar gains (i.e., higher p<sup>+</sup>collector doping).

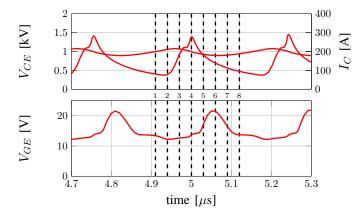

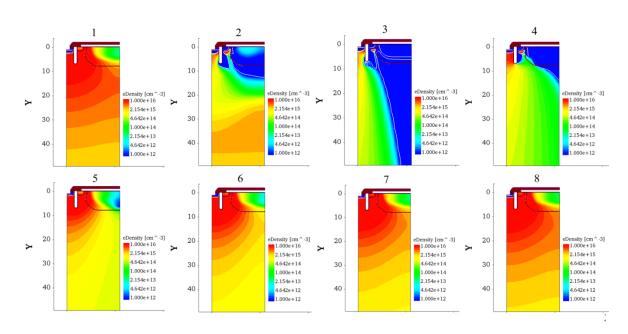

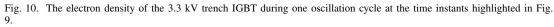

A better understanding of the phenomena taking place inside of the IGBT can be gained by looking at Figs. 9, 10 and 11. In Fig. 9 is presented a time zoom of Fig. 7 between the time instants 4.91  $\mu$ s and 5.12  $\mu$ s. This graph helps to illustrate the phase-shift relation between the electrical waveforms (gate voltage, collector current and collector-emitter voltage) and the 2-D effects happening inside the device. The evolution of the 2-D electron density effects at the time instants highlighted in Fig. 9 are plotted together with the 2-D electric field fluctuations in Figs. 10 and 11, respectively. By looking at the time instants 1, 5, 6, 7 and 8 is evident that the electric field at the emitter is weak coinciding with a charge-storage effect, which increases the miller capacitance. The junction capacitance  $C_{CE}$  value also changes with the variation of the electric field, however to a lesser extend. It would be possible to discuss about a parametric oscillation involving the IGBT and the power circuit, but since the experiments show the highest amplification on the gate loop, the parametric oscillation on the power circuit has been discarded.

In the time instants 2, 3 and 4, the voltage across the device is high and the electric field at the emitter is strong associated with a low electron charge density and therefore lower miller capacitance values. A vertical cut of the IGBT has been performed in order to show the electric field shape differences between the time instant when the collector emitter voltage is high and low. This effect can be observed in Fig. 12 for the IGBT with low collector doping level, proving that the IGBT shows two different modes during each oscillation

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/JESTPE.2019.2913044, IEEE Journal of Emerging and Selected Topics in Power Electronics

5

Fig. 11. The electric field of the 3.3 kV trench IGBT during one oscillation cycle at the time instants highlighted in Fig. 9.

cycle:

- 1) Electrons flow vertically coinciding with a strong electric field at the emitter. This occurs when  $V_{CE}$  rises in Fig. 9.

- 2) Electrons accumulate at the surface of the IGBT, coinciding with an electric field peak stronger at the collector. This occurs when  $V_{CE}$  is the low in Fig. 9.

This phenomenon leads to a time-varying capacitance coinciding with a high capacitance when the charges are accumulated at the surface and having a small capacitance when there are no-charge storage effects. This behavior has been recognized as a parametric oscillation in [6]. The charge-field interactions are happening because the electric field at the emitter is not sufficiently strong, and therefore, the plasma has a strong effect on the electric field which leads to a varying electric field.

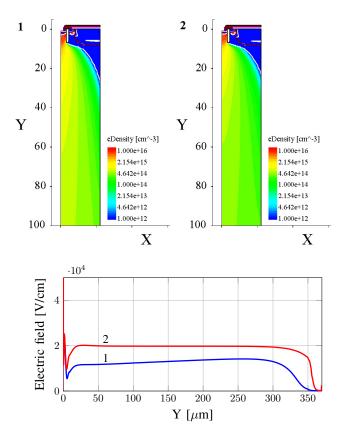

The field-charge interactions are not longer observed when the IGBT with high collector doping is simulated. Fig. 13 illustrates the 2D-plots during the short-circuit time instants highlighted in Fig. 8 with an IGBT design having a higher collector doping concentration. In this case, the short circuit oscillations are not observed and the charge-storage effect neither. Now the electric field becomes dominant over the plasma, resulting in a fixed carrier profile and an electric field

Fig. 12. Short-circuit behaviour of the 3.3-kV Enhanced-Trench IGBT with  $p^+$  collector doping of  $1 \cdot 10^{17}$  cm<sup>-3</sup>, at the time instants 1 and 3 highlighted Fig. 9. Left: electron density; right: electric field.

TABLE I

The effect of the Soft-Punch Through design [19].

|               | On-state<br>losses | Turn-off<br>losses | Recovery softness | Leakage<br>current | Breakdown<br>voltage | Short<br>Circuit |

|---------------|--------------------|--------------------|-------------------|--------------------|----------------------|------------------|

| High PNP gain | +                  | -                  | +                 | -                  | +                    | -                |

| Low PNP gain  | -                  | +                  | -                 | +                  | -                    | +                |

shape that is always strong at the emitter. In this way, the Miller capacitance does not vary with time and the oscillations during short circuit are not observed.

#### B. High bipolar gain trade off

Increasing the collector doping concentration is one approach that can be followed for better short-circuit ruggedness. The buffer design is strongly dependent on the PNP bipolar transistor gain, therefore, an increase of the collector doping concentration leads to higher bipolar gain. It has been shown in [19] that a trade-off relationship exists depending on the value of the PNP bipolar gain. According to Table I, increasing the collector doping concentration for higher short circuit robustness can be achieved at the expense of increased turn-off losses, increased leakage current and weaker turn-off Reverse Bias Safety Operation Area (RBSOA).

## C. IGBT Losses and Short-Circuit Robustness Trade Off

1) Study Case: The improvement of the short-circuit robustness comes with compromises in respect to normal op-

Fig. 13. Short-circuit behaviour of the 3.3-kV enhanced-trench IGBT with  $P^+$  collector doping of  $3 \cdot 10^{17}$  cm<sup>-3</sup>, at the time instants 1 and 2, highlighted in Fig. 8. Left: electron density; right: electric field.

eration. By increasing the doping concentration of the P<sup>+</sup> collector, the carrier distribution profile is shaped in a way that the IGBT builds up a denser plasma near the collector. This means that the IGBT will become more stable under short circuit at the expense of increased turn-off losses under normal operations. Therefore, an optimization procedure is needed in order to achieve the minimum injection efficiency to keep the effective charge density positive at the worst conditions, i.e., room temperature (T<sub>case</sub> = 25°C) and minimum gate voltage (V<sub>GE</sub> = 15 V) [4], [11].

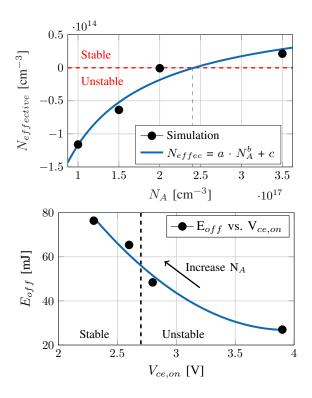

First, the 3,300 V Enhanced-Trench IGBT has been simulated under short-circuit conditions at  $V_{CE} = 700$  V and  $T_{case} = 25^{\circ}$ C, varying gradually the peak collector doping concentration from N<sub>A</sub> = 1e17 cm<sup>-3</sup> up to 3.5e17 cm<sup>-3</sup>. Fig. 14 demonstrates once again that the IGBT short-circuit operation becomes stable with increased injection efficiency.

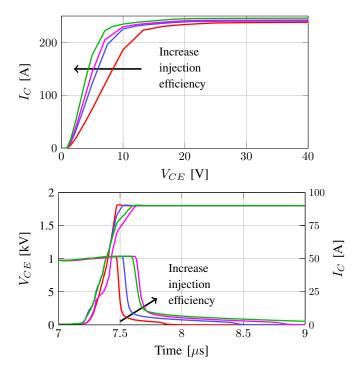

The next step is to study the impact of the peak collector doping concentration on the on-state losses. Fig. 15 presents the typical forward characteristics at  $V_{GE} = 15$  V and  $T_{case} = 25^{\circ}$ C, for the Trench IGBT having four different collector doping doses. It is observed that for the nominal current of 50 A, the IGBT with the highest peak collector doping concentration (i.e.,  $N_A = 3.5e17$  cm<sup>-3</sup>) shows the smallest onstate voltage. In Fig. 16, the vertical profiles of the electric field strength and the carrier densities in the drift zone are compared in the static I-V curve. The results show that a denser carrier concentration at the emitter side is observed for the largest

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/JESTPE.2019.2913044, IEEE Journal of Emerging and Selected Topics in Power Electronics

Fig. 14. Short-circuit simulations of the 3.3-kV trench IGBT at  $V_{CE} = 700$  V and 25°C, with different collector doping concentrations ( $N_A$ ) showing stable and unstable behaviours.

collector doping concentration, hence the on-state losses are reduced. The fact that the short-circuit robustness and on-state losses can be optimized simultaneously is an attractive option for applications where the switching frequency is low.

The turn-off losses have also been evaluated by means of mixed-mode simulations at the nominal conditions, i.e., 1,800 V collector voltage and 50 A collector current. The gate resistance and the load inductance have been chosen as 10  $\Omega$  and 2,400 nH, respectively. The results from the TCAD simulation with four different collector doping doses are shown in Fig. 15. Due to increased collector doping concentration (N<sub>A</sub>), the turn-off tail current has a higher amplitude leading to increased turn-off losses. In Fig. 16 can be observed that with increasing injection efficiency, there are excess carriers in the proximity of the collector region that must be swept out during the turn-off transition, i.e., they contribute to the turn-off losses.

2) Stability Map: It has been demonstrated that the stability of the IGBT under short circuit conditions has a negative impact on the turn-off losses since high-injection efficiency emitter IGBT designs are needed to counteract the Kirk Effect. The stable operation can be achieved when the effective charge concentration ( $N_{effective}$ ) is greater than 0, being  $N_{effective}$ equal to 0 the limit of stability. Fig. 17 shows the relationship between the collector doping concentration ( $N_A$ ) and the effective charge concentration ( $N_{effective}$ ) extracted from the TCAD simulations when the Trench IGBT is simulated with four different collector doping concentrations. The optimum value of  $N_A$  can be calculated as a function of  $N_{effective}$ through the proposed fitting curve:

$$N_{effective} = a \cdot N_A^b + c \tag{2}$$

where the coefficients a, b and c are the fitting parameters (a = -5.9E28, b = -0.8 and c = 1E14). The optimum value of N<sub>A</sub> must be equal or greater than 2.4e17 cm<sup>-3</sup>.

## V. SHORT CIRCUIT EXPERIMENTS

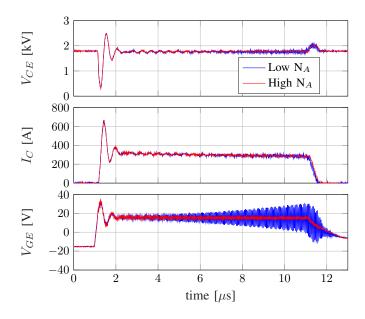

The IGBT short-circuit capability has been experimentally investigated by adopting different PNP bipolar gains. Fig.

Fig. 15. Simulated static I - V curves at 25°C (left) and dynamic turn-off current and voltage waveforms at 50 A and 1.8 kV DC-link and 25°C (right).

Fig. 16. Simulated 3.3kV trench IGBT vertical cross-section showing the electric field and the difference between the holes and electrons at  $V_{CE}$  = 700V in the static I - V curve.

18 shows the short-circuit behaviour of two 3.3-kV IGBTs fabricated with different  $P^+$  collector doping doses. All design parameters except for the  $p^+$ collector dose were the same for the two devices. As it can be seen, the oscillatory behaviour is best seen with low injection efficiency designs, which is in agreement with the TCAD simulations results. Because of the lower bipolar gain, a decrease in the hole current injection from the collector is expected, revealing its large impact on the short-circuit instability of the device. The benefit of employing an IGBT with a high injection efficiency design is validated through the experiments, which corroborates the explanation from the internal physics angle that has been formulated and supported by finite-element simulations in Section IV.

2168-6777 (c) 2018 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Fig. 17. Stability map of the IGBT as a function of  $N_A$ : technology curve (left) and  $N_A$  vs. Kirk effect onset,  $N_{eff} < 0$  (right): a = -5.9e28, b = -0.8 and c = 1.0e14.

Fig. 18. Short-circuit experiments of the 3.3-kV SPT<sup>+</sup> trench IGBTs with different collector dopings.  $R_{g,on} = 2.2 \Omega$ ,  $L_{\sigma} = 600$  nH and  $T_{case} = 25^{\circ}$ C.

## VI. DESIGN RULES FOR ROBUST SHORT CIRCUIT OPERATION

The short-circuit performance of IGBTs is mainly determined by the carrier distribution profile and the associated electric field shape, which can be adjusted in several ways, depending on the targeted application. There are several design strategies in order to optimize the IGBT with respect to onstate losses (i.e., n-enhancement layers) and low turn-off losses (i.e., low hole injection supplied from the collector) which have been effectively implemented. These strategies can also be implemented by ensuring a robust operation during short circuit. The key is to ensure that the electric field is strong at the emitter side, which is possible if the following design rules are applied:

- Carrier enhancement at the emitter for low on-state losses. The IGBT can be designed to have a dense plasma near the emitter by adopting Trench cell designs [20], implementing n-enhancement layers [21] or by reducing the mesa width between trenches [22]. Modern IGBTs, which are designed in accordance with one of these approaches, have to provide a sufficient hole injection from the collector side in order to ensure shortcircuit stability.

- 2) Carrier reduction at the collector for low turn-off losses. The IGBT can be designed with relatively low carrier concentration at the collector, by employing IGBTs with low injection efficiencies or by localized lifetime control techniques [1]. Modern IGBTs, which are designed in accordance with one of these approaches, have to provide a smaller electron injection from the MOS channel to make sure that the electric field is sufficiently strong at the emitter.

- 3) Reduction of the thickness for low losses. The IGBT can be designed with smaller thickness with the purpose of minimizing the total power losses. The resistance of the device during the on-state phase decreases when using thinner IGBTs, for example, from Punch-Through to Non-Punch Through or Soft-Punch Through buffers. At the same time, to achieve the desired blocking capability for thinner devices, the doping concentration in the drift region is reduced. Modern IGBTs, which are designed in accordance with this approach, have to ensure that the relation between electrons and holes is optimum in order to guarantee that the effective charge density is still positive and thus a stable short circuit behavior.

#### VII. CONCLUSIONS

The gate oscillation phenomenon occurring in trench IGBTs under short circuit conditions is investigated through both finite-element simulations and experimental validation. The analysis has been demonstrated that the external circuit has an impact on the oscillation phenomenon, especially the gate inductance  $L_q$ , which is involved in the parametric oscillation between the IGBT and the gate circuit. It has been found out that the most effective way to mitigate the unstable operation is by shaping the carrier profile in a way that the electric field is sufficiently strong at the emitter under short circuit conditions. There are several ways to do so, one of them is to use IGBTs with a high hole injection supplied from the PNP bipolar transistor. Then, the electric field at th emitter of the IGBT is strong and less influenced by the plasma, which helps to counteract charge-storage effects happening at the emitter of the IGBT and affecting the Miller capacitance value, eventually leading to a parametric oscillation. Furthermore, it has been pointed out that the design elements of the Bipolar-mode Insulated Transistors (BIGTs) help to increase the robustness of the short circuit event against short circuit oscillations. The advantage of applying IGBTs with high bipolar gain is that high-frequency oscillations in the range of 20 MHz disappear, and failure mechanisms of this type are better understood. The main drawback of this approach is the increase in switching losses, but on the other hand, conduction losses can be further minimized. The proposed method has been validated through finite-element simulations, which are coherent with the experimental test in a 3.3-kV Enhanced-Trench IGBTs having different collector doping concentrations.

## REFERENCES

- [1] S. Linder, Power Semiconductors. EPFL press, First edition, 2006.

- [2] F. Iannuzzo, C. Abbate, and G. Busatto, "Instabilities in silicon power devices," *IEEE Industrial Electronics Magazine*, vol. 8, no. 3, pp. 28–39, Sept 2014.

- [3] I. Omura, W. Fichtner, and H. Ohashi, "Oscillation effects in IGBT's related to negative capacitance phenomena," *IEEE Transactions on Electron Devices*, vol. 46, no. 1, pp. 237–244, Jan 1999.

- [4] P. D. Reigosa, R. Wu, F. Iannuzzo, and F. Blaabjerg, "Evidence of gate voltage oscillations during short circuit of commercial 1.7 kV/1 kA IGBT Power Modules," in *Proc. of PCIM Europe 2015*, May 2015, pp. 1–8.

- [5] C. Abbate, G. Busatto, A. Sanseverino, F. Velardi, S. Iavarone, and C. Ronsisvalle, "Measurement of IGBT high-frequency input impedance in short circuit," *IEEE Transactions on Power Electronics*, vol. 32, no. 1, pp. 584–592, Jan 2017.

- [6] P. D. Reigosa, F. Iannuzzo, M. Rahimo, C. Corvasce, and F. Blaabjerg, "Improving the short-circuit reliability in igbts: How to mitigate oscillations," *IEEE Transactions on Power Electronics*, vol. 33, no. 7, pp. 5603–5612, July 2018.

- [7] K. Saito, T. Miyoshi, D. Kawase, S. Hayakawa, T. Masuda, and Y. Sasajima, "Suppression of self-excited oscillation for common package of Si-IGBT and SiC-MOS," in *Proc. of ISPSD*, May 2017, pp. 427–430.

- [8] T. Kikuchi, K. Nakamura, and K. Takao, "Investigation of the mechanism of gate voltage oscillation in 1.2kV IGBT under short circuit condition," in *Proc. of ISPSD*, May 2018, pp. 503–507.

- [9] P. Reigosa, R. Wu, F. Iannuzzo, and F. Blaabjerg, "Robustness of MW-Level IGBT modules against gate oscillations under short circuit events," *Microelectronics Reliability*, vol. 55, no. 9-10, pp. 1950–1955, Aug. 2015.

- [10] V. van Treek, H. Schulze, F. Niedernostheide, C. Sandow, R. Baburske, and F. Pfirsch, "Influence of doping profiles and chip temperature on short-circuit oscillations of IGBTs," in *Proc. of ISPSD*, May 2018, pp. 108–111.

- [11] P. D. Reigosa, F. Iannuzzo, and M. Rahimo, "TCAD analysis of shortcircuit oscillations in IGBTs," in *Proc. of ISPSD*, May 2017, pp. 151– 154.

- [12] A. Kopta, M. Rahimo, C. Corvasce, and et. al, "Next generation IGBT and package technologies for high voltage applications," *IEEE Transactions on Electron Devices*, vol. 64, no. 3, pp. 753–759, March 2017.

- [13] T. Basler, J. Lutz, R. Jakob, and T. Brckner, "The influence of asymmetries on the parallel connection of IGBT chips under short-circuit condition," in *Proc. of EPE*, Aug 2011, pp. 1–8.

- [14] "Modern IGBT gate driving methods for enhancing reliability of highpower converters an overview," *Microelectronics Reliability*, vol. 58, pp. 141 – 150, 2016.

- [15] P. D. Reigosa, F. Iannuzzo, M. Rahimo, C. Corvasce, and F. Blaabjerg, "Increasing emitter efficiency in 3.3-kv enhanced trench igbts for higher short-circuit capability," in *Proc. of APEC*, March 2018, pp. 1722–1728.

- [16] A. Kopta, M. Rahimo, U. Schlapbach, N. Kaminski, and D. Silber, "Limitation of the short-circuit ruggedness of high-voltage IGBTs," in *Proc. of ISPSD*, June 2009, pp. 33–36.

- [17] P. D. Reigosa, Short-Circuit Instabilities in Silicon IGBTs and Silicon Carbide Power MOSFETs. Aalborg Universitetsforlag, 2017.

- [18] P. D. Reigosa, F. Iannuzzo, and F. Blaabjerg, "Packaging solutions for mitigating IGBT short-circuit instabilities," in *Proc. of PCIM*, May 2017, pp. 1–7.

- [19] M. Rahimo, U. Schlapbach, A. Kopta, and S. Linder, "An assessment of modern igbt and anti-parallel diode behaviour in hard-switching applications," in *Proc. of EPE*, Sep. 2005.

- [20] S. Watanabe, M. Mori, T. Arai, K. Ishibashi, Y. Toyoda, T. Oda, T. Harada, and K. Saito, "1.7kv trench igbt with deep and separate floating p-layer designed for low loss, low emi noise, and high reliability," in *Proc. of the 23rd International Symposium on Power Semiconductor Devices and ICs*, May 2011, pp. 48–51.

- [21] M. Rahimo, A. Kopta, and S. Linder, "Novel enhanced-planar IGBT technology rated up to 6.5 kV for lower losses and higher SOA capability," in *Proc. of ISPSD*, June 2006, pp. 1–4.

- [22] M. Tanaka and I. Omura, "Scaling rule for very shallow trench IGBT toward CMOS process compatibility," in *Proc. of ISPSD*, June 2012, pp. 177–180.

**Paula Diaz Reigosa** (M'17, SM'14) received the B.S. degree in industrial engineering with a specialization in electrical engineering from the University of Oviedo, Spain, in 2012, and the M.S. degree in power electronics and drives from Aalborg University, Denmark, in 2014. She received the Ph.D. degree from Aalborg University, Denmark, in 2017. She has been a postdoctoral researcher with the University of Aalborg during 2018 and she is currently Associate Scientist with the University of Applied Sciences Northwest Switzerland. Her cur-

rent research interests include the reliability of power devices and especially power device failures, development of non-destructive testing facilities for assessment of high power modules under extreme conditions and emerging power electronics applications.

**Francesco Iannuzzo** (M'04 - SM'12) received the M.Sc. degree in Electronic Engineering and the Ph.D. degree in Electronic and Information Engineering from the University of Naples, Italy, in 1997 and 2001, respectively. He is primarily specialized in power device modelling. From 2000 to 2006, he has been a Researcher with the University of Cassino, Italy, where he became Aggregate Professor in 2006 and he is currently Associate Professor since 2012. In 2014 he got a contract as professor in Reliable Power Electronics at the Aalborg University, Den-

mark, where he is also part of CORPE (Center of Reliable Power Electronics). His research interests are in the field of reliability of power devices, including cosmic rays, power device failure modelling and testing of power modules up to MW-scale under extreme conditions, like overvoltage, overcurrent, overtemperature and short circuit.

Chiara Corvasce received her M.S. Degree in Physics from the University of Bari, Italy in 1994. In 1995 she joined the Memory Product Group of STMicroelectronics in Catania, working on nonvolatile memory devices and leading the team for the development of a ferroelectric memory. In 2002 she has moved to the Integrated Systems Laboratory (IIS) of the ETH Zurich where she received the PhD in Electrical Engineering focusing on high temperature characterization and modeling of semiconductor devices. She joined the BiMOS R&D Department of

ABB Semiconductors in 2006 where she has been leading numerous IGBT and diode development projects before she took over the management of the R&D chip development group in 2013.

**Munaf Rahimo** (M'98) received his B.Sc. from Baghdad University, Iraq in 1991 and his M.Sc. and Ph.D. from Staffordshire University, UK in 1993 and 1996, respectively. He joined the power device R&D department at GEC Plessey Semiconductors, UK in 1996 and in 1998 he joined the power development group at Semelab plc, UK as a senior R&D engineer. He joined ABB Switzerland, Semiconductors in 2000 and has been involved in the R&D of power semiconductor devices for high voltage power electronics applications. He has worked with many

device concepts such as MOSFETs, Diodes, IGBTs, IGCTs, Thyristors and Silicon Carbide based power devices. He pioneered the first high power Reverse Conducting RC-IGBT. He has 80 patent families and has authored and co-authored 160 conference and journal publications.