Aalborg Universitet

### Reliability of GaN-on-Si high-electron-mobility transistors for power electronics application

Song, Sungyoung

DOI (link to publication from Publisher): 10.5278/vbn.phd.eng.00071

Publication date: 2018

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Song, S. (2018). *Reliability of GaN-on-Si high-electron-mobility transistors for power electronics application*. Aalborg Universitetsforlag. Ph.d.-serien for Det Ingeniør- og Naturvidenskabelige Fakultet, Aalborg Universitet https://doi.org/10.5278/vbn.phd.eng.00071

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

? Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

? You may not further distribute the material or use it for any profit-making activity or commercial gain

? You may freely distribute the URL identifying the publication in the public portal ?

Take down policy If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

RELIABILITY OF GAN-ON-SI HIGHELECTRON-MOBILITY TRANSISTORS FOR POWER ELECTRONICS APPLICATION

> BY SUNGYOUNG SONG

**DISSERTATION SUBMITTED 2018**

AALBORG UNIVERSITY Denmark

# RELIABILITY OF GAN-ON-SI HIGH-ELECTRON-MOBILITY TRANSISTORS FOR POWER ELECTRONICS APPLICATION

by

Sungyoung Song

Dissertation submitted to Faculty of Engineering and Science

at Aalborg University

•

| Dissertation submitted:   | September 21, 2018                                                   |

|---------------------------|----------------------------------------------------------------------|

| PhD supervisor:           | Prof. Stig Munk-Nielsen<br>Aalborg University                        |

| Assistant PhD supervisor: | Associate Prof. Christian Uhrenfeldt<br>Aalborg University           |

|                           | Prof. Kjeld Pedersen<br>Aalborg University                           |

| PhD committee:            | Associate professor Erik Schaltz (CHAIRMAN)<br>Aalborg University    |

|                           | Dr Olayiwola Alatise<br>University of Warwick                        |

|                           | Associate professor Yunzhong Chen<br>Technical University of Denmark |

| PhD Series:               | Faculty of Engineering and Science, Aalborg University               |

| Department:               | Department of Energy Technology                                      |

| ISSN (online): 2446-1636  |                                                                      |

ISSN (online): 2446-1636 ISBN (online): 978-87-7210-327-3

Published by: Aalborg University Press Langagervej 2 DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Sungyoung Song

Printed in Denmark by Rosendahls, 2018

# CV

Sungyoung Song was born in Pusan, Korea, in 1980. He received the B.S and M.S degrees from the Department of Electrical Engineering from Changwon National University, Changwon, Korea, in 2006 and 2008, respectively. In the graduate school, he had studied on power integrated circuits. He participated in the analog-to-digital converter design project as an exchange student at the University of Washington, USA, from Aug. 2016 to Feb. 2017. He had worked as a development engineer of silicon-based semiconductor power devices with Magnachip Semiconductor, Korea, from 2008 to 2014. He is currently pursuing the Ph.D. degree with the Department of Energy Technology, Aalborg University, Aalborg, Denmark. His research interests include device technology and reliability for gallium nitride device. He is currently collaborating on the optimization technologies of GaN HEMTs for power applications with Charmers University of Technology, Sweden.

# **ENGLISH SUMMARY**

The power electronic field is experiencing diastrophism with the advent of wide-bandgap devices. As the performance development of silicon metal-oxide-semiconductorfield-effect-transistors (MOSFET) and silicon insulated gate bipolar transistors (IGBT) that have taken over the market for the past four decades has almost saturated, the people have turned to new devices that can overcome their limitations. In principle, it makes sure that the wide-bandgap (WBG) devices have superior performance compared to the silicon counterparts. Nonetheless, there may be some technical barriers to achieving their success in the market, such as the reliability. The reliability of the power devices is very critical because it may directly affect the safety of the power electronic systems. Thus, the reliability of the WBG devices should be deeply investigated to convince the market that silicon devices already occupy.

A Gallium nitride (GaN) power device is a promising candidate to replace silicon MOSFETs at the market below a thousand volts. Several major companies have commercialized discrete GaN devices, and new products using the GaN devices are targeting mainly in new markets; light detection and ranging (LiDAR), Envelope Tracking, and wireless charging. Despite this great interest, the reliability of the commercial power GaN devices is only being verified with the Joint Electron Device Engineering Council (JEDEC) standard based on Si-based devices. The discrete GaN devices are fundamentally different from Si MOSFETs or IGBTs, from the principle the operation to the package technologies. Therefore, it is very urgent to study the reliability of them to prepare for new defects that can occur in the field in the future and to verify the problem in advance. In this PhD project, various researches on the reliability of the GaN devices from a packaged GaN device level to a GaN High-electron-mobility transistors (HEMT) unit structure level are performed.

The main content is divided into three main parts: the first part Chapter 2, the second part of Chapter 3 and 4, and the last part Chapter 5. The first part is including the performance assessment results of current commercial power GaN devices, their theoretical limit and their figure of merit information. The second part is discussing the reliability and failure mechanisms of the cutting-edge commercial GaN device regarding thermal and thermo-mechanical stress. The GaN device to be tested has been selected based on the assessment results in Chapter 2. The apparatus and methodology for an accelerated power cycling test of the GaN device have been presented. The failure analysis of the GaN devices degraded by the power cycling test has been performed with supplement experiments, collected data, the literature and physical examination techniques in Chapter 4. In the last part, the device technologies that could affect the performance and the reliability of a GaN HEMT is discussed, and an experiment plan to find the optimization conditions is proposed.

Main contributions in this project are the first power cycling test with the cutting-edge GaN device and the in-deep consideration of failure mechanisms induced by thermal stress. The power cycling test suitable for the operating features of the advanced GaN devices has been conducted. The new failure phenomenon that has never been reported has been found. The diverse possibilities that could lead to this failure have been checked one by one. Furthermore, potential risk and a solution for this risk have been proposed through this analysis process.

Various experimental results and analysis results carried out in this thesis verify the effectiveness of this project.

# DANSK RESUME

Effektelektronik-feltet oplever en rivende udvikling på grund af fremkomsten af "wide-bandgap" komponenter. Silicium transistorene "metal-oxide-semiconductorfield-effect-transistors" (MOSFET) og "insulated gate bipolar transistors" (IGBT), som har domineret transistor-markedet de sidste 4 årtier, er næsten nået grænsen af mulig ydeevne. Dette har fået folk til at søge mod nye komponenter der kan overkomme de gamle transistorers begrænsninger. Teoretisk har "wide-bandgap" (WBG) komponenter overlegen ydeevne i forhold til deres silicium-baseret modstykke. Der kan dog alligevel være tekniske barrierer mod WBG komponenters success på markedet, som for eksempel deres pålidelighed. Pålideligheden af effekt komponenter er meget kritisk da det kan direkte påvirke sikkerheden af et effektelektronisk system. Derfor bør pålideligheden af WBG komponenter undersøges grundigt for at overbevise det marked som silicium allerede sidder på.

En Galiumnitrid (GaN) effekt komponent er en lovende kandidat for at erstatte silicium MOSFET'er under 1000 volt på markedet i dag. Flere store firmaer har kommercialiseret diskrete GaN komponenter og nye produkter der bruger GaN komponenter retter sig hovedsageligt mod nye markeder, såsom "LiDAR", "Envelope Tracking", og trådløs opladning. Trods den store interesse bliver GaN komponenter kun verificeret med "Joint Electron Device Engineering Council" (JEDEC)-standarden som er baseret på silicum-baseret komponenter, men diskrete GaN komponenter er fundamentalt anderledes end Si MOSFET'er eller IGBT'er, fra deres virkemåde til brugte "packaging" teknologier. Det er derfor meget vigtigt at undersøge pålideligheden af disse komponenter for at forberede sig på nye typer af defekter der can opstå i fremtiden og for at verificere problemerne på forhånd. I dette PhD projekt er forskellige undersøgelser lavet af pålideligheden af GaN komponenter, fra et "packaged" GaN komponent niveau til et GaN "High-electron-mobility-transistor" (HEMT) enheds-struktur niveau.

Hovedmaterialet er opdelt i tre dele: Den første del er kapitel 2, den anden del er kapitel 3 og 4 og den sidste del er kapitel 5. Den første del drejer sig om vurderingen af ydeevnen af GaN effekt komponenter der er tilgængelige kommercielt i dag, samt deres teoretiske grænse og deres "figure of merit" information. Den anden del diskuterer pålideligheden og fejlmekanismerne i den banebrydende kommercielt tilgængelige GaN komponent i forhold til termisk og termomekanisk stress. GaN komponentet der blev testet blev valgt på baggrund af kapitel 2. Apparaterne og methoderne for en accelereret "power cycling" test af GaN komponentet er her præsenteret. Fejlanalysen af GaN komponenterne som er blevet degraderet af "power cycling" testen med supplerende eksperimenter, indsamlet data, literaturliste og fysiske undersøgelsesmetoder kan findes i kapitel 4. I den sidste del diskuteres de komponent-teknologier der kan påvirke ydeevnen og pålideligheden af en GaN eHEMT, og en experiment plan for at finde de optimale betingelser er her foreslået.

De primære bidrag i dette projekt er: Den første "power cycling" test med de banebrydende GaN komponenter og en dybdegående overvejelse af fejlmekanismerne der opstår ved termisk stress. En passende "power cycling" test af funktionerne af de advancerede GaN komponenter er udført, og en ny fejlmekanisme der aldrig har været rapporteret før er blevet fundet. De forskellige grunde der kunne forårsage denne fejlmekanisme er blevet undersøgt én efter én. Der er derudover også blevet vurderet den potentielle risiko denne fejlmekanisme udgør og en mulig løsning dertil gennem en analytisk process.

Mange forskellige eksperimentielle og analytiske resultater fundet igennem denne PhD-afhandling bekræfter værdien af dette projekt.

# ACKNOWLEDGEMENTS

I am very thankful to the financial support provided by Semiconductor materials for power electronics (SEMPEL), Department of Energy Technology, Aalborg University (AAU) during my Ph.D. study.

Firstly, I would like to express my sincere gratitude and appreciation to my supervisor Prof. Stig Munk-Nielsen for his valuable guidance, patience, motivation, and encouragement throughout the whole of my Ph.D. study. He had given me this research opportunity. His continuous support helped me in all the time of research.

I also would like to thank my co-supervisor Assoc. Prof. Christian Uhrenfeldt for his supports, technical opinions, and valuable advice. Various views in his physical perspective have been significant to resolve the many problems during the Ph.D. study. I also like to appreciate Ionut Trinitis from Vestas Wind Systems A/S. He also had given valuable guidance and encouragement as a co-supervisor in the first half of my Ph.D. study. I am grateful to Prof. Kjeld Pedersen from the Department of nanotechnology in AAU for their valuable discussions and suggestions.

I also would like to appreciate Prof. Niklas Rorsman from the Chalmers University of Technology in Sweden for great support, guidance, and help. He not only has helped manufacture the newly proposed GaN HEMTs but also had offered various advice regarding an experiment for me. Further, I am grateful to Prof. Lis K. Nanver from the University of Twente in the Netherlands for their valuable discussions and suggestions.

I also would like to express my appreciation to Assoc. Prof. Szymon Beczkowski, Assis. Prof. Lajos Török, and Prof. Francesco Iannuzzo for helpful discussions and technical support. Moreover, many thanks to Shivakumar Thammaiah, Asger Bjørn Jørgensen, and Thore Stig Aunsborg for helpful technical support.

Furthermore, many thanks to my friends and colleagues in the Department of Energy Technology, especially Junbum Kwon, Changwoo Yoon, Uimin Choi, Hoon Heo, Yanfeng Shen, Nick Baker, Yi Zhang, Zhongxu Wang, Simon Dyhr Sønderskov, and Nicklas Christensen. Thanks to Jannick Kjær for helping me write Danish Resume.

I am deeply thankful to my family; my father, mother, father-in-law, mother-in-law, brothers, and sister-in-law, for their belief and invaluable love. And most importantly, I send my special thanks to my beloved wife Yuwon Kim. I believe that none of my achievements would have been possible without her unconditional love, wholehearted support, and great encouragement. I also want to say thank our precious daughter Sieun.

Sungyoung Song

September 2018

Aalborg Denmark

# TABLE OF CONTENTS

| Chapter 1. Introduction                                                                        | 19 |

|------------------------------------------------------------------------------------------------|----|

| 1.1. Potential of GaN devices in power application                                             | 19 |

| 1.1.1. Prospect of GaN power devices                                                           | 19 |

| 1.1.2. Application of power gaN devices                                                        | 20 |

| 1.1.3. Potencial of a GaN power device                                                         |    |

| 1.2. A GaN HEMT in power application                                                           | 22 |

| 1.2.1. A substrate                                                                             | 22 |

| 1.2.2. Normaly-off technology                                                                  |    |

| 1.2.3. Package technology                                                                      |    |

| 1.3. Reliability of GaN HEMTs in power application                                             |    |

| 1.3.1. Reliability of Power devices in power electronics                                       |    |

| 1.3.2. Failure mechanisms by a power cycling test                                              | 27 |

| 1.3.3. Reliability of GaN HEMTs                                                                |    |

| 1.4. Thesis objectives                                                                         |    |

| 1.4.1. Research questions and objectives                                                       |    |

| 1.4.2. Project limitations and assumptions                                                     | 31 |

| 1.5. Outline of the Thesis                                                                     | 32 |

| 1.6. List of the publications                                                                  | 33 |

| Chapter 2. Performance assessment of commercial GaN on Si discredevices with a Figure of Merit |    |

| 2.1. FOM of GaN power transistors                                                              | 35 |

| 2.2. Measurement methodology                                                                   |    |

| 2.2.1. Review of test samples                                                                  | 36 |

| 2.2.2. Test environment                                                                        | 37 |

| 2.2.3. On-state resistance compensation                                                        | 39 |

| 2.3. Characterstics of commecital GaN power devices                                            | 40 |

| 2.3.1. Static characteristics                                                                  | 40 |

| 2.3.2. Dynamic characteristics                                                                 | 41 |

| 2.3.3. Active GaN area                                                                         | 43 |

| 2.4. FOM of cummercial GaN devcies                                                               | 44     |

|--------------------------------------------------------------------------------------------------|--------|

| 2.5. Summary                                                                                     | 47     |

| Chapter 3. Power cycling test for a cutting-edge GaN device in power ap                          |        |

| 3.1. Power cycling test for a GaN device                                                         |        |

| 3.2. Bidirection conductive advantage of a GaN HEMT                                              | 49     |

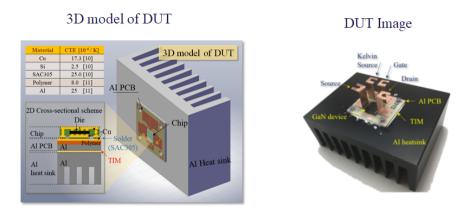

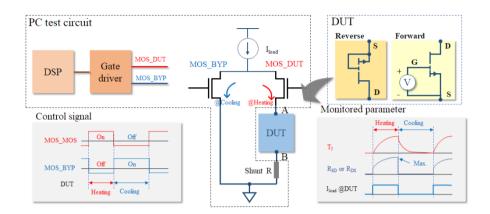

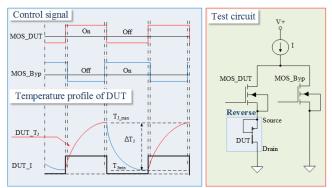

| 3.3. Power cycling test setup                                                                    | 50     |

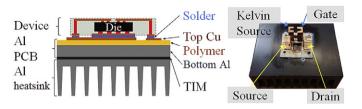

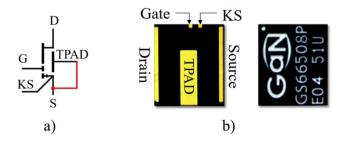

| 3.3.1. Device under test                                                                         | 51     |

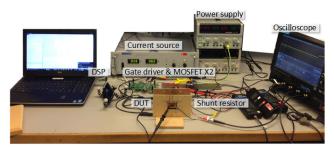

| 3.3.2. Power cycling test setup                                                                  | 52     |

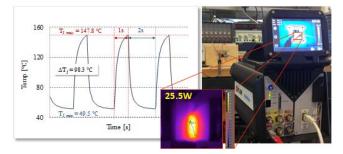

| 3.3.3. Periodic device characteristics in offline to PC test                                     | 55     |

| 3.3.4. Failure criteria                                                                          | 56     |

| 3.3.5. Operation strategy and initial stress conditions                                          | 57     |

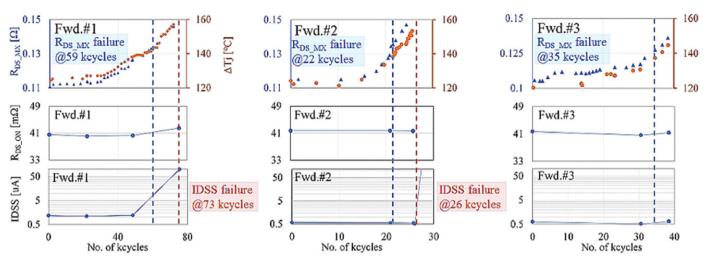

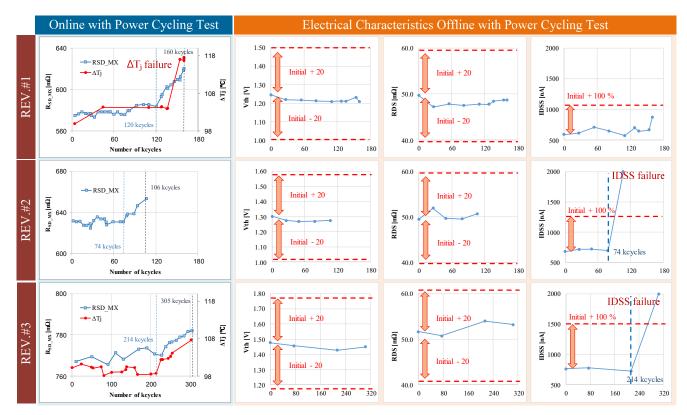

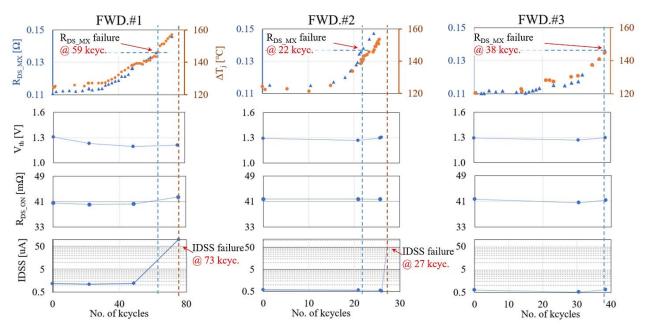

| 3.4. Result of power cycling tests                                                               | 58     |

| 3.4.1. Online parameter results of PC test: reverse Vs. forward conduct                          |        |

| 3.4.2. Offline parameter results of PC tests: reverse vs. forward conduct                        |        |

| 3.4.3. Result summary                                                                            | 61     |

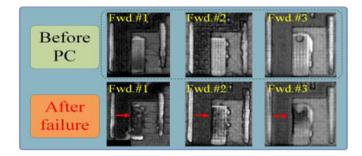

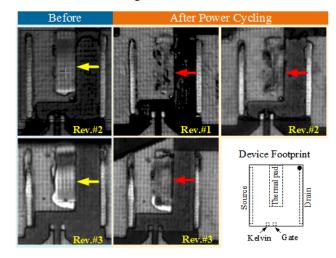

| 3.5. Failure analysis of aged devices by power cycling                                           | 62     |

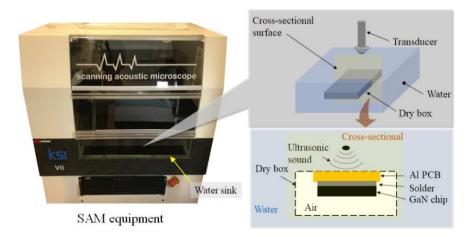

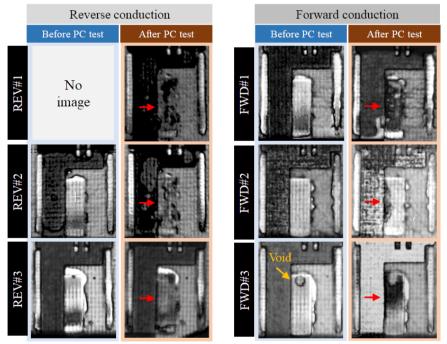

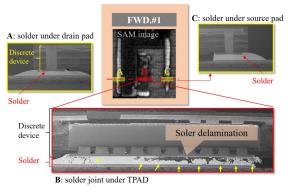

| 3.5.1. A scanning acoustic microscope                                                            | 62     |

| 3.5.2. Failure analysis with SAM                                                                 | 64     |

| 3.6. Summary                                                                                     | 64     |

| Chapter 4. Failure mechanism analysis of off-state drain-to-source<br>current failure in PC test |        |

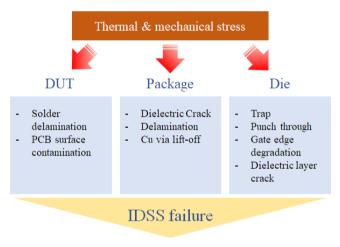

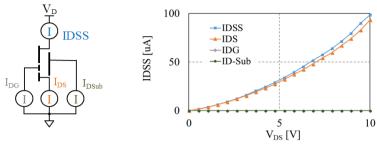

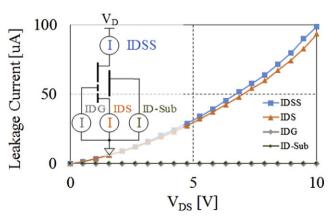

| 4.1. IDSS failure mechanisms induced by PC test                                                  | 65     |

| 4.2. IDSS failure mechanism induced by PC test in a DUT                                          | 67     |

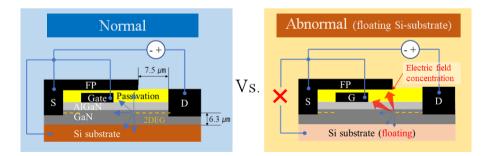

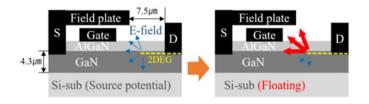

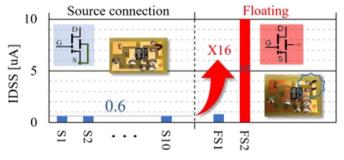

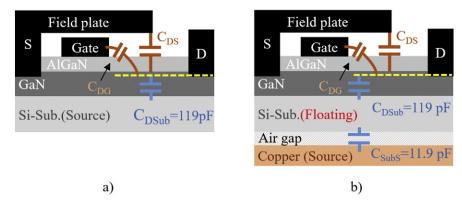

| 4.2.1. Hypothesis: IDSS failure by Si-substrate floating                                         | 67     |

| 4.2.2. Effect of floating Si substrate on IDSS characteristics                                   | 68     |

| 4.2.3. The floating Si substrate tested using measured output capacitan                          | ice 69 |

| 4.2.4. Cross-sectional anlysis of the aged DUT                                                   | 71     |

| 4.3. IDSS failure mechanism induced by PC test in a package                                      | 73     |

| 4.4. IDSS failure mechanism induced by PC test in a die                                          |        |

| 4.4.1. Leakage current localisation analysis                                                     |        |

| 4.4.2. The IDSS failure in PC test Vs. conventional failure mechanism          | . 75 |

|--------------------------------------------------------------------------------|------|

| 4.5. Summary                                                                   | . 77 |

| Chapter 5. Optimization of a high voltage GaN HEMT for power application       | ı 78 |

| 5.1. Technical factors for a high voltage GaN HEMT                             | . 78 |

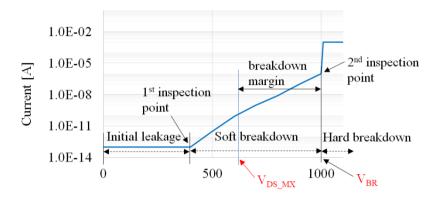

| 5.1.1. Characteristics of breakdown capability                                 | . 78 |

| 5.1.2. Factors able to affect breakdown capability                             | . 79 |

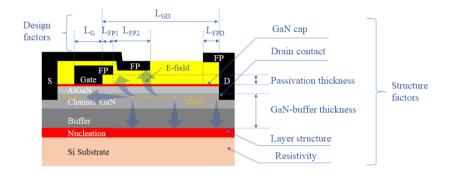

| 5.2. Design factors for a high voltage GaN HEMT                                | . 81 |

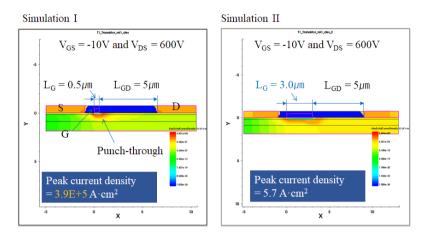

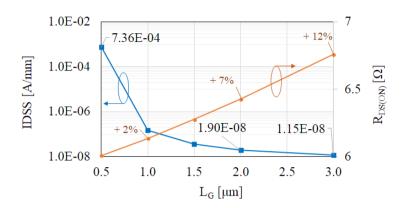

| 5.2.1. Gate length                                                             | . 81 |

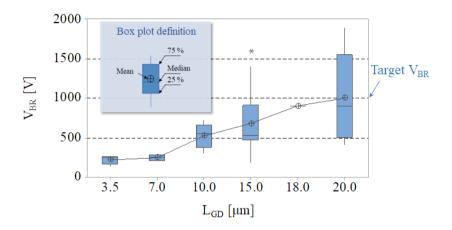

| 5.2.2. Drain to gate length                                                    | . 82 |

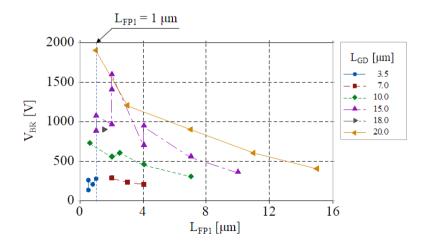

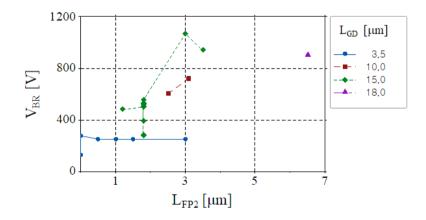

| 5.2.3. Field plate: L <sub>FP1</sub> , L <sub>FP2</sub> , and L <sub>FPD</sub> | . 84 |

| 5.3. Structural factors for a high voltage GaN HEMT                            | . 86 |

| 5.3.1. The first Passivation thickness                                         | . 87 |

| 5.3.2. GaN cap on an AlGaN barrier                                             | . 88 |

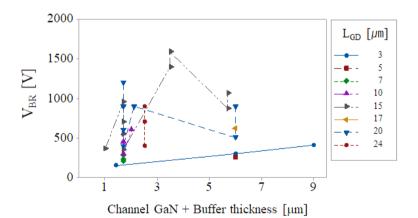

| 5.3.3. Entire thickness of channel GaN and buffer                              | . 88 |

| 5.3.4. Si substrate resistvity                                                 | . 89 |

| 5.3.5. Drain contact: Ohmic or Schottky contact                                | . 90 |

| 5.4. Experiment plan for factor analysis of breakdown capability               | . 91 |

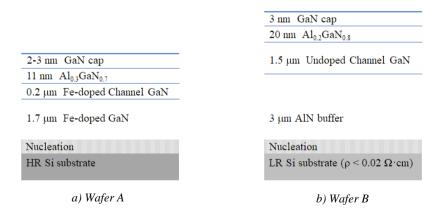

| 5.4.1. Experiment plan for Structural factors analysis                         | . 91 |

| 5.4.2. The design of experiments for factors analysis                          | . 92 |

| 5.4.3. Device information to be fabricated and future test plan                | . 93 |

| 5.5. Summary                                                                   | . 93 |

| Chapter 6. Conclusions and future work                                         | 95   |

| 6.1. Summary of thesis                                                         | . 95 |

| 6.2. Contributions                                                             | . 97 |

| 6.3. Future work                                                               | . 99 |

| LITERATURE LIST                                                                | 102  |

# **TABLE OF FIGURES**

| Figure 1-1 Market size prospect of GaN power devices from 2016 to 2022 [4] 19                           |

|---------------------------------------------------------------------------------------------------------|

| Figure 1- 2 Market segmentation and applications of major power electronic                              |

| devices [139]                                                                                           |

| Figure 1- 3 Basic structure of a depletion mode GaN HEMT                                                |

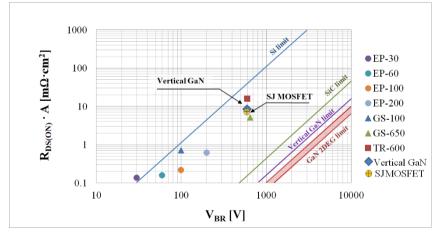

| Figure 1-4 Ideal $R_{sp}$ and $V_{BR}$ capability of Si, 4H-SiC, vertical GaN, and GaN HEMT.            |

| 22                                                                                                      |

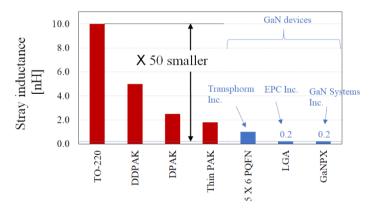

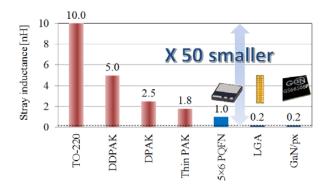

| Figure 1-5 Stray inductances of different package technologies [25-27]                                  |

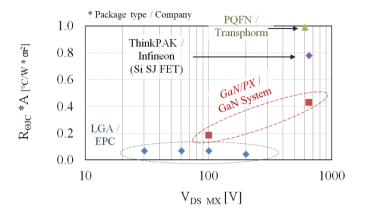

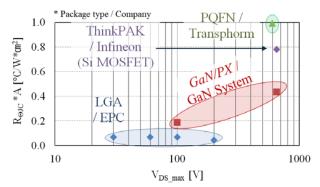

| Figure 1- 6 $R_{\theta JC}$ * A versus maximum drain-to-source voltage of commercial discrete           |

| GaN power devices [16,17, 28-33]                                                                        |

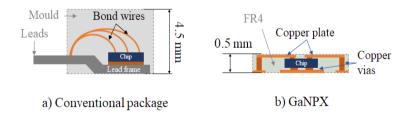

| Figure 1-7 Cross section of a) conventional package technology with bond wires [32]                     |

| b) GaNPX <sup>TM</sup> [25]                                                                             |

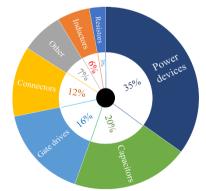

| Figure 1-8 Failure distribution in power electronic systems from the survey [36]. 26                    |

|                                                                                                         |

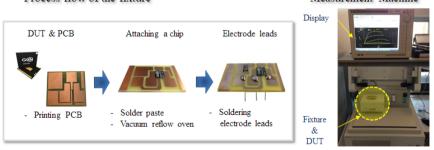

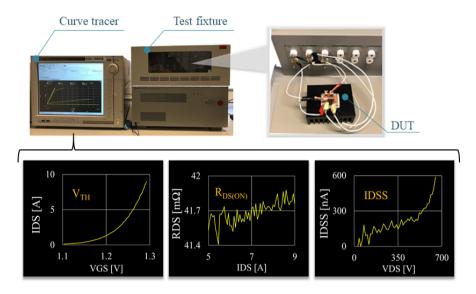

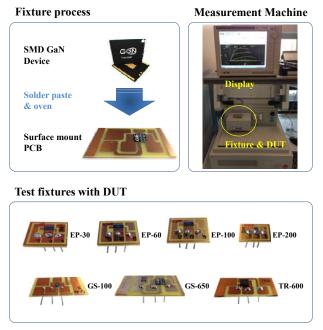

| Figure 2-1 Process flow of the test fixtures and the measurement instrument 37                          |

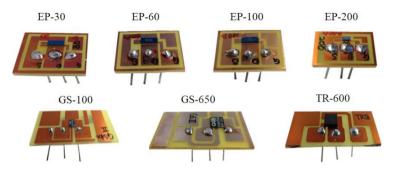

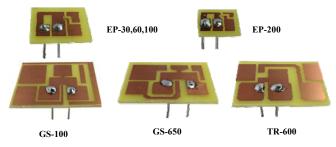

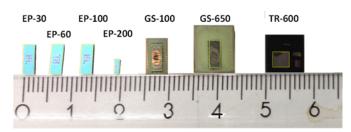

| Figure 2- 2 Seven kinds of test fixtures with power GaN devices                                         |

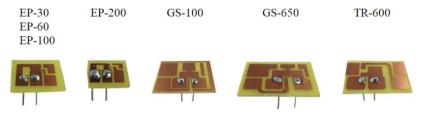

| Figure 2- 3 Five PCBs to measure R <sub>fixture</sub> of each test fixture                              |

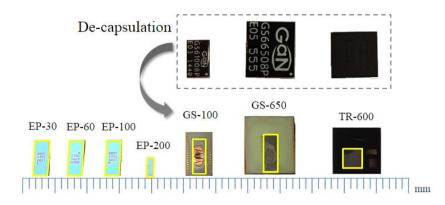

| Figure 2- 4 Actual GaN areas of the tested commecial GaN-on-Si device                                   |

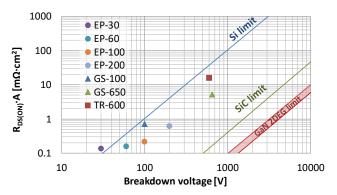

| Figure 2- 5 $R_{DS(ON)}$ · A based on measured date versus breakdown voltage for                        |

| commercial GaN devices                                                                                  |

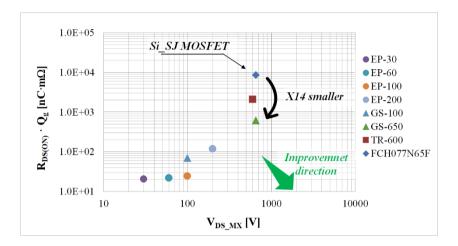

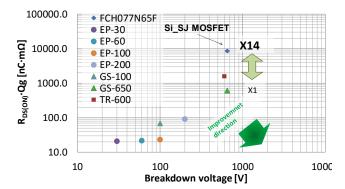

| Figure 2- 6 $R_{DS(ON)}$ · $Q_g$ based on measured date versus the maximum drain voltages               |

| for commercial GaN devices                                                                              |

|                                                                                                         |

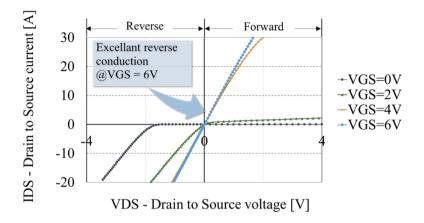

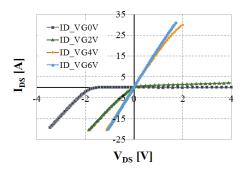

| Figure 3- 1 Measured V <sub>DS</sub> Vs. I <sub>DS</sub> curve of a commercial E-mode 650 V GaN device. |

| 50                                                                                                      |

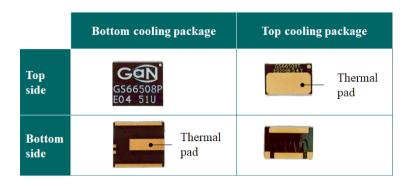

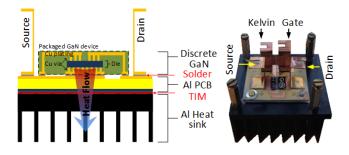

| Figure 3- 2 Bottom side cooling and top side cooling packages of a commercial GaN                       |

| device from GaN Systems Inc                                                                             |

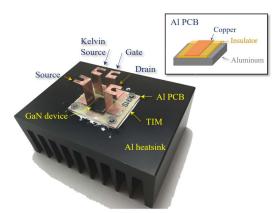

| Figure 3- 3 A cross-section image of DUT 3D model and real image of the DUT. 52                         |

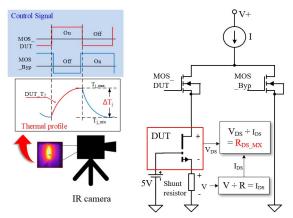

| Figure 3- 4 Configuration of PC test setup: A PC test circuit, a DUT, control signal,                   |

| and monitored parameters                                                                                |

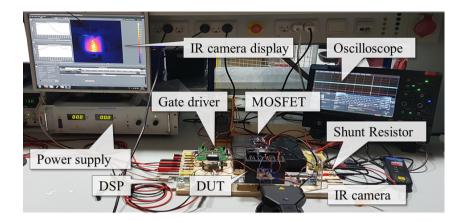

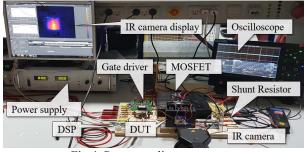

| Figure 3- 5 A PC test setup                                                                             |

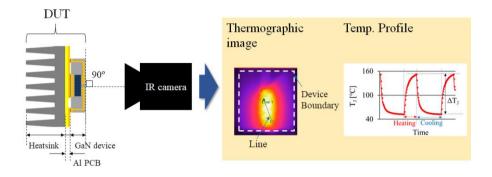

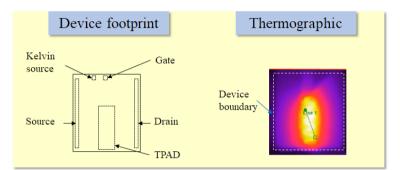

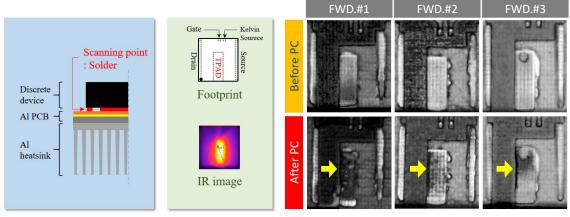

| Figure 3- 6 Temperature measurement environment with IR camera, a thermographic                         |

| image, and temperature profile                                                                          |

| Figure 3- 7 An offline test environment: curve tracer Keysight's B1505A                                 |

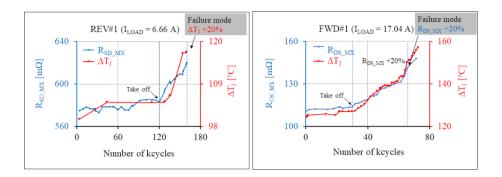

| Figure 3- 8 Online parameters of REV#1 Vs. FWD#1 during PC test                                         |

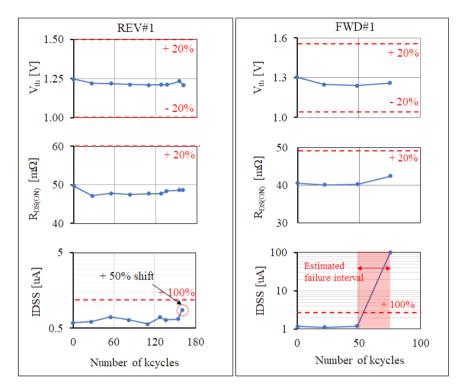

| Figure 3- 9 Offline parameters of PC tests of REV#1 Vs. FWD#1 during PC test                            |

|                                                                                                         |

| Figure 3- 10 SAM equipment (KSI V-8 from IP Holding) and analysis environment.                          |

|                                                                                                         |

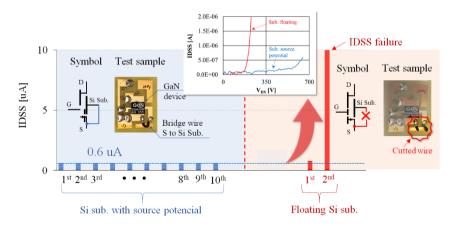

| Figure 4- 2 The expected difference of the electric field distributions between the source-connected Si substrate versus the floating Si substrate under a drain-to-source |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| reverse bias condition                                                                                                                                                     |

| Figure 4- 3 IDSS measurement results at $V_{\text{DS}}$ = 650 V with source potential Si                                                                                   |

| substrate versus floating Si substrate                                                                                                                                     |

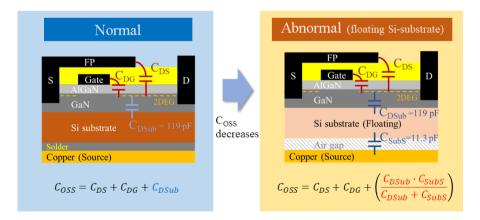

| Figure 4- 4 $C_{OSS}$ configuration with source potential on Si substrate versus $C_{OSS}$ configuration with the complete delamination solder under TPAD                  |

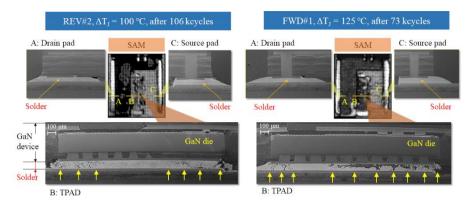

| Figure 4- 5 a) SAM and Cross-sectional SEM images of REV#2 and b) FWD#1 at the end of PC test [93, 98]                                                                     |

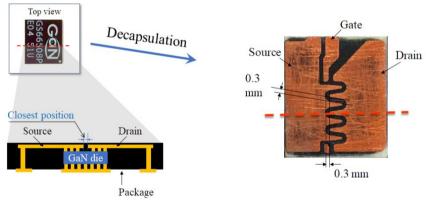

| Figure 4- 6 a) A cross-sectional image of the GaN device, b) top view of Cu plates of                                                                                      |

| a decapsulated GaN device                                                                                                                                                  |

|                                                                                                                                                                            |

| Figure 4-7 a) Test circuit for leakage localization, b) test results of IDSS localization.                                                                                 |

|                                                                                                                                                                            |

|                                                                                                                                                                            |

| Figure 5-1 An example of the leakage current versus reverse bias voltage in off-state                                                                                      |

| with primary definitions of leakage current curve                                                                                                                          |

| Figure 5- 2 Primary factors in a GaN HEMT that affect electric field distribution in                                                                                       |

| reverse bias                                                                                                                                                               |

| Figure 5- 3 Current density TCAD simulation of GaN HEMTs with $L_G$ = 0.5 $\mu m$ and                                                                                      |

| $L_G = 3 \ \mu m.$ 81                                                                                                                                                      |

| Figure 5- 4 Trends of IDSS and $R_{DS(ON)}$ according to the $L_G$ range from 0.5 $\mu m$ to 3                                                                             |

| μm based on TCAD simulation                                                                                                                                                |

| Figure 5- 5 The box plot that illustrates $V_{BR}$ distribution of forty-four GaN HEMTs                                                                                    |

| by $L_{GD}$ groups based on literature (44 cases from 9 papers)                                                                                                            |

| Figure 5- 6 The scatter plot that exhibits a relation between $L_{\text{FP1}}$ and $V_{\text{BR}}$ by $L_{\text{GD}}$                                                      |

| groups based on literature (33 cases from 8 papers)                                                                                                                        |

| Figure 5- 7 The scatter plot that exhibits a relation between $L_{\text{FP2}}$ and $V_{\text{BR}}$ by $L_{\text{GD}}$                                                      |

| groups based on literature (19 cases from 6 papers)                                                                                                                        |

| Figure 5-8 a) TCAD simulation b) the electric field distributions along the 2DEG                                                                                           |

| beween a GaN HEMT without FP and with FP                                                                                                                                   |

| Figure 5-9 The scatter plot that exhibits a relation between a passivation thickness                                                                                       |

| and V <sub>BR</sub> by L <sub>GD</sub> groups based on literature (26 cases from 7 papers)                                                                                 |

| Figure 5-10 The box plot that exhibits the leakage current distributions between with                                                                                      |

| and without a thin GaN cap layer (24 cases from 9 papers)                                                                                                                  |

| Figure 5- 11 The scatter plot that exhibits a relation between a channel GaN + buffer                                                                                      |

| thickness and $V_{BR}$ by $L_{GD}$ groups based on literature (34 cases from 10 papers) 88                                                                                 |

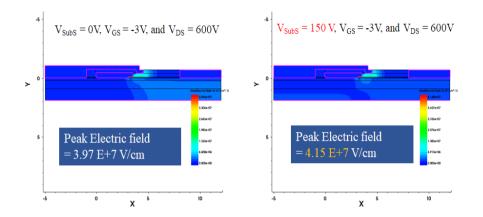

| Figure 5- 12 Comparison of TCAD simulation between $V_{SubS} = 0V$ and $V_{SubS} = 150$                                                                                    |

| V                                                                                                                                                                          |

| Figure 5-13 Schematic cross section of a) Wafer A and b) Wafer B                                                                                                           |

| Figure 5-14 a) Full factorial design versus b) Plackett-Burman design of three factors                                                                                     |

| two levels                                                                                                                                                                 |

# **TABLE OF TABLES**

| Table 1- 1 Material properties of Si, 4H-SiC, GaN, GaN HEMT [6, 7, 140].21Table 1- 2 Material properties of different substrates [10].22                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 1- 3 Threshold voltages (Vth) and gate technologies for normally-off operationof commercial discrete GaN transistors [15-22].23                                                                                        |

| Table 1- 4 The qualification results of major products from the manufactures [50-53].                                                                                                                                        |

| Table 2- 1 Information of test samples based on data sheet [16,17,28-32].36Table 2- 2 Test conditions of static and dynamic characteristics.38Table 2- 3 Measured static characteristics of tested seven samples in the room |

| temperature                                                                                                                                                                                                                  |

| Table 3- 1 The failure criteria of parameters monitored in PC test.56Table 3- 2 Initial stress conditions of PC test for six test samples.58Table 3- 3 Summary from the PC tests results of six samples [93, 98].61          |

| Table 4- 1 The comparison of measured COSS before PC test and at the end of PC test.         Table 4- 2 Failure mechanisms, stress sources, and symptoms of parameters of GaN HEMTs based on the literature [114].           |

| Table 5- 1 Crucial information of eight kinds of devices to be produced for the experiment                                                                                                                                   |

# **CHAPTER 1. INTRODUCTION**

This chapter firstly presents the overall background and motivation of this research project. After that, the thesis outline and the list of publications related to this research are described.

### **1.1. POTENTIAL OF GAN DEVICES IN POWER APPLICATION**

### 1.1.1. PROSPECT OF GAN POWER DEVICES

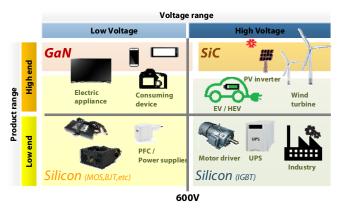

Wide-band-gap (WBG) semiconductor materials such as Gallium nitride (GaN) and Silicon carbide (SiC) are renowned as alternative candidates against silicon (Si) [1]. Their WBG properties enables a power device to be more compact, faster, and more efficient compared to silicon-based devices. Thanks to the excellence of WBG devices, they are receiving constant attention from the power electronics field. Both GaN and SiC products had already been on the market. Employing WBG devices has been reported mainly in high-end applications such as renewable energy over the recent years [2, 3]. Although GaN devices were universally applied to the three fields of radio frequency (RF), a light emitting diode (LED), and power electronics a decade ago, this thesis is limited to the power electronics field.

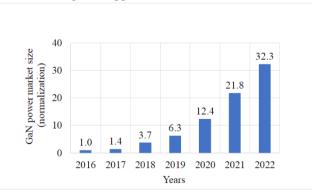

The market share of GaN devices at present is tiny in the entire power market, but sustained growth of them is predicted with the possibility of development. Yole Development expects a thirty-two-times increase of GaN device market by 2022 based on 2016 revenue [4]. Fig 2-1 shows the promising outlook of GaN device market. Emerging end-products using GaN transistors inside are now gradually expanding especially in power supply for datacentre and telecom, AC fast charger, automotive LiDAR, Envelope Tracking, and wireless power [5]. There is a promising future for GaN devices in power applications.

Figure 1-1 Market size prospect of GaN power devices from 2016 to 2022 [4].

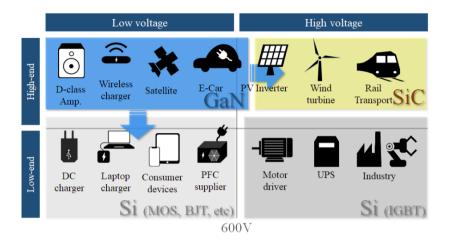

Figure 1-2 Market segmentation and applications of major power electronic devices [139].

### **1.1.2. APPLICATION OF POWER GAN DEVICES**

GaN power devices is an attractive device in the field of low voltage (LV) power electronics application. They can promise end-users higher efficiency, size and weight reduction, and faster operation frequency. Despite these advantages, commercial GaN devices are expensive compared to the similar voltage-rate Si metal-oxide semiconductor field-effect-transistor (MOSFET). Figure 1-2 exhibits the market segmentation of the significant power devices for each use [1, 3]. Although the GaN devices are in the high-end and under 650 V application range [2, 3], they are expanding their area through ongoing cost savings and technology improvement. Hence, the prospects of GaN power devices are bright for the future.

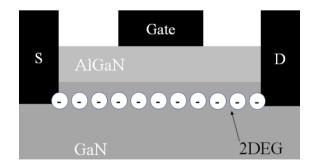

Figure 1-3 Basic structure of a depletion mode GaN HEMT.

#### **1.1.3. POTENCIAL OF A GAN POWER DEVICE**

Most of commercial GaN power devices have a GaN high-electron-mobility-transistor (HEMT) structure. Figure 1-3 shows a basic structure of a depletion-mode GaN HEMT. The GaN HEMTs intrinsically have a two-dimensional electron gas (2DEG) as a current channel. Because the 2DEG is highly conductive, it can contribute to the excellent on-state resistance characteristics of a GaN HEMT.

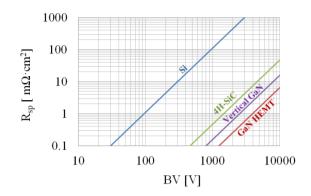

The properties of a GaN power device can be examined looking at their theoretical limit of the device. The relationship between specific  $R_{DS(ON)}(R_{SP})$  and breakdown voltage ( $V_{BR}$ ) of a power device is stated as given in Equation (1.1). In this equation based on solid-state physics [6],  $\epsilon_0$  is the permittivity of a vacuum,  $\epsilon_r$  is the relative permittivity of the crystal compared to a vacuum,  $E_{crit}$  is the critical electric field of material, and  $\mu_n$  is the electron mobility in given semiconductor.

$$R_{SP} = \frac{4 \cdot V_{BR}^2}{\varepsilon_0 \cdot \varepsilon_r \cdot \varepsilon_{crit}^3 \cdot \mu_n} \quad [m^2 \cdot \Omega]$$

(1.1)

The fraction of Equation (1.1) is composed of constants from the physical properties of given material. Si, SiC, and GaN are primary candidates for a power transistor. GaN power devices can be classified into two types: a vertical GaN transistor and a GaN HEMT using a 2DEG. The theoretical limits of both are different because of electron mobility difference between GaN and 2DEG. Table 1-1 displays specific characteristics of each material. In GaN HEMT material, the electron mobility of 2DEG is adopted as  $\mu_n$ . The electron mobility of GaN material is applied to the theoretical limit of a vertical GaN transistor. The equation can be plotted with the material properties of Si, SiC, vertical GaN, and GaN HEMT as shown in figure 1.4. Theoretical borders of a power device by a given semiconductor material are included

| Para              | <b></b>                 | <b>TT</b> •/     | Material properties |        |     |             |

|-------------------|-------------------------|------------------|---------------------|--------|-----|-------------|

| meter             | Description             | Unit             | Si                  | 4H-SiC | GaN | GaN<br>HEMT |

| ε <sub>0</sub>    | Vacuum permittivity     | F/cm             | 8.9 E-14            |        |     |             |

| ٤ <sub>r</sub>    | Relative permittivity   | -                | 11.8                | 9.7    | 9   | 9           |

| E <sub>crit</sub> | Critical electric field | MV/cm            | 0.3                 | 2.2    | 3.3 | 3.3         |

| $\mu_n$           | Electron mobility       | $cm^2/V \cdot s$ | 1300                | 950    | 900 | 2215        |

Table 1-1 Material properties of Si, 4H-SiC, GaN, and GaN HEMT [6, 7, 140].

Figure 1-4 Ideal R<sub>sp</sub> and V<sub>BR</sub> capability of Si, 4H-SiC, vertical GaN, and GaN HEMT.

in the chart. In theory, GaN HEMTs can have the best conductivity than Si, SiC, or vertical GaN transistors at the same  $V_{BR}$ , thanks to their 2DEG and WBG properties.

### **1.2. A GAN HEMT IN POWER APPLICATION**

A GaN HEMT built on a SiC substrate emerged as a transistor for radio frequency (RF) application in 2004 [6]. There had been various efforts for GaN HEMT to be used as the switching device for power application [12]. Subsequently, we can meet a commercial power GaN HEMT that overcomes technical hurdles on the market. In this section, technologies used in a commercial GaN HEMT are discussed.

#### 1.2.1. A SUBSTRATE

The appearance of a GaN HEMT grown on Si substrate had attracted attention of the power electronics device market [6, 12]. In the early of development, a GaN layer the

| Parameters                                            | Unit   | Material properties |     |     |  |

|-------------------------------------------------------|--------|---------------------|-----|-----|--|

|                                                       |        | Sapphire            | SiC | Si  |  |

| Thermal conductivity                                  | W/cm·K | 0.3                 | 4.9 | 1.5 |  |

| Lattice mismatch with<br>GaN                          | %      | 16                  | 4   | 17  |  |

| Coefficient thermal<br>expansion mismatch<br>with GaN | %      | 39                  | 3.2 | 54  |  |

Table 1-2 Material properties of different substrates [10].

basis of a GaN HEMT had been mostly grown on sapphire or SiC. The sapphire substrate has some disadvantages: lower thermal conductivity, the large lattice mismatch with GaN, and significant coefficient of thermal expansion (CTE) mismatch. On the other hand, a SiC substrate shows high thermal conductivity, low lattice mismatch, relatively low CTE mismatch compared with Si or sapphire [8]. Despite these merits, a SiC substrate wafer is more expensive than a Si substrate wafer. In Ref. [9], a SiC wafer cost is fifteen times as much as a Si wafer. Primary properties of each substrate in Table 1-2 describe their advantages and disadvantages [10]. For these reasons, power GaN device suppliers have developed a product with a GaN on Si HEMT.

Price competitiveness of GaN devices is essential to penetrate the power electronics market. Although the Si substrate has lower thermal conductivity, more considerable lattice mismatch with GaN, and larger CTE mismatch compared to the SiC substrate, most commercial power GaN devices are fabricated on a Si wafer most inexpensive of the above three candidates. Besides, wafer suppliers such as EpiGaN has developed an 8-inch GaN-on-Si wafer [11, 12]. Currently, primary power GaN device suppliers such as EPC, Panasonic and GaN systems Corporation are applying a 6-inch wafer to their products [5, 13, 14]. Therefore, if they migrate to an 8-inch GaN-on-Si wafer, the price of GaN devices may drop further.

### 1.2.2. NORMALY-OFF TECHNOLOGY

Normally-off characteristic of GaN transistors is required in power electronics application. A transistor with the normally-off characteristics is often called an enhancement mode (E-mode) transistor. Various technical challenges have been attempted to achieve a positive threshold voltage: p-doped GaN under gate, p-doped AlGaN under gate, recessed gate, plasma treatment under gate, recessed AlN gate, hybrid MOS-HFET, and cascode structure [15]. These technologies are very significant factors which affect the electrical performance of GaN devices such as on-state resistance and off-leakage current.

| Company               | Vth [V] | Gate technology for normally-off                                   |  |  |

|-----------------------|---------|--------------------------------------------------------------------|--|--|

| EPC [15, 16]          | 1.4     | P-doped GaN gate cap                                               |  |  |

| GaN Systems [17, 18]  | 1.3     | P-doped GaN gate cap                                               |  |  |

| Panasonic [19, 20]    | 1.2     | AlGaN recess etch, P-doped GaN gate<br>cap, P-doped GaN near drain |  |  |

| Transphorm [21]       | 1.8     | Cascode                                                            |  |  |

| On-Semiconductor [22] | 2.1     | Cascode                                                            |  |  |

Table 1- 3 Threshold voltages (Vth) and gate technologies for normally-off operation of commercial discrete GaN transistors [15-22].

Commercial GaN devices are using different gate technologies for the normally-off operating. Table 1-3 shows the threshold voltage level and gate technologies of primary suppliers of GaN transistors on the market. EPC and GaN Systems are using p-doped GaN gate cap layer for E-mode operation [7, 8]. Even though Panasonic had employed a simple p-doped GaN cap layer in the beginning, they had introduced a new product named X-GaN with a hybrid drain-gate injection transistor (HD-GIT) technology in 2017 [9]. The architecture is complex and uses three techniques; AlGaN recess etch, p-doped GaN in the gate, and p-doped GaN layer in drain [10]. They improved current collapse issues due to the new technology. The last two companies Transphorm and On Semiconductor incorporate an additional low-voltage Si MOSFET for normally-off operation. Two chips a normally-on GaN die and a normally-off Si MOSFET are connected in a cascode structure [11]. These diverse technologies eventually result in performance difference among products.

#### 1.2.3. PACKAGE TECHNOLOGY

Package technology of a power GaN device has a significant effect on overall performance of the product. It had been confirmed that a GaN device could offer promising switching performance for a power conversion circuit [23, 24]. To maximize this advantage of the GaN device, the performance of the package becomes more critical than others. There are three primary functions required of the power GaN device: small stray inductance, high thermal conductivity, and high reliability. Particularly in the high-speed application, a low parasitic inductance characteristic of the package is emphasized more. Therefore, commercial GaN devices need more enhanced package technology.

Package technologies of commercial GaN devices show exceptional performance compared to conventional packages. Stray inductance and junction-to-case thermal resistance times package area ( $R_{ ext{BUC}} * A$ ) are crucial figures of merit (FOM) which

Figure 1-5 Stray inductances of different package technologies [25-27].

Figure 1-6 Rosc \* A versus maximum drain-to-source voltage of commercial discrete GaN power devices [16,17, 28-33].

express the performance of specific package technology. A bar graph in Figure 1-5 displays the stray inductances of different package technologies [25-27]. The commercial GaN devices have relatively lower stray inductances than others. The stray inductance of land grid array (LGA) and GaNPX<sup>TM</sup> from GaN Systems packages is 0.2 nH fifty times smaller than the TO-220. Figure 1-6 illustrates thermal conductivity of each device. To easily understand, the state-of-the-art Si-based Superjunction (SJ) device are added [33]. LGA and GaNPX show less  $R_{\theta JC}$  \* A than the Si SJ device. At  $V_{BR} = 650$  V, GaNPX has two times better thermal conductivity compared to the Si SJ device. These advanced package technologies are contributing to the performance of the commercial GaN devices.

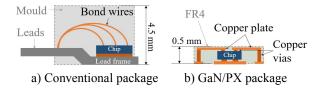

The GaNPX package, which exhibits excellent performance in the highest operating voltage of commercial power GaN devices, is different from the conventional package technology. Figure 1-7 displays that GaNPX is much geometrically different than a conventional package [25, 32]. GaNPX can achieve nine times thinner thickness due

Figure 1-7 Cross section of a) conventional package technology with bond wires [32] b) GaNPX<sup>TM</sup> [25].

to the spetial structure using copper vias and plates instead of the bond wires. The compact structure allows the GaN device to possess not only better electrical performance but also better thermal conductivity. Besides, this packaging technology ultimately can be embedded in an FR4 printed circuit board (PCB). For these reasons, the package has received attention from the power device market.

### **1.3. RELIABILITY OF GAN HEMTS IN POWER APPLICATION**

Concerning the possibilities for superior electrical performance, the GaN HEMTs can be a challenging candidate to replace Si-based transistor in specific fields of the power electronics. For successful positioning of GaN HEMTs on the power electronics market, GaN HEMTs must be accompanied by sufficient evaluation results to prove their reliability. Major GaN suppliers recently are currently under the qualification of their products with the Si-based qualification standard Joint Electron Device Engineering Council (JEDEC). However, the reliability of the GaN HEMT products cannot wholly guarantee solely with the existing qualification procedures of Si devices because of the new failure phenomena found only in GaN HEMTs. Therefore, additional qualification standard suitable for GaN HEMTs and new reliability studies focused on GaN HEMTs are needed. In this section, the reliability of GaN devices in power electronics application and the needs for additional reliability studies will be discussed.

#### **1.3.1. RELIABILITY OF POWER DEVICES IN POWER ELECTRONICS**

Power devices play a crucial role for the reliability of power electronics systems. The systems consist of various components such as a power device, gate driver IC, inductor, capacitor, resistor, transformer etc. They can affect individually the reliability of the entire systems [35]. There was a survey to inverstigate which device is critical for the reliability of power electronics products [36]. A pie chart in Figure 1-8 shows the failure contribution in power electronics systems from the survey. In

Figure 1-8 Failure distribution in power electronic systems from the survey [36].

the survery, it is revealed the the power device are the most breakable element in a power electronics product. In this regard, securing the robustness of the power device allows for a more rubust systems.

Thermo-mechanical stress is a significant stressor that can destroy power devices [37]. For this reason, there had been many studies on test methodes, failure mechanisms, and life time modeling of the failure induced by thermo-mechanical stress [38-40]. The failure mechanism from the thermo-mechanical stress can be described with the different coefficient of thermal expansion (CTE) among the material constituting a power device. In the above survey, the half of overall converter operation is subjected to juction temperature swings larger than 80 degree Celcius [36]. The repeated temperature variation during operating provokes the thermo-mechanical stress amongst elements inside a power device. Finally, the power device loses their normal function due to this stress at a certain point in time.

### **1.3.2. FAILURE MECHANISMS BY A POWER CYCLING TEST**

There are representative two test methodologies relevant to verify the robustness of a power device against the repeated thermal-mechanical stress: i) temperature cycling test and ii) power cycling test. The temperature cycling (TC) test is called a passive TC test because they use external temperature swings [41]. It is to examine the reliability of package technologies for ambient temperature changes. In contrast, the PC test is closer to the actual operation of the power devices because the test simulates the temperature changes from heat generated at the internal junction by the power consumption of a power semiconductor chip. The failure phenomenon by the PC test can occur in not only the package area but also the semiconductor chip area [42-46].

There are provoked failure mechanisms that can occur in the PC test [47]: bond wire fatigue, solder fatigue, metallization reconstruction, gate oxide failure, and burnout failure. A device under test for the PC test consists of a power semiconductor device and a heat sink structure. The bond wire fatigue and the solder fatigue are the predominant failure mechanisms in the power devices. Although these two are observed outside a power semiconductor chip, the other three failure modes are related to the power chip. These various failure mechanisms reflect the underlying device technology. To date, studies on the failure mechanism by the PC test have been conducted mainly with Si-based power devices such as IGBT or MOSFET [38-48].

### 1.3.3. RELIABILITY OF GAN HEMTS

The reliability of commercial power GaN HEMTs can be one of the biggest challenges to occupy the new or current power electronics markets [49]. Some companies are performing their reliability tests for their products based on Joint Electron Device Engineering Council (JEDEC) standard. Table 1-4 exhibits the qualification results of

| Test items                                                    | EPC  | Transphorm | Panasonic | GaN<br>Systems      |

|---------------------------------------------------------------|------|------------|-----------|---------------------|

| High temperature<br>reverse bias (HTRB)                       | Pass | Pass       | Pass      |                     |

| High temperature gate<br>bias (HTGB)                          | Pass | -          | Pass      |                     |

| High temperature<br>storage life (HTS)                        | Pass | Pass       | Pass      |                     |

| High temperature high<br>humidity reverse bias<br>(H3TRB)     | Pass | -          | Pass      | Under<br>qualifying |

| Temperature cycling<br>test (TC)                              | Pass | Pass       | Pass      |                     |

| Power cycling test (PC)                                       | Pass | Pass       | Pass      |                     |

| Highly accelerated<br>temperature and<br>humidity test (HAST) | -    | Pass       | -         |                     |

Table 1-4 The qualification results of major products from the manufactures [50-53].

major products from the manufactures: EPC, Transphorm, Panasonic, and GaN Systems [50-53]. Their reliability qualification is work in progress in the first half of

2018 and will be continuously updated. The reliability reports of EPC and Panasonic corporation particularly include the electrostatic discharge (ESD) test results. In case of GaN Systems, they announce that their devices success beyond ten times of JEDEC requirements [53] and do not release in detail reports yet. In spite of these various efforts, one remaining question for this reliability assessment is "Is the existing JEDEC standard sufficient to ensure the reliability of the current power GaN devices ?" [49, 54].

The mainstream standards of significant power devices are providing reliability assessment methods and verification criteria [55-57]. They reflect the enormous knowledge and experiments accumulated over the last few decades. Basic reliability research for the standards is based on finding various failure modes and lifetime models against a couple of stress sources. Actually, the conventional investigation mostly had been implemented with Si-based devices. Due to these standards, many Si-based power device manufacturers have been able to stably supply their products to the market. The qualification standards have been very mature for Si-based power devices.

There is a new movement to develop the specific qualification standard oriented to power GaN devices. Most reliability standards including JEDEC was established by Si device procedures [55-57] so that the conventional evaluation methodologies need to be extended to be appropriate for power GaN HEMTs. GaN Standards for Power Electronics Conversion Devices Working Group (GaNSPEC DWG) that comprises industry experts is leading this action [58]. Their objectives are to create standards and guidelines for test methods, reliability & qualification procedures, and datasheet parametric for power GaN devices. They are working closely with JC-70.1 the new committee involved in a GaN device in JEDEC [59]. Hence, we will soon see the new JEDEC standard for a power GaN device and products satisfied by the standard on the market.

Besides, new possible failure modes of GaN HEMTs have to be taken into consideration [54]. GaN HEMTs employing 2DEG have a fundamentally different structure from Si MOSFET or IGBT using p and n junctions. Apart from a semiconductor part, package technologies they use also are challenging compared to conventional packages of power devices. LGA and GaNPX are package technologies without a bond-wire that do not apply to other Si-based or SiC-based discrete power devices. There already had been many studies on the failure phenomenon confirmed distinctively in GaN HEMT technology [60-62]. Therefore, the reliability of power GaN HEMTs has to be investigated in various degrees outside of the Si device range.

The market always wants power devices to have better performance than the present. One of the GaN device performances the power electronics market expects for the future may be the higher operation junction temperature over 150 Celcius degrees [63]. All Si-based semiconductor cannot be used over the 150 Celcius degrees due to the intrinsic property of Si material, while GaN HEMT is able to operate over the temperature [64]. If the temperature limitation of power device can increase, it can efficientively reduce the complex thermal management structure that occupies a large area in overall power systems [65]. Electric vehicles (EV) applications are interested in this performance [63]. Nevertheless, raising the operating temperature should cause the severe reliability problems. For these reasons, GaN HMETs also require constant research regarding the reliability with high temperature.

## **1.4. THESIS OBJECTIVES**

### 1.4.1. RESEARCH QUESTIONS AND OBJECTIVES

The fundamental goal of this thesis is to understand the GaN device technology in power applications. Power GaN devices are standing at the beginning of their long journey, considering the entire history of Si power devices until now. In spite of the enormous interest in the GaN devices from power electronics engineers, their present market share of power applications is not high. But, as the new markets that need GaN devices will progressively emerge and expand, their market prospects are up-andcoming. New various techniques have been applied to GaN HEMTs with a sudden change of the market. These new attempts have not been studied enough to convince the market. Therefore, these cutting-edge techniques should be deeply investigated for GaN HEMTs to succeed in the power electronics market.

Two big topics to describe the device technology should be electrical performance and reliability of GaN HEMTs in power electronics applications. It is known that the electrical performance of GaN devices can theoretically go beyond SiC as well as Si. We can understand the matured GaN device technology at present with commercial GaN devices. Considering the reliability of power electronics systems, the robustness of the GaN device against thermo-mechanical stress is essential to convince the market. Unfortunately, possible failure mechanisms related to GaN devices against the thermo-mechanical stress have not been sufficiently investigated yet. Besides, for better performance and reliability of GaN HEMTs for the future, various design and structural factors of the devices also should be multiply analyzed here and now. Taking into account the needs for investigating GaN device technologies, the following research questions are raised:

- 1. Where has been a current location of commercial GaN devices on the way to their theoretical limit?

- 2. How to evaluate the robustness of a commercial power GaN device with an advanced electrical performance against thermo-mechanical stress?

- 3. What are failure mechanisms of a commercial power GaN device regarding thermo-mechanical stress? And, is there any possible failure phenomenon that uniquely happens in GaN devices regarding that stress?

- 4. What are the primary factors of power GaN devices to optimize their electrical performance and reliability?

To answer for the above research questions, studies on the performance, reliability, and optimization of GaN devices are performed.

The primary objectives of this project are

- 1. To compare the performance of commercial power GaN devices using the FOM.

- 2. To conduct accelerated power cycling (PC) tests for the selected GaN device and to evaluate the reliability of the tested power GaN device.

- 3. To analyze the specific failure mechanisms of GaN devices aged by the power cycling test.

4. To find the critical design and structural factors for optimizing performance and reliability of GaN HEMTs.

In this thesis, the performance assessment of the leading commercial power GaN devices is conducted for the first objective. In the result of the assessment, the stateof-the-art commercial GaN device is selected for the PC test, and the accelerated power cycling test with the selected GaN device is carried out for the second objective. The specific failure mechanisms of aged GaN devices is analyzed in detail for third objectives. For the last objective, various design and structural factors that can affect device performance are reviewed based on the literature of conventional GaN HEMTs, and an experiment plan to optimize electrical performance and reliability of a GaN HEMT is proposed.

#### **1.4.2. PROJECT LIMITATIONS AND ASSUMPTIONS**

In Chapter 2, seven GaN devices of seven different models on the market have been selected for performance assessment. Electrical characteristics of the power device products in a single model are normally distributed in the specification limits promised by a manufacturer. Some device variation in electrical parameters is to be expected even with the same product. The characteristics measured with one selected devices may not precisely represent the technology of devices due to the distribution. Hence, there can be in a little gap between the measured characteristics and the representative values of each model, but still, key performance characteristics can be compared between devices.

In Chapter 3, the power cycling tests were conducted with only one type and only a restricted number of samples to allow failure mechanism in-depth analysis of the degradation. Stress conditions were accelerated compared to temperature swing in practical operation in the field in PC tests to obtain the results in a reasonable test time. These PC tests had been conducted with the two kinds of temperature swings 100 and 125 Celsius degrees to confirm the failure phenomenon within reasonable test time. A failure phenomenon in the PC test with the relatively lower temperature swing, however, may be different from the failure phenomena observed in the accelerated PC tests. Hence, further PC tests are required with lower temperature swings below 100 degrees Celsius. Besides, during PC tests, electrical characteristics are periodically carried out to diagnose test sample health in a curve tracer machine separated from the PC test circuit. If this measurement result determines a failure, it is difficult to specify the exact number of cycles to the failure because this measurement interval is around thousands of cycles. The studies were focused on failure mechanism analysis.

In Chapter 4, a new failure mechanism, that had not been reported in conventional PC tests with Si-based devices, is observed. Various experiments and analysis were conducted to understand this new failure phenomenon. Although a reasonable failure

mechanism based on the test results and logical analysis was proposed in this thesis, the additional experiment, physical failure analysis using photon emission microscope, and finite element method simulation are currently being investigated, but results are not concluded in this paper.

In Chapter 5, an efficient experiment plan was suggested with statistical analysis and Technology Computer-Aided Design (TCAD) simulation results to optimize electrical performances and reliability of power GaN HEMTs. To finally verify these analysis results, GaN HEMTs that reflect the above experiment plan are being manufactured at Chalmers University of Technology. The evaluation results of the real GaN HEMTs will be discussed and will be published further outside this report.

## 1.5. OUTLINE OF THE THESIS

The Ph.D. dissertation of six chapters is organized as the follows:

#### **Chapter 1: Introduction**

The background and motivation for this research project are demonstrated. The objectives of this project corresponding to the proffered research questions also are presented. Finally, the outline of an entire thesis is explained here.

# Chapter 2: Performance assessment of commercial GaN-on-Si discrete power device with a figure of merit

Performances of the selected commercial GaN devices are assessed with two sorts of FOM:  $R_{DS(ON)}$  \* Area and  $R_{DS(ON)}$  \*  $Q_g$ . For the reliable FOM, electrical parameters of the selected commercial GaN devices are characterized under the same test environment. Each parameter by devices is defined under the consistent concept proposed in this chapter. Decapsulating discrete devices derive active area information of each device needed in the first FOM. The performances of each device are compared each other with the extracted FOM based on the measured values, and the possibility of power GaN devices is discussed with their theoretical limit.

# Chapter 3: Power cycling test for a cutting-edge GaN device in power application

Overall test environment and result analysis for the implemented PC tests are demonstrated in detail. For the PC test environment, the fundamental operating principle and the methodology for monitoring the DUT health aged are presented. In the test results, a failure mechanism confirmed at the end of the test is analyzed with the monitored data and addition physical failure analysis.

# Chapter 4: Failure mechanism analysis of off-state drain-to-source leakage current failure in PC test

Newly detected failure phenomenon that has not been reported in the PC tests with Si-based power devices has been introduced. A hypothesis is proposed, and additional experiments and physical failure analysis are implemented to evaluate this hypothesis. Also, various failure mechanisms to be able to provoke this failure are reviewed based on the current literature regarding GaN HEMTs for RF and power applications.

#### Chapter 5: Optimization of high voltage GaN HEMT for power application

Design factors and structure factors of GaN HEMTs that affect the electrical performance are discussed based device information from the literature and TCAD simulation. Importance of each factor is confirmed with statistical analysis methodology. Finally, an logical experiment plan that reflects significant factors extracted from the importance review result is proposed.

#### **Chapter 6: Conclusion and Future work**

This chapter presents the summary, main findings and conclusion of this thesis. Topics for the future research are also discussed.

In the end of the thesis, the published papers during the Ph.D. study period are attached.

### **1.6. LIST OF THE PUBLICATIONS**

#### A. Journal

[J.1] S. Song, S. Munk-Nielsen, and C. Uhrenfeldt. "Failure mechanism analysis of off-state drain-to-source leakage current failure of a commercial 650 V discrete GaNon-Si HEMT power device by accelerated power cycling test," Microelectronics Reliability, Vol. 76-77, pp. 539-543, Jul. 2017.

#### B. Conference

[C.1] S. Song, S. Munk-Nielsen, C. Uhrenfeldt, and I. Trintis, "Performance Assessment of Commercial Gallium Nitride-on-Silicon Discrete Power Devices with Figure of Merit," in Proc. of IEEE Industrial Electronics Society (IECON), pp. 1143-1148, Oct. 2016.

[C.2] S. Song, S. Munk-Nielsen, C. Uhrenfeldt, and I. Trintis, "Failure Mechanism Analysis of a Discrete 650 V Enhancement Mode GaN-on-Si Power Device with

Reverse Conduction Accelerated Power Cycling Test," in Proc. of IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 756-760, Mar. 2017.

[C.3] S. Song, S. Munk-Nielsen, C. Uhrenfeldt, and K. Pedersen, "Power Cycling Test of a 650 V Discrete GaN-on-Si Power Device with a Laminated Packaging Embedding Technology," in Proc. of IEEE Energy Conversion Congress and Expo (ECCE), pp. 2540-2545, Oct. 2017.

## CHAPTER 2. PERFORMANCE ASSESSMENT OF COMMERCIAL GAN ON SI DISCRETE POWER DEVICES WITH A FIGURE OF MERIT

Commercialized GaN devices can provide more compact, fast switching, and more efficient power conversion systems for users compared to Si-based devices. Even though their market share is not high, they are drawing much attention from the market. A FOM is used objectively to assess and compare their performance to other devices. The FOM is expressed by electrical characteristics and actual die area of each device. In this chapter, electrical characteristics of each device measured in the same test environment and the active areas derived by decapsulation of packages are introduced. The performances of commercial GaN devices are evaluated with their FOM based on the measured data. Their development possibility is discussed based on their theoretical limit.

## 2.1. FOM OF GAN POWER TRANSISTORS

The FOM of power switching devices becomes an objective barometer when a designer of a power conversion system selects a power device [66]. There are two types of FOM that typify the performance of power devices: the specific on-state resistance ( $R_{sp}$ ) and on-state resistance ( $R_{DS(ON)}$ ) multiplied the gate charge ( $Q_g$ ) [6]. The  $R_{sp}$  is expressed as the product of an  $R_{DS(ON)}$  and an active area (A) representing the area of the die actually operating in the package. They are ultimately associated with power efficiency of a power conversion system. Hence, the information helps the user to choose a power device.

$\begin{array}{rcl} & - & 1^{st} \mbox{ FOM: } R_{DS(ON)} \cdot A = R_{sp} & \leftarrow \mbox{ conduction loss capability} \\ & - & 2^{nd} \mbox{ FOM: } R_{DS(ON)} \cdot Q_g. & \leftarrow \mbox{ conduction and switching loss capability} \end{array}$

The FOM of a power device elucidates its quantitative performance, technology competitive, and potential for development. The performance and technology competitive of power GaN devices can be demonstrated compared to a Si-based device in a similar level of the maximum drain voltage. Also, the possibility of the power GaN devices can be discussed with their theoretical limits introduced in Section 1.1.3. Obtaining the exact FOM is very important because of these various meanings. Although  $R_{DS(ON)}$  and  $Q_g$  values representing their specific models are basically provided in their datasheet, the difference in measurement methods and measurement conditions can produce unwanted errors in the FOM comparison. Therefore, it is

significant to evaluate their electrical characteristics under the equivalent measurement methodology for the more accurate FOM.

## 2.2. MEASUREMENT METHODOLOGY

It is essential for a designer of power conversion systems to choose the proper device. A power device selected can directly affect the performance of the entire system. Electrical characteristics and FOM of a power GaN device should be valuable information to pick out them. Choosing representative samples and reasonable test environment are essential to obtain a significative result. In this section, the state-of-the-art commercial GaN devices for evaluation and the environment to test them is introduced.

#### 2.2.1. REVIEW OF TEST SAMPLES

Current commercial GaN devices embody full-grown cutting-edge technologies. Power density and parasitic elements of current GaN devices had been substantially improved when compared to the early products. A complete normally-off operation of a commercial power device had been achieved in power application. The normallyoff operation is not required of a GaN HEMT in RF applications. The commercial GaN devices can be divided into an enhancement mode group and a cascode group

| Commons        | Name of | Information of samples |                                 |                              |              |

|----------------|---------|------------------------|---------------------------------|------------------------------|--------------|

| Company        | sample  | $V_{DS\_MX}{}^a$       | V <sub>GS_MX</sub> <sup>b</sup> | I <sub>ON</sub> <sup>c</sup> | Package      |

|                | EP-30   | 30                     | 5                               | 60                           | LGA<br>[26]  |

| EPC            | EP-60   | 60                     | 5                               | 60                           |              |

| EIC            | EP-100  | 100                    | 5                               | 60                           |              |

|                | EP-200  | 200                    | 5                               | 8.5                          |              |

| GaN<br>Systems | GS-100  | 100                    | 7                               | 90                           | GaNPX        |

|                | GS-650  | 650                    | 7                               | 30                           | [23]         |

| Transphorm     | TR-600  | 600                    | 8                               | 17                           | PQFN<br>[67] |

$V_{DS\_MX^a}$ : Drain to source maximum operating voltage  $V_{GS\_MX^b}$ : Gate to source maximum operating voltage  $I_{ON^c}$ : Continuous drain to source current in on-state at 25 °C

Table 2-1 Information of test samples based on data sheet [16,17,28-32].

based on the way to implements the normally-off operating. These two groups are clearly distinguished from each other in electrical characteristics. Improvement of their power density capability is currently underway. The power density of commercial GaN devices can be demonstrated by the comparison of their FOM to the state-of-the-art silicon device. The seven GaN power devices, which are reflected in the state-of-the-art technology of a commercial GaN device, have been assessed. They are built in a grown epitaxial GaN layer on a Si substrate wafer in common and utilize different package solutions by a company.

Table 2-1 displays the critical information for each sample as collected from the datasheets offered by the manufacturers. Commercial GaN device products assure a maximum drain-to-source voltage up to 650 V. Product lines of the GaN devices are distributed widely from 15 V to 650 V of maximum operating voltage. There are not many kinds of the products by voltage rating in the market under 200 V. Most GaN manufactures aim to the 600s V-rated applications. In this chapter, representative voltage levels of commercial GaN devices are firstly decided considering main applications, and then the typical devices in the similar voltage level are selected for electrical characteristics. Package solutions employed by each manufacturer are various, which is to maximize the potential of their GaN transistors.

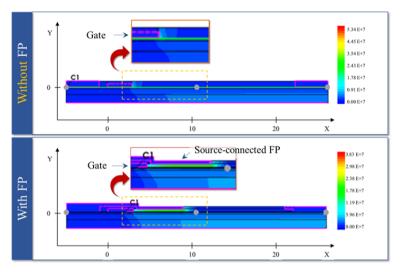

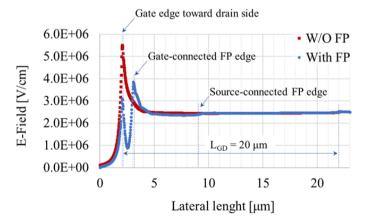

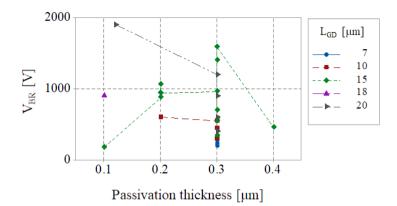

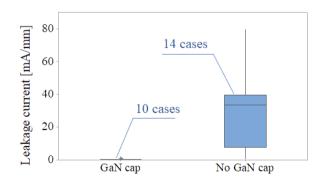

## 2.2.2. TEST ENVIRONMENT