### **Aalborg Universitet**

## Smart SiC MOSFET accelerated lifetime testing

Baker, N.; lannuzzo, F.

Published in: Microelectronics Reliability

DOI (link to publication from Publisher): 10.1016/j.microrel.2018.07.067

Creative Commons License CC BY-NC-ND 4.0

Publication date: 2018

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Baker, N., & lannuzzo, F. (2018). Smart SiC MOSFET accelerated lifetime testing. *Microelectronics Reliability*, 88-90, 43-47. https://doi.org/10.1016/j.microrel.2018.07.067

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ?

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Smart SiC MOSFET Accelerated Lifetime Testing

# N. Baker, F. Iannuzzo

Aalborg University, Aalborg, Denmark

#### **Abstract**

Accelerated lifetime testing of power modules is time consuming and expensive due to the destructive nature of the tests. Therefore, it makes sense to extract as much data as possible from each consumed component. Traditional power cycling methods, however, monitor a single parameter and stop the test after this parameter reaches a predefined threshold. This leaves little data available for real-time analysis of the aging process, which instead must take place post-failure. In this paper, we present full results from a power cycling test on SiC MOSFETs which uses a novel method to extract both the semiconductor die resistance and bondwire resistance separately. Using this method, we are able to observe degradation phenomena that has previously been hidden when using conventional monitoring methods. We hope that the presentation of this data will demonstrate the incentive to incorporate smart monitoring functions during accelerated lifetime testing of power semiconductors. In essence, we aspire to advance the techniques in this area to provide a 'window' into the module, which allows the failure process to be accurately observed in real time. In turn, we hope these methods will allow more targeted improvements to module design from a reliability perspective.

#### 1. Introduction

#### 1.1. Accelerated Lifetime Testing in Power Modules

Power semiconductors are among the most expensive and unreliable components in power electronic systems. They are used to provide high efficiency power conversion in applications encompassing renewable energy generation, automotive, railway, aerospace and motor drives. Reliability is of utmost importance for both economic and safety reasons. Therefore, power semiconductor module manufacturers and their customers spend considerable resources on assessing the reliability aspects of these components.

Reliability assessment of power semiconductor modules is commonly performed using accelerated aging test techniques known as power cycling. The modules are mounted on a heatsink and a forward current is applied. This current through the device leads to a power loss throughout the entire module and results in an increase in semiconductor junction temperature. By periodically switching the current on and off, the temperature of the semiconductor will rise and fall accordingly. This temperature swing induces

thermomechanical stress which ages the module. One period of heating and cooling via the conducting current is generally referred to as a 'power cycle'. Depending on the absolute temperature swing, module type, and test procedure, it may take anywhere between a few thousand, to tens of millions, of power cycles until module fails [1].

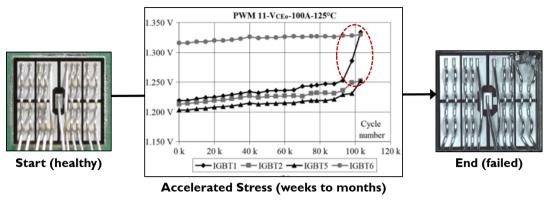

Fig. 1 displays a depiction of the above described traditional power cycling test on a power semiconductor module. Power cycling tests are generally time consuming – commonly used cycle periods are between 0.2 seconds to 1 minute [1] – so testing with high numbers of power cycles can take up to several months [1, 2].

In most power cycling tests, an electrical parameter is usually monitored and the test is stopped after this parameter reaches a predefined threshold indicating that the device is at the end of its life.

The most commonly used failure parameters are the collector-emitter voltage ( $V_{CE}$ ) and thermal resistance ( $R_{TH}$ ) [1, 3, 4]. According to a 2016 survey on power cycling tests [1], over 60% of power cycling tests select an increase of between 5-20% in  $V_{CE}$  or  $R_{TH}$  as the signal to conclude the test, while 8% of

$\mathbf{V}_{\mathsf{CE}}$  is monitored to indicate when test has ended

Figure 1. Graphical depiction of a power cycling test on IGBTs, all figures taken from [5]

studies simply wait until the module reaches complete failure. The monitored failure parameter may often be recorded with little resolution and primarily used as a trigger to signal the conclusion of the test.

This approach is adequate if the goal of the power cycling test is to validate that a module can survive a certain number of power cycles, or acquire data for the generation lifetime models.

However, basic monitoring such as the above provides little data to examine for insight into the degradation process as the test progresses, i.e. the degradation process cannot be observed in real-time, and the final cause of failure must be determined using post-failure analysis. Since up to 40% of power cycling tests are performed with the intention to analyse the failure process (along with the influence of design changes on this process) [1], it would make sense to have data regarding the entire aging process, rather than a 'before and after' picture as is common now. This would also provide efficient use of the time consumed in power cycling tests with large amount of power cycles to complete.

#### 1.2. Silicon Carbide MOSFETs

Silicon Carbide (SiC) MOSFET modules are often cited as a future alternative to Silicon (Si) IGBTs that will allow operation of power converters at higher frequency, efficiency, and temperature. They are now commercially available with current ratings of several hundred Amps. Nevertheless, the reliability, and reliability testing procedures for SiC MOSFET modules remain an important issue.

First of all, SiC has different material properties in comparison to Si. The coefficient-of-thermal-expansion is slightly higher in SiC, while the Young's Modulus is 3 times higher. The result of this is differing thermo-mechanical strain inside the semiconductor for SiC and Si chips of identical

geometry. Early power cycling results on SiC devices have shown a reduced power cycling capability in comparison to Si devices, when transferring standard packaging techniques across to the SiC device [6].

Secondly, the failure mechanisms for SiC MOSFETs can be different to those of Silicon IGBTs. Therefore, the typical degradation indicators such as the  $V_{CE}$  (on-resistance in MOSFETs) or  $R_{TH}$  are unlikely to behave in the same manner. A prominent example of this is the instability of the threshold voltage in SiC MOSFETs, which can alter the measurement of both of these parameters [7, 8].

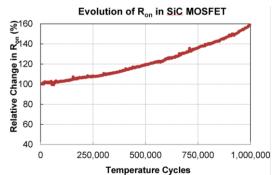

This can be seen in early publications regarding SiC MOSFET power cycling tests [8, 9]. For example, Fig. 2 shows the evolution of the on-resistance ( $R_{\rm ON}$ ) of a SiC MOSFET during an accelerated aging test from 2013 [9]. The  $R_{\rm ON}$  increases over 60% from the original value without the device experiencing a failure. It is not possible to ascertain what mechanism is causing this increase (i.e. whether it is packaging related or semiconductor die related), nor whether the device is actually close to failure, unless post-failure analysis is used.

Figure 2. Evolution of R<sub>ON</sub> of a SiC MOSFET in TO-247 packaging during a power cycling test [6].

A further issue is that the cost per component for SiC MOSFETs is an order of magnitude greater than

Si devices. Therefore, it makes sense for reliability researchers to be able to maximise the amount of data collected from each SiC MOSFET during power cycling tests, in order to understand more quickly the degradation process without incurring unnecessary financial expense.

#### 1.3. Paper Objectives

Power cycling on Si IGBTs is very well established, with over 60% of all studies being performed on the IGBT from 1994 – 2016 [1]. Nevertheless, the issues outlined above regarding SiC MOSFETs having differing material properties, failure mechanisms, and the high cost per component, mean that we feel that directly transferring power cycling techniques from Si IGBTs to SiC MOSFETs is not an efficient strategy.

In particular, we feel that there is the need (and opportunity) to increase the amount of acquired data during the power cycling process. Monitoring a single failure parameter to trigger the conclusion of the power cycling test is inefficient in both time and money in order to gain insight into the aging process inside the SiC MOSFET.

As a result, in his paper we will present full results from a power cycling test on SiC MOSFETs which uses a novel method to extract both the semiconductor die resistance and bondwire resistance separately. We monitor both parameters with high measurement and temporal resolution, which enables monitoring of the bondwire resistance to  $\mu\Omega$  resolution.

Using this method, we are able to observe degradation phenomena that has previously been hidden when using conventional monitoring methods. We would like to note that the presented monitoring method can also be used in Si IGBTs, however the spur to develop this method was brought upon by the issues with SIC MOSFETs highlighted in Section 1.2.

#### 2. Power Cycling Test Bench

# 2.1. Semiconductor Die and Bondwire Resistance Monitoring

The origins of the test bench stem from the use of the auxiliary-source terminal which is common in many SiC MOSFETs (although not all) due to their fast switching nature. The auxiliary-source terminal is present in SiC MOSFETs to provide the reference potential for the gate control voltage. This separates the current path of the control current from the path of the load current, and results in increased switching

speed and efficiency [10].

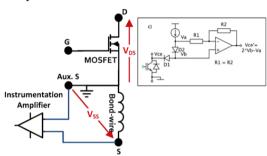

The auxiliary-source terminal provides the opportunity for separate monitoring of the voltage drop across the semiconductor die and the voltage drop across the bondwires and the source side packaging [11]. Fig. 3 displays the measurement principle.

Figure 3. Schematic of measurement principle for measuring voltage across the semiconductor die and bondwires separately in a device with an auxiliary-source connection [11].

We previously provided a preliminary proof-of-concept for this measurement concept in a high voltage single phase converter [11]. However, we have since improved the measurement system considerably, and in this paper we apply the measurement concept to 12 SiC MOSFETs in a low voltage power cycling test.

Outside of [11], a review of past literature does not yield any evidence of previous use of the auxiliary-source connection to monitor the die and bondwire resistance separately. However, one study was performed by Farokhzad et al. in 1996 [12, 13]. This study was performed on IGBTs, and an additional current source was used to inject a sensing current (independent of the load current) between the power-emitter and auxiliary-emitter. The primary difference in the method presented in this paper is that the resistance between the power-source and auxiliary-source is evaluated while the device is conducting the load current, and no additional sensing current source is used.

#### 2.2. Power Cycling Setup and Results

We performed power cycling tests on 12 SiC MOSFETs from two different Wolfspeed CCS020M12CM2 six-pack modules. Figure 4 displays a photo of the measurement board used to monitor both the die resistance and bondwire resistance during the test, along with an image of the SiC MOSFET die and bondwires in question. The MOSFETs were rated for approximately 20A and each contained 2 bondwires.

Electrical measurements were made primarily using operational amplifiers and 14-bit AD7367 analogue-to-digital converters. An ARM mbed LPC1768 (not shown in the photo) is used to control the test bench and stream data real-time into a MATLAB interface. To monitor the current through each MOSFET and calculate the die and bondwire resistance, we used an LEM current transducer.

The junction temperature was monitored using optical fibres. This is because the CCS020M12CM2 module contains external freewheeling diodes. If this had not been the case, we would have selected the voltage over the MOSFET body-diode as a TSEP to monitor the junction temperature [14].

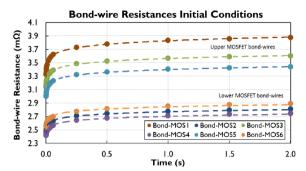

The bondwire resistances can be measured to a  $\mu\Omega$  resolution, and we make 20 measurements of both resistances during each on-pulse during the power cycling test.

As an example, Figure 5 shows an example of the transient response of the bondwire resistance for the six MOSFETs in the module during a 2-second onpulse. The total resistance of the bondwires in the lower side MOSFETs are approximately  $1m\Omega$  lower than those on the upper side MOSFETs – possibly due to layout discrepancies. In addition, the self-heating of the bondwires can clearly be observed through the use of this measurement – for example, the bondwires of MOSFET 1 increase from  $3.3m\Omega$  to  $3.9m\Omega$ .

Figure 4. Photo of Measurement Board for SiC MOSFET Power Cycler, including image of MOSFET die from the module.

Figure 5. Transient response of the bondwire resistances for six SiC MOSFETs during a 2-second on-pulse in a power cycling test.

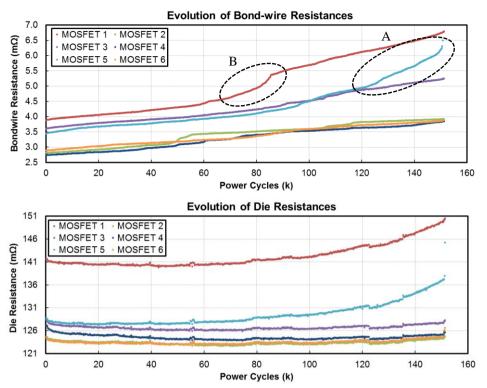

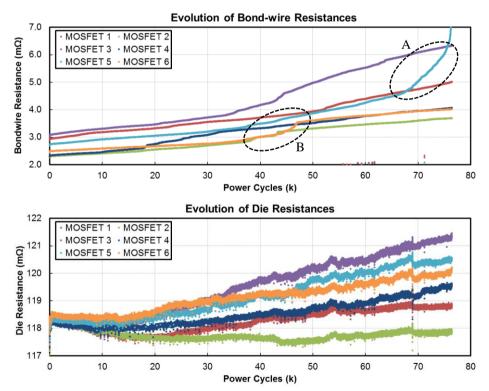

Fig. 6 and 7 displays the evolution of both the die and bondwire resistance during the power cycling test for each set of six MOSFETs from the module. The modules were tested under differing current levels and this therefore explains the discrepancy between the number of cycles until failure.

We are able to make an interesting observation of both linear and stepwise degradation processes of varying speeds in the bondwires. Stepwise increases have typically been associated with actual bondwire lift-off in past aging studies [3, 4]. However, in this study the first complete bondwire lift-off of the two bondwires on the MOSFET lift off after approximately 150k and 75k power cycles.

We can also observe a decrease in the voltage across the MOSFET die, which is due to  $V_{TH}$  shift dominating over increase in thermal resistance.

Most notably, we would like to point out the phenomena outlined in circles A and B in both modules. It is interesting to note that in both modules, it is MOSFET 5 that experiences failure first. Before the failure however, the bondwires in both MOSFETs display a marked increase in the linear rate of aging for the final 10-15% of the test cycles, this is marked by circle A.

Additionally, we would like to point at the phenomenon depicted by circle B in MOSFETs 1 and 6 for module A and B respectively. Here, the bondwires also display a rapid increase in the degradation rate, however rather than leading to a bondwire lift-off, the process abruptly slows down and continues at the same rate as previous.

We are unable to find any previous observation such as this in any prior power cycling studies, and therefore the contrast between the events of A and B are an area that require further research.

#### 3. Conclusion

In this paper results from a power cycling test on

SiC MOSFETs which uses a novel method to extract both the semiconductor die resistance and bondwire resistance separately. We are able to observe that the aging process of the bondwires is a combination of stepwise and linear process, and we are able to identify degradation phenomena that has previously been hidden when using conventional monitoring methods.

We hope that this work can be expanded upon with further investigation into the phenomena outlined by circles A and B in Figs. 5 and 6, and to continue to advance the monitoring strategies in power cycling tests in order to ever more details on the real-time aging process in power modules.

#### References

- [1] C. Durand, M. Klingler, D. Coutellier and H. Naceur, "Power Cycling Reliability of Power Module: A Survey," in IEEE Transactions on Device and Materials Reliability, vol. 16, no. 1, pp. 80-97, March 2016.

- [2] W. Kanert, Active cycling reliability of power devices: Expectations and limitations, Microelectronics Reliability, Volume 52, Issues 9–10, 2012, Pages 2336-2341.

- [3] U. M. Choi, F. Blaabjerg and S. Jørgensen, "Power Cycling Test Methods for Reliability Assessment of Power Device Modules in Respect to Temperature Stress," in IEEE Transactions on Power Electronics, vol. 33, no. 3, pp. 2531-2551, March 2018.

- [4] Oh, H.; Han, B.; McCluskey, P.; Han, C.; Youn, B.D. Physics-of-Failure, Condition Monitoring, and Prognostics of Insulated Gate Bipolar Transistor Modules: A Review. IEEE Trans. Power Electron. 2015, 30, 2413–2426.

- [5] V. Smet, "Aging and failure modes of IGBT power modules undergoing power cycling in high temperature environments," Ph.D. dissertation, Dept. IES (Southern Electr. Inst.), Montpellier 2 Univ., Montpellier, France, 2010.

- [6] C. Herold, M. Schaefer, F. Sauerland, T. Poller, J. Lutz and O. Schilling, "Power cycling capability of Modules with SiC-Diodes," CIPS 2014; 8th International Conference on Integrated Power Electronics Systems, Nuremberg, Germany, 2014, pp. 1-6

- [7] A. Ibrahim, J.P. Ousten, R. Lallemand, Z. Khatir, Power cycling issues and challenges of SiC-MOSFET power modules in high temperature conditions, Microelectronics Reliability, Volume 58, 2016, Pages 204-210.

- [8] F. Göthner, "Experimental Investigation of Operational Reliability of Silicon Carbide MOSFETs" Masters Thesis, NTNU, 2017

- [9] Baker, N.; Munk-Nielsen, S.; Bęczkowski, S. Test setup for long term reliability investigation of Silicon Carbide MOSFETs. In Proceedings of the 2013 15th

- European Conference on Power Electronics and Applications (EPE), Lille, France, 2–6 September 2013; pp. 1–9.

- [10] H. Li, S. Munk-Nielsen, X. Wang, S. Bęczkowski, S. R. Jones and X. Dai, "Effects of Auxiliary-Source Connections in Multichip Power Module," in IEEE Transactions on Power Electronics, vol. 32, no. 10, pp. 7816-7823, Oct. 2017.

- [11] N. Baker, H. Luo, and F. Iannuzzo, "Simultaneous On-State Voltage and Bond-Wire Resistance Monitoring of Silicon Carbide MOSFETs," Energies, vol. 10, no. 3, p. 384, Mar. 2017.

- [12] Farokhzad, B.; Türkes, P.; Wolfgang, E.; Goser, K. Reliability indicators for lift-off of bond wires in IGBT power-modules. Microelectron. Reliab. 1996, 36, 1863–1866.

- [13] Farokhzad, B. Method for Early Failure Recognition in Power Semiconductor Modules. U.S. Patent 6,145,107A, 7 November 2000.

- [14] C. Herold, J. Sun, P. Seidel, L. Tinschert and J. Lutz, "Power cycling methods for SiC MOSFETs," 2017 29th International Symposium on Power Semiconductor Devices and IC's (ISPSD), Sapporo, 2017, pp. 367-370.

Figure 6. Evolution of Die and Bondwire Resistances for Module A

Figure 7. Evolution of Die and Bondwire Resistances for Module B