# **Aalborg Universitet**

# Modified Secondary-Control-Based Fault Current Limiter for Inverters

Beheshtaein, Siavash; Savaghebi, Mehdi; Cuzner, Robert M.; Golestan, Saeed; Guerrero, Josep M.

Published in:

I E E E Transactions on Industrial Electronics

DOI (link to publication from Publisher): 10.1109/TIE.2018.2851970

Publication date: 2019

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Beheshtaein, S., Savaghebi, M., Cuzner, R. M., Golestan, S., & Guerrero, J. M. (2019). Modified Secondary-Control-Based Fault Current Limiter for Inverters. I E E Transactions on Industrial Electronics, 66(6), 4798-4804. [8408730]. https://doi.org/10.1109/TIE.2018.2851970

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ?

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 27, 2020

# A Modified Secondary-Control-Based Fault Current Limiter for Four-Wire Three-Phase DGs

Siavash Beheshtaein, Student Member, IEEE, Mehdi Savaghebi, Senior Member, IEEE, Robert M. Cuzner, Senior Member, IEEE, Saeed Golestan, Senior Member, IEEE, and Josep M. Guerrero, Fellow, IEEE

Abstract— Fault Current Limiters (FCLs) are one of the main solutions to upcoming challenges in microgrid protection. Regarding the high penetration of distributed generations (DGs) in future power system, designing cheap and effective FCL is a necessity. The present study addresses this issue by proposing an embedded FCL operating based on modifying the secondary control of four-wire DG. As this method is presented for a four-wire system, besides very low implementing cost, it has independency and flexibility to only limit the current of DG faulted phase. This study also provides real-time simulation results by OPAL-RT to compare the proposed method with a virtual-impedance-based FCL to validate its effectiveness. Finally, experimental results are presented to validate the effectiveness of the proposed FCL.

Index Terms— Fault current limiter, moving average filter (MAF), protection, secondary control.

## I. INTRODUCTION

URING the recent decades, different types of Fault Current Limiters (FCLs) including passive FCL (PFCL), superconducting FCL (SFCL), solid state FCL (SSFCL), and controlled-based FCL have been proposed [1]. PFCLs use passive elements to limit the fault current. Although it is the cheapest and simplest type of FCL, the voltage drop during the normal condition is the main drawback of this approach. SFCLs are classified into resistive and inductive types. Both types have the advantages of low power loss during the normal conditions and fast response. Whereas, high weight/size, requiring of an advanced cooling system, and high cost are their main drawbacks [2]. With the recent advances in the semiconductor technology, implementing the SSFCL has become more realistic and cost-efficient [3]. SSFCL have fast response and low weight/size; however it has high commutation and on-state losses [4]. Recently, wide bandgap power switches, which are mostly constructed based on Silicon Carbide (SiC) and Gallium Nitride (GaN) materials, have been developed commercialized [5].

Manuscript received October 21, 2017; revised December 06, 2017 and March 20, 2018; accepted June 07, 2018. (Corresponding author: Siavash Beheshtaein.)

S. Beheshtaein, M. Savaghebi, S. Golestan, and J. Guerrero are with the Department of Energy Technology, Aalborg University, Aalborg 9220, Denmark (e-mail: sib@et.aau.dk; mes@et.aau.dk; sgd@et.aau.dk; joz@et.aau.dk)

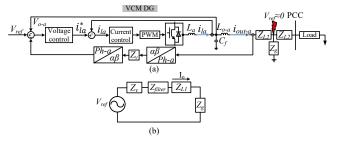

Fig. 1. (a) Model of a VCM-VSI connected to a load. (b) Equivalent model of the system from VCM-VSI perspective.

These devices have characteristics such as, low on-state loss, low thermal loss, high frequency, and high voltage capability. Thanks to these properties, wind band gap devices are a promising solution to address high loss of the SSFCL. In addition to these external FCLs, virtual impedance (VI)-based FCL had been proposed as a cost-efficient and low power loss solution to reduce fault current [6]. In this method, the VI is set to zero when the peak current is lower than its threshold and increases to a positive non-zero value when the peak current is larger than its threshold. However, due to no usage of any filters for current if a high level of current harmonics exists in the grid, the peak value of current is not a constant anymore. As a consequence, VI oscillates between zero and non-zero values, which results in loss of controlling. Furthermore, fixed value of maximum VI for all fault conditions, which is chosen in [6], leads to the same behavior. Because VI fluctuates between a zero and nonzero value when the required VI is lower than selected maximum values.

The objective of this study, which is an extension of the work proposed in [7], is addressing the aforementioned problems of VI-based FCL. To this end, a secondary control-based FCL is presented to limit the fault current to twice its nominal value for a four-wire three-phase DG working in the Voltage-Control Mode (VCM). The proposed FCL has a fast response and low implementation cost. The real-time simulation results as well as experimental results are presented to validate the efficiency of the proposed method over the VI-FCL.

R. Cuzner is with the Department of Electrical Engineering, University of Wisconsin-Milwaukee, Milwaukee, WI 53211 USA (e-mail: cuzner@uwm.edu)

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

# II. MULTILOOP CONTROL OF FOUR-WIRE THREE-PHASE INVERTER

In low-voltage microgrids, the three-phase four-wire system is a commonly used topology to support single-phase and unbalanced loads by building a path for the zero-sequence current of the loads. The three-leg inverter with split dc-link capacitors is one of the most widely used configuration where the midpoint of the dc-link is connected to a neutral point [8]. It must be noted that, four leg inverters can be used with the same purpose. In the islanded operation mode of the microgrid, at least one DG has to operate in the VCM to control both voltage and frequency.

Each VCM Voltage Source inverter (VCM-VSI) control system composes of a primary, secondary, and tertiary control. In the primary level, the droop control and virtual impedance is utilized to regulate the power sharing as well as stabilizing the voltage and frequency. In a VCM-VSI, the generated voltage reference is fed into inner control loops consisting of outer voltage loop and inner current loop to regulate the capacitor voltage.

In the steady state, voltage and frequency may deviate from their nominal values. In this case, the secondary control could be used to restore the voltage and frequency to their nominal values. In the secondary control level, proportional integral (PI) controllers are applied to generate proper control signals to be followed by droop controllers and restore both frequency and voltage to their nominal values. The related equations are as follows [9]:

$$\delta E = k_{PE} (E_{MG}^* - E_{MG}) + k_{iE} \int ((E_{MG}^* - E_{MG})) dt$$

(1)

$$\delta f = k_{Pf}(f_{MG}^* - f_{MG}) + k_{if} \int ((f_{MG}^* - f_{MG})) dt$$

(2)

where,  $f_{MG}$ ,  $f_{MG}^*$ ,  $E_{MG}$ ,  $E_{MG}^*$ , and  $k_{PE}(k_{Pf})$  as well as  $k_{iE}(k_{if})$  denote the actual frequency, reference frequency, actual voltage, reference voltage, and the parameters of PI controllers, respectively. Once these correction values of voltage and frequency are obtained, these signal values are sent to the primary control of each DG units.

#### III. PROPOSED METHOD

As mentioned before, the secondary control is used to manipulate voltage and frequency references to restore voltage and frequency, respectively. However, under faulty conditions a high compensation term has to be added to the voltage reference to approach output voltage to its nominal value. This approach results in the injection of a large current to the grid. Hence, the secondary control must be modified to avoid damage to the VCM-VSI.

The model of a simple microgrid that composes of a VCM DG, connected to a constant load is shown in Fig. 1 (a). For a fault happening between the VCM-VSI and PCC, the equivalent model of microgrid from the VCM-VSI perspective is presented in Fig. 1 (b).

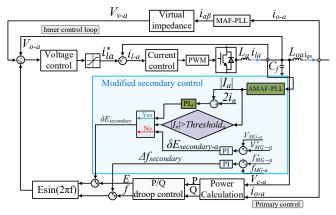

Fig. 2. Proposed FCL for voltage-control of phase-a of the three-phase four-wire VCM DG with a split dc capacitors.

Fig. 3. Proposed FCL for voltage-control of phase-a of the three-phase four-wire VCM DG with a split dc capacitors.

According to this Figure, the output current amplitude of VCM-VSI can be calculated as follows:

$$\left|\overrightarrow{I_o}\right| = \left|\frac{\overrightarrow{V_{ref}}}{Z_v + Z_{filter} + Z_{L11} + Z_g}\right| = \left|\frac{\left|\overrightarrow{V_{ref}}\right|}{\left|Z_{eg}\right|}\right| < \left|\overrightarrow{I_o}\right|_{max}$$

(3)

where,  $Z_v$ ,  $Z_{filter}$ ,  $Z_{L11}$ , and  $Z_g$  are VI, filter impedance, line impedance from DG to ground fault, and ground impedance, respectively. According to (3), the output current can be limited by reducing the reference voltage or increasing the VI. However, applying VI will convey current transient or current harmonics to voltage reference and it exerts disturbance to the grid in the first couple of cycles. In addition, determination of optimum VI for all fault locations and different fault impedances is not easy. Finally, it is necessary to determine an appropriate current threshold for the activation of VI during the fault. On the other hand, the modified secondary control has numerous advantages including simplicity in obtaining optimum value of the secondary voltage value during the faulty condition, robustness against the disturbance in current signal, and fast time response in comparison with VI method.

# A. Fault current limiter strategy

According to the traditional secondary control operation, if a current limiting threshold is not applied during the faulty conditions, a high amount of voltage amplitude is added to voltage reference of VCM-VSIs to keep microgrid voltage within an accepted level. This would lead to current considerable increase in the VSI output current. On the other hand, a converter-based DG has to protect itself from being damaged by limiting its output current. In order to have the capability of limiting fault current, this study presents a multifunctional secondary control that has two objectives:

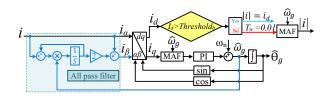

keeping the voltage amplitude at its nominal value during the normal operation and limiting output current of VCM-VSI to twice its nominal value. In the normal conditions, each voltage and frequency errors is passed through slow PI controllers to generate voltage and frequency compensation references, respectively. As it is shown in Fig. 2, where sf in PIsf is abbreviation of Secondary for Fault, this is val id while the current amplitude is below a definite threshold, Threshold<sub>a</sub>. However, once the current amplitude is above *Threshold*<sub>a</sub>, the objective of secondary control is changed from keeping voltage to its reference to keeping VCM-VSI current to twice its nominal current by reducing voltage reference. In the faulty condition, the amplitude of each phase is calculated by an Adaptive Moving Average Filter-based Phase Locked Loop (AMAF-PLL). As shown in Fig. 3, the single-phase AMAF-PLL utilizes a first-order all pass filter (APF), APF(s)=(ω<sub>g</sub>s)/ $(\omega_{\alpha}+s)$ , to generate a fictitious orthogonal signal. Although, APF has several benefits such fast dynamic response and low computation burden, it has no harmonic filtering ability. To deal with this issue, a MAF, which has high harmonic filtering, is used to provide a smooth dc signal in d and q frames [10]. The MAF is a rectangular window filter with the windows length of  $T_{\omega}$  and can be described in the s-domain as:

$$G_{MAF}(s) = \frac{1 - e^{-T_{\omega}s}}{T_{\omega}s} \tag{4}$$

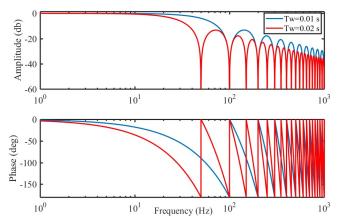

From (4), it can be conceived that a wide window length results in a slow transient response. By substituting  $s=j\omega$ , and performing some mathematical simplification, the magnitude and phase expression of MAF can be written as:

$$G_{MAF}(j\omega) = \left| \frac{\sin(\omega T_{\omega}/2)}{\omega T_{\omega}/2} \right| \angle - \omega T_{\omega}/2 \tag{5}$$

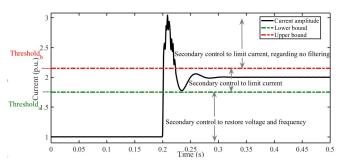

According to (5), in the zero frequency, the MAF gain is unity and for the frequencies equals to  $n/T_{\omega}$ , the gain is zero. The characteristics of MAF for two different window lengths are visualized in Fig. 4. As it can be seen, for  $T_{\omega}$ =0.01 s, all integer multiples of 100 Hz would be blocked by MAF. When the grid distortion pattern is unknown, it is recommended to consider  $T_{\omega}$ =0.02 s to eliminate the dc offset as well as all harmonics. It is reported that the MAF-PLL with  $T_{\omega}$ =0.02 s has a slow dynamic response [10]. This would result in delay in operation of the proposed FCL for the first couple of cycles. To address this issue, when the amplitude of current regarding all harmonic is above the  $Threshold_b$ , this value is considered as current amplitude to improve transient response at the expense of low harmonic filtering. This idea is implemented and visualized in Fig. 3 and 5, respectively. In addition to the AMAV-PLL, a saturation block with the value of 3 p.u. is used to limit the inner current loop reference. This block prevents a large inrush current in the inverter output.

### B. Optimization of the proposed FCL

As shown in Figs. 2 and 3, parameters including *Threshold*<sub>a</sub>, *Threshold*<sub>b</sub> as well as  $k_p$  and  $k_i$  of  $PI_{sf}$  are unknown.

In order to find the optimum values of unknown parameters, the following optimization problem must be solved:

Fig. 4. Bode plot of MAF for  $T_{\omega}$ =0.01 s, and  $T_{\omega}$ =0.02 s.

Fig. 5. Behaviour of secondary-control, regarding  $T\omega$ =0.02 s, during the three levels

$$\begin{aligned} &\textit{Minimize: } \sum_{i=1}^{N} \left| i_{ref}(i) - \left| i_{one-phase}(i) \right| \right| \Delta T_{s} \\ &i_{ref} = \begin{cases} 1 \ p. \ u. & for \left| i_{one-phase}(i) \right| < Threshold_{a} \\ 2 \ p. \ u. & for \left| i_{one-phase}(i) \right| > Threshold_{a} \end{cases} \\ &\textit{Subjected to: } \begin{cases} 0 \le k_{p} \le 1000 \\ 0 \le k_{i} \le 10000 \\ 1.6 \ p. \ u. \le Threshold_{a} \le 2.2 \ p. \ u. \\ 2.2 \le Threshold_{b} \end{cases} \end{aligned} \tag{6}$$

The lower bound of the  $Threshold_a$  is a triggering level for activation of the proposed FLC. This value must be higher than the VCM-VSI current magnitude during the maximum possible loads in the grid. In this letter, 1.6 p.u. is chosen as the minimum value of the *Thresholda*. The upper bound of the *Thresholda*, which is equal to the lower bound of Thresholdb, triggers acceleration of limiting fault current only for the first couple of cycles by measuring current amplitude regarding all current harmonics. As a result, the maximum value of  $Threshold_a$  or the minimum value of the *Threshold*<sub>b</sub> must be chosen in such a way to avoid harmonic effects during the faulty condition. Considering current harmonic of the inverter, 2.2 p.u. is selected for the minimum value of the *Threshold<sub>b</sub>*. In this study, optimization problem of (6) is solved by utilizing particle swarm optimization (PSO) algorithm [11]. It must be noted that the optimization procedure must be carried out for the harshest fault condition.

#### IV. REAL-TIME SIMULATION RESULTS

The model of Fig. 1 is implemented in OPAL-RT with sampling time of fixed 20  $\mu s.$  Other control parameters of VCM can be found in Table I.

In order to investigate the effectiveness of the proposed method, both the VI-based FCL and the proposed FCL are optimized for *scenario 1*. Then, those FCLs are investigated for *scenario 2* and 3:

TABLE I SYSTEM PARAMETERS

|                      | Parameters                                 |                                                                                                    | 37.1                                                                          |

|----------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Type                 | Symbol                                     | Quantity                                                                                           | Value                                                                         |

| Electrical setup     | $V_{dc}$                                   | DC Voltage                                                                                         | 650 V                                                                         |

|                      | $V_{MG}$                                   | Nominal voltage                                                                                    | 311 V                                                                         |

|                      | F                                          | Nominal Frequency                                                                                  | 50 Hz                                                                         |

|                      | С                                          | Filter Capacitance                                                                                 | 9 μF                                                                          |

|                      | L                                          | Filter Inductance                                                                                  | 1.8 mH                                                                        |

|                      | Lo                                         | Output Inductance                                                                                  | 1.8 mH                                                                        |

|                      | P <sub>load1</sub>                         | Load active power<br>(For real-time system)                                                        | 2 kW                                                                          |

|                      | R <sub>load2</sub> ,<br>R <sub>load3</sub> | Linear load impedance<br>(For experimental setup)                                                  | 230/115 Ω                                                                     |

|                      |                                            | Nonlinear load impedance<br>(For real-time system)                                                 | $46~\mu F, 8.4~mH,$ and $500~\Omega$                                          |

|                      |                                            | Nonlinear load impedance<br>(For experimental setup)                                               | $\begin{array}{cc} 235\mu F, & 0.084 \\ mH, \ and \ 115 \ \Omega \end{array}$ |

|                      | Zlinel                                     | Line impedance between constant<br>power load/nonlinear load and<br>inverter (for real-time setup) | 1.2 Ω +5.4 mH                                                                 |

|                      | Zline2                                     | Line impedance between Nonlinear<br>load and inverter<br>(for experimental setup)                  | 0.1 Ω +1.8 mH                                                                 |

| Inner Loops (VCM)    | k <sub>p</sub> v                           | Proportional coefficients of voltage                                                               | 0.05                                                                          |

|                      | $k_{rV}$                                   | Resonant coefficients of voltage                                                                   | 10                                                                            |

|                      | $k_{pI}$                                   | Proportional coefficients of current                                                               | 33                                                                            |

|                      | $k_{rI}$                                   | Resonant coefficients of current                                                                   | 666                                                                           |

|                      | $\omega_{cV}$                              | cut-off frequency of voltage loop                                                                  | 2 Hz                                                                          |

|                      | ωcI                                        | cut-off frequency of control loop                                                                  | 2 Hz                                                                          |

| Droop<br>Control     | $k_{pP}$                                   | Active power droop term                                                                            | 0.0003                                                                        |

|                      | $k_{iP}$                                   | Active power droop integral term                                                                   | 0.0015                                                                        |

|                      | $k_{pQ}$                                   | Reactive power droop term                                                                          | 0.2 VAr/V                                                                     |

| Secondary<br>Control | $k_{\mathrm{pf}}$                          | Frequency proportional term                                                                        | 0.001                                                                         |

|                      | $k_{\rm if}$                               | Frequency integral term                                                                            | 1 s <sup>-1</sup>                                                             |

|                      | $k_{pE}$                                   | Voltage proportional term                                                                          | 0.001                                                                         |

|                      | $k_{iE}$                                   | Voltage integral term                                                                              | 0.5 s <sup>-1</sup>                                                           |

- Scenario 1: A three-phase ground fault with  $R_f$ =0.1  $\Omega$ . at the PCC. In this scenario a constant power load with 2 kW is connected to the VSI through a line with  $Z_{line1}$ =1.2  $\Omega$  +5.4 mH.

- Scenario 2: A three-phase ground with  $R_f=1$   $\Omega$  and the load same as Scenario 1.

- Scenario 3: A three phase ground fault with  $R_f=1~\Omega$ . In this scenario. In this scenario a nonlinear load including three-phase diode rectifier, inductor with 46  $\mu$ F, 8.4 mH, and resistance equaled to 500  $\Omega$  is connected to the VSI through a line with  $Z_{line1}=1.2~\Omega+5.4$  mH.

Regarding the proposed method, (6) is solved for *scenario1* and the best parameters are obtained by PSO algorithm:  $Threshold_a=1.6$  p.u.,  $Threshold_b=2.236$  p.u., Thresh

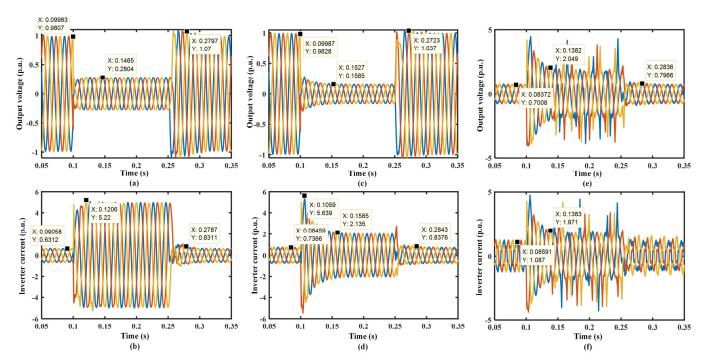

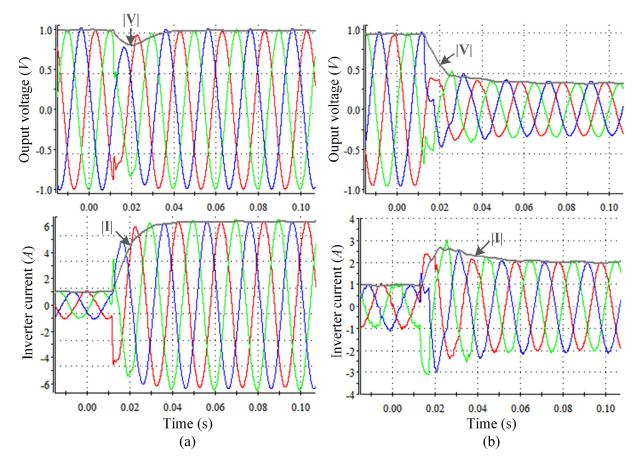

As it can be seen in Fig. 6(a) and (b), scenario 1 is applied at 0.1s and the voltage and current of the VSI are deviated from their nominal values to 0.2804 p.u. and 5.22 p.u, respectively. According to Fig. 6 (c) and (d), the VI-based FCL applies optimal value to limit the fault after 60 ms. However, for both scenario 2 and scenario 3, the VI-FCL has no ability to limit the output current (see Fig. 6 (e) and (f)). As it can be seen, for these two scenarios, the VI fluctuates between zero and its optimum value. This process continues until the fault is isolated.

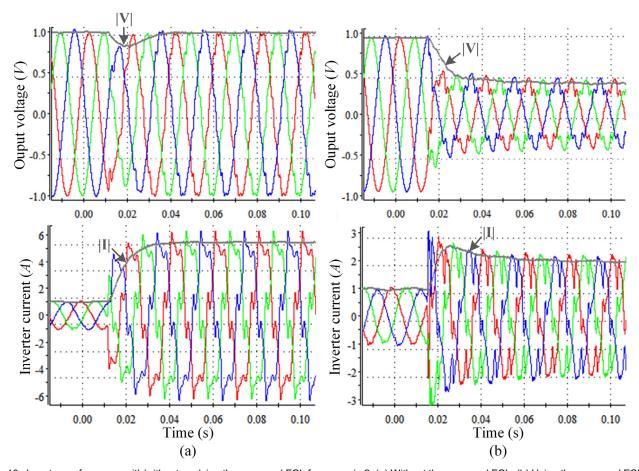

In the proposed approach, thanks to optimum values of Threshold<sub>a</sub> and Threshold<sub>b</sub>, the tuned PI controller adds proper additional negative values to voltage reference to limit the fault current to twice its nominal current in steady state for all considered Scenarios in around 40 ms (see Fig. 7(a),(b),(c)). The saturation block applied at the generated current reference will limit the first peak of fault current to 3.0 p.u.. Because of this saturation block, the VSI will not experience transient inrush current, and it would be safe against any harsh condition. In addition, the proper value of threshold, helps limiting fault current to its predifined value in the shortest possible time. Similarly for the *Scenario 2 and 3*, the proposed FCL confines the inverter current to twice its nominal value in 45 ms (See Fig. 7 (b) and (c)). It must be noted that since the proposed FCL is tuned for the worst condition, Scenario 1 (see Fig. 7 (f)), the proposed FCL will not cause any instability problem for other higher fault impedances.

### V. EXPERIMENTAL RESULTS

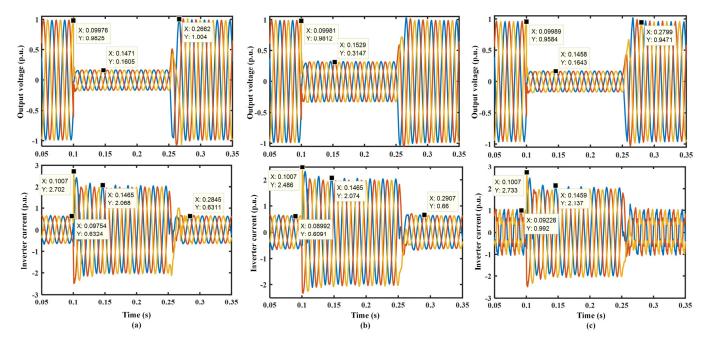

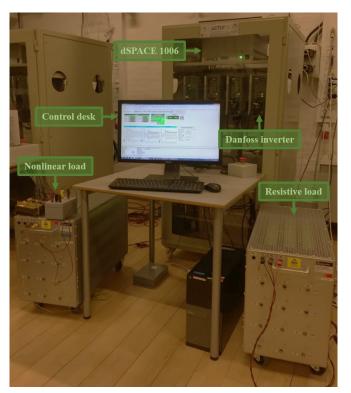

To further support the effectiveness of the proposed method, some experimental results are presented in this section. The experimental setup is shown in Fig. 8. The setup consists of a Danfoss inverter (2.2-kW inverter with an LCL filter), dSPACE1006 for control and monitoring, two resistive loads, and a nonlinear load.

Fig. 6. VCM-VSI performance under VI-based FCL: (a) V<sub>out</sub> without applying FCL, (b) I<sub>inverter</sub> without applying FCL, (c) V<sub>out</sub> for scenario 1 (d) I<sub>inverter</sub> for scenarios 2; (f) I<sub>inverter</sub> for scenarios 3.

Fig. 7. VCM-VSI performance under the preposed FCL: (a) Scenario 1 (b) Scenario 2, (c) Scenario 3.

The setup specifications are presented in Table I. Due to experimental limitations, instead of the fault scenarios, two overcurrent scenarios are emulated.

- Scenario 1: First, the inverter is connected to a load with  $R_{load2}$ =230  $\Omega$ . Then a load with  $R_{load3}$ =115  $\Omega$  is connected to the inverter.

- Scenario 2: First, the inverter is directly connected to the load with  $R_{load2}$ =230  $\Omega$ , then nonlinear load including three-phase diode rectifier, a capacitor with 235 $\mu$ F, an inductor with 0.084 mH, and a resistance equaled to 115  $\Omega$  is added to the inverter through a line with  $Z_{line2}$ =0.1  $\Omega$ +1.8 mH

These two scenarios result in overcurrent around 6 p.u., which are shown in Fig. 9 (a) and 10 (a). In the first scenario, while the amplitude of the inverter current exceeds the Threshold<sub>a</sub>, the proposed FCL starts to operate. As it can be seen in Fig. 9 (b), thanks to the saturation block, the first peak current of the inverter is fixed to 3 p.u. As a result, the inverter is kept safe from being damaged by transient inrush current. In addition, the inverter current approaches 2 p.u. in around 50 ms. Fig. 10 (b) shows the voltage and current of inverter for the second scenario where the inverter current has harmonics. As can be seen in this figure, the proposed FCL is kept safe from being damaged by limiting transient inrush current to 3 p.u. In addition, the inverter current approaches 2 p.u. in around 50 ms. These experimental results demonstrate that the proposed method is quite robust to the harmonics caused by the nonlinear loads.

Fig. 8. Experimental setup.

Fig. 9. Inverter performance with/without applying the proposed FCL for scenario 1: (a) Without the proposed FCL, (b) Using the proposed FCL.

Fig. 10. Inverter performance with/without applying the proposed FCL for scenario 2: (a) Without the proposed FCL, (b) Using the proposed FCL.

## VI. CONCLUSION

This paper proposes a modified secondary control with two objectives of keeping voltage and frequency to their nominal. values in the normal conditions as well as limiting the fault current in faulty conditions. To evaluate the efficiency of the proposed method, two different values of fault impedances as well as connecting the nonlinear load are considered. It is shown that the VI-FCL method [6] could lose ability to limit current in some cases. However, the modified secondary control is stable through the worst possible conditions and can limit current of the VCM-VSI in less than 50 ms.. Finally, the performance of the proposed FCL is validated by experimental results in two different conditions.

## REFERENCES

- [1] M. Nazari-heris, H. Nourmohamadi, M. Abapour, and M. Sabahi, "Multilevel Nonsuperconducting Fault Current Limiter: Analysis and Practical Feasibility," *IEEE trans. Power Electron.*, vol. 32, no. 8, pp. 6059–6068, 2017.

- [2] Z. Wei, Y. Xin, J. Jin, and Q. Li, "Optimized Design of Coils and Iron Cores for a Saturated Iron Core Superconducting Fault Current Limiter," *IEEE Trans. Appl. Supercond.*, vol. 26, no. 7, 2016.

- [3] T. Ghanbari and E. Farjah, "Development of an efficient solid-state fault current limiter for microgrid," *IEEE Trans. Power Deliv.*, vol.

27, no. 4, pp. 1829–1834, 2012.

- [4] W. P. Generation, A. R. Fereidouni, B. Vahidi, S. Member, and T. H. Mehr, "The Impact of Solid State Fault Current Limiter on Power Network With," *IEEE Trans. Smart Grid*, vol. 4, no. 2, pp. 1188–1196, 2013.

- [5] P. Godignon and X. Perpi, "A Survey of Wide Bandgap Power Semiconductor Devices," in in Proc. IEEE Workshop Wide Bandgap Power Devices Appl. (WiPDA), pp. 402–405.

- [6] X. Lu, J. Wang, J. M. Guerrero, and D. Zhao, "Virtual Impedance Based Fault Current Limiters for Inverter Dominated AC Microgrids," *Trans. Smart Grid*, no. to be published.

- [7] S. Beheshtaein, M. Savaghebi, J. M. Guerrero, R. Cuzner, and J. C. Vasquez, "A Secondary-Control Based Fault Current Limiter for Four-Wire Three Phase Inverter-Interfaced DGs," in 43rd Annual Conference of the IEEE Industrial Electronics Society, 2016, pp. 2363–2368.

- [8] A. Bidram, S. Member, and A. Davoudi, "Hierarchical structure of microgrids control system," *IEEE Trans. Smart Grid*, vol. 3, no. 4, pp. 1963–1976, 2012.

- [9] J. Wang, J. Liang, F. Gao, L. Zhang, and Z. Wang, "A Method to Improve the Dynamic Performance of Moving Average Filter-Based PLL," *IEEE trans. Power Electron.*, vol. 30, no. 10, pp. 5978–5990, 2015.

- [10] M. M. Mansour, S. F. Mekhamer, and N. E. S. El-Kharbawe, "A modified particle swarm optimizer for the coordination of directional overcurrent relays," *IEEE Trans. Power Deliv.*, vol. 22, no. 3, pp. 1400–1410, 2007.

Siavash Beheshtaein (S'12) was born in Shiraz, Iran. He received the B.Sc. and M.Sc. degrees in electrical engineering from Shiraz University, Iran, in 2012 and 2014, respectively. He is currently persuading the Ph.D. degree with Aalborg University. His research interests include microgrid protection, adaptive protection, solid-state transformer, and dc circuit breakers.

Mehdi Savaghebi (S'06-M'15-SM'15) was born in Karaj, Iran, in 1983. He received the B.Sc. degree from University of Tehran, Iran, in 2004 and the M.Sc. and Ph.D. degrees with highest honors from Iran University of Science and Technology, Tehran, Iran in 2006 and 2012, respectively, all in Electrical Engineering. In 2010, he was a visiting Ph.D. Student with the Department of Energy Technology, Aalborg

University, Aalborg, Denmark and with the Department of Automatic Control Systems and Computer Engineering, Technical University of Catalonia, Barcelona, Spain.

From 2014 to 2017, he was a Postdoc Fellow in the Department of Energy Technology, Aalborg University where he is currently an Associate Professor. His main research interests include distributed generation systems, microgrids, power quality, Internet of Things (IoT) and smart metering. Dr. Savaghebi has been a Guest Editor of Special Issue on Power Quality in Smart Grids, IEEE Transactions on Smart Grid. He is a member of Technical Committee of Renewable Energy Systems, IEEE Industrial Electronics Society and vice-chair of subcommittee on Smart Buildings, IEEE Power and Energy Society.

Robert Cuzner (M'90, SM'03) received the B.S.degree from Brigham Young University, Provo, UT, USA, and the M.S. and Ph.D. degrees from the University of Wisconsin–Madison, Madison, WI, USA, all in electrical and computer engineering. In 1990, his professional work began with Miller Electric Manufacturing Company, Appleton, WI, USA designing generators for engine-driven welders. He worked at Eaton Corporation,

Milwaukee, WI, USA, from 1993 to 2002 and then DRS Power and Control Technologies, Inc., from 2002 to 2014 as a designer of power conversion systems for Navy shipboard applications. He is presently Associate Professor in the Department of Electrical Engineering and Computer Science at the University of Wisconsin–Milwaukee. Dr. Cuzner has over 25 years of experience working in power generation, power conversion, and drive system controls and packaging for both Navy and industrial applications. He has authored over 50 publications, including IEEE journal and conference papers and tutorials, and is the holder of three U.S. patents. His interests include microgrid protection, distributed generation, power electronics for power distribution and drive systems, low- and medium-voltage power conversion system design, high power-density packaging of power electronics, and electric machine design.

Saeed Golestan (M'11-SM'15) received the B.Sc. degree in electrical engineering from Shahid Chamran University of Ahvaz, Iran, in 2006, and the M.Sc. degree in electrical engineering from the Amirkabir University of Technology, Tehran, Iran, in 2009.

He is currently working towards the Ph.D. degree at the Department of Energy Technology, Aalborg University, Denmark. His research interests include phase-locked loop and

nonlinear filtering techniques for power engineering applications, power quality measurement and improvement, estimation of power system parameters, and microgrid.

Josep M. Guerrero (S'01-M'04-SM'08-F'15) received the B.S. degree in telecommunications engineering, the M.S. degree in electronics engineering, and the Ph.D. degree in power electronics from the Technical University of Catalonia, Barcelona, in 1997, 2000 and 2003, respectively. Since 2011, he has been a Full Professor with the Department of Energy Technology, Aalborg University, Denmark, where he is responsible for the Microgrid Research

Program (www.microgrids.et.aau.dk). From 2012 he is a guest Professor at the Chinese Academy of Science and the Nanjing University of Aeronautics and Astronautics; from 2014 he is chair Professor in Shandong University; from 2015 he is a distinguished guest Professor in Hunan University; and from 2016 he is a visiting professor fellow at Aston University, UK, and a guest Professor at the Nanjing University of Posts and Telecommunications.

His research interests is oriented to different microgrid aspects, including power electronics, distributed energy-storage systems, hierarchical and cooperative control, energy management systems, smart metering and the internet of things for AC/DC microgrid clusters and islanded minigrids; recently specially focused on maritime microgrids for electrical ships, vessels, ferries and seaports. Prof. Guerrero is an Associate Editor for a number of IEEE TRANSACTIONS. He received the best paper award of the IEEE Transactions on Energy Conversion for the period 2014-2015, and the best paper prize of Power Electronics in 2016. In 2014, 2015, 2016, and 2017 he was awarded by Thomson Reuters as Highly Cited Researcher, and in 2015 he was elevated as IEEE Fellow for his contributions on "distributed power systems and microgrids."