#### **Aalborg Universitet**

#### Modeling, Analyzing, and Designing Advanced Synchronization Techniques for Power Converters

| Golestan, | Saeed |

|-----------|-------|

|-----------|-------|

Publication date: 2018

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Golestan, S. (2018). *Modeling, Analyzing, and Designing Advanced Synchronization Techniques for Power Converters*. Aalborg Universitetsforlag. Ph.d.-serien for Det Ingeniør- og Naturvidenskabelige Fakultet, Aalborg Universitet

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research. ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ?

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

## MODELING, ANALYZING, AND DESIGNING ADVANCED SYNCHRONIZATION TECHNIQUES FOR POWER CONVERTERS

BY SAEED GOLESTAN

**DISSERTATION SUBMITTED 2018**

# MODELING, ANALYZING, AND DESIGNING ADVANCED SYNCHRONIZATION TECHNIQUES FOR POWER CONVERTERS

#### PH.D. DISSERTATION

Saeed Golestan

Department of Energy Technology Aalborg University, Denmark

Dissertation submitted March 20, 2018

Dissertation submitted: March 20, 2018

PhD supervisor: Prof. Josep M. Guerrero

Aalborg University

Assistant PhD supervisor: Associate Prof. Juan C. Vasquez

Aalborg University

PhD committee: Associate Professor Tamas Kerekes (chairman)

**Aalborg University**

Professor Nimrod Vazquez Instituto Tecnologico de Celaya

Professor Francisco Neves

Federal University of Pernambuco

PhD Series: Faculty of Engineering and Science, Aalborg University

Department: Department of Energy Technology

ISSN (online): 2446-1636

ISBN (online): 978-87-7210-162-0

Published by: Aalborg University Press Langagervej 2

DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Saeed Golestan

Printed in Denmark by Rosendahls, 2018

#### CV

Saeed Golestan received the B.Sc. degree in electrical engineering from Shahid Chamran University of Ahvaz, Iran, in 2006, and the M.Sc. degree in electrical engineering from the Amirkabir University of Technology, Tehran, Iran, in 2009.

He is currently working towards the Ph.D. degree in the Department of Energy Technology, Aalborg University, Denmark. His research interests include phase-locked loop and nonlinear filtering techniques for power engineering applications and control of power converters.

#### **ENGLISH SUMMARY**

Synchronization, in simple words, can be defined as the procedure of coordinating a generator (here, a power converter with its DC source) and the main grid so that they are able to effectively work in parallel. This procedure involves extracting the grid voltage parameters (i.e., phase, frequency, and amplitude). This task is often carried out using phase-locked loops (PLLs) and frequency-locked loops (FLLs), which are closed-loop synchronization techniques, or in an open-loop manner using different filtering techniques.

The main challenge that all synchronization techniques regardless of their nature are facing with is growing power quality issues (i.e., the presence of harmonics, DC offset, imbalance, voltage sag and swell, etc.) in the grid voltage. These disturbances, which are mainly attributable to the high penetration of distributed generation systems and nonlinear power electronics-based loads in the distribution system, adversely affect the performance of synchronization technique. To deal with this challenge, some research efforts have been made in the literature. The main objective of this dissertation is to provide an analysis of these efforts and make further contributions to the field by designing more advanced synchronization techniques. These contributions cover the major categories of synchronization techniques, i.e., PLLs, FLLs, and open-loop techniques, as explained below.

The main contributions to the PLL field are as follows. First, the small-signal modeling of a large number of advanced single-phase and three-phase PLLs is conducted. These models make the stability assessment, performance analysis, and tuning the control parameters of these PLLs straightforward and effective. Second, some advanced PLLs are designed. Roughly speaking, these PLLs improve the speed/accuracy tradeoff of the state-of-the-art PLLs while maintaining simplicity.

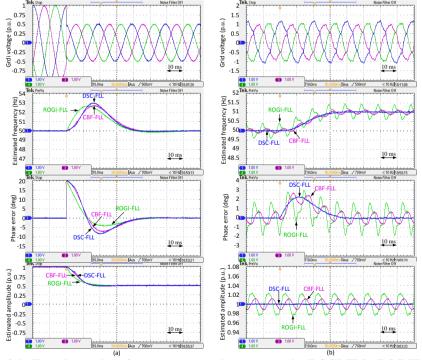

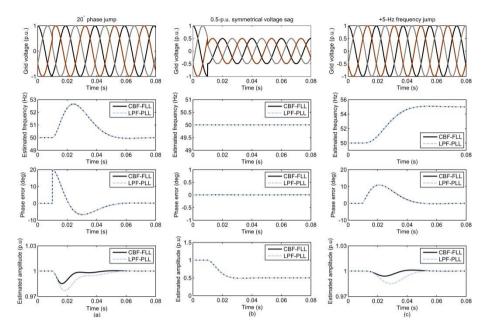

Regarding FLLs, the following contributions are made in this thesis. First, it is demonstrated how the small-signal modeling of typical and advanced single-phase and three-phase FLLs should be conducted. Thanks to these models, the FLLs tuning and stability analysis can now be easily and effectively carried out. Second, a performance comparison among some advanced FLLs is conducted to better understand their properties. Third, the concept of inloop filter for designing more effective FLLs is introduced. Fourth, it is proved that FLLs are mathematically equivalent to PLLs. It means that FLLs and PLL are practically the same control systems that are implemented in different reference frames. Finally, through establishing a resemblance between the average model of a single-phase grid-connected converter with a proportional-resonant (PR) current controller and a typical single-phase FLL, it is demonstrated that the frequency estimation capability can be easily added to the resonant term of the PR controller. In this way, the need

for a separate synchronization unit (like a PLL) is removed, which leads to a simpler and more compact structure.

Some contributions to open-loop synchronization (OLS) techniques are also made in this dissertation. First, a true OLS technique for three-phase systems is designed, which does not use any feedback in its structure and works effectively under frequency drifts without requiring any knowledge of the grid frequency. This synchronization technique benefits from a low computational burden and offers a fast dynamic response and a high customizability to deal with different grid scenarios. Second, a moving average filter-based OLS technique for single-phase applications is designed. This synchronization method offers interesting advantages such as the zero average phase/frequency/amplitude error under nominal/offnominal frequencies, a complete DC offset rejection ability, a complete (effective) filtering of the grid voltage harmonics under a nominal (off-nominal) frequency, and a fast dynamic response.

**Keywords:** Amplitude extraction, filters, frequency estimation, frequency-locked loops, grid-connected converters, grid voltage imbalance, harmonic distortion, open-loop techniques, phase detection, phase-locked loops, power electronics, quadrature signal, single-phase systems, synchronization, three-phase systems.

#### **DANSK RESUME**

Synkronisering, i enkle ord, kan defineres som proceduren for at koordinere en generator (her en power converter med dens DC-kilde) og el-nettet, så de effektivt kan arbejde parallelt. Denne fremgangsmåde involverer ekstraktion af spændingsparametrene (dvs. fase, frekvens og amplitude). Denne opgave udføres ofte ved hjælp af faselåste sløjfer (Phase Lock Loop - PLL) og frekvenslåsede sløjfer (Frequency Lock Loop - FLL), som er synkroniseringsteknikker med closedloop eller på en open-loop måde ved anvendelse af forskellige filtreringsteknikker.

Den største udfordring, at alle synkroniseringsteknikker uanset deres natur står overfor, er ved at voksende problemer med strømkvaliteten (dvs. harmoniske komponenter, DC-offset, ubalance, svingende spænding osv.) i net spændingen. Disse forstyrrelser, som hovedsageligt kan henføres til den høje penetration af generationssystemer og ikke-lineære strømelektronikbaserede belastninger i distributionssystemet, påvirker synkroniserings-teknologiens ydeevne negativt. For at klare denne udfordring er der gjort nogle forskningsindsatser i litteraturen. Hovedformålet med denne afhandling er at levere en analyse af disse indsatser og yde yderligere bidrag til feltet ved at designe mere avancerede synkroniseringsteknikker. Disse bidrag dækker alle kategorier synkroniseringsteknikker, dvs. PLL'er, FLL'er og open-loop teknikker, som forklaret nedenfor.

De vigtigste bidrag til PLL-feltet er som følger. For det første udføres små signalmodellering af et stort antal avancerede enfasede og trefasede PLL'er. Disse modeller gør stabilitetsvurderingen, præstationsanalysen og justering af kontrolparametrene for disse PLL'er ligetil og effektiv. For det andet er nogle avancerede PLL'er også designet. Tilnærmelsesvis forbedrer disse PLL'er hastigheden / nøjagtigheden af de state-of-the-art PLL'er, samtidig med at der opretholdes enkelhed.

Med hensyn til FLL'er, er følgende bidrag lavet i denne afhandling. For det første er det demonstreret, hvordan små signalmodellering af typiske og avancerede enfaseog trefasede FLL'er skal udføres. Takket være disse modeller kan FLLs tuning og

stabilitetsanalyse nu nemt og effektivt udføres. For det andet udføres en

sammenligning blandt nogle avancerede FLL'er for at bedre forstå deres egenskaber.

For det tredje indføres begrebet "in-loop filter" til design af mere effektive FLL'er.

For det fjerde er det bevist, at FLL'er er matematisk ækvivalente med PLL'er. Det

betyder, at FLL og PLL er praktisk de samme styresystemer, der implementeres i

forskellige referencerammer. Endelig er det demonstreret at den gennemsnitlige

model af en enkeltfaset nettilsluttet frekvensomformer med en "proportionel

resonant" (PR) strømstyring og en typisk enfaset FLL, at frekvensberegningsevnen

let kan tilføjes til PR-regulatorens resonante del. På denne måde fjernes behovet for

en separat synkroniseringsenhed (som en PLL), hvilket fører til et enkelt og mere kompakt struktur.

Nogle bidrag til open-loop synkronisering (OLS) teknikker er også lavet i denne afhandling. For det første er der udviklet en ægte OLS-teknik til trefasesystemer, som ikke bruger nogen feedback i sin struktur og fungerer effektivt under frekvensdrift uden at kræve kendskab ti1 netfrekvensen. Denne synkroniseringsteknik har fordele ved en lav beregningsbyrde og giver et hurtigt dynamisk respons og en høj tilpassbarhed til at håndtere forskellige gridscenarier. For det andet er der udviklet en bevægende gennemsnitlig filterbaseret OLS-teknik til enkeltfaseprogrammer. Denne synkroniseringsmetode giver spændende fordele, såsom nul-middelfase / frekvens / amplitudefejl under nominelle / off-nominelle frekvenser, en komplet DC-offset afvisningsevne, en fuldstændig (effektiv) filtrering af harmoniske komponenter under en nominel (off-nominel) frekvens og et hurtigt dvnamisk respons.

Nøgleord: Amplitude-ekstraktion, filtre, frekvens estimation, frekvenslåsede sløjfer, netforbundne omformere, nettospændingsbalance, harmonisk forvrængning, åbenløbsteknikker, faseopdagelse, faselåste sløjfer, strømelektronik, kvadratur signal, enkeltfasesystemer, synkronisering, trefasesystemer.

#### THESIS DETAIL AND PUBLICATIONS

Thesis Title: Modeling, Analyzing, and Designing Advanced

Synchronization Techniques for Power Converters

Ph.D. Student: Saeed Golestan

Supervisor: Prof. Josep M. Guerrero, Aalborg University

Co-supervisor: Associate Prof. Juan C. Vasquez, Aalborg University

#### **Publications**

- S. Golestan, J. M. Guerrero, and J. C. Vasquez, "Three-phase PLLs: A review of recent advances," *IEEE Transactions on Power Electronics*, vol. 32, no. 3, pp. 1894-1907, Mar. 2017.

- S. Golestan, J. M. Guerrero, and J. C. Vasquez, "Single-phase PLLs: A review of recent advances," *IEEE Transactions on Power Electronics*, vol. 32, no. 12, pp. 9013-9030, Dec. 2017.

- S. Golestan, J. M. Guerrero, A. Vidal, A. G. Yepes, J. Doval-Gandoy, and F. D. Freijedo, "Small-signal modeling, stability analysis and design optimization of single-phase delay-based PLLs," *IEEE Transactions on Power Electronics*, vol. 31, no. 5, pp. 3517-3527, May 2016.

- S. Golestan, J. M. Guerrero, J. C. Vasquez, A. M. Abusorrah, and Y. Al-Turki "Research on variable-length transfer delay and delayed signal cancellation based PLLs," *IEEE Transactions on Power Electronics*, (accepted for the publication).

- S. Golestan, J. M. Guerrero, A. M. Abusorrah, M. M. Al-Hindawi, and Y. Al-Turki "An adaptive quadrature signal generation based single-phase phase-locked loop for grid-connected applications," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 4, pp. 2848-2854, Apr. 2017.

- S. Golestan, J. M. Guerrero, and J. C. Vasquez, "Steady-state linear Kalman filter-based PLLs: A second look", *IEEE Transactions on Industrial Electronics*, (accepted for the publication).

- S. Golestan, J. M. Guerrero, and J. C. Vasquez, "DC-offset rejection in phase-locked loops: A novel approach," *IEEE Transactions on Industrial Electronics*, vol. 63, no. 8, pp. 4942-4946, Aug. 2016.

- S. Golestan, J. M. Guerrero, A. Vidal, A. G. Yepes, and J. Doval-Gandoy, "PLL with MAF based prefiltering stage: Small-signal modeling and performance enhancement," *IEEE Transactions on Power Electronics*, vol. 31, no. 6, pp. 4013- 4019, Jun. 2016.

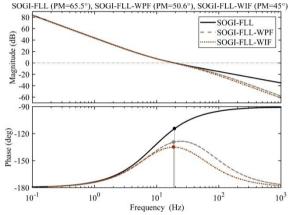

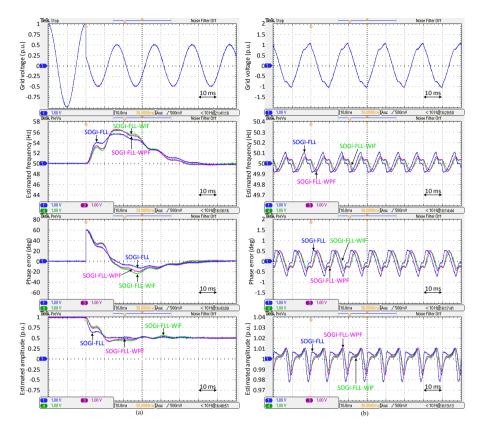

- S. Golestan, J. M. Guerrero, J. C. Vasquez, A. M. Abusorrah, and Y. Al-Turki "Modeling, tuning, and performance comparison of advanced second-order generalized integrator-based FLLs", *IEEE Transactions on Power Electronics*, (accepted for the publication).

- S. Golestan, J. M. Guerrero, J. C. Vasquez, A. M. Abusorrah, and Y. Al-Turki "A study on three-phase FLLs," *IEEE Transactions on Power Electronics*, (under review).

- S. Golestan, E. Ebrahimzadeh, J. M. Guerrero, and J. C. Vasquez, "An adaptive resonant regulator for single-phase grid-tied VSCs," *IEEE Transactions on Power Electronics*, vol. 33, no. 3, pp. 1867-1873, Mar. 2018.

- S. Golestan, J. M. Guerrero, and J. C. Vasquez, "An open-loop grid synchronization approach for single-phase applications," *IEEE Transactions on Power Electronics*, vol. 33, no. 7, pp. 5548-5555, July 2018.

- S. Golestan, A. Vidal, A. G. Yepes, J. M. Guerrero, J. C. Vasquez, and J. Doval-Gandoy, "A true open-loop synchronization technique," *IEEE Transactions on Industrial Informatics*, vol. 12, no. 3, pp. 1093-1103, Jun. 2016.

This present report combined with the above listed scientific papers has been submitted for assessment in partial fulfillment of the Ph.D. degree. The thesis is based on the submitted or published scientific papers which are listed above. Parts of the papers are used directly or indirectly in the extended summary of the thesis. The scientific papers are not included in this version due to copyright issues. Detailed publication information is provided above and the interested reader is referred to the original published papers. As part of the assessment, co-author statements have been made available to the assessment committee and are also available at the Faculty of Engineering and Science, Aalborg University

#### **PREFACE**

This thesis, which is a collection of papers and submitted as a partial fulfillment of the requirements for the Danish Ph.D. degree, has been conducted under the supervision of Prof. Josep M. Guerrero and Prof. Juan. C. Vasquez at the Department of Energy Technology, Aalborg University.

I would like to express my gratitude to my advisor and co-advisor, Prof. Josep M. Guerrero and Prof. Juan. C. Vasquez, for their support and friendship during the course of this work. I would also like to thank my family for their encouragement, support, and patience.

### **TABLE OF CONTENTS**

| Chapter 1. Introduction                                                   | 19 |

|---------------------------------------------------------------------------|----|

| 1.1. Background and Motivation                                            |    |

| 1.1.1. Phase-Locked Loops (PLLs)                                          |    |

| 1.1.2. Frequency-Locked Loops (FLLs)                                      |    |

| 1.1.3. Open-Loop Synchronization (OLS) Techniques                         |    |

| 1.2. Thesis Objectives                                                    |    |

| 1.3. Thesis Outline                                                       |    |

| Chapter 2. Modeling, Analyzing, and Designing PLLs                        | 42 |

| 2.1. Transfer Delay-Based PLLs (TD-PLLs)                                  |    |

| 2.1.1. Standard TD-PLL 42                                                 |    |

| 2.1.2. Non-frequency-dependent TD-PLL (NTD-PLL)                           |    |

| 2.1.3. Variable-Length TD-PLL (VLTD-PLL)                                  |    |

| 2.1.4. Adaptive TD-PLL (ATD-PLL)                                          |    |

| 2.1.5. Delayed Signal Cancelation (DSC) Based PLLs                        |    |

| 2.2. Steady-State Linear Kalman Filter (SSLKF) Based PLLs                 | ı  |

| 2.2.1. Two-State SSLKF-PLL                                                |    |

| 2.2.2. Three-State SSLKF-PLL                                              |    |

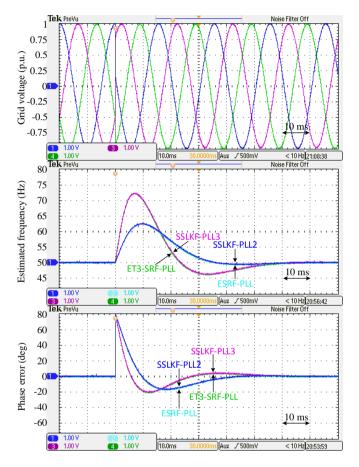

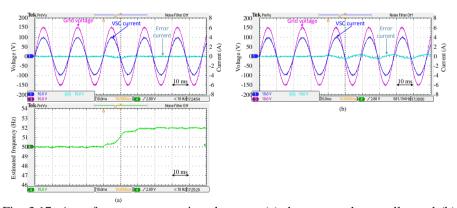

| 2.2.3. Experimental Results                                               |    |

| 2.3. Designing An Approach for DC-offset Rejection in Three-phase PLLs 64 |    |

| 2.3.1. Design Procedure                                                   |    |

| 2.3.2. Modeling, Tuning, and Stability Analysis                           |    |

| 2.3.3. Numerical Results                                                  |    |

| 2.4. PLL with A MAF Based Prefiltering Stage                              |    |

| 2.4.1. Eliminating the Need for A Parallel frequency Detector             |    |

| 2.4.2. Modeling and Tuning                                                | ı  |

| 2.4.3. Experimental Results                                               |    |

| Chapter 3. Modeling, Analyzing, and Designing FLLs                        | 74 |

| 3.1. Single-Phase FLLs                                                    |    |

| 3.1.1. Modeling                                                           |    |

| 3.1.2. Tuning                                     |     |

|---------------------------------------------------|-----|

| 3.1.3. Performance Comparison                     |     |

| 3.2. Three-Phase FLLs 80                          |     |

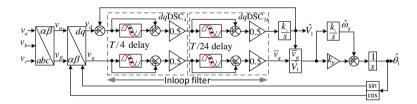

| 3.2.1. Concept of Inloop Filter                   |     |

| 3.2.2. Relation Between PLLs and FLLs             |     |

| 3.3. Designing an Adaptive Resonant Regulator     |     |

| 3.3.1. Design                                     |     |

| 3.3.2. Modeling and Tuning                        |     |

| 3.3.3. Experimental Results                       |     |

| Chapter 4. Analyzing and Designing OLS Techniques | 91  |

| 4.1. Designing a Single-phase OLS Technique       |     |

| 4.1.1. Design Procedure                           |     |

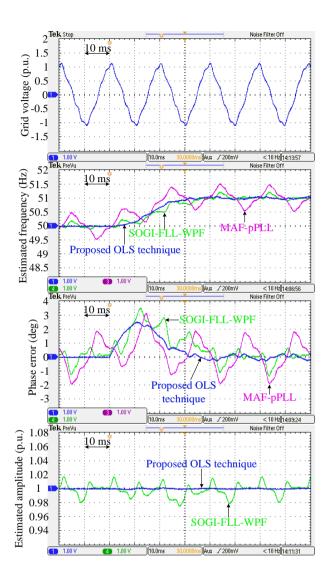

| 4.1.2. Experimental Results                       |     |

| 4.2. Designing a Three-phase OLS Technique        |     |

| 4.2.1. Design Procedure                           |     |

| 4.2.2. Experimental Results                       |     |

| Chapter 5. Concluding Remarks                     | 103 |

| Literature list                                   | 107 |

| Appendix. Papers                                  | 116 |

#### **CHAPTER 1. INTRODUCTION**

#### 1.1. BACKGROUND AND MOTIVATION

In recent years, with growing awareness regarding the environmental damages of the generation of electrical energy using fossil fuels, which around 80% of the world electrical energy generation is based on them [1], raising energy demand, and technological advances in power electronics and digital signal processors, producing the electrical energy using renewable sources, particularly photovoltaic and wind, has received a considerable attention. This fact can be supported by the energy roadmaps planned by industrial and developing countries. For example, according to Denmark's roadmap, this country should produce around 50% of its electrical energy needs using wind energy by the year 2025 [2].

The renewable energy-based generation systems often need an interface for connecting to the main grid and/or local loads because their output voltage may be a DC or a variable-frequency (or high-frequency) AC signal. This interface is often a power electronic converter and is responsible for extracting the highest possible power from the renewable energy source and deliver a high-quality power to the grid and/or local loads [3]. These converters may have different topologies depending on the application in hand and performance requirements. The most popular option is probably a pulse-width modulated voltage source converter (VSC).

A highly important unit in the control of power converters is the synchronization part. This unit is responsible to perform a series of action so that the power converter and the main grid are able to safely and effectively work in parallel [4]-[6]. The information provided by the synchronization unit may also be used for different monitoring and protection purposes, such as islanding detection [7]-[8], fault detection [9], [10], etc.

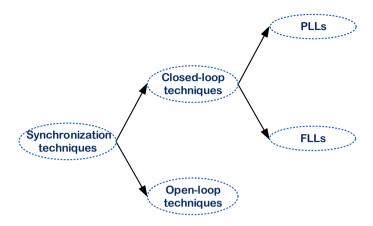

The synchronization techniques in power converters may be broadly categorized into open-loop and closed-loop approaches [11], [12]. The closed-loop synchronization (CLS) methods are those approaches whose implementation involve feeding back one or more signals. The frequency-locked loops (FLLs) and phase-locked loops (PLLs) are two main categories of the CLS techniques. The open-loop synchronization (OLS) methods, nevertheless, are free from any feedback signals in their structures. The diagram illustrated in Fig. 1.1 illustrates this classification of synchronization techniques. These synchronization techniques will be discussed in more details later.

Fig. 1.1: A classification of synchronization techniques.

Roughly speaking, all synchronization techniques, regardless of their structural differences, work satisfactorily under an ideal condition, in which the grid voltage is free from any noise. This situation, however, almost never happens in practice because of ever-increasing power quality issues (i.e., the presence of harmonics, interharmonics, DC offset, asymmetrical voltage sags, etc.) in the power systems [13]. These power quality problems may be caused by different factors. For example, the DC component may appear in the grid voltage signal because of power system faults, geomagnetic phenomena, half-wave rectification, cycloconverters, and the direct current injection by distributed generation systems, particularly PV inverters, into the grid [14]-[17]. And the grid voltage harmonics and interharmonics are mainly attributable to the nonlinear loads, particularly power electronics-based equipment, which their penetration in the power system is continuously increasing [18]-[20].

The power quality issues adversely affect the performance of synchronization techniques. To be more exact, they cause oscillatory and offset errors in the estimated quantities (phase, frequency, and amplitude) by the synchronization units [5], [6], [21], [22]. To deal with this problem, some efforts for designing more efficient synchronization methods have been made recently. Roughly speaking, these efforts often result in complicated structures that suffer from one or more of the following shortcomings: 1) high computational burden, 2) implementation complexity, 3) difficulty of modeling and stability analysis, 4) inefficiency under large frequency drifts. In what follows, this fact is discussed with more details for different categories of synchronization techniques. Before that, a general description of these categories is presented.

#### 1.1.1. PHASE-LOCKED LOOPS (PLLS)

Focusing on power and energy applications, a PLL is a feedback control system with a nonlinear nature that is implemented in the synchronous reference frame and synchronizes its output signal with the fundamental component of the grid voltage, which is its input signal [5], [6]. In addition to synchronizing power converters, PLLs are widely employed for different applications such as islanding detection [7]-[8], fault detection [9]-[10], measurement of synchrophasors [23], [24], harmonics extraction [25], [26], computation of power quality factors [27], [28], etc.

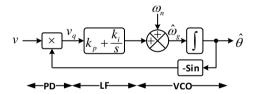

Regardless of the application in hand, three parts are found in almost all PLLs [5], [6], [29], [30]. These elements are the phase detector (PD), which is mainly responsible for generating a signal containing the phase error information, the loop filter (LF), also known as the loop controller, which drives the phase error signal to zero, and voltage-controlled oscillator (VCO), which produces a synchronized unit vector in its output [5], [6], [29], [30].

#### 1.1.1.1 Three-phase PLLs

#### 1.1.1.1.1 Standard Three-phase PLL

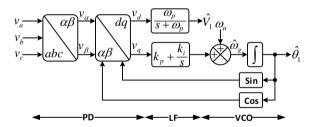

Fig. 1.2 illustrates a standard three-phase PLL, which is called the conventional SRF-PLL [5], [21], [22]. As the conventional SRF-PLL is the basic structure for implementing almost all advanced PLLs, a brief description of its operating principle and properties is first presented.

Fig. 1.2: Conventional SRF-PLL.

In the conventional SRF-PLL, Clarke's and Park's transformations are applied to the grid voltage signals for transferring them to the synchronous (dq) reference frame. The resultant dq-axis signals contain the phase error and amplitude information. The signal containing the phase error, here  $v_q$ , is passed through the LF, which is a proportional-integral (PI) regulator. The cooperation of this regulator and the VCO guarantees a zero average phase tracking error in the nominal and off-nominal frequencies in the steady state. Notice that the unit vector generated by the VCO [i.e.,  $\sin(\hat{\theta})$  and  $\cos(\hat{\theta})$ ] is used by the PD (the Park's transformation) for generating

the phase error and amplitude information. Notice also that the PI controller output and the *d*-axis signals are estimations of the grid voltage frequency and amplitude, respectively. The *d*-axis signal is fed to a low-pass filter (LPF) to reject/attenuate possible noise/disturbances and accurately estimate the grid voltage amplitude.

Assume that the three-phase input voltages of the SRF-PLL are as follows

$$v_{a}(t) = V_{1}\cos(\theta_{1}) + \sum_{h=-\infty}^{+\infty} V_{h}\cos(\theta_{h})$$

$$v_{b}(t) = V_{1}\cos(\theta_{1} - 2\pi/3) + \sum_{h=-\infty}^{+\infty} V_{h}\cos(\theta_{h} - 2\pi/3)$$

$$v_{c}(t) = V_{1}\cos(\theta_{1} + 2\pi/3) + \sum_{h=-\infty}^{+\infty} V_{h}\cos(\theta_{h} + 2\pi/3)$$

$$(1.1)$$

where  $V_h$  is the amplitude of h-order harmonic component in the PLL input and  $\theta_h$  is its phase angle. In this case, the dq-axis signals can be expressed as

$$v_{d}(t) = V_{1} \overbrace{\cos(\theta_{1} - \hat{\theta}_{1})}^{\leq 1} + \underbrace{\sum_{h=-\infty}^{+\infty} V_{h} \cos(\theta_{h} - \hat{\theta}_{1})}_{h \neq 1} \approx V_{1} + D_{d}(t)$$

$$v_{q}(t) = V_{1} \underbrace{\sin(\theta_{1} - \hat{\theta}_{1})}_{\approx (\theta_{1} - \hat{\theta}_{1})} + \underbrace{\sum_{h=-\infty}^{+\infty} V_{h} \sin(\theta_{h} - \hat{\theta}_{1})}_{h \neq 1} \approx V_{1}(\theta_{1} - \hat{\theta}_{1}) + D_{q}(t).$$

$$(1.2)$$

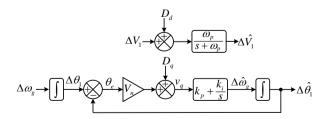

Using (1.2) and the block diagram of the SRF-PLL (see Fig. 1.2) and by defining  $\hat{\theta}_1 = \theta_n + \Delta \hat{\theta}_1$ ,  $\theta_1 = \theta_n + \Delta \theta_1$ ,  $\hat{\omega}_g = \omega_n + \Delta \hat{\omega}_g$ ,  $\omega_g = \omega_n + \Delta \omega_g$ ,  $\hat{V}_1 = V_n + \Delta \hat{V}_1$ , and  $V_1 = V_n + \Delta V_1$  ( $\theta_n = \int \omega_n dt$ ,  $\omega_n$  and  $V_n$  are the nominal angular frequency and amplitude, respectively, and  $\Delta$  refers to a small perturbation), the SRF-PLL linearized model can be developed as depicted in Fig. 1.3.

Fig. 1.3: SRF-PLL linearized model.

According to this model, the SRF-PLL open-loop and closed-loop transfer functions may be determined as follows

$$\Delta \hat{\theta}_1(s) = \frac{V_n(k_p s + k_i)}{s^2} \theta_e(s) \tag{1.3}$$

$$\Delta \hat{\theta}_{1}(s) = \frac{V_{n}(k_{p}s + k_{i})}{s^{2} + V_{n}k_{p}s + V_{n}k_{i}} \Delta \theta_{1}(s) + \frac{(k_{p}s + k_{i})}{s^{2} + V_{n}k_{p}s + V_{n}k_{i}} D_{q}(s). \tag{1.4}$$

$$\Delta \hat{\omega}_{g}(s) = \frac{V_{n}(k_{p}s + k_{i})}{s^{2} + V_{n}k_{p}s + V_{n}k_{i}} \Delta \omega_{g}(s) + \frac{s(k_{p}s + k_{i})}{s^{2} + V_{n}k_{p}s + V_{n}k_{i}} D_{q}(s).$$

(1.5)

$$\Delta \hat{V}_{1}(s) = \frac{\omega_{p}}{s + \omega_{p}} \Delta V_{1}(s) + \frac{\omega_{p}}{s + \omega_{p}} D_{d}(s). \tag{1.6}$$

Notice that in determining the open-loop transfer function (1.3), the presence of the disturbance input  $D_a$  has been neglected.

The transfer functions (1.3)-(1.6) provide valuable information about the SRF-PLL characteristics, which is summarized as follows [5].

- According to (1.3), the open-loop transfer function, which relates the phase error signal to the estimated phase angle, has two poles at the origin. It means that, from the phase angle estimation point of view, the SRF-PLL is a control system of type II [5], [21]. Consequently, it can follow a phase jump and a phase ramp (which corresponds to a frequency jump) with a zero error in the steady state. It, nevertheless, may not be able to follow a parabolic phase input (which corresponds to a frequency ramping change) with a zero error. The phase error during the frequency ramping change can be reduced by increasing the PLL bandwidth. It, nevertheless, degrades the SRF-PLL noise immunity.

- According to (1.3), the SRF-PLL loop gain depends on the grid voltage amplitude. Consequently, any change in the amplitude of the grid voltage (for example, because of a fault), changes the SRF-PLL loop gain and, hence, its dynamic and stability characteristics [5], [31], [32].

- According to (1.4)-(1.6), the phase angle, frequency, and amplitude estimated by the SRF-PLL suffer from the disturbance inputs  $D_q$  and  $D_d$ . These signals, as expressed in (1.2), are resulting from the grid voltage disturbances. Notice that the grid voltage DC offset and fundamental-frequency negative sequence (FFNS) component appear as the fundamental-frequency and double-frequency components in  $D_q$  and  $D_d$ , respectively, and a harmonic of order h appears as a harmonic of order

- h-1. Therefore, the presence of the DC offset, FFNS component, and an h-order harmonic component in the SRF-PLL input, respectively, cause the fundamental-frequency, double-frequency, and h-1-order harmonic frequency ripples on the estimated phase, frequency, and amplitude.

- The SRF-PLL has a very limited capability to mitigate the grid voltage disturbances. This is particularly true when the DC offset and FFNS component exist in the SRF-PLL input because, as mentioned before, they appear as fundamental-frequency and double-frequency disturbances inside the SRF-PLL control loop. Notice that these are low-order disturbances and even a narrow-bandwidth SRF-PLL cannot effectively mitigate them. Notice also that narrowing the SRF-PLL bandwidth significantly degrades its dynamic response.

These drawbacks and shortcomings of the SRF-PLL have been the main motivation behind recent efforts for designing more efficient PLLs in three-phase applications [5]. In what follows, these efforts are very briefly analyzed.

#### 1.1.1.1.2 Three-phase PLLs with Frequency Ramp Tracking Capability

As mentioned before, the inability in tracking frequency ramps with a zero phase error in the steady-state is a drawback of the conventional SRF-PLL. This may be a serious problem in some applications, such as the synchrophasor measurement [23], speed control of electrical motors [33], synchronization and control of converters in more electric aircraft [34], etc. To tackle this issue, a type-III PLL may be used. The type-III PLLs can be implemented in several ways [5]. A simple approach is replacing the PI controller in the conventional SRF-PLL by the following controller [35]

$$LF(s) = k_1 + \frac{k_2}{s} + \frac{k_3}{s^2}$$

(1.7)

in which  $k_1$ ,  $k_2$ , and  $k_3$  are the control parameters. Using this controller causes three open-loop poles at the phase open-loop transfer function of the PLL and, therefore, ensures a zero phase error in response to frequency ramps. The problem is that using (1.7) as the SRF-PLL LF results in a negative gain margin in dB, which may cause instability when the loop gain reduces [35]. This situation may happen under voltage sags and faults. Notice that the PLL loop gain depends on the amplitude of the grid voltage fundamental component, which drops under voltage sags and faults.

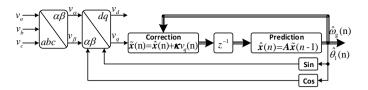

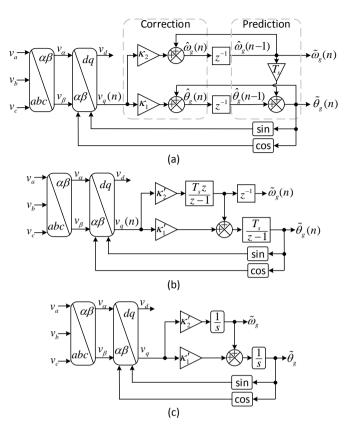

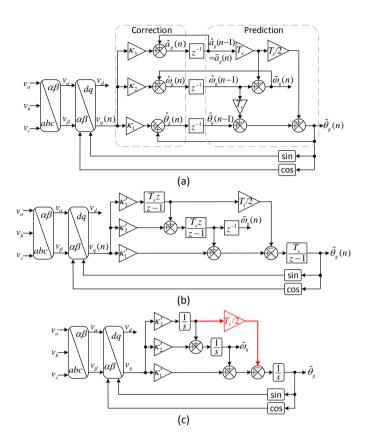

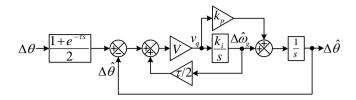

An alternative approach is using the steady-state linear Kalman filter-based PLL (SSLKF-PLL) [8], [34]. In this PLL, a three-state physical model for describing the grid voltage dynamics is considered, and the grid voltage parameters are estimated using a prediction/correction filter. Fig. 1.4 depicts the general block diagram of the SSLKF-PLL.

Fig. 1.4: General Block diagram of the SSLKF-PLL.

The reported results in [34] demonstrate that the SSLKF-PLL ensures a zero steady-state phase error in response to phase jumps, frequency jumps, and frequency ramps. The advantages and disadvantages of this structure compared to a typical type-III SRF-PLL, nevertheless, is unclear.

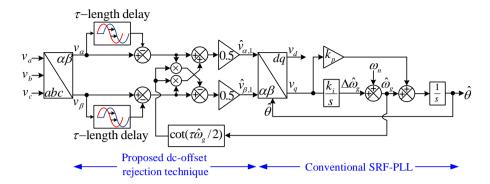

## 1.1.1.1.3 Three-Phase PLLs with Enhanced DC-Offset Rejection Ability

It was discussed before that the SRF-PLL is highly vulnerable to the DC offset presence in its input. The reason is that even a small DC component in the SRF-PLL input may cause large fundamental-frequency oscillations in its estimated phase, frequency, and amplitude [36]. It has also been proved recently that in the presence of this disturbance, the SRF-PLL unit vector (i.e., the sine and cosine of the estimated phase angle) contains a DC component [36]. Considering that the PLL unit vector is often employed for the reference current generation in grid-connected current-controlled converters, a DC component appears in the converter reference current in this condition, which (depends on the converter current control loops) may lead to injecting a DC current by the converter to the grid [36]. It should be emphasized here that the international standards have limited injecting the DC current by grid-tied converters. According to standards IEC61727 [37] and IEEE 1547-2003 [38], this limit is 1% and 0.5% of the nominal current of the converter, respectively. This discussion highlights the importance of a high DC rejection ability for PLLs.

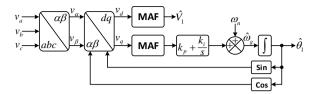

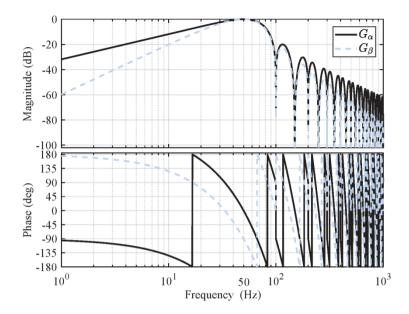

To enhance the SRF-PLL DC-offset filtering ability, some research efforts have been made. A basic approach is including two moving average filters (MAFs) in the SRF-PLL structure, as illustrated in Fig. 1.5 [39], [40]. The MAF is a rectangular window filter with the following s-domain transfer function, in which  $T_w$  is called the window length.

$$G_{MAF}(s) = \frac{1 - e^{-T_w s}}{T_{...} s}$$

(1.8)

Fig. 1.5: SRF-PLL with in-loop MAF.

As discussed before, the DC component presence in the input of the SRF-PLL leads to fundamental-frequency ripples in the dq-axis signals (after the Park's transformation). Considering that the MAF passes the zero frequency component and filters all harmonics whose frequencies are  $m/T_w$  ( $m=1,2,3,\cdots$ ), removing the fundamental-frequency oscillations using the MAF requires a window length equal to the grid fundamental period [39]. As MAFs are within the control loop of SRF-PLL, such a wide window length leads to a large inloop phase delay and, hence, an extremely slow dynamic behavior. It should be emphasized here that, the MAF with a window length equal to the grid fundamental period, removes all harmonics up to aliasing frequency in addition to the fundamental-frequency disturbance component [39].

An alternative approach to support the SRF-PLL in rejecting the DC offset is including the so-called dq-frame delayed signal cancellation (dqDSC) operator in the SRF-PLL structure [41]-[43]. The resultant PLL structure is the same as Fig. 1.5 except that the MAFs are replaced with dqDSC operators.

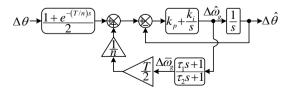

The dqDSC operator is a nonrecursive filter with the following s-domain transfer function [41]-[43]

$$dq DSC_n(s) = \frac{1 + e^{\frac{-Ts}{n}}}{2}$$

(1.9)

in which T denotes the fundamental period of grid voltage and n is the delay factor. As removing a fundamental-frequency disturbance component using the dqDSC operator is concerned here, the delay factor n should be set equal to 2. Such an operator, for sure, effectively rejects the fundamental-frequency ripples caused by the DC component. But, similar to the MAF, it causes a large inloop phase delay. This delay, of course, is not as large as that is caused by a MAF with  $T_w = T$ . But, it is still quite large, and hence, leads to a slow transient response for the SRF-PLL.

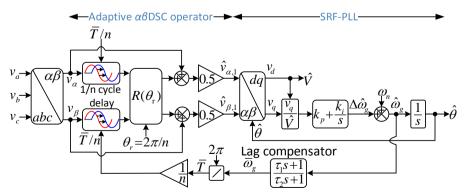

A more interesting approach than previous ones is including the delayed signal cancellation operator in the SRF-PLL input. It is referred to as the  $\alpha\beta$ -frame delayed signal cancelation ( $\alpha\beta$ DSC) operator and is described in the *s*-domain as follows [36], [41], [42], [45]

$$\alpha\beta DSC_n(s) = \frac{1 + e^{\frac{j2\pi}{n}} e^{-\frac{Ts}{n}}}{2}.$$

(1.10)

Similar to the dqDSC operator case, removing the DC offset using this filter requires a delay factor equal to 2. Compared to the previous options, i.e., the dqDSC operator and in-loop MAF, this filter results in a less adverse effect on the SRF-PLL dynamic behavior because it is placed in the SRF-PLL input. However, there is still room for improvement because a half cycle delay for removing only the DC component sounds too large. This is particularly true when rejecting the even-order harmonics is not required.

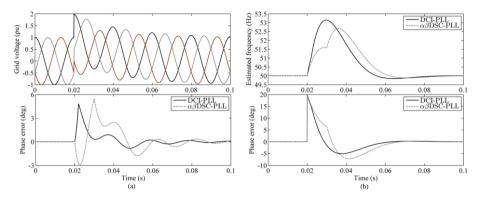

## 1.1.1.1.4 Three-phase PLLs with Enhanced Imbalanced and Harmonic Rejection Ability

It was briefly discussed before that the grid voltage imbalance, which may be caused by asymmetrical loading, grid faults, and the line impedance imbalance, results in a double-frequency oscillatory ripple, and a harmonic component of order h leads to an h-l order harmonic frequency ripple in the SRF-PLL estimated parameters. These ripples significantly degrade the SRF-PLL accuracy. To enhance the SRF-PLL imbalance and harmonic rejection capability some efforts have been made in recent years [5]. The most advanced solutions are examined in what follows.

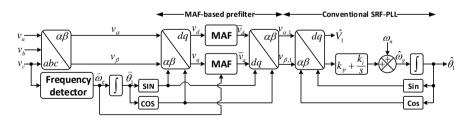

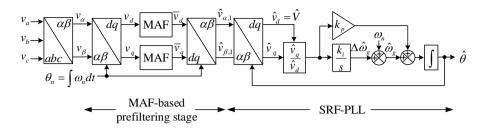

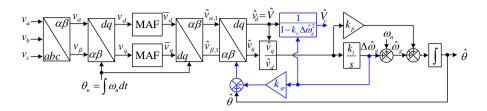

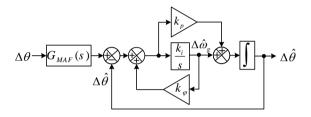

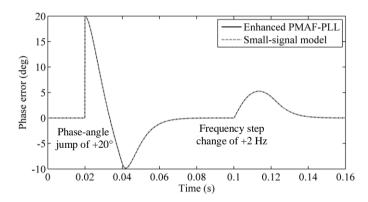

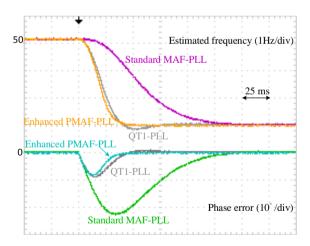

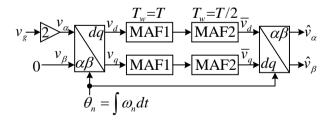

A possible approach to making the SRF-PLL immune to the disturbing effects of the grid voltage harmonics, imbalance, and even DC offset, is using a MAF-based prefilter in its input, as shown in Fig. 1.6 [44]. This prefilter includes two MAFs in the SRF. The window length of MAFs and the rotating angle of its SRF are adapted to the grid frequency changes by employing an additional frequency detector. It should be noted that the phase and frequency detected by the SRF-PLL may not be used for adapting the MAF-based prefilter. The reason is that, from the control point of view, it corresponds to include the MAFs within the control loop of SRF-PLL, which results in a very slow dynamic response.

Fig. 1.6: SRF-PLL with a MAF-based prefilter.

The performance of the SRF-PLL with the MAF-based prefiltering stage highly depends on the frequency detector. In other words, the efficient operation of this PLL demands a highly accurate frequency detector, which is corresponding to an increased complexity and computational burden.

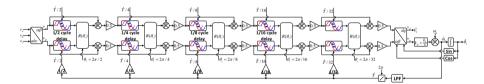

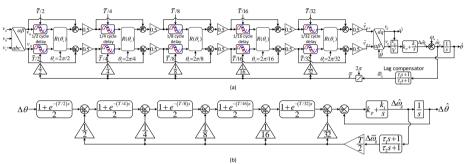

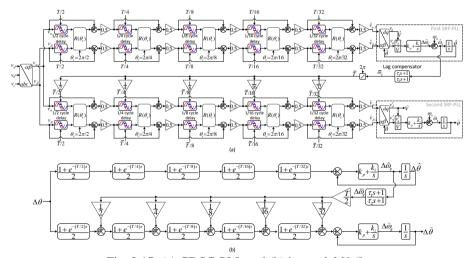

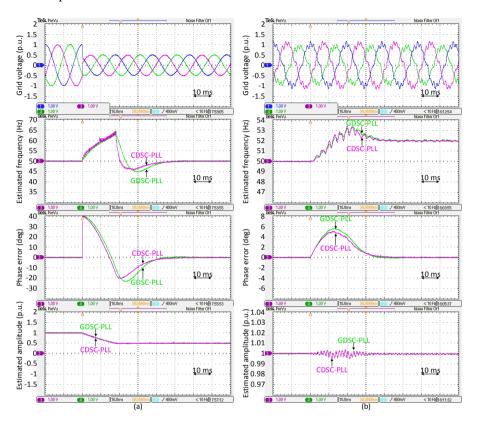

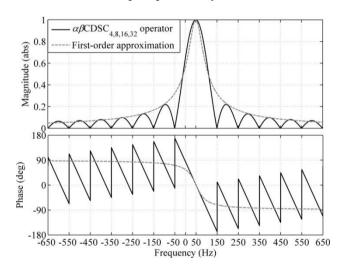

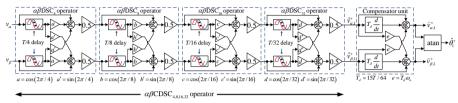

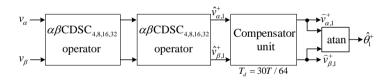

An alternative approach to enhance the SRF-PLL harmonic/imbalance rejection capability is using a chain of  $\alpha\beta$ DSC operators as its prefiltering stage [41], [42], [45]-[48]. Different combinations of  $\alpha\beta$ DSC operators may be used in the chain. Selecting a proper combination depends on the grid voltage distortion pattern. A common practice is assuming an unknown pattern for the grid voltage distortions, which implies that the presence of all harmonics in the grid voltage is possible. In this condition, a chain of five  $\alpha\beta$ DSC operators with the delay factors 2, 4, 8, 16, and 32 is employed in the SRF-PLL input, as shown in Fig. 1.7 [41], [42]. Notice that the delay length of operators is variable. These delays are adapted to the variations of the grid frequency using a frequency feedback loop. This task most often involves employing interpolation techniques because the approximation of fractional delays is almost always required. When the sampling frequency is high, a linear interpolation technique is good enough. But, in high-power converters, where the switching frequency and, hence, the sampling frequency are low, a high-order interpolation is needed, which results in a high computational burden and implementation complexity. Besides, using variable-length delays in the CDSC-PLL complicates its modeling and, consequently, analyzing its stability and selecting its control parameters. No one has yet been able to obtain the linearized model of this PLL structure.

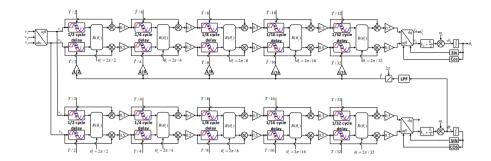

Fig. 1.7:  $\alpha\beta$ -frame cascaded delayed signal cancellation-based PLL (briefly called the CDSC-PLL).

To avoid feeding back the estimated frequency for adapting the length of delays, a different structure referred to as the generalized delayed signal cancellation-based PLL (GDSC-PLL) is proposed [45]-[47]. This structure includes two chains of identical operators and two SRF-PLLs. One chain is nonadaptive and the other one is frequency-adaptive. The nonadaptive chain and its associated SRF-PLL are responsible to provide an initial estimation of the frequency of grid voltage for adjusting the length of delays of the frequency-adaptive chain. In this way, it can be ensured that the PLL structure always remains stable. This advantage is at the cost of a considerably higher computational burden. Notice that the computational burden of the GDSC-PLL is almost twice that of the CDSC-PLL. Notice also that the small-signal modeling and efficient tuning of the GDSC-PLL, similar to the CDSC-PLL, has not been conducted yet.

Fig. 1.8: Generalized delayed signal cancellation-based PLL (GDSC-PLL).

#### 1.1.1.2 Single-phase PLLs

#### 1.1.1.2.1 Standard Single-phase PLL

Fig. 1.9 depicts the block diagram of a standard single-phase PLL, which is often called the power-based PLL (pPLL) [6], [29], [31], [49]. The pPLL characteristic is using a product-type PD, which results in a simple structure. This simplicity, nevertheless, is at the cost of a poor performance. The reason is that the product-type PD, in addition to the phase error information, causes a very large double-frequency disturbance component in its output, which results in large oscillatory and offset errors [6], [29], [31], [49]. In addition, making the pPLL dynamics decoupled from the amplitude variations of grid voltage is not possible as the pPLL does not extract the grid voltage amplitude [6].

Fig. 1.9: Power-based PLL (pPLL).

Solving the drawbacks of the pPLL has been the main motivation behind developing more advanced single-phase PLLs [6]. These advanced single-phase PLLs may be divided into two main categories: Enhanced pPLLs and quadrature signal generation-based PLLs (QSG-PLLs) [6].

What almost all enhanced pPLLs have in common is adding a filtering stage inside the standard pPLL control loop to remove the double-frequency disturbance term. Using a high-order LPF [29], notch filter [50], and MAF [40] are some possible

options. A rather large in-loop phase delay and, therefore, a slow dynamic response is the cost of using these filters. For this reason, enhanced pPLLs have not received a wide attention.

The QSG-PLLs are the single-phase versions of the conventional SRF-PLL [6]. The common feature of almost all QSG-PLLs is generating a quadrature signal from the single-phase grid voltage [51]. This fictitious signal, which is used as the  $\beta$ -axis signal for the frame transformation, may be generated in different ways [6]. This is actually the main difference of QSG-PLLs compared to each other. Transfer delay [52], [53], second-order generalized integrator (SOGI) [30], [54], all-pass filter [55], [56], sliding discrete Fourier transform [25], [57], [58], inverse Park transformation [29], [30], [59], synchronous reference frame MAF [60], differentiator [61], and Hilbert transform [62], [63] are well-known options. In what follows, delay-based and SOGI-based approaches, which are probably the most popular options, are examined.

#### 1.1.1.2.2 Transfer Delayed-based PLLs

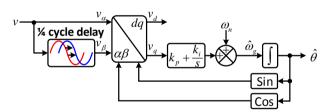

Fig. 1.10 depicts the block diagram of a standard transfer delay-based PLL (TD-PLL), which uses a fixed-length quarter cycle delay for generating a  $\beta$ -axis signal for the conventional SRF-PLL. This structure works satisfactorily under a nominal (or very close to nominal) grid frequency. Under frequency drifts, nevertheless, the generated fictitious signal is nonorthogonal to the grid voltage fundamental component, which leads to offset and oscillatory errors.

Fig. 1.10: Standard TD-PLL.

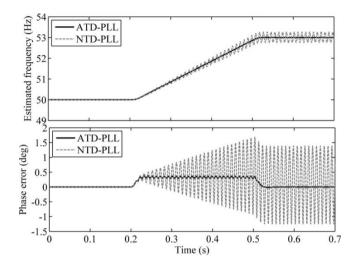

To correct offset and oscillatory errors of the TD-PLL with the fixed-length delay, some attempts have been made. For example, in [52] and [53], a structure referred to as the non-frequency-dependent TD-PLL (NTD-PLL) is suggested. Fig. 1.11 illustrates this idea. As shown, the NTD-PLL uses two fixed-length quarter cycle delays. The first one is for generating the quadrature signal  $v_{\beta}$ , and the second one is for correcting the phase offset error. This correction is carried out by generating  $\cos(\hat{\theta})$  from  $\sin(\hat{\theta})$  using a fixed-length delay.

Fig. 1.11: Non-frequency-dependent TD-PLL (NTD-PLL).

The NTD-PLL benefits from a simple structure as it continues using fixed-length delays. In addition, it corrects the phase offset error of the standard TD-PLL under frequency drifts. It, nevertheless, is not able to solve the double-frequency problem. It is worth mentioning that the modeling and tuning of the NTD-PLL have not been carried out yet.

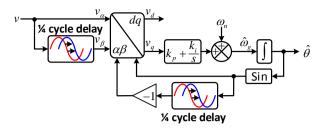

Another approach to solving the standard TD-PLL problems is adapting the length of its delay using a frequency feedback loop, as illustrated in Fig. 1.12. This procedure involves utilizing an interpolation technique as a fractional delay approximation is required. Selecting the interpolation polynomial depends on the sampling frequency and the required accuracy. At a high sampling frequency, which corresponds to a short distance between samples, a linear interpolation is good enough.

The VLTD-PLL is an effective PLL structure that corrects the offset and oscillatory errors of the standard TD-PLL. The VLTD-PLL implementation, however, as mentioned before, involves using a variable length delay, which complicates the modeling and, hence, the tuning and stability assessment. To the best of the Author's knowledge, no accurate model for the VLTD-PLL has yet been derived.

Fig. 1.12: Variable-length transfer delay-based PLL (VLTD-PLL).

#### 1.1.1.2.3 Second-order Generalized Integrator-based PLLs

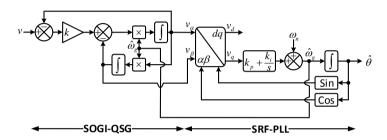

The standard SOGI-PLL (hereafter, just called the SOGL-PLL) is one of the most popular single-phase PLLs because it has a more or less simple structure and offers an acceptable harmonic filtering rejection ability. This PLL structure includes a SOGI-based quadrature signal generator (SOGI-QSG), which extracts the fundamental component of the grid voltage and generate its quadrature (90° phase shifted) version, and a conventional SRF-PLL. There is a frequency feedback loop in this structure that adapts the SOGI resonance frequency to the grid frequency changes. This loop results in a strong coupling between the dynamics of the SOGI-QSG and SRF-PLL. The block diagram of the standard SOGI-PLL can be observed in Fig. 1.13 [54].

Fig. 1.13: Standard SOGI-PLL.

To further enhance the SOGI-PLL performance, some modifications to its structure have been suggested. The important ones are as follows

- The first one is adding an LPF in the frequency feedback loop [64]. This

idea is probably intended to reduce the level of coupling between the

SOGI-QSG and SRF-PLL.

- The second one is removing the frequency feedback loop and fixing the resonance frequency of the SOGI at the nominal frequency and employing a compensator for compensating the errors generated by the nonadaptive SOGI-QSG [65].

- The third one, similar to the previous one, is using a nonadaptive SOGI-QSG in the SRF-PLL input and adding a second nonadaptive SOGI-QSG in the phase feedback loop to compensate for errors [66].

- The fourth one is using two cascaded SOGI-QSG in the SRF-PLL input [67], [68]. Notice that the only input to the second SOGI-QSG is the α-axis output of the first one. In this way, the DC offset is completely removed. Notice also that these two SOGI-QSGs can be frequency-adaptive or not. In the latter case, correcting errors requires a compensator.

- The fifth one is making the SOGI-QSG self-adaptive [69]. In this way, the need for the frequency feedback loop is removed.

In summary, different researchers have recommended different modifications, and all of them claim that these modifications result in a considerable performance enhancement compared to the standard SOGI-PLL. These claims are just supported by some numerical results. It is, however, no evidence to confirm that the condition of comparison has been fair. Moreover, no information about the tuning procedure of these so-called enhanced SOGI-PLLs is available. The key to solving these problems is developing the small-signal models of these PLL structures. Accurate modeling of these enhanced SOGI-PLLs has not yet been carried out.

#### 1.1.2. FREQUENCY-LOCKED LOOPS (FLLS)

FLLs, like PLLs, are classified under the category of closed-loop synchronization techniques. But, contrary to PLLs, they are implemented in the stationary reference frame<sup>1</sup>. In addition to the synchronization of power converters [71]-[77], FLLs are widely used in different industrial applications such as flux estimation for motor drives [78], [79], islanding detection [80], delay estimation of sinusoidal signals [81], estimation of electromagnetic oscillations [82], etc.

#### 1.1.2.1 Single-phase FLLs

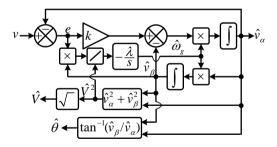

Implementing single-phase FLLs is often based on a generalized integrator. Fig. 1.14 illustrates the block diagram of a standard single-phase FLL, which is based on a SOGI [71].

Fig. 1.14: Standard SOGI-FLL.

-

Very recently, some so-called FLLs have been designed in the synchronous reference frame [70].

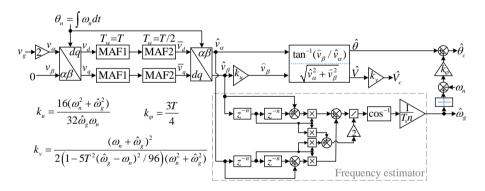

This structure extracts the grid voltage fundamental component and its quadrature version, i.e.,  $\hat{v}_{\alpha}$  and  $\hat{v}_{\beta}$ , using a SOGI-QSG. The phase and amplitude of the grid voltage fundamental component are then obtained as expressed below

$$\hat{\theta} = \tan^{-1} \left( \frac{\hat{v}_{\beta}}{\hat{v}_{\alpha}} \right) \tag{1.11}$$

$$\hat{V} = \sqrt{\hat{v}_{\alpha}^2 + \hat{v}_{\beta}^2} \ . \tag{1.12}$$

Adapting the SOGI center frequency is carried out based on the following differential equation

$$\frac{d\hat{\omega}_g}{dt} = -\frac{\lambda}{\hat{V}^2} (v - \hat{v}_\alpha) \hat{v}_\beta \tag{1.13}$$

in which  $\lambda$  is the frequency estimation gain.

The standard SOGI-FLL has a limited disturbance rejection ability. In addition, the accurate small-signal modeling of the SOGI-FLL has not yet been carried out.

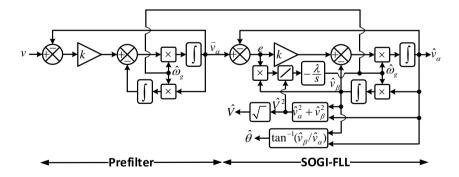

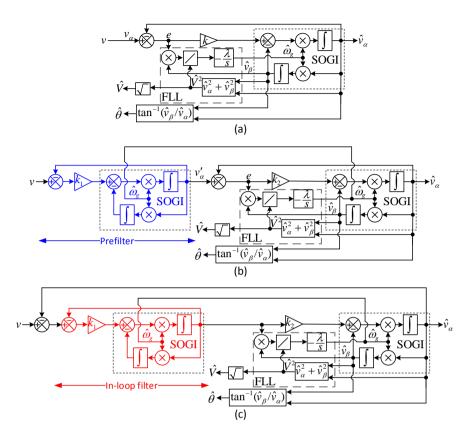

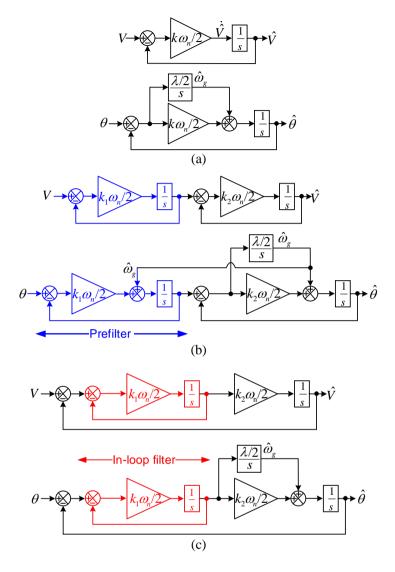

To enhance the SOGI-FLL filtering capability, some research efforts have been made. For example, Fig. 1.15 illustrates a SOGI-FLL with prefilter (SOGI-FLL-WPF) [75]. The prefilter is a SOGI-QSG, but only its  $\alpha$ -axis output is used. In this way, the SOGI-FLL-WPF is totally immune to the DC offset of the grid voltage. Using the prefilter is also expected to improve the SOGI-FLL ability in filtering the grid voltage harmonics. The modeling of this structure, however, has not yet been conducted. The lack of a small-signal model makes the tuning and stability analysis of the SOGI-FLL-WPF difficult.

Fig. 1.15: SOGI-FLL with prefilter (SOGI-FLL-WPF).

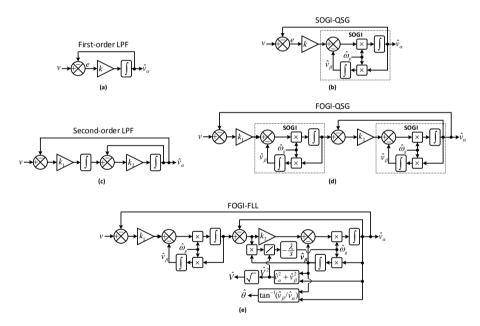

In [76], an advanced FLL through establishing a structural resemblance between an LPF and SOGI-QSG is designed. The developing procedure of this FLL is as follows. It is first shown that if the loop integrator of a first-order LPF [see Fig.

1.16(a)] is replaced by a SOGI, the SOGI-QSG [see Fig. 1.16(b)] is obtained. Based on this structural resemblance, a four-order generalized integrator-based QSG (FOGI-QSG) [see Fig. 1.16(d)] is proposed in [76], which is obtained by substituting two integrators of a second-order LPF [see Fig. 1.16(c)] by two SOGIs. And finally, using this FOGI-QSG and the same frequency estimator as that of the standard SOGI-FLL, an advanced FLL as shown in Fig. 1.16(e) is developed.

The FOGI-FLL has been designed very recently, and its small-signal modeling, stability analysis, tuning procedure have not yet been carried out. In addition, its advantages and disadvantages compared to the SOGI-FLL-WPF are unclear.

Using a parallel configuration of multiple SOGIs centered at low-order harmonic frequencies is another approach for enhancing the SOGI-FLL performance [71]. A limitation of this approach is its computational burden as removing any additional harmonic requires an extra SOGI.

Fig. 1.16: Developing an advanced FLL through establishing a structural resemblance between an LPF and SOGI-QSG. (a) First-order LPF, (b) SOGI-QSG, (c) second-order LPF, (d) four-order generalized integrator-based QSG (FOGI-QSG), and (e) FOGI-FLL.

#### 1.1.2.2 Three-phase FLLs

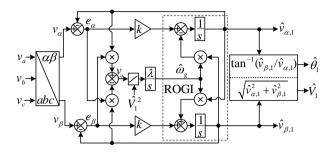

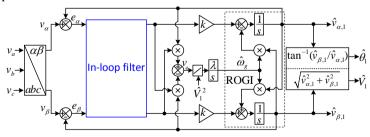

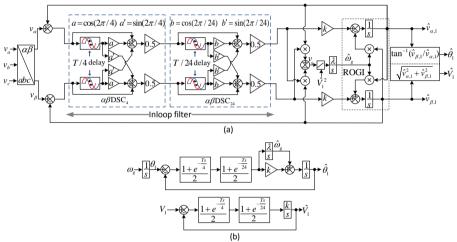

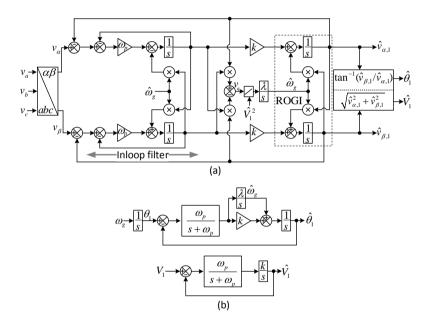

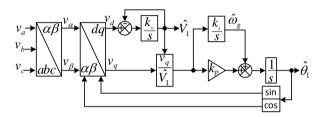

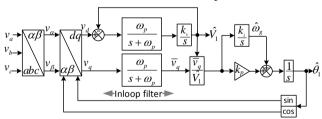

Implementing three-phase FLLs is based on the reduced-order generalized integrator (ROGI), which is described in the s-domain as  $1/(s-j\omega_c)$  [83], where  $\omega_c$  is the ROGI center frequency. Fig. 1.17 illustrates the block diagram of a standard three-phase FLL, which is called the ROGI-FLL.

Fig. 1.17: Standard ROGI-FLL.

The ROGI-FLL is based on using a ROGI in a unity feedback structure, which results in a complex bandpass filter (CBF) centered at the fundamental frequency. Therefore, the signals  $\hat{v}_{\alpha,1}$  and  $\hat{v}_{\beta,1}$  at the ROGI-FLL outputs are the estimations of the grid voltage FFPS component. The ROGI resonance frequency, which is the CBF center frequency, is updated based on the following differential equation

$$\frac{d\hat{\omega}_g}{dt} = \frac{\lambda}{\hat{V}^2} \left( e_{\beta} \hat{v}_{\alpha,1} - e_{\alpha} \hat{v}_{\beta,1} \right) \tag{1.14}$$

in which  $\lambda$  is the frequency estimation gain. The phase and amplitude of the grid voltage are finally calculated using the extracted FFPS component as shown in Fig. 1.17. The ROGI-FLL has a limited filtering capability and its modeling has not been conducted yet.

The available methods for enhancing the ROGI-FLL filtering capability are similar to those described for the SOGI-FLL (i.e., using a parallel configuration of multiple ROGIs centered at low-order harmonic frequencies [84]-[87], designing a high-order FLL by establishing a structural resemblance between an LPF and CBF [76], etc.) Therefore, for the sake of brevity, they are not repeated here.

#### 1.1.3. OPEN-LOOP SYNCHRONIZATION (OLS) TECHNIQUES

The key characteristic of an OLS technique, as mentioned before, is using no feedback signal in its structure, which results in an unconditional stability. It is probably the main benefit of an OLS technique compared to PLLs and FLLs.

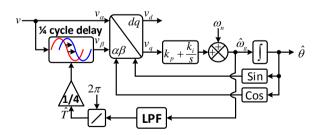

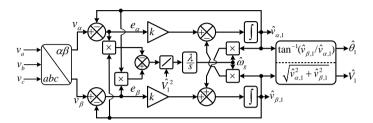

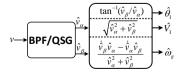

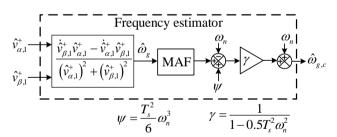

Fig. 1.18 illustrates a standard three-phase OLS technique. The key part of this structure is a bandpass filter that extracts the grid voltage FFPS component. The frequency, phase, and amplitude are then calculated using this extracted FFPS component as  $\hat{\omega}_g = (\dot{\hat{v}}_{\beta,l}\hat{v}_{\alpha,l} - \dot{\hat{v}}_{\alpha,l}\hat{v}_{\beta,l})/(\hat{v}_{\alpha,l}^2 + \hat{v}_{\beta,l}^2)$ ,  $\hat{\theta}_l = \tan^{-1}(\hat{v}_{\beta,l}/\hat{v}_{\alpha,l})$  and  $\hat{V}_l = \sqrt{\hat{v}_{\alpha,l}^2 + \hat{v}_{\beta,l}^2}$ , where  $\dot{v}_x = dv_x/dt$ . Simplicity, low computational burden, unconditional stability, and fast dynamic response are the key features of this structure. It, however, has a serious drawback: It may not work effectively under off-nominal frequencies as the BPF center frequency is not adaptive (it is fixed at the nominal frequency) [89]. To be more exact, a frequency change results in errors in the phase and amplitude of the extracted FFPS component and, hence, the estimated phase and amplitude. Solving this problem has been the main motivation behind developing advanced OLS techniques. A brief review is conducted below.

Fig. 1.18: A standard three-phase OLS technique.

An approach, which is sometimes used by researchers to solve the above-mentioned errors, is feeding back the estimated frequency for adapting the BPF to the grid frequency changes [90]. In such a case, however, the synchronization technique may not be regarded open-loop anymore.

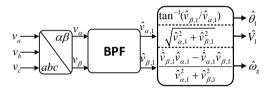

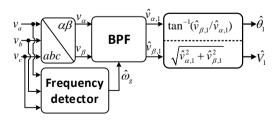

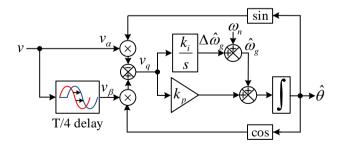

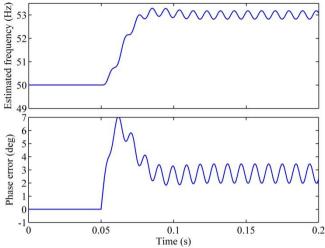

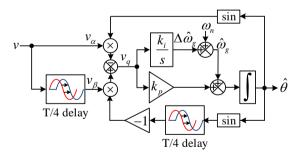

Another method is employing a parallel frequency detector for extracting the grid frequency and adapting the BPF to the grid frequency changes [91], [92]. Fig. 1.19 illustrates this idea. This frequency detector needs to have its own filtering stage and should provide a fast yet accurate estimation of the grid frequency. Such requirement results in a considerable increase in the implementation complexity and computation burden.

Fig. 1.19: Using a parallel frequency detector in an OLS technique to avoid errors under off-nominal frequency.

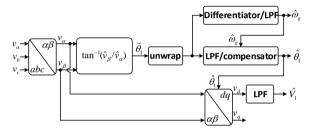

Some researchers do not follow the standard structure and use a totally different topology for implementing an open-loop technique. An example is shown in Fig. 1.20 [93], [94]. In this structure, the grid voltage angle is calculated by applying an arctangent function to the  $\alpha\beta$ -axis grid voltage signals. Then, an unwrapping algorithm is employed to remove the phase discontinuities. As the slope of the unwrapped phase angle is equal to the grid frequency, a differentiator/LPF is used for extracting the grid frequency. The unwrapped phase angle is also passed through an LPF and, subsequently, through a compensator to remove its oscillatory ripples and accurately detect the grid voltage phase angle. The compensator here is responsible to correct the phase offset caused by passing the unwrapped phase angle through the LPF. The grid voltage amplitude is also estimated by passing the *d*-axis signal through an LPF. The *dq*-axis signals are generated by applying the Park's transformation to the  $\alpha\beta$ -axis signals. The rotating angle of this Park's transformation is the estimated phase angle.

Fig. 1.20: A different way of implementing an OLS technique.

This OLS technique, however, may not be very practical. The main limitation here is unwrapping the phase angle. The reason is that, regardless of the implementation complexity of an efficient unwrapping method, the unwrapped phase angle continuously grows, which results in the DSP register overflow. It implies that a resetting system should be included. This resetting, however, causes phase discontinuities and, therefore, large transients in the estimated quantities.

In developing single-phase OLS techniques, the situation is even more complicated than before because, in addition to filter the signal-phase signal, its quadrature version should be provided. Fig. 1.21 illustrates the schematic diagram of a standard single-phase OLS technique.

Fig. 1.21: A standard single-phase OLS technique.

#### 1.2. THESIS OBJECTIVES

Advancing the state-of-the-art in the field is the overall objective of this thesis. To this end, the following specific objectives are considered.

Regarding PLLs, the following objectives are defined:

- The first objective is the modeling, stability analysis, tuning, and performance assessment of single-phase transfer delay-based PLLs (TD-PLLs) and three-phase delayed-signal cancellation based-PLLs (DSC-PLLs). Designing an approach to eliminate the need for adjusting the length of delays in these PLLs is also a part of this objective.

- The second objective is analyzing the steady-state linear Kalman filter-based PLLs (SSLKF-PLLs) and highlighting their advantages and disadvantages compared to a standard SRF-PLL and its close variants.

- The third objective is developing a simple, efficient, and general approach to deal with the DC-offset problem in three-phase PLLs.

- The last but not the least objective is designing a simple yet effective approach to eliminating the need for using a parallel frequency detector in the PLL with the MAF-based prefiltering stage. Deriving a small-signal modeling for this PLL is also a part of this objective.

Regarding FLLs, the following objectives are defined:

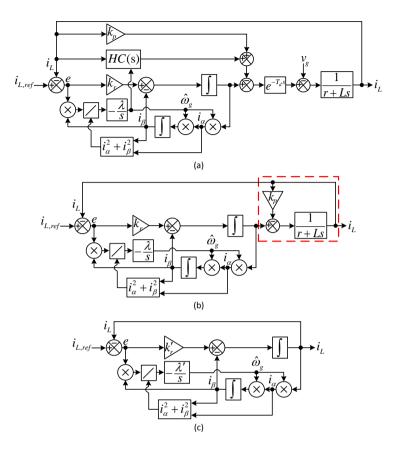

- The first objective is modeling, tuning, analyzing, and comparative performance evaluation of SOGI-based FLLs.

- The second objective is introducing the concept of inloop filter in FLLs.

- The third objective is finding a relationship between FLLs and PLLs.

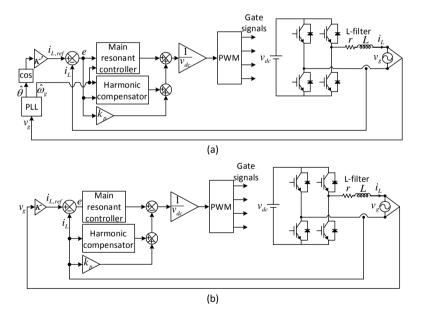

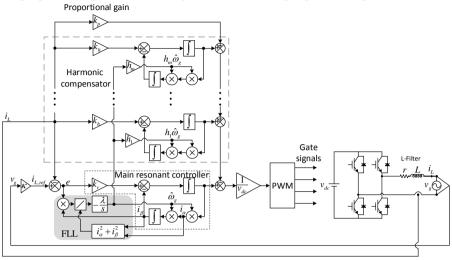

- The last but not the least objective is using the FLL concept to design selfadaptive proportional-resonant (PR) controllers for the control of singlephase grid-interfaced power converters.

Regarding OLS techniques, the following objectives are defined:

The objective is designing OLS techniques with a very fast dynamic response, efficient operation under nominal and off-nominal frequencies, high filtering capability, and simple structure for three-phase and singlephase applications.

#### 1.3. THESIS OUTLINE

The rest of this thesis is organized as follows.

Chapter 2 presents the contributions of this thesis to modeling, analyzing, and designing PLLs. To be more exact, it presents the modeling and tuning procedures of some single-phase and three-phase TD-PLLs, and performs an analysis on SSLKF-PLLs. A general approach for the DC offset rejection in three-phase PLLs is also designed in this chapter. Finally, a method for eliminating the need for using a parallel frequency detector in the PLL with the MAF-based prefiltering stage is presented.

**Chapter 3** summarizes the contributions of this thesis to modeling, analyzing, and designing FLLs. Demonstrating the modeling and tuning procedure of standard and advanced FLLs, introducing the concept of inloop filter in FLLs, demonstrating the relation between PLLs and FLLs, and designing an adaptive resonant regulator for single-phase grid-tied converters are the main parts of the chapter.

**Chapter 4** presents the procedure of designing advanced single-phase and three-phase OLS techniques.

**Chapter 5** summarizes the contributions of this thesis and the directions for the future research.

# CHAPTER 2. MODELING, ANALYZING, AND DESIGNING PLLS

This chapter is a summary of contributions of this thesis to modeling, analyzing, and designing PLLs.

#### 2.1. TRANSFER DELAY-BASED PLLS (TD-PLLS)

This part mainly deals with deriving small-signal models for the advanced single-phase and three-phase TD-based PLLs. To be more exact, the NTD-PLL, VLTD-PLL, CDSC-PLL, and GDSC-PLL are modeled. The tuning procedures of these PLLs are also briefly discussed. An adaptive single-phase TD-based PLL with a fixed-length delay is also designed and presented here.

#### 2.1.1. STANDARD TD-PLL

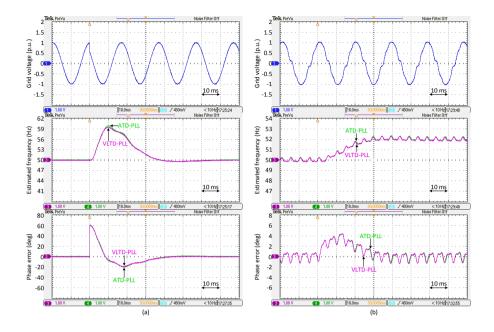

The block diagram representation of a standard TD-PLL is observed in Fig. 2.1 [95]. The key part of this structure is a fixed-length quarter cycle delay, which provides a fictitious orthogonal signal (which is represented by  $v_{\beta}$ ) for transferring information to the synchronous reference frame. This structure offers a great simplicity in the digital implementation; nevertheless, it has a serious drawback: the fictitious signal does not have exactly a 90° phase difference compared to the fundamental component of the grid voltage when its frequency deviates from the nominal value. This problem causes offset and oscillatory errors in the standard TD-PLL output. Fig. 2.2 clearly illustrates these two types of errors. Solving these errors has been the main motivation for developing more advanced single-phase TD-PLLs in the literature.

Fig. 2.1: Block diagram representation of the standard TD-PLL [95].

Fig. 2.2: Performance of the standard TD-PLL under a +3-Hz jump in the grid frequency [97].

#### 2.1.2. NON-FREQUENCY-DEPENDENT TD-PLL (NTD-PLL)

The block diagram representation of the NTD-PLL, which has been proposed in [52] and [53], is seen in Fig. 2.3. The basic idea of the NTD-PLL, as mentioned before, is the indirect generation of the cosine of the estimated phase angle by delaying the sine of the estimated phase angle by a fixed-length quarter cycle delay. Preserving the implementation simplicity of the standard TD-PLL and solving its phase offset error are the key features of the NTD-PLL.

Fig. 2.3: Basic structure of the NTD-PLL [95].

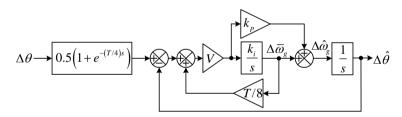

As mentioned before, no small-signal model for this structure has yet been derived. As a result, the only available option for tuning the control parameters of this PLL is trial and error. In what follows, a small-signal model and a systematic tuning method for the NTD-PLL are presented.

#### 2.1.2.1 Modeling of the NTD-PLL

In this section, the modeling procedure of the NTD-PLL is briefly presented. To see a more detailed procedure, refer to [95] (Paper 3 in Appendix).

For deriving the NTD-PLL small-signal model, it is assumed that the input signal is as follows

$$v(t) = v_{\alpha}(t) = V\cos(\theta) \tag{2.1}$$

in which V and  $\theta$  denote the amplitude and phase angle of the input signal, respectively. Without loss of generality,  $\theta = \omega_g t + \varphi$  is considered, where  $\omega_g$  and  $\varphi$  are the angular frequency and initial phase angle, respectively.

Based on the aforementioned assumptions and the structure of the NTD-PLL in Fig. 2.3, the signal  $v_a$  in the input of the PI regulator may be expressed as

$$v_{q}(t) = -v_{\alpha}(t)\sin\left(\hat{\theta}\right) - v_{\beta}(t)\sin\left(\hat{\theta}_{d}\right)$$

$$= \frac{V}{2}\sin\left(\theta - \hat{\theta}\right) + \frac{V}{2}\sin\left(\theta_{d} - \hat{\theta}_{d}\right) - \frac{V}{2}\underbrace{\sin\left(\theta + \hat{\theta}\right)}_{D_{2}^{\prime}(t)} - \frac{V}{2}\underbrace{\sin\left(\theta_{d} + \hat{\theta}_{d}\right)}_{D_{2}^{\prime}(t-T/4)}$$

(2.2)

in which  $\theta_d(t) = \theta(t - T/4)$  and  $\hat{\theta}_d(t) = \hat{\theta}(t - T/4)$ . By defining  $\theta = \theta_n + \Delta\theta$  and  $\hat{\theta} = \theta_n + \Delta\hat{\theta}$ , (2.2) can be approximated by

$$v_{q}(t) \approx \frac{V}{2} \left[ \left( \Delta \theta - \Delta \hat{\theta} \right) + \left( \Delta \theta_{d} - \Delta \hat{\theta}_{d} \right) - D_{2}'(t) - D_{2}'(t - T/4) \right]$$

(2.3)

where  $\Delta \theta_d(t) = \Delta \theta(t - T/4)$  and  $\Delta \hat{\theta}_d(t) = \Delta \hat{\theta}(t - T/4)$ .

In the s-domain, (2.3) is equivalent to

$$v_q(s) \approx V \frac{1 + e^{-sT/4}}{2} \left[ \Delta \theta(s) - \Delta \hat{\theta}(s) - D_2'(s) \right]. \tag{2.4}$$

Using (2.4) and Fig. 2.3, the small-signal model of the NTD-PLL may be obtained as depicted in Fig. 2.4.

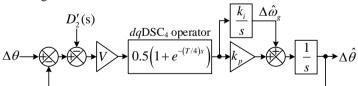

Fig. 2.4: NTD-PLL small-signal model [95].

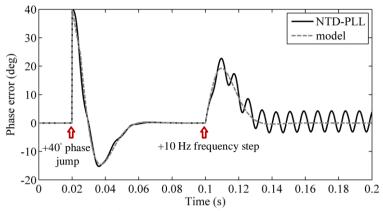

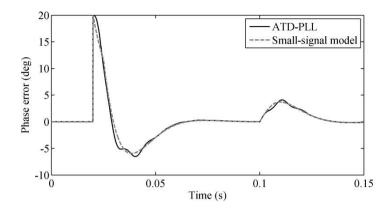

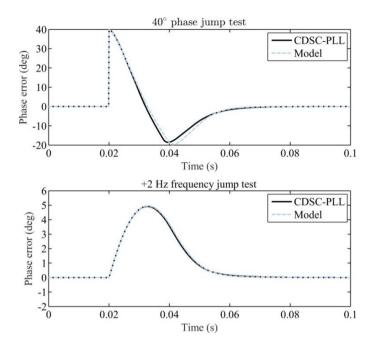

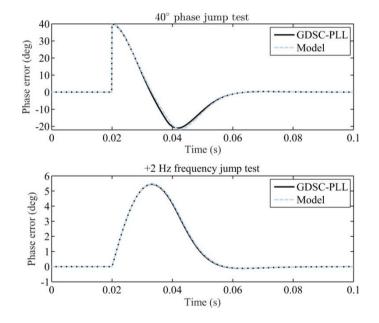

To investigate the accuracy of this model, some standard tests (a phase jump and a frequency jump) are performed. The results of this investigation may be observed in Fig. 2.5. The model, as shown, is able to predict the NTD-PLL average behavior very accurately.

Fig. 2.5: Investigating the accuracy of the NTD-PLL model [95].

#### 2.1.2.2 Tuning of the NTD-PLL

In this part, a method for tuning the NTD-PLL control parameters is briefly presented. For more details, refer to [95] (Paper 3 in Appendix).

According to the small-signal model of the NTD-PLL and by neglecting the disturbance input to its model, the open-loop transfer function of this PLL may be expressed as

$$G_{ol}(s) = \frac{\Delta \hat{\theta}(s)}{\Delta \theta(s) - \Delta \hat{\theta}(s)} \bigg|_{D_{s}^{1}(s) = 0} = V \frac{1 + e^{-(T/4)s}}{2} \frac{k_{p} s + k_{i}}{s^{2}}.$$

(2.5)

The equation (2.5) can be rewritten as (2.6) by replacing its delay term by the first-order Pade approximation.

$$G_{ol}(s) \approx V \frac{1}{(T/8)s+1} \frac{k_p s + k_i}{s^2}$$

(2.6)

Now the symmetrical optimum (SO) method is simply applied to (2.6), which gives the control parameters as follows

$$k_{p} = \frac{1}{Vb(T/8)}$$

$$k_{i} = \frac{1}{Vb^{3}(T/8)^{2}}.$$

(2.7)

In (2.7), b is the phase margin (PM) determining factor, i.e.,  $PM = \tan^{-1} \left( \frac{b^2 - 1}{2b} \right)$ .

By choosing  $b = \sqrt{2} + 1$ , which is corresponding to an optimum damping factor for

the closed-loop poles of the NTD-PLL and provides a PM equal to 45°, the control parameters can be calculated as  $k_p = 166$  and  $k_i = 11371$ .

#### 2.1.3. VARIABLE-LENGTH TD-PLL (VLTD-PLL)

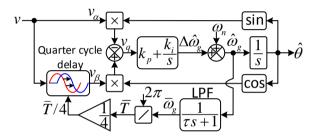

As discussed before, the standard TD-PLL suffers from oscillatory and offset errors and the NTD-PLL structure may only solve its phase offset problem. To correct both errors of the standard TD-PLL, a VLTD-PLL may be used. The block diagram representation of this PLL is illustrated in Fig. 2.6.

Fig. 2.6: Block diagram representation of the standard VLTD-PLL [96].

In the VLTD-PLL, the length of quarter cycle delay is not fixed anymore. Indeed, as mentioned before, it is adjusted using a frequency feedback loop in each sampling period. In this way, the signal  $v_{\beta}$  is always orthogonal to the grid voltage fundamental component and, therefore, no offset and oscillatory errors happen under frequency drifts. The presence of this variable length delay in the VLTD-PLL structure, nevertheless, makes the modeling procedure complicated. No small signal model for the VLTD-PLL has yet been derived. And because of the lack of a linearized model, the tuning procedure is carried out based on the trial and error, which is time-consuming. In what follows, a small-signal model for the VLTD-PLL is derived and a systematic tuning method for selecting its control parameters is presented.

#### 2.1.3.1 Modeling of the VLTD-PLL

In this section, the modeling procedure of the VLTD-PLL is briefly presented. For a more detailed procedure, refer to [96] (Paper 4 in Appendix). Similar to the case of the NTD-PLL, the input signal of the VLTD-PLL is

considered to be as (2.1). Based on this assumption and the VLTD-PLL structure, the orthogonal signal  $v_B$  may be expressed as

$$v_{\beta}(t) = V\cos(\theta - \omega_{\alpha}T/4). \tag{2.8}$$

Considering (2.1), (2.8), and Fig. 2.6, we may express the signal  $v_q$  in the input of the PI regulator as

$$v_q(t) = \frac{V}{2} \left[ \cos(\theta - \hat{\theta} - \omega_g \overline{T} / 4) + \sin(\theta - \hat{\theta}) - \sin(\theta + \hat{\theta}) + \cos(\theta + \hat{\theta} - \omega_g \overline{T} / 4) \right]. \tag{2.9}$$

Notice that the highlighted terms cancel each other in the steady state. Notice also that  $\omega_g \overline{T}/4$  is a nonlinear term and needs to be linearized. Considering that  $\overline{T} = 2\pi/\overline{\omega}_g$  and defining  $\overline{\omega}_g = \omega_n + \Delta \overline{\omega}_g$  and  $\omega_g = \omega_n + \Delta \omega_g$ , this term may be approximated by

$$\frac{\omega_{g}\overline{T}}{4} = \frac{2\pi}{4} \frac{1 + \frac{\Delta\omega_{g}}{\omega_{n}}}{1 + \frac{\Delta\overline{\omega}_{g}}{\omega_{n}}} \approx \frac{2\pi}{4} \left(1 - \frac{\Delta\overline{\omega}_{g}}{\omega_{n}}\right) \left(1 + \frac{\Delta\omega_{g}}{\omega_{n}}\right) \approx \frac{\pi}{2} - \frac{T}{4}\Delta\overline{\omega}_{g} + \frac{T}{4}\Delta\omega_{g}$$

(2.10)

By substituting (2.10) into (2.9) and considering the definitions made earlier for  $\theta$  and  $\hat{\theta}$ , we have

$$v_{q}(t) \approx V \left[ \frac{T}{8} \Delta \bar{\omega}_{g} - \Delta \hat{\theta} + \frac{\Delta \theta + \left\{ \Delta \theta - (T/4) \Delta \omega_{g} \right\}}{2} \right]$$

(2.11)

which results in (2.12) in the s-domain.

$$v_{q}(s) \approx V \left[ \frac{T}{8} \Delta \overline{\omega}_{g}(s) - \Delta \hat{\theta}(s) + \frac{1 + e^{-(T/4)s}}{2} \Delta \theta(s) \right]. \tag{2.12}$$

Using (2.12) and the Fig. 2.6, the linear model of the VLTD-PLL is achieved as illustrated in Fig. 2.7.

Fig. 2.7: VLTD-PLL model [96].

Similar to before, some standard tests are performed to investigate the model accuracy. Fig. 2.8 illustrates the results of this investigation. This figure clearly demonstrates the accuracy of the obtained model in predicting the average transient behavior of the VLDT-PLL.

Fig. 2.8: A comparison between the VLTD-PLL and its model under (a) a 40° phase jump and (b) +2-Hz frequency step change [96].

#### 2.1.3.2 Tuning of the VLTD-PLL

In this part, the tuning procedure of the VLTD-PLL control parameters is briefly discussed. For more details, refer to [96] (Paper 4 in Appendix).

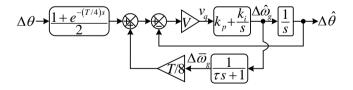

According to the VLTD-PLL model, its closed-loop transfer function may be expressed as

$$G_{cl}(s) = \frac{\Delta \hat{\theta}(s)}{\Delta \theta(s)} = \frac{1 + e^{\frac{-Ts}{4}}}{2} \frac{V(\tau s + 1)(k_p s + k_i)}{(s^2 + Vk_p s + Vk_i)(\tau s + 1) - \frac{T}{8}Vs(k_p s + k_i)}.$$

(2.13)

Selecting  $k_p/k_i = \tau$  results in a pole-zero cancellation and simplifies (2.13) as

$$G_{cl}(s) = \frac{1 + e^{-(T/4)s}}{2} \frac{Vk_p s + Vk_i}{s^2 + V(k_p - k_i T/8)s + Vk_i}.$$

(2.14)

Now, by defining  $V(k_p - k_i T/8) = 2\zeta \omega'_n$  and  $Vk_i = (\omega'_n)^2$ , where  $\zeta$  is the damping factor and  $\omega'_n$  is the natural frequency, the VLTD-PLL proportional and integrator gains may be expressed as

$$k_{p} = \frac{\left(\omega'_{n}T/8 + 2\zeta\right)\omega'_{n}}{V}$$

$$k_{i} = \frac{\left(\omega'_{n}\right)^{2}}{V}$$

$$\tau = \frac{k_{p}}{k_{i}} = \frac{T}{8} + \frac{2\zeta}{\omega'_{n}}.$$

(2.15)

Here, an optimum damping factor, i.e.,  $\zeta = 0.707$ , and  $\omega'_n = 2\pi 20$  rad/s are chosen which, according to (2.15), results in  $k_p = 217$ ,  $k_i = 15791$  and  $\tau = 0.01375$ .

#### 2.1.4. ADAPTIVE TD-PLL (ATD-PLL)

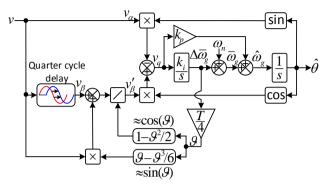

The VLTD-PLL structure, as mentioned before, solves all errors of the standard TD-PLL. Its implementation, however, requires adjusting the length of a delay. This procedure almost always involves the fractional delay approximation. This task demands to apply interpolation methods, which makes the VLTD-PLL implementation a bit complicated. The aim of this part is presenting a PLL structure with exactly the same performance as the VLTD-PLL, but without the requirement for adapting its delay length. The design procedure is briefly presented in what follows. For a more detailed design procedure, refer to [97] (Paper 5 in Appendix).

As the starting point of the design procedure, consider the standard TD-PLL structure, which is shown in Fig. 2.1. By considering (2.1) as its input signal, the fictitious signal  $v_{\beta}$  (i.e., the output of the fixed-length quarter cycle delay) may be expressed as

$$v_{\beta}(t) = V \cos\left(\theta - \frac{\omega_{g}T}{4}\right). \tag{2.16}$$

Considering the definition of the grid frequency as a perturbation around the nominal frequency, i.e.,  $\omega_g = \omega_n + \Delta \omega_g$ , (2.16) can be rewritten as

$$v_{\beta}(t) = V \sin\left(\theta - \frac{\Delta\omega_{g}T}{4}\right) = -V \cos(\theta) \sin\left(\frac{\Delta\omega_{g}T}{4}\right) + V \sin(\theta) \cos\left(\frac{\Delta\omega_{g}T}{4}\right). \tag{2.17}$$

The highlighted (bold) term is the required orthogonal signal. This signal, according to (2.17), may be expressed as a function of the single-phase input signal ( $\nu_{\alpha}$ ) and the fixed-length quarter cycle delay output ( $\nu_{\beta}$ ) as follows

$$v_{\beta}'(t) = \frac{v_{\alpha}(t)\sin\left(\frac{\Delta\omega_{g}T}{4}\right) + v_{\beta}(t)}{\cos\left(\frac{\Delta\omega_{g}T}{4}\right)}.$$

(2.18)

Based on (2.18) and the standard TD-PLL structure (Fig. 2.1), the proposed PLL structure, which is briefly called the adaptive TD-PLL (ATD-PLL), is obtained as

illustrated in Fig. 2.9. Notice that the output of the PI regulator integrator is considered as an estimation of  $\Delta \omega_{\sigma}$  for the calculation of  $v'_{\beta}$ .

Fig. 2.9: Block diagram representation of the proposed ATD-PLL [97].

Notice also that, as the grid frequency variations are limited in practice, the trigonometric terms in the frequency feedback loop are approximated by the first two terms of their Taylor series expansions.

#### 2.1.4.1 Modeling and Tuning of the ATD-PLL

In this part, the modeling and tuning procedure of the ATD-PLL are briefly discussed. For more details, refer to [97] (Paper 5 in Appendix).

By considering (2.1) as the input signal, the signal  $v'_{\beta}$  in the ATD-PLL structure may be expressed as

$$v_{\beta}'(t) = \frac{V\cos(\theta)\sin\left(\frac{\Delta\bar{\omega}_{g}T}{4}\right) + V\sin\left(\theta - \frac{\Delta\omega_{g}T}{4}\right)}{\cos\left(\frac{\Delta\bar{\omega}_{g}T}{4}\right)}.$$

(2.19)

Using (2.19), the signal  $v_a$  in the PI regulator input can be expressed as

$$v_{q}(t) = \frac{V}{2} \left[ \sin(\theta - \hat{\theta}) + \tan\left(\frac{\Delta \overline{\omega}_{g} T}{4}\right) \cos(\theta - \hat{\theta}) + \frac{\sin\left(\theta - \frac{\Delta \omega_{g} T}{4} - \hat{\theta}\right)}{\cos\left(\frac{\Delta \overline{\omega}_{g} T}{4}\right)} \right]$$