**Doctoral Thesis**

# Self-Calibrated, Low-Jitter and Low-Reference-Spur Injection-Locked Clock Multipliers

Seyeon Yoo

Department of Electrical Engineering

Graduate School of UNIST

2020

## Self-Calibrated, Low-Jitter and Low-Reference

Spur Injection-Locked Clock Multipliers

Seyeon Yoo

Department of Electrical Engineering

Graduate School of UNIST

# Self-Calibrated, Low-Jitter and Low-Reference Spur Injection-Locked Clock Multiplier

A thesis/dissertation submitted to the Graduate School of UNIST in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Seyeon Yoo

12/04/2019

Approved by

Advisor Kyuho Lee

## Self-Calibrated, Low-Jitter and Low-Reference Spur Injection-Locked Clock Multiplier

Seyeon Yoo

This certifies that the thesis/dissertation of Seyeon Yoo is approved.

12/04/2019

Advisor: Professor Kyuho Lee

Thesis Committee Member: Professor Jaehyouk Choi

" N

Thesis Committee Member: Professor Seong-Jin Kim

RKZ

Thesis Committee Member: Professor Kyung Rok Kim

Thesis Committee Member: Professor Hyun Jong Yang

#### Abstract

This dissertation focuses primarily on the design of calibrators for the injection-locked clock multiplier (ILCM). ILCMs have advantage to achieve an excellent jitter performance at low cost, in terms of area and power consumption. The wide loop bandwidth (BW) of the injection technique could reject the noise of voltage-controlled oscillator (VCO), making it thus suitable for the rejection of poor noise of a ring-VCO and a high frequency *LC*-VCO. However, it is difficult to use without calibrators because of its sensitiveness in process-voltage-temperature (PVT) variations. In Chapter 2, conventional frequency calibrators are introduced and discussed. This dissertation introduces two types of calibrators for low-power high-frequency *LC*-VCO-based ILFMs in Chapter 3 and Chapter 4 and high-performance ring-VCO-based ILCM in Chapter 5.

First, Chapter 3 presents a low power and compact area LC-tank-based frequency multiplier. In the proposed architecture, the input signals have a pulsed waveform that involves many high-order harmonics. Using an LC-tank that amplifies only the target harmonic component, while suppressing others, the output signal at the target frequency can be obtained. Since the core current flows for a very short duration, due to the pulsed input signals, the average power consumption can be dramatically reduced. Effective removal of spurious tones due to the damping of the signal is achieved using a limiting amplifier. In this work, a prototype frequency tripler using the proposed architecture was designed in a 65 nm CMOS process. The power consumption was 950  $\mu$ W, and the active area was 0.08 mm<sup>2</sup>. At a 3.12 GHz frequency, the phase noise degradation with respect to the theoretical bound was less than 0.5 dB.

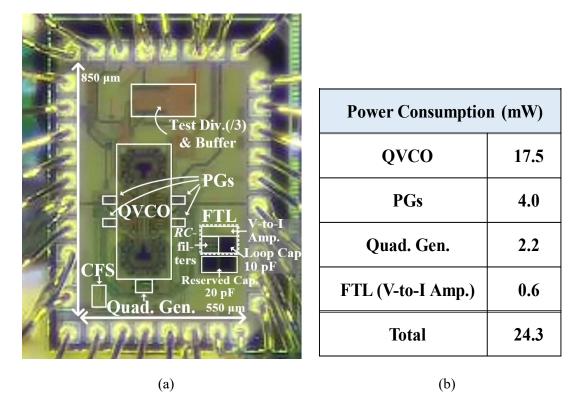

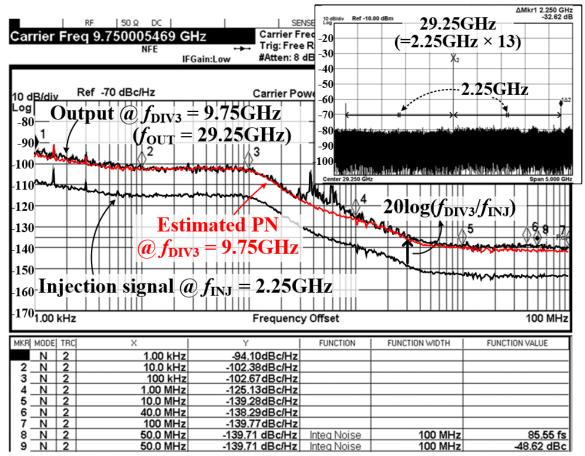

Second, Chapter 4 presents an ultra-low-phase-noise ILFM for millimeter wave (mm-wave) fifthgeneration (5G) transceivers. Using an ultra-low-power frequency-tracking loop (FTL), the proposed ILFM is able to correct the frequency drifts of the quadrature voltage-controlled oscillator of the ILFM in a real-time fashion. Since the FTL is monitoring the averages of phase deviations rather than detecting or sampling the instantaneous values, it requires only 600µW to continue to calibrate the ILFM that generates an mm-wave signal with an output frequency from 27 to 30 GHz. The proposed ILFM was fabricated in a 65-nm CMOS process. The 10-MHz phase noise of the 29.25-GHz output signal was -129.7 dBc/Hz, and its variations across temperatures and supply voltages were less than 2 dB. The integrated phase noise from 1 kHz to 100 MHz and the rms jitter were–39.1 dBc and 86 fs, respectively.

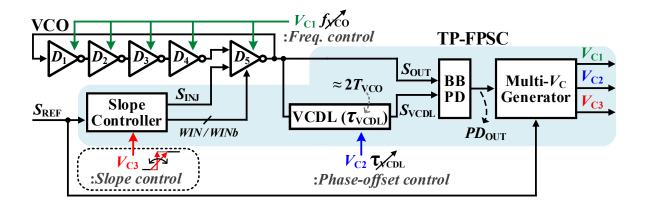

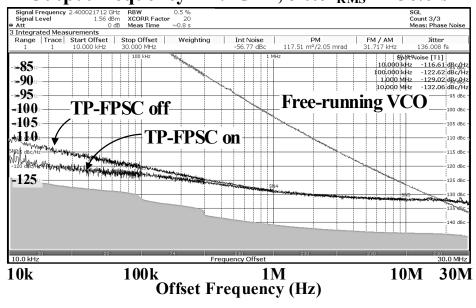

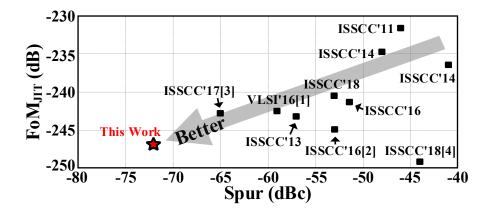

Third, Chapter 5 presents a low-jitter, low-reference-spur ring voltage-controlled oscillator (ring VCO)-based ILCM. Since the proposed triple-point frequency/phase/slope calibrator (TP-FPSC) can accurately remove the three root causes of the frequency errors of ILCMs (i.e., *frequency drift, phase*)

offset, and slope modulation), the ILCM of this work is able to achieve a low-level reference spur. In addition, the calibrating loop for the *frequency drift* of the TP-FPSC offers an additional suppression to the in-band phase noise of the output signal. This capability of the TP-FPSC and the naturally wide bandwidth of the injection-locking mechanism allows the ILCM to achieve a very low RMS jitter. The ILCM was fabricated in a 65-nm CMOS technology. The measured reference spur and RMS jitter were -72 dBc and 140 fs, respectively, both of which are the best among the state-of-the-art ILCMs. The active silicon area was 0.055 mm<sup>2</sup>, and the power consumption was 11.0 mW.

## Contents

| ABSTRACTV                                                                          |

|------------------------------------------------------------------------------------|

| CONTENTS                                                                           |

| LIST OF FIGURESIX                                                                  |

| LIST OF TABLES                                                                     |

| Chapter 1. Introduction                                                            |

| 1.1. Motivation1                                                                   |

| 1.2. Dissertation Organization                                                     |

| Chapter 2. Prior ILCMs with Real-Time Frequency Calibration                        |

| 2.1. ILCMs with a PLL-Based Frequency Calibrator4                                  |

| 2.2. ILCMs with a Frequency Calibrator Using a Replica-VCO or a Replica-Cell-Based |

| Delay Line                                                                         |

| 2.3. ILCMs with a Period-Detector-Based Calibrator7                                |

| 2.4. ILCMs with a Frequency Calibrator Detecting Phase Shift9                      |

| 2.4.1. Phase-Shift Detector Using a TDC10                                          |

| 2.4.2. Phase-Shift Detector Using a Pulse Gating Technique                         |

| 2.4.3. Phase-Shift Detector Using Delay Cells12                                    |

| Chapter 3. An Ultra-Low Power and Compact LC-Tank-Based Frequency Tripler          |

| 3.1. Motivation                                                                    |

| 3.2. Circuit Designs                                                               |

| 3.3. Measurement Results                                                           |

| 3.4. Discussion                                                                    |

| Chapter 4. A Low-IPN mm-Wave Injection-Locked Frequency Multiplier for 5G22        |

| 4.1. Motivation                                                                    |

| 4.2. Limits of Prior Frequency-Tracking-Loop Architectures for mm-Wave ILFMs25     |

| 4.3. Proposed ILFM With an Ultra-Low-Power FTL Using the Averages of the Phase     |

| Deviations                                                                         |

| 4.3.1. Overall Architecture                                                        |

| 4.3.2. V-to-I Amplifier and the QVCO                                               |

#### SCIENCE AND TECHNOLOGY

| 4.3.3. Quadrature Generator, the Pulse Generator, and the Switched <i>RC</i> -filters35 |

|-----------------------------------------------------------------------------------------|

| 4.3.4. Coarse Frequency Selector                                                        |

| 4.4. Analysis of Phase Noise and Static Frequency Offset                                |

| 4.4.1. Phase Noise of the Proposed ILFM                                                 |

| 4.4.2. Static Frequency Offset by Mismatch Effects in the FTL42                         |

| 4.5. Experimental Results44                                                             |

| 4.6. Discussion                                                                         |

| Chapter 5. A Low-Jitter and Low-Reference-Spur Ring-VCO-Based Injection-Locked          |

| Clock Multiplier Using a Triple-Point Background Calibrator                             |

| 5.1. Motivation                                                                         |

| 5.2. Analysis on Frequency Error Generation Mechanisms of Root Causes and Limits of     |

| Conventional Calibrators                                                                |

| 5.2.1. Three Root Causes of Frequency Errors and Limits of Conventional                 |

| Calibrators                                                                             |

| 5.2.2. How Slope Modulation Generates Phase Error and thus Frequency Error60            |

| 5.3. ILCM Using the Proposed Background TP-FPSC63                                       |

| 5.3.1. Overall Architecture of the ILCM with the Background TP-FPSC63                   |

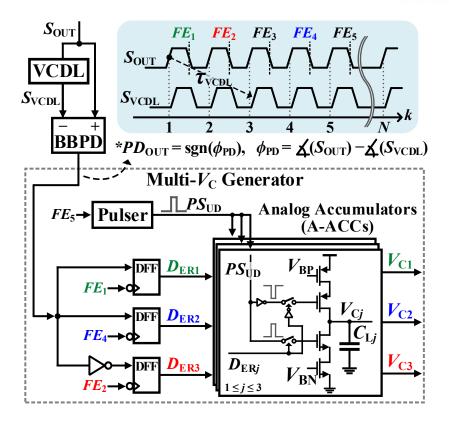

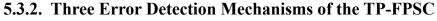

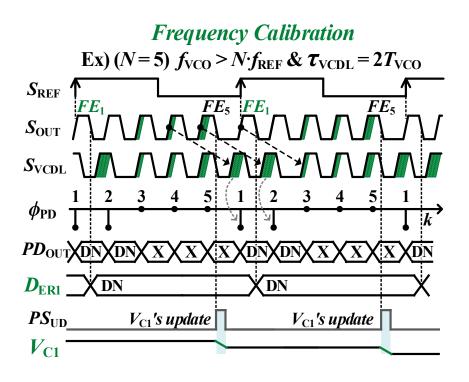

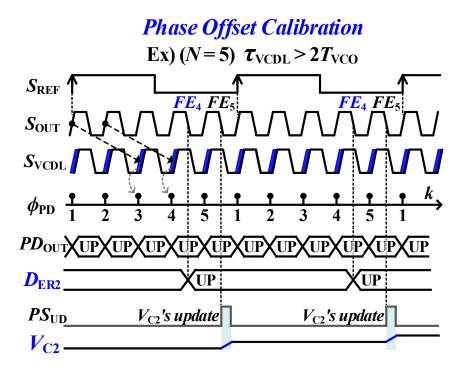

| 5.3.2. Three Error Detection Mechanisms of the TP-FPSC65                                |

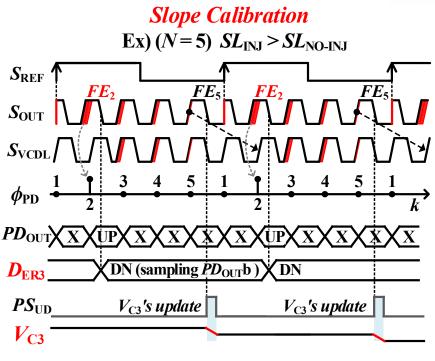

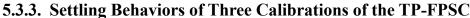

| 5.3.3. Settling Behaviors of Three Calibrations of the TP-FPSC                          |

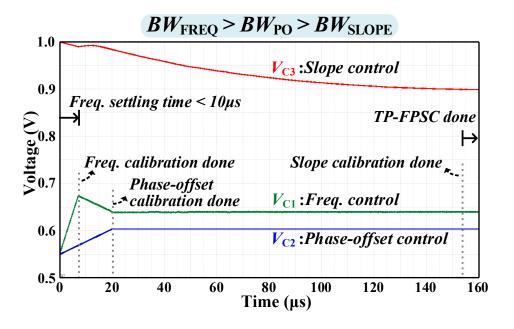

| 5.4. Design of Sub-Building Blocks: Slope Controller, VCO, and VCDL69                   |

| 5.5. Experimental Results71                                                             |

| 5.6. Discussion                                                                         |

| Chapter 6. Conclusion                                                                   |

| REFERENCES                                                                              |

| ACKNOWLEDGMENTS                                                                         |

| PUBLICATIONS                                                                            |

## **List of Figures**

| Figure 1.1. (a) phase realignment mechanism of the injection locking technique (b) reference spur over                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| <i>f</i> <sub>ERR</sub> 's2                                                                                                                |

| Figure 2.1. ILCM with a conventional PLL-based frequency calibrator                                                                        |

| Figure 2.2. ILCM with a frequency calibrator using a replica-VCO or a replica-cell-based delay line. 5                                     |

| Figure 2.3. (a) ILCM with a period-detector-based calibrator. (b) Timing diagram                                                           |

| Figure 2.4. (a) ILCM with a TDC-based frequency calibrator. (b) Timing diagram                                                             |

| Figure 2.5. (a) ILCM with a pulse gating frequency calibrator. (b) Timing diagram                                                          |

| Figure 2.6. (a) ILCM with a frequency calibrator using delay cells. (b) Timing diagram12                                                   |

| Figure 3.1. Frequency triplers: (a) conventional self-mixing architecture [35] (b) proposed architecture                                   |

| Figure 3.2. Overall architecture of the proposed <i>LC</i> -based frequency multiplier using a pulsed input signal                         |

| Figure 3.3. Waveforms of the output of the proposed architecture with a different <i>Q</i> from (1) and simulations                        |

| Figure 3.4. Reference spurs at the outputs of the <i>LC</i> -resonator and the D-to-S amplifier, $(V_0 + - V_0 -)$                         |

| and $V_{\text{OUT}}$ , respectively                                                                                                        |

| Figure 3.5. Chip micrograph of the proposed frequency tripler                                                                              |

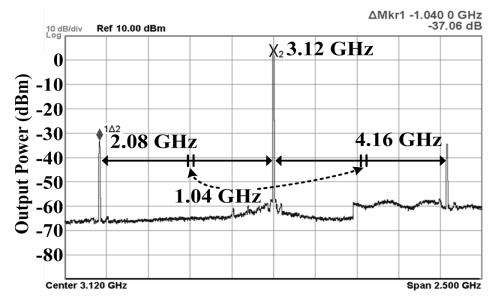

| Figure 3.6. Measured spectrum of the 3.12 GHz output signal of the proposed frequency tripler 18                                           |

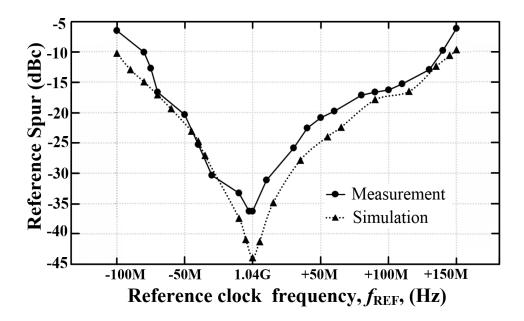

| Figure 3.7. Measured and simulated reference spur level with respect to the input reference clock                                          |

| frequency19                                                                                                                                |

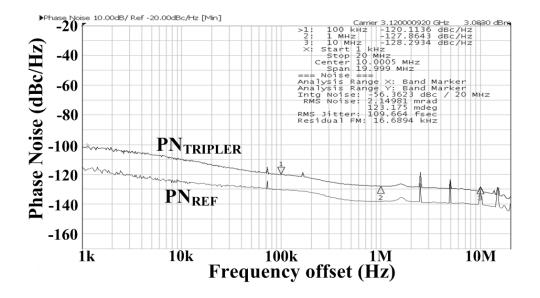

| Figure 3.8. Measured phase noise of the 3.12 GHz output signal and the 1.04 GHz reference clock19                                          |

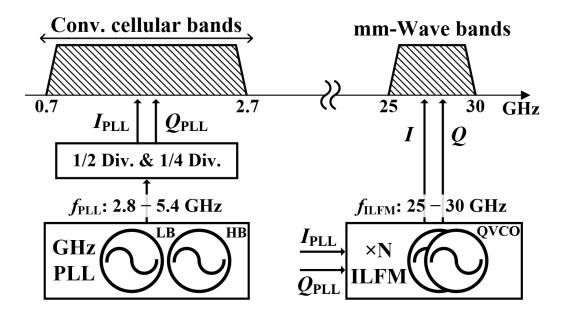

| Figure 4.1. LO generation with a gigahertz-range PLL and a cascaded mm-wave ILFM for multi-band and multi-standard cellular communications |

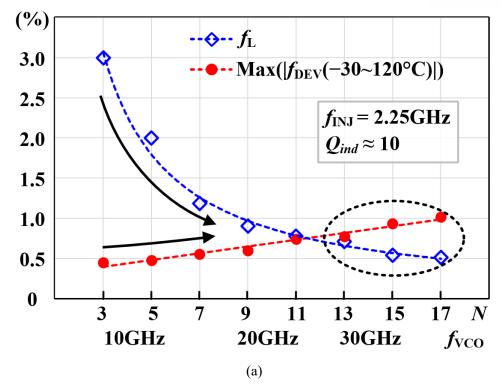

| Figure 4.2. (a) Lock range $f_L(\%)$ and maximum deviation of the free-running frequency $f_{DEV}(\%)$ over                                |

| temperature of an <i>LC</i> -VCO injected by a 2.25-GHz tone, when the target harmonic factor $N$ is                                       |

| changed. (b) Degradations of the10-MHz phase noise with respect to $f_{\text{DEV}}$ for different N's26                                    |

| Figure 4.3. ILFMs with different FTLs using (a) a replica-VCO; (b) a TDC; (c) a mixer; (d) an envelope                                     |

| detector                                                                                                                                   |

| Figure 4.4. (a) Conceptual diagram of the cascaded architecture of an mm-wave LO generator. (b)                                            |

| Principle of the proposed frequency-tracking loop (FTL)                                                                                    |

| Figure 4.5. Proposed mm-wave ILFM with the ultra-low power FTL. (a) Overall architecture. (b)                                              |

| Conceptual timing diagram                                                                                                                  |

| Figure 4.6. Schematics of (a) V-to-I amplifier and (b) QVCO                                                                                |

| Figure 4.7. (a) Schematics of the CFS. (b) Conceptual timing diagram of the CFS                                                            |

#### SCIENCE AND TECHNOLOGY

| Figure 4.8. Noise model of the proposed mm-wave ILFM                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.9. NTFs of building blocks based on (5) – (9). (b) Estimated phase noise from the noise model.                                                      |

| Figure 4.10. Linear model of static frequency offset due to mismatch effect of FTL                                                                           |

| Figure 4.11. (a) Die photograph. (b) Power-breakdown table                                                                                                   |

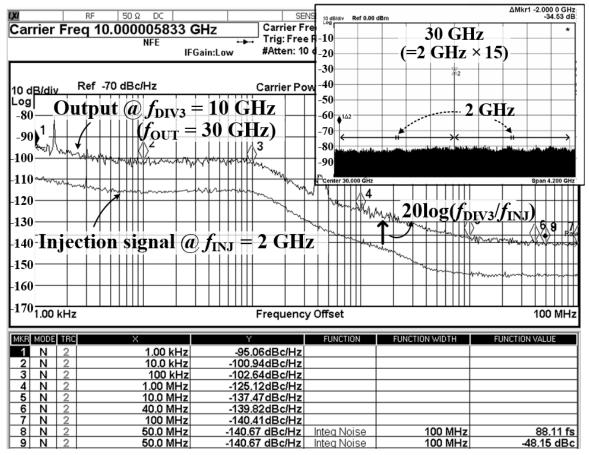

| Figure 4.12. Measured spectrum and phase noise of the output signal with 29.25 GHz ( $f_{INJ} = 2.25$ GHz,                                                   |

| N = 13) with estimated phase noise from the noise model in Section 4.445                                                                                     |

| Figure 4.13. Measured spectrum and phase noise of the output signal with 30.0 GHz ( $f_{INJ} = 2.0$ GHz, $N = 15$ )                                          |

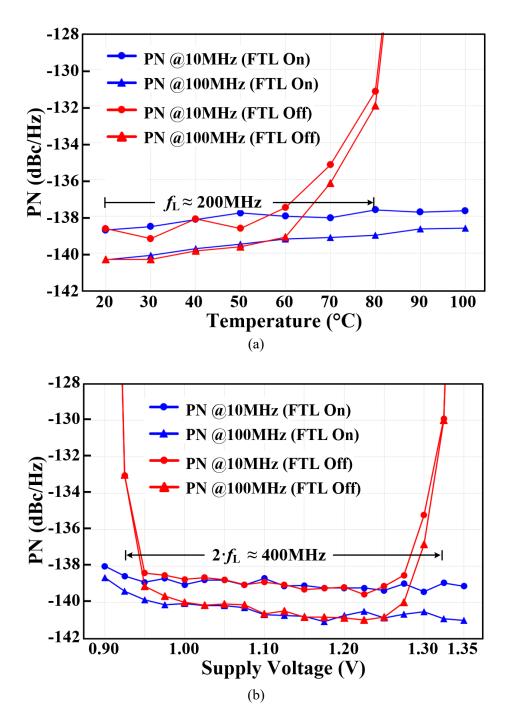

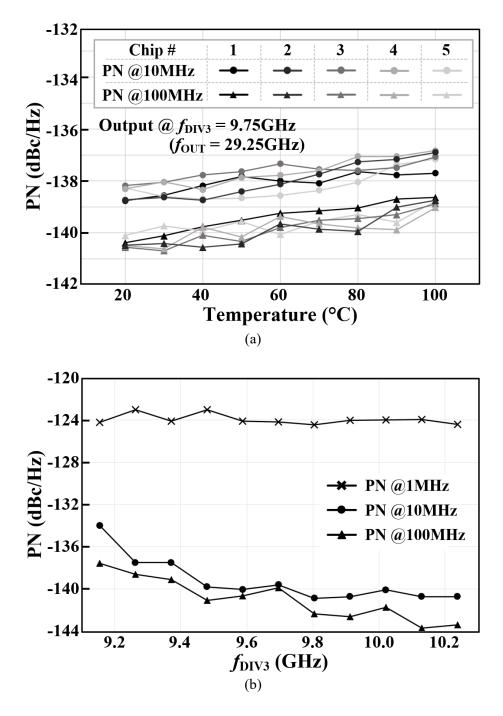

| Figure 4.14. Measured phase noise at the frequency of 9.75 GHz (29.25 GHz /3) over (a) temperatures                                                          |

| and (b) supply-voltages, when the FTL was on or off                                                                                                          |

| Figure 4.15. Measured phase noise at $f_{DIV3}$ across (a) temperatures for five different chips and (b) output                                              |

| frequencies from 27.4 to 30.8 GHz ( $f_{INJ}$ changed with a fixed N of 13)                                                                                  |

| Figure 5.1 Level of reference spur with respect to $f_{\text{ERR}}$                                                                                          |

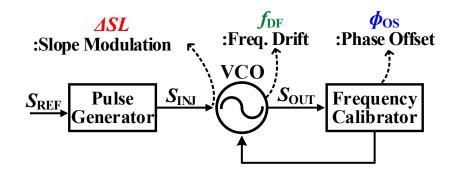

| Figure 5.2. Three causes of the frequency error in ILCMs                                                                                                     |

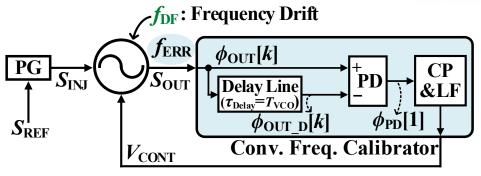

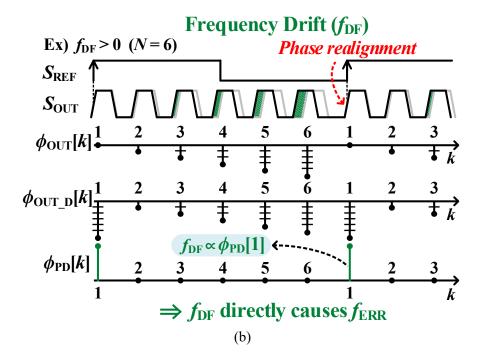

| Figure 5.3. (a) First cause of $f_{ERR}$ in ILCMs, i.e., <i>frequency drift</i> ; (b) mechanism of the generation of $f_{ERR}$ due to <i>frequency drift</i> |

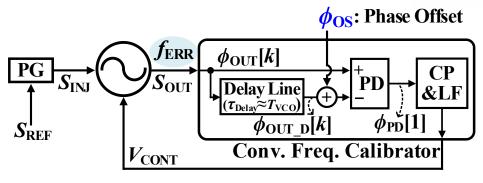

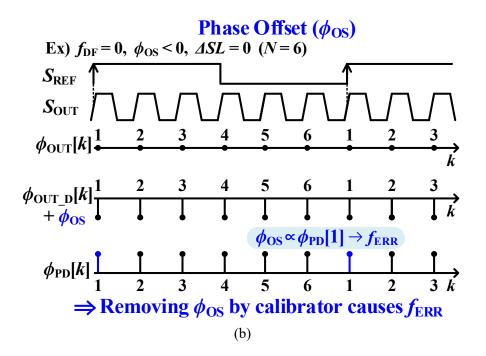

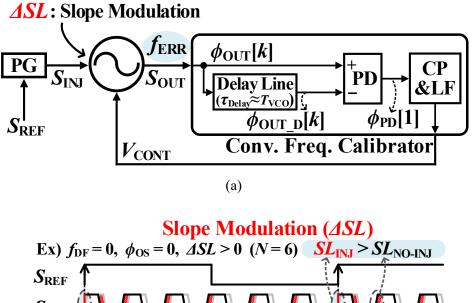

| Figure 5.4. (a) Second of $f_{ERR}$ , i.e., <i>phase offset</i> , in conventional frequency calibrators; (b) mechanisms                                      |

| of <i>f</i> <sub>ERR</sub> generation due to <i>phase offset</i>                                                                                             |

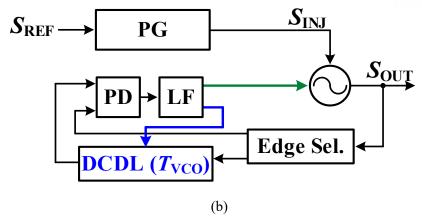

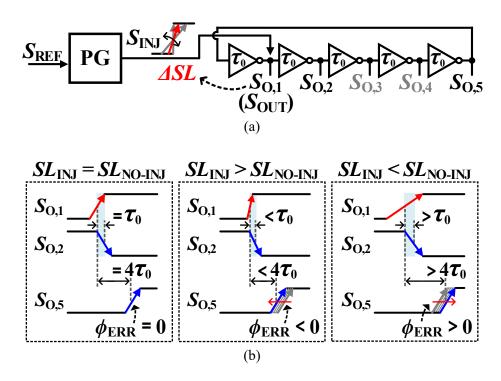

| Figure 5.6. (a) Third causes of $f_{ERR}$ , i.e., <i>slope modulation</i> , in conventional frequency calibrators; (b)                                       |

| mechanisms of <i>f</i> <sub>ERR</sub> generation due to <i>slope modulation</i>                                                                              |

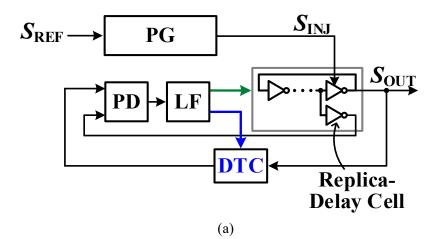

| Figure 5.5. Conventional frequency calibrators for removing $f_{DF}$ & $\phi_{OS}$ based on (a) DTC; and (b) DCDL.                                           |

| Figure 5.7. Mechanism of the <i>slope modulation</i> generating phase shift in $S_{OUT}$ (a) five-stage ring VCO                                             |

| having the injection of $S_{INJ}$ ; (b) difference in slopes fades after a chain of inverters, but the phase shift remains                                   |

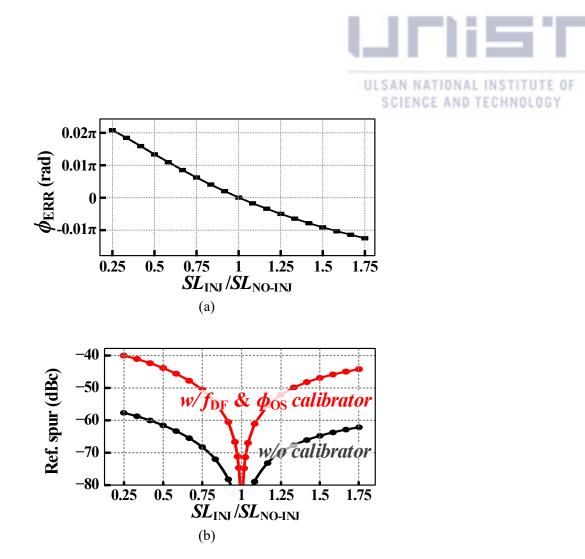

| Figure 5.8. (a) Simulated phase shifts due to the <i>slope modulation</i> assuming neither $f_{DF}$ nor $\phi_{OS}$ without                                  |

| any calibrators; (b) simulated reference spur with a calibrator removing $f_{\rm DF}$ and $\phi_{\rm OS}$ (red) or without                                   |

| any calibrators (black)61                                                                                                                                    |

| Figure 5.9. Overall architecture of the proposed ILCM with the triple-point frequency/phase/slope                                                            |

| calibrator (TP-FPSC)                                                                                                                                         |

| Figure 5.10. Implementation of TP-FPSC                                                                                                                       |

| Figure 5.11. Three causes detection mechanisms of the TP-FPSC; (a) <i>frequency drift</i> , (b) <i>phase offset</i> ,                                        |

| and (c) <i>slope modulation</i>                                                                                                                              |

| Figure 5.12. The settling behaviors of three control voltages in the TP-FPSC                                                                                 |

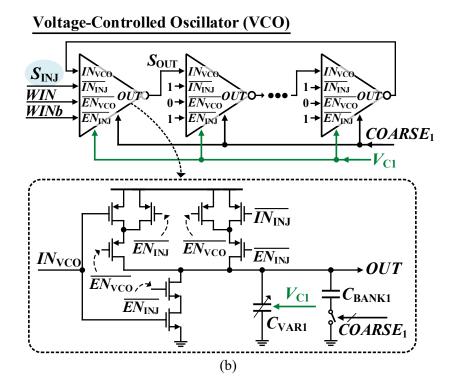

| Figure 5.13. Schematics of (a) slope controller, (b) VCO, and (c) VCDL70                                                                                     |

#### SCIENCE AND TECHNOLOGY

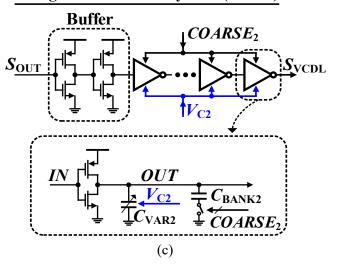

| Figure 5.14. (a) Die photograph. (b) Power-breakdown table                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------|

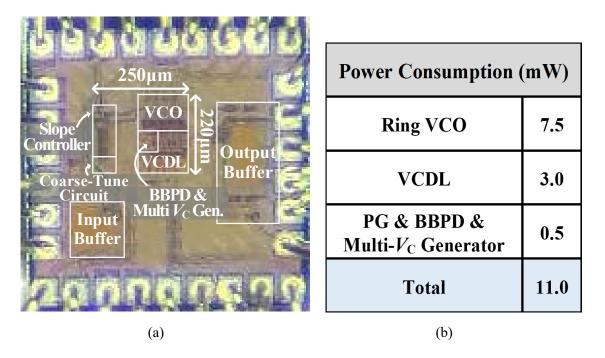

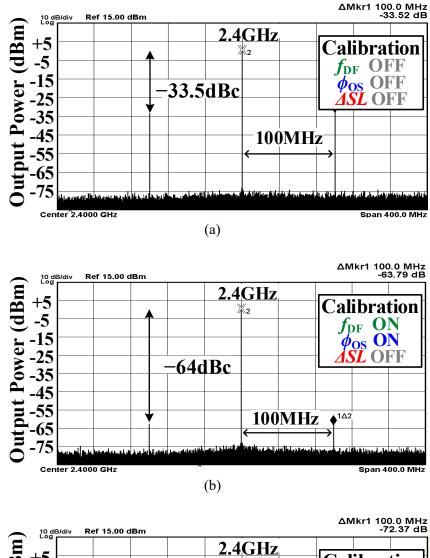

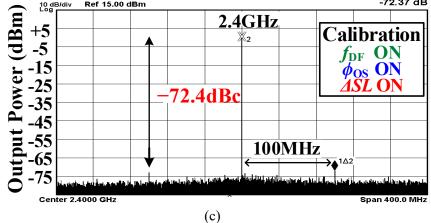

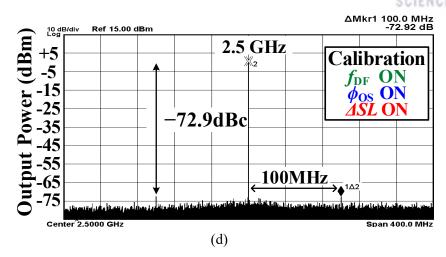

| Figure 5.15. Measured spectrum of the output signal with a frequency of 2.4 GHz, when (a) TP-FPSC                                 |

| was turned off, (b) $f_{\rm DF}$ and $\phi_{\rm OS}$ calibrations were turned on, but $\Delta SL$ calibration was turned off, (c) |

| TP-FPSC was fully turned on. (d) Measured spectrum of the output signal with 2.5 GHz73                                            |

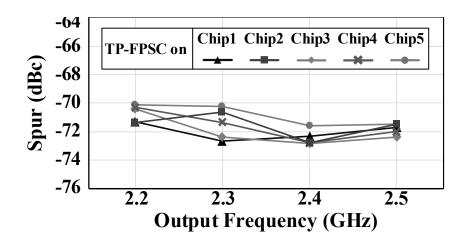

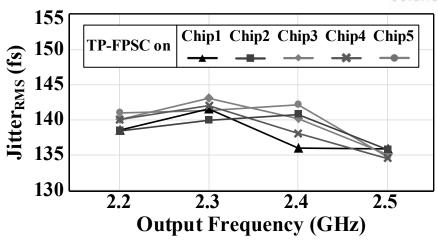

| Figure 5.16. Variations of reference spurs over output frequencies in five different sample chips73                               |

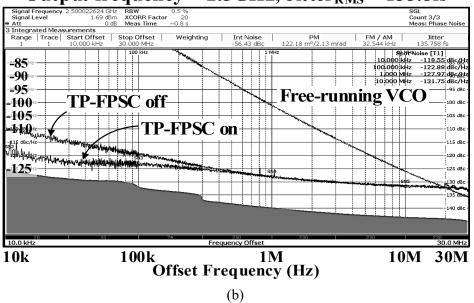

| Figure 5.17. Measured phase noise, when the TP-FPSC was turned on and off at (a) 2.4 GHz and; (b)                                 |

| 2.5 GHz                                                                                                                           |

| Figure 5.18. Variations of integrated RMS-jitter over output frequencies in five different sample chips.                          |

|                                                                                                                                   |

|                                                                                                                                   |

Figure 5.19. Benchmark of performances of this work and state-of-the-art ring-VCO-based ILCMs. 75

## List of Tables

| Table 1. Comparison with State-of-the-Art Frequency Triplers        | .20  |

|---------------------------------------------------------------------|------|

| Table 2. Performance Comparison with State-of-the-Art mm-Wave ILFMs | . 50 |

| Table 3 Comparison with Ring-VCO-Based ILCMs                        | .76  |

### Chapter 1.

#### Introduction

#### 1.1. Motivation

For modern high-speed digital systems, especially mobile applications, the demand for further improvement in the performance of the jitter of clock signals is increasing. To date, phase-locked loop (PLL)-based architectures using a *LC*-type voltage-controlled oscillator (*LC*-VCO) have been used dominantly in many applications for generating high-performance clocks, but their low level of integration has hindered the effort to lower the implementation cost. Recently, multiplying delay-locked-loop (MDLL)-based architectures [1] – [4] and a subharmonic injection-locked clock multiplier (ILCM)-based architectures [5] – [22] are considered as alternatives to conventional PLL-based architectures. Due to the phase realignment mechanism of the injection locking technique, without external loop, those architectures are able to generate precise clock signals with the excellent jitter performance. Although they use a ring-type oscillator or a high-frequency *LC*-VCO that provides poor spectral purity, the ILCM can suppress the jitter of the VCO and provides high-performance clocks. The ILCM is thus widely used in a mm-wave band for low-power multipliers and in a gigahertz-range for compact low-jitter clock multipliers.

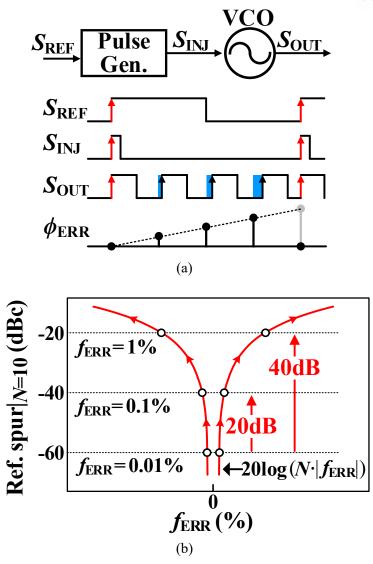

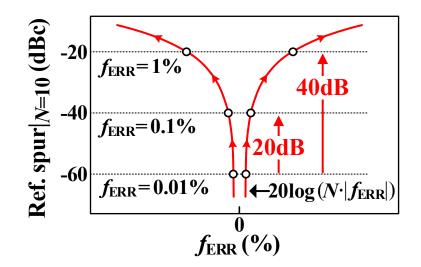

However, an ILCM has critical problems in that excellent performance of the RMS jitter and reference spur can be maintained only when the frequencies of the free-running VCO,  $f_{VCO}$ , is sufficiently close to target harmonic of the injection signal,  $N \cdot f_{REF}$ , where  $f_{REF}$  is the frequency of the reference clock and N is the target harmonic index. In general, the amount of the possible frequency drifts of the VCO due to process-voltage-temperature (PVT) variations is much larger than the lock range of the injection. If the frequency drift is out of the locking range, the ILCM will fail in the lock acquisition [5]. For an ILCM to stay within the lock range,  $f_{VCO}$  can be adjusted to be close to  $N \cdot f_{REF}$ . Nonetheless, ILCMs still suffer from the high level of reference spur, caused by the periodic phase-shift (or deterministic jitter) of the VCO, as shown in Fig. 1.1(a), when it is injection-locked. This is because the level of the reference spur sharply increases as  $f_{VCO}$  deviates from  $N \cdot f_{REF}$ , i.e., SpurdBe  $\approx 20\log(N \cdot |f_{ERR}|)$  where  $f_{ERR} = (f_{VCO} - N \cdot f_{REF})/(N \cdot f_{REF})$  [6]. Fig. 1.1(b) shows, when N is 10, as  $\alpha$  increases to just 0.1%, the spur-level rises exponentially by 20 dB and reaches -40 dBc. Consequently, to minimize not only phase noise, but also the reference spur in ILCMs, they need to be required to have

Figure 1.1. (a) phase realignment mechanism of the injection locking technique (b) reference spur over  $f_{\text{ERR}}$ 's

a very precise frequency calibrator.

In this dissertation, we propose two designs of frequency calibrators. First, we present an ultra-lowpower frequency calibrator for mm-wave ILCMs. Despite the high frequency, the proposed frequency calibrator can correct the drifts of  $f_{VCO}$  and requires low power without the use of high-frequency circuits. It was the first calibrator to calibrate real-time drifts of  $f_{VCO}$  in mm-wave band with ultra-low power consumption of less than 1mW. Second, we present a high-performance versatile calibrator. This versatile calibrator can remove three major causes of  $f_{ERRS}$ , especially calibrating the slope modulation for the first time which is caused by the injection. Thanks to this calibrator, the ILCM achieved the lowest reference spur, while using a small area and little power.

#### 1.2. Dissertation Organization

This dissertation focuses primarily on calibration techniques for ILCMs to generate low-jitter and low-reference-spur signals using a compact silicon area and low power. We introduce the calibration techniques in mm-wave band. Also, we analyze all causes of the frequency error that interfere with the accurate frequency calibration and degrade the performance of the ILCMs. This dissertation is organized as follows:

Chapter 2 introduces and discuss conventional frequency calibrators for ILCMs. The advantages and disadvantages of each structure is explained.

Chapter 3 presents a design of a low-power and compact open-loop ILFM. In this work, due to the pulsed input signals, the core current flows for a very short duration and the average power consumption can be dramatically reduced. In Chapter 3, design consideration on an LC tank of the multiplier and a differential-to-single amplifier are analyzed. We present the measurement results from a prototype chip fabricated in 65-nm CMOS technology.

In Chapter 4, a PVT-robust, low-PN mm-wave band ILFM with an ultra-low-power frequency calibrator is presented. The reason why the frequency drifts of the VCO are critical in mm-wave bands is discussed. Using the noise model of the proposed ILFM, the noise contribution of each building blocks is analyzed. The static frequency offset due to mismatches along the signal paths of the calibrator is also analyzed. The implementation of this work is then explained, and we present the measurement results of a prototype chip fabricated in 65-nm CMOS technology.

Chapter 5 presents a low-rms-jitter and low-reference-spur ring-VCO-based ILCM using a background triple-point frequency/phase/slope calibrator (TP-FPSC). The three causes of frequency errors and the limits of conventional calibrators are discussed. The reference spur caused by *slope modulation* was simulated and analyzed. The architecture and mechanism of the proposed TP-FPSC is explained. Finally, we describe the implementation of the calibrator and the VCO, and we present the measurements results from a prototype chip fabricated in 65-nm CMOS technology.

Finally, Chapter 6 summarizes the proposed works and concludes this dissertation.

### Chapter 2.

### **Prior ILCMs with Real-Time Frequency Calibration**

#### 2.1. ILCMs with a PLL-Based Frequency Calibrator

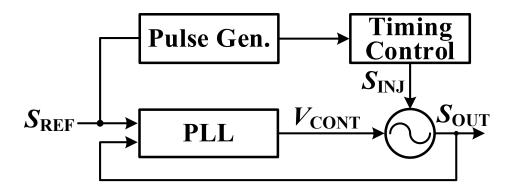

Figure 2.1. ILCM with a conventional PLL-based frequency calibrator.

To date, the most popular method to calibrate the free-running frequency of the VCO is to use the phase-locked loops (PLL). There have thus been some attempts to use the PLL-based frequency calibrator in ILCMs, as shown in Fig. 2.1 [7], [8], [12], [13], [23]. However, these structures have a serious problem with the frequency error,  $f_{ERR}$ , detection. In the conventional PLLs, when  $f_{ERR}$  exists, the phase error is accumulated over the *N* cycles of the VCO signal and this accumulated phase error is detected by the phase detector (PD). However, in the ILCM, the rising edge of  $S_{OUT}$  is realigned by that of  $S_{REF}$ , so this phase error of the VCO is periodically reset to zero by  $S_{INJ}$  before the PLL detects it. as shown in Fig. 1.1(a). Therefore, the PLL-based calibrator is not suitable for the real-time frequency calibration. Even if it could detect the phase error, it is not efficient due to poor detection gain. Although it cannot well prevent the real-time  $f_{ERR}$  of the VCO due to temperature or voltage variations, it can correct static  $f_{ERR}$  due to process variations. Therefore, PLL is mainly used to bring  $f_{VCO}$  into the lock range of the injection locking at the initial stage or start-up stage before the VCO is injection-locked.

2.2. ILCMs with a Frequency Calibrator Using a Replica-VCO or a Replica-Cell-Based Delay Line.

Figure 2.2. ILCM with a frequency calibrator using a replica-VCO or a replica-cell-based delay line.

To detect the real-time frequency drifts of the VCO due to temperature or voltage variations without the effect of injection, a replica-VCO [16] – [20] or a replica-cell-based delay line [24], [25] can be used, as shown in Fig. 2.2. Since the replica-VCO or the replica-delay cells are equally affected by voltage or temperature variations with the main-VCO in the ILCM, the free-running frequency of the main-VCO can be easily detected by monitoring the frequency of the replica-VCO or the delay of the replica-cell-based delay line. The PLL or DLL can bring frequency of the replica-VCO or delay of the replica-cell-based delay line to the target frequency and share the same control-voltage,  $V_{\text{CONT}}$ , to correct the main-VCO's frequency.

These structures have three serious problems. First, the replica-VCO or this delay line are supposed to spend the same power consumption as the main-VCO. Second, mismatches between the main-VCO and replica-VCO limit the accuracy of the calibration and degrades the jitter performance and the level

of the reference spur in the ILCM. Third, the noise of the replica-VCO and main-VCO are uncorrelated to each other; this frequency calibrator thus cannot suppress the noise of the main-VCO. Rather, shared control-voltage,  $V_{\text{CONT}}$ , brings the noise of the replica-VCO into the in-band noise of the output signal in the ILCM. In conclusion, this structure suffers from the issues that the VCO consumes twice the power, while doubling the noise of the VCO.

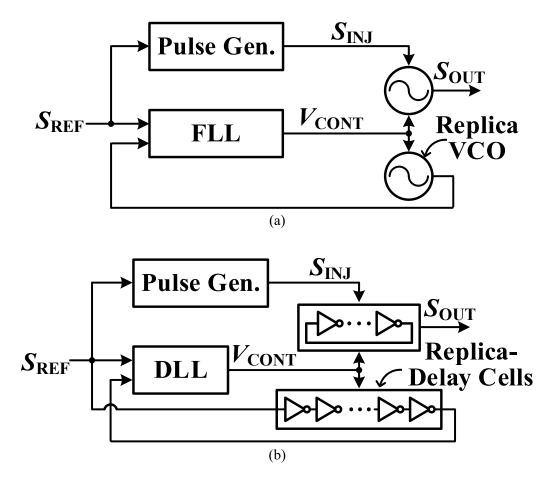

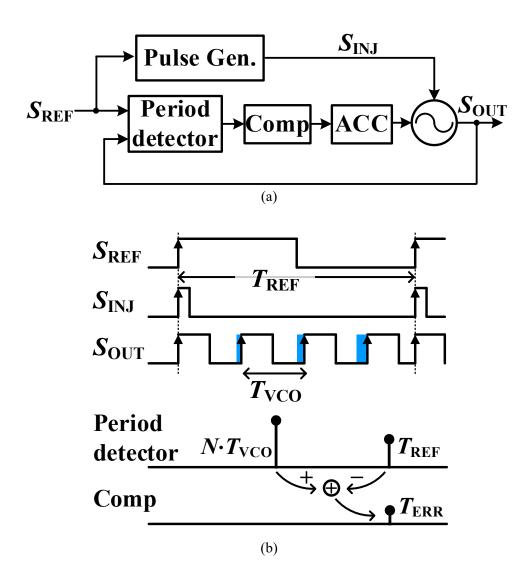

#### 2.3. ILCMs with a Period-Detector-Based Calibrator

Figure 2.3. (a) ILCM with a period-detector-based calibrator. (b) Timing diagram.

The main reason why it is difficult to detect  $f_{ERR}$  in ILCM is that the phase error is reset to zero every reference period. However, during the intervals in which injection pulses are not injected,  $S_{OUT}$  preserves the information of the VCO's free-running period,  $T_{VCO}$ . By comparing *N*-times  $T_{VCO}$  to the period of  $S_{REF}$ ,  $T_{REF}$ ,  $f_{ERR}$  can be detected. Fig. 2.3 shows a period-detector-based calibrator to monitor  $T_{VCO}$  without the effect of the injection [26]. As shown in Fig. 2.3(b), the period detector measures the period of  $N \cdot T_{VCO}$  and  $T_{REF}$  using the charge pump or TDC. Then, the comparator detects the error period,  $T_{ERR}$  and passes this error to the accumulator. By accumulating  $T_{ERR}$ , these structures can correct  $f_{ERR}$  of the injection locked VCO.

These structures have two issues. First, measuring the period is very vulnerable to noise because the

detector must be turned on for a long time. To measure the period of the VCO precisely, the noise of the period detector should be lower than that of the VCO. If not, according to the noise transfer function, the noise of the detector degrades in-band noise of the ILCM. To lower the noise, the detector must use more power than the VCO during measuring periods. Second, since  $T_{\text{ERR}}$  is very small compared to  $T_{\text{REF}}$ , the detection gain of the frequency error is small. For example, the charge-pump-based period detector always have a constant voltage value corresponding to  $T_{\text{REF}}$ . However, the voltage value corresponding to  $T_{\text{ERR}}$  is small compared to the constant voltage value. To get a high detection gain, the current in the charge pump needs to be increased, which is difficult because of the voltage headroom. This small detection gain makes these structures more susceptible to the noise of the loop components.

#### 2.4. ILCMs with a Frequency Calibrator Detecting Phase Shift

As shown in Fig. 1.1, when  $f_{ERR}$  exists, the phase is shifted in proportion to  $f_{ERR}$  by  $S_{INJ}$ . It would be nice if this phase shift,  $\Delta \phi_{shift}$ , could be detected simply, but as mentioned in Chapter 1, it is difficult to do so due to the phase reset. To overcome this issue, recently, there have been many efforts to develop new architectures for the frequency calibration [6], [27] – [31], which use the time-to-digital converter (TDC) [6], pulse-gating technique [27], [28], or delay cells [29] – [31] to detect  $\Delta \phi_{shift}$ .

Phase-shift-detector-based calibrators have two general advantages. First, the in-band VCO noise at low frequency offset such as flicker noise can be further suppressed. As the gate length of the transistor gets smaller and flicker noise worsens, this noise reduction effect is very efficient for producing lowjitter clocks. Second, the detection gain of the frequency error and phase error is large, since the phase shift includes error information accumulated during N VCO cycles. This large detection gain reduces the noise contribution of the loop components at  $S_{OUT}$ , thus reducing the power consumption of the calibrator. However, these architectures still contain disadvantages, which are discussed in this subsection.

#### 2.4.1. Phase-Shift Detector Using a TDC

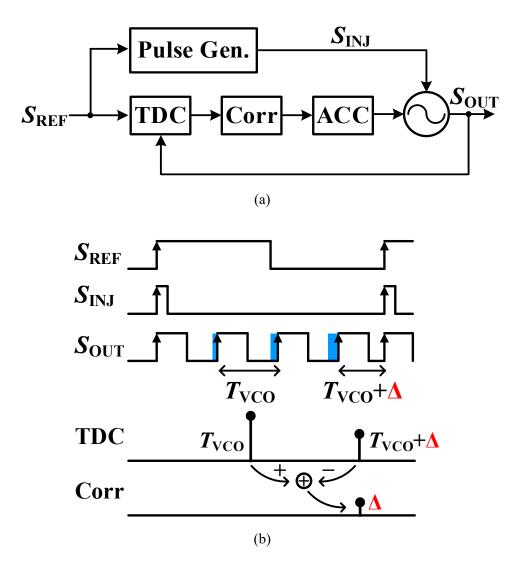

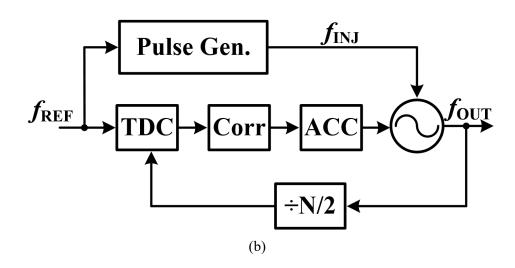

Figure 2.4. (a) ILCM with a TDC-based frequency calibrator. (b) Timing diagram.

Fig. 2.4 shows a frequency calibrator that used a TDC to detect  $f_{ERR}$  [6]. As shown in Fig. 2.4(b), the TDC measures free-running period of the VCO,  $T_{VCO}$ , and the injection-altered period,  $T_{VCO} + \Delta$ . The correlator compares  $T_{VCO}$  to  $T_{VCO} + \Delta$  and generates the error signal  $\Delta$ . By accumulating  $\Delta$ , this calibrator can detect real-time  $f_{ERR}$ .

These structures have two issues. First, to measure the period of the VCO, the TDC has to be turned on for a long time and becomes vulnerable to noise of the TDC. Second, there is a trade-off between the resolution and the power consumption in the TDC. In conclusion, since this phase-shift-detector requires a lot of power to lower the noise of the TDC and increase the resolution of the TDC, it did not achieve good figure of merit (FoM) considering the noise performance and power consumption.

#### 2.4.2. Phase-Shift Detector Using a Pulse Gating Technique

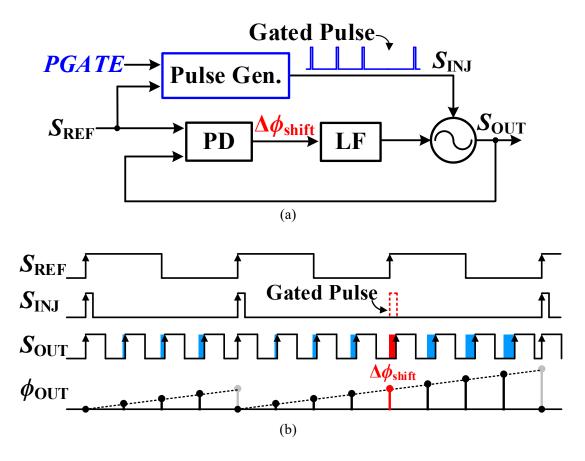

Figure 2.5. (a) ILCM with a pulse gating frequency calibrator. (b) Timing diagram.

Fig. 2.5 shows a frequency calibrator using a pulse gating technique to detect  $f_{ERR}$  [27], [28]. As shown in Fig. 2.5(a), the pulse generator generates an injection pulse signal from rising edge of  $S_{REF}$ depending on a gating signal, *PGATE*. In Fig. 2.5(b), we see how this calibrator detects the phase shift,  $\Delta \phi_{shift}$ , using the gated pulse signal. When the injection pulse is gated, the accumulated phase error of the VCO is not realigned and preserves the phase error, and the PD can thereby detect  $\Delta \phi_{shift}$  and frequency error.

These structures have two problems. First, the VCO's noise reduction effect due to calibrator is decreased because the calibration is possible only when the injection pulse is gated, not every time. Since the bandwidth of the  $f_{ERR}$  and phase error calibration is slow, this calibrator does not effectively remove flicker noise of the VCO. However, frequently gating the injection pulse to widen the bandwidth of the calibration, the effect of the injection will be reduced, and the overall noise also may worsen. Second, the periodical gating of injection could generate in-band spurs, which degrade the noise performance of the ILCM.

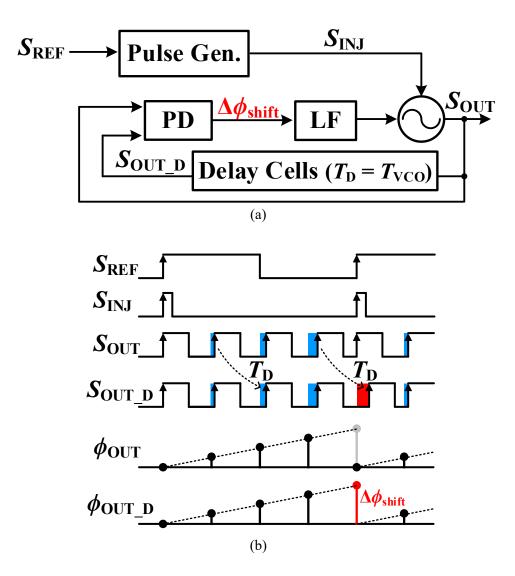

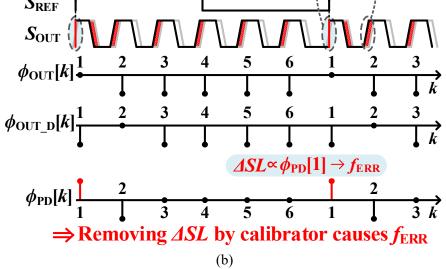

Figure 2.6. (a) ILCM with a frequency calibrator using delay cells. (b) Timing diagram.

Fig. 2.6 shows a frequency calibrator using delay cells to detect  $f_{\text{ERR}}$  [29] – [31]. As shown in Fig. 2.6(a), the delay cells delay  $S_{\text{OUT}}$  by the free-running period of the VCO,  $T_{\text{VCO}}$ , and generate a delayed signal of  $S_{\text{OUT}}$ ,  $S_{\text{OUT}_D}$ . As shown in Fig. 2.6(b), since the delay cells receive and delay the signal of the VCO before injection, they can preserve the intrinsic phase information of the VCO without the effect of the injection. Then, the PD compares the phase difference between  $S_{\text{OUT}}$  and  $S_{\text{OUT}_D}$ , and  $\Delta\phi_{\text{shift}}$  can be detected. Since this method can detect  $f_{\text{ERR}}$  with the simple structure, it requires low power and small silicon area. In addition, the calibrator can detect  $\Delta\phi_{\text{shift}}$  at each reference period, so the bandwidth of the frequency calibration can be wide enough to suppress the flicker noise of the VCO. However, the accuracy of the  $\Delta\phi_{\text{shift}}$  detection could be degraded by the delay error of delay cells and the input offset of the PD, so the additional offset calibration is crucial.

### Chapter 3.

## An Ultra-Low Power and Compact LC-Tank-Based Frequency Tripler

#### **3.1.** Motivation

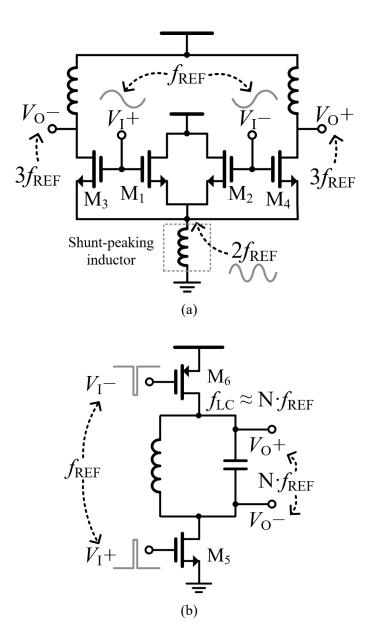

Generating a low phase noise, high frequency signal is one of the most important tasks in designing a modern electronic system. Especially for mobile applications, low-cost implementation, in terms of power consumption and silicon area, must be the primary goal. An open-loop frequency tripler is a good candidate for meeting these design goals without the need for the loop-building blocks of a phase-locked loop (PLL) or a delay-locked loop (DLL)-based architecture. To date, many frequency triplers have been reported [32] – [35]. References [32], [33] presented architectures that use a current-reused subharmonic mixer, but they must have input signals with four quadrature-phases. In the architectures of [34], [35], shown in Fig. 3.1(a), the signal at the second order harmonic frequency was extracted by the shunt-peaking inductor, and it was mixed with the original signal. However, they included multiple area-hungry inductors. Furthermore, [32] - [35] are unsuitable for low-power applications since the transistors in mixers must keep consuming static power due to their sinusoidal inputs.

In this work, we propose a new ultra-low power and compact open-loop frequency multiplier, as shown in Fig. 3.1(b). In the proposed architecture, input signals have a pulsed waveform with a narrow pulse width that includes many high-order harmonics of the reference frequency,  $f_{REF}$ . When the resonant frequency of the *LC*-tank,  $f_{LC}$ , is tuned close to a specific harmonic, the signal component at that harmonic frequency is amplified, while other components are filtered out. Thus, by changing  $f_{LC}$  any different multiplication factors, *N*s, can be obtained. The use of an *LC*-tank as a load to select the target harmonic was presented in frequency doublers [36], [37]. However, as they used differential sinusoidal inputs, only the second harmonic component was available for amplification; moreover, no odd-order harmonics could be present at all. In addition, in the proposed architecture, due to the pulsed input signals that briefly turn on the input transistors, the core current flows for a very short duration. Thus, the average power consumption can be dramatically reduced. The proposed architecture also has

<sup>\* © 2016</sup> IEEE. Part of this chapter is reprinted, with permission, from S. Yoo, S. Choi, T. Seong, and J. Choi, "An Ultra-Low Power and Compact *LC*-Tank-Based Frequency Tripler Using Pulsed Input Signals," in *IEEE Microwave and Wireless Components Letters* (MWCL), vol. 26, no. 2, pp. 140-142, February 2016.

small silicon area, since it includes only one inductor. In this work, a prototype frequency tripler was designed in a 65 nm CMOS technology. Depending on the selection of  $f_{LC}$ , the proposed architecture can be implemented as a frequency multiplier with an arbitrary multiplication factor.

Figure 3.1. Frequency triplers: (a) conventional self-mixing architecture [35] (b) proposed architecture

#### 3.2. Circuit Designs

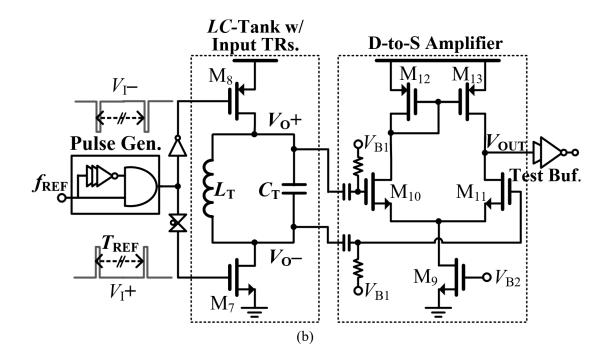

Figure 3.2. Overall architecture of the proposed *LC*-based frequency multiplier using a pulsed input signal

Fig. 3.2 shows the overall architecture of the proposed frequency multiplier, consisting of a pulse generator, an *LC*-tank with the input transistors,  $M_7$  and  $M_8$ , and a differential-to-single (D-to-S) amplifier. The mechanism of the proposed architecture can be easily understood in the time domain as follows. From the reference clock, the pulse generator produces narrow differential pulses, which continue to turn on and off  $M_7$  and  $M_8$ . When  $M_7$  and  $M_8$  are turned on briefly by the pulsed input signals in every reference period, the *LC*-tank receives energy differentially through the closed paths from the supply and the ground. When  $M_7$  and  $M_8$  are turned off, the commuting current in the *LC*-tank generates the output signals. If the loss of the tank were ideally zero, this signal would be sustained permanently. However, due to the finite parallel resistance of the *LC*-tank and the leakages of  $M_7$  and  $M_8$ , the amplitude of the signal decays. Thus, to prevent the amplitude of the signal from being diminished, the  $C_T$  of the tank must be periodically recharged. The decay of the differential magnitude of the output voltages,  $(V_0+ - V_0-)$ , can be estimated from the impulse response of the *LC*-tank, h(t), as

$$h(t) = \frac{1}{C_{\rm T}} \cdot \exp\left(-\frac{\pi f_{\rm LC}}{Q} \cdot t\right) \cdot \left[\cos\left(\pi\sqrt{4 - 1/Q^2} \cdot f_{\rm LC} \cdot t\right) - \frac{\sin\left(\pi\sqrt{4 - 1/Q^2} \cdot f_{\rm LC} \cdot t\right)}{\sqrt{4Q^2 - 1}}\right]$$

(1)

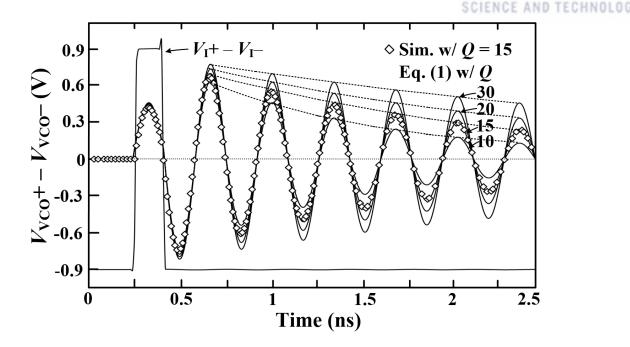

Figure 3.3. Waveforms of the output of the proposed architecture with a different Q from (1) and simulations

where Q, and  $f_{LC}$  are the loaded Q-factor and the LC-resonant frequency, respectively. Fig. 3.3 shows the waveforms of the convolution of h(t) and a rectangular pulse with a pulse width of  $1/2f_{LC}$  and an amplitude of 0.9 V, when the  $f_{LC}$  is 3.12 GHz and Q is varied from 10 to 30. When Q is 30, the decay of the amplitude is slow since the time constant of h(t) is large, but it becomes gradually steeper as Qdecreases. This is because the energy stored in the LC-tank dissipates faster as the tank loss increases. Thus, if the Q of the tank is maximized, the frequency of the recharging process can be reduced, which implies that a high multiplication number is possible. Fig. 3.3 also shows the differential output voltage,  $(V_O + - V_O -)$ , from the transient simulation with Q of 15, which is matched precisely to the theoretical estimation, based on (1).

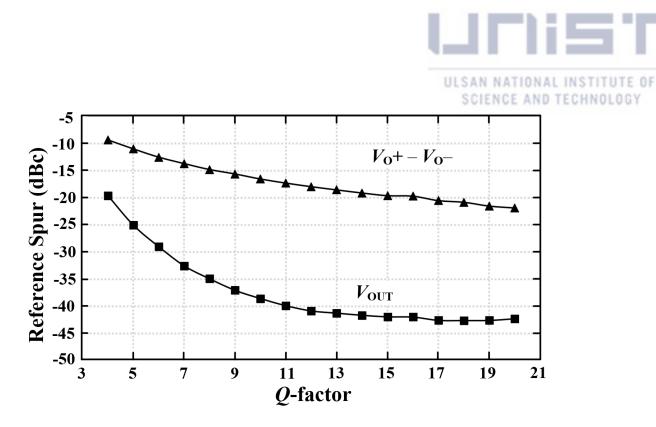

In the proposed architecture, the excessive damping of the amplitude of the output signal can be prevented by a periodical recharging process. However, a significant periodic amplitude modulation (AM) is still problematic. Along with the phase modulation (PM), due to the difference between the frequencies of the LC-tank and the target harmonic of the reference clock [1], the amplitude modulation (AM) as shown in Fig. 3.3 could increase the level of the reference spur. To remove the AM component, the *LC*-tank is followed by the D-to-S amplifier, which amplifies  $V_0$ + and  $V_0$ - in order to be clipped to the supply voltage [38]. Fig. 3.4 shows the level of the reference spur at the output of the resonator,  $(V_0+ - V_0-)$ , and the D-to-S amplifier,  $V_{OUT}$ , when Q varies from 4 to 20. As shown in Fig. 3.4, the level of the spur was suppressed significantly by the D-to-S amplifier that eliminated the AM disturbance. Even if the AM disturbance can be suppressed by the D-to-S amplifier, the swings of  $V_0$ +

Figure 3.4. Reference spurs at the outputs of the *LC*-resonator and the D-to-S amplifier,  $(V_0 + - V_0 -)$ and  $V_{OUT}$ , respectively

and  $V_0$ - that are too small demand that the D-to-S amplifier consume large power. As shown in Fig. 3.3, when Q is 15, a reasonable value for an on-chip LC-tank, the amplitude of the fourth peak is reduced to 53.3% of that of the first (or the highest) peak. To guarantee safe operation while also minimizing the power consumption of the D-to-S amplifier, we fixed the frequency multiplication number, N, at 3 in this work. However, by relaxing the power budget or the requirement for spurious tones, N can be extended to a higher value. In this work,  $L_T$ ,  $C_T$ , and Q values of the tank were 2 nH, 1.4 pF, and 15 at 3 GHz, respectively. With a Q of 15, the reference spur can be minimized to less than -40 dBc, as shown in Fig. 3.4.

#### 3.3. Measurement Results

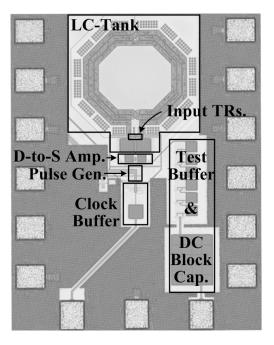

Figure 3.5. Chip micrograph of the proposed frequency tripler

The prototype frequency tripler using the proposed LC-tank-based frequency multiplier was fabricated in a TSMC 65 nm CMOS process. A test chip was mounted on a test board, and received the reference clock from a signal generator, Holzworth HS9002A. To measure output-signal performance, a spectrum analyzer, Agilent PXA N9030A, and a phase noise analyzer, Agilent E5052B, were used. In measurement, the proposed frequency tripler consumed 950 $\mu$ W from a 0.9-V supply voltage, where the tank core consumed only 600 $\mu$ W. As shown in Fig. 3.5, the frequency tripler occupied an active area of 0.08 mm<sup>2</sup>.

Figure 3.6. Measured spectrum of the 3.12 GHz output signal of the proposed frequency tripler

Fig. 3.6 shows the measured spectrum of the output signal with a 3.12 GHz frequency, which is the third harmonic of the 1.04 GHz reference frequency. As shown in the spectrum in Fig. 3.6, the level of the reference spur was -37 dBc. Fig. 3.7 shows the measured and the simulated levels of the reference spur when the reference clock frequency,  $f_{REF}$ , was swept. The spur level was minimized when the third harmonic of  $f_{REF}$  was close to the resonant frequency of the *LC*-tank, but it increased as  $f_{REF}$  deviated.

Figure 3.7. Measured and simulated reference spur level with respect to the input reference clock frequency

Figure 3.8. Measured phase noise of the 3.12 GHz output signal and the 1.04 GHz reference clock.

Fig. 3.8 shows the measured phase noises of the reference clock and the output signal with a 1.04 GHz and a 3.12 GHz frequency, respectively. The phase noise of the output signal at the 1MHz offset was -127.8 dBc/Hz, and the jitter, integrated from 1 kHz to 20 MHz, was 110 fs. The difference between the two phase-noise curves was very close to 9.5 dB (20·log 3dB), which is the theoretical bound. Table 1 compares the proposed work with state-of-the-art frequency triplers [32] – [35]. The proposed work had lowest power consumption, while restricting the degradation of phase noise from the theoretical boundary, PN<sub>DEG</sub>, to less than 0.5 dB. In addition, the proposed frequency tripler had the smallest silicon area with one inductor.

|                                | [32]   | [33]   | [34]   | [35]   | This work |

|--------------------------------|--------|--------|--------|--------|-----------|

| Process (CMOS)                 | 180 nm | 180 nm | 180 nm | 180 nm | 65 nm     |

| Output freq. (GHz)             | 3.0    | 21.0   | 21.83  | 19.5   | 3.12      |

| PN <sub>DEG</sub> @1MHz (dB)*  | < 0.5  | < 0.5  | < 1.0  | < 0.5  | < 0.5     |

| Ref. spur (dBc)                | -26    | -16    | -18    | -29    | -37       |

| <i>P</i> <sub>DC</sub> (mW)    | 68     | 7.5    | 8.1    | 18.8   | 0.95      |

| Active area (mm <sup>2</sup> ) | 0.42   | 0.36   | 0.39   | 0.84   | 0.08      |

Table 1. Comparison with State-of-the-Art Frequency Triplers

\*  $PN_{DEG}$  @1MHz =  $PN_{TRIPLER}(1MHz) - 20 \cdot \log(3) - PN_{REF}(1MHz)$

\*\* Power consumption of the frequency tripler only

#### 3.4. Discussion

In this work, we proposed a low power, compact area *LC*-tank-based frequency multiplier. By using input signals with a pulsed waveform to minimize the duration of the core current flow, the proposed architecture was able to reduce power consumption dramatically. With the *LC*-tank having a resonant frequency close to the target frequency, the signal component of the target harmonic was effectively amplified while other components were suppressed. AM spurs, caused by the damping of the signal due to the tank loss, were removed using the D-to-S amplifier. The proposed frequency tripler had a low power consumption of less than 1 mW and a compact silicon area of 0.08 mm<sup>2</sup>. It also achieved excellent phase noise performance; the deviation from the theoretical bound was less than 0.5 dB.

#### Chapter 4.

## A Low-IPN mm-Wave Injection-Locked Frequency Multiplier for 5G

#### 4.1. Motivation

Fifth-generation (5G) wireless systems have attracted attention as the next-generation cellular standard because they provide super-fast communication speeds. To meet the requirement of high data rates, RF transceivers for the 5G standard must satisfy an extremely low error vector magnitude (EVM) specification over a very wide bandwidth in a millimeter wave (mm-wave) frequency band. From this demand, one of the fundamental challenges in the design of a 5G transceiver is to generate an ultra-low-phase-noise local oscillator (LO) signal to suppress integrated phase noise (IPN) over a wide bandwidth. For example, to satisfy the EVM requirements of high-order modulations, such as 16 quadrature amplitude modulation (QAM) and 64 QAM, the IPN of an LO signal should be reduced to less than -30 dB at mm-wave frequencies [39] – [42]. Moreover, LO-signal generators also must provide quadrature signals with a very small I/Q mismatch.

The most straightforward architecture that can be used to generate the required LO signals is a high-frequency phase-locked loop (PLL) that directly generates mm-wave signals [43] – [47]. However, this architecture is not such a good solution in terms of its power consumption and phase noise. First, to synthesize a high-frequency signal in mm-wave bands, the PLL must involve power-hungry frequency dividers that operate at the target frequencies. Using typical CMOS technologies, it is difficult to design a frequency divider that operates at a high frequency, such as more than 30 GHz. Even if the design itself were possible, it would require a great amount of power to suppress the elevation of a noise floor. Second, also with respect to phase noise, a PLL that directly generates mm-wave signals is not an effective solution. According to [48], when the phase noises of recent CMOS PLLs with different output frequencies are normalized, the PLLs that have output frequencies around 3–5 GHz have much better performance with respect to phase noise than PLLs that have output frequencies greater than 10 GHz.

<sup>\* © 2018</sup> IEEE. Part of this chapter is reprinted, with permission, from S. Yoo, S. Choi, J. Kim, H. Yoon, Y. Lee, and J. Choi, "Low-Integrated-Phase-Noise 27–30-GHz Injection-Locked Frequency Multiplier With an Ultra-Low-Power Frequency-Tracking Loop for mm-Wave-Band 5G Transceivers," in *IEEE J. Solid-State Circuits*, vol. 53, no. 2, pp. 375-388, February 2018.

One of the major reasons why this occurs is that the LC-tank of a voltage-controlled oscillator (VCO) does not have a sufficiently high quality factor (Q-factor) at mm-wave frequencies. This degradation of the overall Q-factor is mainly because of the significant decrease in the Q-factor of capacitive components in the LC-tank, caused at high frequencies [49], [50]. As above, if we consider power consumption and phase noise, it is obvious that a more efficient way to generate an mm-wave-band LO

Figure 4.1. LO generation with a gigahertz-range PLL and a cascaded mm-wave ILFM for multiband and multi-standard cellular communications.

signal is to obtain an output frequency in the range of 3–5 GHz from a PLL and increase it to a higher frequency using a low-noise frequency multiplier.

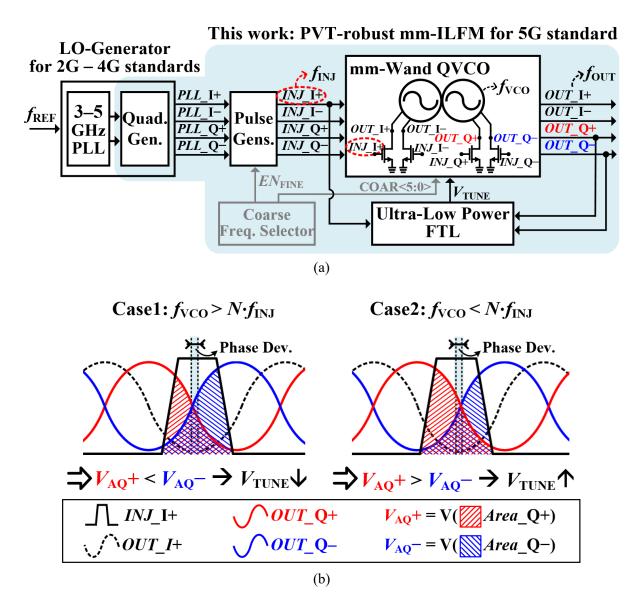

Fig. 4.1 shows the architecture proposed to generate LO signals for multi-standard, multi-band cellular transceivers. The proposed LO generator consists of a gigahertz-range PLL, an mm-wave-band, quadrature, and injection-locked frequency multiplier (ILFM). Since a gigahertz-range PLL can generate an output signal with a good phase-noise performance, if the following ILFM multiplies the frequency of the signal without degrading the noise performance, the proposed LO generator must be able to achieve sufficiently low IPN that satisfies the stringent requirement of the 5G standard. Another important advantage of the proposed architecture is that it can support the backward compatibility. Fig. 4.1 shows that a gigahertz-range PLL can be used to support conventional cellular frequency bands, i.e., 0.7–2.7 GHz [51], [52], when they are designed to have output frequencies between 2.8 and 5.4 GHz.

The key building block of the proposed multi-standard LO generator in Fig. 4.1 is a low-phase-noise mm-wave-band quadrature ILFM. However, the inherent design challenge of an ILFM is the

#### SCIENCE AND TECHNOLOGY

vulnerability of its operation and phase noise to process-voltage-temperature (PVT) variations [28], [29], [53], [54]. The normal operation of an ILFM with a low phase noise is available only when the free-running frequency of the VCO  $f_{VCO}$  is sufficiently close to the target frequency N:  $f_{INJ}$  where N and  $f_{\rm INJ}$  are the multiplication factor and the injection frequency, respectively. In other words, the deviation of  $f_{VCO}$  from N f<sub>INJ</sub>,  $f_{DEV}$ , should be kept small with respect to the lock range of the ILFM  $f_L$ . The vulnerability is more problematic for an mm-wave ILFM, where  $f_L$  is the typically restricted to less than 3% of  $f_{VCO}$  [55] – [57]. To alleviate this problem, the mm-wave ILFM in [58] uses a technique to extend the lock range, but it involves increases in power consumption and design complexity. In recent years, there have been many efforts to design frequency-tracking loop (FTL) architectures [15], [17], [19], [20], [25], [56], [57] that continue to adjust  $f_{VCO}$  so that it remains close to  $N \cdot f_{INJ}$  in a real-time fashion. However, these architectures still have practical problems, so they are inadequate for use for an mmwave ILFM that must provide extremely low phase noise. The prior FTL architectures and their problems are discussed in Section 4.2. To multiply frequencies into an mm-wave band, the cascaded PLL in [59] uses a sub-sampling PLL (SSPLL) instead of an ILFM. However, the SSPLL requires a large amount of power due to the use of a sample-and-hold phase detector and a voltage-to-current converter, which operates at the frequency of the precedent PLL, i.e., around 7 GHz.

In this work, we present an mm-wave-band ILFM that can continue to provide ultra-low-phase-noise quadrature output signals, irrespective of PVT variations [60]. By monitoring the distortions between the output phases of the injection-locked quadrature VCO (QVCO) of the ILFM that are caused when  $f_{VCO}$  deviates from the target frequency, the proposed FTL can correct the drifts of  $f_{VCO}$  and continuously suppress phase noise without the loss of the injection lock. The FTL monitors the averages of the phase deviations rather than detecting or sampling the instantaneous values, so it only operates at a very low frequency. Since it does not use any high-frequency circuits, the FTL should have ultra-low-power consumption.

The rest of this Chapter is organized as follows. Section 4.2 shows why the drifts of  $f_{VCO}$  are critical in mm-wave bands and presents the limits of prior FTLs. In Section 4.3, the concept and the design of the proposed FTL and ILFM are presented. Section 4.4 describes the analysis of the phase noise and the static frequency offset due to the mismatches along the signal paths of the FTL. Experimental results and conclusions are presented in Sections 4.5 and 4.6, respectively.

## 4.2. Limits of Prior Frequency-Tracking-Loop Architectures for mm-Wave ILFMs

As aforementioned, the degradation of the phase noise of an ILFM due to PVT variations becomes more severe as  $f_{VCO}$  increases. Fig. 4.2(a) shows the results of the simulation of the maximum  $f_{DEV}(\%)$ of a free-running LC-VCO according to frequency drifts due to temperature variations. It also shows  $f_{\rm L}(\%)$  of the same VCO, when a 2.25-GHz signal is injected. According to N from 3 to 17, the inductance of the LC-tank was scaled to maintain the same Q-factor ( $Q_{ind}$ ) despite the change in  $f_{VCO}$ . Fig. 4.2(a) shows the maximum  $f_{\text{DEV}}$  for the temperature range of -30 °C to 120 °C increases gradually as N increases. This is due to the increase in the contribution of the PVT-sensitive parasitic capacitances of the core transistors when  $f_{VCO}$  is defined. Contrary to the increase in  $f_{DEV}$ ,  $f_L$  continues to decrease as N increases. This is because the effective current of the injection signal's Nth harmonic component decreases with respect to the VCO's current, thereby reducing the strength of the injection [61], [62]. Consequently, the increase in  $f_{\text{DEV}}$  along with the decrease in  $f_L$  for a larger N makes the performance of an ILFM more vulnerable to environmental variations. Fig. 4.2(b) shows the changes of the 10-MHz phase noise with respect to  $f_{\text{DEV}}$  for different N's. The noise data were obtained from the same VCOs and the injection signal used in Fig. 4.2(a), and the graphs were plotted by MATLAB using the equation of the theoretical phase noise of an ILFM in [63]. As shown in Fig. 4.2(b), when  $f_{\text{DEV}}$  is relatively small with respect to  $f_L$ , the level of the phase noise approaches the theoretical minimum boundary, i.e.,  $20 \cdot \log N$  above the phase noise of the injection signal. However, as  $f_{\text{DEV}}$  approaches  $f_{\text{L}}$  due to drifts of  $f_{\rm VCO}$ , the phase noise is degraded significantly, and, finally, the lock is released. This problem becomes more severe as N increases, i.e., a possible  $f_{\text{DEV}}$  increases even greater than  $f_{\text{L}}$ , when N is more than 13. Thus, to ensure the robust operation with a low phase noise irrespective of environmental variations, an mm-wave ILFM must be equipped with a dedicated FTL that can continue to correct the frequency of the VCO during real-time frequency drifts.

Figure 4.2. (a) Lock range  $f_L(\%)$  and maximum deviation of the free-running frequency  $f_{DEV}(\%)$  over temperature of an *LC*-VCO injected by a 2.25-GHz tone, when the target harmonic factor *N* is changed. (b) Degradations of the10-MHz phase noise with respect to  $f_{DEV}$  for different *N*'s.

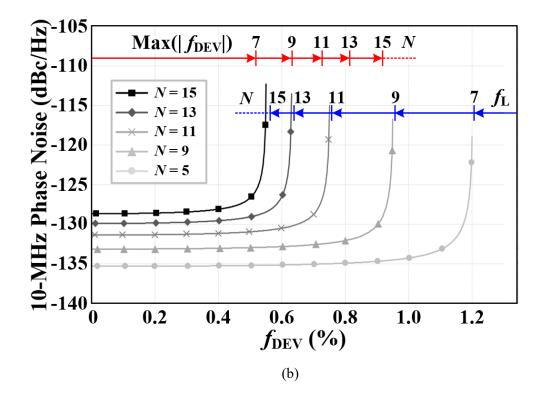

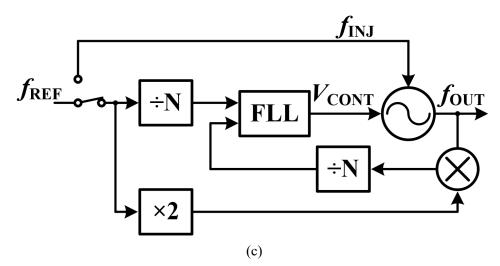

For calibrating  $f_{VCO}$  over PVT variations, many FTLs have been reported for ILFMs [15], [17], [19], [20], [25], [56], [57]. However, to detect the information of  $f_{\text{DEV}}$ , each architecture in those conventional FTLs has used building blocks operating at  $f_{VCO}$ . Since the power consumption of these circuits is supposed to grow proportionally as  $f_{VCO}$  increases, conventional FTLs are not suitable for mm-wave ILFMs. Fig. 4.3(a) shows a replica-VCO-based FTL using a replica-VCO that has the same control voltage as the main VCO [17], [19], [20]. In this architecture, the replica-VCO is not injection locked; thus, a frequency-locked loop (FLL) can continue to detect and correct any drifts in its frequency. Then, by sharing the control voltage of the FLL, the  $f_{VCO}$  of the injection-locked VCO can stay close to the target frequency. This calibration method has an advantage in that it can operate regardless of whether the VCO is injection locked or not. However, the critical problem of this architecture when it is used for an mm-wave ILFM is that the replica-VCO has to consume the same amount of power as the main VCO. As a variation, the architecture in [25] uses a delay-locked loop (DLL) consisting of replica-delay cells to track the drifts of  $f_{VCO}$ , but the DLL also must use the same amount of power as the VCO. Fig. 4.3(b) shows the time-to-digital converter (TDC)-based architecture that uses TDC to detect the instantaneous phase shift of the output of the VCO at the moment a pulse is injected from the reference clock [15]. Although these FTLs are popular for calibrating frequency drifts at gigahertz-range frequencies, they should not be used at mm-wave frequencies, at which circuits, such as frequency dividers and TDCs, use excessive power. The ILFM in [56], shown in Fig. 4.3(c), is targeted for generating the output signals at an mm-wave frequency, but since a mixer and dividers, operating at high frequencies, are included, the FLL consumes a large amount of power, more than 60 mW. To overcome the problem of excessive power usage of the calibrating circuits for mm-wave ILFMs, the architecture in [57] presents an FTL using an envelope detector, as shown in Fig. 4.3(d). Based on the observation that the envelope of the output of the VCO becomes constant when the injection lock is acquired, but it fluctuates when the lock is not acquired, this FTL can determine whether injection locking has been acquired or not. Since this architecture is supposed to track the change of the envelope, much slower than the change of the output of the VCO, it can be designed only using building circuits that operate at low frequencies; thus, low-power calibration is available even for an mm-wave ILFM. However, tracking of the envelope provides hardly any additional information after the injection lock is acquired. Thus, while this architecture can be used to overcome the static change of  $f_{\rm VCO}$  across process corners, it cannot be used to correct real-time drifts of  $f_{\rm VCO}$  from the target frequency due to temperature changes or to prevent the degradation of phase noise.

SCIENCE AND TECHNOLOGY

(a)

Figure 4.3. ILFMs with different FTLs using (a) a replica-VCO; (b) a TDC; (c) a mixer; (d) an envelope detector.

# **4.3.** Proposed ILFM With an Ultra-Low-Power FTL Using the Averages of the Phase Deviations

#### 4.3.1. Overall Architecture

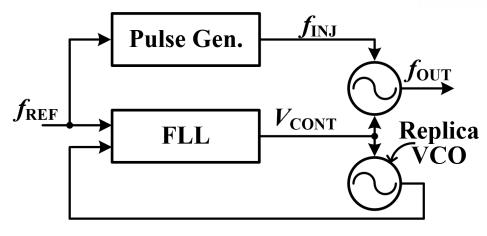

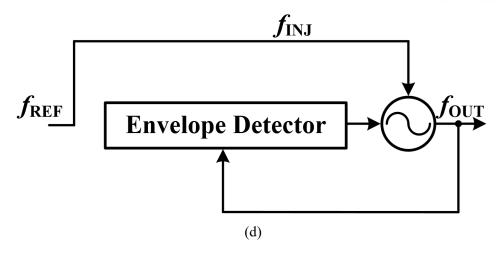

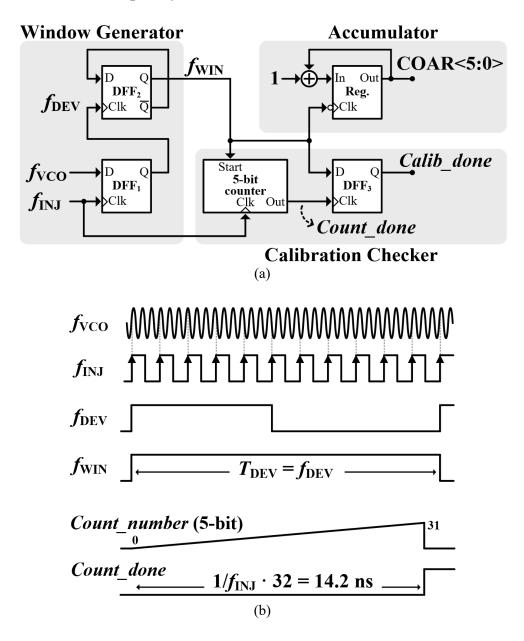

Fig. 4.4(a) shows the proposed ILFM, which consists a quadrature generator, QVCO, pulse generators (PGs), coarse frequency selector (CFS), and low-power FTL. Since an on-chip PLL was not designed in this work, an external RF-signal generator or external PLL is used to provide input signals to the quadrature generator. The PGs receive the quadrature signals and generate the injection pulses, i.e.,  $INJ_I+$ ,  $INJ_I-$ ,  $INJ_Q+$ , and  $INJ_Q-$ , where the frequency is  $f_{INJ}$ . These pulses are injected to the

Figure 4.4. (a) Conceptual diagram of the cascaded architecture of an mm-wave LO generator. (b) Principle of the proposed frequency-tracking loop (FTL).

gates of the injection transistors, where the drains are connected to the outputs of the QVCO. When an injection pulse enters the gate, the corresponding output the QVCO is pulled down, leading to instantaneous phase realignment. Fig. 4.4(b) shows the principle of the proposed FTL, which uses the relationship between the phases of INJ I+, OUT Q+, and OUT Q-. At the moment when INJ I+ is injected, the phase of OUT I+ is realigned momentarily. However, OUT Q+ and OUT Q- still maintain their intrinsic phases independent of INJ I+, since the coupling strength between the two VCOs of the QVCO is much less than the phase-realigning strength of the injection pulses. Thus, if  $f_{VCO}$ deviates from  $N \cdot f_{INJ}$ , the quadrature relationship between the outputs of the QVCO is distorted instantaneously, i.e., INJ I+ becomes closer to either OUT Q+ or OUT Q-. This distortion can be detected by comparing the overlapped area of INJ I+ with OUT Q+ and that with OUT Q-; the difference between the two areas is proportional to the difference between  $f_{VCO}$  and  $N \cdot f_{INJ}$ . In this paper, the information of the areas is obtained as voltages, i.e.,  $V_{AQ}$ + and  $V_{AQ}$ -, by multiplying INJ I+ by OUT Q+ and by multiplying INJ I+ by OUT Q-, respectively. As shown in Case 1 in Fig. 4.4(b), in which  $f_{VCO}$  is higher than N· $f_{INJ}$ ,  $V_{AQ}$ + should be lower than  $V_{AQ}$ - since INJ\_I+ is closer to OUT\_Qthan it is to OUT Q<sup>+</sup>. Then, the control voltage  $V_{\text{TUNE}}$  decreases to lower  $f_{\text{VCO}}$ . When  $f_{\text{VCO}}$  is lower, as shown in Case 2,  $V_{AQ}$ + is higher than  $V_{AQ}$ -, and, thus,  $V_{TUNE}$  must increase to adjust  $f_{VCO}$  to be higher.

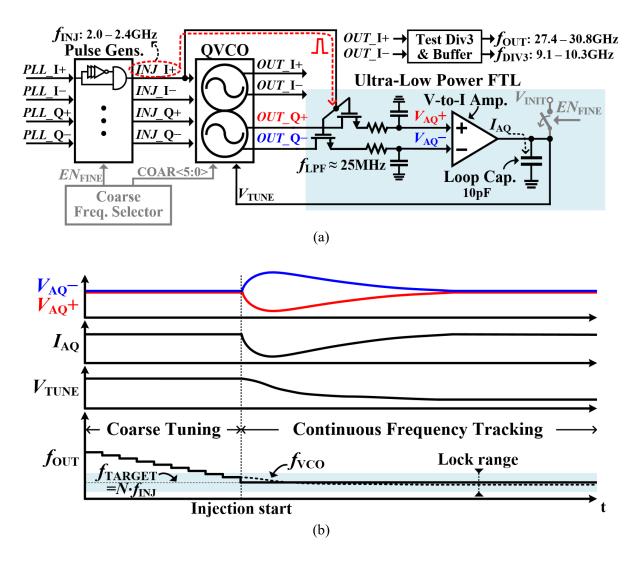

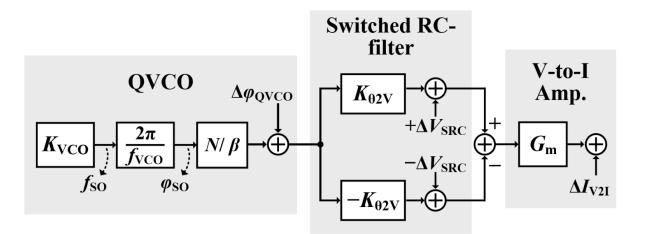

Fig. 4.5(a) and (b) shows the overall architecture and the conceptual transient behavior of the proposed FTL, respectively. When the coarse tuning is done by the CFS, the FTL starts continuous tracking of the frequency in order to monitor the average phase deviations. In the FTL, OUT Q+ and OUT Q- are transferred to the low-pass RC-filters through the NMOS switches, which are closed during the pulsewidth of INJ I+. Since the effective bandwidth of the low-pass filters  $f_{LPF}$  (including the effect of the NMOS switches) is much lower than  $f_{INJ}$ ,  $V_{AQ}$ + and  $V_{AQ}$ - almost become dc voltages, implying the average values of the overlapped areas of OUT Q+ and OUT Q-, respectively. The series resistors in the RC-filters also have the role of preventing the reduction of the tank-Q of the VCO by the capacitors of the filters, while the switches are turned ON. The following V-to-I amplifier generates the current  $I_{AQ}$  depending on the difference between  $V_{AQ}$ + and  $V_{AQ}$ -. As  $I_{AQ}$  charges or discharges the loop capacitor,  $V_{\text{TUNE}}$  is controlled to adjust  $f_{\text{VCO}}$  to be very close to  $N \cdot f_{\text{INJ}}$ . Since any drifts of  $f_{\text{VCO}}$  in steady-state operation would cause mismatches between  $V_{AQ}$ + and  $V_{AQ}$ -, the FTL can keep correcting f<sub>VCO</sub> without the loss of injection locking. The loop bandwidth of the FTL was approximately 2 MHz, whereas the  $f_L$  of the ILFM was 200 MHz. Since the loop bandwidth of the FTL is much less than  $f_L$ , the stability of the system can be ensured without any conflicts between two frequency-control mechanisms. To correct the frequency of a multi-phase ring VCO, the multi-phase generator in [64] uses a similar method. However, it uses the relationship between the output phases of the VCO themselves using a quadrature mixer, while the proposed FTL uses the relationship of the phases of the injection signal and the signals of the VCO. Due to this difference, the proposed FTL can achieve a

much higher loop gain, when it is used for an ILFM having a large N. In addition, to drive the quadrature mixer operating at  $f_{VCO}$ , the buffers need a relatively large power in [64].

Figure 4.5. Proposed mm-wave ILFM with the ultra-low power FTL. (a) Overall architecture. (b) Conceptual timing diagram.

#### 4.3.2. V-to-I Amplifier and the QVCO

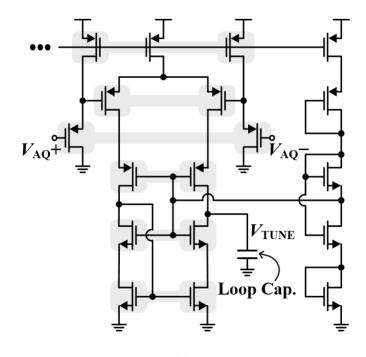

Fig. 4.6(a) shows the schematics of the V-to-I amplifier of the FTL that consists of two stages. The first stage acts as a level shifter to shift up the operating points of the inputs,  $V_{AQ}$ + and  $V_{AQ}$ -, from the level of the voltage of the precedent RC-filters. The second stage, based on an operational transconductance amplifier, has a cascode active load to enhance the gain and reduce mismatches in the currents. The inter-digitation technique is used in the layout of each transistor pair to improve the differentially. As shown in Fig. 4.6(b), the QVCO is composed of two CMOS-type VCOs. Along with the pairs of NMOS and PMOS gm-transistors, each VCO also has additional pairs of NMOS switches; one pair is for coupling the two VCOs, and the other is for applying the injection pulses from the reference clock. As in the foregoing discussion, the fundamental operation principle of the proposed FTL is to detect the instantaneous distortion of the quadrature relationship between OUT I+ (or OUT I-) and OUT Q+ (or OUT Q-) of the QVCO at the moment when the injection pulse is applied to OUT I+ (or OUT I–). This operation is based on the assumption that only the phase of OUT I+ (or OUT I-) is realigned instantaneously by the injection pulse, whereas OUT Q+ (or OUT Q-) maintains its intrinsic phase according to  $f_{VCO}$ . Therefore, to improve the efficiency of the detecting operation, the phase-realigning strength of the injection pulses must be greater than the strength of the internal coupling within the QVCO. To satisfy this condition, the ratio of the size of the NMOS switches for the injection to that for the coupling was designed to be nine to one. Despite the relatively weak coupling within the QVCO, the 3-sigma value of the quadrature error of the QVCO in this work was 1.8°, according to the Monte-Carlo simulation. Each VCO includes six-bit binary-weighted metaloxide-metal capacitors and a varactor to adjust  $f_{VCO}$ . The six-bit capacitor bank is controlled by COAR<5:0> from the CFS in the coarse-tuning step. In the frequency-tracking mode, the varactor is adjusted continuously by  $V_{\text{TUNE}}$ , which is generated from the FTL.

## V-to-I Amp.

: Inter-digitation

(a)

Figure 4.6. Schematics of (a) V-to-I amplifier and (b) QVCO

## 4.3.3. Quadrature Generator, the Pulse Generator, and the Switched *RC*-filters

To realize the complete concept, as shown in Fig. 4.4(a), an on-chip PLL generating 3–5-GHz signals should be designed together with the proposed ILFM. Then, a simple divide-by-2 divider could easily generate quadrature signals from the differential signals of the PLL. However, in this work, since only the proposed mm-wave ILFM was implemented as a prototype, no internal differential signals were available. Thus, the quadrature generator is based on a divide-by-4 divider, receiving an input signal with a frequency of  $4f_{\text{INJ}}$  from an external signal generator, and it consumes 2.2 mW. A quadrature error in the injection signals could lead to that in the output signals of the QVCO, which is more severe as *N* increases. However, this effect is significantly alleviated by the coupling within the QVCO. This is because although the coupling strength of the QVCO is weaker than the injection strength, it corrects the quadrature error in the injection signals caused a 2.1°-quadrature error in the output signals. This value can be further reduced by increasing the coupling strength of the QVCO at the expense of a slow operation of the FTL.

Each of the four PGs consists of three inverters and a NAND gate. The width of the injection pulses PW was designed to be 15 ps, but it could change between 12 and 22 ps according to corner and temperature simulations. PW is an important factor to define the conversion gain  $K_{\theta 2V}$  from the phase error of the VCO's signal to the dc voltage of  $V_{AQ}$ + (or  $V_{AQ}$ -). From simulations to observe a change in the voltage of  $V_{AQ}$ + (or  $V_{AQ}$ -) due to a phase error,  $K_{\theta 2V}$ 's were 0.39, 0.3, and 0.2 V/rad, when PW's were 12, 15, and 22 ps, respectively.

For the switched *RC*-filters, the resistance and the capacitance are approximately 2.1 k $\Omega$  and 100 fF, respectively. The NMOS switches used low threshold voltage devices, and the width and the length of the switches were designed to be 370 and 60 nm, respectively. To match capacitive loadings to the VCOs, dummy NMOS switches were also used for the outputs of VCO\_I. Since the on-resistance of the NMOS switches was approximately 1.6 k $\Omega$ , the series resistors of the *RC*-filters were designed to have a resistance of 0.5 k $\Omega$ . The charge injection or sharing due to the switching of the *RC*-filters could cause undesired periodic phase shifts in the outputs of the VCO. However, from the simulation results, the phase shift due to this effect is almost negligible compared to other non-ideal factors, such as the quadrature error of the QVCO. This is because the size of the NMOS switches is very small, and the resistance of the switched *RC*-filters is large enough to suppress the charge sharing. Since the switched *RC*-filters are connected to the differential outputs of the VCO, the effects of delivered charges can be canceled out due to the nature of the differential signaling.

#### 4.3.4. Coarse Frequency Selector

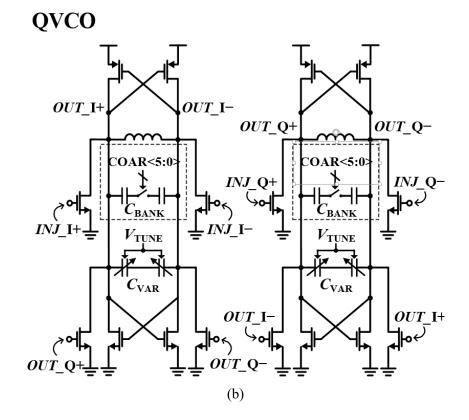

Figure 4.7. (a) Schematics of the CFS. (b) Conceptual timing diagram of the CFS.

Fig. 4.7(a) and (b) shows the schematics and the conceptual timing diagram of the CFS [63]. As shown in Fig. 4.7(a), the CFS consists of a window generator, an accumulator, and a calibration checker. Initially,  $f_{VCO}$  is set to the maximum value with the lowest value of COAR<5:0>. As shown in Fig. 4.7(b), the window generator provides a window signal, where its length corresponds to the difference between  $f_{VCO}$  and  $N \cdot f_{INJ}$ . Every time when a window signal is generated, the calibration checker compares the length of the window signal with the reference time, i.e., 14.2 ns, generated by a five-bit counter. Then, if the length of the window is less than the reference time, the accumulator increases the value of COAR<5:0> by one, which decreases  $f_{VCO}$ . This process is iterated until the difference between

$f_{VCO}$  and N: $f_{INJ}$  is sufficiently reduced, and, thus, *Calib\_done* goes high. The frequency resolution of the CFS is fixed at approximately one third of the lock range. Since the CFS was designed to detect the difference between  $f_{VCO}$  and N· $f_{INJ}$  using a D-flip-flop, DFF<sub>1</sub>, without the help of a frequency divider, it must suffer from a limited capture range. However, in this work, only one specific N is targeted for a given  $f_{INJ}$  to generate the output frequency around 30 GHz; thus, this CFS circuit is sufficient to initialize  $f_{VCO}$  before the operation of the continuous FTL.

#### 4.4. Analysis of Phase Noise and Static Frequency Offset

#### 4.4.1. Phase Noise of the Proposed ILFM

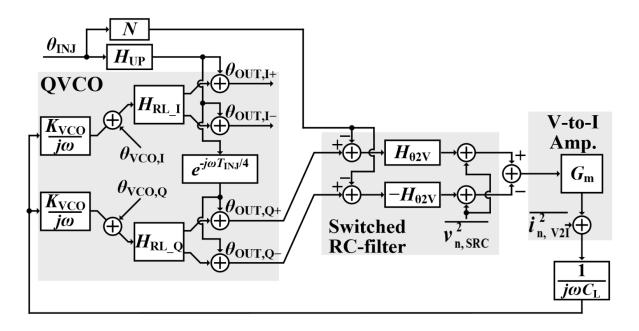

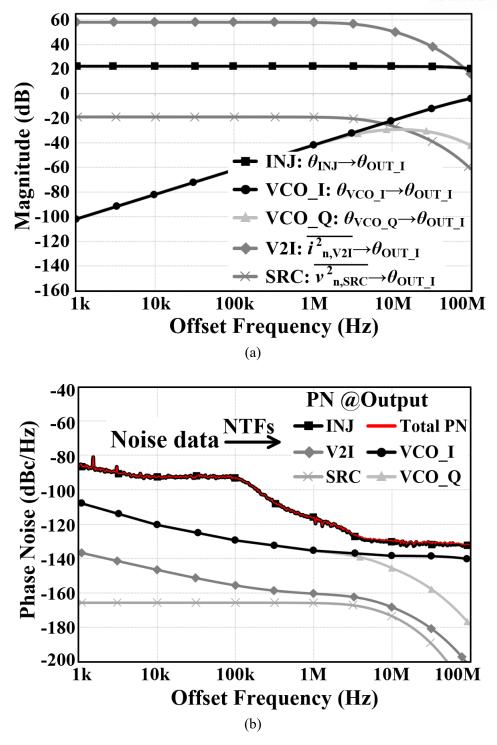

Figure 4.8. Noise model of the proposed mm-wave ILFM.

Fig. 4.8 shows the noise model of the proposed ILFM. The units of the gains of the VCO,  $K_{VCO}$ , the switched *RC*-filter,  $H_{\theta 2V}$ , and the V-to-I amplifier,  $G_m$ , are [rad/s/V], [V/rad], and [A/V], respectively. *N* is the multiplication factor, and  $C_L$  is the value of the loop capacitance followed by the V-to-I amplifier. The symbol  $\theta_{INJ}$  is the output-referred phase error of the injection clock, and  $\theta_{VCO,I}$  and  $\theta_{VCO,Q}$  are the output-referred phase errors of the two VCOs of the QVCO. The terms  $\overline{v_{n,SRC}^2}$  and  $\overline{i_{n,V2I}^2}$  are the output-referred voltage noise of the switched *RC*-filter and the output-referred current noise of the V-to-I amplifier, respectively. The phase realignment by the injection clock can be modeled by the following three transfer functions:

$$H_{\rm UP}(j\omega) = \frac{N \cdot \beta \cdot e^{-j\omega T_{\rm INJ}/2}}{1 + (\beta - 1)e^{-j\omega T_{\rm INJ}}} \frac{\sin(\omega T_{\rm INJ}/2)}{\omega T_{\rm INJ}/2},$$

(1)

$$H_{\mathrm{RL}_{\mathrm{I}}}(j\omega) = 1 - \frac{\beta \cdot e^{-j\omega T_{\mathrm{INJ}}/2}}{1 + (\beta - 1)e^{-j\omega T_{\mathrm{INJ}}}} \frac{\sin(\omega T_{\mathrm{INJ}}/2)}{\omega T_{\mathrm{INJ}}/2},$$

(2)

and

$$H_{\mathrm{RL}_{Q}}(j\omega) = 1 - \frac{e^{-j\omega T_{\mathrm{INJ}}/4} \cdot \beta \cdot e^{-j\omega T_{\mathrm{INJ}}/2}}{1 + (\beta - 1)e^{-j\omega T_{\mathrm{INJ}}}} \frac{\sin(\omega T_{\mathrm{INJ}}/2)}{\omega T_{\mathrm{INJ}}/2},$$

(3)

where  $T_{INJ}$  represents the period of injection clock and  $\beta$  is the phase realign factor that indicates the strength of the phase correction by the injection clock [7], ranging from zero to one. The transfer function of  $H_{UP}(j\omega)$  in (1) represents the up-conversion of the injection signal noise to the output. In Fig. 4.8,  $\theta_{OUT,I}$  represents the phase error of OUT\_I+ (or OUT\_I-), when its phase is realigned by INJ\_I+ (or INJ\_I-), and  $\theta_{OUT,Q}$  represents the phase error of OUT\_Q+ (or OUT\_Q-), when its phase is realigned by INJ\_Q+ (or INJ\_Q-). The transfer functions of  $H_{RL_I}(j\omega)$  in (2) and  $H_{RL_Q}(j\omega)$  in (3) represent the effects of the phase realignment of the  $\theta_{OUT,I}$  and  $\theta_{OUT,Q}$  by the corresponding injection pulses, respectively. Since the phase of OUT\_Q+ (or OUT\_Q-) lags behind that of OUT\_I+ (or OUT\_I-) by a 90°,  $H_{RL_Q}(j\omega)$  in (3) includes the term of  $\exp(-j\omega T_{INJ}/4)$ , different from  $H_{RL_I}(j\omega)$  in (2). From the noise model in Fig. 4.8, the open-loop transfer function  $LG(j\omega)$  can be obtained as

$$LG(j\omega) = 2 \cdot H_{\theta 2V}(j\omega) \cdot G_{\rm m} \cdot \frac{1}{j\omega C_{\rm L}} \cdot \frac{K_{\rm VCO}}{j\omega} \cdot H_{\rm RL_Q}(j\omega), \quad H_{\theta 2V}(j\omega) = \frac{K_{\theta 2V}}{j\omega/\omega_{\rm LPF} + 1}, \tag{4}$$

where  $\omega_{LPF}$  is the effective bandwidth of the low-pass filters in radian. Using (1) – (4), the noise transfer functions (NTFs) to the output  $\theta_{OUT,I}$  from the noise sources can be obtained as:

$$H_{\rm INJ}(j\omega) = \frac{\theta_{\rm OUT\_I}}{\theta_{\rm INJ}} = H_{\rm UP}(j\omega) + \left(H_{\rm UP}(j\omega) \cdot e^{-j\omega T_{\rm INJ}/4} - N\right) \cdot \frac{LG(j\omega)}{1 - LG(j\omega)} \cdot \frac{H_{\rm RL\_I}(j\omega)}{H_{\rm RL\_Q}(j\omega)}, \quad (5)$$

$$H_{\text{VCO}_{I}}(j\omega) = \frac{\theta_{\text{OUT}_{I}}}{\theta_{\text{VCO}_{I}}} = H_{\text{RL}_{I}}(j\omega), \qquad (6)$$