# HARDWARE IMPLEMENTATIONS OF SCALABLE AND UNIFIED ELLIPTIC CURVE CRYPTOSYSTEM PROCESSORS

A Thesis Submitted to the

College of Graduate Studies and Research

in Partial Fulfillment of the Requirements

for the degree of Doctor of Philosophy

in the Department of Electrical and Computer Engineering

University of Saskatchewan

Saskatoon, Saskatchewan, Canada

Ву

Kung Chi Cinnati Loi

©Kung Chi Cinnati Loi, February 2015. All rights reserved.

#### PERMISSION TO USE

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Department of Electrical and Computer Engineering

57 Campus Drive

University of Saskatchewan

Saskatoon, Saskatchewan

Canada

S7N 5A9

#### Abstract

As the amount of information exchanged through the network grows, so does the demand for increased security over the transmission of this information. As the growth of computers increased in the past few decades, more sophisticated methods of cryptography have been developed. One method of transmitting data securely over the network is by using symmetric-key cryptography. However, a drawback of symmetric-key cryptography is the need to exchange the shared key securely. One of the solutions is to use public-key cryptography.

One of the modern public-key cryptography algorithms is called Elliptic Curve Cryptography (ECC). The advantage of ECC over some older algorithms is the smaller number of key sizes to provide a similar level of security. As a result, implementations of ECC are much faster and consume fewer resources. In order to achieve better performance, ECC operations are often offloaded onto hardware to alleviate the workload from the servers' processors.

The most important and complex operation in ECC schemes is the elliptic curve point multiplication (ECPM). This thesis explores the implementation of hardware accelerators that offload the ECPM operation to hardware. These processors are referred to as ECC processors, or simply ECPs. This thesis targets the efficient hardware implementation of ECPs specifically for the 15 elliptic curves recommended by the National Institute of Standards and Technology (NIST).

The main contribution of this thesis is the implementation of highly efficient hardware for scalable and unified finite field arithmetic units that are used in the design of ECPs. In this thesis, scalability refers to the processor's ability to support multiple key sizes without the need to reconfigure the hardware. By doing so, the hardware does not need to be redesigned for the server to handle different levels of security. Unified refers to the ability of the ECP to handle both prime and binary fields. The resultant designs are valuable to the research community and industry, as a single hardware device is able to handle a wide range of ECC operations efficiently and at high speeds. Thus, improving the ability of network servers to handle secure transaction more quickly and improve productivity at lower costs.

#### ACKNOWLEDGEMENTS

This thesis is supported by the Natural Sciences and Engineering Research Council of Canada (NSERC) through the Alexander Graham Bell Graduate Scholarship and the University of Saskatchewan College of Graduate Studies and Research Dean's Scholarship. I would like to thank my supervisor, Dr. Seok-Bum Ko, for his support in the past 4 years of my studies and the advice he has given me along the way. Also, thanks to Rylan for his input on the SSL protocol and countless post-midnight online chats to discuss the possibilities of my thesis. A special thanks goes out to Mandy and her family for keeping me sane during the most stressful times of my life. Most importantly, I would also like to thank my family for their continuous support in my life, without them I would not be where I am today!

# CONTENTS

| Pe       | ermis                  | ssion to Use                                                    | i    |

|----------|------------------------|-----------------------------------------------------------------|------|

| Al       | ostra                  | act                                                             | ii   |

| A        | ckno                   | wledgements                                                     | iii  |

| Co       | onter                  | nts                                                             | iv   |

| Li       | st of                  | Tables                                                          | vi   |

| Li       | st of                  | Figures                                                         | viii |

| Li       | st of                  | Algorithms                                                      | x    |

| Li       | $\operatorname{st}$ of | Abbreviations                                                   | xi   |

| Li       | st of                  | Publications                                                    | xiii |

| 1        | Intr                   | roduction                                                       | 1    |

|          | 1.1                    | Literature Review of ECC Processors                             | 4    |

|          | 1.2                    | Motivation                                                      | 7    |

|          | 1.3                    | Description of the Research and Major Contributions             | 10   |

|          | 1.4                    | Organization of Thesis                                          | 12   |

| <b>2</b> | Bac                    | kground                                                         | 13   |

|          | 2.1                    | Introduction to Cryptography                                    | 13   |

|          | 2.2                    | Elliptic Curve Cryptography                                     | 15   |

|          | 2.3                    | Finite Field Arithmetic                                         | 23   |

|          |                        | 2.3.1 Finite Field Arithmetic in Binary Fields                  | 23   |

|          |                        | 2.3.2 Finite Field Arithmetic in Prime Fields                   | 32   |

|          | 2.4                    | Xilinx Virtex-5 FPGA and XtremeDSP Slices                       | 34   |

| 3        | Sca                    | lable ECC Processors for Binary Curves                          | 39   |

|          | 3.1                    | 163-bit ECC Processor                                           | 39   |

|          | 3.2                    | Scalable ECC Processor for Binary Curves                        | 42   |

|          |                        | 3.2.1 Scalable ECP over Koblitz Curves                          | 43   |

|          |                        | 3.2.2 Scalable ECP over Pseudo-Random Curves                    | 48   |

|          | 3.3                    | Parallelization of Scalable ECC Processor for Binary Curves     | 51   |

|          |                        | 3.3.1 Parallelization of Scalable ECP over Koblitz Curves       | 51   |

|          |                        | 3.3.2 Parallelization of Scalable ECP over Pseudo-Random Curves | 61   |

|          | 3.4                    | Low Latency Scalable ECC Processor for Binary Curves            | 69   |

| 4                         | Scalable ECC Processor for Prime Curves      | 73  |

|---------------------------|----------------------------------------------|-----|

|                           | 4.1 Design and Architecture                  | 73  |

|                           | 4.2 Implementation Results                   | 81  |

| 5                         | Scalable and Unified ECC Processor           | 84  |

|                           | 5.1 Design and Architecture                  | 84  |

|                           | 5.2 Hardware/Software Co-design              | 102 |

| 6                         | Conclusion                                   | 105 |

| 7                         | Future Work                                  | 109 |

|                           | 7.1 Koblitz $\tau$ NAF Conversion            | 109 |

|                           | 7.2 Post-Quantum Cryptography                | 111 |

|                           | 7.3 Identity-Based Encryption                | 112 |

| Re                        | eferences                                    | 114 |

| $\mathbf{A}_{\mathbf{l}}$ | ppendix A Binary Fields Reduction Algorithms | 121 |

| $\mathbf{A}_{\mathbf{J}}$ | ppendix B Prime Fields Reduction Algorithms  | 125 |

# LIST OF TABLES

| 1.1<br>1.2 | Comparison between ECC and RSA Security [13] Summary of ECPs in the Current Literature                                                                      | 2<br>8   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1        | NIST Recommended Irreducible Polynomials                                                                                                                    | 27       |

| 2.2        | Decomposition of $m-1$ for Itoh-Tsujii Algorithm                                                                                                            | 30       |

| 2.3        | OPMODE control signals for X Multiplexer                                                                                                                    | 36       |

| 2.4        | OPMODE control signals for Y Multiplexer                                                                                                                    | 36       |

| 2.5        | OPMODE control signals for Z Multiplexer                                                                                                                    | 36       |

| 2.6        | Three-input ALU operations                                                                                                                                  | 37       |

| 2.7        | Two-input ALU operations                                                                                                                                    | 37       |

| 3.1        | Implementation Results and Comparison of the 163-bit ECP                                                                                                    | 41       |

| 3.2        | Implementation Results and Comparison of the Koblitz ECP                                                                                                    | 47       |

| 3.3        | Implementation Results and Comparison of the Random ECP                                                                                                     | 50       |

| 3.4        | Latency in number of clock cycles of the MULT and SA blocks.                                                                                                | 56       |

| 3.5        | Instructions executed by the 1-MULT Koblitz ECP                                                                                                             | 57       |

| 3.6        | Instructions executed by the 2-MULT Koblitz ECP                                                                                                             | 59       |

| 3.7        | Implementation Results and Comparison of the Parallelized Scalable ECPs for                                                                                 | C1       |

| 20         | Koblitz Curves                                                                                                                                              | 61       |

| 3.8        | Instructions executed by the 1-MULT Random ECP                                                                                                              | 65<br>67 |

| 3.9        | Instructions executed by the 2-MULT Random ECP                                                                                                              | 67       |

| 3.10       | Implementation Results and Comparison of the Parallelized Scalable ECPs for Pseudo-Random Curves                                                            | 68       |

| 3 11       | Implementation Results of the Low-Latency ECPs                                                                                                              | 72       |

| 0.11       | implementation results of the Lew Educate, Let's                                                                                                            |          |

| 4.1<br>4.2 | Operation sequence for the addition/subtraction/reduction (AR) block for $p_{192}$ Latency in number of clock cycles of the MULT and AR blocks in the Prime | 76       |

|            | ECP.                                                                                                                                                        | 77       |

| 4.3        | Instructions executed during PDBL and PADD states by the Prime ECP                                                                                          | 80       |

| 4.4        | Instructions executed during inversion and FINAL states by the Prime ECP                                                                                    | 81       |

| 4.5        | Implementation Results and Comparison of the Prime ECP                                                                                                      | 82       |

| 5.1        | Latencies in clock cycles of the MULT and AR blocks in the Scalable and                                                                                     |          |

|            | Unified ECP.                                                                                                                                                | 89       |

| 5.2        | Instructions executed in the PRIME states of the Scalable and Unified ECP                                                                                   | 93       |

| 5.3        | Instructions executed in the KOBLITZ states of the Scalable and Unified ECP                                                                                 | 94       |

| 5.4        | Instructions executed in the RANDOM states of the Scalable and Unified ECP                                                                                  | 95       |

| 5.5        | Latency comparison of the inversion algorithms                                                                                                              | 96       |

| 5.6        | Instructions executed in the BINARY INVERSION states of the Scalable and                                                                                    |          |

|            | Unified ECP                                                                                                                                                 | 98       |

| 5.7        | Instructions executed in the PRIME INVERSION states of the Scalable and                                                                                     | 00       |

|            | Unified ECP                                                                                                                                                 | 98       |

| 5.8 | Instructions executed in FINAL states of the Scalable and Unified ECP | 99  |

|-----|-----------------------------------------------------------------------|-----|

| 5.9 | Implementation Results and Comparison of the Scalable and Unified ECP | 100 |

# LIST OF FIGURES

| 1.1  | Levels of abstraction in ECC implementations                                            | 3  |

|------|-----------------------------------------------------------------------------------------|----|

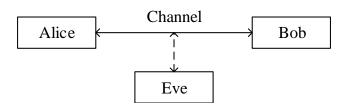

| 2.1  | Simple communication model of an unsecured channel.                                     | 13 |

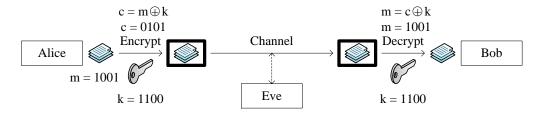

| 2.2  | Communication model with symmetric-key cryptography.                                    | 14 |

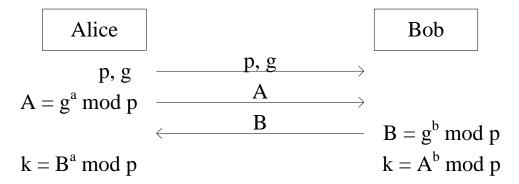

| 2.3  | Diffie-Hellman key exchange.                                                            | 14 |

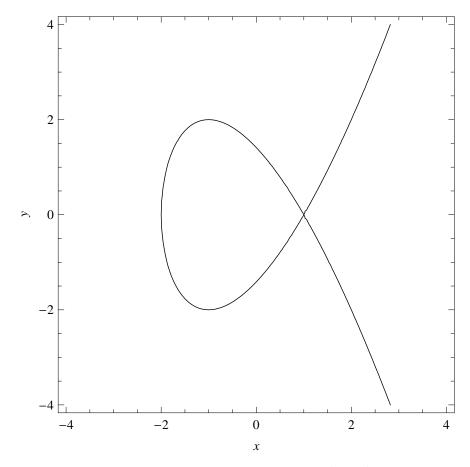

| 2.4  | Example of an elliptic curve $(y^2 = x^3 - 3x + 2)$ .                                   | 16 |

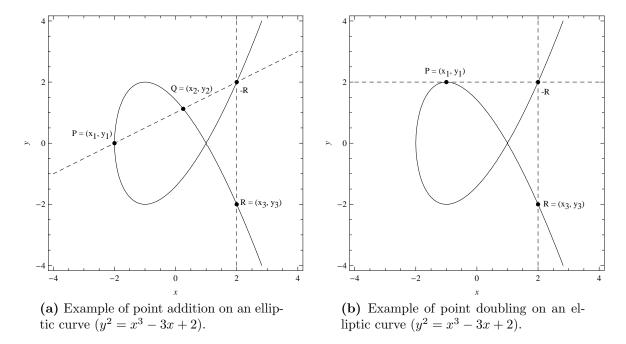

| 2.5  | Example of point operations on an elliptic curve.                                       | 17 |

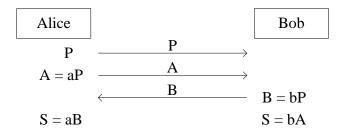

| 2.6  | Communication model with Elliptic Curve Diffie-Hellman (ECDH).                          | 22 |

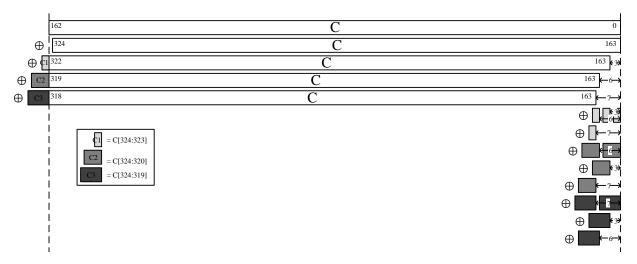

| 2.7  | Example of a polynomial of degree 324 reduced by $P(t) = t^{163} + t^7 + t^6 + t^3 + 1$ | 28 |

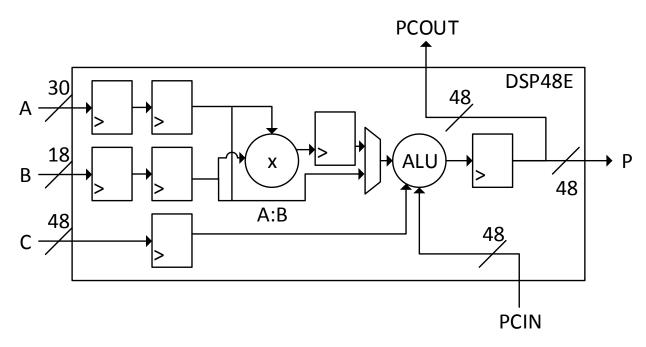

| 2.8  | Simplified block diagram of the DSP48E slice.                                           | 34 |

| 3.1  | ECC processor from Zhang et al. [14]                                                    | 40 |

| 3.2  | ALU of the ECC processor from Zhang et al. [14]                                         | 40 |

| 3.3  | Architecture of 2-stage Karatsuba-Ofman multiplier                                      | 42 |

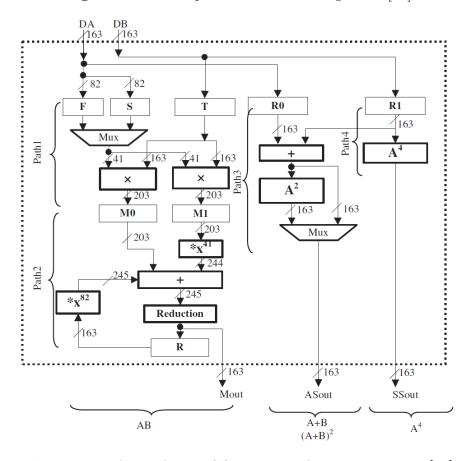

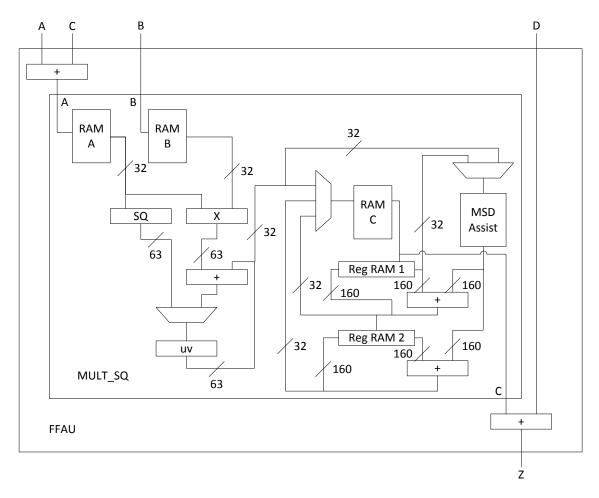

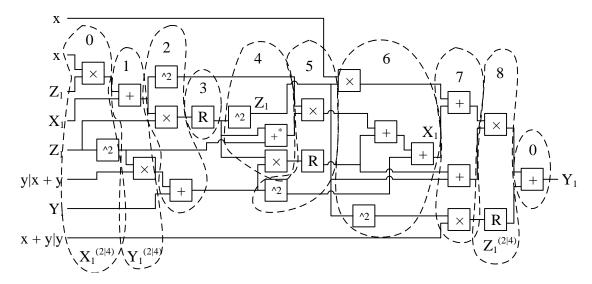

| 3.4  | Block diagram of the Finite Field Arithmetic Unit.                                      | 44 |

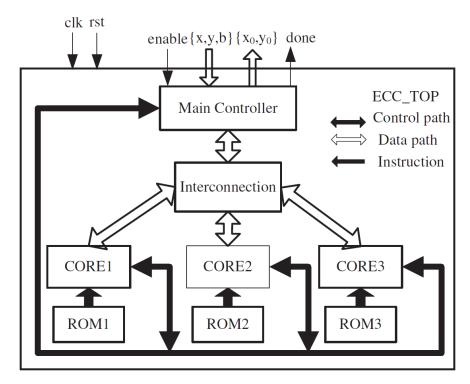

| 3.5  | Block diagram of the Koblitz ECP.                                                       | 45 |

| 3.6  | Block diagram of the FFAU of the Random ECP.                                            | 48 |

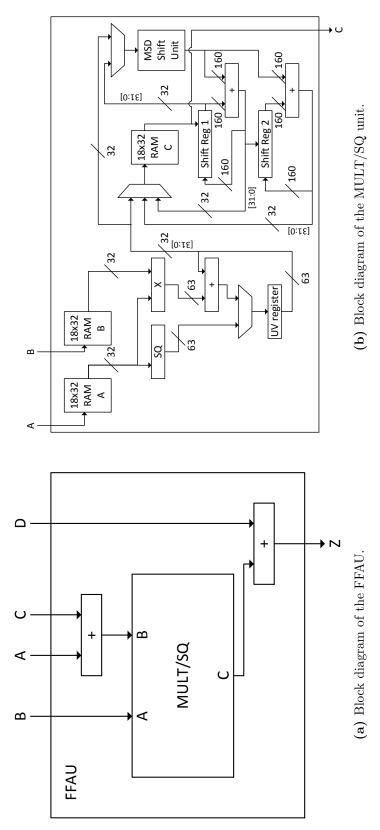

| 3.7  | Block diagram of Parallelized Finite Field Arithmetic Blocks.                           | 53 |

| 3.8  | The RAM addresses read in the MULT block for 163-bit operation.                         | 54 |

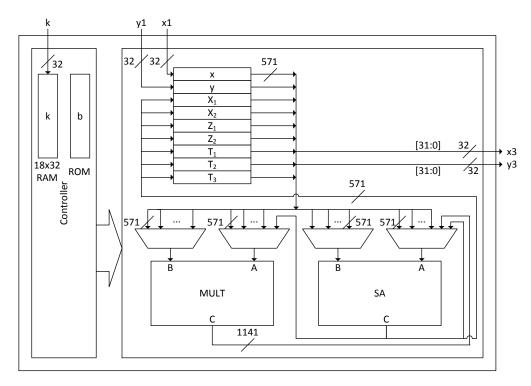

| 3.9  | Block diagram of the 1-MULT Koblitz ECP.                                                | 54 |

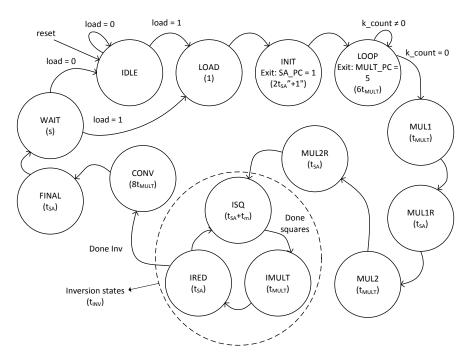

|      | FSM of the 1-MULT Koblitz ECP.                                                          | 55 |

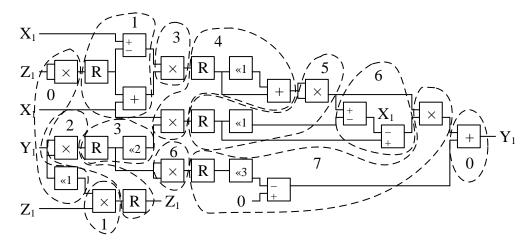

| 3.11 | Data dependency graph of PDQA for 1-MULT Koblitz ECP.                                   | 56 |

| 3.12 | Block diagram of the revised SA block to support 2 MULT blocks.                         | 58 |

| 3.13 | Block diagram of the 2-MULT Koblitz ECP.                                                | 60 |

| 3.14 | Block diagram of the 1-MULT Random ECP.                                                 | 62 |

| 3.15 | FSM of the 1-MULT Random ECP.                                                           | 63 |

| 3.16 | Data dependency graph of LOOP for the 1-MULT Random ECP.                                | 63 |

|      | Data dependency graph of coordinate conversion for the 1-MULT Random ECP.               | 64 |

|      | Block diagram of the 2-MULT Random ECP.                                                 | 66 |

|      | Block diagram of the Finite Field Arithmetic Blocks in the Low-Latency ECPs.            | 70 |

| 3.20 | Block diagram of the Low-Latency Random ECP.                                            | 71 |

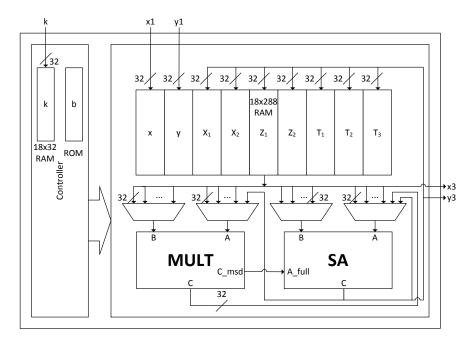

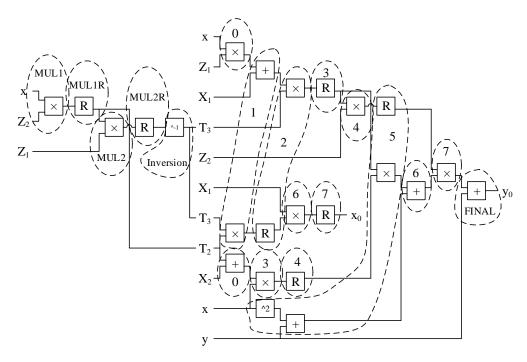

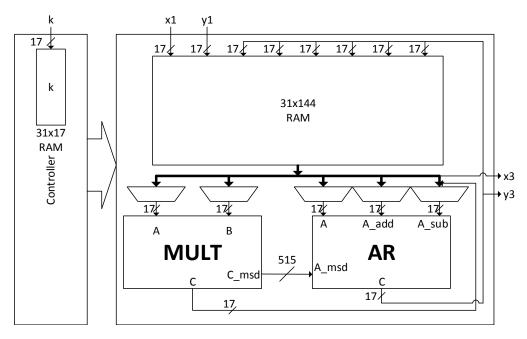

| 4.1  | Block diagram of the Finite Field Arithmetic Blocks in the Prime ECP.                   | 74 |

| 4.2  | Block diagram of the Prime ECP.                                                         | 77 |

| 4.3  | Data dependency graph of PDBL of the Prime ECP.                                         | 78 |

| 4.4  | Data dependency graph of PADD of the Prime ECP.                                         | 78 |

| 4.5  | FSM of the Prime ECP.                                                                   | 79 |

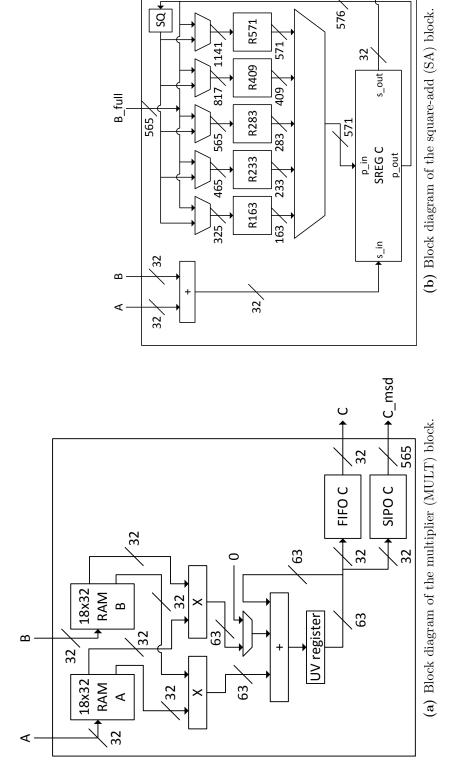

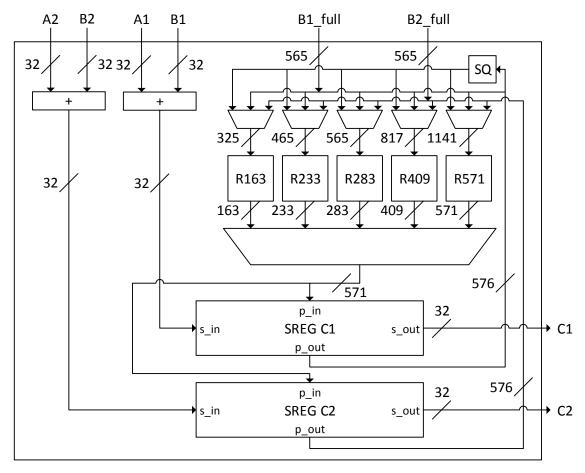

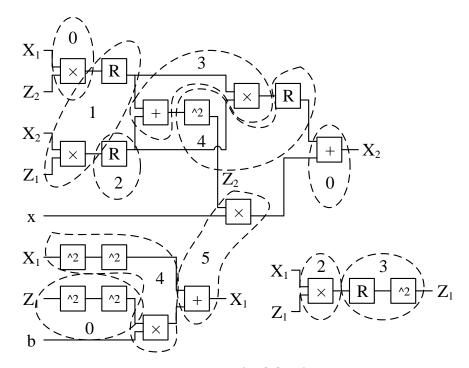

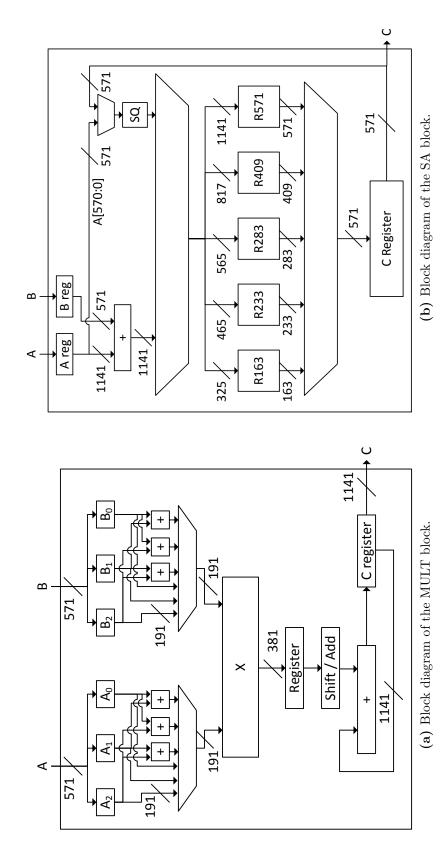

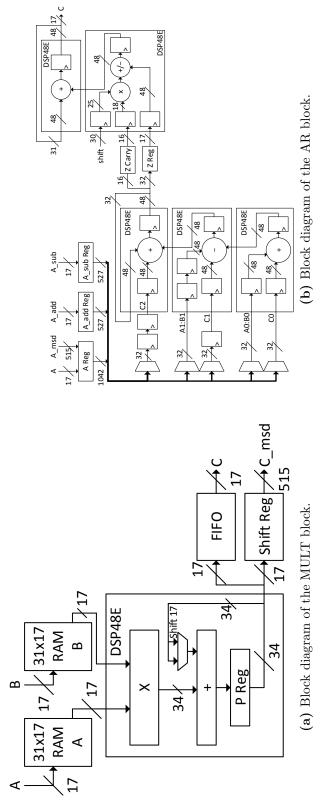

| 5.1  | Block diagram of the MULT block for the Scalable and Unified ECP.                       | 85 |

| 5.2  | Block diagram blocks used in the MULT block of the Scalable and Unified ECP.            | 86 |

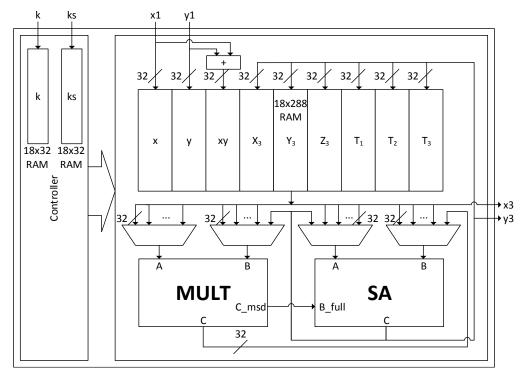

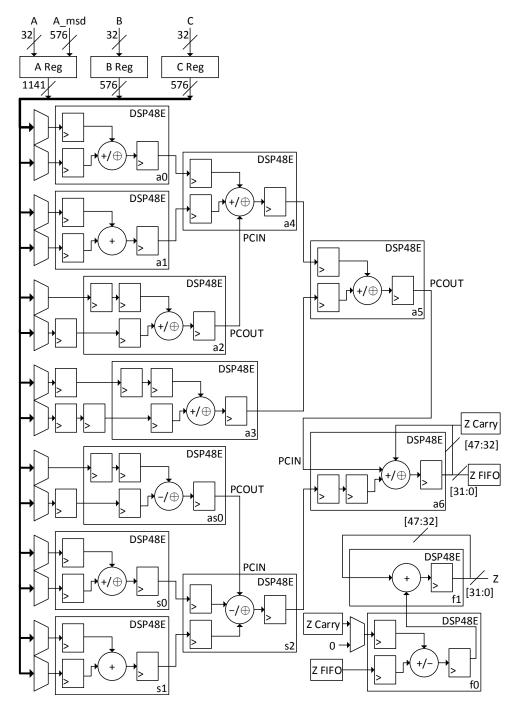

| 5.3  | Block diagram of the AR block for the Scalable and Unified ECP.                         | 88 |

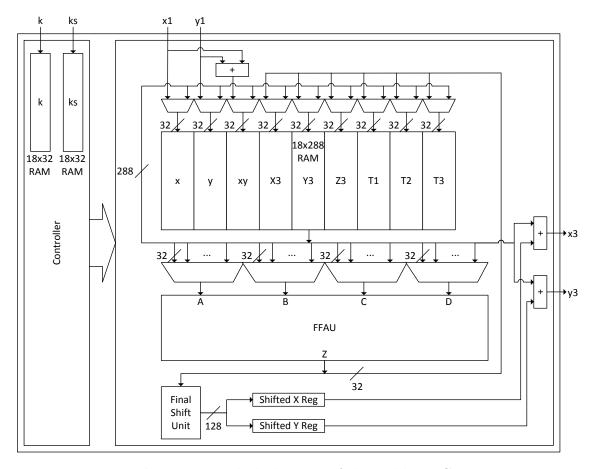

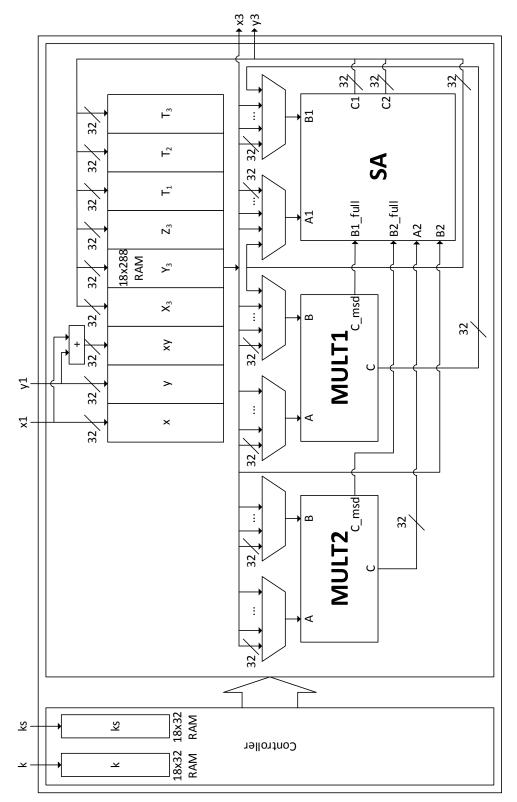

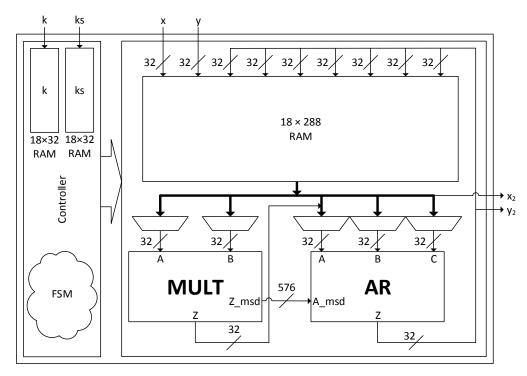

| 5.4  | Block diagram of the Scalable and Unified ECP.                                          | 90 |

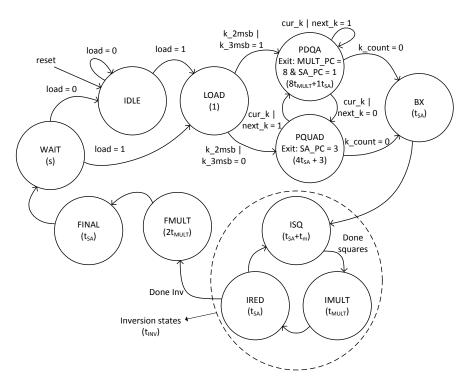

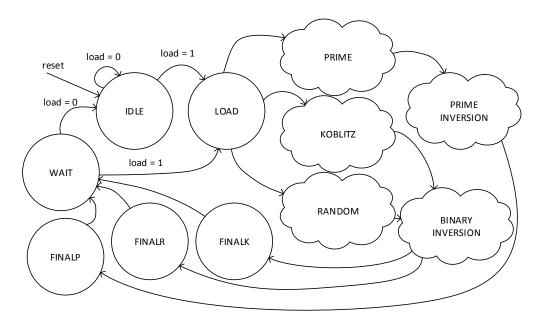

| 5.5 | FSM of the Scalable and Unified ECP.                               | 91  |

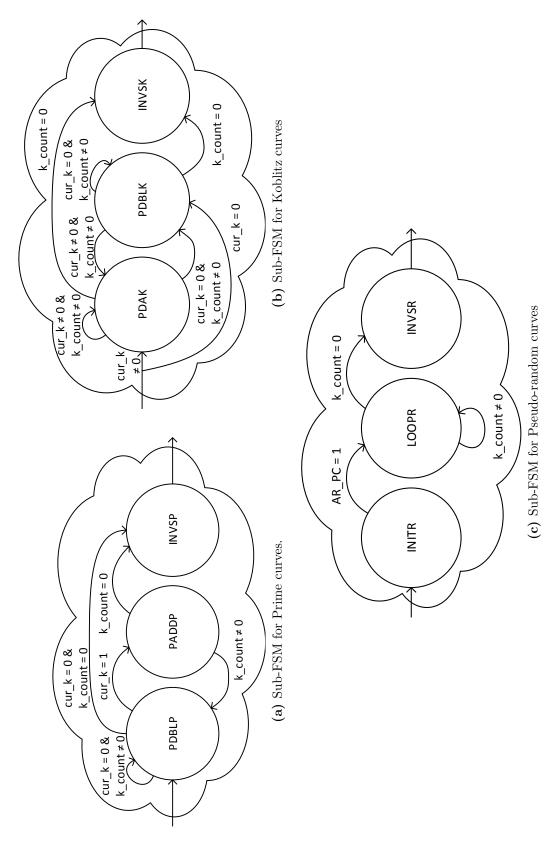

|-----|--------------------------------------------------------------------|-----|

| 5.6 | Sub-FSM for the main loop of the Scalable and Unified ECP.         | 92  |

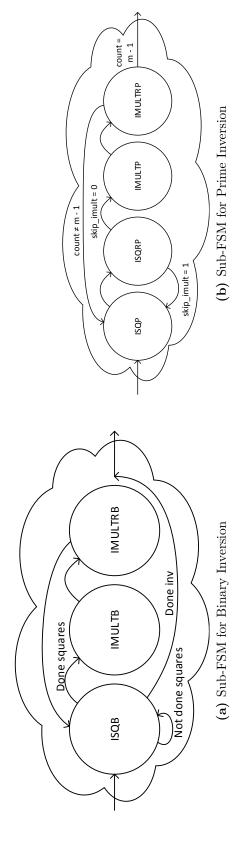

| 5.7 | Sub-FSM for inversion of the Scalable and Unified ECP.             | 97  |

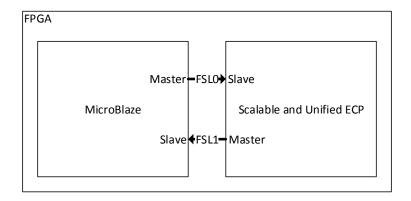

| 5.8 | Block diagram of the interface between the Microblaze and the ECP. | 102 |

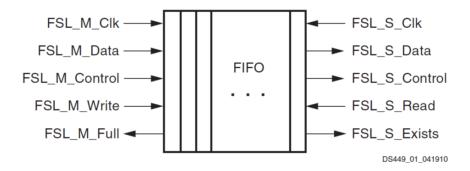

| 5.9 | Block diagram of Xilinx Fast Simplex Link (FSL) [69].              | 103 |

# LIST OF ALGORITHMS

| 2.1 | Left-to-right point multiplication                                    | 18  |

|-----|-----------------------------------------------------------------------|-----|

| 2.2 | Lopez-Dahab algorithm                                                 | 20  |

| 2.3 | $\tau$ NAF point multiplication on Koblitz Curves                     | 22  |

| 2.4 | Comba Multiplication                                                  | 25  |

| 2.5 | Binary inversion algorithm in binary fields                           | 31  |

| 2.6 | Binary inversion algorithm in prime fields                            | 33  |

| 7.1 | $\tau$ NAF conversion algorithm                                       | 110 |

| A.1 | Reduction by $P(t) = t^{163} + t^7 + t^6 + t^3 + 1$                   | 121 |

|     | Reduction by $P(t) = t^{233} + t^{74} + 1$                            | 122 |

| A.3 | Reduction by $P(t) = t^{283} + t^{12} + t^7 + t^5 + 1$                | 123 |

| A.4 | Reduction by $P(t) = t^{409} + t^{87} + 1$                            | 123 |

| A.5 | Reduction by $P(t) = t^{571} + t^{10} + t^5 + t^2 + 1$                | 124 |

| В.1 | Reduction modulo $p_{192} = 2^{192} - 2^{64} - 1$                     | 125 |

| B.2 | Reduction modulo $p_{224} = 2^{224} - 2^{96} + 1$                     | 125 |

| В.3 | Reduction modulo $p_{256} = 2^{256} - 2^{224} + 2^{192} + 2^{96} - 1$ | 125 |

| B.4 | Reduction modulo $p_{384} = 2^{384} - 2^{128} - 2^{96} + 2^{32} - 1$  | 126 |

|     | Reduction modulo $p_{521} = 2^{521} - 1$                              | 126 |

|     |                                                                       |     |

#### LIST OF ABBREVIATIONS

AHB Advanced High-performance Bus

ALU Arithmetic Logic Unit

ASIC Application-Specific Integrated Circuit

AU Arithmetic Unit BRAM Block RAM

CLB Configurable Logic Block

DSA Digital Signature Algorithm

DSP Digital Signal Processing

EC Elliptic Curve

ECC Elliptic Curve Cryptography ECDH Elliptic Curve Diffie-Hellman

ECDSA Elliptic Curve Digital Signature Algorithm

ECP Elliptic Curve Processor

ECPM Elliptic Curve Point Multiplication

FF Finite Field

FFAU Finite Field Arithmetic Unit

FIFO First-In First-Out

FIPS Federal Information Processing Standards

FPGA Field-Programmable Gate Array

FSL Fast Simplex Link FSM Finite State Machine

GF Galois Field

HSC Hardware/Software Co-designIBE Identity-Based Encryption

LD Lopez-Dahab

LSB Least-Significant Bit LSD Least-Significant Digit

LUT Look-Up Table

MSB Most-Significant Bit

MSD Most-Significant Digit

NIST National Institute of Standards and Technology

PADD Point Addition

PDA Personal Digital Assistant

PDBL Point Doubling

PFRB Point Frobenius Endomorphism

PKG Private Key Generator RAM Random Access Memory

RFID Radio Frequency Identification

RNS Residue Number System RSA Rivest-Shamir-Adleman

SA Square-Add

SECG Standards for Efficient Cryptography Group SIPO Serial-In Parallel-Out

SSL Secure Socket Layer

TLS Transport Layer Security

XOR Exclusive OR

#### LIST OF PUBLICATIONS

- [50] K.C.C. Loi and S. B. Ko, "Improvements for High Performance Elliptic Curve Cryptosystems Processor over  $GF(2^{163})$ ", International Symposium on Electronic System Design (ISED), pp. 140 144, December 2012.

- [51] K.C.C. Loi and S.B. Ko, "High Performance Scalable Elliptic Curve Cryptosystem Processor for Koblitz Curves", *Microprocessors and Microsystems*, Elsevier, Volume 37, Issues 4 5, pp. 394 406, June July 2013.

- [52] K.C.C. Loi and S.B. Ko, "High Performance Scalable Elliptic Curve Cryptosystem Processor in  $GF(2^m)$ ", International Symposium on Circuits and Systems (ISCAS), pp. 2585 2588, May 2013.

- [53] K.C.C. Loi, S. An and S.B. Ko, "FPGA Implementation of Low Latency Scalable Elliptic Curve Cryptosystem Processor in  $GF(2^m)$ ", International Symposium on Circuits and Systems (ISCAS), pp. 822 825, June 2014.

- [54] K.C.C. Loi and S.B. Ko, "Scalable Elliptic Curve Cryptosystem FPGA Processor for NIST Prime Curves", *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, accepted for future publication.

- [67] K.C.C. Loi and S.B. Ko, "Parallelization of Scalable Elliptic Curve Cryptosystem Processors in  $GF(2^m)$ ", *IEEE Transactions on Computers*, draft submitted to journal for peer review.

- [68] K.C.C. Loi and S.B. Ko, "Efficient Scalable and Unified Elliptic Curve Cryptography Coprocessor using DSP Slices on FPGAs", *IEEE Transactions on Industrial Electronics*, draft submitted to journal for peer review.

#### Chapter 1

#### Introduction

The growth of secure online transactions in recent years has created a demand for higher security needs for information transmitted over the Internet, which requires servers of online service providers to process a large number data coming from all the users. In addition, in today's fast-paced society, increasing security at the expense of the users' long wait times for the information to be processed is not desirable. Thus, this thesis looks to improve on the current cryptographic processors to provide a high-speed and secured communication channel for data transmission.

One of the protocols used to establish such a secure channel is the Secure Socket Layer (SSL) or its successor Transport Layer Security (TLS) protocol [1]. The SSL protocol can be separated into two stages: handshaking and bulk-data. In the handshaking stage, the client and the server exchange messages in order to establish a shared secret key using public-key cryptography. The shared secret key is in turn used in the bulk-data stage, which uses private-key cryptography. Generally, public-key cryptography is only used during the handshaking stage due to its computational complexity compared to private-key cryptography. However, even though SSL reduces the number of public-key cryptographic operations by transmitting data using private-key cryptography and by supporting reuse of previously established keys, public-key cryptography is still the most time consuming operation in the transmission channel [2]. Thus, in order to accelerate processing of the public-key cryptography operations, secure server systems offload these complex operations into faster running hardware platforms, such as SSL accelerator cards or standalone SSL processing units [3]. Companies, such as Elliptic Technologies<sup>1</sup> and Broadcom<sup>2</sup>, have created such products that either support

<sup>1</sup>http://www.elliptictech.com/

<sup>&</sup>lt;sup>2</sup>http://www.broadcom.com/

**Table 1.1:** Comparison between ECC and RSA Security [13]

| Symmetric | ECC | RSA   | Protection Lifetime |

|-----------|-----|-------|---------------------|

| 80        | 163 | 1024  | Until 2010          |

| 112       | 233 | 2048  | Until 2030          |

| 128       | 283 | 3072  | Beyond 2030         |

| 192       | 409 | 7680  |                     |

| 256       | 571 | 15360 |                     |

the complete SSL protocol [4, 5, 6, 7] or simply some of the underlying operations [8, 9].

In recent years, the use of elliptic curve cryptography (ECC) for public-key cryptography has been increasingly popular among researchers and industry members. ECC was independently proposed by Miller [10] and Koblitz [11] in the 1980s. The advantage of ECC over the more commonly used Rivest-Shamir-Adleman (RSA) [12] algorithm for public-key cryptography is that ECC allows for reduced key sizes while providing a similar level of security. Table 1.1 [13] shows the comparison of the key sizes for symmetric-key and public-key cryptosystems and their respective protection lifetimes. The security levels shown assume that the adversary has computational powers limited to the state-of-the-art at the time (i.e. computational security), as opposed to informational theoretic security where the algorithms can be proven to be secure. The shorter key sizes allow implementations of ECC to be more efficient either in terms of higher throughput or lower area. Higher throughput implementations can be found in applications where high speeds are required, such as network servers, at the expense of area and power consumptions [14, 15]. In more restricted environments, such as Personal Digital Assistant (PDA), cell phones and Radio Frequency Identification (RFID) readers [16, 17], the design goal becomes to reduce the area and power consumptions at the expense of lower throughput. Due to these advantages, ECC has been adopted by many standards, such as National Institute of Standards and Technology (NIST) [18], Standards for Efficient Cryptography Group (SECG) [19], and Federal Information Processing Standards (FIPS) 186-3 [20].

In particular, NIST [18] and SECG [19] recommend the use of different specific named curves to be used for various purposes. For example, the United States National Security

# Protocol Point Multiplication Point Addition/Doubling Finite Field Arithmetic

Figure 1.1: Levels of abstraction in ECC implementations

Agency (NSA) chose to use prime field elliptic curves of key size 256, 384 and 521 published by NIST [18] for both classified and unclassified information [21]. These recommended curves can be divided into two categories: prime Galois fields (or prime fields), GF(p), and binary Galois fields (or binary fields),  $GF(2^m)$ . Furthermore, the binary field curves can be further divided into pseudo-random and Koblitz curves. In order to maximize the usability of a server, it should be able to support all the named curves recommended by the standards. Thus, this thesis investigates scalable and unified ECC processor architectures that can support all the curves recommended by NIST [18].

Offloading complex public-key cryptography operations to hardware can take place in any level of abstraction shown in Figure 1.1. In other words, hardware accelerator implementations can range from offloading only the finite field arithmetic operations to hardware and implementing all the overlaying levels in software to implementing a complete protocol, such as Elliptic Curve Digital Signature Algorithm (ECDSA) or Elliptic Curve Diffie-Hellman (ECDH), including all its underlying levels in hardware, such that the interface merely needs to input the message to be signed, in case of ECDSA, and the module outputs the resultant signed message.

In this thesis, scalability is defined as the ability for the design to be able to support a range of key sizes without the need to redesign or reprogram the hardware, and a unified design is one that is able to compute both GF(p) and  $GF(2^m)$  operations using the same hardware. Designing a scalable and unified ECC processor improves the efficiency of the hardware utilization, since the same hardware is able to handle both primes and binary fields

and a range of key sizes without the need for any human intervention.

The remainder of this chapter is organized as follows: Section 1.1 looks at the current literature on scalable and unified ECC processors; Section 1.2 further discusses the motivation of this thesis; Section 1.3 describes the research problem and the major contributions of this thesis; and Section 1.4 outlines the organization of the remainder of this thesis.

#### 1.1 Literature Review of ECC Processors

Savas et al. [22] proposed a scalable and unified multiplier in 2000, which uses the Montgomery multiplication algorithm and it can handle operands of any size, but requires precomputations and transformations. The design has been implemented on application-specific integrated circuit (ASIC). Furthermore, it only offloads the finite field arithmetic. In [23], two more dual-field multiplier architectures are presented by Savas et al. that use precomputation technique and dual-radix design to achieve faster computation times in both fields at the expense of larger area utilization on ASIC.

In 2004, Chelton and Benaissa [24] propose a scalable arithmetic unit that can operate over any field in  $GF(2^m)$ , but not prime fields. It proposes architectures for both a scalable multiplier and a scalable divider that can be used in a ECC processor, but does not design the complete processor.

In [25], Tanimura et al. propose a hardware implementation of the Montgomery multiplication in ASIC using 4 parallel radix- $2^{16}$  multipliers in GF(p) and a radix- $2^{64}$  multiplier in  $GF(2^m)$  in order to balance the time delay difference when computing prime field and binary field arithmetic in hardware.

In 2009, Chiou et al. [26] propose a scalable unified multiplier architecture for both fields, but it only supports prime fields of modulo  $P = 2^m - 1$  and all-one polynomials (AOP), which most NIST [18] and SECG [19] recommended curves are not.

In all of the above describe implementations, only the finite field arithmetic is offloaded into hardware. Hardware implementations of designs that also include higher levels of abstraction are described below.

In 2001, Goodman and Chandrakasan [27] describes a microcode-based design that im-

plements finite field arithmetic in both fields, point addition, point doubling and point multiplication. The design is implemented using ASIC and provides an energy-efficient solution. It also uses the Montgomery multiplication algorithm.

In 2003, Satoh and Takano [28] propose a scalable dual-field processor that supports any prime or binary field, but only shows results up to 256 bits. The design uses Montgomery multiplication algorithm and is implemented on ASIC. It also supports protocol level operations, such as DSA and ECDSA.

In 2008, Wang et al. [29] present a coprocessor that operates over both fields that is capable of performing both RSA and ECC operations. The implemented arithmetic unit includes multiplication, addition, subtraction and inversion for both prime and binary fields. However, the design only supports 1 field size at a time. Implementation results are presented for both field programmable gate array (FPGA) and ASIC platforms.

In 2008, Lai and Huang [30] proposed a dual-field coprocessor that supports arbitrary prime or binary fields and arbitrary elliptic curves. It optimizes the scheduling of the point operations to increase performence. However, the buffer size of the processor limits the key size of the processor. The paper only presents results up to 256-bit key sizes. Lai and Huang have also presented 2 other designs that improve on the first one in [31, 32].

Chen et al. [33] propose a unified design for both RSA and ECC. The authors implement a microcode-based architecture, where 3 tiers of instruction sets can be executed depending on desired level of abstraction in RSA or ECC operations. Furthermore, the proposed design does not support prime field operations in ECC. The processor is optimized for modular exponentiation in GF(p) and arithmetic in  $GF(2^m)$ . Therefore, in order to support GF(p) in ECC, it would require support for addition, subtraction, inversion, in addition to multiplication that it currently implements. By doing so, the critical path of the processor would increase, considerably due to the carry propagation of the addition and subtraction.

In [34], Chen et al. propose a 160-bit and 256-bit unified ECC processor implemented on ASIC that can support both fields. It uses a radix-4 division unit to increase the speed of the calculations. However, the processor is not a scalable design.

Lee et al. [35] present a dual-field heterogeneous processing element architecture, where one processing unit performs multiplication-addition/subtraction and the other evaluates all of the above plus division.

There are also architectures in the current literature, which are not unified but are scalable. These designs either implement the ECC processor (ECP) in binary or in prime fields. The binary field ECPs are discussed first. In 2006, Benaissa and Lim [36] proposed a scalable ECC processor that uses a digit-serial multiplier and squaring unit. Thus, the design is scalable and can support multiple fields. In 2009, Hassan and Benaissa [37] proposed a scalable ECC processor that uses the PicoBlaze soft-core microcontroller in Xilinx FPGAs to implement the design using the hardware/software co-design (HSC) approach. The motivation is to design a processor that can handle the elliptic curves up to the 193-bit key size suggested in SECG [19] without the need to reconfigure the hardware. The design goal is to reduce area consumption for area constrained platforms, such as RFID, mobile handsets, smart cards, and wireless sensor networks [37]. Since then, Hassan and Benaissa have also proposed scalable designs that support curves up to 571 bits recommended by the National Institute of Standards and Technology (NIST) [38, 17, 39] also for area-constrained environments.

The design proposed in [40] is also a HSC scalable ECC processor, where the authors use the on-chip PowerPC in Virtex-4 FX series to build the system. However, the reconfiguration of the portion that computes the elliptic curve point multiplication (ECPM) is dynamically reloaded at run time using partial reconfiguration technology on Virtex FPGAs.

The following ECP designs present scalable ECPs in prime fields. In 2006, McIvor et al. [41] presented an ECP that can compute the ECPM over prime fields with less than 256 bits based on a new unified modular inversion algorithm. It is one of the fastest prime field ECPs at the time and it can perform a 256-bit ECPM in 3.86 ms on a Virtex-2 Pro FPGA. One of the strengths of [41] is that it can evaluate ECPM for any curve. However, it cannot evaluate all NIST recommended prime field curves because it can only support up to 256-bits. If the design is extended to 521 bits, hardware utilization will increase immensely and the maximum clock frequency might also suffer due to more difficult routing in the FPGA. Thus, in [42], Ananyi et al. proposed a scalable ECP that can support curves up to 521 bits, but only for NIST recommended prime fields, as opposed to any curve up to 521 bits. The advantage of only supporting NIST recommended curves is the ability to take advantage of the prime moduli selected by NIST, which can be reduced very easily, requiring fewer

hardware resources compared to using Montgomery multiplications and inversions as in [41].

Similar to [41], the authors in [42] chose a very wide datapath, using 265 bits for the modular adder, subtractor and multiplier and using 521 bits for the modular inverter. As a result, the implemented design on a Xilinx Virtex-4 FPGA uses 20,793 slices and 32 DSP48 blocks and only runs at 60 MHz. It can compute ECPM for 192-, 244-, 256-, 384-, and 521-bit curves in 4.8 ms, 5.8 ms, 6.9 ms, 19.9 ms, and 45.6 ms, respectively. In 2011, the authors in [43] developed MicroECC, which only has 16- or 32-bit datapaths to make the implementation much smaller and faster.

There are also designs that are neither scalable nor unified. These target a specific curve and can have very optimized designs. In [14], the authors present a highly efficient ECP for the 163-bit pseudo-random curve recommended by NIST. The design uses parallel cores to perform arithmetic. The ECPs in [44] are specifically designed for 163, 233 and 283-bit Koblitz curves recommended by NIST. The design uses 4 parallel multipliers to improve the performance of the ECPM operation. In 2008, Güneysu and Paar [45] optimized the architecture of the ECP using high performance Digial Signal Processing (DSP) slices on FPGAs. In [46], the authors developed a side channel attack resistant ECP using the double-and-add-always algorithm. The authors of [47] and [48] use the residue number system (RNS) to parallelize the operations in the ECP.

A summary of the works reviewed in this section is provided in Table 1.2. The table describes the technology used and the level of abstraction implemented on hardware. It indicates whether or not the designs are scalable and the finite field that is supported. Finally, some brief remarks are provided about each work.

#### 1.2 Motivation

In the works described in Section 1.1, there are no designs that are scalable and unified for all 15 elliptic curves recommended by NIST [18] on the same hardware. Many ECC implementations in literature are highly optimized designs. Many of the architectures presented are flexible, where a different field or key length can be implemented by scaling the proposed architecture accordingly. However, this results in larger designs when implementing the larger

**Table 1.2:** Summary of ECPs in the Current Literature

| Work  | Tech.    |            | Scalable | Field   | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-------|----------|------------|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [22]  | ASIC     | Multiplier | Yes      |         | Montgomery multiplication.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| [23]  | ASIC     | Multiplier | Yes      | Unified | • 2 multipliers: precomputation; duual-radix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| [24]  | FPGA     | AU         | Yes      | Binary  | HSC: Control in software, arithmetic in hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| [25]  | ASIC     | Multiplier | Yes      |         | • 4 parallel radix-2 <sup>16</sup> . multipliers in prime                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| . ,   |          | 1          |          |         | • Radix-2 <sup>64</sup> multiplier in binary.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| [26]  | N/A      | Multiplier | Yes      | Unified | • prime number has the form $2^m - 1$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| [ -]  | <b>'</b> |            |          |         | • Irreducible polynomial is an all one polynomial.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| [27]  | ASIC     | ECPM       | Yes      | Unified | Microcode-based design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| [-,]  |          |            |          |         | • Energy efficient.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| [28]  | ASIC     | Protocol   | Yes      | Unified | Arbitrary prime number and irreducible polynomial.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| [=0]  | 11010    | 11000001   | 100      |         | • Uses 64-bit multipliers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| [29]  | ASIC &   | ECPM       | No       | Unified | • Supports RSA and ECC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| [20]  | FPGA     | LOIW       | 110      | Cinnea  | <ul> <li>Uses signed-digit number representation.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| [30]  | ASIC &   | ECPM       | No       | Unified | Arbitrary elliptic curve and finite field.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

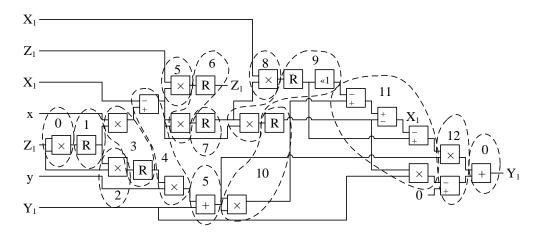

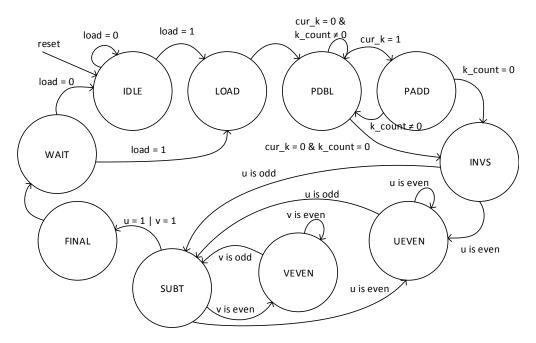

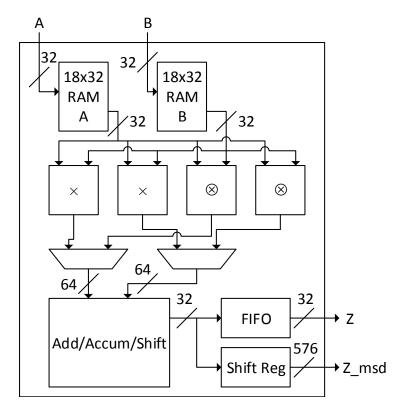

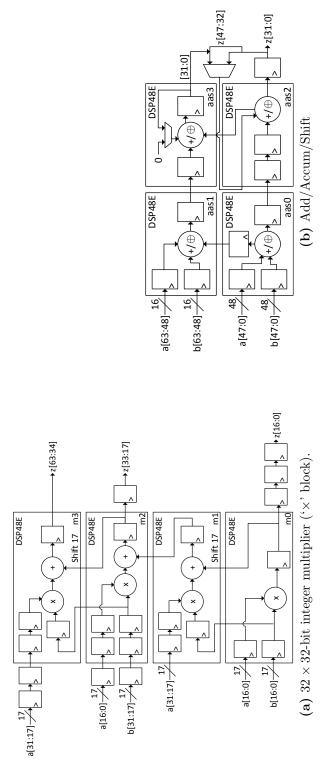

| [90]  | FPGA     |            | 110      | Onnied  | <ul> <li>4 32-bit multipliers and 4 64-bit adders.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |