# UNIVERSIDADE FEDERAL DE SANTA CATARINA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

#### Gabriel Maicon Marcílio

# Verificação Funcional Pós-Particionamento em Sistemas Integrados de Hardware e Software

Dissertação submetida à Universidade Federal de Santa Catarina como parte dos requisitos para a obtenção do grau de Mestre em Ciência da Computação.

Luiz Cláudio Villar dos Santos, Dr. (orientador)

Florianópolis, dezembro de 2008

# Verificação Funcional Pós-Particionamento em Sistemas Integrados de Hardware e Software

#### Gabriel Maicon Marcílio

| Esta Dissertação foi julgada adequada para a obtenção do título de Mestre em Ciên- |

|------------------------------------------------------------------------------------|

| cia da Computação na área de concentração "Sistemas de Computação" e aprovada      |

| em sua forma final pelo Programa de Pós-Graduação em Ciência da Computação.        |

|                                                                                    |

|                                                                                    |

| Frank Siqueira                                                                     |

|                                                                                    |

|                                                                                    |

| Banca Examinadora                                                                  |

|                                                                                    |

| Luiz Cláudio Villar dos Santos, Dr. (orientador)                                   |

|                                                                                    |

| Flávio Rech Wagner, Ph.D.                                                          |

| riavio Recii wagner, i ii.D.                                                       |

|                                                                                    |

| Sandro Rigo, Dr.                                                                   |

|                                                                                    |

Carlos Barros Montez, Dr.

The road goes ever on and on.

Down to the door where it began.

-Bilbo Baggins

À minha família

# Agradecimentos

Ao professor Sandro Rigo e a Bruno Albertini que cederam a infraestrutura de implementação utilizada neste trabalho.

Aos membros do LAPS e do LABSOFT por todo auxílio prestado.

À Minha mãe Albertina da Silva, meu irmão Marcos P. Marcílio e meu pai João P. Marcílio e a Karine M. Arasaki pela compreensão, estímulo, amor, paciência e incentivo.

Ao Professor Dr. Luiz Cláudio Vilar dos Santos pela orientação e incentivo que tornaram este trabalho possível.

Ao Brasil Test Center (BTC) da Motorola Industrial do Brasil pelo fomento parcial à produção deste trabalho, com bolsa paga no âmbito do projeto Test Automation.

À CAPES, no âmbito do Programa Nacional de Cooperação Acadêmica, pelo custeio parcial da execução deste trabalho (Processo nº 0326054).

# Sumário

| Li               | sta d | le Figuras                                             | ix  |

|------------------|-------|--------------------------------------------------------|-----|

| Li               | sta d | le Tabelas                                             | x   |

| Li               | sta d | le Acrônimos                                           | xi  |

| Li               | sta d | le Símbolos                                            | xii |

| $\mathbf{R}_{0}$ | esum  | 10                                                     | xiv |

| $\mathbf{A}$     | bstra | act                                                    | xv  |

| 1                | Intr  | rodução                                                | 1   |

|                  | 1.1   | O contexto histórico                                   | 1   |

|                  | 1.2   | O projeto baseado em plataforma                        | 2   |

|                  | 1.3   | O projeto em nível de sistema                          | 3   |

|                  | 1.4   | A verificação de sistemas                              | 5   |

|                  | 1.5   | O problema-alvo e a abordagem proposta                 | 7   |

|                  | 1.6   | O efeito da não-preservação da ordem de comportamentos | 12  |

|                  | 1.7   | Um exemplo ilustrativo                                 | 13  |

|                  | 1.8   | O escopo e a contribuição desta dissertação            | 16  |

|                  | 1.9   | A organização desta dissertação                        | 18  |

| 2                | Tra   | balhos correlatos                                      | 19  |

|                  | 2.1   | Principais abordagens para verificação funcional       | 19  |

|   |      |         |                                                 | vii       |

|---|------|---------|-------------------------------------------------|-----------|

|   |      | 2.1.1   | Verificação formal                              | 19        |

|   |      | 2.1.2   | Verificação dinâmica                            | 22        |

|   |      | 2.1.3   | Suporte à verificação em plataformas comerciais | 23        |

|   | 2.2  | Outro   | s mecanismos de suporte à verificação           | 24        |

|   | 2.3  | Abord   | lagens para a não-preservação da ordem          | 25        |

|   | 2.4  | A pers  | spectiva de uma abordagem alternativa           | 27        |

| 3 | Mod  | delage  | m do problema                                   | 29        |

|   | 3.1  | Propri  | iedades da relação entre RGM e DUV              | 29        |

|   | 3.2  | Formu   | ılação do problema-alvo                         | 32        |

|   | 3.3  | Garan   | tias teóricas decorrentes da formulação         | 35        |

| 4 | A to | écnica  | de verificação proposta                         | 41        |

|   | 4.1  | O algo  | pritmo proposto                                 | 41        |

|   | 4.2  | Garan   | tias de verificação da técnica proposta         | 48        |

|   |      | 4.2.1   | Análise de falso negativo                       | 48        |

|   |      | 4.2.2   | Análise de falso positivo                       | 49        |

|   |      | 4.2.3   | Discussão                                       | 51        |

| 5 | Imp  | olemen  | tação e resultados experimentais                | <b>54</b> |

|   | 5.1  | Imple   | mentação                                        | 54        |

|   | 5.2  | Result  | cados experimentais                             | 57        |

|   |      | 5.2.1   | Infra-estrutura e configuração experimental     | 58        |

|   |      | 5.2.2   | Cenário 1: eventos não ordenados                | 59        |

|   |      | 5.2.3   | Cenário 2: eventos totalmente ordenados         | 62        |

|   |      | 5.2.4   | Cenário 3: eventos parcialmente ordenados       | 64        |

|   | 5.3  | Discus  | ssão                                            | 68        |

| 6 | Con  | ıclusõe | es e perspectivas                               | 71        |

|   | 6.1  | Concl   | usões                                           | 71        |

|   | 6.2  | Perspe  | ectivas de trabalhos futuros                    | 74        |

**7**9

| $\mathbf{T}$ | c    | ^          | •    | $\mathbf{D} \cdot \mathbf{i}$ | •     | , ,                           |    |

|--------------|------|------------|------|-------------------------------|-------|-------------------------------|----|

| ~            | Oto: | $n \cap n$ | 0100 | Ribi                          | 100   | ráfica                        | 20 |

|              | EIE  |            | เปลอ | 1 )   1 / 1                   | שנווו | $\mathbf{I}$ and $\mathbf{C}$ | 15 |

|              |      |            |      |                               | ~~~   |                               |    |

# Lista de Figuras

| 1.1        | O fluxo de projeto usando a abordagem ESL                                                                                       | 4  |

|------------|---------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2        | Um exemplo de ambiente de verificação                                                                                           | 7  |

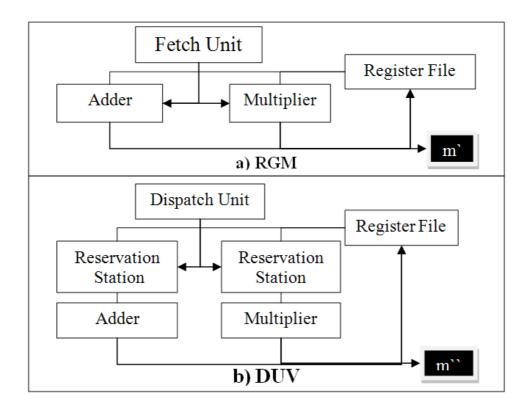

| 1.3        | Uma representação para o modelo de referência                                                                                   | 8  |

| 1.4        | Uma representação para o DUV                                                                                                    | 9  |

| 1.5        | Uma representação para o gerador de estímulos                                                                                   | 10 |

| 1.6        | Um grafo bipartido e um casamento próprio                                                                                       | 11 |

| 1.7        | Exemplo de execução fora de ordem                                                                                               | 14 |

| 1.8        | Representação do co-processador hipotético                                                                                      | 15 |

| 2.1<br>2.2 | Estrutura de um <i>scoreboard</i> (extraído e adaptado de [BER 05]) O impacto da limitação temporal na qualidade da verificação |    |

| 3.1        | Correlação entre topologia e causalidade                                                                                        | 34 |

| 3.2        | Componente conexo impróprio induzido por aresta imprópria                                                                       | 39 |

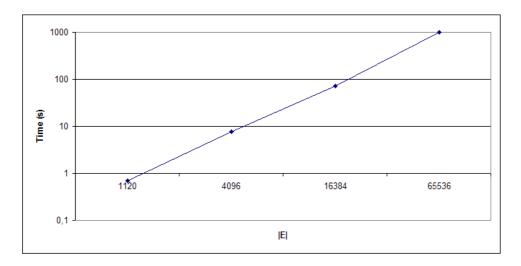

| 5.1        | Análise do tempo de execução                                                                                                    | 56 |

| 5.2        | Estrutura do experimento                                                                                                        | 68 |

| 5.3        | Resultados do experimento                                                                                                       | 69 |

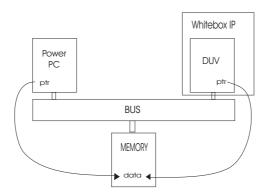

| 6.1        | IP com um ponteiro para acessar um dado na memória                                                                              | 75 |

# Lista de Tabelas

| 5.1 | Cenário 1 - Casamento encontrado                      | 59 |

|-----|-------------------------------------------------------|----|

| 5.2 | Cenário 1 - Casamento completo não encontrado         | 61 |

| 5.3 | Cenário 2 - Casamento próprio encontrado              | 62 |

| 5.4 | Cenário 2 - Casamento próprio não encontrado          | 63 |

| 5.5 | Cenário 3 - Casamento próprio encontrado              | 65 |

| 5.6 | Cenário 3 - Casamento próprio não encontrado (caso 1) | 66 |

| 5.7 | Cenário 3 - Casamento próprio não encontrado (caso 2) | 67 |

# Lista de Acrônimos

**DUV:** Device Under Verification

**EDA:** Electronic Design Automation

**ESL:** Electronic System Level

**IP:** Intellectual Property

**PBD** Platform-Based Design

RTL: Register-Transfer Level

**SoC:** System-on-Chip

TTM: Time-to-Market

**RGM:** Reference Golden Model

**SAT:** Satisfability (Boolean satisfiability problem)

## Lista de Símbolos

| N. | lonitor | $\mathbf{e}$ | seus | espel | hos: |

|----|---------|--------------|------|-------|------|

|----|---------|--------------|------|-------|------|

m: Um monitor

$m^+$ : Instância do monitor m no modelo de referência

$m^-$ : Instância do monitor m no DUV

Instâncias de módulo:

I: Instância de um módulo de uma plataforma

$I^+$ : Representação do modelo de referência de um módulo I

$I^-$ : Representação do modelo sob verificação de um módulo I

Relações:

$u \approx v$ : Os valores u e v monitorados são compatíveis

R: Relação de precedência entre eventos no RGM

Funções:

μ: Um mapeamento próprio

BVG(m): Grafo bipartido de verificação associado ao monitor m

Adj(v): Conjunto de vértices adjacentes ao vértice v

Adj(S): Conjunto dos vértices adjacentes aos vértices do conjunto S

Elementos de Grafos:

$V^+$ : Conjunto de eventos monitorados no RGM

$V^-$ : Conjunto de eventos monitorados no DUV

E: Conjunto de arestas de um grafo

M: Um casamento arbitrário

M: Um casamento próprio para o BVG

$C_j$ : Componente conexo de um grafo bipartido  $V_j$ : Conjunto de vértices de um componente conexo  $E_j$ : Conjunto de arestas de um componente conexo

|Adj(v)|: Grau do vértice v

# Resumo

O escopo tradicional da verificação funcional foi ampliado com o surgimento dos fluxos de projeto em nível de sistema eletrônico (ESL). Nesses fluxos, logo após o particionamento hardware-software, a verificação precisa lidar com tipos abstratos de dados, com artefatos de implementação e com a possível não-preservação, no dispositivo sob verificação (DUV), da ordem dos comportamentos no modelo de referência (golden model). As técnicas existentes para verificação pósparticionamento estão limitadas pelo uso de heurísticas (que colocam em risco as garantias de verificação) ou por abordagens black-box (que restringem a observabilidade).

Este trabalho adota uma abordagem white-box e propõe uma nova técnica que opera sobre amostras de dados capturadas por monitores e armazenadas na forma dos assim-chamados logs. Para cada ponto a ser verificado, inserem-se monitores espelhados: um no modelo de referência, outro no DUV. A verificação automática dos logs é formulada com um problema de casamento (matching) em um grafo bipartido. O problema clássico foi modificado para capturar não apenas a compatibilidade de valores monitorados, mas também a precedência de eventos, de forma a viabilizar o tratamento da não-preservação da ordem no DUV.

A formulação adotada permitiu provar várias propriedades, as quais foram utilizadas como base teórica para determinar as garantias de verificação da técnica proposta. A implementação dos monitores utilizou infra-estrutura pré-existente baseada em reflexão computacional. São apresentados resultados experimentais que validam a formulação e os algoritmos propostos.

## Abstract

The traditional scope of functional verification has been extended with the rise of electronic-system-level (ESL) design flows. In those flows, immediately after hardware-software partitioning, verification has to deal with abstract data, with implementation artifacts, and, possibly, with the non-preservation, by the device under verification (DUV), of the the order of behaviors at the golden model. Existing approaches are limited either by the use of greedy heuristics (jeopardizing verification guarantees) or by black-box approaches (impairing observability).

This work adopts a white-box approach and proposes a new technique that operates on data samples captured by monitors and stored in the form of so-called logs. For each point to be verified, mirrored monitors are inserted: one at the golden model, another at the DUV. The automatic verification of the logs of a pair of mirrored monitors is cast as a bipartite graph matching problem. The classical problem was modified to capture not only value compatibility, but also event precedence, so as to allow the treatment of the non-preserved event order at the DUV.

The adopted formulation allowed us to prove several properties, which were used as stepping stones for determining the verification guarantees of the proposed technique. The implementation of monitors relied on pre-existing infrastructure based upon computational reflection. Experimental results validate the formulation and the proposed algorithms.

# Capítulo 1

# Introdução

Depois de contextualizar este trabalho em relação aos paradigmas contemporâneos de projeto de sistemas integrados, este capítulo ilustra, através de dois exemplos, o problema abordado nesta dissertação.

Além de introduzir informalmente o problema-alvo e a abordagem proposta para a sua solução, os exemplos destacam dois dos principais efeitos resultantes da implementação, que precisam ser tratados por ferramentas de verificação:

- A existência de comportamentos implementados que não foram especificados (devido a artefatos de implementação);

- A não-preservação da ordem de comportamentos (devida à adoção de modelos atemporais em paradigmas de projeto contemporâneos e ao distinto tratamento de concorrência ao longo do fluxo de projeto).

#### 1.1 O contexto histórico

A revolução dos sistemas integrados (SoCs: Systems-on-Chip) teve início em meados da década de 90, quando a tecnologia de semicondutores alcançou dimensões de cerca de 0,35 a 0,25  $\mu m$  [MAR 03b]. Essa redução permitiu que os mais importantes elementos de um sistema computacional (processadores, memória e alguns periféricos) fossem integrados em uma mesma pastilha de silício (SoC).

Entre os anos de 1995 e 1999 a comunidade científica viveu um período de grande entusiasmo porque acreditava que, na virada do milênio, seria possível desenvolver SoCs num curto intervalo de tempo, atendendo assim às pressões do time-to-market (TTM).

Entretanto, as previsões feitas durante a primeira fase da revolução não se concretizaram. Não era simples integrar blocos de propriedade intelectual (IP: *Intelectual Property*) desenvolvidos por terceiros e, à medida que a complexidade dos sistemas crescia, a dificuldade de integrar (reusar) componentes aumentava. Isto ocorreu porque, no afã de promover o reuso, algumas áreas importantes foram negligenciadas (principalmente o desenvolvimento de novas metodologias e ferramentas de projeto) [MAR 03b].

Apesar disso, o mercado de IPs entre os grande fabricantes manteve seu crescimento entre os anos de 1993 e 2001 [MAR 03b]. Os projetos desta época foram desenvolvidos seguindo metodologias e padrões de projeto bem definidos.

Baseado nessas experiências preliminares, entre os anos de 2000 e 2002, surgiu a noção de projeto baseado em plataforma (PBD: *Platform-based design*) [SV 01].

#### 1.2 O projeto baseado em plataforma

Pode-se definir esta abordagem de projeto como um método organizado para reduzir os tempos e o risco envolvidos no projeto e verificação de SoCs, através do intenso reuso de hardware e software. O PBD agrega grupos de componentes dentro de uma plataforma reutilizável [MAR 03b].

Em outras palavras, PBD é essencialmente uma combinação de uma arquitetura de referência com técnicas de reuso [BER 02].

Assim, cada instância de uma plataforma deriva de uma arquitetura de referência e é caracterizada pelos seus componentes programáveis. A utilização de componentes programáveis garante a flexibilidade necessária para oferecer suporte a um conjunto de aplicações que viabilizem a produção de uma plataforma [SV 01].

As plataformas CoreConnect (IBM) [IBM 08], TI OMAP<sup>TM</sup> (Texas Intruments) [INS 08] e a Nexperia-DVP (Philips) [NXP 08] são exemplos conhecidos da utilização do paradigma de PBD.

#### 1.3 O projeto em nível de sistema

A abordagem de projeto em nível de sistema eletrônico (ESL: *Electronic System Level*) é um conjunto de métodos que têm foco na utilização de níveis mais altos de abstração, visando aumentar a compreensão do sistema para viabilizar a implementação eficiente de um projeto [GM 07].

Embora o fluxo ESL possa ser idealizado como uma abordagem topdown (onde o projeto parte do nível mais alto, para o nível mais baixo de abstração) o reuso de componentes requer uma abordagem meet-in-the-middle (que envolve iterações top-down e bottom-up).

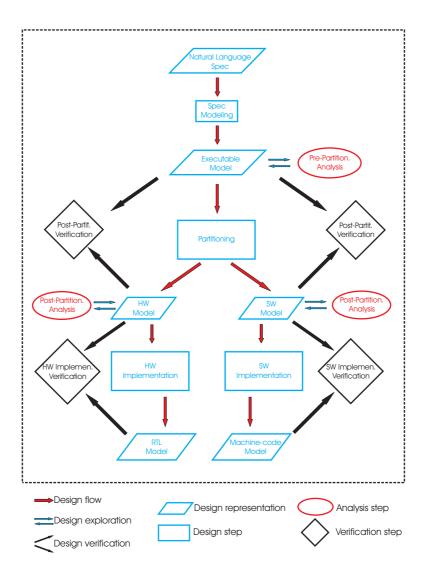

Segundo [GM 07], o fluxo de projeto usando a abordagem ESL pode ser dividido em seis etapas, ilustradas esquematicamente na Figura 1.1.

Na etapa de especificação e modelagem são identificadas as funcionalidades que o sistema deve atender, além de suas restrições. Geralmente, estas especificações são escritas utilizando linguagem natural.

A análise pré-particionamento consiste na escolha de modelos e algoritmos que serão utilizados na implementação do sistema. Esta escolha deve levar em conta aspectos como desempenho, área ocupada em silício, potência consumida e complexidade.

A etapa de *particionamento* consiste em definir quais algoritmos escolhidos nas etapas anteriores devem ser implementados em software e quais em hardware.

Na etapa de análise pós-particionamento os modelos concebidos durante a análise pré-particionamento são refinados para refletir o particionamento adotado. A partir desta representação do sistema já é possível efetuar algumas estimativas de desempenho, potência e custo [GM 07]. É possível que ocorram algumas

Figura 1.1: O fluxo de projeto usando a abordagem ESL

iterações entre a etapa de análise e particionamento visando alguma otimização no sistema. Este processo é conhecido como exploração do espaço de projeto (design space exploration).

Durante a verificação pós-particionamento, a equipe de projeto deve avaliar se a descrição do sistema, obtida após o particionamento, preservou o comportamento especificado. Essa avaliação ocorre através da comparação do modelo de referência com o modelo resultante do particionamento.

A verificação inicia-se a com a elaboração de um plano de verificação

(verification plan). Neste documento, fica registrado o escopo da verificação, as entidades que deverão ser monitoradas e os testes que devem ser realizados para validar o sistema. Assim, esse plano é utilizado como base para a implementação do ambiente de verificação.

A implementação do hardware consiste na criação de modelos que, futuramente, poderão ser implementados através de síntese comportamental, lógica e física. Algumas decisões de projeto que impactam diretamente o desempenho do sistema devem ser tomadas nesta etapa, tais como o como compartilhamento de recursos e as inserções de estruturas de pipeline.

Tradicionalmente, a *implementação do software* de um sistema era iniciada quando uma versão estável do hardware já estava disponível. Numa abordagem ESL, o software e o hardware são desenvolvidos paralelamente, para acelerar o desenvolvimento do projeto (*hardware-software codesign*).

Os refinamentos de hardware e software produzidos durante esta etapa devem ser submetidos ao ambiente de verificação elaborado na etapa anterior, ou seja, faz-se a *verificação da implementação*. Esta interação entre a etapa de implementação e a etapa de verificação assegura a compatibilidade entre a diferentes representações do modelo implementado.

O tópico de pesquisa abordado nesta dissertação é a verificação funcional de representações executáveis de blocos de hardware e software (que podem ser obtidas utilizando, por exemplo, SystemC [OSC 08]). Embora o foco de aplicação da técnica aqui proposta resida na verificação pós-particionamento (para a qual há um menor número de técnicas disponíveis), isso não exclui sua aplicação para a verificação da implementação, desde que representações executáveis estejam disponíveis para isso.

#### 1.4 A verificação de sistemas

A história da área de verificação e o seu papel crucial na automação de projeto eletrônico (EDA: *Eletronic Design Automation*) resultou num grande

número de técnicas e ferramentas para verificar se uma dada implementação está de acordo com uma especificação. Livros inteiros já foram escritos sobre este importante assunto [MAR 03a, BW 03, SI 04, BAI 05, MEY 04], discutindo aspectos importantes da verificação de um sistema como a geração correta de vetores de estímulo, a cobertura de testes, as asserções temporais, os ambientes e as linguagens de verificação.

Com o surgimento da abordagem ESL, o escopo da verificação foi ampliado. Além da tradicional verificação da implementação, surgiu a noção de verificação pós-particionamento.

Neste escopo estendido, a verificação tem que lidar com resoluções distintas [BB 05] para dados (token, propriedade, valor, formato, sinal lógico) e para temporização (eventos parcialmente ordenados, eventos do sistema, ciclo de instrução, precisão de ciclos e precisão de tempo). Por exemplo, valores de dados a serem monitorados podem estar associados a atributos de uma representação orientada a objeto de um módulo de um sistema (eles não estão mais limitados a saídas bit-true de um componente do hardware).

Além disso, a verificação deve levar em conta a utilização de diferentes níveis de abstração ao longo de um projeto. Assim, estabelecer a compatibilidade entre modelos tem um papel crucial no projeto de um sistema. Ou seja, deve ser possível estabelecer uma correspondência entre duas representações em diferentes níveis de abstração de mesmo projeto quando submetidos a uma mesma seqüência de estímulos. Para estabelecê-la, costuma-se utilizar abordagens com diferentes graus de observabilidade. Abordagens do tipo black-box têm acesso somente a elementos externos (entradas e saídas), enquanto abordagens do tipo white-box possuem uma observabilidade maior, permitindo acesso a elementos internos (atributos).

Um aspecto crucial é como tornar observáveis os atributos de um objeto, para permitir a comparação entre implementação e comportamento especificado. Outro aspecto importante é como analisar automaticamente os registros históricos de eventos monitorados, que chamaremos de *logs*.

Um aspecto fundamental da verificação pós-particionamento diz

respeito à não-preservação da ordem de comportamentos no modelo sob verificação (DUV: *Device Under Verification*), como será discutido na Seção 1.6.

#### 1.5 O problema-alvo e a abordagem proposta

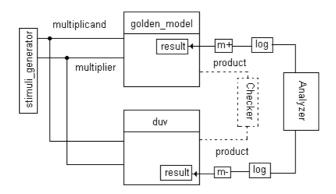

Assuma que um módulo capaz de realizar operações de multiplicação é o módulo sob verificação (DUV: Device Under Verification). A Figura 1.2 mostra um ambiente de verificação típico. Um modelo de referência (RGM: Reference Golden Model) representa os comportamentos especificados. Para cada estímulo gerado (multiplicand e multiplier) um comparador verifica se a saída obtida equivale à saída esperada (product). Isto resulta numa abordagem black-box.

Figura 1.2: Um exemplo de ambiente de verificação

Entretanto, suponha que um engenheiro de verificação precisa inspecionar elementos internos ao DUV (por exemplo, uma variável). A técnica proposta neste trabalho viabiliza este enfoque *white-box*, anexando um *monitor* a um atributo, variável, sinal ou registrador de um DUV.

Na Figura 1.2, duas instâncias de um monitor m ( $m^+$  e  $m^-$ ) foram anexadas a uma variável interna (result). O histórico dos valores observados é armazenado na forma de um log.

A Figura 1.3 mostra uma representação SystemC [OSC 08] para o

modelo de referência. Note que ela implementa o comportamento desejado, empregando diretamente uma operação de multiplicação para calcular o produto (linha 17).

```

1 \quad \textbf{SC\_MODULE}(\ \texttt{golden\_model}\ ) \{

2

sc_in < int > multiplier;

3

4

sc_in < int > multiplicand;

sc\_out < int > product;

6

int result; //Monitor m+ will be attached to this variable

void run()

9

10

while (true)

11

{

^{12}

result = 0:

13

int factor1 = multiplier -> read();

14

int factor2 = multiplicand -> read ();

15

16

17

result = factor1 * factor2;

18

19

product -> write ( result );

20

21

}

23

24 }

```

Figura 1.3: Uma representação para o modelo de referência

Assuma que, como resultado de um refinamento visando uma implementação mais barata, o módulo na Figura 1.4 foi obtido. Note que as operações de soma utilizadas para calcular o produto (linha 19) podem ser consideradas como efeitos colaterais da implementação da funcionalidade desejada (multiplicação). Estes efeitos colaterais são chamados de artefatos de implementação [GM 07].

Devido ao uso de um artefato de implementação, os valores monitorados em  $m^-$  vão apresentar comportamentos não especificados, os quais devem ser identificados e separados daqueles especificados no modelo de referência.

A Figura 1.5 mostra a descrição do gerador de estímulos, que foi preparado para disparar duas operações sucessivas de multiplicação.

Na técnica aqui proposta, toda mudança de valor observada por

```

1 SC_MODULE(duv){

sc_in < int > multiplier;

4

sc_in <int> multiplicand;

sc_out<int> product;

5

int result; //Monitor m- will be attached to this variable

8

9

10

while (true)

11

wait();

12

int factor1 = multiplier -> read();

13

14

int factor2 = multiplicand -> read ();

result = 0.

15

16

18

for(i=0; i< factor1; i++)

result += factor2:

19

20

21

product -> write ( result );

22

23

}

26 }

```

Figura 1.4: Uma representação para o DUV

uma instância de um monitor é representada como uma entrada num log.

Um log começa quando um valor inicial é atribuído a um elemento e captura cada novo valor observado durante a seqüência de eventos disparada pelos estímulos aplicados.

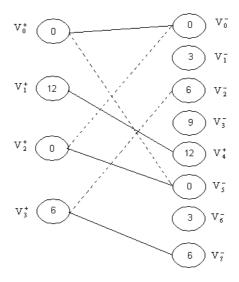

Para o padrão de estímulos gerados, os logs das instâncias  $m^+$  e  $m^-$  são  $\langle 0, 12, 0, 6 \rangle$  e  $\langle 0, 3, 6, 9, 12, 0, 3, 6 \rangle$ , respectivamente. Para o caso particular deste exemplo, vamos convencionar que dois valores só são compatíveis se forem idênticos.

Para verificar se um comportamento especificado no modelo de referência está implementado no DUV, vamos estabelecer uma correspondência entre valores compatíveis nos logs de  $m^+$  and  $m^-$ . Para analisar esta correspondência, vamos construir um grafo bipartido, onde cada partição, digamos  $V^+$  ( $V^-$ ), representa o log de um monitor  $m^+$  ( $m^-$ ). Uma aresta ( $v^+, v^-$ ) significa que os valores associados aos vértices  $v^+$  e  $v^-$  são compatíveis.

A Figura 1.6 mostra o grafo bipartido resultante, onde o valor asso-

```

1 SC_MODULE(stimuli_generator){

2

3

sc\_out < int > multiplier;

4

sc_out<int> multiplicand;

5

6

void run()

8

wait();

9

multiplier -> write (4);

10

multiplicand -> write (3);

11

12

wait();

13

multiplier -> write (2);

multiplicand —>write(3);

14

15

wait();

16

17

sc_stop();

18

19

20 }

```

Figura 1.5: Uma representação para o gerador de estímulos

ciado a um vértice está nele rotulado. Este grafo será denominado de grafo bipartido de verificação (BVG).

Um casamento (matching) em um grafo bipartido é um subconjunto de suas arestas tais que duas arestas não compartilhem um vértice. Desta forma, se encontrarmos um casamento M tal que cada vértice pertencente a  $V^+$  esteja casado, podemos concluir que cada comportamento especificado está implementado pelo DUV. Assim, os comportamentos especificados podem ser distinguidos dos não especificados.

Entretanto, nem todo casamento é apropriado. Como as mudanças de valores nos monitores são provocadas por uma sequência de eventos, para preservar a *causalidade*, nenhuma resposta deverá preceder o evento que a disparou.

Por exemplo, o evento  $v_2^+$  representa a inicialização de result (linha 13 na Figura 1.3) para o segundo estímulo aplicado (linhas 13-14 Figura 1.5), enquanto o evento  $v_3^+$  representa a atribuição do produto a result (linha 17 na Figura 1.3) para o segundo estímulo aplicado (linhas 13-14 a Figura 1.5). Assim, o evento  $v_2^+$  precede o evento  $v_3^+$  na especificação. Se escolhêssemos  $(v_2^+, v_5^-)$  para

Figura 1.6: Um grafo bipartido e um casamento próprio

estar no casamento, então  $(v_3^+, v_2^-)$  não poderia nele estar, já que a atribuição do produto final a **result** (representada por  $v_2^-$ ) no DUV precederia sua inicialização (representada por  $v_5^-$  no DUV). Este comportamento não-causal com certeza não reflete o comportamento desejado e deve ser excluído.

Para manter a causalidade, precisamos levar em conta que os conjuntos  $V^+$  e  $V^-$  estão ordenados pela seqüência de eventos especificados, isto é,  $V^+ = (v_0^+, v_1^+, v_2^+, v_3^+) \text{ e } V^- = (v_0^-, v_1^-, v_2^-, v_3^-, v_4^-, v_5^-, v_6^-, v_7^-)$

Na Figura 1.6, o conjunto de arestas destacadas representa um casamento que preserva a causalidade e, simultaneamente, garante que cada vértice em  $V^+$  está casado. Um casamento com essas propriedades será denominado de casamento próprio. Desta forma, ele indica que todos os comportamentos especificados foram implementados. Se não for possível obter um casamento com estas características, uma travessia no grafo vai apontar qual evento especificado causou a anomalia. Isto torna a técnica aqui proposta útil para encontrar defeitos.

Por simplicidade, o exemplo assume que o DUV preserva a ordem dos eventos especificados no modelo de referência. Entretanto, há situações reais em que a ordem não é preservada pelo DUV para todos os eventos, como será discutido

# 1.6 O efeito da não-preservação da ordem de comportamentos

Um dos primeiros passos em um fluxo de projeto ESL é a criação de uma representação comportamental (funcional) que obedeça à especificação, dando origem a um modelo da especificação (declarativo ou executável). Entretanto, por razões de eficiência, esse modelo deve abstrair aspectos de temporização, pois a maior complexidade computacional de modelos temporizados tornaria proibitivo o co-projeto de hardware e software [GHE 05]. Além disso, o uso de uma representação executável temporizada tornaria não-reusáveis os testbenches [GM 07], pois teriam de ser retrabalhados toda vez que houvesse uma mudança no projeto impactando a temporização.

A necessidade de um modelo comportamental atemporal leva, entretanto, a duas conseqüências para a verificação, a seguir discutidas e ilustradas através de exemplos:

Consequência 1: A verificação pós-particionamento deve checar a ordem dos eventos, mas não sua temporização.

Suponha que uma especificação dite o seguinte requisito: um evento Grant ocorre sempre após um evento Request dentro de no máximo 4 ciclos. Quando a especificação é formalizada em um modelo atemporal (Modelo 1), apenas a ordem dos eventos é capturada: o evento Grant sucede o evento Request. A especificação poderia ter sido capturada em um modelo temporal aproximado (Modelo 2) da seguinte forma: o evento Grant ocorre sempre 2 ciclos após o evento Request (o que satisfaz o requisito original). Entretanto, se após a implementação, o evento Grant ocorre sempre 3 ciclos após o evento Request, ele satisfaz o Modelo 1, mas não o Modelo 2, embora satisfaça a especificação. Por isso, o modelo comportamental não deveria capturar a temporização em si, mas apenas a relação de precedência de even-

tos, que é condição necessária, mas não suficiente, para a validade da temporização.

Consequência 2: A ordem de eventos pode não ser preservada no DUV devido ao tratamento de concorrência adotado no modelo comportamental.

Suponha que uma especificação não imponha qualquer ordem entre os eventos Request 1 e Request 2 nem entre os eventos Grant 1 e Grant 2, embora especifique a seguinte relação de precedência (Request 1, Grant 1) e (Request 2, Grant 2). Assuma que a especificação é formalizada em um modelo atemporal a ser usado como referência para verificação (RGM). Suponha agora que, durante a execução deste modelo, os eventos  $Request\ 1$  e  $Request\ 2$  ocorram simultaneamente. Suponha ainda que a forma como o RGM trate a concorrência dos eventos resulte em disparar o evento Grant 1 antes do evento Grant 2, ou seja (Grant 1, Grant 2). Finalmente, assuma que o modelo do DUV receba Request 2 antes de Request 1 devido a diferentes atrasos de propagação decorrentes da implementação. Neste cenário, a ordem dos eventos no DUV seria (Grant 2, Grant 1), ao contrário da ordem induzida no modelo atemporal de referência (RGM). Assim, para o mesmo conjunto de estímulos de entrada, os comportamentos de saída observados entre RGM e DUV não exibiriam a mesma ordem de eventos. O que parece ser um indício de erro de implementação é na verdade consequência da ausência de uma restrição na especificação.

A não-preservação da ordem dos eventos pelo DUV é talvez um dos aspectos mais complexos da verificação em um fluxo de projeto ESL [GM 07].

A próxima seção ilustra, através de um exemplo propositadamente simples, como esta dissertação aborda estes aspectos.

#### 1.7 Um exemplo ilustrativo

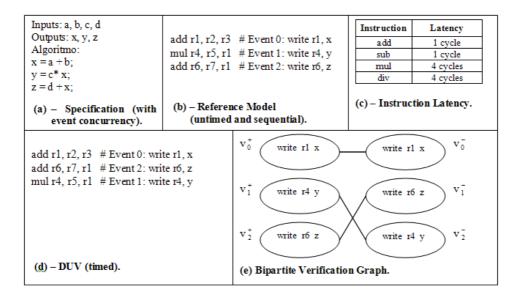

A Figura 1.7a ilustra uma especificação em que não há restrição alguma para a ordem relativa entre as escritas de y e z, mas apenas estabelece que a escrita de x deve precedê-las.

Figura 1.7: Exemplo de execução fora de ordem

Suponha que os comportamentos especificados venham a ser implementados em um co-processador aritmético. Assuma que se adote um modelo atemporal de referência para capturar a especificação, o qual trate a concorrência dos eventos através de sua mera serialização, na ordem em que as instruções são buscadas. Ora, este seria exatamente o caso típico em que um simulador do conjunto de instruções (puramente funcional) fosse utilizado para a modelagem. A Figura 1.7b ilustra esquematicamente o efeito desse modelo atemporal, que assume execução seqüencial. Além disso, ela mostra a correspondência entre as instruções no modelo de referência e os respectivos eventos de escrita no banco de registradores. Um evento de escrita, denotado por  $write\ r,\ v,$  representa a escrita do valor v no registrador-destino r.

Considere agora que, para a implementação do co-processador, seja adotada uma micro-arquitetura que suporte o bem-conhecido algoritmo de Tomasulo [PAT 07], para explorar a concorrência de operações independentes em unidades funcionais distintas. Assuma que as latências das instruções sejam aquelas representadas na Figura 1.7c. Suponha que existam estações de reserva distintas e livres para operações de soma e de multiplicação, conforme ilustra a Figura 1.8. Suponha

também que um monitor seja adicionado à porta de escrita do banco de registradores.

Figura 1.8: Representação do co-processador hipotético

A Figura 1.7d exibe a ordem efetiva de execução das intruções quando submetidas ao DUV. Nessa implementação, o Evento 1 ocorrerá ao final do primeiro ciclo, quando as demais instruções serão simultaneamente iniciadas. Devido às diferentes latências, o Evento 3 ocorrerá ao final do segundo ciclo; o Evento 2, ao final do quinto ciclo.

A Figura 1.7e ilustra o grafo bipartido de verificação e o casamento que corresponde à compatibilidade dos comportamentos especificados. Note que o cruzamento entre as arestas  $(v_1^+, v_2^-)$  e  $(v_2^+, v_1^-)$  não pode ter a interpretação de erro de implementação, pois a ordem dos eventos resultou invertida no DUV devido ao distinto tratamento de concorrência entre modelos.

Seja R = $\{(v_0^+,v_1^+),(v_0^+,v_2^+)\}$  a relação que captura a seguinte precedência entre eventos: (Evento 0, Evento 1) e (Evento 0, Evento 2).

Note que para decidir se o casamento obtido no BVG da Figura 1.7(e) satisfaz o princípio da causalidade, teve-se que analisar se a troca de ordem dos eventos no DUV satisfaz a relação de precedência R.

Portanto, não é possível analisar a compatibilidade de comportamentos sem uma relação de precedência de eventos que permita distinguir se a ordem induzida pelo DUV viola ou não a especificação. Note que essa relação é inerente à própria especificação, a partir da qual pode ser extraída, e não uma restrição imposta à resolução do problema.

No caso específico da abordagem aqui proposta, essa relação de precedência será a chave para distinguir casamentos próprios de impróprios. Como os algoritmos clássicos de casamento, ao procurar um casamento de maior cardinalidade, não assumem qualquer relação adicional entre seus vértices, exceto pela relação de compatibilidade capturada pelas arestas do grafo bipartido, tais algoritmos não podem ser diretamente reusados para resolver o problema da verificação que será formulado na Seção 3.2. Em outras palavras, o simples reuso de algoritmos clássicos não é adequado porque o casamento resultante poderia não obedecer ao princípio da causalidade.

Por isso, um novo algoritmo precisa ser concebido para restringir as soluções que seriam obtidas por algoritmos clássicos, instrumentando-os para distingüirem entre arestas pertencentes ou não a um casamento próprio.

#### 1.8 O escopo e a contribuição desta dissertação

As premissas da abordagem adotadas nesta dissertação são as seguintes:

**Premissa 1:** A técnica proposta assume que a geração de estímulos para um dado componente foi tratada no ambiente de verificação de forma a garantir adequada cobertura.

Premissa 2: A técnica proposta aborda verificação de resposta aos estímulos e diagnóstico de erros baseada apenas no modelo de referência (verificadores temporais e de dados estão fora do escopo desta dissertação).

**Premissa 3:** A análise proposta é inerentemente limitada ao universo de comportamentos amostrados pelos monitores inseridos.

Premissa 4: A técnica proposta assume que se um monitor amostra no DUV valores não especificados no RGM, os comportamentos não especificados referem-se a artefatos de implementação.

Assim, se um dado comportamento especificado no modelo de referência fosse duplicado no DUV (por exemplo, se um request gerasse dois grants), a anomalia não seria capturada pela técnica proposta).

**Premissa 5:** A técnica proposta supõe que os elementos monitorados no RGM sejam preservados no DUV e que, portanto, faça sentido introduzir monitores no mesmo elemento nas duas representações.

Desta forma, se o refinamento de um modelo não preservasse algum elemento monitorado no modelo de alto nível, deveria ser criada alguma relação de mapeamento para viabilizar indiretamente a amostragem do elemento desejado.

**Premissa 6:** A técnica proposta pressupõe que se possa extrair da especificação informações sobre causa e efeito de eventos, que serão capturadas por uma relação de precedência R.

A relação R é dependente do domínio de aplicação. Por exemplo, ela pode capturar as dependências de dados e de controle de um código embarcado, a ordem de sinalização em um protocolo *handshaking*, etc.

As principais contribuições desta dissertação são:

- A viabilização do tratamentos do efeito de não-preservação da ordem de comportamentos sem limitar a observabilidade, no âmbito de uma abordagem white-box.

- O estabelecimento de garantias formais para a qualidade da verificação, como resultado da formulação escolhida para o problema, amparando-se em propriedades de casamento em grafos bipartidos.

Não é do conhecimento do autor a existência de técnicas que tratem a não-preservação de ordem em abordagem *white-box*, nem a existência de trabalhos correlatos que se amparem em propriedades de grafos bipartidos para fornecer garantias de qualidade da verificação.

#### 1.9 A organização desta dissertação

Esta dissertação está organizada da seguinte maneira: O Capítulo 2 apresenta inicialmente uma breve revisão dos trabalhos correlatos nas áreas de verificação dinâmica, verificação formal e verificação em plataformas e concentra-se depois na análise de abordagens convencionais para o tratamento da não-preservação da ordem de comportamentos. O Capítulo 3 inicialmente formaliza algumas noções básicas que são em seguida utilizadas para formular o problema-alvo; ao final, provam-se algumas propriedades fundamentais a serem preservadas durante a verificação. O Capítulo 4 propõe algoritmos para resolver o problema-alvo e analisa as garantias de verificação, apresentando provas da ausência de falso negativo, além de discutir as condições de ocorrência de falsos positivos. O Capítulo 5 discute a implementação e apresenta resultados experimentais como evidência da correção da abordagem. O Capítulo 6 resume as principais conclusões e indica as perspectivas de trabalhos futuros.

# Capítulo 2

## Trabalhos correlatos

Como a literatura sobre verificação funcional é muito vasta, neste capítulo serão analisados algumas técnicas recentes mais próximas do foco deste trabalho, no âmbito das abordagens ESL e PBD. A primeira seção aborda algumas técnicas de verificação funcional enquanto a segunda seção aborda técnicas utilizadas para tratar a não-preservação da ordem de comportamentos.

# 2.1 Principais abordagens para verificação funcional

#### 2.1.1 Verificação formal

A verificação formal de um sistema consiste na utilização de dispositivos formais ou matemáticos para provar que o sistema avaliado está correto. Uma das formas utilizadas consiste em estabelecer uma equivalência entre modelos em diferentes níveis de abstração. Se for possível provar que um modelo de alto nível, previamente validado, é equivalente a um modelo de baixo nível, então considera-se este último como validado.

Esta validação do modelo de baixo nível em função da validação prévia de um modelo em maior nível de abstração acelera o desenvolvimento do

sistema, já que a simulação em modelos em níveis mais baixos de abstração é muito mais lenta do que a simulação em modelos em mais alto nível.

Uma das técnicas utilizadas para estabelecer a compatibilidade entre modelos é o uso de pontos de corte (cutpoints). A noção de cutpoints está baseada na suposição de que se dois circuitos são funcionalmente similares, então deve ser possível definir um conjunto de pontos logicamente equivalentes, os quais não requerem verificação no modelo de baixo nível.

O trabalho de Feng e Hu [FEN 97] utilizou a noção de *cutpoints* para estabelecer equivalência entre um modelo SystemC (com precisão de pinos e de ciclos) e um modelo RTL. Para estabelecer esta equivalência, os autores comparam representações funcionais (obtidas através de simulação simbólica) das implementações em diferentes níveis de abstração. Esta comparação permite determinar pontos logicamente equivalentes, diminuindo o esforço total de verificação do sistema.

Outro ramo da verificação formal utiliza asserções para validar um modelo. O trabalho de Kasuya [KAS 07] propõe o uso das assim-chamadas asserções nativas em SystemC (NSCa: Native SystemC assertion) para modelar asserções com precisão de ciclos em SystemC. Por um lado, esta técnica viabiliza o reuso de asserções nos diferentes níveis de abstração, o que reduz o esforço de verificação. Por outro lado, ela é intrusiva, pois requer mudanças no DUV para inserção das asserções.

Em [HAB 06] asserções são utilizas para avaliar a cobertura funcional de um dado conjunto de vetores de verificação. Para avaliar a cobertura, os autores utilizam um modelo de referência (RGM) escrito na linguagem denominada AsmL (Abstract State Machine Language). Asserções são inseridas nas variáveis de estado do modelo de referência e avaliadas sempre que o valor da variável correspondente tem o seu valor alterado, ou seja, o modelo tem o seu estado alterado. Assim, a cobertura de um dado vetor  $v_i$  é avaliada pela razão entre o número de estados assumidos pelo modelo quando estimulado por  $v_i$  e número de estados possíveis. Após a avaliação da cobertura de um determinado conjunto de vetores, os autores sugerem o uso de algoritmos genéticos para aumentar a cobertura funcional através

de otimização da geração de vetores de verificação. Entretanto, o uso desta técnica requer que o engenheiro de verificação defina quais são as variáveis de estado de um DUV (onde estão inseridas as asserções). Ademais, o uso de algoritmos genéticos requer instrumentação para capturar informações específicas do domínio de aplicação: qual a representação de cromossomos através de uma codificação dos estímulos, além das operações de herança, mutação e recombinação para a codificação adotada.

Em [COR 00] propõe-se uma representação baseada em redes de Petri para a verificação de um sistema, a qual é denominada PRES+ (Petri net based Representation for Embedded Systems). Nesta representação as marcações nos lugares da rede representam os estados do sistema, enquanto as transições representam as operações realizadas pelo sistema. Cada transição possui anotações tais como, por exemplo, as condições necessárias para o seu disparo, além de informações como o tempo máximo necessário para realizar a transição. Através da representação PRES+, é possível avaliar-se, por exemplo, para que entradas um determinado estado do sistema é alcançado, ou qual o intervalo mínimo de tempo necessário para alcançar um determinado estado. No entanto, segundo [VAR 07] representações que enumerem todos os estados possíveis estão limitadas pelo crescimento exponencial do número de estados, inviabilizando assim a simulação de modelos mais complexos.

Como nem sempre é possível provar que dois modelos são equivalentes, Vardi [VAR 07] analisou algumas técnicas formais para estabelecer sua compatibilidade. Nesta abordagem, um modelo beneficia-se da verificação previamente realizada em modelo de alto nível compatível, permitindo que a verificação de cada implementação foque nos aspectos relevantes para aquele modelo de abstração. Por exemplo, a verificação de um modelo RTL pode se limitar aos artefatos de implementação inseridos, enquanto a verificação nos níveis superiores esta focada nas estruturas (particionamento) e algoritmos escolhidos.

#### 2.1.2 Verificação dinâmica

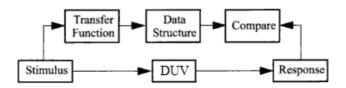

A verificação dinâmica está associada à simulação do sistema. Tradicionalmente um ambiente de verificação é composto de um gerador de estímulos, um módulo a ser verificado (DUV) e um monitor. A função do gerador de estímulos é a de aplicar um conjunto de estímulos no DUV. Já o monitor deve capturar as saídas do DUV e verificar se seus valores estão corretos.

Em níveis mais baixos de abstração, a grande quantidade de detalhes torna proibitiva a simulação de todo o sistema. Além disso, em alguns casos, o ambiente de verificação precisa ser adaptado para incluir informações de baixo nível (por exemplo, o ambiente precisa ser alterado para capturar detalhes do protocolo de comunicação do DUV).

Uma alternativa para resolver o problema de reduzir o tempo de simulação do sistema é a co-simulação de componentes em diferentes níveis de abstração [SWA 06]. Assim, embora o DUV seja descrito em uma linguagem de descrição de hardware (como VHDL ou Verilog), os demais componentes podem ser descritos em níveis mais altos de abstração (C ou C++).

Para reaproveitar o ambiente de verificação, uma alternativa é a tradução automática de estímulos [BOM 06]. Esta abordagem utiliza transactors, que são um componentes responsáveis pela tradução de mensagens entre o ambiente de verificação (que utiliza chamadas de alto nível, como write ou read) e o DUV (que pode utilizar, por exemplo, sinais lógicos). Desta forma, o transactor reduz consideravelmente o esforço de implementação do ambiente de verificação. Outra vantagem é que, se o protocolo de comunicação do DUV for alterado, apenas o transactor deverá ser alterado para refletir a mudança (sem a utilização de um transactor, poderia ser necessário re-implementar todo o conjunto de rotinas de verificação).

No entanto, as técnicas citadas não são suficientes para verificar sistemas muito complexos. Para isto as plataformas costumam contar com mecanismos próprios adicionais, como será mostrado na próxima seção.

#### 2.1.3 Suporte à verificação em plataformas comerciais

O reuso de componentes promovido pela abordagem PBD diminui o esforço total de verificação de um sistema, pois os módulos que compõem uma plataforma já foram verificados previamente. Desta forma, a verificação deve estar focada na interação entre os componentes.

Para sua plataforma CoreConnect, a IBM desenvolveu o TOS (Test Operation System)[MG 03], que é constituído de um kernel, uma API, um padrão e um ambiente de desenvolvimento. O kernel do TOS é desenvolvido em C e fornece algumas facilidades para a execução de rotinas de verificação, tais como a inicialização dos componentes, o tratamento de interrupções e o escalonamento de tarefas. Esta ferramenta possibilita que o projetista escreva uma rotina de verificação para um determinado componente. Quando a plataforma for executada, o TOS carrega a rotina escrita pelo projetista junto com as demais rotinas de verificação da plataforma.

Outra ferramenta disponível é o CoreConnect Test Generation (CTG).

O CTG gera um conjunto de rotinas para verificar se um dado dispositivo é compatível com a arquitetura de barramento da plataforma. As rotinas automatizados são construídas a partir de algumas informações fornecidas pelo projetista, através de uma interface gráfica, favorecendo assim a sua usabilidade.

A plataforma ARM PrimeXsys [ALP 03] também possui um mecanismo semelhante para facilitar a verificação da interação de um componente com um barramento. Esta ferramenta denomina-se *AMBA Complience Test-bench* (ACT) [ALP 03]. O ACT gera um conjunto de rotinas para verificar a compatibilidade entre um determinado dispositivo e o barramento AMBA. Esta compatibilidade é garantida quando o dispositivo é verificado em uma lista de cenários-chave para o protocolo de comunicação.

A grande diferença entre CTG e ACT é que o primeiro opera num nível mais alto de abstração, enquanto o ACT é utilizando para o suporte à simulação RTL.

# 2.2 Outros mecanismos de suporte à verificação

Em [CAR 99] apresenta-se um método para construir sistemas funcionalmente insensíveis à latência de comunicação entre componentes pré-verificados. Para viabilizar a transmissão de dados com elevada latência entre módulos (por exemplo, acima de um ciclo de relógio), os autores propõem o uso de relay stations. Uma relay station é um buffer que atua como um pipeline em um determinado canal de comunicação, gerando sinais de stall (pausa) para paralisar os componentes do sistema enquanto realiza a transmissão de dados.

Existem algumas semelhanças entre a abordagem apresentada em [CAR 99] e a técnica proposta neste trabalho. Por exemplo, para analisar o fluxo de dados em um canal, os autores daquele trabalho desconsideram os sinais de stall gerados pelas relay stations. De forma similar, na abordagem proposta neste trabalho as entradas de log que correspondem a eventos gerados pelos artefatos de implementação são desconsideradas, pois estes eventos não exercem influência sobre o fluxo de dados no sistema.

No entanto, a técnica proposta neste trabalho (Capítulo 4) difere da abordagem proposta em [CAR 99] nos seguintes pontos:

- Os sinais de *stall* gerados pelas *relay stations* possuem uma marcação (*tag*) que os diferencia dos sinais válidos do sistema, enquanto as entradas de *log* produzidas pelos artefatos de implementação não possuem marcação alguma que as diferencie dos demais dados produzidos pelo sistema. Ou seja, a técnica aqui proposta não requer instrumentação para identificar artefatos de implementação, pois isto limitaria sua aplicabilidade em verificação.

- O método proposto em [CAR 99] supõe que os componentes do sistema sempre conservam a ordem dos dados, ao contrário da técnica proposta neste trabalho, que opera adequadamente mesmo quando o DUV não preserva a ordem dos comportamentos (uma das maiores dificuldades na verificação pósparticionamento segundo [GM 07])

- A observabilidade da técnica aqui proposta é maior do que a do método apresentado em [CAR 99], pois ela permite o acesso a elementos internos de um componente (white-box).

- A técnica proposta em [CAR 99] só pode ser aplicada em sistemas construídos com componentes que possuem a propriedade de serem paralisados através de um sinal de stall, uma limitação ao projeto da qual a técnica aqui proposta pode prescindir.

Em [ALB 07], a verificação white-box é viabilizada através do mecanismo de reflexão computacional. A contribuição-chave está no mecanismo de suporte minimamente intrusivo (o projetista não precisa fazer instrumentação adicional alguma no DUV, nem adicionar biblioteca alguma; os elementos internos do DUV podem ser inspecionados sem que seja necessário revelar o código-fonte). Embora essa técnica tenha sido cuidadosamente construída para permitir uma abordagem white-box minimamente intrusiva, seu potencial ainda não foi inteiramente explorado. Devido a estas vantagens, este trabalho utiliza o mecanismo proposto em [ALB 07] como infra-estrutura de implementação para inserção de monitores e para a captura de comportamentos, os quais serão automaticamente analisados pela técnica proposta nesta dissertação.

# 2.3 Abordagens para a não-preservação da ordem

Há pelo menos três abordagens convencionais para contornar o problema da não-preservação da ordem de comportamentos:

- Uso de modelo de referência com precisão de ciclos [GHE 05]: ao temporizar o modelo de referência em relação à implementação, a ordem seria preservada, mas estariam comprometidos o desempenho do modelo e a reusabilidade do *testbench*, conforme já discutido na Seção 1.6.

- Ordenação baseada em antevisão do modelo RTL [YIM 97]: toda vez que uma tomada de decisão se fizer necessária para o tratamento de eventos

concorrentes, uma amostra ("trace") da implementação RTL é sintetizada sob demanda para instrumentar a decisão de forma a escolher apropriadamente a ordem. Esta implementação pode, por exemplo, ser executada concorrentemente com o modelo funcional, recebendo os mesmos estímulos. A diferença entre os sinais de saída dos modelos funcional e RTL deve guiar os projetistas na ordenação de comportamentos. No entanto, ainda segundo [YIM 97], heurísticas são necessárias para diferenciar defeitos reais de artefatos de implementação, as quais podem limitar as garantias de verificação

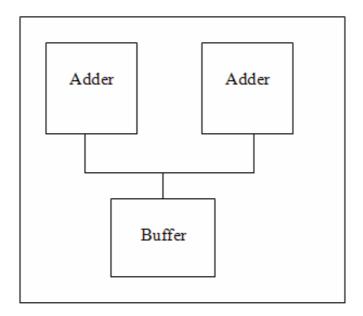

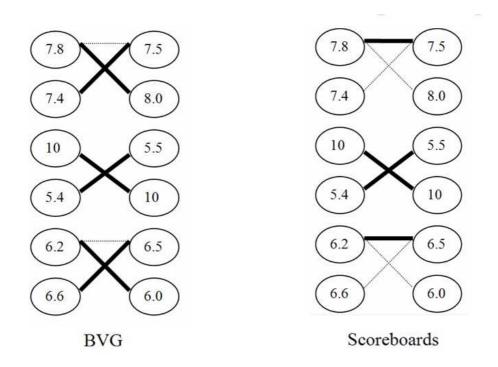

• Uso de scoreboard [GM 07]: Um scoreboard é uma estrutura de dados que armazena resultados esperados (ou estímulos injetados) e que compara o resultado obtido no DUV com o resultado armazenado (ou transformado a partir dos estímulos armazenados). A Figura 2.1 ilustra a estrutura de um scoreboard.

Figura 2.1: Estrutura de um scoreboard (extraído e adaptado de [BER 05])

Segundo [BER 05], um *scoreboard* pode tratar o problema da não-preservação de ordem através do módulo de comparação. Este módulo pode ser implementado de forma a lidar com discrepâncias temporais e de ordenamento entre os dados obtidos no DUV e aqueles armazenados na estrutura de dados. Por outro lado, um *scoreboard* não é capaz de verificar aspectos internos ao DUV [BER 05].

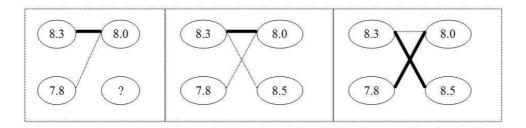

Além desta limitação espacial, o tratamento dos dados amostrados por um scoreboard possui uma limitação temporal. Ou seja, para cada dado amostrado no DUV o scoreboard deve efetuar uma decisão local para encontrar a entrada correspondente no modelo de referência. Esta decisão local está apoiada em

heurísticas que podem afetar a qualidade da verificação conforme será ilustrado a seguir.

Suponha uma variável, que ao ser implementada num modelo de mais baixo nível admita uma perda de precisão da ordem de 0.5. A Figura 2.2a ilustra uma possível execução deste modelo. Repare que, quando o valor 8 é amostrado à saída do DUV, o scoreboard precisa tomar uma decisão local para determinar qual das duas entradas amostradas no modelo de referência é a entrada correspondente ao valor 8 amostrado pelo DUV. Como o scoreboard não possui nenhuma informação a respeito de quais serão os próximos valores amostrados, a associação de entradas deve ser feita baseada numa heurística, conforme ilustrado na Figura 2.2b. No entanto, conforme apresentado na Figura 2.2c, a associação efetuada não está correta.

Em outras palavras, as limitações de visibilidade de um *scoreboard* sacrificam a qualidade da verificação em prol de uma maior eficiência computacional. O Capítulo 5 apresenta indícios dessa limitação no que diz respeito a qualidade da verificação.

Figura 2.2: O impacto da limitação temporal na qualidade da verificação

# 2.4 A perspectiva de uma abordagem alternativa

Esta dissertação propõe uma abordagem alternativa para viabilizar a verificação de DUVs que possam não preservar a ordem dos comportamentos do modelo comportamental atemporal. A abordagem proposta não requer um modelo

temporizado, não requer a antevisão de um modelo RTL e provê o acesso aos elementos internos do DUV, o que amplia a observabilidade da verificação para além das possibilidades de um *scoreboard*.

O próximo capítulo descreve os fundamentos para a análise automática de *logs* (a ser proposta no Capítulo 4), formulando um problema de verificação funcional de um sistema como um problema de casamento em um grafo bipartido.

Entretanto, a construção de casamentos próprios deve levar em conta a compatibilidade de valores capturada no grafo e a causalidade de eventos à luz da relação de precedência de eventos extraída da especificação. Se não fosse especificada ordem alguma entre eventos, algoritmos clássicos poderiam ser reusados para encontrar casamentos. Entretanto, quando a ordem está especificada, casamentos não podem ser obtidos diretamente a partir de algoritmos clássicos, sob pena de ser violado o princípio da causalidade.

# Capítulo 3

# Modelagem do problema

# 3.1 Propriedades da relação entre RGM e DUV

Para estabelecer uma correlação funcional entre dois modelos, vamos utilizar três conceitos principais:

- Unicidade (para determinar que cada comportamento é preservado e exibido uma única vez),

- Compatibilidade (para determinar quais valores são aceitáveis),

- Causalidade (para garantir comportamento temporal adequado).

Antes de formular o problema-alvo é preciso formalizar algumas noções preliminares. Assuma que um engenheiro de verificação selecionou k pontos  $m_1, m_2, ... m_k$  para monitorar em um módulo de uma plataforma. Vamos chamar estes pontos de *monitores*.

Toda vez que um monitor detecta uma alteração e um novo valor v, observado em um instante  $t_i$ , dizemos que ocorreu um  $evento\ v_i$ .

Assuma que todo valor observado num monitor é amostrado toda vez que é alterado, durante um intervalo de observação.

**Definição 1:** Log de um monitor. Vamos denotar como  $t_i$  (com  $i \neq 0$ ) o tempo em que um elemento monitorado sofre a sua i-ésima transição e vamos cha-

mar de  $t_0$  o momento em que o elemento recebe o seu valor inicial. O log de um monitor  $m_k$  é uma série de eventos caracterizada por uma seqüência de valores  $\langle v_{k0}, v_{k1}, ..., v_{ki}...v_{kn} \rangle$  observados nos instantes  $\langle t_0, t_1, ..., t_i, ...t_n \rangle$ .

Quando os valores observados por um monitor m são atributos representados como números inteiros sinalizados ou não (por exemplo: char, int, short, long, unsigned, etc.) tanto no RGM como no DUV e desde que os valores monitorados por m' e m'' usem exatamente o mesmo número de bits em sua representação, uma relação de equivalência deve ser verificada para os valores monitorados por m, conforme formalizado abaixo.

**Definição 2: Equivalência de valores.** Dois valores u e v são equivalentes e denotados como  $u \equiv v$ , se e somente se u = v.

No caso de serem representados como números de diferentes tipos (por exemplo: double no RGM e sc\_fixed no DUV) ou com diferente precisão (por exemplo: sc\_int<16> no RGM e sc\_int<12> no DUV), deve ser adotada uma relação de compatibilidade onde seja definida uma margem aceitável de ruído de quantização (por exemplo, se um atributo do tipo double é monitorado por m' no RGM e um atributo do tipo sc\_fixed<5,3> é monitorado por m'' no DUV, então uma relação de compatibilidade deve adotar uma margem de quantização de 0,25, pois o atributo no DUV pode assumir qualquer valor x no intervalo -4,75  $\leq$  x  $\leq$  3,75 em incrementos de 0,25). Esta noção é formalizada a seguir.

**Definição 3: Compatibilidade de valores.** Dois valores u e v são compatíveis e denotados como  $u \approx v$ , se e somente se forem iguais ou se a sua diferença estiver dentro de uma margem pré-estabelecida.

Note que esta definição permite verificar, por exemplo, modelos abstratos contra modelos com precisão de bits.

Seja  $I^+$  uma instância de um módulo em uma plataforma, usada como referência. Esta instância será chamada de modelo de referência (RGM). Seja  $I^-$  uma nova instância de um módulo, derivada de  $I^+$  (através de um refinamento,

por exemplo).  $I^-$  será chamado de dispositivo sob verificação (DUV).

Vamos denotar por R a relação de precedência entre eventos ditada pela especificação, como formalizado a seguir:

Definição 4: Relação de precedência entre eventos no RGM. Vamos denotar por  $V^+$  o conjunto de eventos monitorados no modelo de referência. A relação de precedência entre eventos é o conjunto  $R = \{(v_i^+, v_j^+) \in V^+ \times V^+ : v_i^+ \text{ precede } v_j^+\}.$

A próxima definição utiliza as Definições 1, 3, 4 para estabelecer o conceito de mapeamento próprio. Um mapeamento próprio é utilizado para estabelecer a correlação entre dois modelos. Dois modelos serão considerados correlatos quando implementam todos os comportamentos especificados, guardando a compatibilidade de valores (a qual é capturada pela relação  $\approx$ ) e respeitando a noção de causalidade (a qual é capturada pela relação R).

**Definição 5: Mapeamento próprio.** Dadas duas instâncias  $I^+$  e  $I^-$  de um módulo, um monitor m e as seqüências de eventos  $\langle v_0^+, v_1^+, ..., v_n^+ \rangle$  e  $\langle v_0^-, v_1^-, ..., v_p^- \rangle$  observados para  $I^+$  e  $I^-$ , respectivamente, diz-se que existe um mapeamento próprio de eventos, se e somente se existir um mapeamento  $\mu$ :  $V^+ \to V^-$  onde  $V^+ = \{v_0^+, v_1^+, ..., v_n^+\}$  e  $V^- = \{v_0^-, v_1^-, ..., v_p^-\}$  tal que todas as cláusulas abaixo seja satisfeitas:

- $\mu$  é uma injeção (completude e unicidade);

- $\mu(v_i^+) = v_j^- \Rightarrow v_i^+ \approx v_j^-$  (compatibilidade);

- $\forall v_i^+, v_x^+ : ((v_i^+, v_x^+) \in R) \land (\mu(v_i^+) = v_i^-) \land (\mu(v_x^+) = v_k^-) \Rightarrow j < k \text{ (causalidade)}$

Note que não é necessário que  $\mu$  seja uma bijeção, já que as implementações em níveis mais baixos podem apresentar comportamentos não especificados (i.e.  $|V^+| \leq |V^-|$ ). Note também que, se um mapeamento  $\mu$  for encontrado, pode-se garantir que cada comportamento especificado no RGM está corretamente implementado no DUV, sob a perspectiva de um dado monitor.

Definição 6: Compatibilidade baseada em logs. O DUV  $I^-$  é funcionalmente compatível com o golden model  $I^+$  no que diz respeito ao conjunto de monitores  $\{m_k\}$ , se e somente se existir um mapeamento próprio para cada monitor.

## 3.2 Formulação do problema-alvo

As definições apresentadas permitem formular, de forma sucinta, o problema-alvo:

**Problema-Alvo:** Dados dois modelos  $I^+$  e  $I^-$ , verificar se eles são funcionalmente compatíveis no que diz respeito ao conjunto de monitores  $\{m_k\}$ .

Este problema-alvo pode ser reformulado como um problema de casamento em grafos bipartidos para cada monitor. Para isso, serão preliminarmente revisadas algumas noções clássicas, as quais serão personalizadas, em seguida, com informações específicas do problema-alvo.

Um grafo G(V, E) é dito bipartido se e somente se:

- $V = V^+ \cup V^- \text{ e } V^+ \cap V^- = \emptyset;$

- $\forall (u, v) \in E : (u \in V^+) \land (v \in V^-).$

Um casamento (ou matching) de um grafo G(V, E) é um subconjunto M de E tal que nenhum vértice é incidente a mais de uma aresta em M. Dizemos que um vértice u está casado, se existe uma aresta  $(u, v) \in M$  ou livre, em caso contrário.

Um casamento com a cardinalidade máxima é denominado de casamento máximo. Se cada vértice de G incidir em uma aresta de M, então M será

considerado um casamento perfeito (note que todo casamento perfeito é máximo,

mas nem todo máximo é perfeito). Se cada vértice da partição  $V^+$  incide em uma

aresta de M, então M será denominado de casamento completo.

Um componente conexo  $C_j(V_j, E_j)$  de um grafo bipartido G(V,E) é um subgrafo de G tal que, para todos  $u, v \in V_j$ , há um caminho entre u e v.

A noção de componente conexo corresponde à relação de equivalência "v é alcançável a partir de u". Como uma relação de equivalência é o mesmo que uma partição [COR 90], a decomposição de um grafo G(V,E) em termos de seus componentes conexos resulta em uma partição de G.

Por resultar em uma partição de G, quando um algoritmo de casamento garante um casamento completo de cada componente conexo, pode-se garantir o casamento completo do grafo G.

**Definition 7:** Grafo bipartido de verificação de um monitor. Sejam  $m^+$  e  $m^-$  instâncias de um monitor m cujos logs são  $\langle v_0^+, v_1^+, ..., v_n^+ \rangle$  e  $\langle v_0^-, v_1^-, ..., v_p^- \rangle$ . O grafo bipartido de verificação, denotado por BVG(m), é um grafo bipartido G(V, E) onde:

- $V^+ = \{v_0^+, v_1^+, ..., v_n^+\}, V^- = \{v_0^-, v_1^-, ..., v_p^-\};$

- Existe uma aresta  $(v_i^+, v_j^-) \in E$ , se e somente se  $v_i^+ \approx v_j^-$ .

**Definição 8:** Casamento próprio. Um casamento  $\mathcal{M}$  de um BVG(m) será considerado próprio, se e somente se induz um mapeamento próprio  $\mu$ .

**Definição 9:** Aresta imprópria. Uma aresta  $(v^+, v^-)$  é dita imprópria se e somente se  $(v^+, v^-) \notin \mathcal{M}$ .

Para abordar a não-preservação da ordem de comportamentos no DUV, a técnica aqui proposta baseia-se em uma noção fundamental, o assim-chamado cruzamento impróprio de arestas. Antes de formalizar esta importante noção, um exemplo ilustrativo é utilizado para introduzi-la.

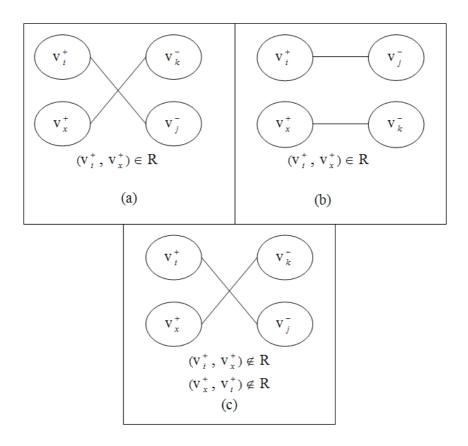

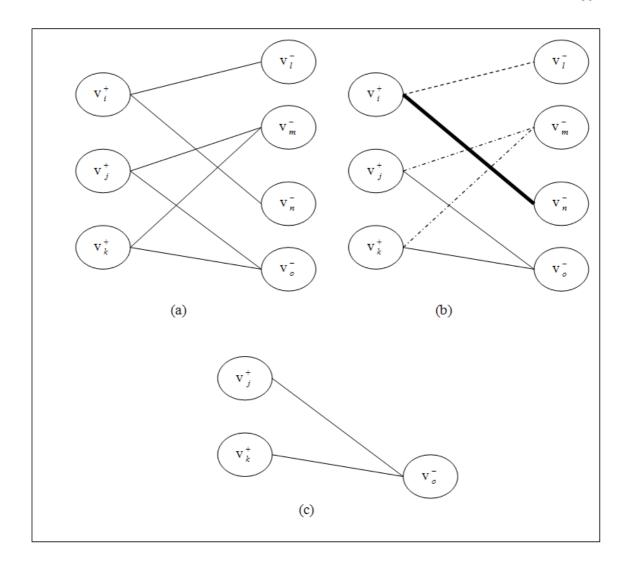

As Figuras 3.1a 3.1b mostram a relação topológica entre duas arestas, sob uma mesma relação de precedência de eventos: o evento  $v_i^+$  precede o evento  $v_x^+$  no RGM. Assim, no cenário da Figura 3.1a, o cruzamento topológico entre as arestas  $(v_i^+, v_j^-)$  e  $(v_x^+, v_k^-)$  resultaria numa inversão de eventos no DUV que não obedeceria a precedência especificada. Portanto, nestas condições, tais arestas não

podem co-existir em um casamento próprio, pois representariam uma violação do princípio da causalidade. Por outro lado, a inexistência de cruzamento topológico entre as arestas, conforme ilustrado na Figura 3.1b, permite que ambas possam co-existir em um casamento próprio. Note que a mera existência de um cruzamento topológico não indica por si só a violação do princípio da causalidade, como mostra a Figura 3.1c: se a relação de precedência não especifica ordem alguma entre os eventos  $v_i^+$  e  $v_x^+$ , ambas as arestas são elegíveis para um casamento próprio. Assim, nem todo cruzamento topológico resulta em cruzamento impróprio, conforme formalizado a seguir.

Figura 3.1: Correlação entre topologia e causalidade.

**Definição 10: Função cruzamento.** Dadas duas arestas  $(v_i^+, v_j^-)$  e  $(v_x^+, v_k^-)$ , com  $i \neq x$ , sua função cruzamento, escrita  $\chi((v_i^+, v_j^-), (v_x^+, v_k^-))$ , retorna verdadeiro se e somente se:  $(((v_i^+, v_x^+) \in R) \land (j > k) \lor ((v_x^+, v_i^+) \in R) \land (k > j)))$ .

Definição 11: Cruzamento impróprio de arestas. Dizemos que existe um cruzamento impróprio entre duas arestas  $(v_i^+, v_j^-)$  e  $(v_x^+, v_k^-)$ , com  $i \neq x$ , se e somente se  $\chi((v_i^+, v_j^-), (v_x^+, v_k^-))$  retorna verdadeiro.

Note que, ao se detectar um cruzamento impróprio, não se pode decidir qual das arestas envolvidas é imprópria. Somente quando uma delas está garantidamente no casamento  $\mathcal{M}$ , a outra torna-se imprópria. Assim, a noção de cruzamento impróprio permitirá identificar e eliminar arestas não elegíveis para um casamento próprio, assim que for detectada que uma delas é própria.

# 3.3 Garantias teóricas decorrentes da formulação

As noções apresentadas nas seções anteriores viabilizam a prova de algumas propriedades que serão utilizadas durante a construção de um casamento próprio.

Teorema 1: Identificação de aresta imprópria através de cruzamento impróprio. Sejam um casamento próprio  $\mathcal{M}$  e uma aresta  $(v_i^+, v_j^-) \in \mathcal{M}$ . Se existe um vértice  $v_x^+$  tal que  $(v_i^+, v_x^+) \in R$  e há um cruzamento impróprio entre as arestas  $(v_x^+, v_k^-)$  e  $(v_i^+, v_j^-)$ , então a aresta  $(v_x^+, v_k^-)$  é imprópria.

**Prova:** Se há cruzamento impróprio e o evento  $v_i^+$  precede o evento  $v_x^+$ , concluímos da Definição 10 que j > k, o que contraria a definição de mapeamento próprio  $\mu$  (terceira condição da Definição 5). Logo, pela Definição 8, conclui-se que  $(v_x^+, v_k^-) \notin \mathcal{M}$  e esta aresta é, portanto, imprópria.  $\square$

Note que o Teorema 1 assume que  $\mathcal{M}$  existe e que  $(v_i^+, v_j^-) \in \mathcal{M}$ . Assim, a identificação de arestas impróprias só pode ser realizada a partir de uma aresta já casada (e ainda assim sob a hipótese de que esta aresta pertence a  $\mathcal{M}$ ). Ou seja, o Teorema 1 deve ser aplicado incrementalmente à medida que os vértices são visitados (pruning dinâmico), mas não poderia ser aplicado a priori (pruning estático).

Teorema 2: Identificação de aresta compulsória. Se existe um casamento  $\mathcal{M}$

e há uma única aresta  $(v^+, v^-)$  incidente em  $v^+$ , então  $(v^+, v^-) \in \mathcal{M}$  e esta aresta é dita compulsória.

**Prova:** Como  $(v^+, v^-)$  é única, ela deve pertencer a um casamento completo (se existir um), o que é condição necessária para a existência de um casamento  $\mathcal{M}$  (do contrário  $\mu$  não seria uma função).  $\square$

Cabe ressaltar que o Teorema 2 é um corolário do assim-chamado "Teorema da Redução de Grau Um" [KAR 81], quando aplicado ao problema do casamento completo.

Note ainda que, ao contrário do Teorema 1, o Teorema 2 pode ser aplicado a priori, ou seja, antes de se iniciar quaisquer visitas a vértices para promover seu casamento (*pruning* estático).

Teorema 3: Identificação de aresta imprópria induzida por aresta compulsória. Se  $(v^+, v^-)$  é uma aresta compulsória, então todas as demais arestas incidentes em  $v^-$  são impróprias.

**Prova:** Como  $(v^+, v^-) \in \mathcal{M}$ , pela Definição 8, temos  $\mu(v^+) = v^-$ . Ora, para que uma aresta arbitrária  $(u^+, v^-)$  com  $u^+ \neq v^+$  fosse própria, deveríamos ter  $\mu(u^+) = v^-$ , o que contrariaria a primeira condição da Definição 5 (não-injeção). Logo, toda aresta  $(u^+, v^-)$  é imprópria.  $\square$

Note que, o Teorema 3 não pode ser aplicado isoladamente, mas pode ser invocado imediatamente após a aplicação do Teorema 2 (que representa portanto uma pré-condição).

Vamos enunciar uma importante propriedade de grafos bipartidos, que será invocada no algoritmo a ser proposto, para avaliar a existência de um casamento.

**Teorema 4: Teorema de Hall**: Seja um grafo bipartido G(V,E) cujas partições são  $V^+$  e  $V^-$ . Sejam  $S \subseteq V^+$  e  $Adj(S) = \{v^- \in V^- \mid ((v^+, v^-) \in E) \land (v^+ \in S)\}$ . Existe um casamento completo M, se e somente se  $|S| \leq |Adj(S)|$  para todo  $S \subseteq V^+$ .

**Prova:** Disponível em [HAL 56]  $\square$ .

Por resultar em uma partição do BVG, a noção de componente conexo é central para o algoritmo a ser proposto. Uma primeira utilidade desta noção é formalizada a seguir.

**Definição 11:** Componente conexo impróprio. Um componente conexo  $C_j(V_j, E_j)$  de um grafo bipartido G(V,E) é dito *impróprio*, se e somente se o grafo  $C_j(V_j, E_j)$  não satisfaz o Teorema de Hall.

Teorema 5: Identificação de componente conexo impróprio. Dado um componente conexo  $C_j(V_j, E_j)$  de um grafo bipartido G(V,E), se  $|V_j^+| > |V_j^-|$  então não existe um casamento próprio para G.

**Prova:** Para  $S = V_j^+$ , pela definição de componente conexo, temse  $Adj(S) = V_j^-$ . Como por hipótese  $C_j$  é impróprio, temse |S| > |Adj(S)|, o que contraria a condição necessária para a existência de um casamento completo dos vértices da partição  $V^+$ , segundo o Teorema de Hall. Ora, isso viola a primeira cláusula da Definição 5 e, pela Definição 8, não há casamento próprio em G.  $\square$

Note que o Teorema 5 estabelece uma condição suficiente para identificar um componente conexo impróprio. Em outras palavras, podem existir componentes conexos impróprios não identificáveis através deste teorema.

Assim, para a observabilidade de um dado conjunto de monitores, a aplicação do Teorema 5 garante que nenhum defeito existente no DUV é negligenciado (ausência de falso negativo). Por outro lado, o Teorema 5 por si só não garante que um casamento completo é encontrado sempre que existir um (potencial de falso positivo). Conclui-se assim que esse teorema tem a virtude de restringir o espaço de pesquisa, mas como sua capacidade de diferenciar artefatos de implementação de defeitos é limitada, não pode ser usado como única garantia para a verificação de um sistema. Uma discussão detalhada do impacto do Teorema 5 sobre a qualidade da verificação é apresentada na Seção 4.2.

Lembre, que pelos Teoremas 1 e 3, quando uma aresta  $(v^+, v^-)$  é