# **VU Research Portal**

# Abstractions and Static Analysis for Verifying Reactive Systems

UNIVERSITEIT AMSTERDAM

Yustinova, N.

2004

document version Publisher's PDF, also known as Version of record

Link to publication in VU Research Portal

citation for published version (APA) Yustinova, N. (2004). Abstractions and Static Analysis for Verifying Reactive Systems.

General rights Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain You may freely distribute the URL identifying the publication in the public portal ?

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

E-mail address: vuresearchportal.ub@vu.nl

# Abstractions and Static Analysis for Verifying Reactive Systems

Nataliya Yustinova

#### Centrum voor Wiskunde en Informatica

The work reported in this thesis has been carried out at the CWI (Centrum voor Wiskunde en Informatica) within the SVC (Systems Validation Centre) project funded by Telematics Institute and the KTVFM project funded by the Dutch Ministry of Defence.

Nataliya Yustinova Abstractions and Static Analysis for Verifying Reactive Systems / by Nataliya Yustinova. - Amsterdam: CWI, 2004. Proefschrift. - ISBN 906196 525 X

Subject headings: formal methods / software verification / model checking / static analysis / abstraction / reactive systems

Copyright C2004 by Nataliya Yustinova, Amsterdam, The Netherlands. All rights are reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without prior permission of the author.

# VRIJE UNIVERSITEIT

# Abstractions and Static Analysis for Verifying Reactive Systems

# ACADEMISCH PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Vrije Universiteit Amsterdam, op gezag van de rector magnificus prof.dr.T. Sminia, in het openbaar te verdedigen ten overstaan van de promotiecommissie van de faculteit der Exacte Wetenschappen op donderdag 4 november 2004 om 10.45 uur in het auditorium van de universiteit, De Boelelaan 1105

door

# Nataliya Yustinova

geboren te Yaroslavl, Rusland

promotor: prof.dr. W.J. Fokkink

copromotor: dr. N. Sidorova

# Acknowledgments

The work presented in this thesis has been started in the last year I was employed as a teaching assistant at the Chair of Information and Communication Services, Rostock University, Germany. A major part of this work was done during the three years I was working at the SEN2 (Specification and Analysis of Embedded Systems) group of the Department of Software Engineering, CWI (Centrum voor Wiskunde en Informatica), within the SVC (Systems Validation Centre) project funded by Telematics Institute and the KTVFM project funded by the Dutch Ministry of Defence.

There are many people who helped me to finish this thesis and whom I would like to thank. I am grateful to my promotor Wan Fokkink for his confidence in my ability to succeed, for his advice, constructive criticism and support at important moments. He carefully read all parts of this work and provided feedback that helped me to look at the results of my work from a broader perspective and to reach a significant progress in presenting the results.

I deeply appreciate the help of my co-promotor Natalia Sidorova who guided me in my everyday research life. She encouraged and supported me by sharing with me scientific interests and by being patient explaining me complicated details. I am grateful for the time she spent reading and commenting on this thesis. I have learned a lot from her about planning research, writing scientific articles and giving presentations. Her optimism and good sense of humour kept me going in moments of uncertainty and helped me to finish this work.

My sincere thanks to my other co-authors Martin Steffen, Dragan Bošnački and Stefan Blom. I really enjoyed working with Martin. He never stopped asking critical questions until he was satisfied with the quality of the achieved results. I appreciate the time that Dragan spent helping me to get into subtle implementation details of *Spin* and *DTSpin*, and reading this work as a member of the reading committee. His comments helped me to improve the readability of this thesis. The competent support of Stefan facilitated my work with the  $\mu$ CRL toolset and verification framework. Thanks for our discussions and scientific quarrels.

I am grateful to Walter Vogler, Jaco van de Pol and Jan Willem Klop for their consent to be members of the reading committee. Their comments and remarks contributed to the quality of this thesis. I also thank Kees van Hee and Jan Bergstra who agreed to be members of the promotion committee.

Leon Wolters and Michail Petreczky spent uncounted hours in proof-reading this thesis.

I also owe my success to my former "bosses" Valery Sokolov and Clemens Cap who persuaded me to go on with my scientific career.

In Rostock, I have really enjoyed the journeys to Rügen and playing squash with my colleagues Stephan Preuss, Mykhailo Lyubich, Nico Maibaum and Igor Sedov. Enormous thanks to my flatmates and friends Nadege Spella, Nina Kitzig, Helge Haufe, Katrin Zansinger, Karsten Kaika, Anja Gellert and Donald Reebs with whom I spent a lot of nice evenings.

In Amsterdam, I very much enjoyed the company of Simona Orzan and Daniel Benden who showed me the nightlife of this wonderful town. Thanks to Vincent van Oostrom for scientific hints. I am grateful to Paul Klint for true interest in the progress of my work. Thanks to Joost Visser, Alban Ponse and Engelbert Hubbers who helped me with learning Dutch.

The most heartfelt thanks I want to express to my parents who encouraged my intellectual curiosity and gave me the opportunity to make my own choices and mistakes. I always trusted in their help and support.

# Table of Contents

| Acknowledgments                                                                                                                                                                                                                                                                                     | v                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 1 Introduction1.1 Towards Reliable Reactive Systems1.2 Formal Methods1.3 Research Questions1.4 Road Map1.5 Origins of Chapters                                                                                                                                                                      | 1<br>2<br>4<br>7<br>9<br>10                  |

| <ul> <li>2 Preliminaries</li> <li>2.1 Partially Ordered Sets and Lattices</li> <li>2.2 Transition Systems and Behavioural Equivalences</li> <li>2.3 Temporal and Modal Logic</li> <li>2.4 Model Checking and Automata Theory</li> <li>2.5 Verification by Abstraction</li> </ul>                    | 13<br>14<br>15<br>18<br>24<br>28             |

| <ul> <li>3 Timer Transformation to Verify SDL Specifications</li> <li>3.1 Introduction.</li> <li>3.2 SDL.</li> <li>3.2.1 Syntax Overview</li> <li>3.2.2 SDL Semantics.</li> <li>3.3 Timer Transformation</li> <li>3.4 Model Equivalence</li> <li>3.5 Conclusion</li> </ul>                          | 31<br>32<br>33<br>34<br>37<br>45<br>49<br>68 |

| 4 Using Fairness to Make Abstractions Work         4.1 Introduction.         4.2 Timer Abstraction         4.3 Fair Timer Abstraction         4.4 Incorporating t-Fairness into the Verification Algorithm         4.5 T-fairness in DTSpin         4.6 Experimental Results         4.7 Conclusion | 69<br>70<br>73<br>79<br>82<br>86<br>87<br>91 |

| <ul> <li>5 Closing and Flow Analysis for Model Checking<br/>Reactive Systems</li> <li>5.1 Introduction</li> <li>5.2 Semantics</li> </ul>                                                                                                                                                            | 93<br>94<br>96                               |

## Contents

| 5.3 | Marking Chaotically-influenced Variables                                                                                                 | 105 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | 5.3.1 Data-Flow Analysis                                                                                                                 | 105 |

| 5.4 | Program Transformation                                                                                                                   | 110 |

|     | 5.4.1 Preservation Result                                                                                                                | 114 |

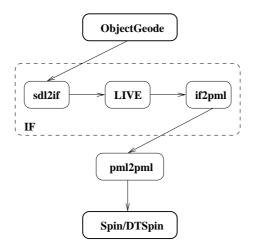

| 5.5 | Implementation                                                                                                                           | 129 |

|     | 5.5.1 Extending the Vires Toolset                                                                                                        | 129 |

|     | 5.5.2 Implementation of the Program Transformation                                                                                       | 130 |

|     | 5.5.3 Experiments                                                                                                                        | 134 |

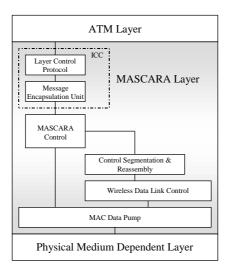

|     | 5.5.4 Case Study: a Wireless ATM Medium-access Protocol                                                                                  | 139 |

| 5.6 | Conclusion                                                                                                                               | 145 |

| _   |                                                                                                                                          |     |

|     | Timed Verification with $\mu$ CRL                                                                                                        | 147 |

|     | Introduction                                                                                                                             | 148 |

|     | $\mu$ CRL: Basic Notions                                                                                                                 | 149 |

|     | Semantics of Time                                                                                                                        | 152 |

|     | Specifying Timed Systems in $\mu$ CRL                                                                                                    | 154 |

|     | Experiments                                                                                                                              | 158 |

| 6.6 | Timed Verification                                                                                                                       | 163 |

|     | $6.6.1 \text{ Regular } LTL \dots \dots$ | 163 |

|     | 6.6.2 Regular $LTL$ with Time                                                                                                            | 164 |

|     | 6.6.3 tick-encoding of Regular <i>LTL</i> with Time                                                                                      | 166 |

| 6.7 | Conclusion                                                                                                                               | 170 |

| 7   | Conclusion                                                                                                                               | 171 |

| •   | conclusion                                                                                                                               | 111 |

|     | Bibliography                                                                                                                             | 176 |

|     | Summary                                                                                                                                  | 187 |

|     | Samenvatting                                                                                                                             | 189 |

## viii

Introduction

1

# 1.1 Towards Reliable Reactive Systems

In the last decades, the application domain of reactive systems has drastically increased. Nowadays, reactive systems are used in various areas, from avionics and automotive systems to telecommunication and manufacturing systems. *Reactive systems* are the systems whose role is to maintain an ongoing interaction with their environment, rather than produce a final value on termination. A typical reactive system exhibits the following distinctive characteristics [125, 84]:

- It continuously interacts with its environment, using inputs and outputs.

- The inputs and outputs are often *asynchronous*, meaning they may arrive and change values at any point of time.

- Its operation and reaction to inputs often reflects strict *time* requirements.

- It has many possible operational scenarios, depending on the current mode of operation and on the current values of its *data* as well as its past behavior.

- Often, it is not expected to terminate.

- In general, it consists of many interacting processes that operate in *parallel*.

Typical examples of reactive systems are on-line interactive systems, such as flight reservation systems; traffic control systems; systems controlling mechanical and electronic devices in a train or a plane; systems controlling ongoing processes in a nuclear reactor.

Behaviour of reactive systems is usually very complex. It cannot be described in an unambiguous, clear and concise way by giving a verbal description. Verbal descriptions tend to be lengthy, incomplete and usually not wellstructured. They contain phrases that can be misinterpreted and implemented in many different ways. Therefore, the need for formal description techniques was realized a long time ago.

In the second half of the 1970s, ISO (International Organization for Standardization) started to work on *formal description techniques* (FDTs) that allow to *specify* reactive systems. After eight years of work, the outcome was standards for Estelle (Extended Finite State Machine Language), LOTOS (Language of Temporal Ordering Specification) and SDL (Specification and Description Language) [161]. The last one is the subject of particular attention in this thesis.

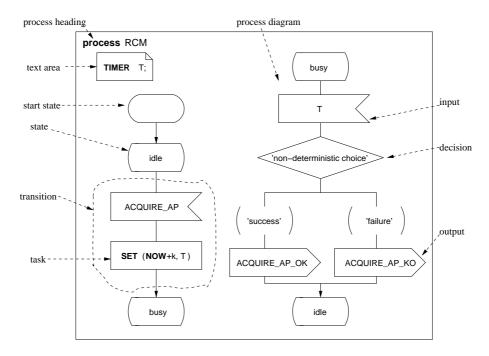

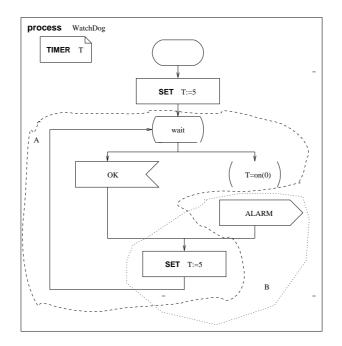

Nowadays SDL is a modern, high-level specification language suitable for the description of complex event-driven real-time communicating systems. SDL provides concepts for the specification of behaviour covering asynchronous communication and parallelism. It also allows to express qualitative and quantitative time requirements for reactive systems. SDL concepts used for describing system behaviour and communication were integrated into those of UML (e.g. SDL process diagrams correspond to UML state diagrams; SDL communication links correspond to UML associations [141]).

In the telecommunication field, SDL is the language of choice for the development of a broad range of software and hardware. Examples are 3G products, cellular phones, switches, WAP stacks, Bluetooth devices, GPRS systems, DECT phones, radio systems, network management platforms and network services systems. Other examples are telecommunication standards like UMTS, GSM, ISDN, V5.2, INAP, etc. SDL is also used in factory automation systems, aerospace and automotive applications, and other safety-critical systems, e.g. kidney-dialysis devices and train-control systems. SDL is used by standardization organizations, universities and companies all over the world (e.g. Alcatel, Ericsson, Fujitsu, Hewlett-Packard, Lucent Technologies, Motorola, Nokia, Nortel, Siemens, BT, Deutsche Telekom and NTT) [157]. In this thesis, we chose an approach to the specification of reactive systems inspired by SDL.

There is a wide range of reactive systems where errors can have catastrophic consequences leading to loss of lives, serious environmental damage, failure of an important mission, or major economic loss. Here are just two examples of such errors.

Huge losses of monetary and intellectual investment were caused by a rocket boost failure in Ariane 5 in June, 1996 ([99]). Ariane 5, an expendable launch system, was designed by the European Space Agency (ESA) and manufactured, operated and marketed by Arianespace as part of the Ariane program. Ariane 5 software reused old code from Ariane 4 that was not respecified and retested in the new environment. Ariane 5 being more powerful than Ariane 4 caused an unanticipated floating-point exception that would never have occurred on Ariane 4. The exception was not caught. Direct cost of this failure was estimated at 0.5 billion EUR, indirect cost at 2 billion EUR.

Another example is a failure that caused a power shutdown of cruiser USS Yorktown in November 1998 ([99]). A crew member of the guided-missile cruiser USS Yorktown mistakenly entered zero for a data value, which resulted in a division by zero. The division by zero caused an arithmetic exception, which propagated through the system, crashed all LAN consoles and remote terminal units, and led to a power shutdown for about three hours.

The failure in Ariane 5 software and the power shutdown of cruiser USS Yorktown are just a few of many reactive system's failures with serious consequences. Therefore, the production of reliable reactive systems became a fundamental concern to computer scientists. Different techniques like static analysis, testing, and various formal methods were developed by academic and industrial communities to ensure the quality and reliability of reactive systems.

Static analysis [131] is a broad term covering a wide range of analysis techniques evaluating programs without executing them. Traditionally, static analysis was aimed at the optimization of programs. Typical applications include detecting *redundant* computations, e.g. loop invariants, and detecting *superfluous* computations that lead to results that are not used or results that are known already at compile-time. Static analysis is also applied for type checking, performance analysis and partial evaluation. Moreover, there are approaches integrating static analysis with formal methods. For example, static analysis is often used prior to model checking (cf. Section 1.2) to slice programs into smaller parts or to identify independent fragments of a program that can be executed in parallel.

Testing [172, 33] is still one of the most popular techniques that is used in industry to ensure the reliability of systems. In testing approaches, the system is simulated with certain inputs called stimuli, and the reaction of the system to stimuli is compared with the one defined by the requirement specification. Exhaustive testing covering all possible system scenarios is practically impossible, hence testing allows to gain confidence about the correctness of the system by looking at *some* of them but it cannot guarantee the absence of errors. This thesis does not deal with testing.

*Formal methods* allow to determine system correctness by formal proofs that cover *all* possible scenarios of the system. They not only help to find errors that are missed by testing but can also prove that the system meets its requirements. The usage of formal methods in early phases of system development makes possible early detection of errors, which greatly reduces the costs of their correction.

# **1.2 Formal Methods**

The term *formal methods* covers different approaches to specification and verification based on mathematical formalisms. Formal methods are aimed at establishing system correctness with mathematical precision. Every formal approach to system verification usually involves a mathematical *model* of a system, a *formal language* to specify properties of the system, and a *method* to check whether the model satisfies the specification.

Labelled transition systems (LTSs) are a common basis for modelling the behaviour of reactive systems. LOTOS, Estelle and SDL share LTSs as the formal basis of their operational semantics. Therefore, we have chosen LTSs as mathematical model for reactive systems.

Various logics have been proposed to specify properties of systems, e.g. computation tree logic (*CTL* [62]), linear temporal logic (*LTL* [137]) and  $\mu$ -calculus [112]. In this thesis, we use *LTL* and some subsets of  $\mu$ -calculus to express properties of reactive systems.

Verifying (or checking) whether a model of a system satisfies certain properties may be partially or completely *automated*. Two well-established formal approaches to computer-aided verification are *theorem proving* and *model checking*.

**Theorem Proving**. In theorem proving, a system and its properties are expressed in terms of some mathematical logic. This logic is defined by a formal system that provides a set of axioms and a set of inference rules. Theorem proving consists in finding a proof of a property from the axioms of the system. Steps in the proof appeal to the axioms, rules, and, possibly, to derived definitions and intermediate lemmas. There are tools supporting machine-assisted theorem proving, e.g. PVS [134]. Theorem provers are increasingly being used

today in the mechanical verification of safety-critical properties of hardware and software designs [43, 149].

Theorem proving can deal directly with infinite state spaces. It relies on techniques like structural induction to construct proofs over possibly infinite domains. Interactive theorem provers, by definition, require a *lot of interaction* with a human, so the theorem proving process is *slow and very expensive* [43]. In the process of finding the proof, however, the user often gains better insight into the system or the property being proved. Theorem proving is out of the scope of this thesis.

**Model Checking**. Model checking is considered as the method of choice in the verification of reactive systems and is increasingly accepted in industry for its push-button appeal. The term *model checking* designates a collection of formal techniques for the automatic analysis of reactive systems. Subtle errors in the design of reactive systems that often elude conventional verification techniques like testing can be and have been found in this way. Since model checking has been proved cost-effective and integrates well with conventional design methods, model checking has been accepted as a standard procedure to assure the quality of reactive systems [42, 43].

The input to a model checker is usually a finite-state description of the system to be analyzed and a number of properties that are expected to hold for the system, often expressed as formulas of some temporal logic. In contrast to theorem proving, model checking is completely *automatic* and relatively *fast*, often producing an answer in a matter of seconds. The model checker reports either that the property holds or that it is violated. In the latter case, it *provides a counterexample*, a run of the system that violates the property. Such a run can provide a valuable feedback and points to design errors. Model checking can be used to check partial specifications, and thus it can provide useful information about a system's correctness even if the system has not been completely specified.

There are two approaches to model checking: *symbolic* as in NuSMV [37] and COSPAN [83], and explicit state (or *enumerative*) as in Spin [93] and CADP [65]. In the *symbolic* approach, a finite-state system is encoded using a set of binary variables, just as ordinary data types of programming languages are represented in binary form on a computer. The transition relation is expressed as a propositional formula in terms of two sets of variables, one set encoding the old state and the other encoding the new one. Propositional formulas are then represented as binary decision diagrams (BDDs [32]). The model checking algorithm is based on computing fixpoints of predicate transformers that are obtained from the transition relation [124].

Although the symbolic approach can lead to spectacular results, it is not a panacea. Effectiveness of symbolic model checking depends on finding a "good" variable ordering for the representation of a BDD. However, finding a "good" variable ordering is very difficult [127].

State space *enumeration* methods consider each reachable state of a model (a finite-state system) to determine whether the model satisfies a given property.

The main obstacle in model checking of industrial reactive systems is the state explosion problem. The size of the model often grows exponentially with the number of system components working in parallel. The research questions considered in this thesis mainly deal with the development of techniques to cope with the state explosion problem in enumerative model checking.

A number of techniques have been developed to mitigate the state explosion problem: *abstraction* [122, 41, 50], *compositional verification* [148], *partial-order reduction* [74, 163, 95], and *on-the-fly* techniques [93].

**Abstraction.** The size of systems that can be analyzed by model checking directly remains rather limited. It is still far from the size of real reactive systems, which are often not only large but infinite. Therefore, model checking must be performed on abstract models.

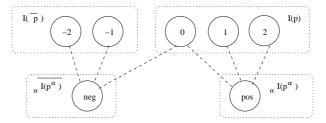

Abstraction methodologies are concerned with the following question [48]: Given a concrete system and a property to be checked, how to get a suitable abstract system of finite (smaller) size? To answer this question, an abstraction framework must provide three things: a method for obtaining abstract models, a method for relating abstract and concrete models, and a logic stating properties so that properties satisfied on the abstract system can be related to properties of the concrete system. In general, when we say that a system  $T^{\alpha}$  is an abstraction of a system T, we mean that the observable behaviour of T is contained in the observable behaviour of  $T^{\alpha}$ .

Methods for obtaining abstract models range from slicing and variable hiding to more general algorithmic approaches like program transformation based on Abstract Interpretation [46]. The relationship between abstract and concrete models is usually defined in terms of bisimulation, homomorphism, Galois connection or simulation (cf. Chapter 2). Given a property of some logic, two types of preservation are considered: *weak preservation*, when every property that is *true* on the abstract model is also *true* on the concrete one, and *strong preservation*, when the same properties hold on the abstract and concrete models [121].

**Compositional Verification.** State explosion can be alleviated by decomposing a system into components and considering the components of the system one at a time. As in the case of abstraction, compositional verification requires additional input from the user who must specify appropriate properties of individual components. The components do not necessarily function properly in an arbitrary environment. Their behaviour relies on the properties of the rest of the system. Thus, corresponding assumptions have to be introduced in the statement of components' properties [122].

**Partial-Order Reduction** is aimed at reducing the size of a system by exploiting the commutativity of concurrently executed actions that result in the same state when executed in different orders. The effectiveness of partial-order reduction methods in general depends on the structure of the system: they are useless for tightly synchronized systems, while they may dramatically reduce the number of states and transitions explored during model checking of loosely coupled, asynchronous systems [42].

**On-the-fly** techniques allow to minimize the memory demands of model checkers by constructing only those parts of systems that are necessary to verify or refute a given property [93].

#### Verification of Timed Systems

Quantitative time aspects are often important for correct functionality of reactive systems. Various formalisms such as timed transition systems [89], timed automata [1] and logics [3] have been proposed to model them. When modelling time, two time domains, discrete and dense, are usually differentiated. In the case of a *dense time domain*, time is modelled by real numbers and time progression has a continuous nature. In the case of a *discrete time domain*, time is modelled by non-negative integers and time progresses by discrete steps.

Dense time often allows a more adequate representation of reality than discrete time but it also leads to verification algorithms with higher complexity. UPPAAL [119] is a leading toolset produced in the academic community for the verification of timed systems with dense time. Various verification options like bit-hashing, inactive clock reduction, compact memory management, counterexample generation, etc. are provided for the verification [15]. Designed for the analysis of timed aspects of reactive systems, UPPAAL is not aimed at the verification of the data aspects.

In [88], Henzinger, Manna and Pnueli showed that discrete time suffices for a large and important class of systems and properties, including all systems that can be modelled as timed transition systems, and such properties as timebounded invariance and time-bounded response. In [29], the authors state that discrete-time automata can be analyzed using any representation scheme used for dense time, and *additionally* can benefit from enumerative and symbolic techniques, which are not naturally applicable to the systems with dense time.

In this thesis, we limit our attention to reactive systems with discrete time. DTSpin [24, 55], a discrete time extension of the Spin model checker, was used for the majority of experiments mentioned in this thesis.

# **1.3 Research Questions**

In this section, we formulate the research questions that are considered in this thesis. All research questions are related to the state explosion problem, which can be caused by various factors like interpretation of time, data aspects, asynchronous communication, etc.

#### Modelling time aspects

Reactive systems are usually timed systems that must respond within certain time limits. Interpretation of time and time constraints in a specification language is very much affected by the intended mode of its use. In implementationorientated languages, time is modelled as an infinitely growing variable of integer or real type. One infinitely growing variable immediately leads to an infinite system.

Timers are usually employed to express time constraints imposed on a reactive system. They can be used for several purposes: to control the release of a limited resource, to control answers from unreliable resources, to issue actions on a regular basis, etc. Timers are modelled as alarm clocks that either send a signal or throw an exception at the right moment of time. Timers are set to moments in time when they should expire. Since reactive systems are usually not supposed to terminate, settings of timers are unbounded. This interpretation, natural for implementation purposes, is, however, not the best choice for verification.

Taking SDL as an instance of the class of implementation-oriented languages, our objective is to provide an interpretation of time and timers that alleviates the state explosion problem and to show that systems with this interpretation can safely be used for verification.

#### Abstracting timers

Correctness of reactive systems often depends on right timer settings. Model checkers can only verify a single finite-state system at a time. Direct model checking whether a system works for all settings of a timer larger than or equal to some k would require one iteration for each setting larger than some k, i.e., we would need infinitely many iterations. In some cases, it would be more convenient to reason automatically about a family of similar systems. The verification problem in this case can be formulated as follows: given a family of systems whose timer settings satisfy condition "larger than or equal to some k" and a property, check whether the property holds for each system in the family. This problem is undecidable for model checking [7]. In some cases, an abstraction that treats settings of a timer as a system parameter can be used to solve this problem.

Abstractions, however, introduce infinite traces that do not correspond to any behaviour of the real system that can lead to false negatives. Our objective is to show how to exclude nuisance behaviour in case of a timer abstraction and how to do that in the most efficient way.

#### Closing open systems

Most model checkers cannot handle open systems. Therefore, the next step following the decomposition of a system into components is *closing* components with an environment.

Closing open systems is commonly done by adding an environment that is an abstraction of the real environment. The simplest safe abstraction of the environment thus behaves *chaotically*. When done manually, this closing, as simple as it is, is tiresome and error-prone for large systems, for instance due to the sheer amount of signals.

#### 1.4 Road Map

For model checking, the approach to closing should be well-considered, to counter the state explosion problem. This is especially true in the context of model checking reactive systems where components communicate *asynchronously*. Sending arbitrary message streams to unbounded input queues will immediately lead to an infinite system, unless some assumptions restricting the environment behaviour are incorporated in the closing process. Even so, external chaos results in a combinatorial explosion caused by all combinations of messages in the input queues.

Another problem addressed by closing is that the *data* carried with the messages coming from the environment is usually drawn from some infinite data domain. Special care must be taken to ensure that chaos also shows more behaviour with regards to *timing* issues such as timeouts and time progress. Our objective is to provide an automatic approach to closing asynchronous open timed systems.

#### Reuse of untimed verification methods for timed verification

Many formalisms have been proposed for timed verification. Most of them are designed for the analysis of timed aspects of reactive systems, while data aspects are usually not taken into account. On the other side, there exist powerful formalisms that are able to handle both data and behaviour aspects of reactive systems but are originally not aimed at the verification of time issues. Our challenge is to show how to reuse untimed formalisms with good support for data types and behaviours for the verification of reactive systems with discrete time.

# 1.4 Road Map

Chapter 2 reviews some mathematical notions and some notions from computer science that will be used in the rest of the thesis.

Chapter 3 presents a transformation of SDL timers aimed at reducing the infinite domain of timer values to a finite one. We justify the proposed transformation by proofs that allow us to transfer both negative and positive results of verification from the transformed model to the original one. We show that the transformed model and the original one are related by path equivalence up to stuttering. This guarantees that any LTL-X-formula satisfied by the transformed model is satisfied by the original one, and that a counterexample trace found in the transformed system can also be found in the original one.

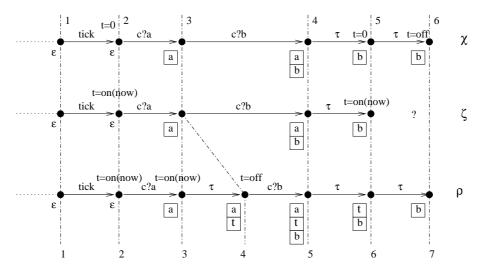

In Chapter 4, we propose a timer abstraction and argue its correctness. The abstraction introduces infinite traces that have no corresponding traces at the concrete level. We show how to exclude them by imposing a strong fairness constraint on the abstract model. By employing the fact that the timer abstraction introduces a self-loop, we render the strong fairness constraint into a weak fairness constraint and embed it into the verification algorithm.

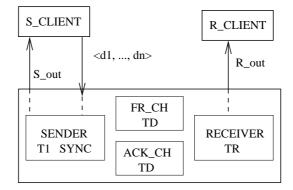

In Chapter 5, we propose an automatic transformation yielding a closed system. By *embedding* the outside chaos into the system, we avoid the state-space penalty in the input queues mentioned above. To capture the chaotic timing behaviour of the environment, we introduce a non-standard three-valued timer abstraction. The transformation is based on *data-flow analysis* that detects instances of chaotic variables and timers. The approach is implemented in a tool that automatically closes DTPROMELA translations of SDL-specifications. To corroborate the usefulness of our approach, we compare the state space of a system closed by embedding chaos with the state space of the same system closed with chaos as external environment process on a case study for a wireless ATM medium-access protocol.

In Chapter 6, we propose a manner of introducing discrete time into the  $\mu$ CRL language without extending the language. The specification language  $\mu$ CRL [78] (micro Common Representation Language) is a process algebraic language that was especially developed to take account of data in the study of communicating processes. The  $\mu$ CRL toolset [19] together with the CADP toolset [65] provides support for enumerative model checking. The semantics of discrete time we use makes it possible to reduce the *time progress* problem to the diagnostics of "no action is enabled" situations. The synchronous nature of  $\mu$ CRL facilitates this task. We show some experimental verification results obtained on a timed communication protocol.

Each of these chapters contains an introduction giving an elaborated motivation and an overview of related work.

Chapter 7 discusses how our research questions are answered in this thesis.

# **1.5** Origins of Chapters

Chapter 3, "Timer Transformation to Verify SDL Specifications", was coauthored with Natalia Sidorova. It was published earlier as:

N. Ioustinova and N. Sidorova. Transformation of SDL specifications - a step towards the verification. In D. Bjorner, M. Broy, and A. Zamulin, editors, *Post*proceedings of Andrei Ershov Fourth International Conference Perspectives of System Informatics (PSI 01), volume 2244 of Lecture Notes in Computer Science, pages 64–78. Springer, 2001.

Chapter 4, "Using Fairness to Make Abstractions Work", was co-authored with Dragan Bošnački and Natalia Sidorova. It was published earlier as:

D. Bošnački, N. Ioustinova, and N. Sidorova. Using fairness to make abstractions work. In S. Graf and L. Mounier, editors, *Proc. of the 11th Int. Spin Workshop on Model Checking of Software*, volume 2989 of *Lecture Notes in Computer Science*, pages 198–215. Springer, 2004. Chapter 5, "Closing and Flow Analysis for Model Checking Reactive Systems", was co-authored with Natalia Sidorova and Martin Steffen. It was published earlier as:

N. Ioustinova, N. Sidorova, and M. Steffen. Abstraction and flow analysis for model checking open asynchronous systems. In P. Strooper and P. Muenchaisri, editors, *Proc. of the 9th Asia Pacific Software Engineering Conference (APSEC 2002)*, pages 227–235. IEEE Computer Society, 2002.

N. Ioustinova, N. Sidorova, and M. Steffen. Closing open SDL-systems for model checking with *DTSpin*. In L. H. Eriksson and P. A. Lindsay, editors, *FME 2002: Formal Methods - Getting IT Right, Proc. of International Symposium of Formal Methods Europe, FME 2002*, volume 2391 of *Lecture Notes in Computer Science*, pages 531–548. Springer, 2002.

N. Ioustinova, N. Sidorova, and M. Steffen. Synchronous closing and flow abstraction for model checking timed systems. In *Proc. of the Second International Symposium on Formal Methods for Components and Objects (FMCO'03)*, volume (to appear) of *Lecture Notes in Computer Science*. Springer, 2004.

Chapter 6, "Timed Verification with  $\mu$ CRL", was co-authored with Stefan Blom and Natalia Sidorova. It was published earlier as:

S. Blom, N. Ioustinova, and N. Sidorova. Timed verification with  $\mu$ CRL. In M. Broy and A. Zamulin, editors, *Proc. of the 5th Int. Conf. Perspectives of System Informatics*, volume 2890 of *Lecture Notes in Computer Science*, pages 178–192. Springer, 2003.

Preliminaries

This chapter reviews some mathematical notions and some notions from computer science that will be used in the rest of the thesis.

# 2.1 Partially Ordered Sets and Lattices

The notions of a partially ordered set, a complete lattice and fixed points play a crucial role in static analysis. Here we review basic definitions and some results about partial orders, lattices, least and greatest fixed points [53].

#### **Definition 2.1.** [PARTIAL ORDER]

Let S be a set. An order (or partial order) on S is a binary relation  $\sqsubseteq$  on S such that for all  $s, s_1, s_2, s_3 \in S$ ,

$$\begin{array}{l} - s \sqsubseteq s, \\ - s_1 \sqsubseteq s_2 \land s_2 \sqsubseteq s_1 \Rightarrow s_1 = s_2, \\ - s_1 \sqsubseteq s_2 \land s_2 \sqsubseteq s_3 \Rightarrow s_1 \sqsubseteq s_3. \end{array}$$

These conditions are referred to as *reflexivity*, *antisymmetry* and *transitivity*, respectively. A set S equipped with an order relation  $\sqsubseteq$  is called an *ordered set* (or *partially ordered set*) denoted  $(S; \sqsubseteq)$ . Further we use the shorthand *poset*.

Many important posets are expressed in terms of existence of certain upper and lower bounds of subsets of S. The most important classes of posets defined in this way are lattices and complete lattices.  $s \in S$  is the *least element* of Sif  $s \sqsubseteq s'$  for all  $s' \in S$ . The greatest element of S is defined dually. A subset S' of S has  $s \in S$  as an upper bound if for all  $s' \in S'$ :  $s' \sqsubseteq s$ . A subset S' of S has  $s \in S$  as an lower bound if for all  $s' \in S'$ :  $s \sqsubseteq s'$ . A least upper bound sof S' is an upper bound of S' such that  $s \sqsubseteq s''$  for all upper bounds s'' of S'. A greatest lower bound s of S' is a lower bound of S' such that  $s'' \sqsubseteq s$  for all lower bounds s'' of S'.

#### **Definition 2.2.** [COMPLETE LATTICE]

A complete lattice is a poset S such that all its subsets have a least upper bound and a greatest lower bound.

Further, greatest lower bound and least upper bound of S, when they exist, are denoted as lub(S) and glb(S), respectively.

#### **Definition 2.3.** [FIXPOINT]

Let S be a poset and  $f: S \to S$  be a function. We say  $s \in S$  is a fixpoint of f if f(s) = s. The set of all fixpoints of f is denoted fix(f). The least element of fix(f), when it exists, is called the least fixpoint of f. Similarly we define the greatest fixpoint of f.

Let  $(S, \sqsubseteq)$  be a complete lattice and  $f: S \to S$  be a function. We say that f is monotonic if  $f(s) \sqsubseteq f(s')$  whenever  $s \sqsubseteq s'$ .

#### Theorem 2.1. [KNASTER/TARSKI]

Let  $(S, \sqsubseteq)$  be a complete lattice and  $f: S \to S$  be a monotonic function. Then f has a greatest fixpoint gfp(f) and a least fixpoint lfp(f).

#### **Definition 2.4.** [GALOIS CONNECTION]

Let  $(S; \sqsubseteq)$  and  $(A; \preceq)$  be posets. A pair of mappings  $\alpha : S \longrightarrow A$ ,  $\gamma : A \longrightarrow S$ is a Galois connection  $(\alpha, \gamma)$  from S to A iff for all  $s \in S$  and  $a \in A$ ,  $\alpha(s) \preceq a \Leftrightarrow s \sqsubseteq \gamma(a)$ .

# 2.2 Transition Systems and Behavioural Equivalences

#### **Definition 2.5.** [TRANSITION SYSTEM]

A transition system T is a tuple (S, R) where S is a set of states and  $R \subseteq S \times S$  is a transition relation.

A transition system can have various attributes. Often a subset  $S_0 \subseteq S$  is designated to represent the initial states. A transition system may come with an *interpretation function*  $\mathcal{I}: \mathcal{P} \to 2^S$  that specifies interpretation of atomic propositions from  $\mathcal{P}$  over the states (see Section 2.3). Alternatively, valuation of literals in states may be given by a *labelling function*  $\mathcal{L}: S \to 2^{\mathcal{P}}$  specifying the propositions that hold in a state. A transition system with initial states and an interpretation function  $\mathcal{L}$  is also called *Kripke structure* [113] (see Section 2.3). Not only states but also transitions of the system can be labelled.

#### Definition 2.6. [LTS]

A labelled transition system (LTS) T is a tuple  $(S, Lab, \rightarrow, s_0)$  where

- -S is a set of states or locations;

- Lab is a set of labels;

- $\rightarrow \subseteq S \times Lab \times S$  is a labelled transition relation;

- $s_0 \in S$  is an initial state.

Further we write  $s \to_{\lambda} s'$  for a triple  $(s, \lambda, s') \in \to$ . A triple  $(s, \lambda, s')$  is also referred to as a  $\lambda$ -step of T.

#### **Definition 2.7.** [TRACE]

Let  $T = (S, Lab, \rightarrow, s_0)$  be an LTS. A trace  $\zeta$  of T is a pair of mappings  $\zeta_{\gamma} : N \longrightarrow S$  and  $\zeta_{\lambda} : N \setminus \{0\} \longrightarrow Lab$ , where either  $N = \{0, 1, 2, ..., n\}$  or  $N = \mathbb{N}$ , and  $(\zeta_{\gamma}(i) \rightarrow_{\zeta_{\lambda}(i+1)} \zeta_{\gamma}(i+1)) \in \rightarrow$  for all  $i, (i+1) \in N$ . If  $N = \mathbb{N}$ , trace  $\zeta$  is called an infinite trace; otherwise, it is called a finite trace. The length of  $\zeta$  is defined as  $|N \setminus \{0\}|$  and referred to as  $|\zeta|$ .

We use  $\zeta^{(m)}$  to denote the prefix of  $\zeta$  ending at  $\zeta_{\gamma}(m)$ . We also use  $\zeta_{(m)}$  to denote the suffix of  $\zeta$  starting at  $\zeta_{\gamma}(m)$ . Of course  $\zeta^{(m)}$  is defined iff  $\zeta$  has a length at least m.  $\zeta_{(m)}$  is defined only in case  $\zeta$  has a length at least m + 1.

#### **Definition 2.8.** [PARTITIONING]

Let  $\zeta = (\zeta_{\gamma}, \zeta_{\lambda})$  be a trace of an LTS T. Let N be the domain of  $\zeta_{\gamma}$ . Let I be a connected subset of N, i.e., it is either  $I = \{z \mid k \leq z \leq m\}$ , where k < m, or  $I = \{z \mid z \geq k\}$ . A pair  $\zeta^{I} = (\zeta^{I}_{\gamma}, \zeta^{I}_{\lambda})$  of mappings  $\zeta^{I}_{\gamma} : I \longrightarrow S$  and  $\zeta^{I}_{\lambda} : I \setminus \{k\} \longrightarrow$  Lab is called a part of trace  $\zeta$  iff the following conditions are satisfied:

- for all  $i \in I$ :  $\zeta_{\gamma}^{I}(i) = \zeta_{\gamma}(i)$ ;

- for all  $j \in I \setminus \{k\}$ :  $\zeta_{\lambda}^{I}(j) = \zeta_{\lambda}(j)$ .

Let  $\zeta^{I_1}$  and  $\zeta^{I_2}$  be two parts of  $\zeta$ .  $\zeta^{I_1 \cup I_2}$  is called the concatenation of  $\zeta^{I_1}$ and  $\zeta^{I_2}$  iff  $I_1 = \{k, \ldots, m\}$  and  $\min_{i \in I_2} i = m$ .

A partitioning of trace  $\zeta$  is a finite or infinite sequence  $\zeta^{I_1}\zeta^{I_2}\ldots$  of parts of  $\zeta$  such that the concatenation of the parts coincides with  $\zeta$ .

#### **Definition 2.9.** [REACHABLE STATE]

Let  $T = (S, Lab, \rightarrow, s_0)$  be an LTS. A state  $s \in S$  is reachable from the initial state of the system if there is trace  $\zeta$  of T such that  $\zeta_{\gamma}(0) = s_0$  and  $\zeta_{\gamma}(i) = s$  for some  $i \geq 0$ .

A wide range of behavioural equivalences and relations has been developed to distinguish two systems. Often the notion of equivalence between two systems is based upon the idea that we only distinguish between system  $T_1$  and system  $T_2$  if the distinction can be detected by an external system interacting with each of them. [71] provides an overview and comparison of existing behavioural equivalences. Further we review notions of trace equivalence, simulation, bisimulation and isomorphism for LTSs. Trace equivalence requires that systems can execute the same traces but does not require that systems have the same branching structure. Bisimulation and isomorphism allow to distinguish systems that have different branching structures. Let  $T_1 = (S_1, Lab_1, \rightarrow^1, s_0^1)$ and  $T_2 = (S_2, Lab_2, \rightarrow^2, s_0^2)$  be two LTSs.

#### **Definition 2.10.** [STRONG EQUIVALENCE OF TRACES]

Let  $\zeta$  and  $\rho$  be traces of LTSs  $T_1$  and  $T_2$  respectively. We say that  $\zeta \equiv_{tr} \rho$  iff  $|\zeta| = |\rho|$  and  $\zeta_{\lambda}(i+1) = \rho_{\lambda}(i+1)$  for all  $i = 0..|\zeta|$ .

#### **Definition 2.11.** [STRONG TRACE INCLUSION]

We say that the set of traces generated by LTS  $T_2$  includes the set of traces generated by LTS  $T_1$ , written as  $T_1 \preceq_{tr} T_2$ , iff for every trace  $\zeta$  of  $T_1$  there exists a trace  $\rho$  in  $T_2$  such that  $\zeta \equiv_{tr} \rho$ .

#### **Definition 2.12.** [STRONG TRACE EQUIVALENCE]

Two LTSs  $T_1$  and  $T_2$  are trace equivalent, written as  $T_1 \equiv_{tr} T_2$ , iff both  $T_1 \preceq_{tr} T_2$  and  $T_2 \preceq_{tr} T_1$ .

#### **Definition 2.13.** [STRONG SIMULATION]

A relation  $R \subseteq S_1 \times S_2$  is a strong simulation relation between LTS  $T_1$  and LTS  $T_2$  iff  $s_0^1 R s_0^2$ , and pRq together with  $p \to_{\lambda}^1 p'$  implies  $q \to_{\lambda}^2 q'$  and p' Rq', for some  $q' \in S_2$ .

We write  $T_1 \leq T_2$ , if there exists a strong simulation relation R between  $T_1$ and  $T_2$ .

#### **Definition 2.14.** [STRONG BISIMULATION]

A relation  $R \subseteq S_1 \times S_2$  is a strong bisimulation relation between LTS  $T_1$  and LTS  $T_2$  iff both R and  $R^{-1}$  are strong simulations.

We write  $T_1 \leftrightarrow T_2$ , if there exists a strong bisimulation relation R between  $T_1$  and  $T_2$ .

It is straightforward to check that  $\leftrightarrow$  is an equivalence relation, i.e.,  $\leftrightarrow$  is reflexive, symmetric and transitive.

#### **Definition 2.15.** [ISOMORPHISM]

Two LTSs  $T_1$  and  $T_2$  are isomorphic iff there is a bijection  $g: S_1 \to S_2$  such that  $\forall s, s' \in S_1, s \to_{\lambda}^1 s'$  iff  $g(s) \to_{\lambda}^2 g(s')$ .

Isomorphism implies strong bisimulation; strong bisimulation implies strong trace equivalence; strong simulation implies strong trace inclusion.

[72] provides an overview of existing process equivalences and relations in context of process algebras with *silent moves*. There, only a set of external actions of a system is visible to an observer and the internal structure of the system is hidden. Which activities of the system are hidden is a matter of choice that depends on the level of detail at which one wants to analyse the system. The hidden activities of the system are denoted as  $\tau$ .

Weak trace equivalence relates two systems that can perform exactly the same sequence of observable actions.

#### **Definition 2.16.** [WEAK EQUIVALENCE OF TRACES]

Let  $\zeta$  and  $\rho$  be traces of LTSs  $T_1$  and  $T_2$  respectively. We say that  $\zeta \equiv_{wtr} \rho$ iff  $\zeta$  and  $\rho$  can be partitioned as  $\zeta^1 \zeta^2 \dots$  and  $\rho^1 \rho^2 \dots$  respectively, so that the following conditions are satisfied:

$\begin{array}{l} - \ every \ \zeta^k, \ \rho^k \ has \ at \ most \ one \ step \ labelled \ with \ \lambda \neq \tau; \\ - \ \zeta^k \ contains \ a \ step \ labelled \ by \ \lambda \neq \tau \ iff \ \rho^k \ contains \ a \ step \ labelled \ by \ \lambda \neq \tau. \end{array}$

## **Definition 2.17.** [WEAK TRACE INCLUSION]

We say that the set of traces generated by LTS  $T_2$  weakly includes the set of traces generated by LTS  $T_1$ , written as  $T_1 \preceq_{wtr} T_2$ , iff for every trace  $\zeta$  of  $T_1$ there exists a trace  $\rho$  in  $T_2$  such that  $\zeta \equiv_{wtr} \rho$ .

#### **Definition 2.18.** [WEAK TRACE EQUIVALENCE]

Two LTSs  $T_1$  and  $T_2$  are weakly trace equivalent, written as  $T_1 \equiv_{wtr} T_2$ , iff both  $T_1 \preceq_{wtr} T_2$  and  $T_2 \preceq_{wtr} T_1$ .

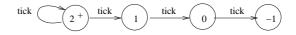

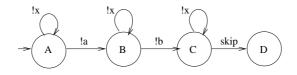

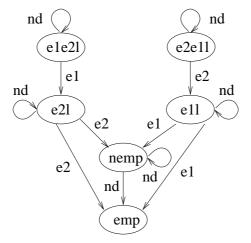

Intuitively, a  $\tau$ -step is not truly silent if it results in a change of "potential" of the system. For example, consider the LTS on Fig. 1. After execution of the  $\tau$ -step the system loses the option to execute step a. Therefore, the  $\tau$ -step of the system is not truly silent. The intuition of a truly silent  $\tau$ -step is formalized in the notions of branching simulation and branching bisimulation [70].

#### **Definition 2.19.** [BRANCHING SIMULATION]

A relation  $R \subseteq S_1 \times S_2$  is a branching simulation relation between LTSs  $T_1$  and  $T_2$  iff  $s_0^1 R s_0^2$  and pRq together with  $p \to_{\lambda}^1 p'$  implies that one of the following conditions holds:

1.  $q \to_{\tau} q'_1 \to_{\tau} \ldots \to_{\tau} q'_n \to_{\lambda} q'$ , for some  $n \ge 0$  and  $q', q'_1, \ldots, q'_n \in S_2$  such that  $pRq'_i$  for all i = 1..n and  $p'Rq'_i$ ;

**Fig. 1.** Not truly silent  $\tau$

2.  $\lambda = \tau$  and p'Rq.

We write  $T_1 \preceq_{br} T_2$  if there exists a branching simulation relation R between  $T_1$  and  $T_2$ .

**Definition 2.20.** [BRANCHING BISIMULATION]

A relation  $R \subseteq S_1 \times S_2$  is a branching bisimulation relation between LTSs  $T_1$ and  $T_2$  iff both R and  $R^{-1}$  are branching simulations.

We write  $T_1 \underset{br}{\leftrightarrow} _{br}T_2$  if there exists a branching bisimulation relation R between  $T_1$  and  $T_2$ .

In [13], it was shown that branching bisimulation is indeed an equivalence relation.

# 2.3 Temporal and Modal Logic

Various logics have been developed to specify properties of systems and programs, e.g., computation tree logic  $(CTL^*)$  [62], linear temporal logic (LTL)[137] and  $\mu$ -calculus [112]. They allow to express universal and existential properties that hold for all or some traces of a system respectively. Various safety ("nothing bad will ever happen") and liveness ("something good must eventually happen") properties can be expressed as well.

#### **Definition 2.21.** $[CTL^*]$

Given a set of atomic proposition  $\mathcal{P}$ , the logic  $CTL^*$  consists of state  $\varphi$  and path  $\psi$  formulas defined by the following grammar:

$$\begin{split} \varphi &::= p \ \mid \ \neg \varphi \ \mid \ \varphi \lor \varphi \ \mid \ \varphi \land \varphi \ \mid \ \mathbf{A}\psi \ \mid \ \mathbf{E}\psi, \ where \ p \in \mathcal{P} \\ \psi &::= \varphi \ \mid \ \neg \psi \ \mid \ \psi \lor \psi \ \mid \ \psi \land \psi \ \mid \ \mathbf{X}\psi \ \mid \ \mathbf{F}\psi \ \mid \ \mathbf{G}\psi \ \mid \ \psi \mathbf{U}\psi \ \mid \ \psi \mathbf{R}\psi \end{split}$$

In definition 2.21, **A** and **E** are *path quantifiers* meaning "for all paths" and "for some paths" respectively; **F**, **G**, **X**, **U**, **R** are temporal operators expressing properties of a single path. Formally, the  $CTL^*$  semantics is defined by Def. 2.24. The "eventually" operator **F** specifies that a property holds at some state of the path. The "always" operator **G** requires that a property holds

at every state of the path. The "next" operator  $\mathbf{X}$  expresses that a property holds in the second state of the path. The "unless" operator  $\mathbf{U}$  holds if there is a state on the path where the second property holds and the first property holds at every state preceding this state. The "release" operator  $\mathbf{R}$  is used to specify that the second property holds in all states along a path up to and including the first state that satisfies the first property. The first property is not required to be eventually satisfied.

Linear Temporal Logic, LTL, is a subset of  $CTL^*$  that consists of formulas having the form  $\mathbf{A}\psi$  where  $\psi$  is a path formula in which the only state subformulas permitted are atomic propositions.

## Definition 2.22. [LTL]

Given a set of atomic prepositions  $\mathcal{P}$ , the logic LTL consists of path formulas of the form defined by the following grammar:

$$\begin{split} \psi ::= p \mid \neg \psi \mid \psi \lor \psi \mid \psi \land \psi \mid \mathbf{F}\psi \mid \mathbf{G}\psi \mid \mathbf{X}\psi \mid \psi \mathbf{U}\psi \mid \psi \mathbf{R}\psi \\ where \ p \in \mathcal{P}. \end{split}$$

In LTL context,  $\Box$  is often used instead of **G** to denote the "always" operator and  $\diamondsuit$  is used instead of **F** to denote the "eventually" operator.

$\mathit{CTL}^\star$  formulas are interpreted over Kripke structures.

#### **Definition 2.23.** [KRIPKE STRUCTURE]

A Kripke structure K is a tuple  $(T, S_0, \mathcal{L})$ , where T is a transition system  $(S, R), S_0$  is a set of initial states,  $\mathcal{L}: S \to 2^{\mathcal{P}}$  is an interpretation function and  $\mathcal{P}$  is a set of atomic propositions.

A sequence in the Kripke structure  $K = (S, R, S_0, \mathcal{L})$  is  $\pi = s_0 s_1 s_2 \dots$ such that  $(s_i, s_{i+1}) \in R$  holds for all  $i \geq 0$ . A path in the Kripke structure  $K = (S, R, S_0, \mathcal{L})$  is an *infinite* sequence. We use  $\pi_{(i)}$  to denote the suffix of  $\pi$  starting at state  $s_i$ ;  $\pi^{(i)}$  is used to denote the prefix of  $\pi$  starting at  $s_0$  and ending at  $s_i$ . In case a state s has no outgoing transitions, we say that there is a *deadlock* in this state. Both paths and finite sequences  $\pi = s_0 s_1 \dots s_k$  ending at a state  $s_k$  that has a deadlock are called *computations* of K. The *length* of  $\pi$  (denoted  $|\pi|$ ) is the number of states on it. The satisfaction of a formula is defined inductively.

#### **Definition 2.24.** $[CTL^* \text{ SEMANTICS}]/42]$

Let  $K = (S, R, S_0, \mathcal{L})$  be a Kripke structure over  $\mathcal{P}$ . Let  $p \in \mathcal{P}$ ,  $\phi$ ,  $\phi_1$ ,  $\phi_2$  be state formulas and  $\psi$ ,  $\psi_1$ ,  $\psi_2$  be path formulas,  $s \in S$  and  $\pi$  be a path in K. The relation  $\models$  is defined inductively as follows:

- $-K, s \models p \text{ iff } p \in \mathcal{L}(s);$

- $-K, s \models \neg \phi \text{ iff } K, s \not\models \phi;$

- $-K, s \models \phi_1 \lor \phi_2 \text{ iff } K, s \models \phi_1 \text{ or } K, s \models \phi_2;$

- $-K, s \models \phi_1 \land \phi_2 \text{ iff } K, s \models \phi_1 \text{ and } K, s \models \phi_2;$

- $-K, s \models \mathbf{E}\psi$  iff there exists a path  $\pi$  starting in s such that  $K, \pi \models \psi$ ;

- $-K, s \models \mathbf{A}\psi$  iff for every path  $\pi$  starting in  $s, K, \pi \models \psi$ ;

- $-K, \pi \models \phi$  iff  $\pi$  starts in s and  $K, s \models \phi$ ;

- $-K, \pi \models \neg \psi \text{ iff } K, \pi \not\models \psi;$

- $K, \pi \models \psi_1 \lor \psi_2 \text{ iff } K, \pi \models \psi_1 \text{ or } K, \pi \models \psi_2;$

- $-K, \pi \models \psi_1 \land \psi_2 \text{ iff } K, \pi \models \psi_1 \text{ and } K, \pi \models \psi_2;$

- $-K, \pi \models \mathbf{X}\psi \text{ iff } K, \pi_{(1)} \models \psi;$

- $-K, \pi \models \mathbf{F}\psi$  iff there exists a  $k \ge 0$  such that  $K, \pi_{(k)} \models \psi$ ;

- $\begin{array}{c} -K, \pi \models \mathbf{G}\psi \text{ iff for all } i \geq 0, K, \pi_{(i)} \models \psi; \\ -K, \pi \models \psi_1 \mathbf{U}\psi_2 \text{ iff there exists a } k \geq 0 \text{ such that } K, \pi_{(k)} \models \psi_2 \text{ and for all } \end{array}$  $\begin{array}{l} 0 \leq j < k, \ K, \pi_{(j)} \models \psi_1; \\ - \ K, \pi \models \psi_1 \mathbf{R} \psi_2 \ \textit{iff for all } k \geq 0, \ \forall i < k \ K, \pi_{(i)} \not\models \psi_1 \ \textit{implies } K, \pi_{(k)} \models \psi_2. \end{array}$

There are several approaches to the interpretation of  $CTL^*$  path formulas. Although in the original definition of  $CTL^{\star}$  in [62] both finite and infinite computations are taken into consideration, definition of  $CTL^{\star}$  in [63] and in [60] revise the original definition by quantifying over paths only. A similar definition is given in [41]. In [61, 39], a transition relation of a Kripke structure is required to be *total* (i.e., every state must have an outgoing transition so that all computations are infinite).

In case only paths are taken in consideration, no properties about finite computations of the system can be expressed. If a Kripke structure contains a deadlock, this will not be caught by checking some  $CTL^*$  formula.

This deficiency is often repaired by assuring that all computations of the system are infinite before checking any other properties. In [47], a Kripke structure is extended by adding an extra state s and a transition leading to s from every state having no outgoing transitions (including s itself). New atomic proposition *is\_in\_s*, which is *true* only in *s*, is added to the set of atomic propositions. The check of deadlocks can be performed by checking  $AG \neg is_in_s$  over system transformed as described above. If this check succeeds, this implies that the original system is deadlock free. Once the system has been checked to be free from deadlocks, the extra transitions and state s can be removed again.

Similar approach is taken in [129]. There, the transition relation of Kripke structure does not have to be total. The authors propose a livelock extension for Kripke structures that is obtained by applying the following transformation: For each state that has no outgoing transitions or occurs in a cycle of states with the same labels, a new outgoing transition is added. The transition leads to a new state s that is labelled by a new proposition that occurs in no other labels on states.

Further in this thesis, we deal with transition systems (LTSs) where the transition relation is *total* due to the fact that a system is *timed* and time can progress even if the system can not do anything useful.

#### Next-free logic

Reactive systems are usually developed by a number of successive steps. At each step, the system is described in more detail and closer to the implementation

level. Refinement allows the replacement of a higher level system specification by a lower, more detailed one. Refinement often changes the granularity of actions, i.e., high-level actions are mapped to multiple low-level actions, and therefore, high-level actions lose their atomicity.

The next operator  $\mathbf{X}$  is closely related to the notion of a next state that can be reached by one step of the system. The  $\mathbf{X}$  operator can be useful to express system properties, but it should be used with caution. The intuitive meaning of the  $\mathbf{X}$  operator is not associated with the granularity of actions that the system can perform. In case the  $\mathbf{X}$  operator is employed to express properties of the system, a change of the granularity can lead to a situation where properties satisfied by a higher level model become *false* for a lower level one.

The necessity of the **X** operator was already questioned in [117]. The main objection against the **X** operator was that it allows the designer to express irrelevant properties of the model. Using the **X** operator one can write a specification of a queue that includes a requirement: "removing an element from the queue should take exactly 17 steps". This property is not meaningful if one gives a high-level specification of a queue. It is a property of an implementation of the "remove" operation, but not a property of the "remove" operation itself. Therefore, Lamport proposed to drop the **X** operator from temporal logics. Further we refer to next-free  $CTL^*$  and to next-free LTL as  $CTL^*-X$  and LTL-X respectively.

The work of Lamport is related to developments in the field of process equivalences, namely to the research on comparative concurrency semantics [71] in the context of process algebras with silent moves [72]. In [73], it is argued that branching bisimulation equivalence is the coarsest equivalence that respects the branching structure of a process with silent moves. In [129], De Nicola and Vaandrager showed that  $CTL^*-X$  induces on LTSs the same identification as branching bisimulation. According to [73], considering  $CTL^*$  would induce an equivalence that is too fine for processes with silent moves. In [47], Dams considers the development from strong bisimulation to branching bisimulation as the parallel of the shift of attention from  $CTL^*$  to  $CTL^*-X$  in specification logics.

Formulas of temporal logic are usually interpreted over Kripke structures; LTSs are mainly used for modelling purposes. In [129], De Nicola and Vaandrager introduced a new kind of structure that can be naturally projected on both LTSs and Kripke structures. The structure is called *doubly labelled transition systems*.

#### **Definition 2.25.** [DOUBLY LABELLED TRANSITION SYSTEMS] [129]

A doubly labelled transition system (L<sup>2</sup>TS) is a structure  $\mathcal{D} = (S, Lab, \rightarrow, s_0, \mathcal{L})$ , where  $(S, Lab, \rightarrow, s_0)$  is an LTS and  $\mathcal{L} \colon S \to 2^{\mathcal{P}}$  is a labelling function that associates a set of atomic propositions to each state. With LTS( $\mathcal{D}$ ) we denote the substructure  $(S, Lab, \rightarrow, s_0)$  and  $KS(\mathcal{D})$  denotes the substructure  $(S, R, s_0, \mathcal{L})$  such that  $\forall s, s' \in S, (s, s') \in R$  iff  $s \to_{\lambda} s' \in \rightarrow$  for some  $\lambda \in Lab$ .

Equivalences defined on LTSs or Kripke structures can be naturally lifted to  $L^2TSs$  by ignoring state or transition labels respectively. The notions of a path and a computation in an  $L^2TS$  are defined analogously to the notion of a path and a computation in a Kripke structure. The notion of a trace in an  $L^2TS$  is defined analogously to the notion of a trace in an LTS. For an  $L^2TS$  $\mathcal{D}$  and a formula  $\varphi$  of LTL, we write  $\mathcal{D} \models \varphi$  iff  $KS(\mathcal{D}) \models \varphi$ . Further we give a definition of path equivalence up to stuttering and an overview of results from [135, 136] relating path equivalence up to stuttering with LTL-X.

**Definition 2.26.** [STUTTERING-FREE PROJECTION] [135, 136] Let  $\pi = s_0 s_1 s_2 \dots$  be a sequence in L<sup>2</sup>TS  $\mathcal{D} = (S, \rightarrow, S_0, \mathcal{L})$ . The stuttering-free projection  $Pr(\pi)$  of  $\pi$  is defined coinductively as follows:

$$- Pr(s_0s_1s_2\ldots) = s_0 \text{ if } \forall i > 0 \text{ (or } \forall 0 < i \le |\pi|), \ \mathcal{L}(s_i) = \mathcal{L}(s_0);$$

$$- Pr(s_0\ldots s_ks_{k+1}\ldots) = Pr(s_0\ldots s_k)Pr(s_{k+1}\ldots) \text{ if } \mathcal{L}(s_k) \neq \mathcal{L}(s_{k+1}).$$

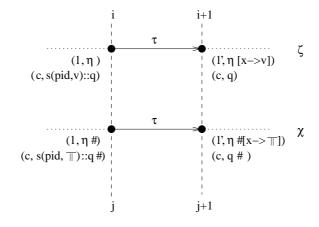

**Definition 2.27.** [EQUIVALENCE UP TO STUTTERING] [135, 136] Let  $\pi$  and  $\rho$  be paths in  $L^2 TSs \mathcal{D}_1 = (S_1, \rightarrow^1, s_0^1, \mathcal{L}_1)$  and  $\mathcal{D}_2 = (S_2, \rightarrow^2, s_0^2, \mathcal{L}_2)$ respectively, where the range of labelling functions  $\mathcal{L}_1$  and  $\mathcal{L}_2$  is  $2^{\mathcal{P}}$ . We say that  $\pi$  and  $\rho$  are equivalent up to stuttering, written as  $\pi \equiv_{st} \rho$ , iff  $\mathcal{L}_1(Pr(\pi)(i)) =$  $\mathcal{L}_2(Pr(\rho)(i))$  for all  $i \geq 0$  (or  $\forall 0 < i \leq |Pr(\pi)|$  and  $|Pr(\rho)| = |Pr(\pi)|$ ), i.e., the interpretations of the stuttering-free projections of  $\pi$  and  $\rho$  are the same.

#### Definition 2.28. [PATH EQUIVALENCE UP TO STUTTERING] [135, 136]

Let  $\mathcal{D}_1 = (S_1, \rightarrow^1, s_0^1, \mathcal{L}_1)$  and  $\mathcal{D}_2 = (S_2, \rightarrow^2, s_0^2, \mathcal{L}_2)$  be two L<sup>2</sup>TSs where the range of labelling functions  $\mathcal{L}_1$  and  $\mathcal{L}_2$  is  $2^{\mathcal{P}}$ .

We write  $\mathcal{D}_1 \preceq_{st} \mathcal{D}_2$  iff for each path  $\pi$  in  $\mathcal{D}_1$  there is a path  $\rho$  in  $\mathcal{D}_2$  such that  $\pi \equiv_{st} \rho$ .

$\mathcal{D}_1$  and  $\mathcal{D}_2$  are path equivalent up to stuttering, written as  $\mathcal{D}_1 \equiv_{st} \mathcal{D}_2$ , iff  $\mathcal{D}_1 \preceq_{st} \mathcal{D}_2$  and  $\mathcal{D}_2 \preceq_{st} \mathcal{D}_1$ .

#### **Theorem 2.2.** [135]

Let  $\mathcal{D}_1$  and  $\mathcal{D}_2$  be two L<sup>2</sup>TSs, where the range of labelling functions  $\mathcal{L}_1$  and  $\mathcal{L}_2$  is  $2^{\mathcal{P}}$ .

Let  $\mathcal{D}_1 \preceq_{st} \mathcal{D}_2$ . Then  $\mathcal{D}_1 \models \varphi$  if  $\mathcal{D}_2 \models \varphi$  for any LTL-X formula  $\varphi$  over  $\mathcal{P}$ . Let  $\mathcal{D}_1 \equiv_{st} \mathcal{D}_2$ . Then  $\mathcal{D}_1 \models \varphi$  iff  $\mathcal{D}_2 \models \varphi$  for any LTL-X formula  $\varphi$  over  $\mathcal{P}$ .

#### Modal $\mu$ -calculus

**Definition 2.29.** [MODAL  $\mu$ -CALCULUS,  $L_{\mu}$ ] [112, 51]

Let Var be a set of propositional variables. Let  $\mathcal{P}$  be the set of atomic propositions. Moreover, let  $p \in \mathcal{P}$ ,  $x \in Var$ ,  $\varphi \in L_{\mu}$ . The logic  $L_{\mu}$  is the set of formulas that is defined by the following grammar:

$\varphi ::= p \mid \neg p \mid x \mid \varphi \lor \varphi \mid \varphi \land \varphi \mid \Box \varphi \mid \Diamond \varphi \mid \mu x.\varphi \mid \nu x.\varphi$

Formula  $\Box \varphi$  expresses that  $\varphi$  is true for every immediate successor, while  $\diamond \varphi$  expresses that there is at least one successor for which  $\varphi$  is true.  $\mu x.\varphi$  and  $\nu x.\varphi$  are the least and greatest fixpoint operators respectively. Their meaning is the smallest (respectively, greatest) set x of states in which  $\varphi$  holds.

Here we consider only formulas in *positive normal form*, where all negations occurring in the formula are applied to atomic propositions and no variable is quantified twice [112]. The *universal* and *existential* fragments  $\Box L_{\mu}$  and  $\diamond L_{\mu}$  are subsets of  $L_{\mu}$  in which the only allowed next-state operators are  $\Box$  and  $\diamond$  respectively.  $L_{\mu}^+$  denotes the *positive fragment* of  $L_{\mu}$ , where the use of negation is forbidden even on the atomic propositions.

$L_{\mu}$  formulas are interpreted over a transition system (see Def. 2.5) with an interpretation function associated to the transition system. Intuitively,  $\mathcal{I}(p)$  is the set of states where p holds. A function  $\|\cdot\|$  interprets an  $L_{\mu}$  formula over a given transition system with an interpretation function.

## **Definition 2.30.** $[L_{\mu} \text{ SEMANTICS}]$ [51]

Let T = (S, R) be a transition system and  $\mathcal{I}: \mathcal{P} \to 2^S$  be an interpretation function. The function  $\|\cdot\|: (L_{\mu} \times (Var \to 2^S)) \to 2^S$  is defined as follows. Let  $p \in \mathcal{P}, x \in Var, \varphi, \varphi_1, \varphi_2 \in L_{\mu}$  and  $e: Var \to 2^S$ .

$$\begin{split} \|p\|_{e} &= \mathcal{I}(p) \\ \|\neg p\|_{e} &= \overline{\mathcal{I}}(p) \\ \|x\|_{e} &= e(x) \\ \|\varphi_{1} \lor \varphi_{2}\|_{e} &= \|\varphi_{1}\|_{e} \ \cup \|\varphi_{2}\|_{e} \\ \|\varphi_{1} \land \varphi_{2}\|_{e} &= \|\varphi_{1}\|_{e} \ \cap \|\varphi_{2}\|_{e} \\ \|\Box \varphi\|_{e} &= \{s \in S \mid \forall \ s' \in S \ sRs' \Rightarrow s' \in \|\varphi\|_{e}\} \\ \|\diamond \varphi\|_{e} &= \{s \in S \mid \exists \ s' \in S \ sRs' \land s' \in \|\varphi\|_{e}\} \\ \|\varphi \varphi\|_{e} &= \{s \in S \mid \exists \ s' \in S \ sRs' \land s' \in \|\varphi\|_{e}\} \\ \|\mu x.\varphi\|_{e} &= \bigcap\{S' \subseteq S \mid \|\varphi\|_{e[x \mapsto S']} \subseteq S'\} \\ \|\nu x.\varphi\|_{e} &= \bigcup\{S' \subseteq S \mid \ S' \subseteq \|\varphi\|_{e[x \mapsto S']}\} \end{split}$$

$e_{[x\mapsto S']}$  is the same as e except that x is mapped to S'. We write  $s \models \varphi$  for  $s \in ||\varphi||$ . For a set of states S', the notation  $S' \models \varphi$  abbreviates  $\forall s \in S', s \models \varphi$ . When there may be confusion between different systems and interpretation functions we write  $T, (I), s \models \varphi$  to denote that  $s \models \varphi$  in T with interpretation function  $\mathcal{I}$ .

The existential and universal fragments of  $\mu$ -calculus subsume the existential and universal fragments of  $CTL^*$  ([87]).

# 2.4 Model Checking and Automata Theory

Model checking [38, 120, 165, 35, 42] is a formal technique for verifying finitestate systems with respect to their specification. The properties of a system are expressed as formulas in some temporal logic [137, 60]. A model checker either confirms that the system satisfies the properties or reports that they are violated. In case a property gets violated, the model checker produces a counter-example that is a system run that violates the property.

Model checking comes in two fashions: symbolic model checking as e.g. in NuSMV [37] and COSPAN [83], where Ordered Binary Decision Diagrams [32] are used to represent states of the system symbolically, and explicit state model checking as in *Spin* [93] and CADP [65], where the states of the system are explicitly enumerated. Here we give an overview of the explicit-state automatabased approach to model checking [165, 93]. In this approach, both the system and the negation of a property are turned into a finite automaton on infinite words [158]. The verification consists in checking whether the language recognized by the synchronous product of the above automata is empty.

Further we focus on finite automata over infinite words. The simplest automata over infinite words are Büchi automata [34].

#### Definition 2.31. [BÜCHI AUTOMATON] [127]

A Büchi automaton  $B = (Q, I, \delta, F)$  over an alphabet  $\Sigma$  is given by a finite set Q of states, a non-empty set  $I \subseteq Q$  of initial states, a transition relation  $\delta \subseteq Q \times \Sigma \times Q$  and a set  $F \subseteq Q$  of accepting states.

A run of B over an  $\omega$ -word  $w = a_0 a_1 \dots \in \Sigma^{\omega}$  is an infinite sequence  $\rho = q_0 q_1 q_2 \dots$  such that  $q_0 \in I$  and  $(q_i, a_i, q_{i+1}) \in \delta$  holds for all  $i \in \mathbb{N}$ . The run  $\rho$  is accepting iff there exists some  $q \in F$  such that  $q_i = q$  holds for infinitely many  $i \in \mathbb{N}$ .

A language  $L(B) \subseteq \Sigma^{\omega}$  is the set of  $\omega$ -words for which there exists some accepting run  $\rho$  of B. A language  $L \subseteq \Sigma^{\omega}$  is called  $\omega$ -regular iff L = L(B) for some Büchi automaton B.

Finite automata can be used to model concurrent and interactive systems. A Kripke structure directly corresponds to a finite automaton over infinite words where all states are accepting. Specifically, a Kripke structure  $K = (S, R, s_0, \mathcal{L})$  where  $\mathcal{L} \colon S \to 2^{\mathcal{P}}$  can be seen as an automaton  $A = (S, S_0, \delta, S)$  over  $2^{\mathcal{P}}$ , where  $(s, a, s') \in \delta$  for  $s, s' \in S$  iff  $(s, s') \in R$  and a = L(s) [168]. (Note that in the general case there is a set of initial states, but for model checking we only require a single initial state.) The specification can be transformed into an automaton B, over the same alphabet. The system A satisfies the specification B when  $L(A) \subseteq L(B)$ . That can be rewritten as  $L(A) \cap \overline{L(B)} = \emptyset$ , i.e., there is no behaviour of A that is disallowed by B. If the intersection is not empty, any behaviour in it corresponds to a counter-example.

Büchi automata are closed under intersection and complement [34]. This means that there exists an automaton that accepts exactly the intersection of the languages of two automata and an automaton that recognizes exactly the complement of the language of a given automaton. In some implementations such as *Spin* [93], the automaton for the complement of the specification is used instead of the automaton for the specification. In this case, not the good behaviour is specified, but the bad behaviour.

We show how to construct an automaton that recognises the intersection of two languages accepted by a pair of Büchi automata. Since all the states of the automaton for the modelled system are accepting, we give the definition of the product for the case when all the states of one of the automata are accepting.

#### **Definition 2.32.** [SYNCHRONOUS PRODUCT] [42]

Let  $B_1 = (Q_1, \ \delta_1, \ Q_1^0, \ Q_1)$  and  $B_2 = (Q_2, \ \delta_2, \ Q_2^0, \ F_2)$  be Büchi automata over  $\Sigma$ . The synchronous product of  $B_1$  and  $B_2$  is the automaton B over  $\Sigma$ given by  $(Q_1 \times Q_2, \ \delta, \ Q_1^0 \times Q_2^0, \ Q_1 \times F_2)$  such that  $((q_1, q_2), a, (q'_1, q'_2)) \in \delta$  iff  $(q_1, a, q'_1) \in \delta_1$  and  $(q_2, a, q'_2) \in \delta_2$ .

It is straightforward to show that the synchronous product of automata  $B_1$  and  $B_2$  accepts  $L(B_1) \bigcap L(B_2)$ .