## FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# **UWB Using Programmable Logic**

Tiago dos Santos Maia Costa

FOR JURY EVALUATION

Mestrado Integrado em Engenharia Eletrotécnica e de Computadores

Supervisor: Professor Sérgio Reis Cunha

Second Supervisor: Professor José Carlos dos Santos Alves

## Resumo

A tecnologia de Banda Ultra-Larga (Ultra-Wideband, ou UWB em inglês) pode servir um grande número de aplicações tais como comunicação rádio bidirecional, Radar, medições de tempos de propagação e distâncias de linhas de transmissão, aplicações biomédicas e captura de imagens através de objetos ou ainda sistemas de radar e anti colisão para automóveis. As aplicações UWB beneficiam de transmissões de baixa potência e são praticamente indetetáveis para os recetores tradicionais de banda estreita, uma vez que os impulsos têm uma Densidade Espectral que cobre uma gama bastante larga de frequências, que consequentemente é confundível com o típico ruído térmico nos recetores comuns. Este trabalho vai demonstrar uma arquitetura para um transmissor e recetor UWB baseado em impulsos, ou IR-UWB (Impulse-Radio Ultra-Wideband), que dispõe da capacidade de realizar medições de tempos de propagação em linhas de transmissão ou oferecer comunicação bidirecional. Também será demonstrado como a arquitetura IR-UWB proposta foi implementada e testada em FPGAs, com o intuito de apresentar duas provas-de-conceito distintas: medir o tempo de propagação de uma linha de transmissão e estimar o seu comprimento, e ainda oferecer a capacidade de comunicação entre dois sistemas com esta arquitetura.

**Palavras-chave**: IR-UWB, Banda Ultra-Larga, Lógica Programável, FPGA, Comunicação UWB, Medição Velocidade Propagação Electromagnética

# **Abstract**

UWB technology potential applications include high data-rate Radio Transceivers, Radar and Ranging measurements devices, Biomedical and through-wall Imaging or Automotive Collision Avoidance Radar systems. UWB applications benefit from a low-power and virtually undetectable communication channel to Narrowband receivers as UWB pulses have a Power Spectral Density which covers a very large range of frequencies and consequently falls below typical thermal noise levels. This work will demonstrate a simple receiver and transmitter architecture to implement an Impulse-Radio Ultra-Wideband (IR-UWB) communication system on a Programmable Logic Device (FPGA), that can perform ranging measurements and also operate as a transceiver. It will also de demonstrated how this IR-UWB architecture was implemented and tested in FPGA hardware for two proof-of-concept scenarios: measurement of the propagation delay of a transmission line and line distance estimation, and also board-to-board transceiver operation.

**Keywords**: IR-UWB, Ultra Wide-Band, Programmable Logic, FPGA, UWB Transceiver, UWB Ranging measurements

# Acknowledgements

I would like to personally thank everyone hereby mentioned for their continued support over the development of this work:

Supervisor Prof. Sérgio Reis Cunha, for suggesting this dissertation work and always sharing ingenious ideas, solutions and guidance for surpassing many design challenges as the work progressed.

Second supervisor Prof. José Carlos Alves, from who I have learned Verilog HDL coding and FPGA development constraints in his comprehensive programmable logic course.

My parents, for always being loving and supportive of my personal academic endeavours and continuously showing deep comprehension and compassion despite all circumstances and mishaps and never, ever questioning if all would be worth it in the end. For providing me with all the resources and opportunities from an early age, and many times depriving themselves of having a more comfortable life solely for the purpose of always putting myself first and investing in my education. You have always inspired me to pursue my passion for electronics that latter evolved into my most important life goal, an engineering degree in that field.

Diana, my soul-mate, for all the patience, care, affection, support and for continuously making me become a better person.

My entire family, and my auntie Irene in special, who always believed in my ability to pursue an higher education degree and continuously supported the pursuit of my academic goals.

To all, I would like to express my profound gratitude and consideration for supporting the development of my academic pathway, by making this dissertation possible and by inspiring me to become the person that I am today. Against unfavourable odds and a few setbacks, together we have overcome them all and proved that not only it was all worth it, but also that adversity only becomes defeat when one stops trying. This achievement is as much as yours as it is mine. Thank You.

Tiago dos Santos Maia Costa

"Don't turn it on, take it apart!"

David L. Jones - EEVBLOG.COM

# **Contents**

| 1 | Intr | oduction                                                               | 1          |

|---|------|------------------------------------------------------------------------|------------|

|   | 1.1  | Objectives, Motivation & Approach                                      | 3          |

|   | 1.2  | Document Structure                                                     | 4          |

|   | 1.3  | Website & Code Repository                                              | 4          |

| 2 | The  | ory & Literature Review                                                | 5          |

|   | 2.1  | UWB definition                                                         | 6          |

|   | 2.2  | Single-Band or Impulse-based (IR-UWB)                                  | 7          |

|   |      | 2.2.1 Modulation Schemes                                               | 8          |

|   |      | 2.2.2 Medium Access Control                                            | 10         |

|   |      | 2.2.3 CTBV Signal Processing & DS Detection                            | 15         |

|   | 2.3  | Multi-Band UWB                                                         | 17         |

|   | 2.4  | IR-UWB Applications                                                    | 19         |

|   |      | 2.4.1 Short-Range Communications                                       | 19         |

|   |      | 2.4.2 Short-Range Radar, Ranging Measurements and Indoor Positioning 1 | 19         |

|   |      |                                                                        | 20         |

|   |      | 2.4.4 Biomedical                                                       | 20         |

|   |      | 2.4.5 Automotive Radar and Collision Avoidance Systems                 | 21         |

|   |      | 2.4.6 Commercially available solutions                                 | 21         |

|   | 2.5  | FPGA implementations of UWB systems                                    | 21         |

|   | 2.6  | Conclusions                                                            | 22         |

| 3 | Syst | em Architecture                                                        | 23         |

|   | 3.1  | Design Challenges & Decisions                                          | 24         |

|   | 3.2  | System Components                                                      | 25         |

|   |      | 3.2.1 Transmitter Module Architecture                                  | 27         |

|   |      | 3.2.2 Receiver Module Architecture                                     | 30         |

|   |      | 3.2.3 Delay Buffer Architecture                                        | 32         |

|   |      | 3.2.4 Control Logic: Finite State Machines                             | 33         |

|   |      | 3.2.5 UART Interface                                                   | 34         |

|   | 3.3  |                                                                        | 34         |

|   |      | 3.3.1 Ranging Configuration                                            | 35         |

|   |      | 3.3.2 Transceiver Configuration                                        | 39         |

|   | 3.4  |                                                                        | <b>4</b> C |

| 4 | Syst | em Implementation on Programmable Logic Hardware                       | 13         |

|   | 4.1  | Hardware Selection                                                     | 14         |

|   | 4.2  |                                                                        | 17         |

X CONTENTS

| Re | feren      | cos                                                          | 103      |

|----|------------|--------------------------------------------------------------|----------|

| D  | RTL        | Simulation Waveforms                                         | 99       |

|    |            | C.2.4 Delay buller chain of K delay elements                 | 9/       |

|    |            | C.2.3 XOR module                                             | 96<br>97 |

|    |            | C.2.2 RX module                                              | 95       |

|    |            | C.2.1 TX module                                              | 93       |

|    | C.2        | Verilog HDL Source-Code                                      | 93       |

|    | C.1        | Matlab scripts                                               | 93       |

| C  | Sour       | rce-Code                                                     | 93       |

|    | B.2        | Set of Kasami codes                                          | 91       |

|    | B.1        | Set of Gold codes                                            | 91       |

| B  |            | l & Kasami codes                                             | 91       |

|    |            |                                                              |          |

|    |            | A.2.2 Waveforms of Payload Transmissions                     | 87       |

|    |            | A.2.1 Transceiver: Data Integrity vs. Hardware Configuration | 87       |

|    | A.2        | Transceiver Proof-of-Concept                                 | 87       |

|    |            | A.1.2 Waveforms of Ranging Measurements                      | 77       |

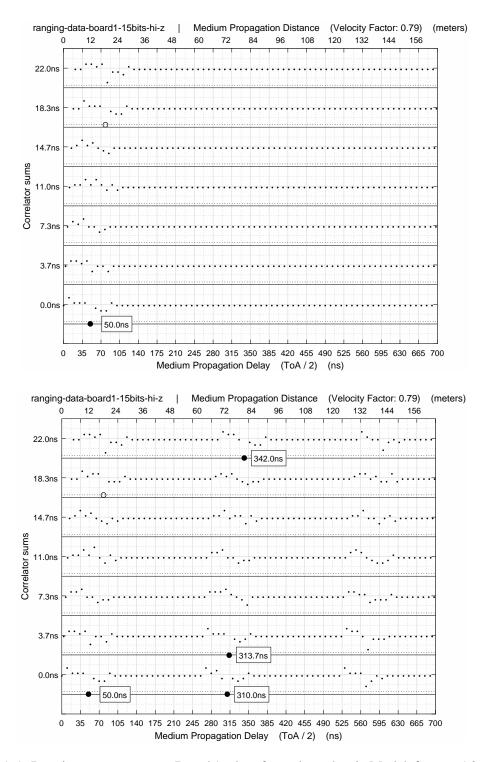

|    | 1          | A.1.1 Ranging Measurements with Matlab                       | 77       |

| 4. |            | Ranging Proof-of-Concept                                     | 77       |

| A  | Com        | plement to Tests & Results' Chapter                          | 77       |

|    | 6.2        | Future Work                                                  | 74       |

|    | 6.1        | Summary of the Work Done                                     | 74       |

| 6  |            | l Remarks & Future Work                                      | 73       |

| _  | г.         |                                                              |          |

|    | 5.4        | Conclusions                                                  | 70       |

|    |            | 5.3.2 Transceiver configuration                              | 69       |

|    |            | 5.3.1 Ranging configuration                                  | 68       |

|    | 5.3        | Summary of System Specifications                             | 67       |

|    |            | 5.2.2 Transceiver Configuration                              | 65       |

|    | <i>ع.د</i> | 5.2.1 Ranging Configuration                                  | 63       |

|    | 5.2        | Proof-Of-Concept Demonstrations                              | 62       |

|    |            | 5.1.1 Ranging Configuration                                  | 61       |

|    | 5.1        | Testing Procedures                                           | 60<br>60 |

| 5  |            | S & Results Tasting Procedures                               |          |

| _  | Tark       | 2 & Doculto                                                  | 59       |

|    | 4.7        | Conclusions                                                  | 57       |

|    |            | 4.6.2 Transceiver Configuration                              | 56       |

|    |            | 4.6.1 Ranging Configuration                                  | 55       |

|    | 4.6        | Hardware Performance Specifications                          | 55       |

|    | 4.5        | Hardware Configuration                                       | 52       |

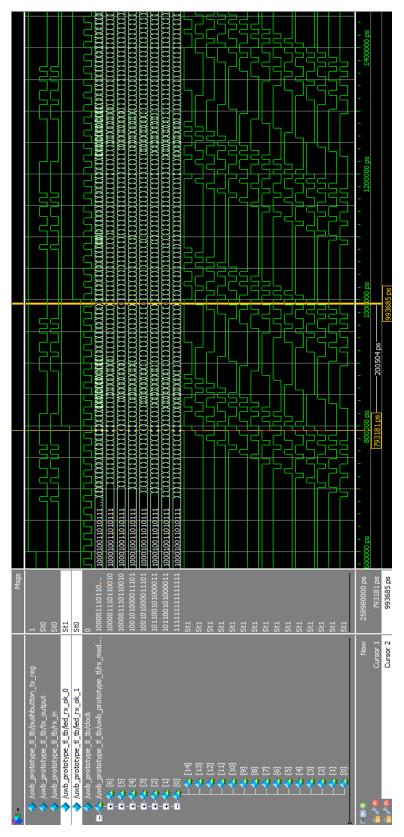

|    |            | 4.4.2 Transceiver Configuration                              | 51       |

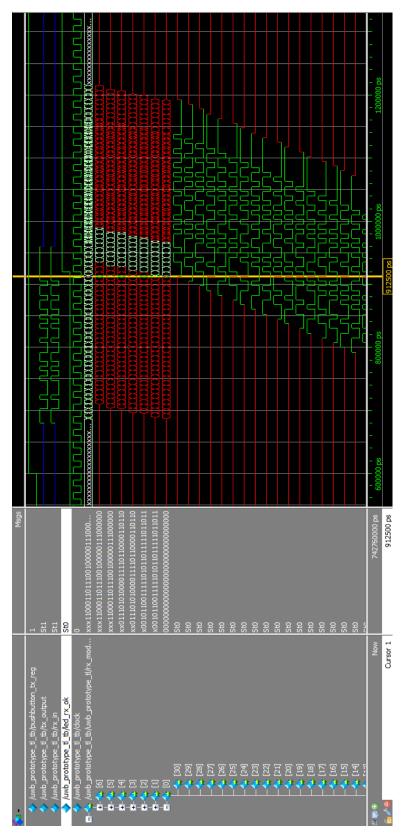

|    |            | 4.4.1 Ranging Configuration                                  | 51       |

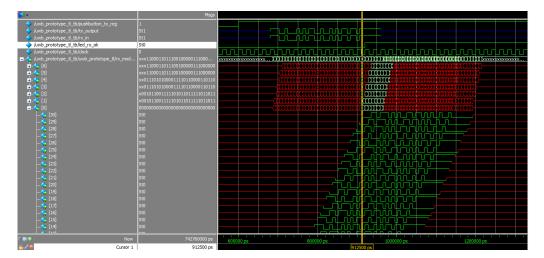

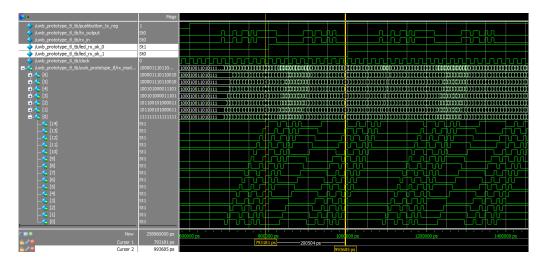

|    | 4.4        | RTL Simulation Results                                       | 50       |

|    | 4.3        | HDL Development                                              | 48       |

# **List of Figures**

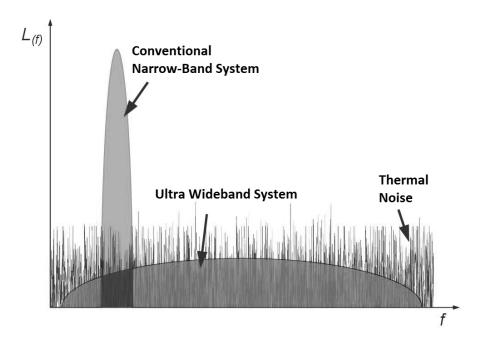

| 1.1                                           | UWB vs. Narrowband relative signal levels over a frequency spectrum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2                                                                    |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

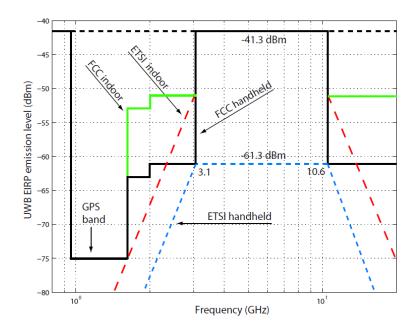

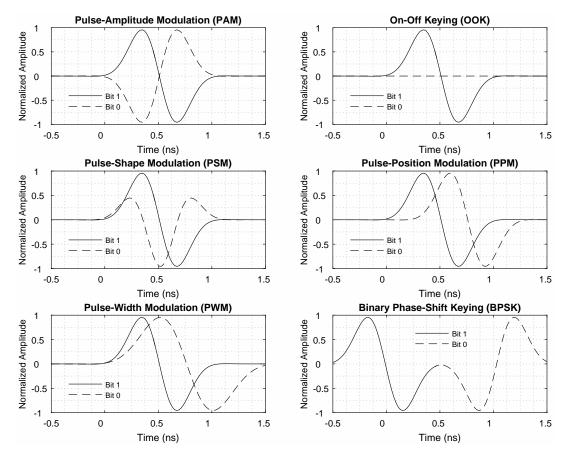

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5               | UWB power limitations regarding transmission regulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10<br>15<br>18<br>21                                                 |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7 | Functional Block Diagram of the TX Module Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26<br>28<br>31<br>33<br>36<br>39<br>41                               |

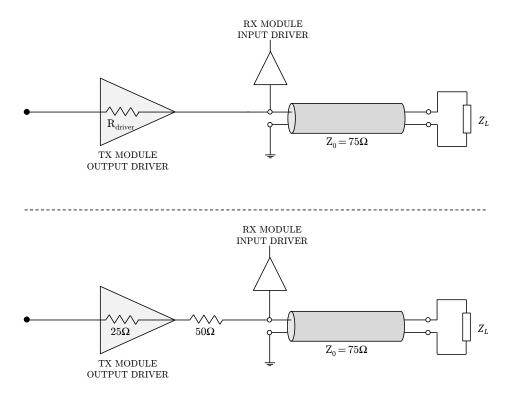

| 4.1<br>4.2<br>4.3<br>4.4                      | RTL simulation waveforms of the Ranging configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 46<br>52<br>53<br>55                                                 |

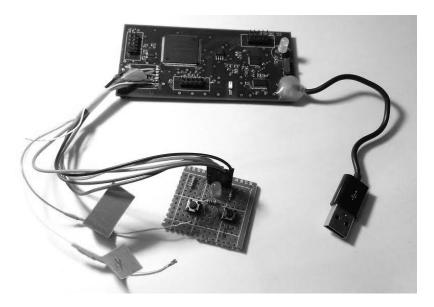

| 5.1                                           | CycloneII-based FPGA board: proof-of-concept testing scenario                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63                                                                   |

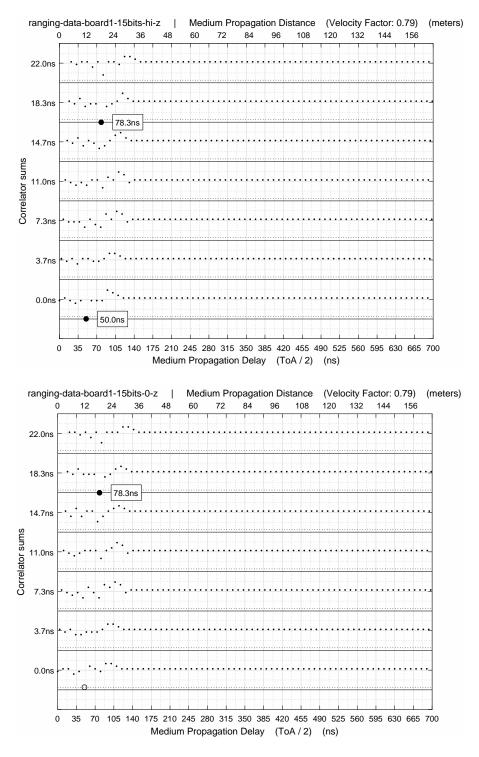

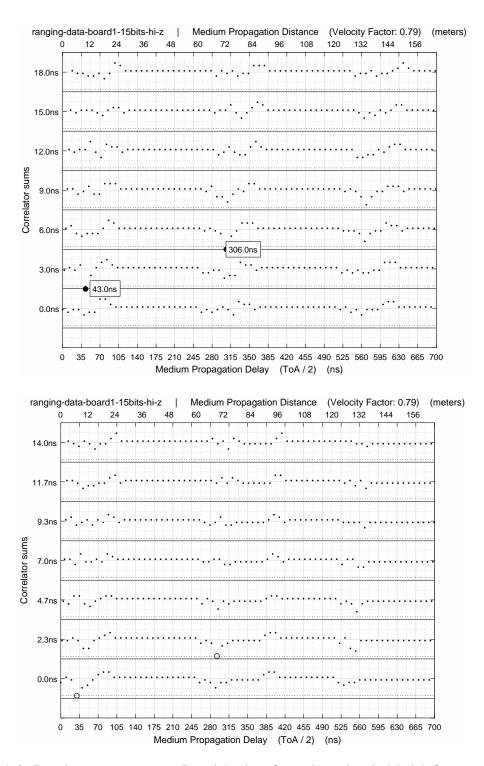

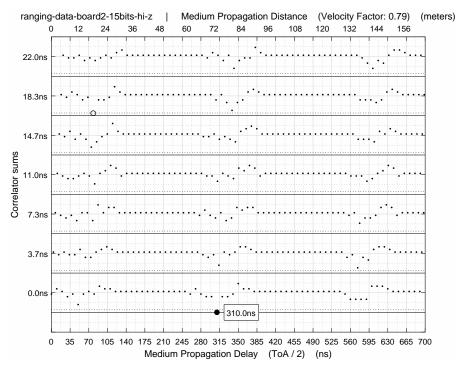

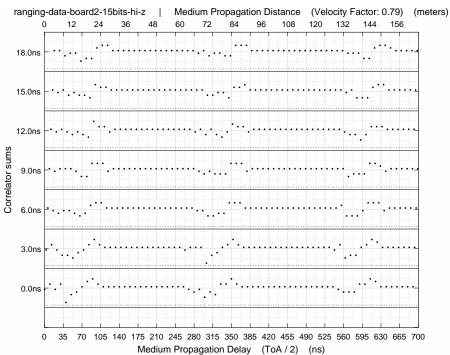

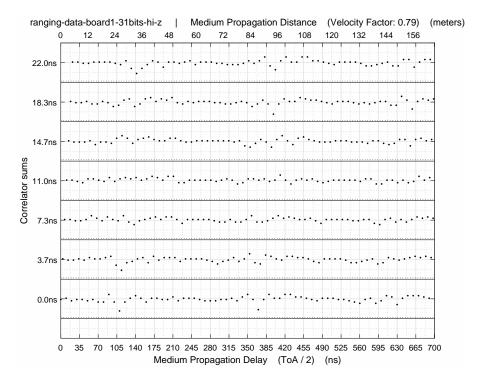

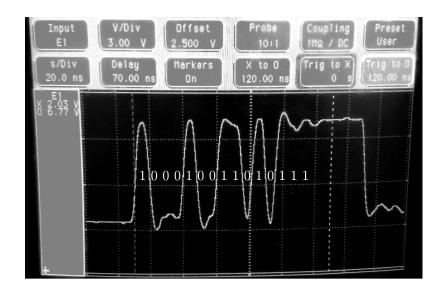

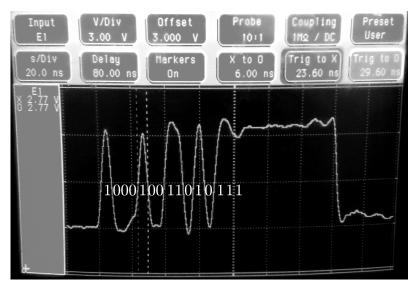

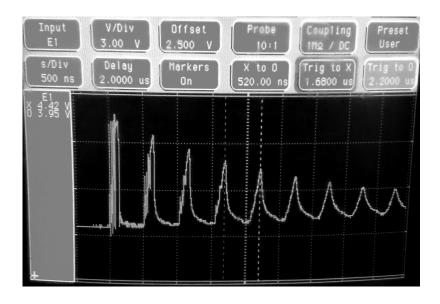

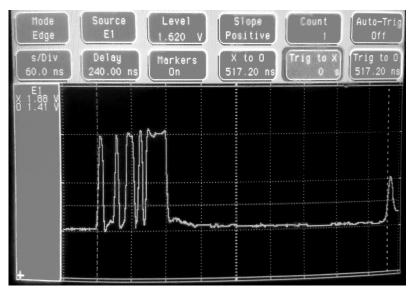

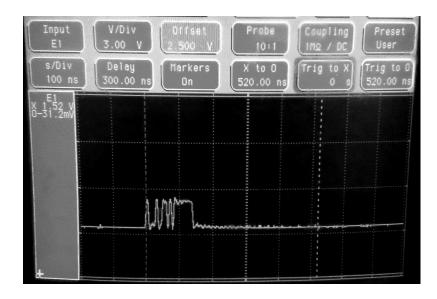

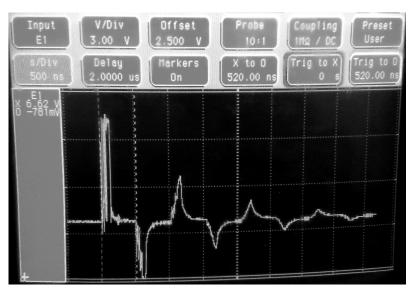

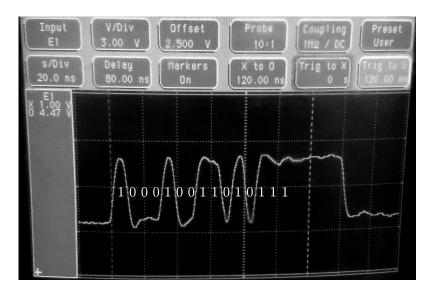

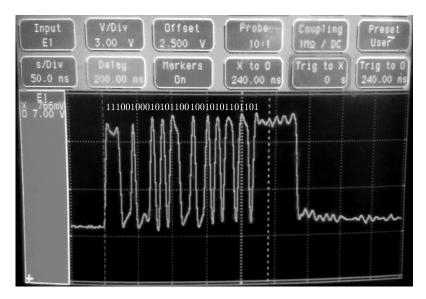

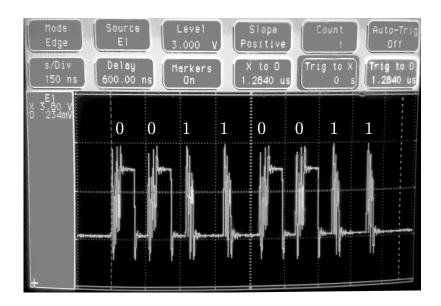

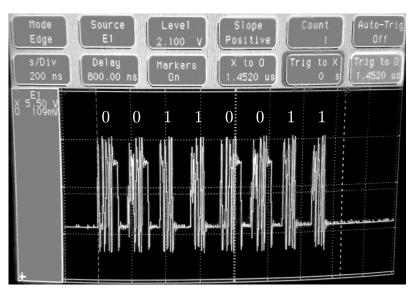

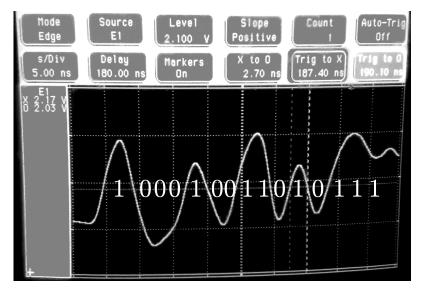

| A.11<br>A.12                                  | Ranging measurements: Board 1, plot of correlator data $(K = 16, 0-Z) \dots$ Ranging measurements: Board 1, plot of correlator data $(K = 12 8, Hi-Z) \dots$ Ranging measurements: Board 2, plot of correlator data $(K = 16 12, Hi-Z) \dots$ Ranging measurements: Board 1, plot of correlator data $(K = 16, Hi-Z, N = 31) \dots$ Ranging measurements: Board 1, waveforms of pulses $< 8 \text{ ns } (K = 16, N = 15) \dots$ Ranging measurements: Board 1, reflections of pulses $< 8 \text{ ns } (K = 16, N = 15) \dots$ Ranging measurements: Board 1, attenuation of pulses $< 8 \text{ ns } (K = 16, N = 15) \dots$ Ranging measurements: Board 2, waveform of pulses $< 8 \text{ ns } (K = 16, N = 15) \dots$ Ranging measurements: Board 1, waveform of pulses $< 8 \text{ ns } (K = 16, N = 15) \dots$ Transceiver measurements: Board 2, waveforms of pulses $< 8 \text{ ns } (K = 4 12, N = 15) \dots$ Transceiver measurements: Board 2, waveform of the shortest pulse $(K = 4, N = 15) \dots$ | 78<br>79<br>80<br>81<br>82<br>83<br>84<br>85<br>86<br>86<br>89<br>90 |

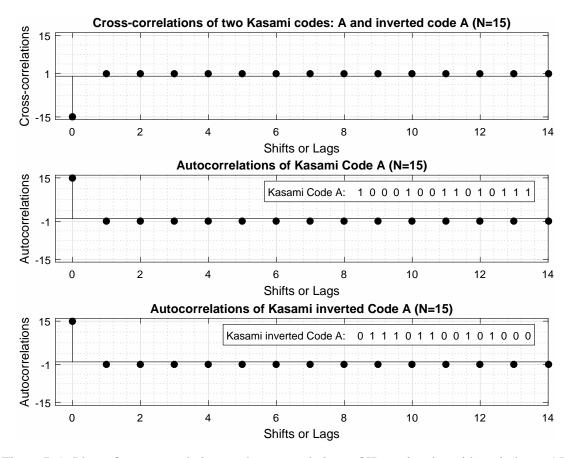

| B.1                                           | Plots of cross-correlations and autocorrelations of Kasami codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 92                                                                   |

| D.1<br>D.2                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 00                                                                   |

xii LIST OF FIGURES

# **List of Tables**

| 3.1 | XOR truth table         28                                |

|-----|-----------------------------------------------------------|

| 4.1 | EP2C5T144C8N Device Features                              |

| 4.2 | Hardware Parts List                                       |

| 4.3 | EP2C5T144C8N Resource Utilization per Configuration       |

| 4.4 | FPGA Board Performance Specifications                     |

| 5.1 | Board Performance in Ranging Measurements                 |

| 5.2 | Board Performance in Transceiver Operation                |

| 5.3 | Number of K Delay Elements vs. Pulse Length               |

| 5.4 | Ranging: Specifications Overview                          |

| 5.5 | Transceiver: Payload Bitrate Overview                     |

| A.1 | Transceiver Configuration: Payload Timeouts (Lost Frames) |

| A.2 | Transceiver Configuration: Payload Errors (Bad Frames)    |

| A.3 | Transceiver Configuration: Bit Errors ( <i>XOR</i> sums)  |

xiv LIST OF TABLES

# **Abbreviations**

ADC Analogue-to-Digital Converter

AM Amplitude Modulation

ASIC Application-Specific Integrated Circuit

BER Bit Error Rate

BoM Bill of Materials

BPF Band-Pass Filter

BPSK Binary Phase-Shift Keying CDMA Code Division Multiple Access

CMOS Complementary Metal-Oxide-Semiconductor

CPLD Complex Programmable Logic Device

CRC Cyclic Redundancy Check

CRC Cyclic Redundancy Check

CTBV Continuous-Time Binary-Value

DDR Double Data Rate

DPPM Differential Pulse-Position Modulation

DS-CDMA Direct Sequence Code Division Multiple Access

DS-UWB Direct Sequence Ultra-WideBand DSO Digital Storage Oscilloscope

DUT Device Under Test

EIRP Equivalent Isotropically Radiated Power

EMI Electromagnetic Interference

ETSI European Telecommunications Standards Institute

FCC (United States of America) Federal Communications Commission

FM Frequency Modulation

FPGA Field-Programmable Gate Array

FSM Finite-State Machine

HDL Hardware Description Language HDMI High-Definition Multimedia Interface

I/O Input/Output IC Integrated Circuit

IDE Integrated Development Environment

IoT Internet of Things

IP Intellectual Property

IR-UWB Impulse-Radio Ultra-WideBand ISI Inter-symbol Interference

ITU-R International Telecommunication Union Radiocommunication Sector

LDO Low-Dropout Regulator LED Light Emitting Diode

LFSR Linear-Feedback Shift-Register

xvi ABBREVIATIONS

LNA Low-Noise Amplifier

LSB Least Significant Bit

LUT Look Up Table

LVDS Low-voltage Differential Signalling

MB-OFDM Multi-Band Orthogonal Frequency-Division Multiplexing

MEMS MicroElectroMechanical Systems

MSB Most Significant Bit

M-UWB Multi-carrier Ultra-WideBand

OOK On-Off Keying

OPM Orthogonal Pulse Modulation

OSI model Open Systems Interconnection model

Pulse-Amplitude Modulation **PAM PAN** Personal Area Network Printed Circuit Board PCB Phase-Locked Loop **PLL** PM Phase Modulation PN Pseudorandom Noise Pulse-Shape Modulation **PSM PPM Pulse-Position Modulation** Pulse-Width Modulation **PWM**

RF Radio Frequency

RFID Radio-Frequency IDentification

RTL Register-Transfer Level

RTS/CTS Request to Send / Clear to Send

RTT Round Trip Time

RX Receiver

SAR Synthetic-Aperture Radar

SNR Signal-to-Noise Ratio

SoC System-on-a-Chip

ToA Time of Arrival

ToF Time of Flight

TX Transmitter

UART Universal Asynchronous Receiver/Transmitter

USB Universal Serial Bus

UWB Ultra-WideBand

VF Velocity Factor

VSWR Voltage Standing Wave Ratio

# **Chapter 1**

# Introduction

In the beginnings of wireless communication, during the 19th century, radio was primarily pulse-based and inherently Wideband. Everything changed with the ban on spark-gap based transmitters that caused interference on medium-wave radios and other receivers. Nevertheless, no practical functionality was really lost with the new rules as the channel capacity of those large RF bandwidths was not being harnessed by the spark-based radio devices of that age. In fact, Wideband utilization was more a result of the technological limitations of the Marconi transmitter era than a desired outcome [1]. Later, with the 20th century came the democratisation of radio when Narrowband and tuned radio communications allowed an efficient and well defined utilization of the ever more crowded RF spectrum, as mandated by the governmental regulatory agencies in most regions of the globe.

Only as of 2002 did the U.S. Federal Communications Commission (FCC) approved a rather conservative usage of some parts of the spectrum for Ultra-WideBand (UWB) communications, such as the 3.1 GHz to 10.6 GHz range, with limited Power Spectral Density emission (maximum of  $-41.3 \, \mathrm{dBm/MHz} \, EIRP$  [2], other restrictions apply), believed to not cause interference on conventional Narrowband transmissions in the same frequency band [3], but which limit UWB usage on other than short-range applications. The European Telecommunications Standards Institute (ETSI) approved similar rules for the European region [4].

The advantages of UWB radio have been long known: the ability to propagate signals through obstacles, the centimetre level ranging capability as a result of the nanosecond resolution and the high data-rates and large channel capacities [2]. Yet, due to regulatory limitations, the development and usage of UWB applications were simply out of reach for the masses. Nowadays, after the FCC liberation and following a large period in time of mostly Narrowband radio communications, a significant interest in UWB has emerged and UWB technology is currently being used and researched for a vast number of civilian, industrial and military applications [3]. Such application possibilities include biomedical and non-medical Imaging Devices [6, 7, 8] such as through-wall and ground mapping, short-range high bitrate Radio Transceivers [9, 10], centimetre-precision

2 Introduction

Figure 1.1: UWB vs. Narrowband relative signal levels over a frequency spectrum (Image source: [5]).

Radar Detection & Measurement Systems [11, 12] and Automotive Radar Collision Avoidance implementations [13]. UWB-based communications tend to not interfere with Narrowband or even other UWB communications due to the narrow-pulse high-bandwidth transmissions and its averaging effect on the Power Spectral Density of UWB signals over the RF spectrum. The transmission of symbols by making use of pseudo-random codes further helps to obfuscate these type of signals from traditional Narrowband receivers. Examples include Maximum Length sequences, Gold sequences, Kasami sequences or Barker sequences. Therefore, UWB systems are suitable for military purposes, as the radiated energy spreads over a large bandwidth and the power of the transmissions falls bellow the typical thermal noise floor observed in the environment, making UWB-based radars harder to detect in the field when compared with Narrowband radars. In medical applications, UWB might help eliminate patient exposure to potentially dangerous side-effects associated with diagnostic equipment still relying on ionizing radiation for producing human body imagery[6].

For these and other reasons, UWB is an exciting and promising technology for the 21st century with a large range of applications already under its scope. On the other hand, modern programmable logic has knowingly become ever more powerful and inexpensive as a side effect of the popular Moore's Law. As such, Field-Programmable Gate Arrays (FPGAs) are an attractive development platform for UWB systems due to their reconfigurable and reprogrammable nature. Yet, a purely digital and FPGA-based UWB implementation is still a challenge as of today because of the associated narrow-pulse timing constraints. But performing signal processing in the digital domain is advantageous in order to lower the complexity of RF front-end circuits. Using

appropriate techniques, the processing may take place almost entirely on the digital domain and this work will propose and demonstrate some examples on how to design Impulse-Radio Ultra-WideBand (IR-UWB) systems for FPGAs, which can operate on baseband and do not require complex analogue IF filtering as the signals are sine-wave free as predicted by [2]. Also, more and more academic research is focussing on UWB solutions relying at some point on programmable logic so this appears to be an appropriate direction to take when developing UWB technology. Even though the solutions to be presented in this work might not have immediate commercial outcome in the foreseeable future, in part due to limitations of the low-budget hardware that was used, the design concepts could be further deployed into more capable hardware by the researchers of tomorrow as FPGA hardware gets increasingly better performance and economic viability.

## 1.1 Objectives, Motivation & Approach

The goal of this dissertation work is to design, develop and test an Ultra-WideBand (UWB) system based on programmable logic, in particular, an FPGA. The result will be a short range IR-UWB communications device that can perform ranging measurements and also operate as a transceiver.

From the beginning it was accepted that it would be difficult to offer the same level of high bandwidth and data-rates usually associated with UWB on a newly developed architecture to be applied in low-cost FPGAs instead the typical CMOS Application Specific Integrated Circuits (ASICs). Nevertheless, the main purpose of the work would be satisfied with the delivery of a proof-of-concept design that could demonstrate UWB concepts on FPGA hardware for both intended applications.

#### Motivation

The main motivation for the work was the challenge of developing a lower-cost and non-ASIC alternative to currently existing custom CMOS designs of UWB applications, ideally offering tens of Mbit/s performance for short-range communications, and also ranging measurements in the range of tens of centimetres. This would be made possible by designing an UWB architecture in Hardware Description Language (HDL), both for the receiver and transmitter chains, that would be compatible with common FPGA chips, as opposed to ASIC-based systems witch are typically more expensive to develop and deploy.

#### **Approach**

The solution came to be based on IR-UWB and Continuous-Time Binary-Value (CTBV) signal processing, as described per [14, 15], in which short-duration impulses in the *nanosecond* or *picosecond* range translate into the utilisation of a large portion of radio spectrum. This is a lower data-rate solution but also lower-power and less complex, therefore consuming fewer logic resources, as opposed to Multi-carrier Ultra-WideBand (M-UWB) options such as Multi-Band Orthogonal Frequency-Division Multiplexing (MB-OFDM) implementations.

4 Introduction

Because the work also focused on obtaining data from testing the design on real hardware, one of the main challenges of the project was managing the variability of propagation delays between logic regions and working with the available speed ratings of the programmable gates, limitations even more relevant on low-budget FPGAs which have operational clock speeds in the range of a few hundreds of MHz. In order to meet the required functionalities of the proof-of-concept applications and accomplishing the goals of signal generation, detection and analysis, while pursuing the speeds and bandwidths as per the UWB definition, no further work was done to implement the system in other than wired propagation mediums. The pursue of a wireless UWB application was dropped as it would bring no additional validation to the design concept and could potentially undermine the development of the transceiver and wave reflection detection functionalities, two relevant proof-of-concept demonstrations later described in the following chapters.

#### 1.2 Document Structure

Following this introductory 1<sup>st</sup> chapter, the report contains five additional chapters.

- Chapter 1: Introduction;

- Chapter 2: Theory & Literature Review, presents a Theoretical Background and a Literature Review on current UWB research and its applications;

- Chapter 3: System Architecture, introduces the architecture of the developed system and its possible applications;

- Chapter 4: System Implementation on Programmable Logic Hardware, demonstrates an FPGA implementation for the proof-of-concept demonstrations;

- Chapter 5: Tests & Results, contains relevant specifications of the hardware implementation:

- Chapter 6: Final Remarks & Future Work, summarizes the work done and suggests some potential Future Works to be developed from this dissertation.

## 1.3 Website & Code Repository

All related documentation, including this dissertation report, slide presentation of the project, software code and final results are available at the website http://www.uwb-radio.com for reference.

# **Chapter 2**

# **Theory & Literature Review**

### Introduction

In this chapter it will be established a theoretical framework for understanding the work done and a brief description regarding the current state-of-the-art of different types of UWB applications. The literature review will offer a brief perspective about the current possibilities associated with this technology. Extended details will be given whenever the research subjects can relate significantly with the goals of this implementation, but other works considered less relevant will be only concisely referenced.

Although the goal of the dissertation work is to develop an IR-UWB system based on Continuous-Time Binary-Value (CTBV) signal processing, as described in [14, 15], it is still important to understand what other approaches are currently available that may provide similar functionality. For this literature evaluation, a couple hundred articles and papers mentioning UWB were accessed from the IEEE Xplore<sup>®</sup> Digital Library and other sources. However, only a limited few, which were considered the most relevant to the work, will be referenced in the following sections of this chapter. It's important to also note that the available studies on UWB technology mostly fall under short-range application scenarios. This is usually imposed by regulatory agencies such as the FCC [3] and ETSI [4] whose rules on UWB limit the power of UWB transmissions.

Following this introduction, the information in this chapter is divided into six major sections:

- Section 2.1: UWB definition, defines UWB technology and related concepts, including a comparison between UWB and traditional Narrowband radio;

- Section 2.2: Single-Band or Impulse-based (IR-UWB), introduces IR-UWB and associated modulation schemes, medium access control techniques, signal detection and sequence despreading approaches;

- Section 2.3: Multi-Band UWB, explains the different aspects of Multi-Band UWB, when compared to Single-Band or IR-UWB;

- **Section 2.4: IR-UWB Applications**, focuses on literature mentioning general IR-UWB designs and its applications;

Figure 2.1: UWB power limitations regarding transmission regulations over the authorized frequency bands, as defined by the FCC and ETSI (Image source: [16]).

- Section 2.5: FPGA implementations of UWB systems, introduces examples of UWB implementations with FPGAs;

- **Section 2.6: Conclusions**, draws some conclusions about the state-of-the-art analysis and the potential of future IR-UWB applications in programmable logic.

## 2.1 UWB definition

UWB was initially known as pulse-radio. Currently, the FCC and ITU-R define UWB signals in terms of its bandwidth when transmitted from an UWB antenna. Signals with an absolute bandwidth greater than 500 MHz or which fractional bandwidth ratio is at least 0.20 are considered Ultra-WideBand.[3] The fractional bandwidth of a baseband UWB signal is then defined as the ratio:

Fractional BandWidth:

$$f_{BW} = \frac{2 \cdot (f_H - f_L)}{f_H + f_L}$$

(2.1)

But it can also be defined as the ratio between the signal's bandwidth and its central frequency,  $f_c = (f_H + f_L)/2$ , leading to:

Fractional BandWidth:

$$f_{BW} = \frac{(f_H - f_L)}{f_c}$$

(2.2)

In both equations,  $f_H$  and  $f_L$  are defined as the upper and lower boundaries of the spectrum where the transmitted signal crosses the  $-10 \, dB$  mark in relation to the power of the highest radiated peak  $(0 \, dB)$ .

#### **UWB** vs Narrowband

Conventional and more common Narrowband broadcasts typically transmit information by varying the amplitude (AM), frequency (FM) and/or phase (PM) of a higher frequency carrier-wave, which is modulated based on a lower frequency baseband signal that holds the information to be transmitted. This ensures the signal is mainly concentrated within a narrow bandwidth around a central frequency that is the frequency of the carrier-wave. The modulated carrier-wave is them amplified by a Power Amplifier circuit and continuously fed to an antenna.

UWB differs from Narrowband radio because information is transmitted through narrow pulses within *nanosecond*-range time instants, resulting in a large bandwidth usage that typically exceeds 500 MHz. UWB can be carrier-free or carrier-based and there are different ways of generating UWB signals as per the definition of regulatory agencies: Impulse-Radio Ultra-WideBand (IR-UWB) was the first recognised method but there are others such as Muti-Band Orthogonal Frequency Division Multiplexing (MB-OFDM) and Frequency Modulation Ultra-Wideband (FM-UWB). This work explores a variant of IR-UWB that relies on Continuous-Time Binary-Value (CTBV) signal processing, later described in additional detail.

Due to the nature of how UWB works and considering *EIRP* limits, the pulse generator circuit can be directly coupled to antennas. This eliminates the need of using mixers or Power Amplifiers, therefore limiting the power consumption of the UWB transmitter. Likewise, the UWB receiver circuit can be as simple as an analogue correlator or a 1-bit ADC detector. As FPGA technology advances, FPGAs become an ever more attracting development platform for building UWB embedded pulse generator circuits and detectors without requiring complex external RF circuitry.

As a direct result of Information Theory and the Shannon–Hartley theorem, in which an increase in bandwidth enables higher channel capacity under the same SNR, UWB allows the deployment of high capacity and high bitrate communication systems particularly at relative short distances. This advantage could perhaps meet specific consumer or industrial level requisites regarding Personal Area Networks (PAN) with high bitrate requirements, as well as low-power specifications in distributed networks of sensors for the Internet of Things (IoT) or industrial applications [2].

Channel Capacity:

$$C = B \cdot log_2(1 + SNR)$$

(bit/s) (2.3)

## 2.2 Single-Band or Impulse-based (IR-UWB)

IR-UWB signals can be carrier-free (baseband) or single-carrier and consist of a sequence of short pulses typically under 2 ns. These narrow-width impulses in the time domain take a large frequency spectrum and therefore their equivalent Spectral Power signatures resemble the Power

Spectral Density of thermal noise to more commonly used Narrowband receivers. [3, 17]. Depending on the application and modulation scheme used, the rate of pulse repetition can vary between several orders of magnitude: in UWB data communication streams this rate is higher than what's usually found on UWB radar systems.[17]

#### **Meeting UWB specifications**

In order for a system to meet UWB specifications, referred in 2.1, and be accepted as Ultra-Wide Band, IR-UWB signals can be up-converted from their baseband frequencies up to the fractional bandwidth limit specification, even if the baseband pulses do not comply with the minimum 500 MHz bandwidth specification. Two viable alternatives to generate complying pulses: the *Switch-based* or *Up-conversion methods*, are described in [18].

- Switch-based In the Switch-based solution a UWB transmitter directly switches the pulse

generator oscillator on and off. Because UWB pulses are very narrow in time, this is the

most power efficient approach as the oscillator is only turned on for very short periods in

time.

- **Up-conversion** The Up-conversion method is the most versatile of the two as the baseband signal from the transmitter is up-converted through a mixer to an upper central frequency that meets the fractional bandwidth requirement in cite equation 2.2. The central frequency can be as high as this fractional bandwidth ratio allows as long as the pulses fall within the *EIRP* mask of applicable regulatory limits.

#### 2.2.1 Modulation Schemes

According to [17, 19], predominant modulation schemes for IR-UWB are Pulse-Amplitude Modulation (PAM), On-Off Keying (OOK), Pulse-Shape Modulation (PSM), Pulse-Position Modulation (PPM), Pulse-Width Modulation (PWM), Binary Phase-Shift Keying (BPSK) and others. Although this work is based on OOK modulation, a brief description of other types is given below in order to illustrate the differences between other IR-UWB systems. Each variant has its own advantages in transceiver complexity, multipath interference, crosstalk immunity and spectral efficiency, but its outside the scope of this work to discuss all the associated pros and cons. It shall also be noted that typical IR-UWB transmissions are made of n-derivative Gaussian pulses which equations are 2.4 and 2.5 as per [20]. These pulses are modulated accordingly to the chosen scheme as illustrated in Figure 2.2.

#### • Pulse-Amplitude Modulation

In binary PAM, the binary signal is transmitted with two antipodal pulses. For instance, if a given Gaussian n-derivative pulse represents the binary I, its corresponding antipodal representation is used to transmit the binary 0.

### • On-Off Keying

OOK is the simplest modulation scheme available for modulating UWB signals. One of the binary symbols is represented by transmitting a pulse, where the complementary binary symbol is represented by the absence of a pulse. This work makes use of OOK modulation for transmitting IR-UWB signals by toggling the state of FPGA output pins. External pulse-shaping circuitry could still be used to re-shape this signal to further resemble Gaussian pulses, improving transmission characteristics and minimizing group delay.

### • Pulse-Shape Modulation

PSM works by assigning a unique pulse for each transmitted binary symbol, hence preventing signal autocorrelation between symbols. Ideally, the pulses are orthogonal as in Orthogonal Pulse Modulation (OPM). In multiple access conditions, this modulation can also help eliminate cross-correlation between concurrent transmissions as each symbol of different channels can be assigned its unique pulse-shape.

#### • Pulse-Position Modulation

In PPM each symbol is represented by a pulse in a precise time slot of a UWB transmission. The information is therefore contained in the precise time of arrival of the pulses at the receiver's end. As the transmitter's clock information is needed to correctly decode the transmissions, a synchronization reference can be obtained with a shared or common clock between transmitter and receiver. Frequently, the synchronization problem can be solved in a differential mode, with Differential Pulse-Position Modulation (DPPM), by encoding the information relatively to the last transmitted symbol.

#### • Pulse-Width Modulation

PWM symbols carry information in the width of UWB pulses - unique pulse-widths in the time domain are reserved for each symbol. Clock information can be also be encoded in the PWM signal, which period can match the width of the shortest symbol's pulse-width.

#### • Binary Phase-Shift Keying

BPSK modulation can be generated by continuously transmitting a pulse which phase shifts when sending the opposite binary symbol.

$$1^{\text{st}} - order \ Gaussian \ derivative: \qquad x^{1}(t) = \frac{A \cdot t}{\sqrt{2\pi} \cdot \sigma^{3}} \cdot e^{-\frac{t^{2}}{2\sigma^{2}}}$$

(2.4)

$$n^{\text{th}}$$

- order Gaussian derivative:  $x^n(t) = \frac{d^n}{dt^n} \left( \frac{A \cdot t}{\sqrt{2\pi} \cdot \sigma} \cdot e^{-\frac{t^2}{2\sigma^2}} \right)$  (2.5)

Figure 2.2: Common IR-UWB Modulation schemes according to [17, 19]. These IR-UWB pulses were generated with 1<sup>st</sup> order derivative Gaussian pulses, except bit 0 of PSM which is a 2<sup>nd</sup> order derivative pulse.

where:

$$\sigma = \frac{\tau_{pulse}}{2\pi}$$

and  $\tau_{pulse}$  the pulse length. (s) (2.6)

#### 2.2.2 Medium Access Control

Impulse-based UWB occupies a single-band, wide enough to comply with the UWB bandwidth definitions in 2.1. There is no band isolation between different IR-UWB transmitters using the same portion of the UWB spectrum. Whether impulses are transmitted in their original baseband or through an up-conversion carrier wave, medium access control techniques can be used to provide multiple access capability and prevent RF interference with other systems nearby.

Such techniques, described in [19], typically consist in randomizing IR-UWB signals in a way that causes the transmissions to appear like RF noise to third-party receivers. This can be achieved in at least two different ways: using a *Time-Hopping* (TH) or *Direct-Sequence* (DS) approach, although not all modulations work with both techniques. For Medium Access Control

in Single-band UWB applications, Time-Hopping or Direct-Sequences can enable band sharing without enforcing RF channel isolation as it is usually the case with Multi-band UWB. Multi-band applications can also concentrate these techniques into their sub-bands for additional medium sharing capabilities.

#### • Time-Hopping (TH)

TH varies the position of transmitted pulses in relation to a known PN code. In this technique, multiple transmissions are allowed if each user has their unique PN code. Every code specifies the position in time of the multiple pulses that spread a binary bit of data payload. PAM, PPM, PWM and PSM are suitable modulations for TH scenarios.

#### • Direct-Sequence (DS)

DS uses different PN codes per modulated binary bit and per channel. The PN codes are converted to several modulated pulses, therefore forming a unique *chip* of suitable length. Simultaneous transmissions can be achieved if the receiver is capable of despreading the channel by matching the received signal with a range of known codes. Accepted modulations for DS are PAM, OOK and PSM, but not PPM as this modulation is the most simple form of TH. This work will focus on using a DS similar approach through making use of different PN codes that translate into *chips* (sequences of OOK pulses) to transmit a binary data payload of *ones* and *zeros* in an IR-UWB channel.

#### PN Sequences for DS IR-UWB

Pseudo-random Noise Sequences can be used to spread the binary data payload over the entire available bandwidth of the transmission channel. In an IR-UWB system, the transmitter generates pulses that match a predetermined PN sequence. Although the signals resemble white noise to common Narrowband transmitters, they are deterministic and can be despread and decoded by DS IR-UWB receivers. Examples of PN sequences are: Maximum Length Sequences (m-sequences), Gold codes, Kasami codes, Barker codes or Walsh–Hadamard codes.

The characteristics of UWB pulses limit the effects of multipath propagation like fading and interference, particularly if adequate PN codes and Rake Receiver techniques are used - both were included in the design of the IR-UWB architecture for this dissertation. Yet, UWB signals are still vulnerable to inter-symbol interference, autocorrelation and cross-correlation phenomena - the choice of ideal PN codes is key to obtaining the best performance out of a DS system.

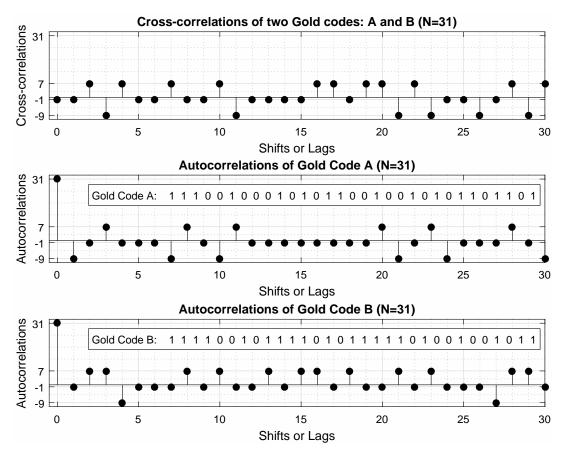

#### **Gold Codes**

Gold codes are a set of PN sequences that are very effective in enabling multiple transmitter operation over the same channel. Sets of Gold codes with  $2+2^n-1$  sequences of odd length  $N=2^n-1$  can be generated by time-shifting *Preferred-Pairs* of m-sequences and using *XOR* operations between them. The resulting codes have predictable, bounded and lower peak cross-correlations than

m-sequences within a particular set, which is an advantage in a multi-user scenario. About half of the codes in a set are balanced, meaning that the number of *zeros* and *ones* differ by one, enforcing the white noise spectral signature of the transmissions. Even though Gold sequences show slightly worse autocorrelation properties than m-sequences, their corresponding autocorrelations are not entirely problematic.

The usage of Gold Codes in favour of other variants of PN sequences was decided in agreement with Supervisor Professor Sérgio Reis Cunha, as these codes are commonly used in CDMA systems and GPS navigation and are well documented in literature. Many resources are available on-line to facilitate the understanding of the algorithms that can generate such codes.

#### **Kasami Codes**

Kasami codes are another kind of PN sequences with good cross-correlation properties. Kasami sequences are divided into two sets: the small set and the large set, but only the former offers the best correlation properties as they approach Welch's lower bound. However, despite the small set performing better than Gold codes, there are only  $2^{n/2}$  sequences in the small set. As for the larger set, it not only includes the small set but also a set of Gold codes, for mod(n,4) = 2, and additional Kasami sequences. Kasami codes also have a length of  $N = 2^n - 1$ , but contrary to Gold codes, n must be even. Nevertheless, Kasami sets can be obtained using shift operations similar to those used for generating Gold codes.

#### • Steps for generating *Preferred-Pairs* of m-sequences ([21, 22, 23])

- 1. Obtain a m-sequence, u, of length  $N = 2^n 1$  with a maximum-length Linear-Feedback Shift-Register (LFSR) of n shift-registers. A LFSR is a shift-register in which its input bit is a linear function of its previous state and can be implemented with cascading exclusive-or (XOR) operations, that can be represented by a feedback polynomial. A maximum-length LFSR has a primitive feedback polynomial and can go through all the possible states, or  $2^n 1$  states, except one (all bits equal to zero).

- 2. Create a  $2^{nd}$  m-sequence, v, by applying decimation by a factor of q to the original m-sequence. Decimation effectively reduces high-frequency components of a signal and performs down-sampling, keeping only every  $q^{th}$  sample while preventing aliasing. These m-sequences are considered *Preferred-Pairs* if the following conditions are simultaneously met:

- (a) n is odd, or mod(n,4) = 2, meaning n can't be divisible by 4

- (b) q is odd and, for a given integer k,  $q = 2^k + 1$  or  $q = 2^{2k} 2k + 1$

- (c) n is odd and gcd(n,k) = 1, or mod(n,4) = 2 and gcd(n,k) = 2

where:

*mod()*: *is the modulo operation;*

gcd(): is the greatest common divider.

13

#### • Steps for generating Gold Codes ([21, 22])

- 1. Obtain a *Preferred-Pair* of m-sequences, (u, v) of period  $N = 2^n 1$ .

- 2. A set of N + 2 Gold codes is defined by:

$$G(u,v) = \left\{ u, v, u \oplus v, u \oplus Tv, u \oplus T^2v, \dots, u \oplus T^{N-1}v \right\}$$

(2.7)

where:

$\oplus$ : is the modulo 2 sum operator (XOR operator);

$T^{N-1}$ : is a cyclic left shift operator by N-1 shifts.

#### • Steps for generating Kasami Codes ([24])

- 1. Given a binary sequence u of period  $N = 2^n 1$ , obtain w by decimating u by  $2^{n/2} + 1$ .

- 2. For an even *n*, the small set of Kasami sequences is given by:

$$K_s(u,n,m) = \begin{cases} u, & m = -1 \\ u \oplus T^m w, & m = [0, 2^{n/2} - 2] \end{cases}$$

(2.8)

where:

$\oplus$ : is the modulo 2 sum operator (XOR operator);

*m*: is a shift parameter for w;

$T^m$ : is a cyclic left shift operator by m shifts.

3. Considering u and w, obtain v by decimating u by  $2^{(n/2)+1}+1$ . For mod(n,4)=2, the large set of Kasami sequences is given by:

$$K_{L}(u,n,k,m) = \begin{cases} u, & k = -2; & m = -1 \\ v, & k = -1; & m = -1 \\ u \oplus T^{k}v, & k = [0, 2^{n} - 2]; & m = -1 \\ u \oplus T^{m}w, & k = -2; & m = [0, 2^{n/2} - 2] \\ v \oplus T^{m}w, & k = -1; & m = [0, 2^{n/2} - 2] \\ u \oplus T^{k}v \oplus T^{m}w, & k = [0, 2^{n} - 2]; & m = [0, 2^{n/2} - 2] \end{cases}$$

$$(2.9)$$

where:

$\oplus$ : is the modulo 2 sum operator (XOR operator);

k: is a shift parameter for v;

*m*: is a shift parameter for w;

$T^k$ : is a cyclic left shift operator by k shifts.

$T^m$ : is a cyclic left shift operator by m shifts.

#### **Cross-correlation & Autocorrelation**

• Cross-correlation — can be defined as a measure of similarity between two signals when one lags relative to the other. Reducing this phenomenon in different transmitting channels or even different symbol's codes is critical to allow correct detection of a PN coded signal and limit the effect of multiple transmissions in a shared medium. In other words, if two systems communicate with orthogonal codes, both can use the medium simultaneously without interfering much with each other's transmissions as the receiver will still be able to correctly despread the symbols of each channel.

The cross-correlation between sequences u and v of length N is given by:

$$R_{u,v}(i) = \sum_{j=-N+1}^{N-1} u(j) \ v(j+i)$$

(2.10)

The cross-correlation function between any shifted or non-shifted Gold sequences takes only three possible values:

$$\theta_{u,v}(i) = \{-t(i), -1, t(i) - 2\}$$

(2.11)

where:

$$t(i) = \begin{cases} 2^{(i+1)/2} + 1, & i \text{ is odd} \\ 2^{(i+2)/2} + 1, & i \text{ is even} \end{cases}$$

(2.12)

The corresponding cross-correlation function for Kasami sequences takes values from:

$$\theta_{u,w,v}(i) = \{-t(i), -s(i), -1, s(i) - 2, t(i) - 2\}$$

(2.13)

where:

$$t(i) = 2^{(i+2)/2} + 1, \quad i \text{ is even}$$

(2.14)

$$s(i) = \frac{1}{2}(t(i)+1)$$

(2.15)

Autocorrelation — or cross-autocorrelation, can be defined as the cross-correlation of a signal with itself at different instants in time. For instance, Inter-symbol Interference (ISI) caused by reflections on the receiver's end can attenuate/amplify parts of the signal and lead to false positives or misdetection of PN codes if the autocorrelation peak is not well delimited. This peak influences the capability of the receiver to self-synchronize, and good code synchronization capability is particularly crucial in wave propagation mediums affected by noise and multipath propagation.

Figure 2.3: Plots of cross-correlations and autocorrelations of Gold codes with period N = 31.

The autocorrelation at lag i for a sequence u of length N is given by:

$$R_{u,u}(i) = \sum_{j=0}^{N-1} u(j) \ u(j-i)$$

(2.16)

The autocorrelation function of a m-sequence has period  $N = 2^n - 1$  and has ideal autocorrelation properties, taking only two possible values:

$$R(i) = \begin{cases} N, & i = 0 \\ -1, & 1 \le i \le 2^n - 2 \end{cases}$$

(2.17)

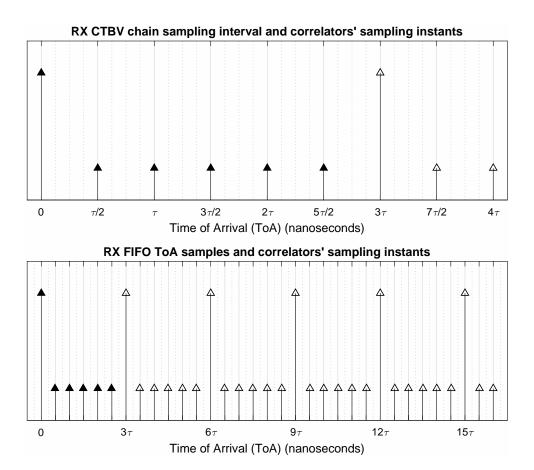

## 2.2.3 CTBV Signal Processing & DS Detection

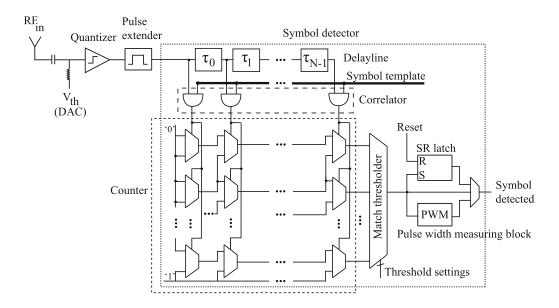

Although not unique, a popular method for processing IR-UWB signals and detecting UWB *chips* consists in feeding a Continuous-Time Binary Value (CTBV) signal to a digital circuit designed in a Rake Receiver topology, an approach described by [14, 15]. Following a threshold sampling stage, the CTBV input is fed upon a Rake Receiver CMOS circuit that performs correlation of the

input signal with a range of expected DS codes. Taking into consideration the objectives of this dissertation work, which makes use of DS, the current section will briefly describe how CTBV signal processing works and how it can be used in a Rake Receiver topology.

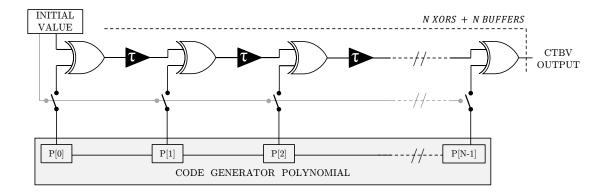

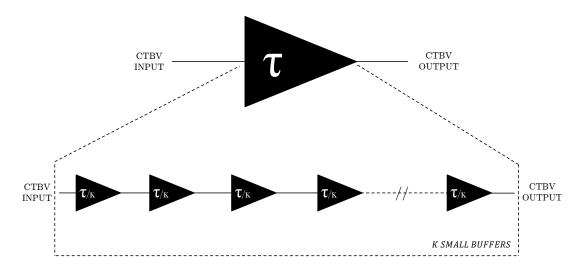

## • CTBV Signal Processing

Continuous-Time Binary Value (CTBV) consists on implementing a receiver that performs continuous 1-bit threshold sampling and serial propagation of the binary value at the input of the receiver to several detection fingers, or correlators, of a Rake Receiver logic circuit. No sampling clock is used, the propagation takes place at the intrinsic speed of the CMOS logic gates, usually around a few tens of *picoseconds*. The length of the CTBV chain should be long enough to accommodate the pulses of at least one entire *chip*. Likewise, the propagation delay of the individual logic elements that form the chain should be significantly lower than the inverse of the bandwidth of the IR-UWB pulses. By combining sets of several logic elements, delay buffers can be implemented along the chain to provide pulse isolation for the Rake correlators.

$$CTBV \ chain \ length \ge chip_{size}$$

(2.18)

CTBV logic propagation delay

$$\ll \tau_{pulse}$$

(s) (2.19)

$$chip_{size} = N (2.20)$$

$$\tau_{pulse} = \frac{1}{BW_{pulse}}$$

(s) (2.21)

$$\tau_{chip} = \tau_{pulse} \times chip_{size}$$

(s) (2.22)

where:

N: is the length of the Gold code;  $au_{pulse}$ : is the IR-UWB pulse length (s);  $BW_{pulse}$ : is the pulse bandwidth (Hz);

$\tau_{chip}$ : is the chip length (s).

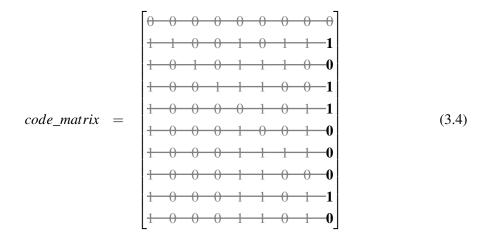

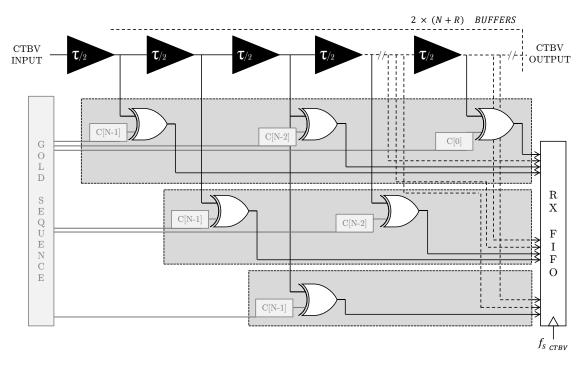

#### • Rake Receiver Topology & DS Detection

A Rake Receiver can be described as a logic circuit that performs correlations between its input signal and a sufficient number of delayed versions of the expected signals, which pulses match known PN sequences. When used in conjunction with a CTBV chain, either the chain

2.3 Multi-Band UWB

or the correlators' output must be sampled at a frequency that should be at least equal to the inverse of the time of *chip* (equation 2.23). Each correlator, or finger, contains a slightly time-shifted version of the pulses derived from the CTBV chain and can potentially contain a recognizable PN sequence. The minimum number of correlators that assures detection of a single PN code is given by the ceiling of the ratio between the IR-UWB pulse bandwidth and the CTBV chain sampling frequency as shown in equation 2.24.

The Rake topology is resilient to the effects of multipath propagation and fading, as each finger attempts to detect a match for a known *chip* on its own, yielding more chances for a sequence to be detected in noisy or multipath environments. Detection thresholds can also be set in ways to enable partial *chip* recovery, therefore increasing the chances of detecting a sequence: for instance, by allowing an arbitrary number of misaligned bits in a received *chip* or by combining the partial detections of different correlator fingers.

CTBV chain sampling frequency:

$$f_{s_{CTBV}} \geq \frac{1}{\tau_{chip}}$$

(Hz) (2.23)

where:

$f_{s CTBV}$ : is the sampling frequency of the CTBV chain (Hz);

$\tau_{chip}$ : is the chip length (s);

Number of Rake Correlators (Fingers):

$$R \geq \left\lceil \frac{BW_{pulse}}{f_{s \ CTBV}} \right\rceil$$

(2.24)

where:

$BW_{pulse}$ : is the IR-UWB pulse bandwidth (Hz);

$f_{s_{CTBV}}$ : is the sampling frequency of the CTBV chain (Hz);

### 2.3 Multi-Band UWB

UWB transceivers can either operate in Single-Band (Impulse-Radio) or Multi-Band schemes, the latter option gaining ever more momentum while IR-UWB is already widely used in several UWB applications. Each of these schemes use corresponding modulation techniques, have appropriate medium access control options available, and each offer unique advantages over the other.

Unlike Single-Band Impulse-based UWB, Multi-Band separates the UWB available spectrum into sub-bands of at least 500 MHz as per the regulatory definition of UWB. This provides isolation between different channels, the bandwidth of each receiver is limited to the sub-band bandwidth. Higher data-rates can still be achieved if several sub-bands are used simultaneously. Multi-Band UWB can be achieved, essentially, in two different ways: Multi-Band Impulse-Radio (MB-IR) and

Figure 2.4: Block diagram of the classic CTBV Rake Receiver topology with multiple parallel correlator fingers (Image source: [25]).

Multi-Band Orthogonal Frequency-Division Multiplexing (MB-OFDM) according to [19]. While MB-IR works similarly to IR-UWB in each sub-band, MB-OFDM uses a Time-Frequency Code mechanism where each time-slot uses a different carrier frequency, useful both for diversity and multiple user access.

This work focus exclusively on Single-Band Impulse-based UWB (IR-UWB) for its simplicity and less complex implementation of RF front-ends over Multi-Band UWB. The aim of using as few resources as possible and low-cost components also determined the use of IR-UWB even if that implies a degradation of noise immunity or reduced number of available channels (user capacity) of the system when compared to a more complex Multi-Band system. Even though Multi-Band UWB receivers can make use of components with softer bandwidth requirements due to band isolation, these systems generally imply the use of multiple transceiver circuits and efficient synchronization schemes to make the all available channels usable, therefore increasing the costs and complexity of the implementation at no additional gain for the purpose of the proof-of-concept demonstrations that this dissertation aims to offer.

As such, IR-UWB architectures, modulation schemes and medium access control techniques have been described in this chapter, leaving out Multi-Band UWB to be later pursued by the reader's interest through other publications such as [19], where further information on Multi-Band UWB can be found. Following these definitions, some IR-UWB current applications will also be referenced in the following section.

### 2.4 IR-UWB Applications

A relevant author in IR-UWB research and prototype development is Professor Tor Sverre Lande from the Department of Informatics at University of Oslo. Extensive literature can be found from this author describing an equally vast range of UWB solutions, applications, techniques and hardware development. These include radar [26, 27, 28] and ranging measurement devices [26, 27, 28] based on IR-UWB and CTBV processing using Direct Sequence CDMA (DS-CDMA) Pseudorandom Noise (PN) codes on dedicated CMOS logic [15]. Other of his publicly known research works with UWB are biomedical sensing [29, 30, 31, 32, 33], radio communication [34, 35], radar imaging [36], RFID [37] and wireless sensor networks [38].

Nevertheless, several other authors have conducted experiments and research on UWB and IR-UWB, and some of those works will be presented in the next sections according to their category of application.

#### 2.4.1 Short-Range Communications

- CMOS Impulse Radio Receiver Front-end [34] describes a CMOS implementation of an UWB receiver front-end architecture based on a combination of a LNA, integrator and threshold pulse shaper. The sequence of received impulses is passed through a delay line of CMOS inverters and sampled at a much lower rate than the input signal frequency, being later decoded by a parallel network of correlators in a Rake Receiver topology.

- A 3 GHz to 5 GHz IR-UWB Receiver Front-End for Wireless Sensor Networks [38] presents a working prototype of a CMOS IR-UWB receiver for sensor networks in the 3 GHz to 5 GHz frequency range, with a low power operation of about 26.6 mW. The system relies on CTBV and its targeted for low-power and low data-rate communication over short distances, offering 1 Mbit/s at 10<sup>-3</sup> BER in a chip area of 0.9 mm<sup>2</sup> under 90 nm CMOS technology.

#### 2.4.2 Short-Range Radar, Ranging Measurements and Indoor Positioning

• Impulse-based ultra-wide-band (UWB) radio systems and applications [15] describes in detail a CMOS implementation of a IR-UWB radar system using CTBV signal processing that makes use of PN codes. The time-domain pulse detector consists of a sweeping threshold sampler and a 1-bit quantizer on the incoming RF signal. This system is similar to the Radio Receiver front-end described in [34] and likewise, the main system and sampling clock can work at several orders of magnitude lower frequency than the UWB pulse frequency. This enables low-power operation in both the receiver and transmitter. Expression 2.25 indicates the relationship between the required system clock/sampling frequency ( $f_{clk}$ ), temporal resolution (minimal pulse duration  $\tau$ ) and size of chip ( $chip_{size}$ ) as per [15]. The prototype device can also perform ranging measurements based on Time of Arrival or Time of Flight

(ToA/ToF) estimations.

Clock/Sampling Frequency:

$$f_{clk} = \frac{1}{\tau \cdot chip_{size}}$$

(Hz) (2.25)

- A High-Resolution Short-Range CMOS Impulse Radar for Human Walk Tracking [28] refers an impulse-based UWB radar with a 4-channel sampling receiver, a LNA and an integrator. It can track the movement of a person indoor up to a distance of 12 m with a range resolution of about 1.5 cm while consuming 80 mW of power.

- A Time to Digital Converter for use in Ultra Wide Band Radar Sensor Nodes [39] describes a Time to Digital Converter architecture for UWB radar implementations that allows RF front-end interfacing with microcontrollers. Contrary to other solutions, the design does not rely on state-of-the-art ADCs, ultra fast memories or high-end logic elements; instead it uses a Time to Voltage converter made of simple latch memory elements, variable threshold comparators and discrete capacitors. The 16 comparator-capacitor pairs works as a form of analog memory chain that is then sampled by the built-in ADC of a microcontroller. The ranging computations are based on ToF/ToA estimation and the detection distance goes up to 10 m with a 1.95 cm range resolution.

Range Resolution:

$$range_{res} \ge \frac{c_0}{BW_{pulse}}$$

(m) (2.26)

#### 2.4.3 Imaging and SAR

- Ultrawideband (UWB) Radar Imaging of Building Interior: Measurements and Predictions [7] explores through-the-wall imaging by implementing an UWB Synthetic-Aperture Radar (SAR).

- Ultra Wide Band Synthetic Aperture Radar Real Time Processing with a Subaperture Non-linear Chirp Scaling Algorithm [40] describes an airborne UWB SAR system that can produce aerial imagery with up to 1 m × 1 m resolution (dependant on aircraft flight level).

- *Imaging of Oil-Well Perforations Using UWB Synthetic Aperture Radar* [41] applies UWB technology to monitor oil well perforations with a SAR algorithm.

#### 2.4.4 Biomedical

Direct RF Subsampling Receivers Enabling Impulse-Based UWB Signals for Breast Cancer Detection [6] promises a less risk-inducing diagnostic alternative based on UWB when compared to ionizing radiation or potentially dangerous high-energy medical diagnostic techniques.

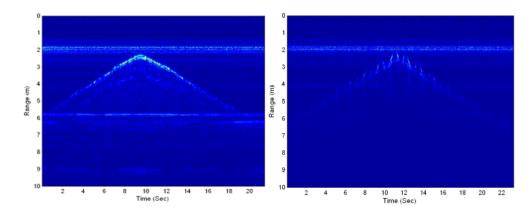

Figure 2.5: Micro-Doppler signature of a person walking in front of an UWB radar system. Left plot: signature of a person walking in front of an UWB radar system. Right plot: person walking and performing an arm swing motion. (Image source: [42]).

• Vital Signs Monitoring with a UWB Radar Based on a Correlation Receiver [43] demonstrates a Vital Signs Monitoring application of respiratory functions and heart-beat rates at a distance of tens of centimetres.

#### 2.4.5 Automotive Radar and Collision Avoidance Systems

• 22–29 GHz Ultra-Wideband CMOS Pulse Generator for Short-Range Radar Applications [13] describes a UWB automotive radar for short-range collision avoidance systems.

#### 2.4.6 Commercially available solutions

Companies such as TimeDomain<sup>®</sup>, Camero<sup>®</sup> and Cambridge Consultants Ltd. have turn-key UWB solutions such as UWB radars on the market, including some for civilian use. Nevertheless, due to the closed development nature of commercial solutions those will not be considered in this state-of-the-art analysis.

## 2.5 FPGA implementations of UWB systems

The following applications include an FPGA in the design to at least partially execute the computations associated with digital signal processing. In the receiver element, the signal is usually obtained from an RF front-end that might include threshold detectors, ADCs or other sampling circuits. Extremely complex RF front-end circuits are out of the scope of the dissertation work but some are hereby referenced to demonstrate current and higher-complexity UWB implementations.

• Towards Low Cost, High Speed Data Sampling Module for Multifunctional Real-Time UWB Radar [42] achieves through-wall radar imaging up to 100 GSamples/s with an FPGA and external high-speed ADCs.

- Crystal-less Duty-Cycled-When-Active IR-UWB Transceivers [44] mentions a working prototype of an IR-UWB communication system that interfaces with a CMOS transceiver architecture.

- Peak Detection Ultra-Wideband Transceiver Using Tunnel Backward Diode [45] shows the

implementation of non-coherent UWB receivers in both single-band and multi-band scenarios. The envelope detector is implemented with a diode detector circuit. The authors claim

a data-rate of 190 Mbit/s in single-band mode and 400 Mbit/s in multi-band operation.

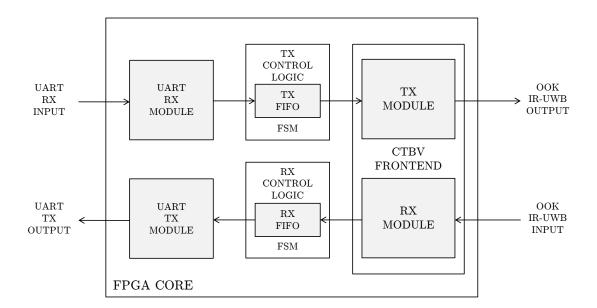

- A Low-Cost COTS UWB Transceiver for Biological Applications Achieves 50 Mbit/s with < 10<sup>-6</sup> Raw BER [46] documents a working system built upon an RF front-end using off-the-shelf parts consisting on a LNA, a BPF, a Gain Amplifier, an RF detector and a Comparator. In the receiver, the output of the comparator is fed onto an FPGA in order to detect the PN sequences and recover the payload data. Although the achieved data-rate and communication range are somewhat limited, this is an interesting work that is closer to the work that is to be developed.

#### 2.6 Conclusions

Taking into consideration the publicly available research on UWB technology, its applications and current capabilities, which only a few comparatively relevant ones were referenced above, its safe to say that UWB development is gaining a lot of momentum since the regulatory liberation. Nevertheless, the technology is still relatively expensive to be made available at the consumer or even industrial level and most current solutions demand the fabrication of custom CMOS chips. Therefore, there is still a gap for cost-effective UWB solutions at the present day. It shall be noted then that the aim of this dissertation work is to help bring UWB technology to a broader range of usages while bringing the deployment cost down by evaluating different methodologies with smaller and less expensive Bill of Materials (BoM) that mostly make use of inexpensive off-the-shelf parts.

Programmable logic could potentially become an attractive development and prototyping platform for IR-UWB technology as its easily reconfigurable and upgradable, unlike custom ASIC development and other more expensive solutions that offer improved performance but yet require higher development and deployment costs.

Contrary to ASIC solutions, the work to be presented in the following chapters will demonstrate how to use FPGAs in ways they are not usually supposed to be exploited such as using logic cells as constant delay buffers. Yet, even considering the inherent limitations and variability of the Place & Route process and the fact that no manual chip floor-planning was done, the design still yield relevant results. As such, the work provides a foundation for future IR-UWB lines of development with lower-cost programmable logic.

## Chapter 3

# **System Architecture**

#### Introduction

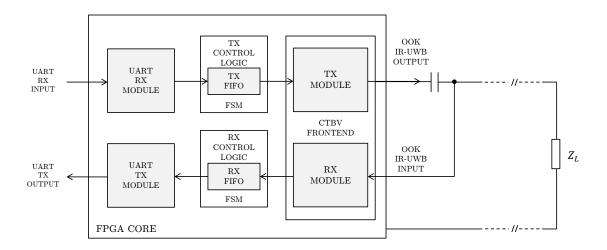

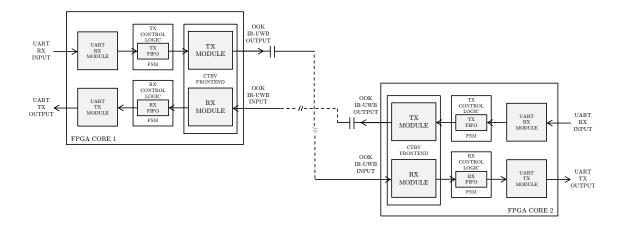

As mentioned in previous chapters, the proposed approach for implementing an IR-UWB system using programmable logic is based on the strategy introduced by Professor Tor Sverre Lande in [25, 15]. The principles of implementation will be prove to be very similar, but the methodology differs in the physical implementation of the system as no custom CMOS chip will be used for the RF front-ends or for PN sequence correlation. This chapter describes how the prototype was designed in order to accomplish the desired goals for the proof-of-concept demonstrations.

One of the challenges introduced by this different approach is the utilisation of off-the-shelf programmable logic chips, like CPLDs and FPGAs, instead of an ASIC solution. Because the CTBV topology relies on fixed and ideally constant delays through the input signal chain, application-specific chips are designed to offer this desired functionality at the maximum performance offered by their CMOS lithography technology. Thus, ASIC designs can meet precise and predictable timing requirements. Yet this CMOS implementation is not usually re-configurable. This means that a performance upgrade typically requires a re-design and fabrication of a new chip.

On the other hand, programmable logic designs are more easily upgradeable as long as the design can be ported to newer FPGA or CPLD cores. Notwithstanding, all upgrades will still need functional validation through formal testing. Despite the challenges, these programmable platforms are very attractive from a system's designer point of view if they could offer similar functionality to ASIC solutions, at a fraction of the development and implementation cost. Even if the performance is still limited, mostly because the design makes use of FPGA's logic elements in ways they were not really designed for, this work will propose a portable architecture for generating and detecting IR-UWB pulses using programmable logic devices with minimal external components.

Following this introduction, the information in this chapter is divided into four major sections:

• Section 3.1: Design Challenges & Decisions, describes some of the challenges encountered during the design phase and some decisions on how to overcome them;

• Section 3.2: System Components, defines the architecture of the components built into the IR-UWB system;

- Section 3.3: System Configurations, demonstrates two possible applications for the system: performing ranging measurements and operating as a transceiver;

- Section 3.4: Conclusions, closes this chapter by showing a summary of what been developed.

## 3.1 Design Challenges & Decisions

This section will summarize some of the foreseen or encountered implementation challenges and the corresponding design decisions.

- **FPGA** vs **CPLD** Programmable logic is available in two different variants: FPGAs or CPLDs. FPGAs traditionally offer faster speeds, greater number of logic resources and more periphels like RAM. A balance on performance vs cost was reached and is described on Chapter 4, System Implementation on Programmable Logic Hardware, further justifying this choice, so the pulse detector (RX) and pulse generator (TX) blocks were implemented in this type of programmable logic device.