## **Durham E-Theses**

# Generic Techniques in General Purpose GPU Programming with Applications to Ant Colony and Image Processing Algorithms

DAWSON, LAURENCE, JAMES

#### How to cite:

DAWSON, LAURENCE, JAMES (2015) Generic Techniques in General Purpose GPU Programming with Applications to Ant Colony and Image Processing Algorithms, Durham theses, Durham University. Available at Durham E-Theses Online: <a href="http://etheses.dur.ac.uk/11211/">http://etheses.dur.ac.uk/11211/</a>

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

## GENERIC TECHNIQUES IN GENERAL PURPOSE GPU $\begin{array}{c} \text{PROGRAMMING WITH APPLICATIONS TO ANT COLONY AND} \\ \text{IMAGE PROCESSING ALGORITHMS} \end{array}$

Laurence Dawson

A thesis presented for the degree of Doctor of Philosophy

#### Abstract

In 2006 NVIDIA introduced a new unified GPU architecture facilitating general-purpose computation on the GPU. The following year NVIDIA introduced CUDA, a parallel programming architecture for developing general purpose applications for direct execution on the new unified GPU. CUDA exposes the GPU's massively parallel architecture of the GPU so that parallel code can be written to execute much faster than its sequential counterpart. Although CUDA abstracts the underlying architecture, fully utilising and scheduling the GPU is non-trivial and has given rise to a new active area of research. Due to the inherent complexities pertaining to GPU development, in this thesis we explore and find efficient parallel mappings of existing and new parallel algorithms on the GPU using NVIDIA CUDA. We place particular emphasis on metaheuristics, image processing and designing reusable techniques and mappings that can be applied to other problems and domains.

We begin by focusing on Ant Colony Optimisation (ACO), a nature inspired heuristic approach for solving optimisation problems. We present a versatile improved data-parallel approach for solving the Travelling Salesman Problem using ACO resulting in significant speedups. By extending our initial work, we show how existing mappings of ACO on the GPU are unable to compete against their sequential counterpart when common CPU optimisation strategies are employed and detail three distinct candidate set parallelisation strategies for execution on the GPU. By further extending our data-parallel approach we present the first implementation of an ACO-based edge detection algorithm on the GPU to reduce the execution time and improve the viability of ACO-based edge detection. We finish by presenting a new color edge detection technique using the volume of a pixel in the HSI color space along with a parallel GPU implementation that is able to withstand greater levels of noise than existing algorithms.

#### Declaration

The work presented in this thesis is based on research carried out at the Department of Engineering and Computing Sciences, Durham University, England. No part of this thesis has been submitted elsewhere for any other degree or qualification and it is all my own work unless referenced to the contrary in the text.

#### Copyright © 2015 by Laurence Dawson.

"The copyright of this thesis rests with the author. No quotation from it should be published without the author's prior written consent and information derived from it should be acknowledged".

#### **Preface**

The contents of this thesis have appeared, in part, in the following peer reviewed publications:

- L. Dawson and I. A. Stewart, "Improving Ant Colony Optimization performance on the GPU using CUDA," in *IEEE Congress on Evolutionary Computation*, *IEEE-CEC'13*, Cancun, Mexico, June 20-23, 2013, pp. 1901–1908, 2013 [1]

- L. Dawson and I. A. Stewart, "Candidate Set Parallelization Strategies for Ant Colony Optimization on the GPU," in *Algorithms and Architectures for* Parallel Processing, vol. 8285 of Lecture Notes in Computer Science, pp. 216– 225, 2013 [2]

- L. Dawson and I. A. Stewart, "Accelerating Ant Colony Optimization based Edge Detection on the GPU using CUDA," in *IEEE Congress on Evolutionary Computation*, *IEEE-CEC'14*, *Beijing*, *China*, *July 6-11*, *2014*, pp. 1901–1908, 2014 [3]

- J. Zhao, Y. Xiang, L. Dawson, and I. A. Stewart, "Color Image Edge Detection based on Quantity of Color Information and its Implementation on the GPU," in 23rd IASTED International Conference on Parallel and Distributed Computing and Systems (PDCS'11), pp. 116–123, 2011 [4]

### Acknowledgments

I would like to thank my supervisor Professor Iain A. Stewart for all of his help, guidance and support throughout my undergraduate and postgraduate studies. There has rarely been an occasion over the last 4 years where he wasn't able to help solve even the most complex of problems with little more than a whiteboard and pen.

I would also like to thank Dr Yonghong Xiang for helping me settle in during the first year of my Ph.D and collaborating with me on my first paper.

Finally I would like to thank Durham University, the Department of Engineering and Computing Sciences and EPSRC for their financial support.

## Contents

| 1                           | Intr | Introduction |                                          |    |

|-----------------------------|------|--------------|------------------------------------------|----|

|                             | 1.1  | Graph        | ics Processing Units                     | 15 |

|                             | 1.2  | NVIDI        | IA CUDA                                  | 16 |

|                             | 1.3  | Motiva       | ation                                    | 19 |

|                             |      | 1.3.1        | Metaheuristics                           | 19 |

|                             |      | 1.3.2        | Image Processing                         | 20 |

|                             | 1.4  | Contri       | butions & Thesis Guide                   | 20 |

| 2                           | Ger  | neral-p      | urpose computation on the GPU using CUDA | 23 |

|                             | 2.1  | Introd       | uction                                   | 23 |

|                             | 2.2  | CUDA         | hardware                                 | 24 |

|                             | 2.3  | The C        | UDA programming model                    | 26 |

|                             |      | 2.3.1        | Blocks and Threads                       | 26 |

|                             |      | 2.3.2        | Memory types                             | 29 |

|                             |      | 2.3.3        | Synchronisation                          | 35 |

|                             |      | 2.3.4        | OpenCL                                   | 38 |

|                             | 2.4  | Recent       | t advances                               | 39 |

|                             |      | 2.4.1        | Fermi, Kepler and Maxwell                | 39 |

|                             |      | 2.4.2        | Embedded and low power applications      | 42 |

|                             |      | 2.4.3        | CUDA roadmap                             | 43 |

| 3                           | Par  | allel A      | nt Colony Optimization on the GPU        | 44 |

| 3.1 Ant Colony Optimisation |      |              | olony Optimisation                       | 44 |

|                             | 3.2  | Solving      | g the Travelling Salesman Problem        | 45 |

|                             |      | 3.2.1        | Solution Construction                    | 47 |

|   |     | 3.2.2  | Pheromone Update                               |  |  |  |  |

|---|-----|--------|------------------------------------------------|--|--|--|--|

|   | 3.3 | Parall | el Ant Colony Optimisation                     |  |  |  |  |

|   |     | 3.3.1  | Parallel ACO on the GPU                        |  |  |  |  |

|   | 3.4 | Relate | ed work                                        |  |  |  |  |

|   |     | 3.4.1  | Large TSP instances                            |  |  |  |  |

|   |     | 3.4.2  | Data-parallelism                               |  |  |  |  |

|   | 3.5 | Imple  | mentation                                      |  |  |  |  |

|   |     | 3.5.1  | Tour construction                              |  |  |  |  |

|   |     | 3.5.2  | Double-Spin Roulette                           |  |  |  |  |

|   |     | 3.5.3  | Pheromone update                               |  |  |  |  |

|   | 3.6 | Result | ss                                             |  |  |  |  |

|   |     | 3.6.1  | Experimental Setup                             |  |  |  |  |

|   |     | 3.6.2  | Solution Quality                               |  |  |  |  |

|   |     | 3.6.3  | Benchmarks                                     |  |  |  |  |

|   |     | 3.6.4  | Shared memory restrictions                     |  |  |  |  |

|   | 3.7 | Concl  | usion                                          |  |  |  |  |

|   |     | 3.7.1  | Contributions                                  |  |  |  |  |

|   |     |        |                                                |  |  |  |  |

| 4 |     |        | e Set Parallelisation Strategies 67 duction    |  |  |  |  |

|   | 4.1 |        |                                                |  |  |  |  |

|   | 4.2 |        | date Sets                                      |  |  |  |  |

|   |     | 4.2.1  | Using candidate sets with the TSP 69           |  |  |  |  |

|   |     | 4.2.2  | The effect of utilising a candidate set        |  |  |  |  |

|   | 4.3 | Relate | ed work                                        |  |  |  |  |

|   | 4.4 | Implei | mentation                                      |  |  |  |  |

|   |     | 4.4.1  | Basic setup                                    |  |  |  |  |

|   |     | 4.4.2  | Candidate set setup                            |  |  |  |  |

|   |     | 4.4.3  | Tour construction using a candidate set        |  |  |  |  |

|   |     | 4.4.4  | Task parallelism                               |  |  |  |  |

|   |     | 4.4.5  | Data parallelism                               |  |  |  |  |

|   |     | 4.4.6  | Data parallelism with tabu list compression 80 |  |  |  |  |

|   | 4.5 | Result | ss                                             |  |  |  |  |

|   |     | 4.5.1  | Experimental Setup                           | 81  |

|---|-----|--------|----------------------------------------------|-----|

|   |     | 4.5.2  | Benchmarks                                   | 81  |

|   | 4.6 | Concl  | usion                                        | 83  |

|   |     | 4.6.1  | Contributions                                | 84  |

| 5 | Ant | Color  | ny Optimization based Image Edge Detection   | 85  |

|   | 5.1 | Introd | luction                                      | 85  |

|   | 5.2 | Edge   | detection using ACO                          | 86  |

|   |     | 5.2.1  | Solution construction                        | 87  |

|   |     | 5.2.2  | Pheromone update                             | 88  |

|   |     | 5.2.3  | Termination conditions                       | 88  |

|   | 5.3 | Relate | ed work                                      | 89  |

|   |     | 5.3.1  | Edge detection using Ant Colony Optimisation | 89  |

|   |     | 5.3.2  | Other edge detection methods on the GPU      | 90  |

|   | 5.4 | Imple  | mentation                                    | 90  |

|   |     | 5.4.1  | Adapting data-parallelism for edge detection | 90  |

|   |     | 5.4.2  | Algorithm setup                              | 91  |

|   |     | 5.4.3  | Solution construction                        | 92  |

|   |     | 5.4.4  | Pheromone update                             | 95  |

|   | 5.5 | Result | ts                                           | 96  |

|   |     | 5.5.1  | Experimental setup                           | 96  |

|   |     | 5.5.2  | Algorithm parameters                         | 96  |

|   |     | 5.5.3  | Solution quality                             | 97  |

|   |     | 5.5.4  | Variable edge thickness                      | 98  |

|   |     | 5.5.5  | Benchmarks                                   | 99  |

|   | 5.6 | Concl  | usion                                        | 100 |

| 6 | Col | or Ima | age Edge Detection                           | 101 |

|   | 6.1 | Introd | luction                                      | 101 |

|   | 6.2 | Color  | image edge detection                         | 102 |

|   |     | 6.2.1  | Edge detection techniques                    | 102 |

|   | 6.3 | Relate | ed work                                      | 103 |

|   | 6.4 | Imple  | mentation                                    | 104 |

#### Contents

|    | 6.5   | Paralle | el Implementation on the GPU | 106 |

|----|-------|---------|------------------------------|-----|

|    |       | 6.5.1   | Algorithm setup              | 106 |

|    |       | 6.5.2   | Edge detection               | 107 |

|    | 6.6   | Result  | s                            | 110 |

|    |       | 6.6.1   | Noise tolerance              | 111 |

|    |       | 6.6.2   | Improved edge detection      | 112 |

|    |       | 6.6.3   | GPU Implementation Results   | 113 |

|    |       | 6.6.4   | Experimental setup           | 113 |

|    |       | 6.6.5   | Benchmarks                   | 113 |

|    | 6.7   | Conclu  | usion                        | 114 |

| 7  | Con   | clusio  | n                            | 115 |

|    |       | 7.0.1   | Future work                  | 116 |

| Bi | bliog | raphy   |                              | 117 |

## List of Figures

| 2.1 | A comparison of the floating point performance                                    | 25 |

|-----|-----------------------------------------------------------------------------------|----|

| 2.2 | A two-dimensional arrangement of 8 thread blocks within a grid                    | 26 |

| 2.3 | An overview of the hierarchical CUDA memory model                                 | 29 |

| 2.4 | An example of multiple threads across separate thread warps ex-                   |    |

|     | ecuting the CUDA all warp vote function and following different                   |    |

|     | execution paths                                                                   | 32 |

| 2.5 | An example of all threads within a block accessing the same 128 byte              |    |

|     | region of global memory resulting in a single 128 byte load                       | 34 |

| 2.6 | An example of the threads from the same block accessing two 128                   |    |

|     | byte regions of memory resulting in two separate global memory loads.             | 34 |

| 2.7 | An example of global thread block synchronisation via executing the               |    |

|     | $function\ cuda Device Synchronize ()\ to\ explicitly\ synchronise\ all\ blocks.$ | 36 |

| 3.1 | An overview of the Ant System algorithm. [19]                                     | 46 |

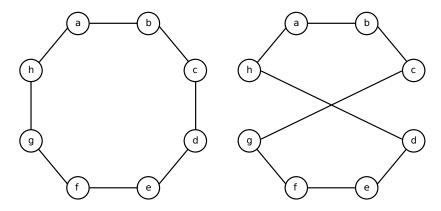

| 3.2 | An example of performing the 2-opt operation on a tour. The edges                 |    |

|     | between $(c,d)$ and $(h,g)$ and are replaced with new edges between               |    |

|     | (c,g) and $(d,h)$                                                                 | 46 |

| 3.3 | Overview of an ant's tour construction                                            | 55 |

| 3.4 | An overview of the double-spin roulette algorithm executed by each                |    |

|     | ant (thread block) during each iteration of the tour construction                 |    |

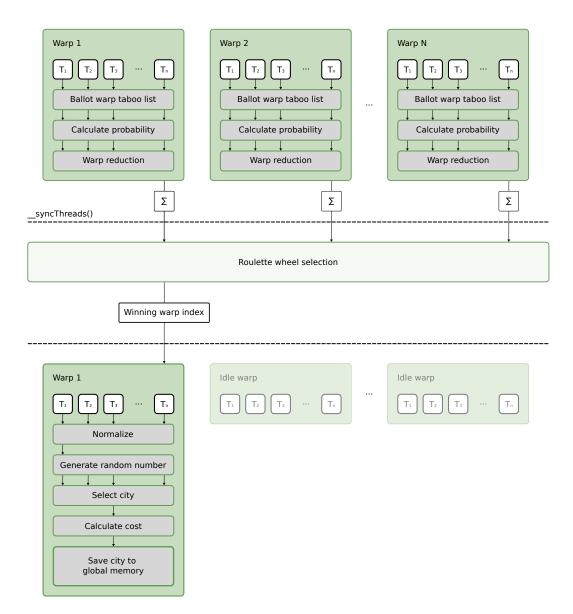

|     | phase of the AS algorithm in order to construct a valid tour                      | 58 |

| 3.5 | The warp-reduce method [52]                                                       | 59 |

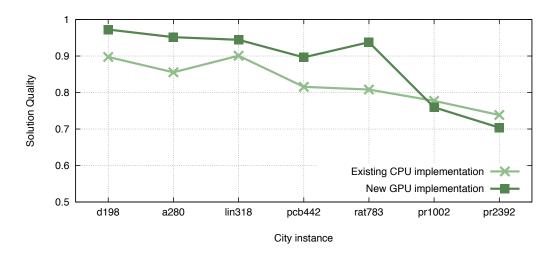

| 3.6 | A comparison of the quality of tours constructed via the existing                 |    |

|     | CPU implementation of AS and new GPU implementation                               | 62 |

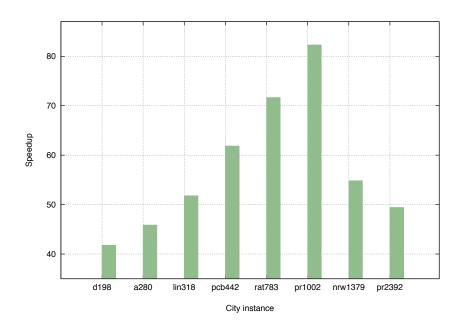

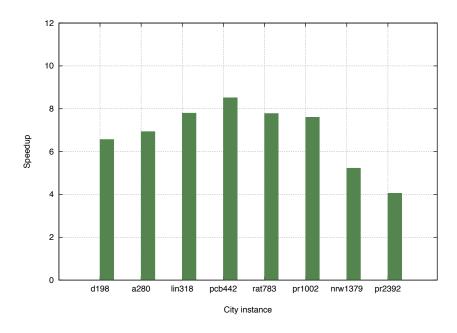

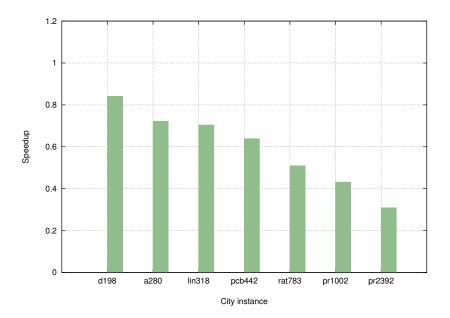

| 3.7        | Speedup of execution against the standard CPU implementation. $$ .                                                                                                                   | 64  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.8        | Speedup of execution against the best existing GPU implementation.                                                                                                                   | 64  |

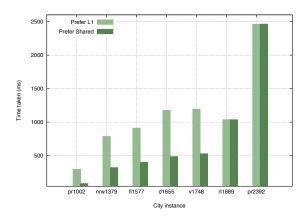

| 3.9        | Observed execution speeds as a product of varying the L1 cache size.                                                                                                                 | 66  |

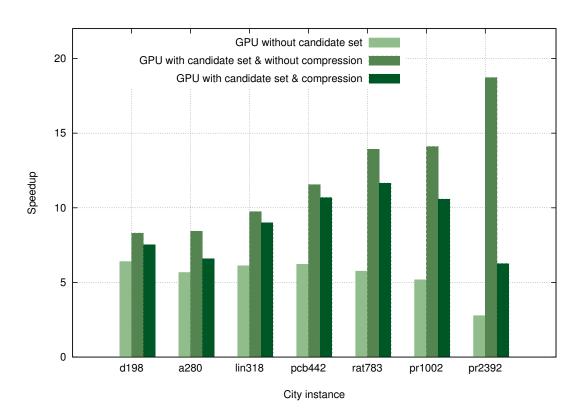

| 4.1        | Performance of the GPU implementation of AS presented by Cecilia et al. [20] without the use of a candidate set against the sequential CPU implementation [53] using a candidate set | 71  |

| 4.2        | Performance of our GPU implementation of AS without the use of a candidate set against the sequential CPU implementation [53] using                                                  |     |

|            | a candidate set                                                                                                                                                                      | 71  |

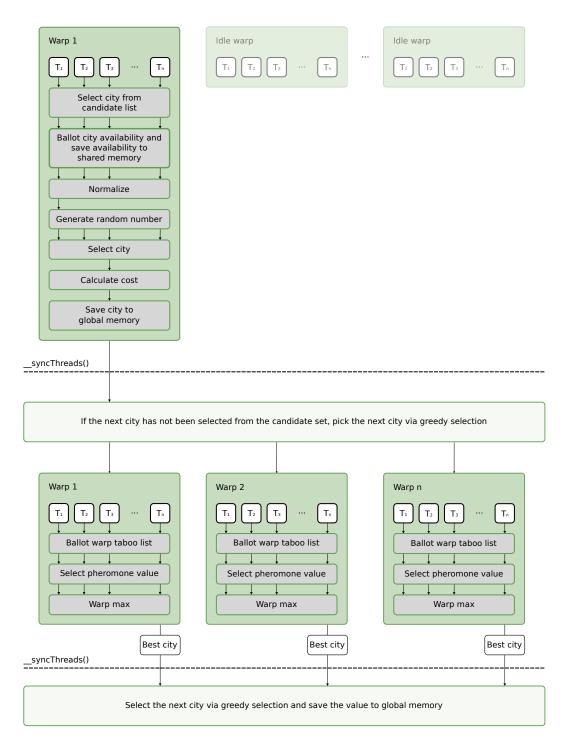

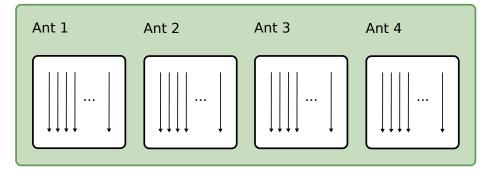

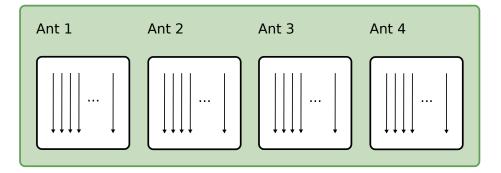

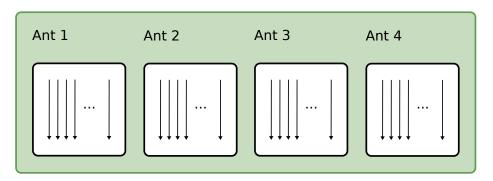

| 4.3<br>4.4 | Overview of an ant's tour construction when using a candidate set.  An overview of our data parallel tour construction algorithm utilising                                           | 74  |

|            | a candidate set to reduce the total execution time of the algorithm.                                                                                                                 | 79  |

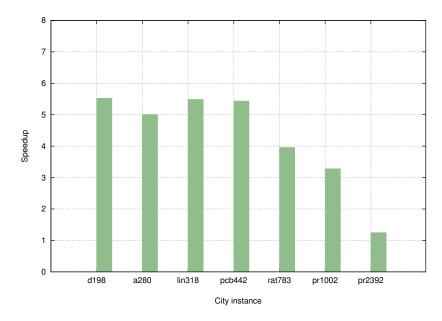

| 4.5        | A comparison of the speedup of execution of multiple GPU instances                                                                                                                   |     |

|            | (with and without use of a candidate set) against the standard CPU implementation using when using a candidate set                                                                   | 82  |

| 5.1        | Surrounding neighbour pixels and valid moves from position $(i, j)$                                                                                                                  |     |

| 0.1        | (providing none of the surrounding pixels have recently been visited)                                                                                                                | 88  |

| 5.2        | Calculating the greyscale value for a color pixel                                                                                                                                    | 91  |

| 5.3        | An overview of our novel mapping technique to pack multiple ants within a thread block. Each ant is mapped to a thread warp and                                                      |     |

|            | four warps are executed per thread block in parallel                                                                                                                                 | 93  |

| 5.4        | An overview of solution construction                                                                                                                                                 | 94  |

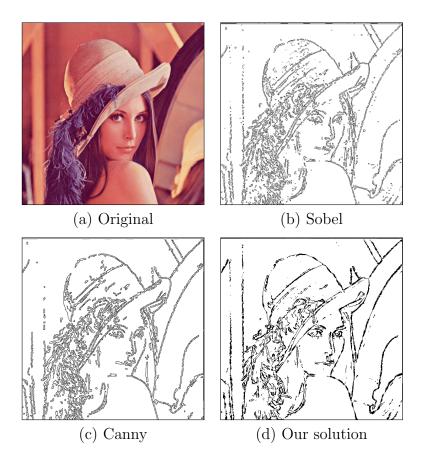

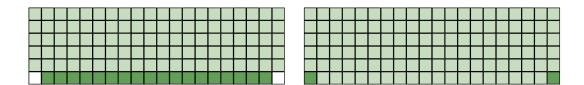

| 5.5        | A comparison of final edge maps produced by the Sobel, Canny and                                                                                                                     | 01  |

|            | our parallel ACO edge detection algorithms                                                                                                                                           | 97  |

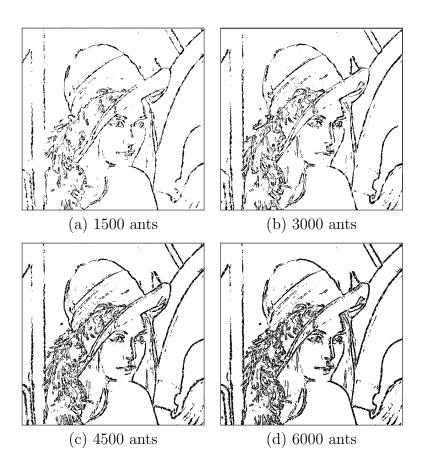

| 5.6        | The effect on edge thickness when alternating the number of ants in                                                                                                                  |     |

|            | a 512x512 standard test image                                                                                                                                                        | 98  |

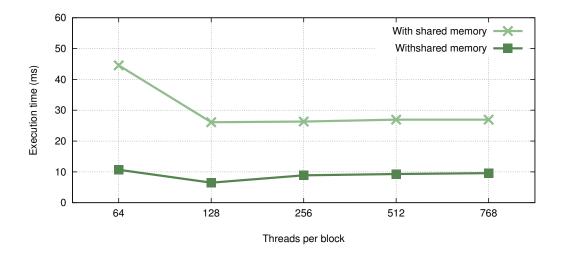

| 5.7        | Observed execution speeds for the ant-to-warp mapping with/without                                                                                                                   |     |

|            | caching visited positions to shared memory.                                                                                                                                          | 100 |

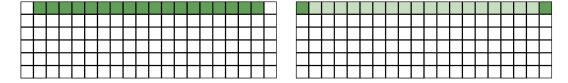

| 6.1        | Load the top apron pixels                                                                                                                                                            | 109 |

| 6.2        | Load the centre and apron pixels                                                                                                                                                     | 109 |

#### List of Figures

| 6.3 | Load the bottom apron pixels                                      | 109 |

|-----|-------------------------------------------------------------------|-----|

| 6.4 | LUT index matrix                                                  | 110 |

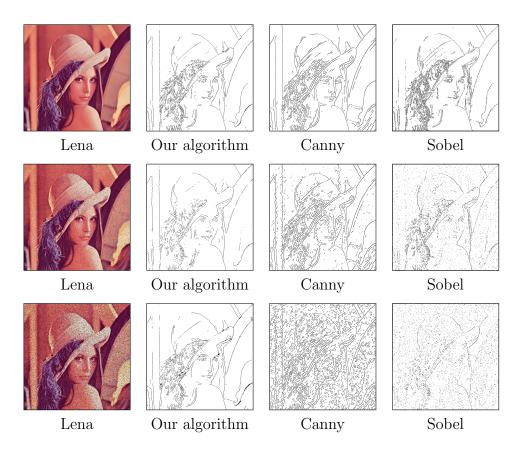

| 6.5 | The effect of introducing noise to the input image when using the |     |

|     | standard image processing test image Lena                         | 111 |

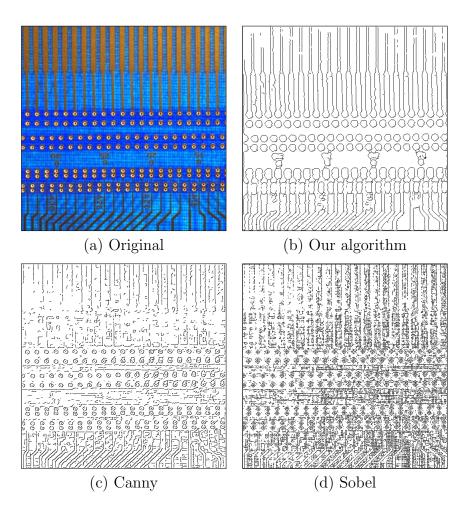

| 6.6 | Edge maps produced for a color image                              | 112 |

## List of Tables

| 2.1 | A comparison of consumer level CUDA GPUs for each hardware revision   | 39 |

|-----|-----------------------------------------------------------------------|----|

| 3.1 | An example run of roulette wheel selection (proportionate selection). | 56 |

| 3.2 | The best tour lengths obtained for various test instances of the TSP  |    |

|     | on the CPU and GPU implementations over 10 independent runs           |    |

|     | with 100 iterations                                                   | 62 |

| 3.3 | The Average execution times (ms) of our GPU implementation against    |    |

|     | the best current GPU implementation from Cecilia et al. and the       |    |

|     | standard sequential test CPU implementation (ACOTSP $[53]$ )          | 63 |

| 3.4 | The execution times for each stage of our proposed GPU implemen-      |    |

|     | tation (ms) across various instances of the TSP                       | 63 |

| 4.1 | The average execution times (ms) of the CPU implementation (with      |    |

|     | and without candidate set), the best current GPU implementation       |    |

|     | from Cecilia et al. and our GPU implementation                        | 70 |

| 4.2 | Average execution times (ms) when using AS and a candidate set        | 82 |

| 5.1 | Average execution times (ms) when varying the number of threads       |    |

|     | per block and mapping arrangement of ants to blocks, threads and      |    |

|     | warps                                                                 | 99 |

6.1 Average execution times (ms) for processing standard image processing test input images using the OpenCV canny implementation, the CUDA GPU implementation [78] with 4 passes of the hysteresis step, the CUDA GPU implementation [78] with 10 passes of the hysteresis step and finally using our new color edge detection method. . . . . . 113

#### Glossary

$\mathcal{MAX} - \mathcal{MIN}$  Ant System.

**ACO** Ant Colony Optimization.

AS Ant System.

CPU Central Processing Unit.

CUDA Compute Unified Device Architecture.

**FPS** Frames per Second.

GPGPU General-Purpose computing on Graphics Processing Units.

**GPU** Graphics Processing Unit.

**HSI** Hue-Saturation-Intensity.

**IPP** Intel Performance Primitives.

LUT Lookup table.

**NPP** NVIDIA Performance Primitives.

OpenCL Open Computer Language.

PCB Printed Circuit Board.

SM Streaming Multiprocessor.

SoC System on a chip.

**SP** Stream Processor.

**SPMD** Single-program, multiple-data.

STL Standard Template Library.

thread warp A collection of 16 to 32 CUDA threads executed in parallel within a thread block. A thread block can consist of multiple threads warps.

**TSP** Travelling Salesman Problem.

## CHAPTER 1

#### Introduction

#### 1.1 Graphics Processing Units

In November 2006 NVIDIA introduced the GeForce 8 Series architecture along with the next generation of *Graphics Processing Units* (GPUs). This generation pioneered the unified shader pipeline combining pixel and shader units into unified shaders each with their own instruction memory, cache and control logic [5]. This move to a unified architecture resulted in each of the units becoming fully programmable and no longer constrained to a single graphic task. Each of the unified shader units execute independently in parallel allowing the GPU to dynamically allocate execution resources depending on the workload. These changes in turn led to increased performance and efficiency [6]. Rege notes [7] that by moving to a unified architecture we can achieve up to a 2x increase in instruction throughput by using scalar instruction shaders resulting in significantly better performing complex graphic shaders (on the first generation of hardware alone). The resulting GPU architecture was a massively parallel general-purpose processor with large memory bandwidth and improved floating point performance that enabled both traditional graphics processing and, more importantly, facilitated general-purpose computation outside of the realm of graphics with the aid of the new unified shader units. These fundamental changes to create a new unified general-purpose GPU architecture were implemented in consumer grade GPUs available in standard desktops and laptops, so putting a parallel processor within reach of all users

Over the last decade parallel processing has become increasingly popular due in part to the diminishing returns when increasing the clock rate of conventional CPUs. Additional power consumption and cooling requirements outweighed the increased performance benefits after CPUs began to approach a clock speed of around 4 GHz [8]. This speed limit restricted the potential of single core CPUs leading to the rise of multiple core CPUs. A typical desktop computer is currently equipped with around 4 to 8 cores per CPU and this can increase upwards of 12 cores for higher end workstations or servers depending on the configuration.

#### 1.2 NVIDIA CUDA

In June 2007 NVIDIA unveiled Compute Unified Device Architecture (CUDA), a parallel programming architecture that allowed developers to harness the massively parallel architecture of the new unified GPU for general-purpose computation (GPGPU). CUDA was the first language designed to facilitate GPGPU using ANSI C which required no prior experience with OpenGL or DirectX. This gave CUDA a competitive advantage over previous attempts which forced developers to coerce non-graphics algorithms into restrictive graphics interfaces for execution on the GPU. By facilitating execution on the massively parallel architecture, code can be written to execute in parallel much faster than its optimised sequential counterpart. Parallel processing allows work to be divided into smaller units and executed in parallel as opposed to executing sequentially. NVIDA note [9] that to get the maximum benefit from CUDA it's best to first find efficient ways to [9] sequential code. By applying Amdahl's Law [9] we can determine the maximum expected speedup from moving sections of sequential code to execute in parallel. NVIDIA note [9] that to maximise the speedup it's worthwhile spending effort increasing larger regions of code to be parallelised. CUDA compatible GPUs can be found in a wide range of devices from desktop computers to laptops and more recently mobile devices such as tablet computers and phones [10]. This allows developers to utilise massively parallel processing in previously restricted domains and crucially improve the performance of their applications whilst preserving portability due to the prevalence of NVIDIA GPUs. Additionally CUDA applications can scale at

runtime to utilise all available processing units so as to achieve the best possible runtime on the available hardware.

Since 2007 finding efficient CUDA implementations and parallel mappings of selected algorithms has been an active and ongoing area of research. There have been seven major releases of the CUDA toolkit along with four major hardware revisions; Tesla, Fermi, Kepler and Maxwell (see Section 2.4.1). In 2008 Tokyo Tech announced [11] the first GPU powered supercomputer to enter the list of top 500 supercomputers worldwide using GPGPU to achieve this. The following year NVIDIA released the first major hardware revision to the platform (Fermi) which significantly improved the speed of the GPU but also releaxed some of the tight memory coalescing restrictions (see Section 2.3.2) imposed by the first hardware generation vastly increasing the programmability of the platform. In 2011 the National Supercomputing Center announced [12] the world's fastest supercomputer Tianhe-1A based on NVIDIA GPUs. The Tianhe-1A used a total of 7168 NVIDIA Tesla GPUs to run molecular dynamics simulations at 1.87 petaflops per second [12]. In 2012 NVIDIA announced the Kepler hardware architecture bringing further CUDA advancements including dynamic parallelism (see Section 2.4.1). In 2012 NVIDIA also announced a virtualised GPU cloud solution known as GRID [13] allowing developers to access the power of the GPU on cloud based platforms such as Amazon Web Services (AWS). In 2014 NVIDIA released the most recent hardware revision of CUDA Maxwell [14]. Maxwell brought continued speed improvements along with an additional energy efficiency. CUDA has been successfully applied to a wide range of problems across multiple domains including medical imaging [15], computational finance [16], bioinformatics [17] and many other areas. CUDA success stories tout significant execution speedups over optimised sequential counterparts, each improving the viability of general-purpose GPU computing.

The simplest parallel implementations can easily offload entire computationally expensive regions of an application to the GPU using CUDA. However this method can require costly memory transfers to and from the GPU which can increase the execution time resulting in marginal speedups when compared to sequential counterparts. This simple implementation only requires minimal effort to port regions of an application as opposed to redesigning an entire application to execute

in parallel. Libraries such as Thrust [18] provide high level interfaces based on the Standard Template Library (STL) to perform common methods such as sorting without requiring detailed knowledge of CUDA programming.

Although CUDA abstracts the underlying GPU architecture, fully utilising and scheduling the GPU is non-trivial. Along with a hierarchical memory system, CUDA imposes many restrictive limitations which must be strictly adhered to in order to attain maximum speedups and performance. As a result, many existing sequential and even parallel algorithms must be redesigned in order to conform to the restrictive parallel GPU architecture. To attain the best performance it is often necessary that the entire application is executed in parallel on the GPU to avoid the aforementioned memory transfers. This can result in a significantly more complex implementation, increased development time and unforeseen parallelisation issues. The complexity of implementing existing algorithms on the GPU depends heavily on the resources used, interaction between processes and control flow of the algorithm. Some algorithms (such as basic image processing) can be classified as *embarrassingly parallel* when little effort is required to split up the process into parallel tasks and are often easily ported to the GPU. Executing in parallel can also bring unexpected scheduling difficulties as some algorithms can be highly sequential thus prohibiting parallelisation and greatly increasing the effort required to implement an efficient CUDA solution that executes faster than a optimised sequential counterpart. In the worst case, regions of algorithms that cannot be easily executed in parallel must still be executed on the GPU to avoid the time penalty of memory transfers. NVIDIA provide a set of comprehensive best practices to help developers port and implement existing and new algorithms on the GPU using CUDA [9]. However, deviating from these strictly defined best practices can lead to severe performance issues such as warp serialisation which imposes a harsh time penalty by executing regions of parallel code sequentially, often negating the performance benefit of executing in parallel.

In summary, developing an efficient parallel implementation is highly dependent on the input algorithm. Although a simple parallel implementation can be easily implemented, the benefits of executing in parallel are often hindered by poor performance. Some problems can be easily parallelised and others require significant changes to adapt sequential regions of the algorithm to execute in parallel without scheduling issues. For maximum speedups all features of the GPU must be utilised requiring detailed knowledge of the GPU however; this is not always possible.

#### 1.3 Motivation

Due to the aforementioned complexities pertaining to GPU development, the motivation behind this thesis is to explore and find efficient parallel mappings of existing and new algorithms on the GPU using NVIDIA CUDA. We place particular emphasis on metaheuristics, image processing and designing reusable techniques and mappings that can be applied to other problems and domains. By extending recent contributions we start by focusing on Ant Colony Optimisation (ACO) and move on to new parallel applications of ACO and image processing.

#### 1.3.1 Metaheuristics

Ant Colony Optimisation is a population-based metaheuristic that has proven to be the most successful ant algorithm for modelling discrete optimisation problems including the Travelling Salesman Problem (TSP) [19]. However, when modelling the TSP, as the number of cities to visit increases, so does the computational time required to construct tours. This problem necessitates the need for a parallel implementation in order to reduce the execution time and increase performance. Many of the nature inspired heuristic approaches for solving optimisation problems may seem intrinsically and even embarrassingly parallel. Dorigo and Stützle remark [19] that for many applications ACO solutions often rival the best in class, however, as previously mentioned, finding efficient parallel implementations to exploit the GPU hardware is non-trivial. Recent contributions from Cecilia et al. [20] and Delévacq et al. [21] have shown that adopting a data-parallel approach can better utilise the GPU. However the speedups attained are relatively low, and both implementations fail to utilise CPU optimisations and only apply their solution to the TSP. Motivated by the high quality of solutions produced by ACO and the recent parallel GPU developments we focus on extending and improving data-parallel techniques whilst utilising CPU optimisations in parallel.

#### 1.3.2 Image Processing

Edge detection is one of the most fundamental operations in computer vision and image processing as other tasks (such as image segmentation, object recognition and classification) can depend upon edge characterisation. It is crucial that the process of edge detection should result in a precise characterisation of the image features. Hence, edge detection must be both reliable and efficient. Edge detection differs according to whether an image is color or not. Novak and Shafer [22] found that about 90% of edges in color images are also edges in terms of their gray values. However, the remaining 10% of edges in color images can not be so characterised. Thus, many color edge detection algorithms have been proposed (see [23,24,25] for examples). In spite of this, there has been little research into developing efficient parallel implementations aside from traditional algorithms such as the Canny edge detection algorithm [26]. Luo and Duraiswami [27] and Ogawa et al. [28] both present GPU implementations of the Canny algorithm. Luo and Duraiswami [27] note that over 75% of the runtime is spent applying edge thresholding to improve the quality of edge maps. However, neither implementation considers using color images to improve the quality of edges detected.

#### 1.4 Contributions & Thesis Guide

As previously mentioned this thesis focuses on finding efficient parallel mappings and optimisations of the Ant Colony Optimisation metaheurisite and image processing algorithms on the GPU using NVIDIA CUDA and is based on the publications [1, 2, 3, 4]. We omit a single related work section in favour of providing detailed related sections. Our primary contributions made and guide to this thesis are outlined as follows:

- In Chapter 2 we provide additional background on parallel GPU development and give an overview of the hardware of the GPU, the CUDA programming model and recent CUDA hardware advancements.

- In Chapter 3 we present an improved data-parallel approach for mapping the Ant System algorithm to the GPU for solving the Travelling Salesman

Problem. We detail a novel implementation of a parallel warp-level roulette wheel selection algorithm called Double-Spin Roulette which is able to significantly outperform the execution time of existing parallel and sequential contributions whilst matching the quality of sequentially generated solutions. Our results show a speedup of up to 8.5x faster than the best existing GPU implementation and up to 82x faster than the sequential counterpart.

- In Chapter 4 we show how existing mappings of ACO on the GPU are unable to compete against their sequential counterpart when common optimisation strategies such as the use of candidate sets are employed. We explore three distinct candidate set parallelisation strategies for execution on the GPU. We show that by extending our previous data-parallel and warp-level approach we were able to efficiently integrate the use of a candidate set to reduce the overall execution time against both sequential and parallel counterparts. Our results show a speedup of up to 18x faster than the sequential counterpart while the best existing implementations struggle to maintain a speedup

- In Chapter 5 we present the first implementation of a parallel ACO-based edge detection algorithm on the GPU using NVIDIA CUDA. By further extending our data-parallel and warp-level approach we map individual ants to thread warps allowing multiple ants to execute on each CUDA block thus exploiting the GPU hardware and was able to yield the fastest execution times. Consequently, we increase the viability of ACO-based edge detection. Our approach is also able to produce variable edge widths that can produce stylised edge maps. Our results show a speedup of up to 150x faster than the sequential counterpart

- In Chapter 6 we propose a new method for quantifying color information so as to detect edges in color images using the volume of a pixel in the HSI color space. We detail a novel GPU implementation featuring an efficient parallel edge thinning algorithm that precomputes all potential thinning outcomes based on surrounding pixel data and storing the results in a look up table. We show that our method can improve the accuracy of detection, withstand greater levels of noise in images and decrease the execution time thus attaining

a speedup against related implementations. When comparing the execution times of our new color edge detection algorithm against the Canny edge detection algorithm our results show a speedup of up to 5x faster than the best performing GPU implementation and up to 20x faster than the sequential counterpart.

• In Chapter 7 we conclude this thesis and give direction for potential future work based on our research and findings.

## CHAPTER 2

#### General-purpose computation on the GPU using CUDA

#### 2.1 Introduction

In Chapter 1.1 we introduced the modern unified GPU and outlined how recent advancements have facilitated the development of the next generation of general-purpose computation on the GPU (GPGPU). By fully harnessing the power of a massively parallel processor, developers can significantly improve the performance of their applications on low-cost GPU hardware now available in most laptops, desktops and recently even mobile devices (including tablet computers). CUDA has since been applied to a wide range of problems across multiple domains.

In Chapter 1.2 we introduced CUDA, a parallel architecture designed for executing applications in parallel on the new unified GPU architecture. In this thesis we focus on finding efficient parallel mappings of existing algorithms to the massively parallel GPU using CUDA. It is important to fully understand the architecture of the modern massively parallel GPU and CUDA programming model before further discussing our primary contributions. In this chapter we provide background information on the GPU and CUDA detailing: the hardware of a CUDA compatible GPU, the CUDA programming model including how it must be utilised when developing parallel applications and the considerations that must be taken into account when developing for parallel execution on the GPU, and recent advancements made to the GPU hardware, the CUDA software toolkit and support for new processor architectures (notably ARM).

#### 2.2 CUDA hardware

First and foremost a CUDA compatible GPU is a separate processing unit that runs alongside the CPU. A modern desktop computer may be equipped with a single GPU or multiple GPUs depending on the configuration. A high-end desktop NVIDIA GPU can be purchased for around £500 and easily added to a standard motherboard. This enables developers to conveniently upgrade the GPU or add GPU support irrespective of the rest of their system. It is important to note that the GPU runs asynchronously to the CPU and therefore work can be distributed between the CPU and GPU [29]. Work can either be executed on the GPU blocking the CPU or executed on the GPU and asynchronously notify the CPU the work has completed. Typically an application will use one of two methods when scheduling work to the GPU. The first method relies upon a high level of parallelism in an application and uses the GPU alongside the CPU in parallel. The second method is suited to an application where events must strictly execute sequentially and each step is dependent on the previous. A computationally expensive region of the application is executed on the GPU, halting execution on the CPU, until the GPU has completed the unit of work. Both methods highlight the concept of using the GPU as a coprocessor alongside the CPU.

Since the introduction of the unified GPU, the typical architecture of a CUDA-compatible GPU consists of a scalable array of threaded streaming multiprocessors (SM), each containing a subset of stream processors (SP) that share control and instruction logic [5]. The number of SMs varies between devices with low-end devices having far fewer than high-end devices and CUDA applications scale transparently to the number of SMs available. The combination of multiple SMs form a CUDA block and the number of SMs required to constitute a block varies between each generation of CUDA. Each SP can also be known as a CUDA core and the total number of CUDA cores per device has increased significantly since the launch of the first generation of CUDA GPU. For example, the first flagship CUDA GPU (8800GTX) was equipped with 128 CUDA cores and this has risen to 2688 CUDA cores for the latest flagship CUDA GPU (Titan). From this we can see that the massively parallel architecture has increased over time with more CUDA cores

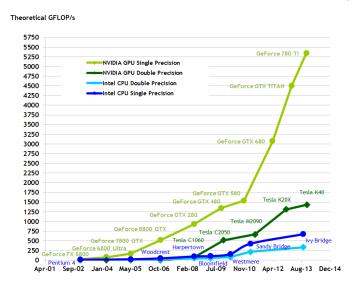

now available for parallel execution. There has also been considerable continued improvements to the clock rate, available memory, memory speed and bandwidth. In Fig. 2.1 we show the increase in floating point performance over the last 10 years on Intel CPUs and consumer level GeForce GPUs [30]. NVIDIA note that the dramatic increase in floating point performance on the GPU is due to the GPU specialising in graphics and therefore highly parallel intensive computation. For this reason the GPU assigns more transistors to data processing [30]. The major jumps in GPU performance of single and double precision data correspond to each major GPU hardware release for example from Fermi to Keppler (580 to 680)

Figure 2.1: A comparison of the floating point performance.

Each GPU has access to a variety of memory types each possessing a range of different properties such as size, speed, location, volatility and built-in caching. In Section 2.3.2 we will discuss the implications this has on the software model and the affect on application performance. Each GPU has its own high-speed physical memory on the PCB of the GPU and the memory space of the GPU is separate to that of the CPU. Data available on the host (CPU) must be transferred to the device (GPU) as the device is unable to access the host memory space. The size of physical memory available on the PCB varies depending on the device and as expected high-end devices typically provide more memory. The current flagship Tesla GPU provides 6GB of high-speed GDDR5 memory.

#### 2.3 The CUDA programming model

As previously mentioned, CUDA allows developers to execute methods in parallel directly on the GPU using a parallel programming interface. These parallel methods are known as *kernels* and are defined using the specifier *\_\_global\_\_* at the start of the method signature. When a kernel method is executed, the application moves execution from the host (CPU) to the device (GPU) [5]. NVIDIA note that unlike a conventional C function, a CUDA kernel is executed N times by N parallel CUDA threads [30]. It it important to note that kernels execute asynchronously and as a result kernels cannot return values. However, as expected, kernels can interact and write to memory but sequential execution must be blocked if subsequent stages depend on the results so as to avoid race condition synchronisation issues (see 2.3.3).

In the following subsections we will describe how kernels execute in parallel using the block and thread model, the memory types available for CUDA threads and execution synchronisation. Within each subsection we will also discuss common implementation issues and design considerations. We direct the reader to the NVIDIA programming guide for additional information regarding CUDA [30].

#### 2.3.1 Blocks and Threads

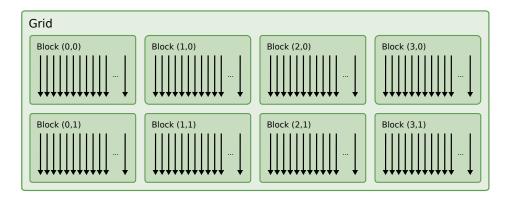

When a kernel method is executed, the execution is distributed over a *grid* of *thread* blocks as illustrated below in Fig. 2.2. Each of the thread blocks contains a subset of parallel CUDA threads which all in turn execute the kernel method.

Figure 2.2: A two-dimensional arrangement of 8 thread blocks within a grid.

#### **Blocks**

Within the CUDA grid, thread blocks can be arranged into a one-dimensional, two-dimensional or three-dimensional formation [30] (an example of a two-dimensional arrangement can be seen in Fig. 2.2). Each thread block contains a number of parallel threads that can only directly interact with threads within the thread block. Each block has a unique position in the grid and this can be determined at run time by each thread. The number of thread blocks and their dimensional arrangement can be defined by the application before or after compilation and will vary depending on the usage. For example, when working with images, a 2-dimensional arrangement is best suited as this matches the two-dimensional array holding the pixel data (although a one-dimensional array could be used with additional calculations to determine the position of the block within the grid).

NVIDIA note [30] that thread blocks must be required to execute independently and this is key to the mapping of thread blocks to SMs. There can be no inferred or presumed order of execution and parallelism between thread blocks. As a result each block must be self contained. The number of thread blocks chosen for each kernel execution should be sufficiently high so as to utilise all of the parallel cores available. During execution we must assume that each block could be the first or the last block to execute. This execution independence allows blocks to be distributed across a variable number of processing elements and executed in parallel [30]. However, as multiple blocks can execute in parallel we must be aware of data integrity when accessing memory outside of the block thus necessitating the use of atomic operators (see 2.3.3) that respect the order of access. Farber notes [29] that NVIDIA's insistence on thread block independence might also be indicative of transparent scheduling execution across multiple devices in future releases.

#### Threads

Within each thread block is a collection of parallel threads. Older cards such as the G80 can support up to 768 parallel threads per block and more recent Fermi cards increased that limit to 1024. The total number of threads per kernel execution is equal to the number of threads per thread block multiplied by the

number of thread blocks. For example executing 128 thread blocks each with 1024 threads would result in 131072 threads each executing the same kernel. Each parallel thread is only able to communicate with other threads in that block and this is facilitated by shared memory. Within a block, threads execute in parallel in smaller sub-blocks known as warps. Each thread warp contains either 16 or 32 threads depending on the compute version and generation of CUDA GPU. There is no guarantee as to what order the warps will execute in; however, within a warp threads can communicate directly with each other using warp level primitives such as \_ballot(). As with thread blocks, the number of threads per block is configurable at runtime but each thread block must have the same number of threads. As a general rule, CUDA applications must keep the GPU busy and achieve a high level of occupancy. NVIDIA recommend that at least 64 threads are used per thread block [30]. Threads can also be configured into a one-dimensional, two-dimensional or three-dimensional formation. The arrangement of threads within a thread block is user configurable and certain configurations may suit particular applications [30].

For optimum performance, all threads within a warp must follow the same execution path. Developers must pay attention to the control flow of each warp so as to avoid branching conditional statements. For example, if statements may cause the warp to branch as CUDA cannot process the resulting multiple paths from this branching statement in parallel. When threads follow different execution paths within a warp, the execution is serialised resulting in a loss of parallelism within the warp until after the branching region has finished execution. This process of warp serialisation due to branching is known as warp divergence and must be avoided if possible. To avoid warp divergence we must ensure that all threads strictly follow the same control flow throughout the kernel execution even if this results in performing redundant computation to align all threads within the warp.

The CUDA programming model allows applications to support fine-grained parallelism capable of instantiating hundreds of thousands of parallel threads for execution on a single task. In contrast CPU applications often apply coarse-grained parallelism typically focusing a significantly lower number of threads on distinctly different tasks. As each of the threads executes the same kernel, we can classify this parallel model of execution as single-program, multiple-data (SPMD) [5].

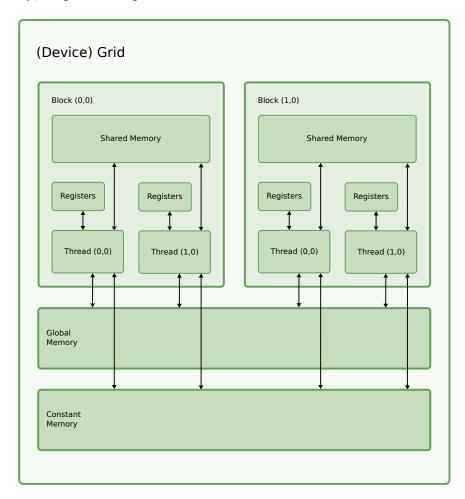

#### 2.3.2 Memory types

CUDA exposes a set of different memory types to developers, each with unique properties that must be exploited in order to maximise performance [30]. Each CUDA thread has access to all of the different memory types but it is up to the developer to know which memory type is applicable for their particular application and how best to utilise each of the different types for performance gains. In Fig. 2.3 we present an overview of the hierarchical CUDA memory model highlighting each of the different available memory types and the accessibility of each memory type. We will now review each of the memory types, detailing their unique properties, accessibility, scope and implementation considerations.

Figure 2.3: An overview of the hierarchical CUDA memory model.

#### Register Memory

The first type of memory is 32-bit register memory. Registers are the fastest form of storage and each thread within a block has access to a set of fast local registers that exist on-chip. However, the accessibility of register memory is severely limited as each thread can only access its own registers. As the number of registers per block is limited, blocks with many threads will have fewer registers per thread. If a thread block uses a high number of threads, each using multiple local variables, the block may use more registers than available. In this case the registers will spill into the significantly slower region of local memory resulting in loss of performance. During compilation the number of spilled registers is presented to the developer and care must be taken to keep this number to a minimum. A kernel may fail to execute if there are not enough registers or shared memory for at least one block to execute [30]. In short, registers are the fastest of all the available memory types but are in limited supply, must be managed to avoid register spilling and do not allow inter-thread communication facilitating the need for additional memory types.

#### Shared Memory

For inter-thread communication within a thread block, shared memory is the fastest available memory type and must be used to achieve optimum performance. As with register memory, shared memory exists on-chip but is accessible to all threads within the block. This increases the scope of accessibility from register memory and thus facilitates fast inter-thread communication within the thread block without moving to off-chip memory. Shared memory is slower than register memory and if a thread can execute without sharing information with other threads, shared memory should not be used over register memory as this will reduce the execution performance. When possible, shared memory should also be cached into local register memory to avoid additional memory reads (providing the data in shared memory is constant and using additional variables will not exhaust the number of registers available). Shared memory is extremely important for increasing application performance. When used correctly, data can be cached locally as to reduce the dependency on additional expensive reads to slower off-chip memory.

The amount of shared memory per block is limited to 16KB or 48KB depending on the split of memory with the L1 cache [29]. Shared memory is arranged into banks and developers must carefully manage access to these banks. Fermi CUDA devices with compute version 2.0, shared memory is arranged as 32 consecutive 32 bit (4 byte) wide memory banks each with a bandwidth of 32 bits per cycle. This configuration is designed to permit each bank to load a single 4 byte word per clock cycle. For optimum performance, each thread in a warp (32 threads) must access a single 4 byte word from a different memory bank. If two or more threads attempt to access a single memory bank this is known as a bank conflict and all subsequent memory requests are serialised. To avoid serialisation, developers must explicitly manage all shared memory reads within a warp to access different memory banks. If just a single thread accesses the same bank as another thread within the warp, this will trigger a bank conflict. An exception to this rule is when all threads within a warp access the same word in a memory bank. In this case the value can be broadcast to all the threads within the warp using a single read operation opposed to multiple serialised reads [29]. Since compute version 3.0, the bank size is now adjustable and can be either set as 4 or 8 bytes. This allows developers to easily support double precision words without bank conflicts [30].

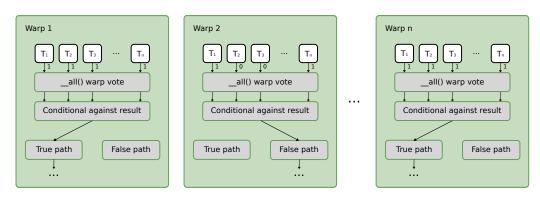

#### Inter-thread communication without shared memory

Aside from shared memory, threads can also communicate directly within a warp by using warp vote functions. The three available warp vote functions allow threads in a warp to communicate to other threads in the warp via a reduction-and-broadcast operation [30] and without using shared or global memory. The mechanism behind the warp vote is simple; each of 32 threads pass an integer into the function and the result is then broadcast to all threads in the warp. An example warp vote operation is the *all* function. The result of the *all* warp vote is only true if all of the 32 threads input a positive integer. In Fig. 2.4 we illustrate multiple threads across thread warps within a single thread block each executing the all warp vote function at the start of the kernel. In the first warp, the input into the vote function from each thread is positive and therefore the warp vote returns true. As a result all threads within the first warp follow the true execution path and so the warp

does not branch or trigger warp divergence. In the second warp the input contains non-positive integers and so the warp vote returns false. The warp then proceeds to follow the false execution path also without branching. The warp vote functions provide one of the most useful techniques to help reduce warp divergence and thus serialising the warp. Warp voting permits all threads in the same warp to check that a condition has been met before performing a potentially branching statement. By balloting threads within a warp, we can dynamically change the execution path depending on the result of the thread consensus reached via voting functions within the warp without using shared memory or serialising the warp.

Figure 2.4: An example of multiple threads across separate thread warps executing the CUDA all warp vote function and following different execution paths.

As of compute version 3.0, newer Kepler GPUs can also communicate directly with other threads within their warp using the new warp shuffle functions [31]. The four available warp shuffle functions (shuffle, shuffle up, shuffle down and shuffle xor) allow single 4 byte variables to be transferred simultaneously between threads in each warp. As with warp vote functions, warp shuffle functions do not require the use of shared memory and only use one instruction to share variables as opposed to three [32]. The shuffle method must be executed twice sequentially when transferring larger 8 byte variables such as doubles. By using the shuffle function the amount of shared memory used per warp can be reduced which can result in a higher occupancy [32]. As each of the threads within the warp execute in parallel, there is no need to synchronise the warp after performing either a warp vote or warp shuffle thus further increasing the performance of the warp level operations.

### Global, Constant and Texture Memory

For inter-block communication, larger data sets, and persistent memory, threads have access to global (DRAM), constant and texture memory. The lifetime of global, constant and texture memory is the lifetime of the application (as opposed to register and shared memory which is only the duration of a single kernel execution). If an application requires memory persistence between multiple kernel executions, global, constant or texture memory must be used. From the device and within kernel execution, global memory has read and write access where as constant and texture memory only has read access. Constant and texture memory can only be written to by the host (CPU) prior to kernel execution. Since the release of compute version 2.0, access to global memory is now automatically cached using L1 and L2 caches. As previously mentioned, the amount of shared memory and the size of the L1 cache can be adjusted by the developer according to the use case and requirements [29]. For example, if each each thread block requires a large amount of shared memory the size of the L1 cache can be reduced to accommodate this. If global memory is accessed frequently (or randomly) the size of the L1 cache can be increased to hide the access latency by reducing the amount of shared memory per block. Texture and constant memory also benefit from caching, but the initial load will still be significantly slower than accessing shared or register memory.

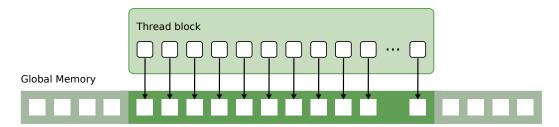

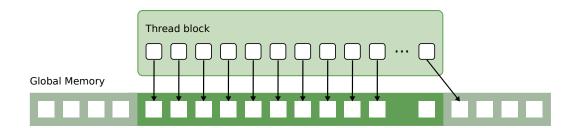

Two of the CUDA implementation best practices detailed by NVIDIA [31] are to minimise redundant accesses to global memory and if possible to coalesce these global memory accesses. One common practice to minimise redundant access to global memory is to cache global memory locally in shared memory. A simple approach can instruct each thread to copy a value from global memory into shared memory. After the initial load all subsequent global memory read accesses would be directed to the shared memory array thus avoiding excessive costly global lookups. If required, any changes can be written from shared memory back into global memory at any point during the execution of a kernel. By replacing slow global memory accesses with fast shared memory reads, the execution time of a kernel can be significantly reduced. To further increase the execution performance, these initial reads can also be coalesced. When global memory reads are coalesced, a

single memory transaction can return an entire section of memory for a warp as opposed to issuing multiple reads for each thread. Prior to the release of compute 2.0, coalescing global memory accesses required strict alignment of threads to consecutive memory addresses within a section of memory. After compute 2.0 these restrictions were relaxed and the penalties of not coalescing memory reads were mitigated by the inclusion of an additional L1 cache. To further reduce the number of memory reads issued, each thread within a warp should access the same 128 byte region of global memory (as illustrated in Fig. 2.5 and Fig. 2.6).

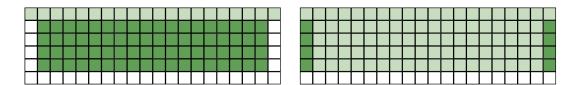

Figure 2.5: An example of all threads within a block accessing the same 128 byte region of global memory resulting in a single 128 byte load.

Figure 2.6: An example of the threads from the same block accessing two 128 byte regions of memory resulting in two separate global memory loads.

To summarise: when designing a kernel for parallel CUDA execution, it is important to fully and properly use the three main memory types (register, shared and global). Kirk and Hwu [5] note, global memory is the slowest of all the memory types but often large, whereas shared memory is fast but extremely limited and must be explicitly managed in order to maximise performance. Register memory is the fastest of all the memory types but has limited accessibility restricted to each thread, and exhausting the number of registers can result in costly spilling.

### 2.3.3 Synchronisation

Key to the design of any parallel algorithm for execution on the GPU is synchronisation. As there are multiple memory types and levels of abstraction (from CUDA threads to thread blocks), there are also multiple types of parallel synchronisation. In the following subsections we review each of the synchronisation types available.

### Warp Synchronisation

Threads within a warp execute non-branching regions of kernels in parallel. There is implicit synchronisation between all threads as long as the warp execution path does not diverge. However, NVIDIA suggest avoiding warp-synchronous programming as this can lead to synchronisation issues and race conditions; furthermore, implementations often incorrectly assume that the number of threads in a warp will always be 32 [31]. NVIDIA note that although warp-synchronous implementations might function correctly now, changes to the CUDA toolchain and CUDA capable hardware might may easily break these implementations. However, warp synchronous programming can lead to improved execution times.

### Thread Synchronisation

There is no guarantee as to what order warps will execute, necessitating the usage of additional block synchronisation techniques where inter-thread communication is required across multiple warps. The method \_\_syncthreads() will block the execution of threads within a block up to a point in the kernel. After all threads have reached the \_\_syncthreads() method the kernel execution will resume ensuring block synchronisation. The \_\_syncthreads() method should not be called within an if-thenelse statement unless all threads follow the same execution path as this may cause a deadlock resulting in the kernel timing out and failing to execute successfully. As of compute 2.0 there are three variants of the \_\_syncthreads() method that allow similar voting functionality to warp vote. An example of a \_\_syncthreads() method variant is \_\_syncthreads\_count(). This variant method takes an integer from each of the threads in the block, synchronises all threads to a point and returns the number of non-zero integers input to each of the threads.

### **Block synchronisation**

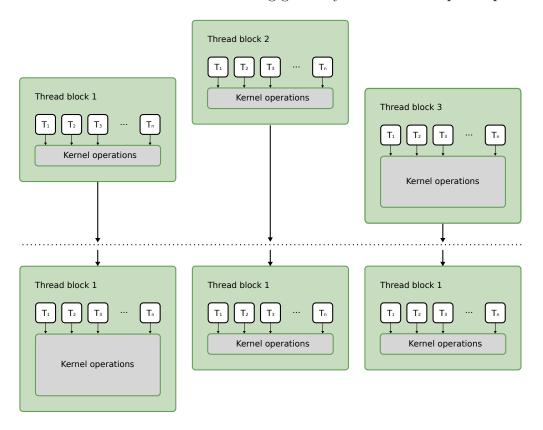

There is no built-in support for block synchronisation in CUDA during kernel execution. This allows the GPU to execute each block independently and adjust the block execution scheduling dynamically according to the number of CUDA cores available on the GPU. As a result there is no guarantee as to the execution order of blocks or which blocks are currently executing at any given point and developers should not presume ordering. In Fig. 2.7 we illustrate a simple alternative to global synchronisation by splitting one kernel into two smaller kernels. A blocking synchronisation method *cudaDeviceSynchronize()* is used to ensure that all thread blocks have fully completed their kernel execution. A second kernel is then scheduled for execution by the host with the guarantee that the previous kernel had finished execution therefore achieving global synchronisation up to a point.

Figure 2.7: An example of global thread block synchronisation via executing the function cudaDeviceSynchronize() to explicitly synchronise all blocks.

One restriction with this method of achieving global synchronisation is that additional expensive memory operations may be required. As previously mentioned, the lifetime of shared memory is limited to the scope of a single kernel. Therefore the contents of shared memory will have to be copied to global memory in the first kernel and back from global memory to shared memory in the second kernel. To avoid this issue, other methods have been proposed to achieve global synchronisation such as using atomic operations, but such practices are discouraged by NVIDIA as they could be unsupported after subsequent new releases of CUDA.

# **Atomic Operations**

As there is no guarantee as to which order threads, warps and thread blocks will execute, additional *atomic* operations are provided to read and update global memory values without interruption from other threads accessing the same region of memory. Atomic operations perform read-modify-write on a region of global memory. Each operation locks a region of memory until the initial operating thread has read the value, modified the value and written the value back to global memory [30]. After the lock is placed on a region of memory, all other threads must wait until this lock is removed before accessing the same region of memory [33].

A simple example of an atomic operator is atomicAdd. The atomicAdd operation reads a word in global memory, adds a value to this word and writes the value back to global memory (read-modify-write). Without atomic operations two threads could potentially read the same value simultaneously, independently modify the value and write back to global memory with the second write overwriting the value of the first write. In this scenario the value written by the first thread is lost. By using the atomicAdd method, the second thread would wait until the first thread has fully completed the read-modify-write operations ensuring the value written to global memory is the initial read value for the second thread. Atomic operations are more expensive than read and write global memory accesses. The use of atomic operations should be limited to the absolute minimum to avoid scenarios where multiple threads are waiting on a single region of memory. For example, instead of using atomicMax, threads within a block should first use shared memory to compute the maximum value so as to avoid each thread using an atomic operation.

### 2.3.4 OpenCL

After the release of CUDA, an alternative open standard general-purpose programming API was released under the name OpenCL (Open Computing Language) [5]. Initially Developed by Apple and subsequently the Khronos Group, OpenCL allows developers to harness the GPU and multi-core CPUs for general-purpose parallel computation. However unlike CUDA, OpenCL has multi-vendor and multiplatform support thus allowing parallel code to be executed on AMD and NVIDIA GPUs as well as x86 CPUs [5]. This gives OpenCL the advantage of portability between platforms. However as Kirk and Hwu [5] note, OpenCL programs can be inherently more complex if they choose to accommodate multiple platforms and vendors. Developers must use different features from each platform to maximise performance and so multiple execution paths dependent on the platform and vendor must be included. This can result in each platform achieving a different execution time depending on the input algorithm, mapping and usage of platform specific APIs that may give an advantage to that specific platform. Kirk and Hwu also note that the design of OpenCL is influenced heavily by that of CUDA and as a result working with OpenCL can be very similar to CUDA. As with CUDA, regions of the application that execute in parallel are encapsulated in kernels. OpenCL also has a similar concept of CUDA blocks and threads which have been renamed to Work group and Work item respectively. The current index of the block within the grid of all blocks has also been renamed as the NDRange. To facilitate support for multiple devices across platforms and vendors, OpenCL introduces the concept of an OpenCL context. Each device is assigned to a context and work is scheduled for execution in a queue for that context [5]. For additional information regarding OpenCL, we direct the reader to the Khronos Group OpenCL specification [34].

In this thesis we choose to use NVIDIA CUDA as the primary programming model along with NVIDIA GPUs. This is due to current API capabilities, better development and profiling tools and improved GPU hardware. This unfortunately comes with the sacrifice of portability between GPU vendors however as we previously noted the two parallel models are very similar. We envisage that our parallel implementations could be ported to use OpenCL and ATI GPUs if necessary.

### 2.4 Recent advances

In this section we detail the recent advances made to CUDA since 2007.

### 2.4.1 Fermi, Kepler and Maxwell

CUDA is now a proven technology in its sixth major toolkit release and as of September 2014, fourth major hardware revision (Maxwell). From the initial CUDA compatible GPU, each major hardware revision has made significant improvements to the speed, number of CUDA cores, on-chip cache sizes and clock speed of the GPU. Improvements have also been made to the programmability of the CUDA applications reducing the need for strict memory coalescing and providing better automatic caching of global memory accesses. In Table 2.1 we compare the high-end CUDA devices showing the considerable improvements from 2006 to 2014 [35].

|                  | Tesla                | Fermi                 | Kepler                | Maxwell  |

|------------------|----------------------|-----------------------|-----------------------|----------|

| Card Name        | 8800 GTX             | GTX 580               | GTX 680               | GTX 980  |

| Chip             | G80                  | GF110                 | GK104                 | GM204    |

| CUDA Cores       | 128                  | 512                   | 1536                  | 2048     |

| Base Clock       | 575 MHz              | 772 MHz               | 1006 MHz              | 1126 MHz |

| Memory Clock     | 900 MHz              | 2004 MHz              | 6008 MHz              | 7010 MHz |

| Shared Memory    | 16 KB                | 48 KB                 | 48 KB                 | 96 KB    |

| Memory           | 768 MB               | 1536 MB               | 2048 MB               | 4096 MB  |

| Memory Bandwidth | $86.4~\mathrm{GB/s}$ | $192.4~\mathrm{GB/s}$ | $192.3~\mathrm{GB/s}$ | 224.3 MB |

Table 2.1: A comparison of consumer level CUDA GPUs for each hardware revision.

### Fermi

In an NVIDIA whitepaper, Patterson describes how the architectural hardware advancements from Tesla to the Fermi architecture are as significant as NV40 (pre-CUDA) to Tesla [36] and goes on to define the top innovations made in Fermi. Of these innovations significant improvements have been made in: the performance (and quality) of floating point operations; on-chip cache sizes; and the performance of atomic instructions. Fermi also introduced Error Correcting Codes (ECC) to

main and cached memory alongside a new instruction set for increased performance. The increase in floating performance results in double precision floats now running only half the speed of single. As previously mentioned Fermi increased the on-chip cache size from 16KB shared memory to 48KB of configurable L1 cache with an additional 768KB of L2 cache. By increasing the shared memory size, Patterson describes how applications with lower levels of parallelism can hide DRAM latency more efficiently. Additionally the L2 cache alleviates the need for complex shared memory caching patterns for applications with random access patterns albeit with a slight penalty for the L2 latency. By reducing the time to switch contexts, Fermi allows concurrent kernel execution with bi-directional parallel memory transfers. This benefits asynchronous applications where the results of one kernel are not necessarily used immediately, or in the case where memory can be transferred in small chunks, a kernel is invoked whilst the next transfer is being completed. The results from the kernel can then be transferred back to the host whilst the next chunk of memory is transferred across. Fermi also boasts atomic instructions which are around 5x to 20x faster than the Tesla as they can be stored in the L2 cache.

### **Kepler**

Following on the success of the Fermi architecture, Kepler tripled the number of CUDA cores, increased GPU performance and decreased power consumption. NVIDIA note that the architecture of Kepler extends the same programming model as Fermi and so the best practices discussed for Fermi are applicable to Kepler. Kepler also introduced warp shuffle methods (for communication between threads in a warp), increased parallelism and increased shared memory bandwidth. The second generation of Kepler GK110 devices also introduced dynamic parallelism. Dynamic parallelism allows kernels to launch additional kernels and thus nest kernel execution. This allows the GPU to dynamically create additional work starting with a coarse grained first kernel and executing finer grained kernels for specific regions when required. A simple example would be processing an image with mostly empty regions: the first kernel would identify regions of interest, executing nested kernels when areas of interest are discovered. Kepler also allows up to 16 kernels to execute simultaneously so further increasing parallelism.

#### Maxwell

Maxwell is the most recent CUDA compatible GPU architecture initially announced by NVIDIA in mid-February 2014 with the GeForce 7 Series. A second more powerful iteration was released in mid-September 2014 along with the new GeForce 9 Series of GPU. As with Kepler, Harris notes [35] that developers will not have to change their existing CUDA implementations to benefit from the increased performance and efficiency benefits. However, to fully utilise the architecture developers should make use of the new hardware and software features available.