## Circuit Optimisation using Device Layout Motifs

Yang Xiao

Ph.D.

University of York Electronics

July 2015

## Abstract

Circuit designers face great challenges as CMOS devices continue to scale to nano dimensions, in particular, stochastic variability caused by the physical properties of transistors. Stochastic variability is an undesired and uncertain component caused by fundamental phenomena associated with device structure evolution, which cannot be avoided during the manufacturing process. In order to examine the problem of variability at atomic levels, the '*Motif*' concept, defined as a set of repeating patterns of fundamental geometrical forms used as design units, is proposed to capture the presence of statistical variability and improve the device/circuit layout regularity. A set of 3D motifs with stochastic variability are investigated and performed by technology computer aided design simulations.

The statistical motifs compact model is used to bridge between device technology and circuit design. The statistical variability information is transferred into motifs' compact model in order to facilitate variation-aware circuit designs. The uniform motif compact model extraction is performed by a novel two-step evolutionary algorithm. The proposed extraction method overcomes the drawbacks of conventional extraction methods of poor convergence without good initial conditions and the difficulty of simulating multi-objective optimisations. After uniform motif compact models are obtained, the statistical variability information is injected into these compact models to generate the final motif statistical variability model.

The thesis also considers the influence of different choices of motif for each device on circuit performance and its statistical variability characteristics. A set of basic logic gates is constructed using different motif choices. Results show that circuit performance and variability mitigation can benefit from specific motif permutations. A multi-stage optimisation methodology is introduced, in which the processes of optimisation are divided into several stages. Benchmark circuits show the efficacy of the proposed methods. The results presented in this thesis indicate that the proposed methods are able to provide circuit performance improvements and are able to create circuits that are more robust against variability.

# Contents

| A        | bstra | ict            | ii                                                                                                                                           |

|----------|-------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Li       | st of | Figur          | es vii                                                                                                                                       |

| Li       | st of | Table          | s xx                                                                                                                                         |

| A        | ckno  | wledgr         | nents xxiii                                                                                                                                  |

| D        | eclar | ation          | xxiv                                                                                                                                         |

| н        | ypot  | hesis          | xxv                                                                                                                                          |

| 1        | Intr  | roduct         | ion 1                                                                                                                                        |

|          | 1.1   | Motiv          | ation $\ldots \ldots \ldots$ |

|          | 1.2   | Aims           | and Objectives                                                                                                                               |

|          | 1.3   | Organ          | isation of The Thesis                                                                                                                        |

| <b>2</b> | Tra   | nsistoi        | Scaling and Variability 6                                                                                                                    |

|          | 2.1   | Scalin         | g of Transistor Device                                                                                                                       |

|          |       | 2.1.1          | Scaling Principle                                                                                                                            |

|          |       | 2.1.2          | Scaling Challenges                                                                                                                           |

|          | 2.2   | Trans          | stor Variability Classification                                                                                                              |

|          |       | 2.2.1          | Random/Stochastic Variation                                                                                                                  |

|          |       | 2.2.2          | Systematic Variation                                                                                                                         |

|          | 2.3   | Source         | es of Stochastic Variability 17                                                                                                              |

|          |       | 2.3.1          | Random Dopant Fluctuation                                                                                                                    |

|          |       | 2.3.2          | Line Edge Roughness 19                                                                                                                       |

|          |       | 2.3.3          | Interface Roughness                                                                                                                          |

|          |       | 2.3.4          | Polysilicon Grain Boundaries                                                                                                                 |

|          | 2.4   | -              | t of Transistor Variability on Device/Circuit Performance and Monte<br>Simulation                                                            |

|          |       | 2.4.1          | Impact on Delay Time    23                                                                                                                   |

|          |       | 2.4.1<br>2.4.2 | Impact on Leakage Current       23                                                                                                           |

|          |       | 4.1.4          | impact on Dearage Current                                                                                                                    |

|          |                         | 2.4.3 Monte Carlo Simulation (Statistical Simulation)    | 25        |  |  |  |

|----------|-------------------------|----------------------------------------------------------|-----------|--|--|--|

|          | 2.5                     | Summary                                                  | 26        |  |  |  |

| 3        | Mo                      | tifs Physical Simulation                                 | <b>27</b> |  |  |  |

|          | 3.1                     | Device Simulation and Methodology                        | 28        |  |  |  |

|          |                         | 3.1.1 CMOS Device Fabrication Flow                       | 28        |  |  |  |

|          |                         | 3.1.2 3D Device Structure Simulation Methodology in TCAD | 32        |  |  |  |

|          | 3.2                     | Motifs Design Methodology                                | 42        |  |  |  |

|          |                         | 3.2.1 Layout Consideration and Variability               | 42        |  |  |  |

|          |                         | 3.2.2 Motif Concept                                      | 46        |  |  |  |

|          |                         | 3.2.3 Motifs Design                                      | 50        |  |  |  |

|          | 3.3                     | TCAD Statistical Variability Simulation Methodology      | 53        |  |  |  |

|          |                         | 3.3.1 Line Edge Roughness Modelling                      | 53        |  |  |  |

|          |                         | 3.3.2 TCAD Statistical Simulation Approach               | 58        |  |  |  |

|          | 3.4                     | Experiment Results and Discussion                        | 59        |  |  |  |

|          |                         | 3.4.1 Motif Verification                                 | 60        |  |  |  |

|          |                         | 3.4.2 Statistical Motif Simulation Results               | 63        |  |  |  |

|          | 3.5                     | Summary                                                  | 66        |  |  |  |

| 4        | Evolutionary Algorithms |                                                          |           |  |  |  |

|          | 4.1                     | What is an Evolutionary Algorithm?                       | 79        |  |  |  |

|          | 4.2                     | Operation of an Evolutionary Algorithm                   | 80        |  |  |  |

|          |                         | 4.2.1 Representation                                     | 80        |  |  |  |

|          |                         | 4.2.2 Selection                                          | 80        |  |  |  |

|          |                         | 4.2.3 Reproduction                                       | 82        |  |  |  |

|          |                         | 4.2.4 Evaluation                                         | 88        |  |  |  |

|          |                         | 4.2.5 Termination Criteria                               | 88        |  |  |  |

|          | 4.3                     | Type of Evolutionary Algorithm                           | 89        |  |  |  |

|          |                         | 4.3.1 Genetic Algorithm                                  | 89        |  |  |  |

|          |                         | 4.3.2 Evolutionary Strategies                            | 90        |  |  |  |

|          |                         | 4.3.3 Evolutionary Programming                           | 91        |  |  |  |

|          |                         | 4.3.4 Genetic Programming                                | 91        |  |  |  |

|          |                         | 4.3.5 Multi-Objective Evolutionary Algorithm (MOEA)      | 92        |  |  |  |

|          | 4.4                     | Evolutionary Algorithm for VLSI Design                   | 93        |  |  |  |

|          |                         | 4.4.1 Charateristics of Problem Instances                | 93        |  |  |  |

|          |                         | 4.4.2 Problem Instances Decomposition                    | 94        |  |  |  |

|          |                         | 4.4.3 Application of EA on VLSI Design                   | 94        |  |  |  |

|          | 4.5                     | Summary                                                  | 97        |  |  |  |

| <b>5</b> | $\mathbf{Ext}$          | raction and Modelling Statistical Motifs Compact Model   | 99        |  |  |  |

|   | 5.1  | Device Compact Model and Extraction Method                                                                                                 | 100 |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   |      | 5.1.1 Device Compact Model                                                                                                                 | 100 |

|   |      | 5.1.2 Model Extraction and Optimisation Methodology                                                                                        | 108 |

|   | 5.2  | Two Step Evolutionary Algorithm Extraction Method                                                                                          | 109 |

|   |      | 5.2.1 Overview of Two Step Evolutionary Algorithm Model Extraction Method 1                                                                | 109 |

|   |      | 5.2.2 Representation $\ldots \ldots 1$          | 11  |

|   |      | 5.2.3 Selection Process                                                                                                                    | 112 |

|   |      | 5.2.4 Mutation Process $\ldots \ldots 1$ | 112 |

|   |      | 5.2.5 Motif Netlist Simulation                                                                                                             | 13  |

|   |      | 5.2.6 Fitness Evaluation $\ldots \ldots 1$      | 13  |

|   | 5.3  | Experiment Results and Analysis                                                                                                            | 16  |

|   |      | 5.3.1 Experiment Setting-up                                                                                                                | 16  |

|   |      | 5.3.2 Reference Device Extraction                                                                                                          | 16  |

|   |      | 5.3.3 <i>O</i> Shaped Device Extraction $\ldots \ldots 1$     | 118 |

|   | 5.4  | Statistical Device Layout Motif Compact Model Modelling                                                                                    | 122 |

|   |      | 5.4.1 Direct Statistical Compact Modelling methodology                                                                                     | 122 |

|   |      | 5.4.2 Statistical Compact Modelling Results and Verification 1                                                                             | 126 |

|   | 5.5  | Summary                                                                                                                                    | 128 |

| 6 | Cire | cuit Optimisation using Motifs and Evolutionary Algorithm 1                                                                                | 30  |

|   | 6.1  | Applying Motifs to Basic Logic Gates 1                                                                                                     | 131 |

|   |      | 6.1.1 Logic Gates Test                                                                                                                     | 131 |

|   |      | 6.1.2 Exhaustive Testing                                                                                                                   | 132 |

|   |      | 6.1.3 Results and Observations                                                                                                             | 133 |

|   | 6.2  | Multi-Stage Evolutionary Algorithm for Circuit Optimisation                                                                                | 145 |

|   |      | 6.2.1 Methodology                                                                                                                          | 145 |

|   |      | 6.2.2 First Stage EA Optimisation                                                                                                          | 148 |

|   |      | 6.2.3 Second Stage EA Optimisation                                                                                                         | 151 |

|   | 6.3  | Evolutionary Algorithm Verification                                                                                                        | 154 |

|   |      | 6.3.1 Benchmark Circuit I: XOR                                                                                                             | 154 |

|   | 6.4  | Benchmark Circuits Evaluation                                                                                                              | 155 |

|   |      | 6.4.1 Benchmark Comparison Circuits                                                                                                        | 155 |

|   |      | 6.4.2 Benchmark Circuit II: Half Adder                                                                                                     | 159 |

|   |      | 6.4.3 Benchmark Circuit III: Full Adder                                                                                                    | 61  |

|   | 6.5  | Summary                                                                                                                                    | 167 |

| 7 | Cor  | nclusions and Future Work 1                                                                                                                | .68 |

|   | 7.1  | Conclusions                                                                                                                                | 168 |

|   | 7.2  | Summary                                                                                                                                    | 169 |

|   | 7.3  | Future Work                                                                                                                                | 172 |

|   |      |                                                                                                                                            |     |

| Α  | NMOS Device TCAD Script       | 174 |

|----|-------------------------------|-----|

| в  | Model Parameters Definition   | 182 |

| С  | NMOS reference device netlist | 185 |

| Bi | bliography                    | 186 |

# List of Figures

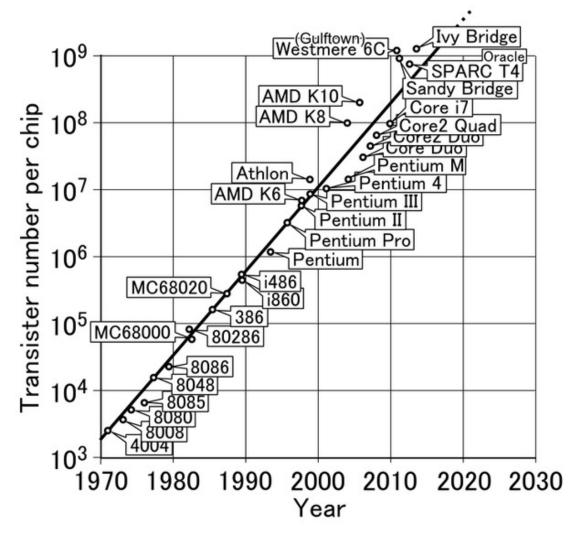

| 1.1 | A comparison of the transistor counts in various microprocessors, with a curve                    |    |

|-----|---------------------------------------------------------------------------------------------------|----|

|     | showing the projected counts following Moore's predictions of a doubling every                    |    |

|     | 24 months [4]                                                                                     | 2  |

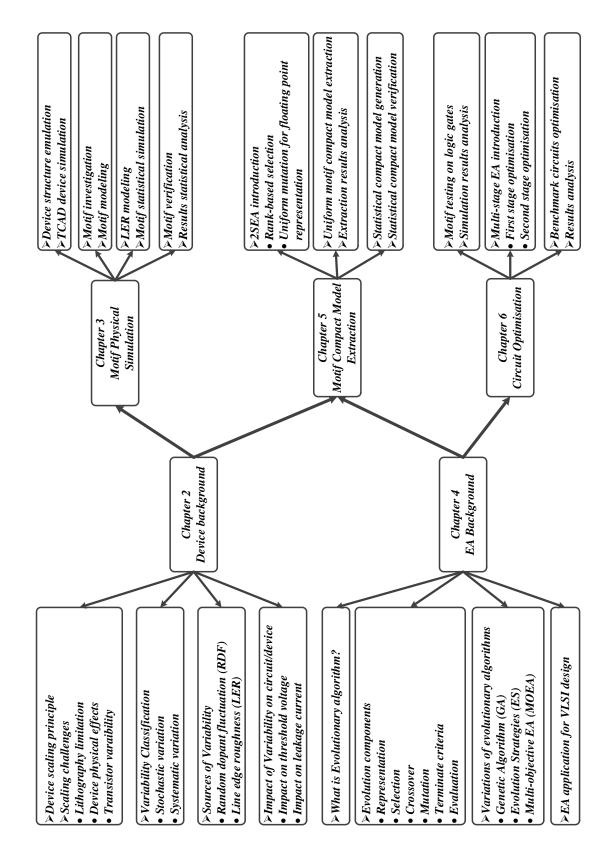

| 1.2 | The thesis organisation diagram, which summaries main chapters' topics, key                       |    |

|     | observations (represented by $\triangleright)$ and points of interest (represented by $\bullet).$ | 5  |

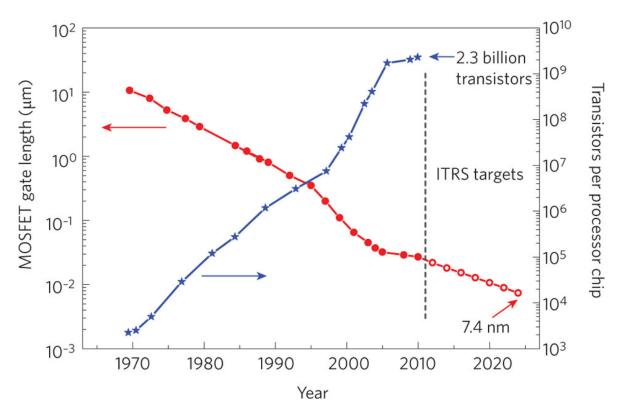

| 2.1 | Trends in device electronics. The number of transistor per processor chip has                     |    |

|     | increased (blue star line) as MOSFET device feature size scaling (red dot line).                  |    |

|     | Evolution of MOSFET gate length is represented by filled red circles and ITRS                     |    |

|     | predictions is shown by open red circles [9]                                                      | 8  |

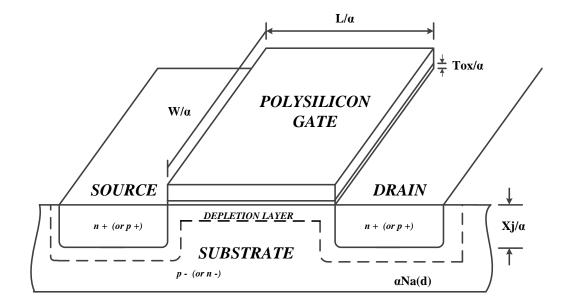

| 2.2 | A cross-sectional structure of scaled MOS device [11]                                             | 9  |

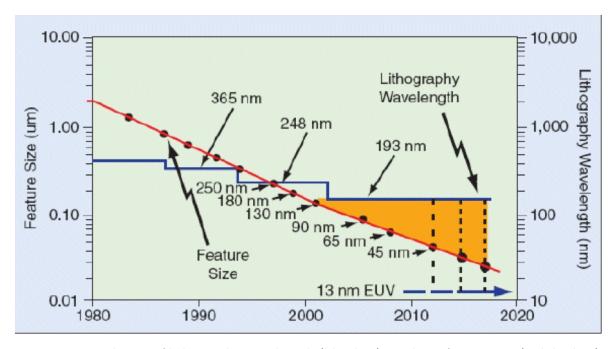

| 2.3 | Evolution of lithography wavelength (blue line) as silicon feature size (red dot                  |    |

|     | line) scaling. As devices scale to nanometer regions, manufacturability chal-                     |    |

|     | lenges "subwavelength gap" continue to grow. The illumination wavelength                          |    |

|     | (193 nm) is much greater than the feature size (45 nm and below) [14]. $\ldots$                   | 11 |

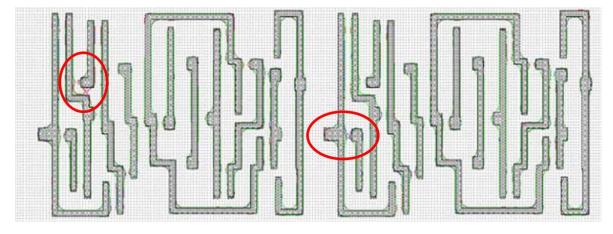

| 2.4 | An example of lithography simulation of flip-flop. Because of pattern distor-                     |    |

|     | tion, some of points in the layout are shorted and highlighted by red circle                      |    |

|     | [16]                                                                                              | 12 |

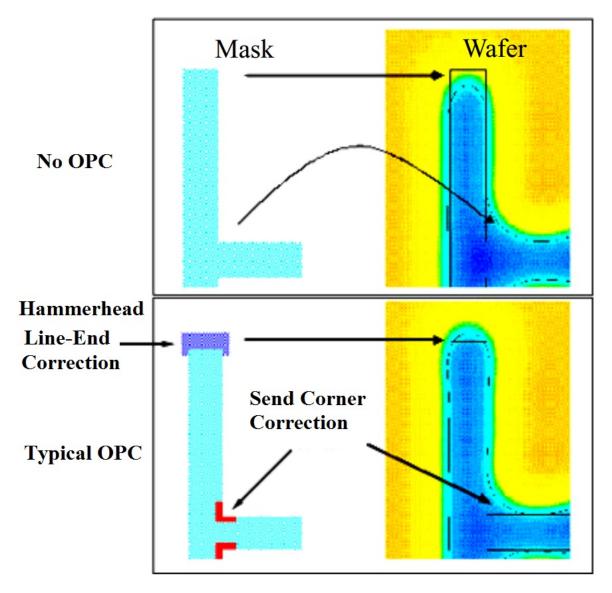

| 2.5 | The comparison of device layout pattern using OPC or no OPC $[17]$ . The case                     |    |

|     | where OPC correction is used obviously has higher yield than no OPC design.                       | 13 |

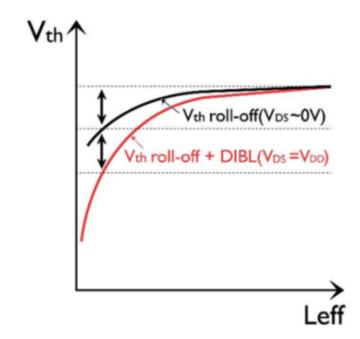

| 2.6 | Threshold voltage $V_{th}$ roll-off and drain induced barrier lowering (DIBL). $V_{th}$           |    |

|     | decreases as the channel length reduction. In addition to this, $V_{th}$ further                  |    |

|     | reduced when drain voltage increases is caused by DIBL [25]. $\ldots$ $\ldots$                    | 14 |

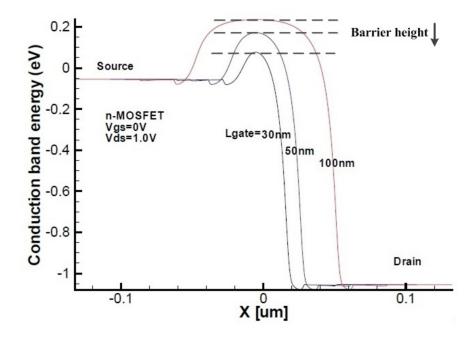

| 2.7 | Barrier height lowering due to channel length reduction [8]                                       | 14 |

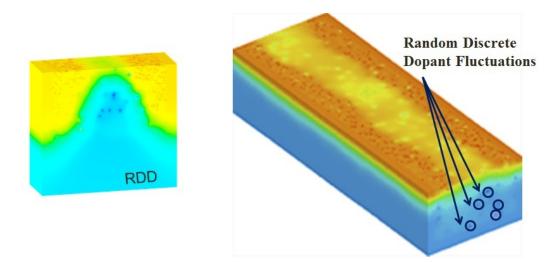

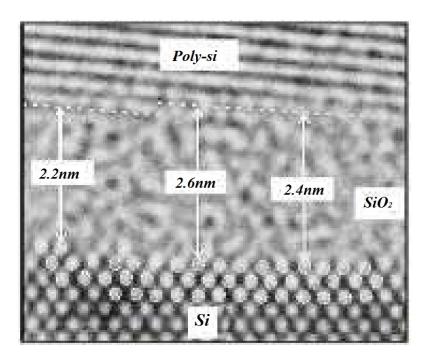

| 2.8  | Random discrete dopant fluctuations illustrated in 3D device structure [22].                      |    |

|------|---------------------------------------------------------------------------------------------------|----|

|      | It is impossible to perfectly control the exact quantity and position of dopant                   |    |

|      | atom while dopant atoms are being implanted into the silicon. These results in                    |    |

|      | exact differences in the electronic characteristics of two transistors, even both                 |    |

|      | are fabricated under the same conditions                                                          | 16 |

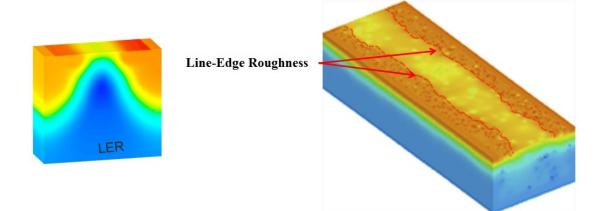

| 2.9  | Line edge roughness (LER) in 3D device structure [22]. The random deviation                       |    |

|      | between actual gate edges and ideal definition of gate edges is not avoided due                   |    |

|      | to the limitation of resolution in optical lithography. LER results in enhanced                   |    |

|      | lateral diffusion and effective channel length reduction                                          | 16 |

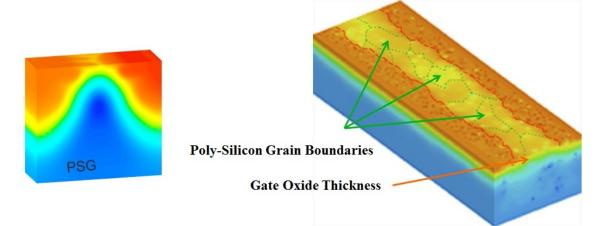

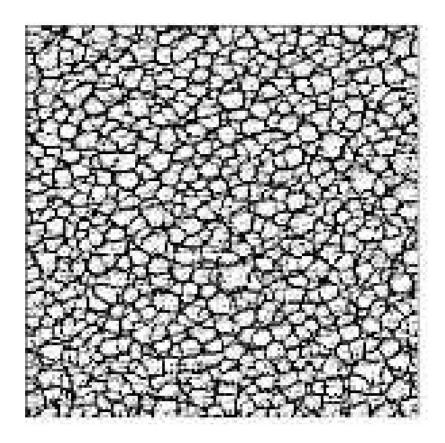

| 2.10 | Poly-silicon grain boundaries (PSG) and gate oxide roughness (TOX) in 3D                          |    |

|      | device structure [22]. PSG is another variability sources to affect on the channel                |    |

|      | current due to the random arrangement of grains within the gate material.                         |    |

|      | Additionally, with the gate oxide thickness scaled, TOX induced variation is                      |    |

|      | not ignored, especially TOX variation induced threshold voltage variation as                      |    |

|      | much as RDF below $30 \ nm$ technology [36]. $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$   | 17 |

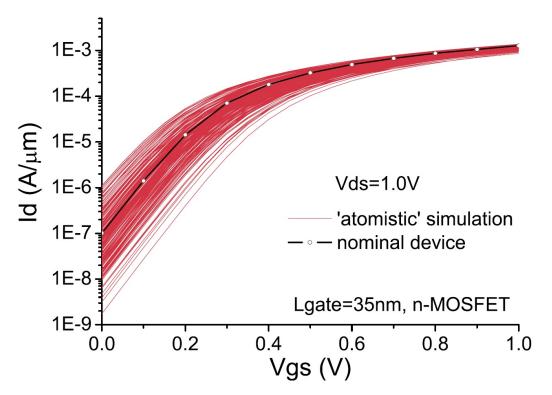

| 2.11 | $I_d\mathchar`-V_g$ characteristics for 35 $nm$ gate length NMOS subject to RDD, LER and          |    |

|      | PSG induced statistical variability[8]                                                            | 17 |

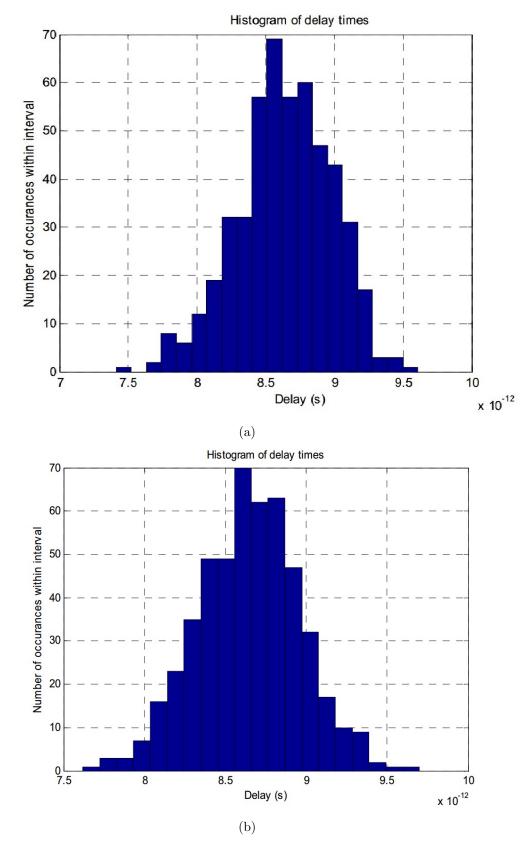

| 2.12 | The histogram of layout with different correlation delay measured from $500$                      |    |

|      | randomised instances [34]. Sub-figure (a) shows (the mean is 8.64ps and                           |    |

|      | standard deviation is $0.345$ ps) results from layout with higher correlation                     |    |

|      | $(\lambda = 0.07)$ ; and Sub-figure (b) design (the mean is 8.647ps and standard                  |    |

|      | deviation is 0.318ps) with low correlation ( $\lambda = 10$ ). Although mean of both              |    |

|      | cases remain similar, the standard deviation obviously reduces by $7.8\%~[34].$ .                 | 18 |

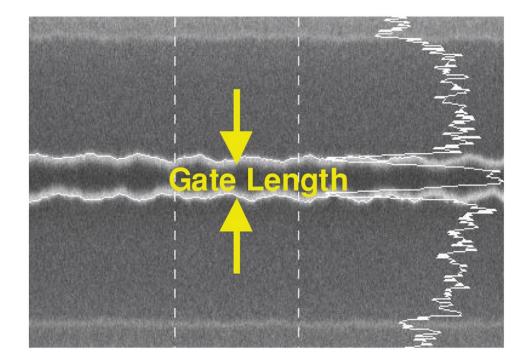

| 2.13 | SEM image of line edge roughness pattern [33]                                                     | 20 |

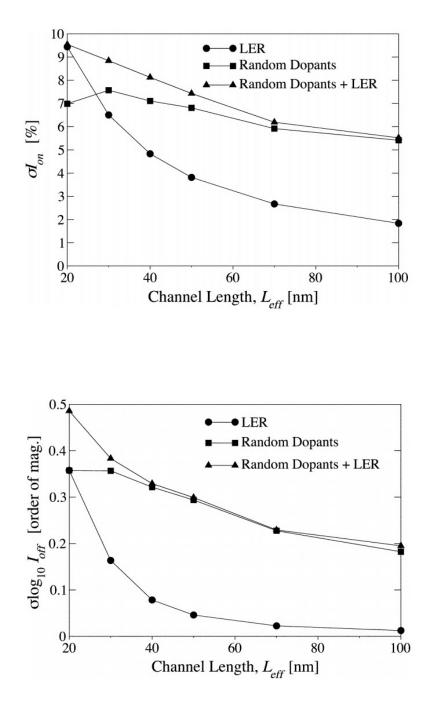

| 2.14 | Dependence of $\sigma I_{on}$ (represented by upper sub-figure) and $\sigma log(I_{off})$ (repre- |    |

|      | sented by bottom sub-figure) on the channel length for a set of device with                       |    |

|      | channel width 50 nm. As channel length reduction, the effect of LER on device                     |    |

|      | performance is much stronger [74]                                                                 | 21 |

| 2.15 | SEM image of interface roughness [40]                                                             | 22 |

| 2.16 | SEM micrograph of typical PSG from bottom [40]                                                    | 23 |

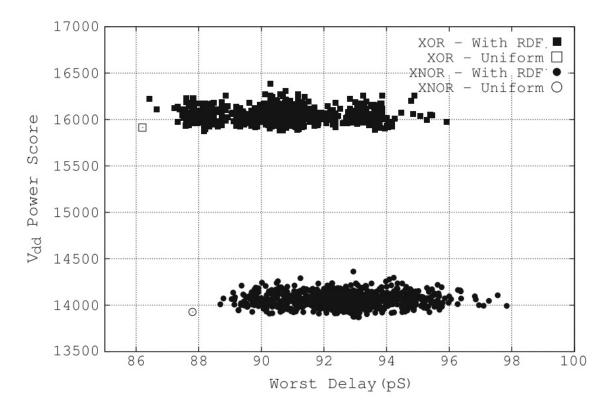

| 2.17 | Effect of intrinsic variability within 35 nm XOR and XNOR logic designs [93].                     | 24 |

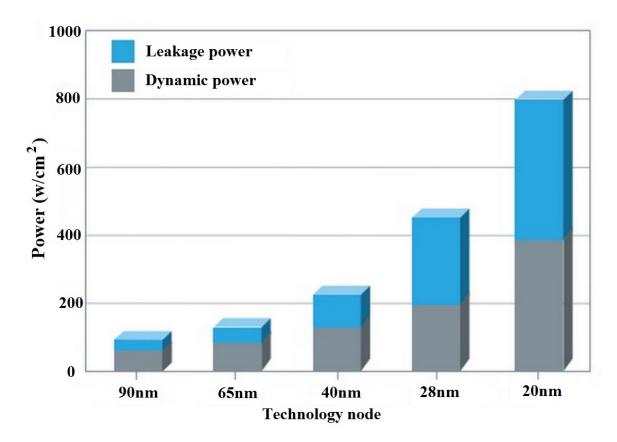

| 2.18 | Total power ratio evolution vs. technology node [39].                                             | 25 |

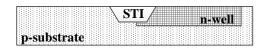

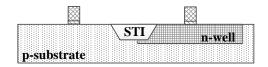

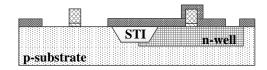

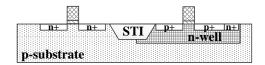

| 3.1  | Cross section of the wafer involved in forming the n-well[42]                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

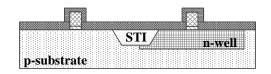

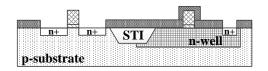

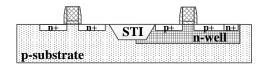

| 3.2  | Cross section of the wafer while forming ploysilicon and diffusion region<br>[42]                                                                                                                                                                                                                                                                                                                                                                                                                  | 31 |

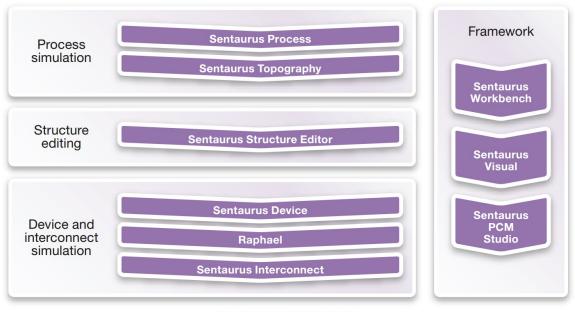

| 3.3  | The framework of Sentaurus TCAD Suite [81].                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 33 |

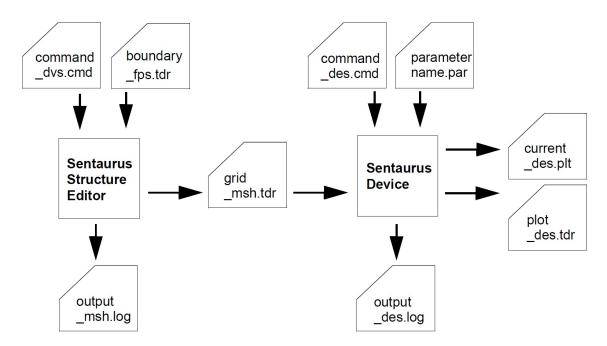

| 3.4  | Typical tool flow with device simulation using Sentaurus Device [44]. The creation of a device structure by process simulation (SP) or structure emulation (SSE) is followed by meshing using SM. Control of mesh refinement is handled automatically via the file _dvs.cmd. Then, SDEVICE is used to perform the electrical characteristics of the device simulation. Finally, the output from device simulation in 2D and 3D is visualized and the electrical characteristics are plotted by SV. | 36 |

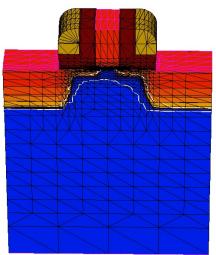

| 3.5  | A virtualized 3D NMOS transistor structure with meshing information, created<br>by TCAD tool.                                                                                                                                                                                                                                                                                                                                                                                                      | 37 |

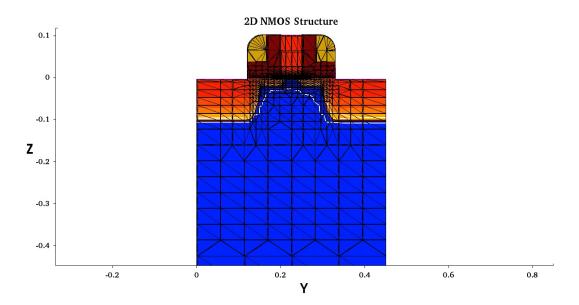

| 3.6  | 2D cross-section of front view NMOS transistor cut from Figure 3.5 shown<br>NMOS 3D structure                                                                                                                                                                                                                                                                                                                                                                                                      | 37 |

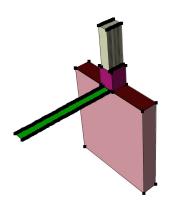

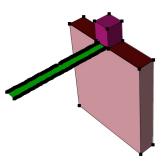

| 3.7  | 3D NMOS device with LER emulation steps (continued on Figure 3.8)                                                                                                                                                                                                                                                                                                                                                                                                                                  | 38 |

| 3.8  | Continued 3D NMOS device with LER emulation steps                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39 |

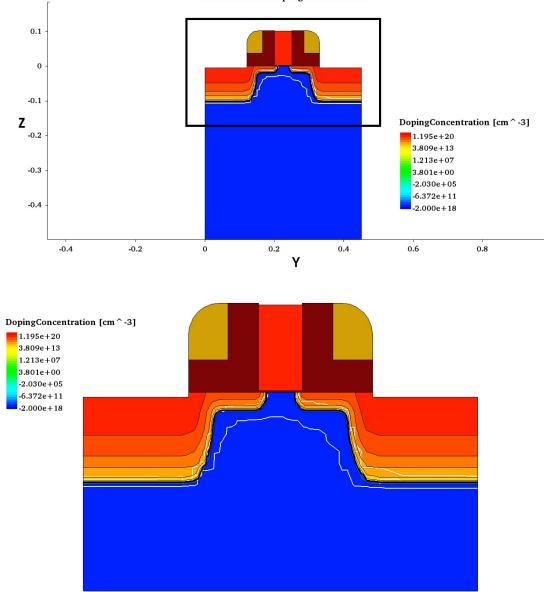

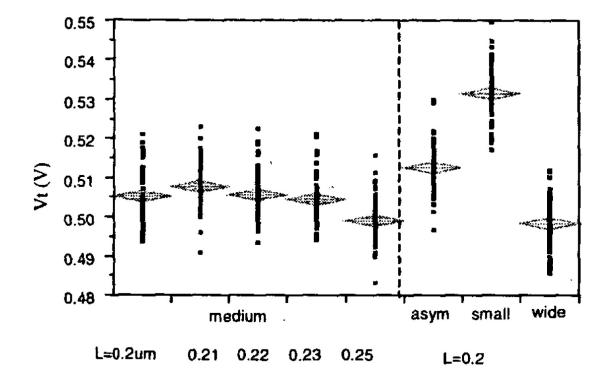

| 3.9  | The upper sub-figure is front view of 2D NMOS device with doping infor-<br>mation. The bottom sub-figure clearly shows the channel and source/drain<br>doping concentration.                                                                                                                                                                                                                                                                                                                       | 40 |

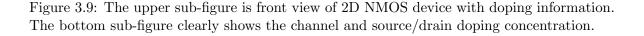

| 3.10 | This standard cell layout demonstrates how characteristic of device in the cell<br>is affected by stress due to STI width. STI width is context dependent which<br>determined by the distances of devices in neighbouring cells (active-to-active<br>spacing). Wider STI leads to greater distances and more compressive stress,<br>results in PMOS performance increase [51].                                                                                                                     | 42 |

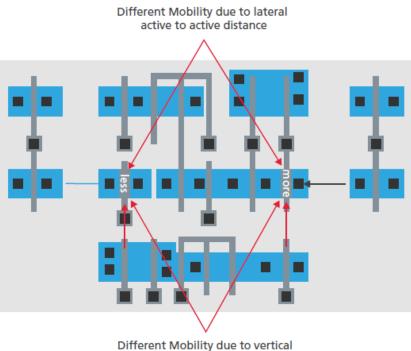

| 3.11 | In order to investigate the impact of LOD on device characteristics, four test<br>layout structures with different LOD (gate length 0.2 $\mu m$ and width 20 $\mu m$ )<br>are used (These test layout structures are taken from [54]). These layouts are<br>classified two types: symmetric and asymmetric placement; And symmetric                                                                                                                                                                | 49 |

| 3.12 | placement includes three layouts with different LOD                                                                                                                                                                                                                                                                                                                                                                                                                                                | 43 |

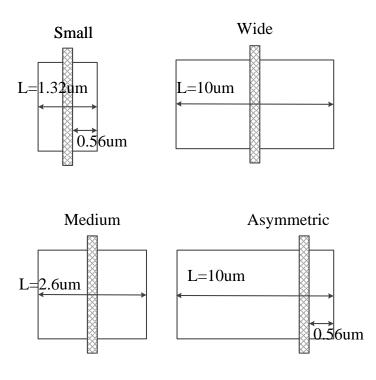

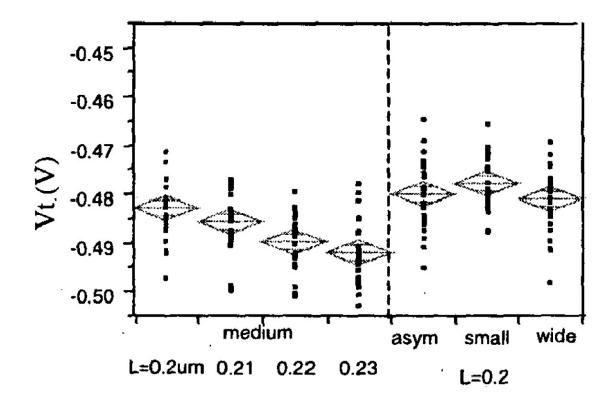

|      | The $V_{th}$ of device is significantly sensitivity to layout placement                                                                                                                                                                                                                                                                                                                                                                                                                            | 44 |

| 3.13 | PMOS $V_{th}$ vs. device layout (device layout as shown in [54]). Comparing to               |    |

|------|----------------------------------------------------------------------------------------------|----|

|      | NMOS devices, PMOS exhibits little sensitivity to layout placement variations                |    |

|      | since stress has a minimal effect on hole mobility [56]-[57]                                 | 45 |

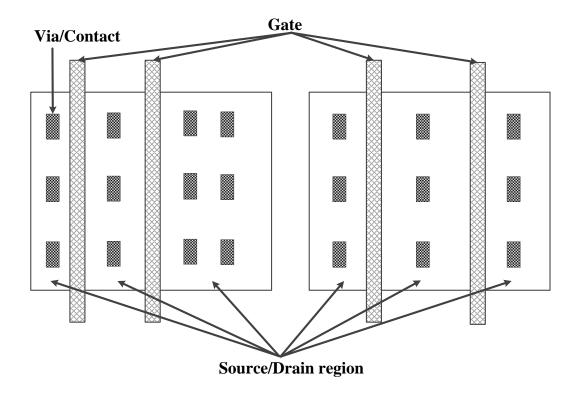

| 3.14 | Test structures with shared source/drain region is proposed. The left test                   |    |

|      | layout is designed to investigate the mismatch in two identical devices changing             |    |

|      | as two gates distance and the right layout placement is used for evaluating the              |    |

|      | relationship of parasitic capacitance in shared source/drain area                            | 46 |

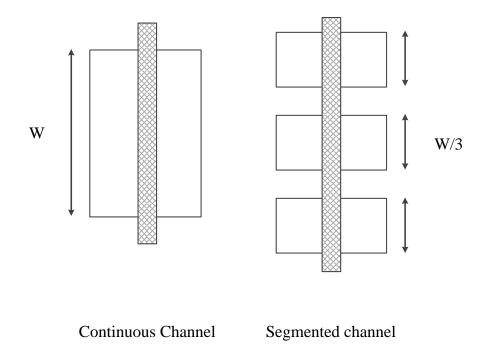

| 3.15 | Test structures with segmented channel [59]. In this case, a continuous channel              |    |

|      | device is separated into three devices with the same small width channel. The                |    |

|      | segment structure inspires one of layout placement structure used in this thesis,            |    |

|      | which $O$ shaped layout structure will be described in next section                          | 47 |

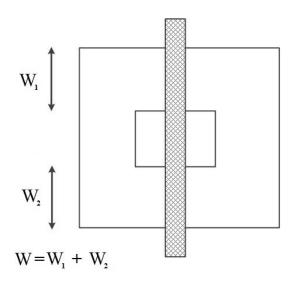

| 3.16 | The proposed $O$ shaped layout structure (Top view). $\ldots$ $\ldots$ $\ldots$ $\ldots$     | 47 |

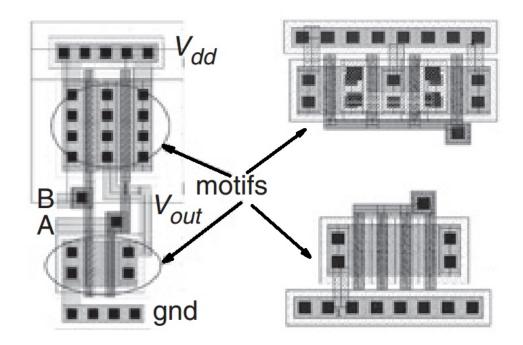

| 3.17 | Examples for layout motif. The left two layout motifs come from NAND2 gate                   |    |

|      | compact layout                                                                               | 48 |

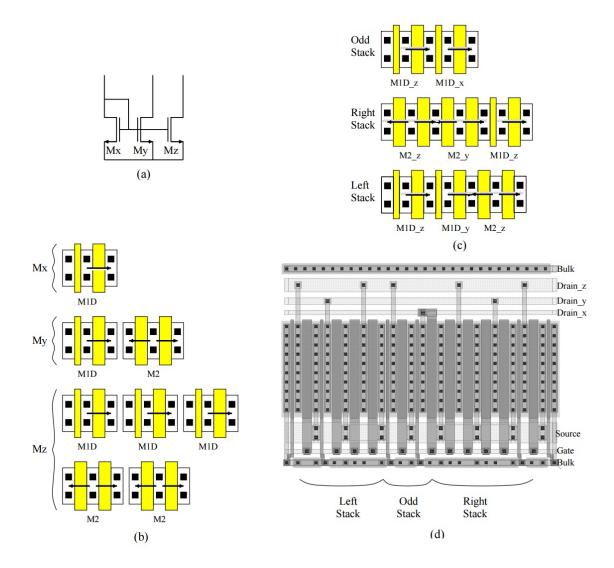

| 3.18 | As an example, consider a current mirror composed of three transistors $M_x$ ,               |    |

|      | $M_y, M_z$ shown in (a) [84]. The assigned motifs of each transistor are shown in            |    |

|      | (b). Based on literature [84] introduced optimisation algorithm, one motif from              |    |

|      | each is placed in the odd stack; and the other two stacks are then composed                  |    |

|      | by taking one motif alternatively from each transistor as shown in (c). (d)                  |    |

|      | shows the physical layout of the current mirror stack after abutting the three               |    |

|      | elementary stacks shown in (c) [84]                                                          | 49 |

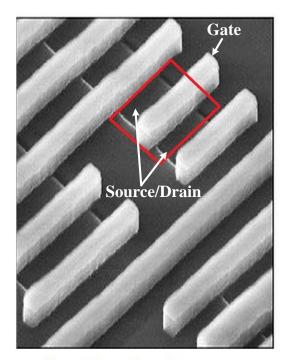

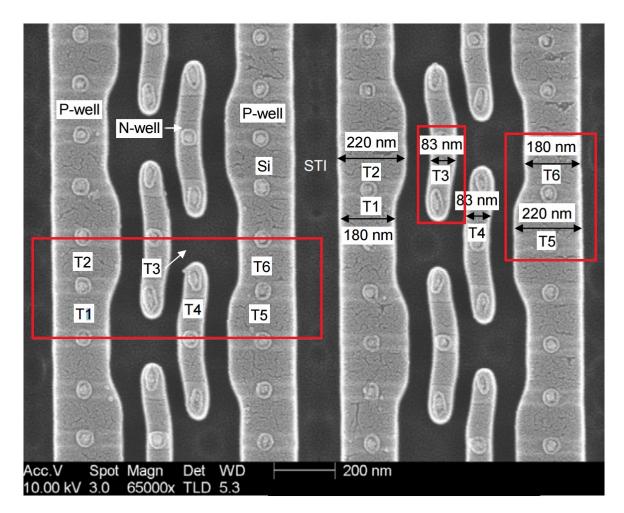

| 3.19 | Two examples of motif (shown in red rectangle) are taken from SEM image                      |    |

|      | of 32nm planar transistors and 22nm tri-gate transistors $\left[65\right],$ respectively. As |    |

|      | motif definition described, motif can be as small as a part of unit in tri-gate              |    |

|      | transistor or a single transistor                                                            | 50 |

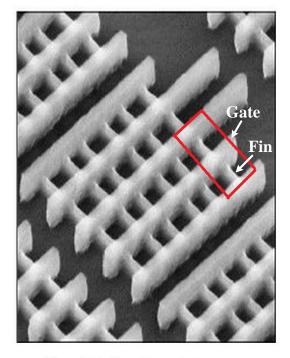

| 3.20 | Several motifs are illustrated by red rectangles from SRAM SEM image [66].                   |    |

|      | Comparing to motifs illustrated in Figure 3.19, motifs can be as large as the                |    |

|      | whole SRAM or the transistors-groupings from SRAM layout.                                    | 51 |

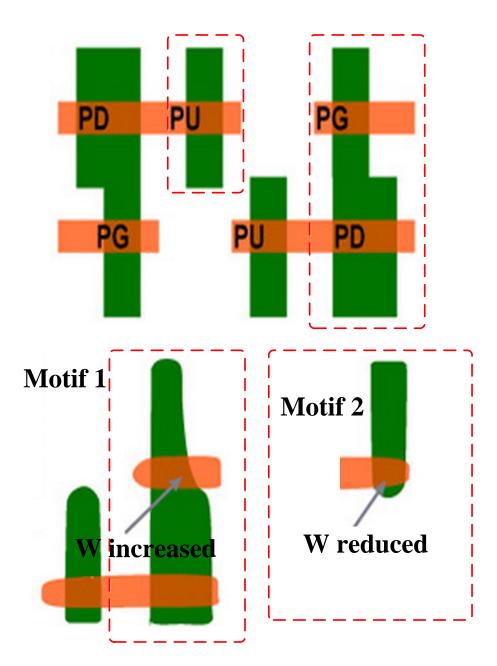

| 3.21 | Two motifs are proposed based on the fundamental repeating geometrical                       |    |

|      | forms from SRAM print image [67]. Some of unexpected layout placements                       |    |

|      | caused the SRAM performance degradation (as the bottom sub-figure shown                      |    |

|      | motifs layout) can be easily investigated by motif.                                          | 52 |

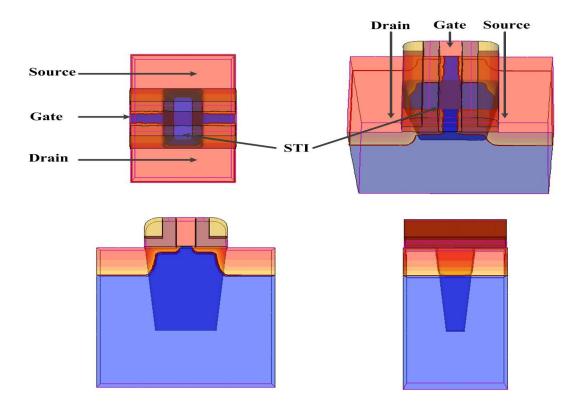

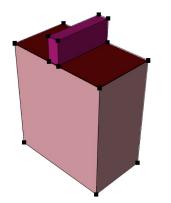

| 3.22 | In order to investigate the impact of series resistance and stress placing on gate   |    |

|------|--------------------------------------------------------------------------------------|----|

|      | due to LOD on transistor performance, long diffusion area motif is proposed.         |    |

|      | Top view (upper left), Front view (low left), Side view (lower right), 3D view       |    |

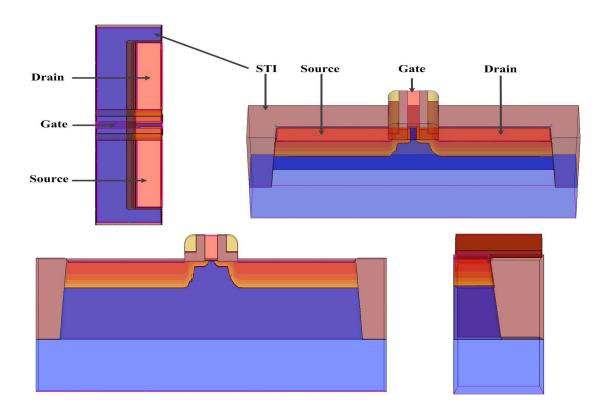

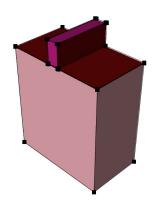

|      | (upper right)                                                                        | 54 |

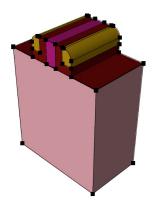

| 3.23 | Multi-finger motif (parallel gates) is a widely used the common unit in circuit      |    |

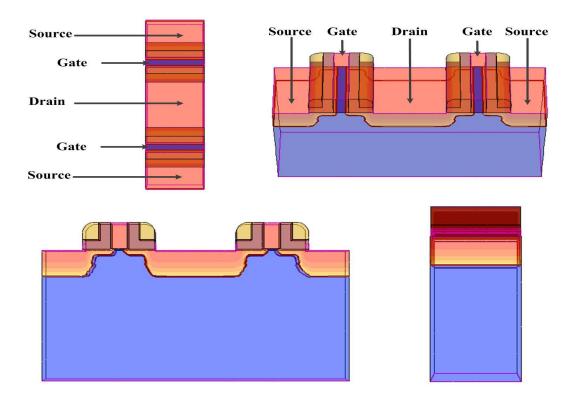

|      | design. As previously described, this motif provides a way to investigate the        |    |

|      | impact of LER-induced variation on two close gates. Top view (upper left),           |    |

|      | Front view (low left), Side view (lower right), 3D view (upper right)                | 55 |

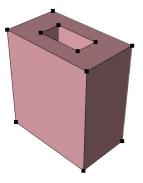

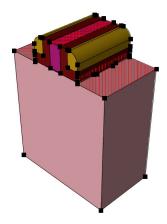

| 3.24 | ${\cal O}$ shaped motif is a complex and irregular layout placement that is inspired |    |

|      | from the channel segment. Top view (upper left), Front view (low left), Side         |    |

|      | view (lower right), 3D view (upper right)                                            | 56 |

| 3.25 | The comparison of the long diffusion motif with different LOD. As the S/D $$         |    |

|      | diffusion area increasing, the drain current deceases due to the S/D resistance      |    |

|      | value changed.                                                                       | 56 |

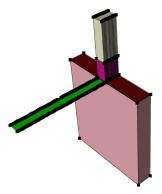

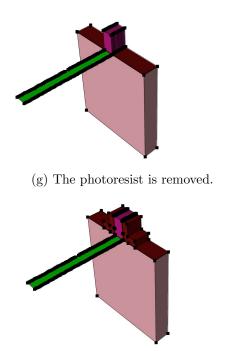

| 3.26 | $O$ shaped Motif 3D structure emulation processing without LER $\ .\ .\ .$ .         | 57 |

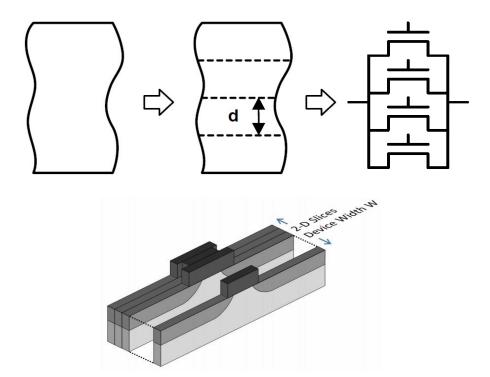

| 3.27 | The flow to divide a gate roughness into a set of narrow slices, where each slice    |    |

|      | is assumed to be ideal with no roughness [27]-[72]. Each slice has a unique          |    |

|      | gate length due to LER and the same width.                                           | 58 |

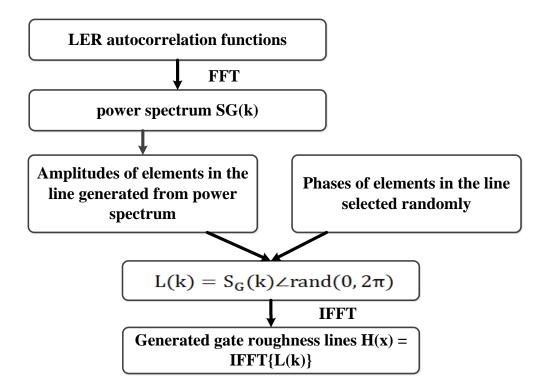

| 3.28 | The flow chart of LER generation.                                                    | 59 |

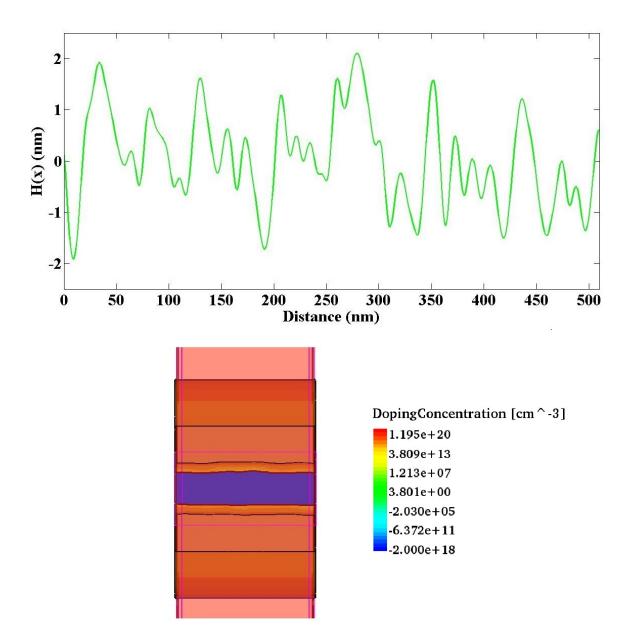

| 3.29 | The roughness of gate edge is generated using PSD method. The top subfigure          |    |

|      | shows the mathematical calculation gate edge line. And the application of the        |    |

|      | mathematical calculated line edge result in TCAD device structure is depicted        |    |

|      | in the bottom subfigure                                                              | 60 |

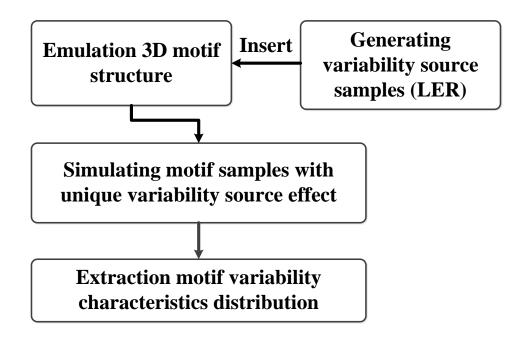

| 3.30 | The flow chart of motifs TCAD statistical simulation.                                | 61 |

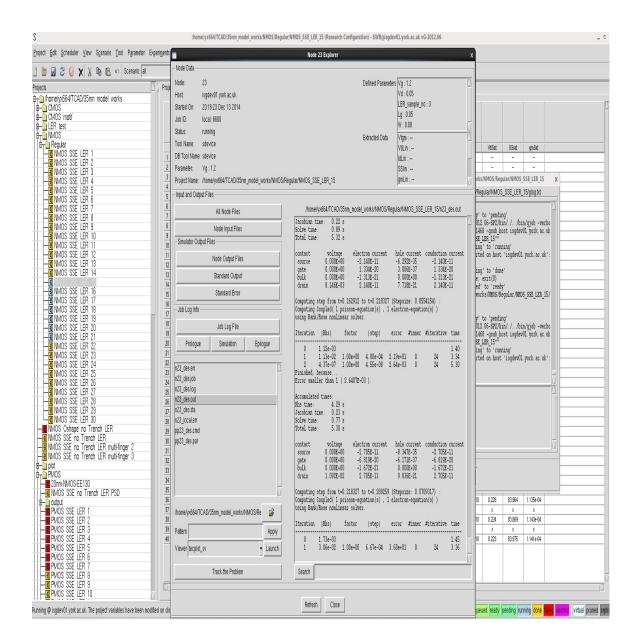

| 3.31 | TCAD Simulation tool GUI and screen capture of simulation information                | 62 |

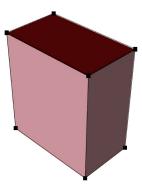

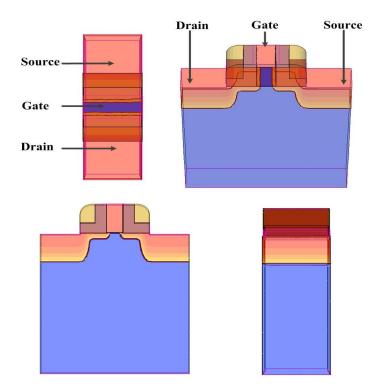

| 3.32 | Reference device with standard transistor layout is constructed by TCAD tools,       |    |

|      | illustrated by different views. Top view (upper left), Front view (low left), Side   |    |

|      | view (lower right), 3D view (upper right)                                            | 63 |

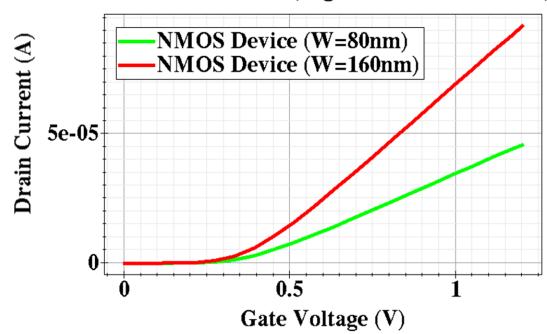

| 3.33 | Reference device $I-V$ characteristic with different width. The device with          |    |

|      | w=160nm is nearly double of the drain current of device with w=80nm. These           |    |

|      | simulations are agreement within the device characteristic theory analysis.          | 64 |

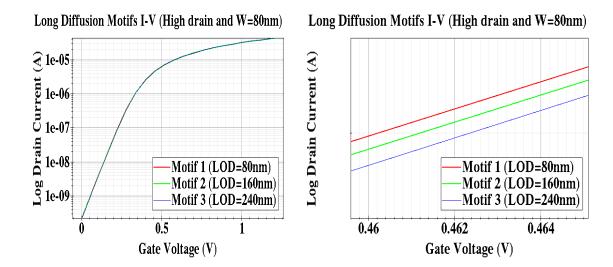

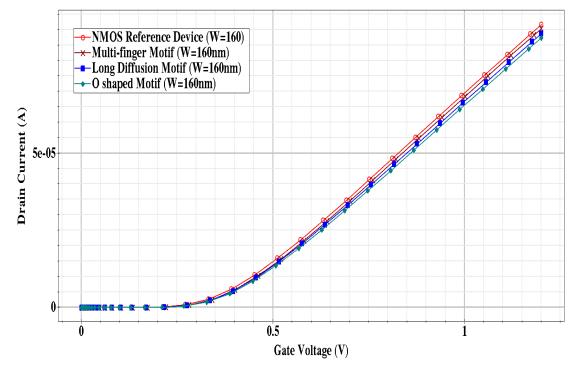

| 3.34 | The comparison of different motifs' $I-V$ characteristic. Although these motifs            |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | I-V characteristic are approximately the same, the various layouts result in               |    |

|      | these motifs existing the slightly difference on their performance.                        | 65 |

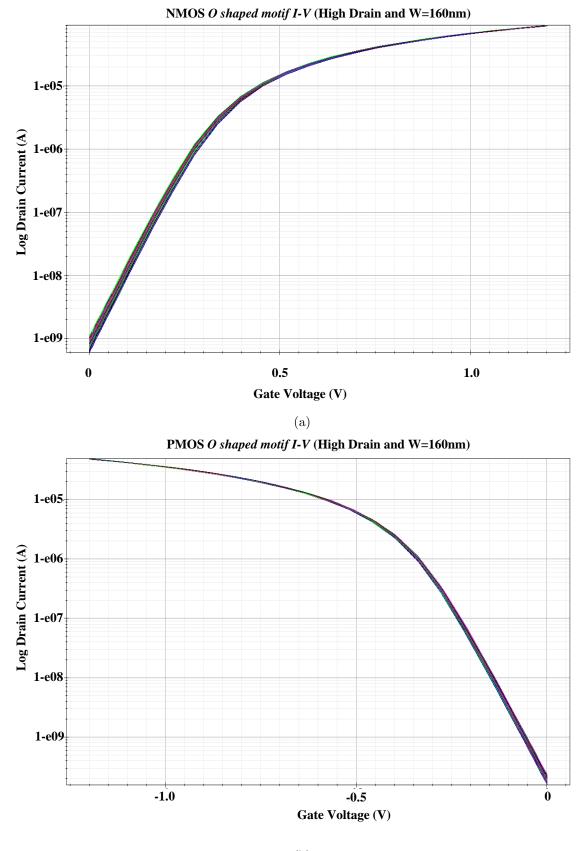

| 3.35 | The complete ensemble of 300 gate transfer characteristics in saturation and               |    |

|      | linear regimes for $O$ shaped motif with 50 $nm$ gate length under high drain              |    |

|      | voltage condition, subjected purely to LER are illustrated in n-channel motif              |    |

|      | (a) and p-channel motif (b), respectively. LER has a relatively impact on                  |    |

|      | on-current variation and the subthreshold region where the variation in the                |    |

|      | leakage current increases                                                                  | 68 |

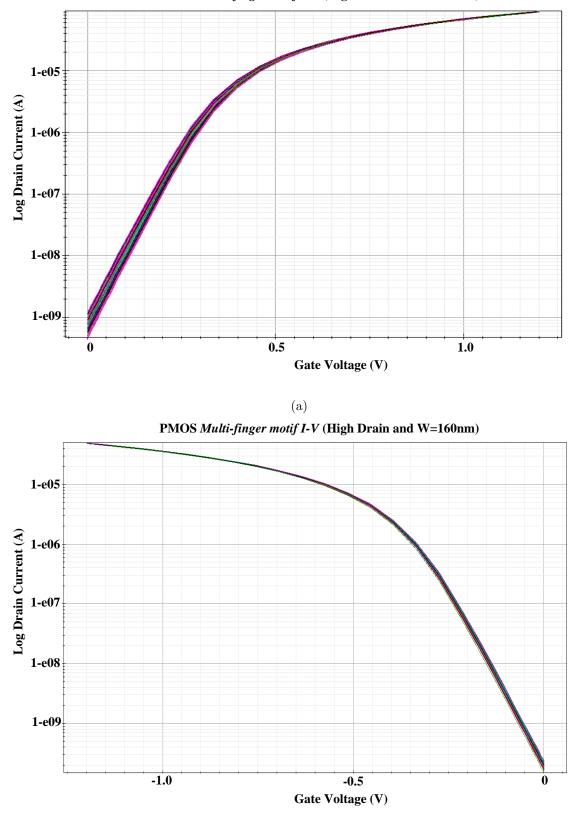

| 3.36 | Large ensemble of 300 $I_d - V_g$ characteristics in saturation and linear regimes for     |    |

|      | multi-finger motif with $50 \ nm$ gate length under high drain voltage condition,          |    |

|      | subjected purely to LER are illustrated in n-channel motif (a) and p-channel               |    |

|      | motif (b), respectively.                                                                   | 69 |

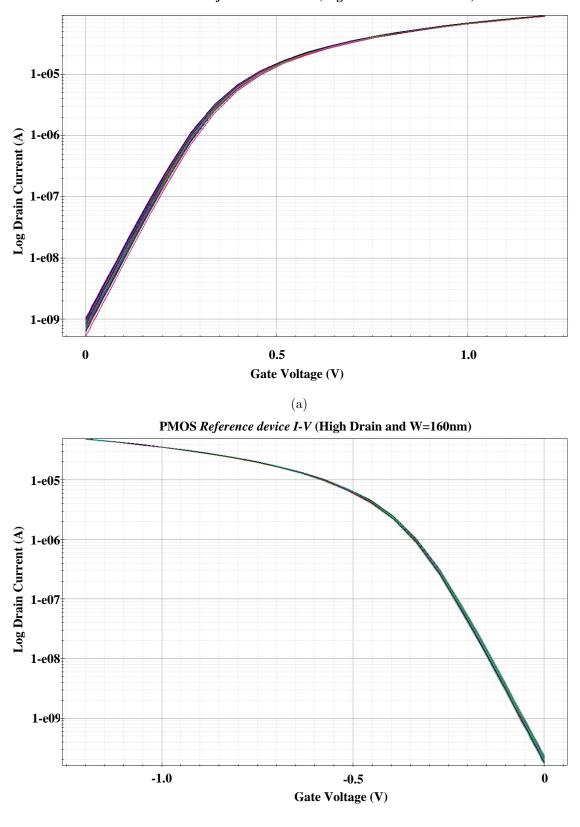

| 3.37 | Large ensemble of 300 $I_d - V_g$ characteristics in saturation and linear regimes         |    |

|      | for reference device with $50 \ nm$ gate length under high drain voltage condition,        |    |

|      | subjected purely to LER are illustrated in n-channel motif (a) and p-channel               |    |

|      | motif (b), respectively. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$    | 70 |

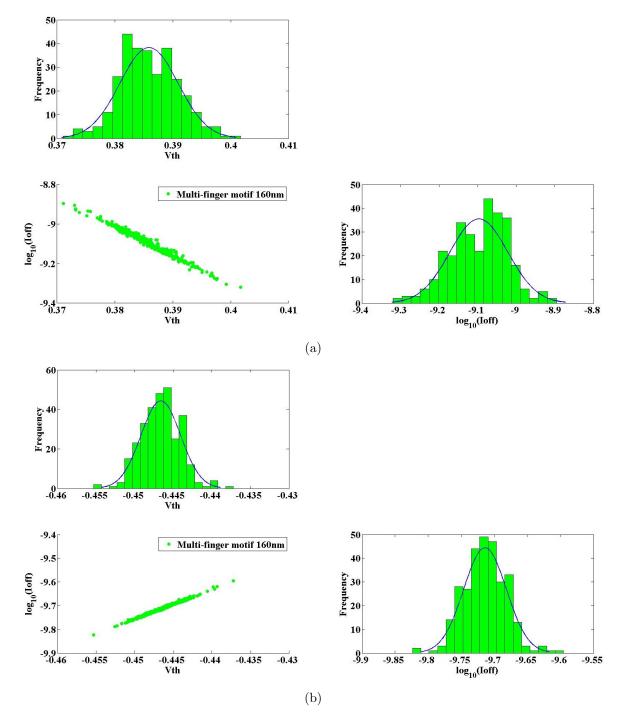

| 3.38 | The scatter plot and histogram of distributions of $V_{th}$ and $I_{off}$ for multi-finger |    |

|      | motif, (a) n-channel motif. (b) p-channel motif. The scatter cloud contains 300            |    |

|      | points obtained from TCAD statistical simulation of multi-finger motif, which              |    |

|      | highlights the affect of LER-induced variability. The density plots (above and             |    |

|      | to the right of the scatter plot) show the distribution for the $V_{th}$ and $I_{off}$     | 71 |

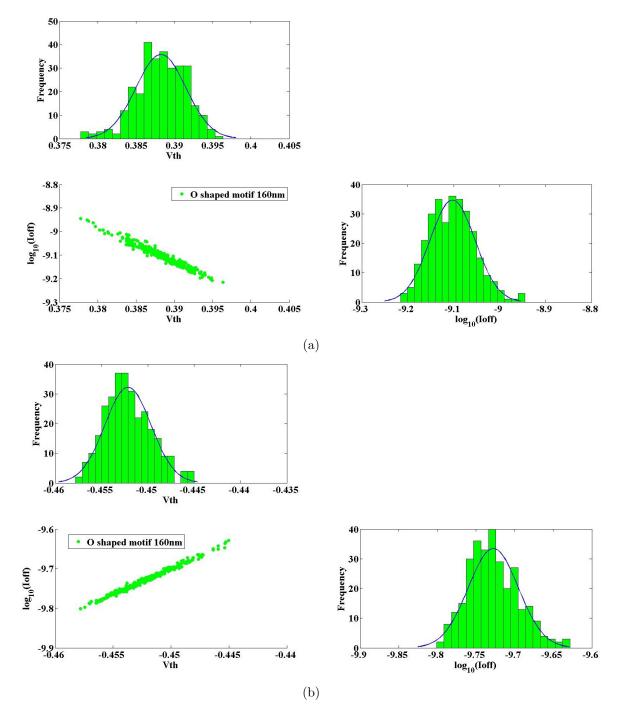

| 3.39 | The scatter plot and histogram of distributions of $V_{th}$ and $I_{off}$ for $O$ shaped   |    |

|      | motif, (a) n-channel motif. (b) p-channel motif. The scatter cloud contains 300            |    |

|      | points obtained from TCAD statistical simulation of ${\cal O}$ shaped f motif, which       |    |

|      | highlights the affect of LER-induced variability. The density plots (above and             |    |

|      | to the right of the scatter plot) show the distribution for the $V_{th}$ and $I_{off}$     | 72 |

|      |                                                                                            |    |

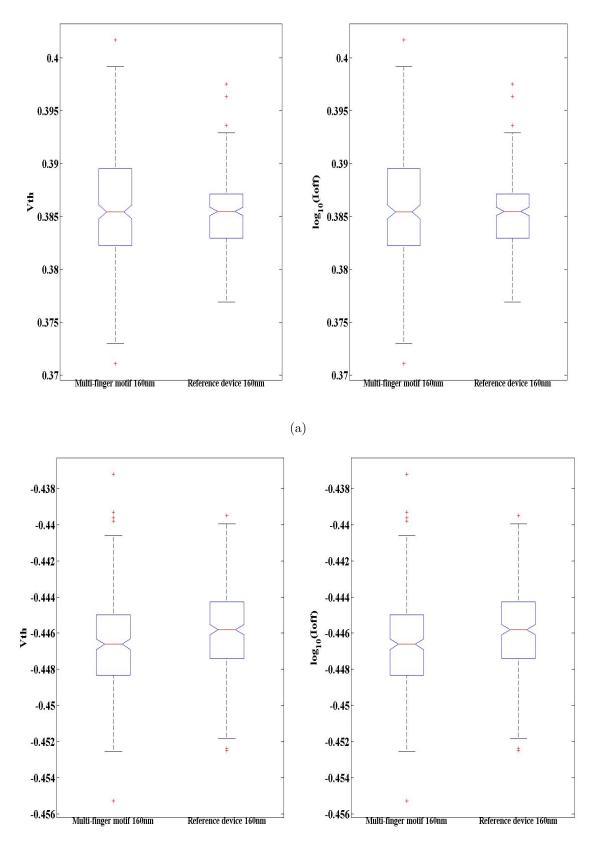

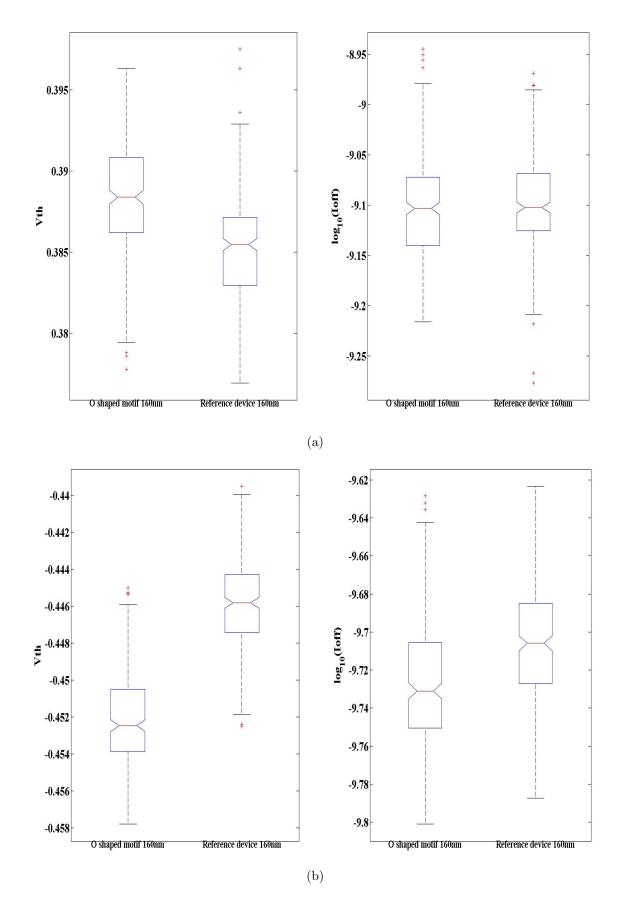

3.40 Comparison of multi-finger motif and reference device at high drain voltage for  $V_{th}$  and  $I_{off}$ , (a) n-channel motif. (b) p-channel motif. The line in the centre of the box denotes the median, the *box* denotes the inter-quartile range (*IQR*). 73

| 3.41 | Comparison of $O$ shaped motif and reference device at high drain voltage for                 |    |

|------|-----------------------------------------------------------------------------------------------|----|

|      | $V_{th}$ and $I_{off}$ represented by <i>Box-and-whisker</i> plots, (a) n-channel motif. (b)  |    |

|      | p-channel motif.                                                                              | 74 |

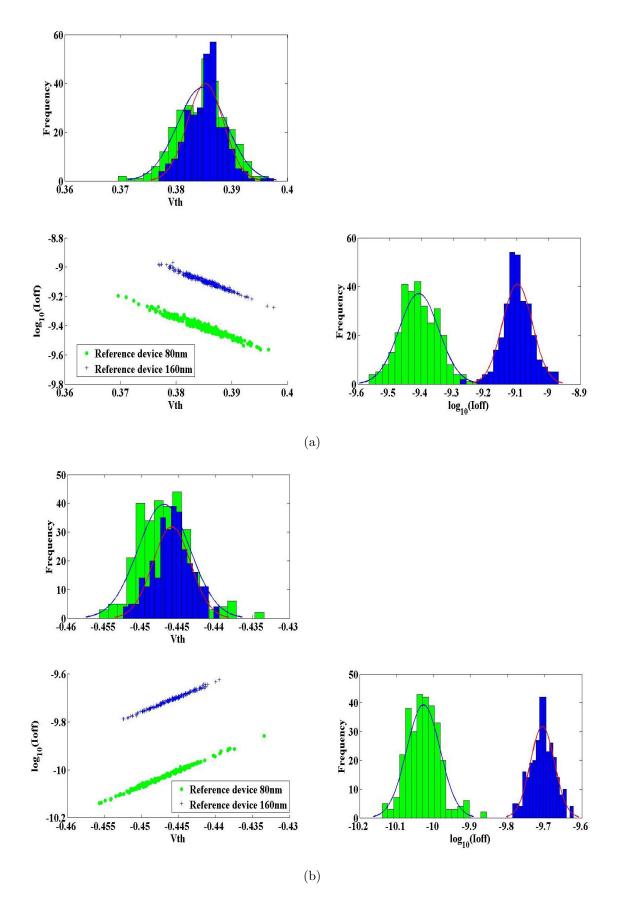

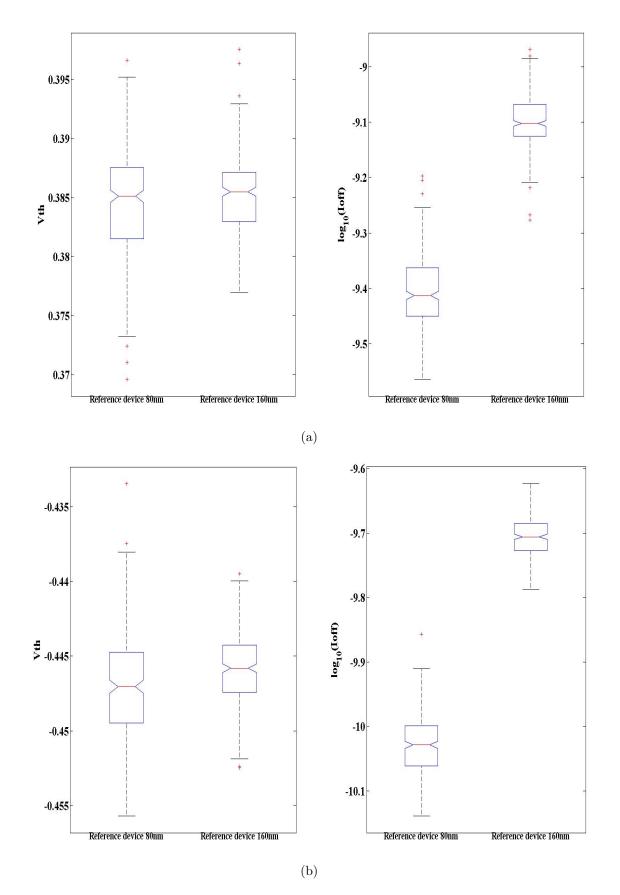

| 3.42 | Comparison of reference device with different width at high drain voltage for                 |    |

|      | $V_{th}$ and $I_{off}$ illustrated by the scatter plot and the density plots, (a) n-channel   |    |

|      | device. (b) p-channel device.                                                                 | 75 |

| 3.43 | Comparison of reference device with different width at high drain voltage for                 |    |

|      | $V_{th}$ and $I_{off}$ represented by <i>Box-and-whisker</i> plots, (a) n-channel device. (b) |    |

|      | p-channel device.                                                                             | 76 |

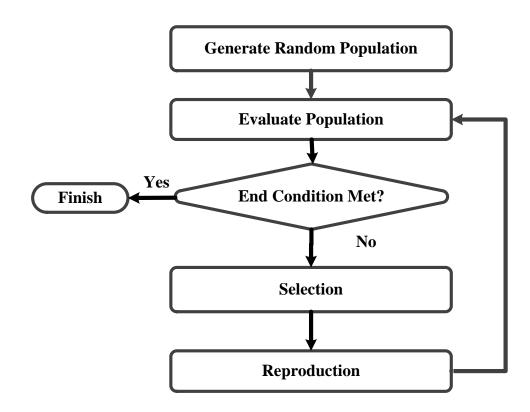

| 4.1  | Block diagram of the main operations of a generic evolutionary loop [99]                      | 79 |

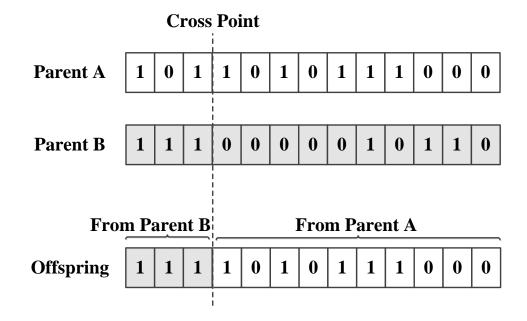

| 4.2  | Example of single-point crossover operation used in evolutionary algorithms .                 | 83 |

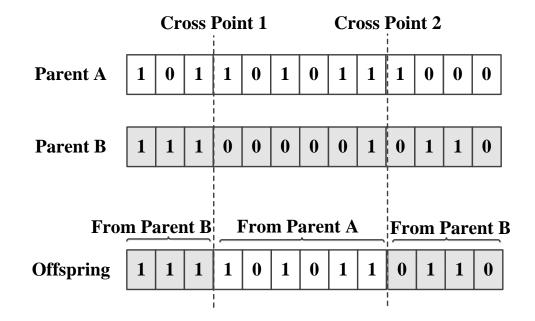

| 4.3  | An example of the multi-point crossover                                                       | 84 |

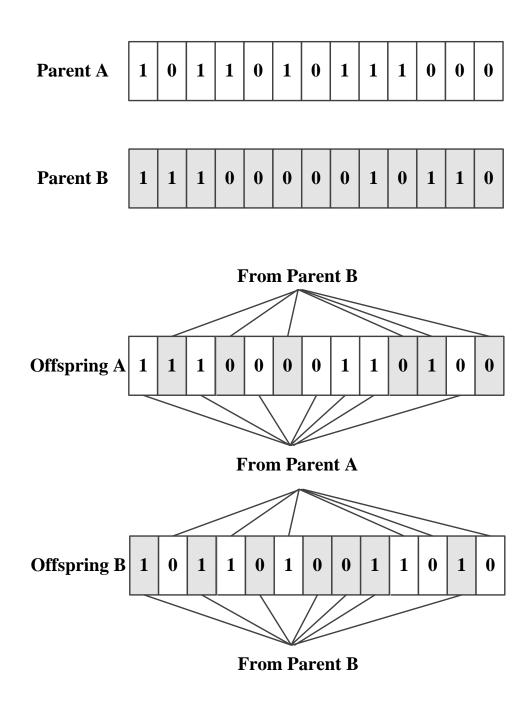

| 4.4  | Uniform-point crossover. In this case, the predetermined parameter is 0.5.                    |    |

|      | The corresponding random variables string is $[0.20, 0.56, 0.41, 0.75, 0.33, 0.62,$           |    |

|      | 0.11, 0.28, 0.39, 0.67, 0.87, 0.11, 0.75]. For offspring A, if random variable in             |    |

|      | each gene position is below 0.5, the gene come from parent A; otherwise from                  |    |

|      | parent B. The inverse mapping is used to create offspring B                                   | 85 |

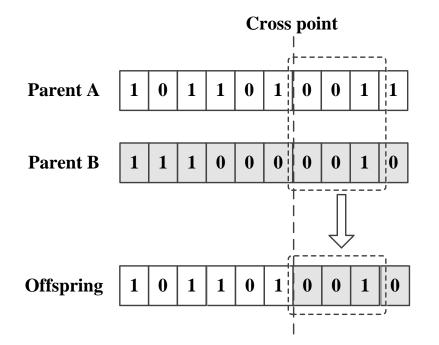

| 4.5  | An offspring is generated from one-point crossover. The drawback of crossover                 |    |

|      | is that offspring genotype is very close to the genotype of parent A because                  |    |

|      | portion of genotype segment in both parents is same, leading to population                    |    |

|      | diversity reductions. In order to solve this problem, the need introduces new                 |    |

|      | gene into mating pool to keep the population diversity.                                       | 86 |

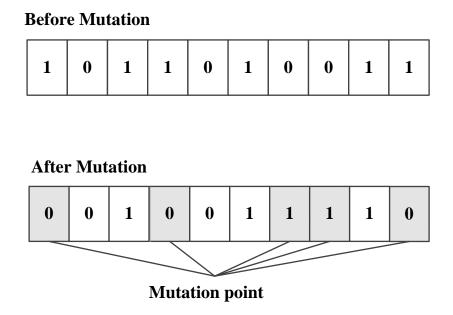

| 4.6  | A common and simple mutation operation in binary representation. The bit-                     |    |

|      | wise mutation randomly selects a set of mutation positions to invert gene value,              |    |

|      | for example, "0" becomes "1" and "1" becomes "0"                                              | 87 |

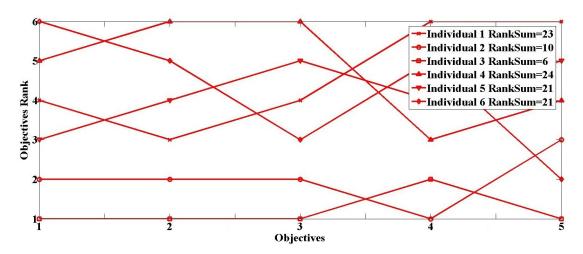

| 4.7  | An example of individuals in a multi-objective problem. The bottom line is the                |    |

|      | Pareto-optimal front [103]. If none of the objective functions can be improved                |    |

|      | in value without degrading some of the other objective values, which solution                 |    |

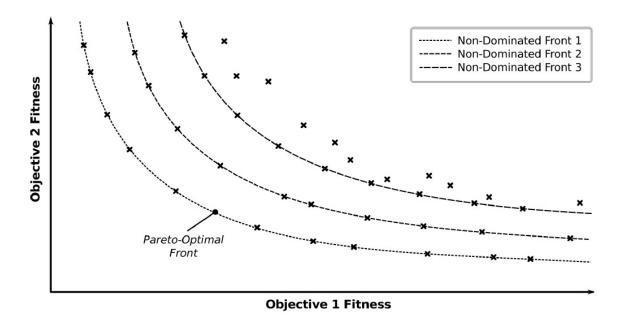

|      | is so-called non-dominated [144].                                                             | 92 |

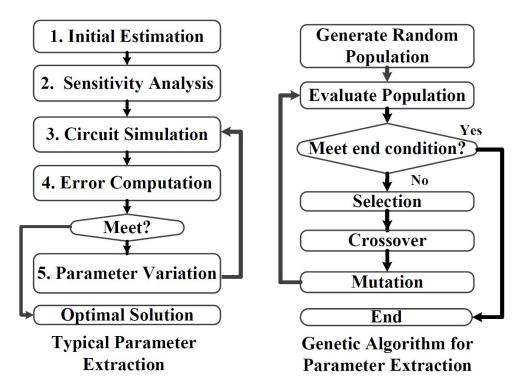

- 4.8 Comparison of a typical parameter extraction procedure (left subfigure) and genetic algorithm (GA) (right subfigure). The circuit simulation and error computation in parameter extraction is analogous with fitness evaluation in GA. The parameter variation can be performed through evolutionary operations. 96

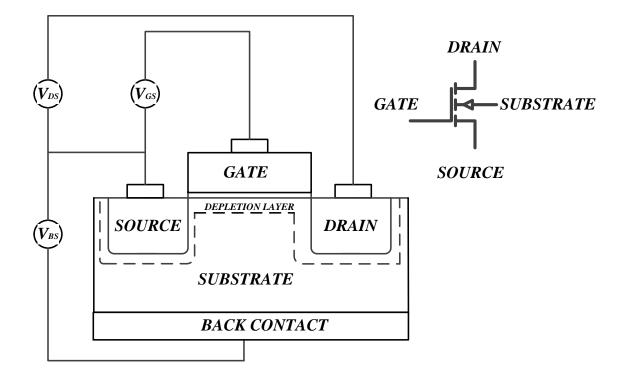

- 5.1 Cross-section and circuit symbol of n-channel MOSFET [170]. When the gate voltage  $V_{GS}$  is positive and over the threshold voltage, the NMOS is on and an n-type conductive channel between the drain and source below the oxide is formed. When the gate voltage is below the threshold voltage, the NMOS is off. In this case, a four terminal NMOS circuit symbol is displayed. . . . . 101

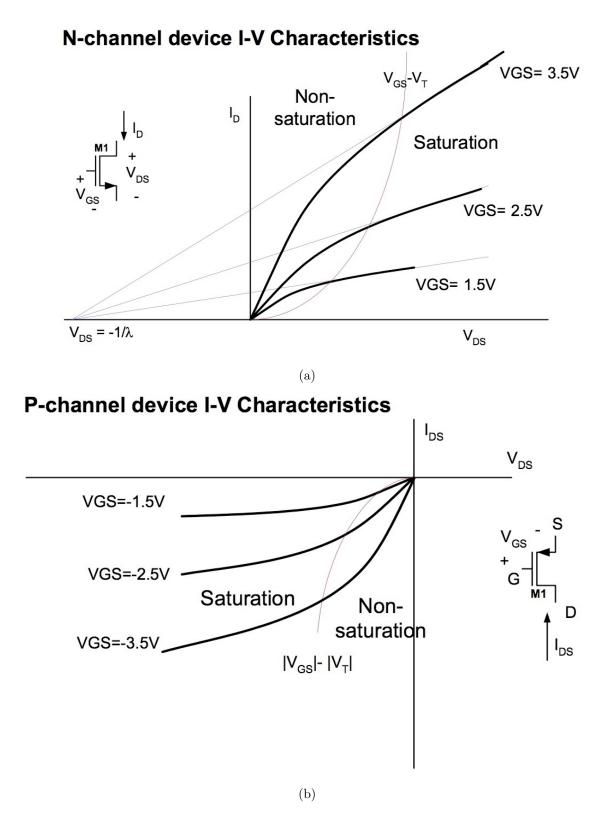

- 5.2 The *I-V* characteristics of *n* and *p*-channel device under different gate voltage condition. The boundary between the linear and saturated regions is indicated by the upward curving parabola (sub-figure (a) NMOS) and downward curving parabola (sub-figure (b) PMOS) [172].

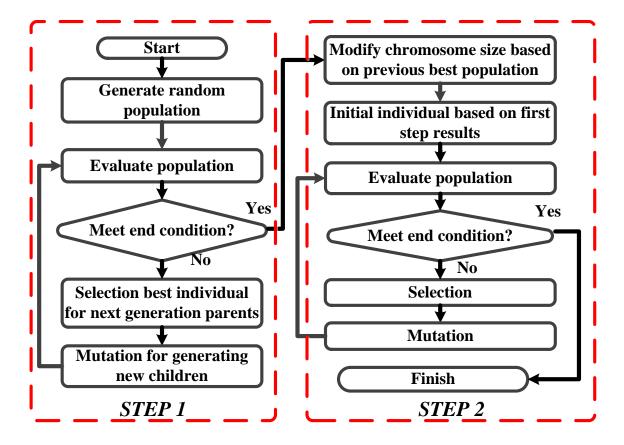

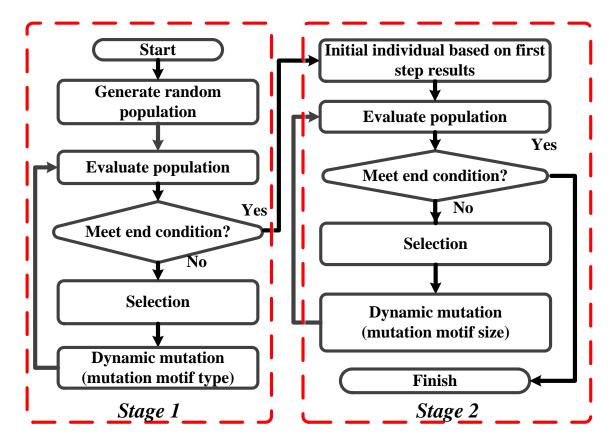

| 5.5  | The flow chart of 2SEA. Here only displays two steps but the algorithm can               |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | be easily extending to more steps. At the beginning of each step optimisation            |     |

|      | except first step, the chromosome parameter size will be adjusted based on               |     |

|      | previous step optimisation results. The aim of step 1 is to find a good initial          |     |

|      | condition for later steps so as to the drawback of the conventional method               |     |

|      | achieving poor convergence without good initial condition. The step 2 is a               |     |

|      | finer extraction and optimisation process according to the step 1 extraction             |     |

|      | results                                                                                  | 110 |

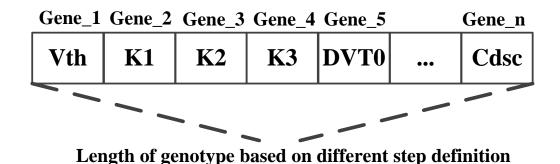

| 5.6  | The outline of the genotype structure. Each gene represents one optimised                |     |

|      | BSIM model parameters and each gene is a floating-point value. Although the              |     |

|      | length of genotype is fixed in every step, the different steps have the variety of       |     |

|      | length of genotype due to optimisation direction changing. $\ldots$                      | 111 |

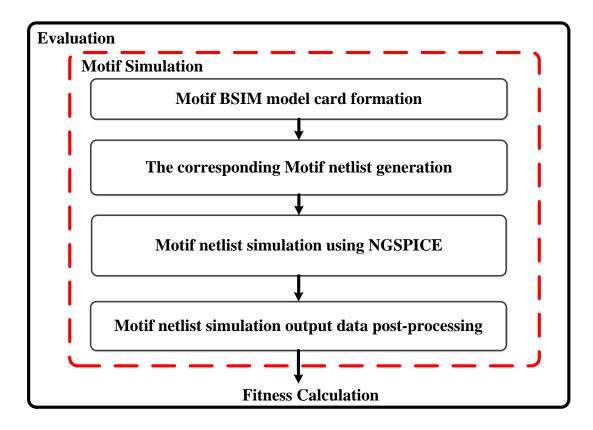

| 5.7  | The steps in the process of candidate solutions evaluation $\ldots \ldots \ldots \ldots$ | 114 |

| 5.8  | Fitness calculation using error rate. Two points with the same gate voltage              |     |

|      | are taken from TCAD measured curves and EA candidate generated curves                    |     |

|      | based on SPICE simulation, respectively. Then, the drain current absolute                |     |

|      | error of both points are calculated as fitness. In the fitness calculation, $12$         |     |

|      | sample point with different gate voltages are applied. $\ldots$                          | 115 |

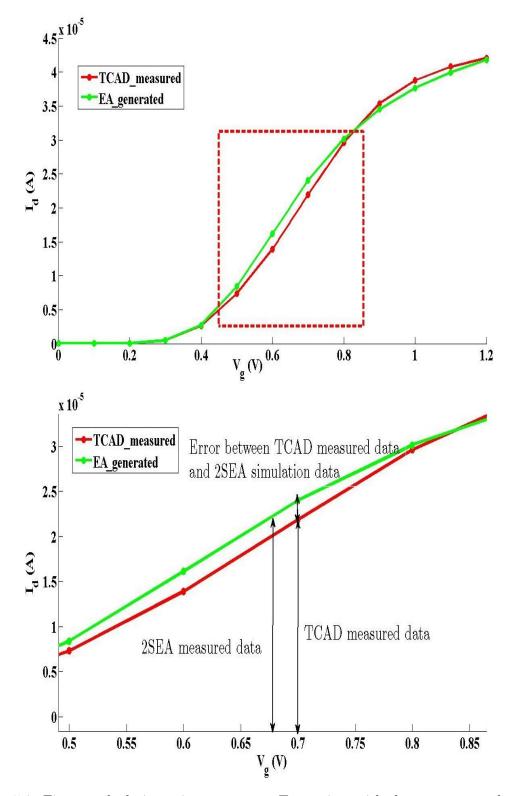

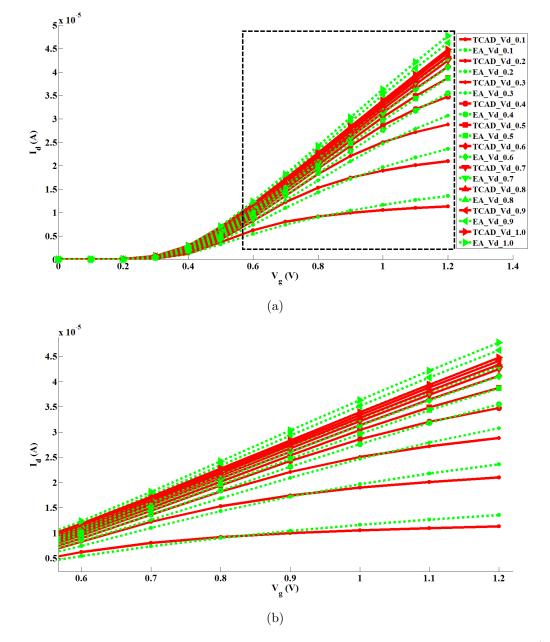

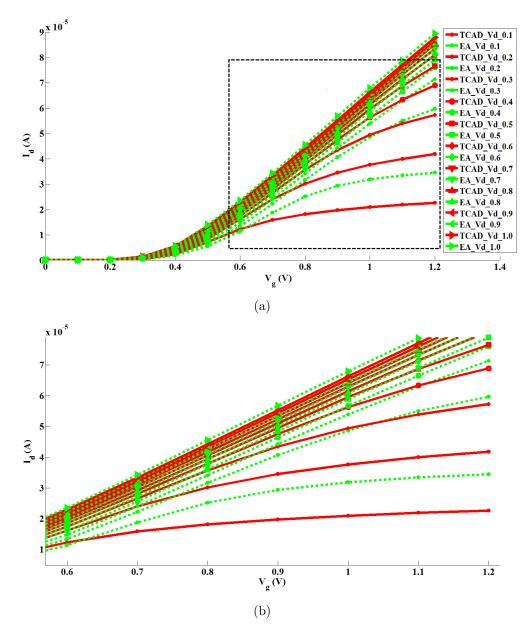

| 5.9  | The comparison between NMOS reference device TCAD measured curves (red)                  |     |

|      | and ES generated simulation curves (green/dash) for the best solution in $10$            |     |

|      | runs on the first step extraction. Two curves fit well in the triode region              |     |

|      | and have less match in the saturation region (shown in bottom sub-figure).               |     |

|      | Suggesting that the optimisation parameter size for the second step extraction           |     |

|      | require adjustment                                                                       | 118 |

| 5.10 | The comparison between NMOS reference device TCAD measured curves (red)                  |     |

|      | and ES generated simulation curves (green/dash) for the best solution in $10$            |     |

|      | runs on the second step extraction. After the second step extraction, two                |     |

|      | curves in the saturation region also have better match. The bottom sub-figure            |     |

|      | zooms the optimised region                                                               | 119 |

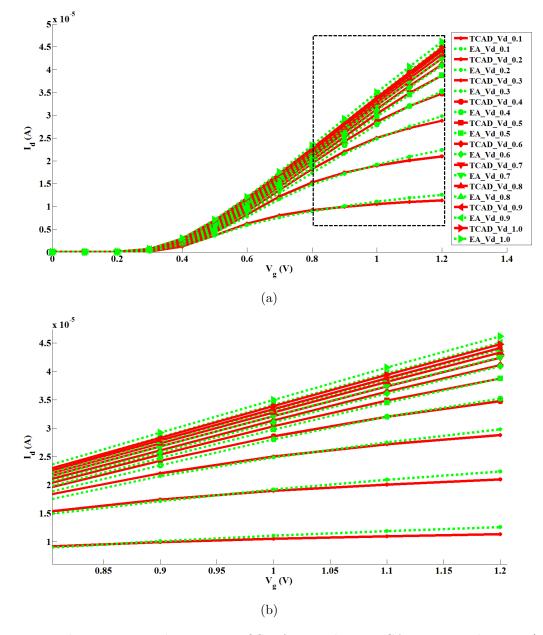

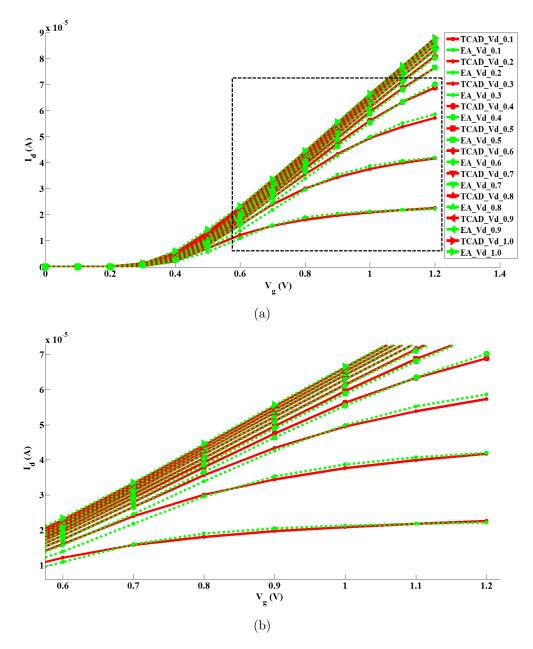

| 5.11 | The comparison between PMOS reference device TCAD measured curves (red)                  |     |

|      | and ES generated simulation curves (green/dash) for the best solution in $10$            |     |

|      | runs on the first step extraction. Larger error region is zoomed in the bottom           |     |

|      | sub-figure                                                                               | 120 |

| 5.12 | The comparison between PMOS reference device TCAD measured curves (red)          |     |

|------|----------------------------------------------------------------------------------|-----|

|      | and ES generated simulation curves (green) for the best solution in 10 runs      |     |

|      | on the second step extraction. After the second step extraction, two curves in   |     |

|      | the saturation region also have better match. The bottom sub-figure zooms        |     |

|      | the optimised region                                                             | 121 |

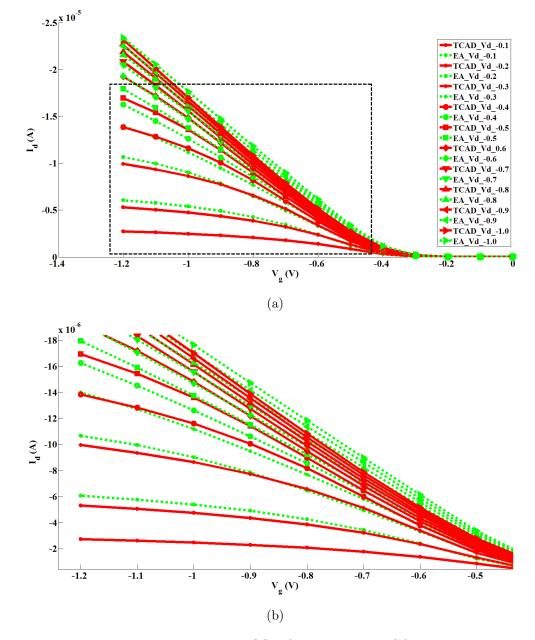

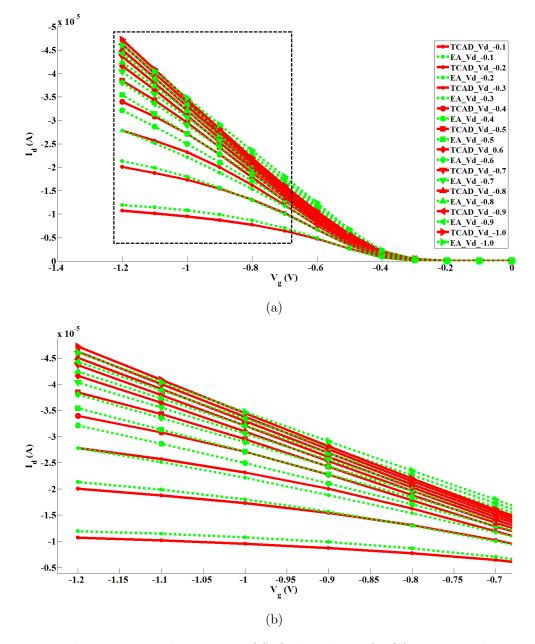

| 5.13 | The comparison between NMOS $O$ shaped motif TCAD measured curves (red)          |     |

|      | and ES generated simulation curves (green/dash) for the best solution in 10      |     |

|      | runs on the first step extraction. Larger error region is zoomed in the bottom   |     |

|      | sub-figure                                                                       | 123 |

| 5.14 | The comparison between NMOS ${\cal O}$ shaped motif TCAD measured curves (red)   |     |

|      | and ES generated simulation curves (green/dash) for the best solution in $10$    |     |

|      | runs on the second step extraction. The bottom sub-figure zooms the optimised    |     |

|      | region                                                                           | 124 |

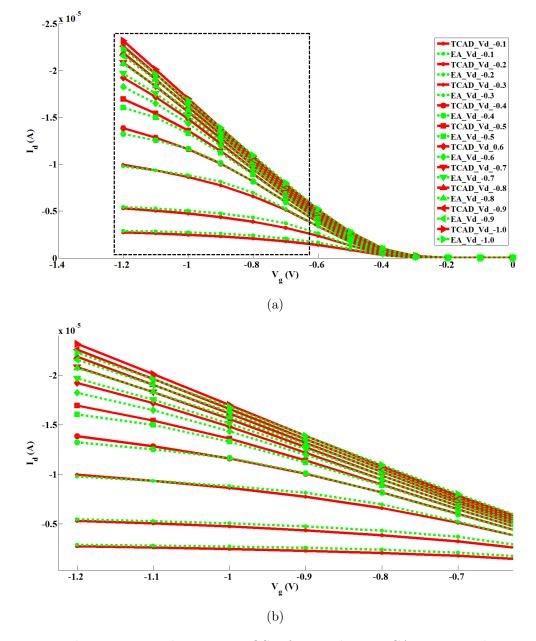

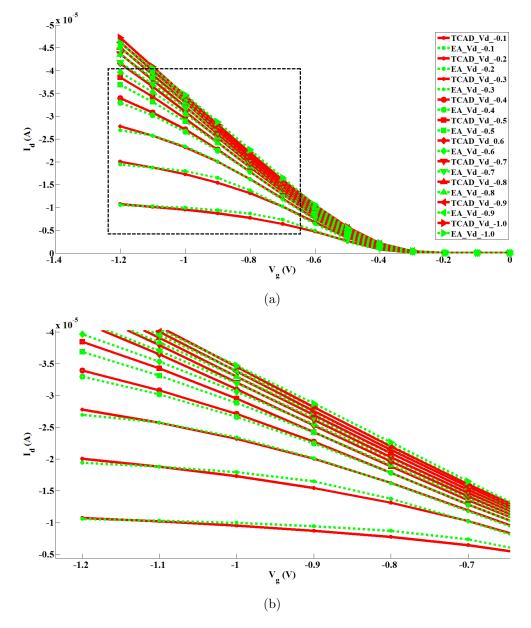

| 5.15 | The comparison between PMOS $O$ shaped motif TCAD measured curves (red)          |     |

|      | and ES generated simulation curves (green/dash) for the best solution in $10$    |     |

|      | runs on the first step extraction. Larger error region is zoomed in the bottom   |     |

|      | sub-figure                                                                       | 125 |

| 5.16 | The comparison between PMOS $O$ shaped motif TCAD measured curves (red)          |     |

|      | and ES generated simulation curves (green/dash) for the best solution in 10      |     |

|      | runs on the second step extraction. The bottom sub-figure zooms the optimised    |     |

|      | region                                                                           | 126 |

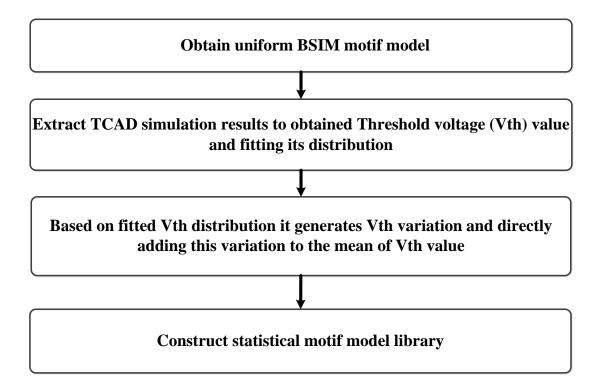

| 5.17 | The flow chart of motifs statistical variability model generation. In this case, |     |

|      | only one parameter, threshold voltage, is used to generate variation. However,   |     |

|      | the described method is a generic approach that can also be adapted to other     |     |

|      | parameters.                                                                      | 127 |

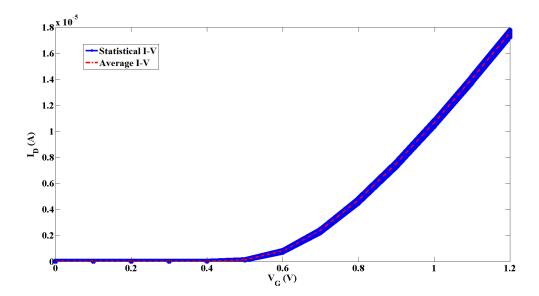

| 5.18 | Large ensembles of NMOS reference device $I-V$ curves presenting different       |     |

|      | instances with LER variability effect. These curves are generated by proposed    |     |

|      | motifs statistical variability modelling approach.                               | 127 |

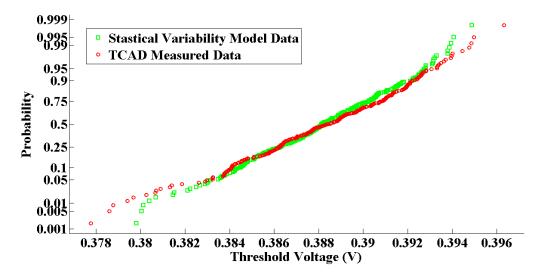

| 5.19 | The probability plots of typical threshold voltage in compact model, which       |     |

|      | clearly demonstrated that approximation between the TCAD measured data           |     |

|      | and data produced by the above mentioned approach is appropriate                 | 128 |

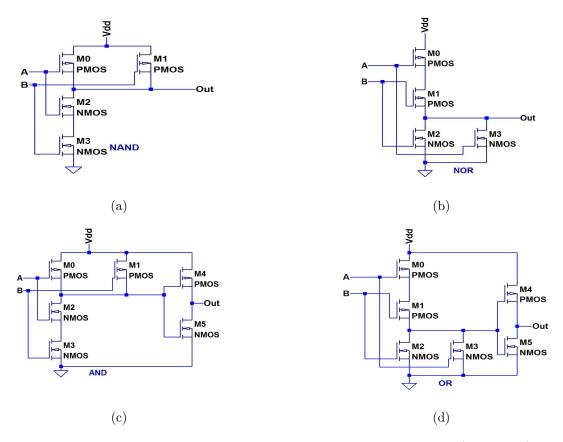

| 6.1  | Transistor level schematic of four basic logic gates, NAND gate (left upper),                 |     |

|------|-----------------------------------------------------------------------------------------------|-----|

|      | NOR (right upper), AND (left bottom), OR (right bottom)                                       | 132 |

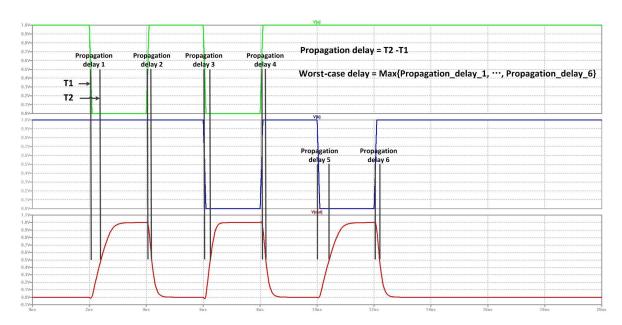

| 6.2  | NAND gate output delay measurement scenario. Six propagation delays are                       |     |

|      | measured in accordance with six various input scenarios. The slowest delay in                 |     |

|      | these six propagation delays is selected as the worst-case delay                              | 135 |

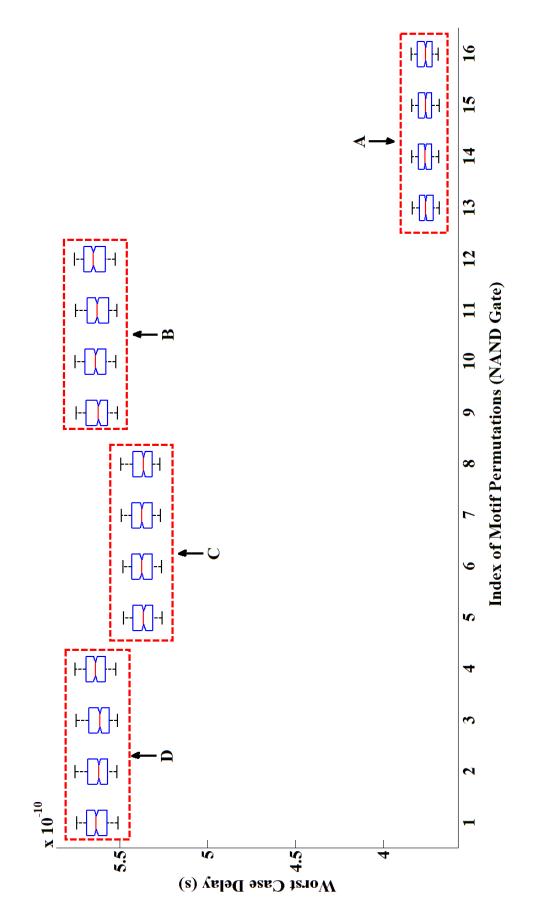

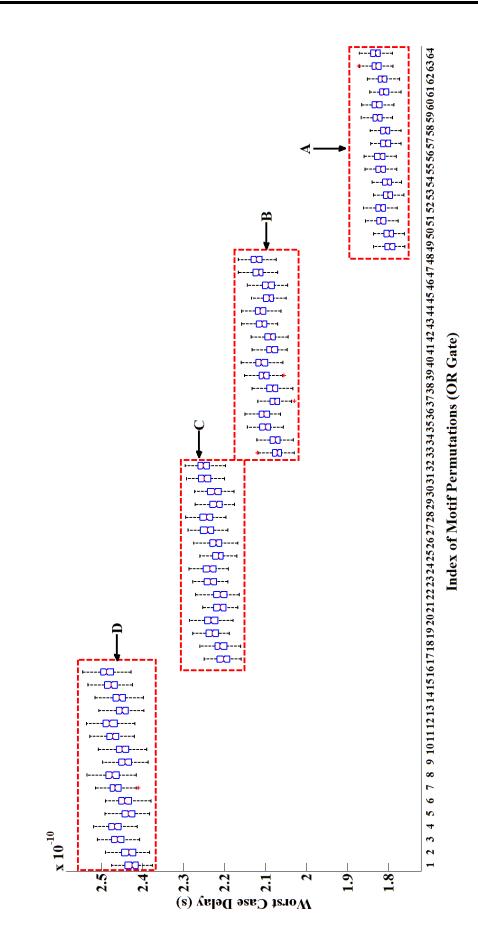

| 6.3  | The relationship of worse case delay and motif permutations (NAND gate).                      |     |

|      | Only $O$ shaped motif and standard (reference) device are used to constitute                  |     |

|      | various motif permutations. These motif permutations are sorted into different                |     |

|      | groups (A, B, C, D) based on measured worst-case delays. $\hfill \ldots \ldots \ldots \ldots$ | 136 |

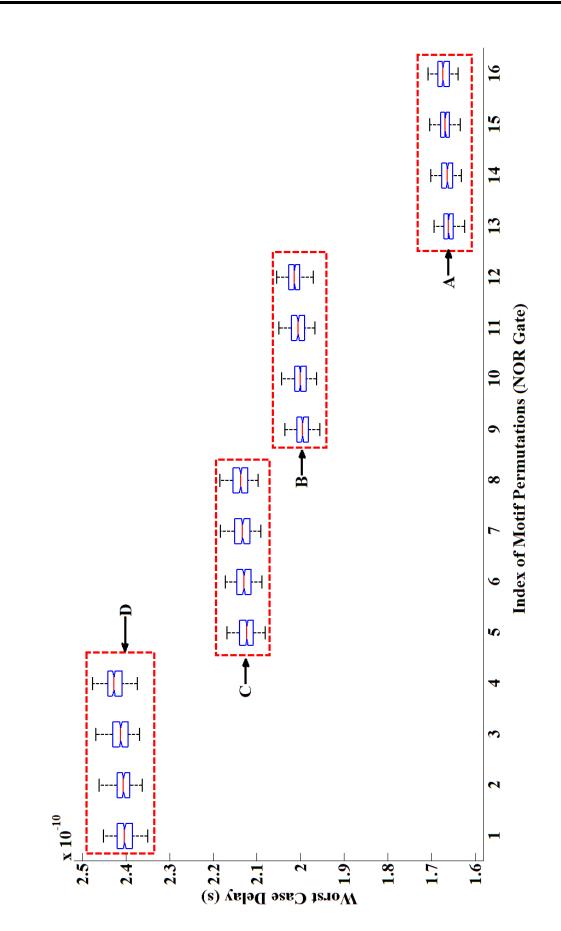

| 6.4  | The relationship of worse case delay and motif permutations (NOR gate). Only                  |     |

|      | ${\cal O}$ shaped motif and standard (reference) device are used to constitute various        |     |

|      | motif permutations. These motif permutations are sorted into different groups                 |     |

|      | (A, B, C, D) based on measured worst-case delays                                              | 137 |

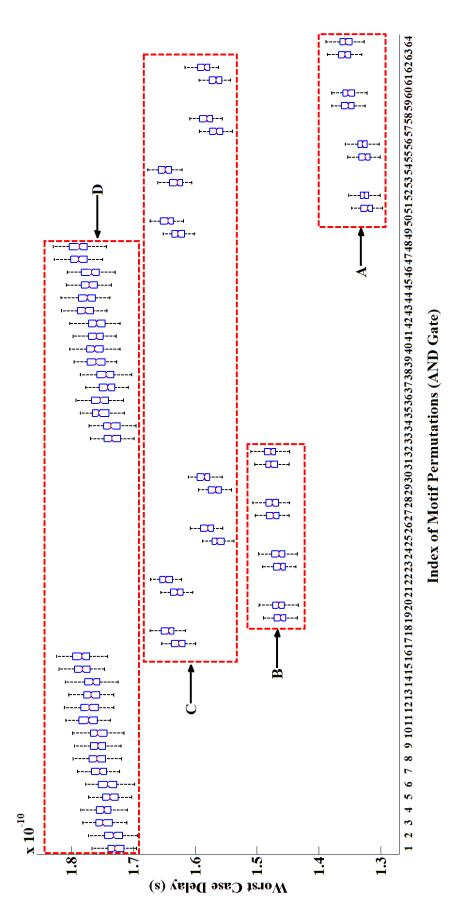

| 6.5  | The relationship of worse case delay and motif permutations (AND gate). Only                  |     |

|      | ${\cal O}$ shaped motif and standard (reference) device are used to constitute various        |     |

|      | motif permutations. These motif permutations are sorted into different groups                 |     |

|      | (A, B, C, D) based on measured worst-case delays                                              | 138 |

| 6.6  | The relationship of worse case delay and motif permutations (OR gate). Only                   |     |

|      | ${\cal O}$ shaped motif and standard (reference) device are used to constitute various        |     |

|      | motif permutations. These motif permutations are sorted into different groups                 |     |

|      | (A, B, C, D) based on measured worst-case delays                                              | 139 |

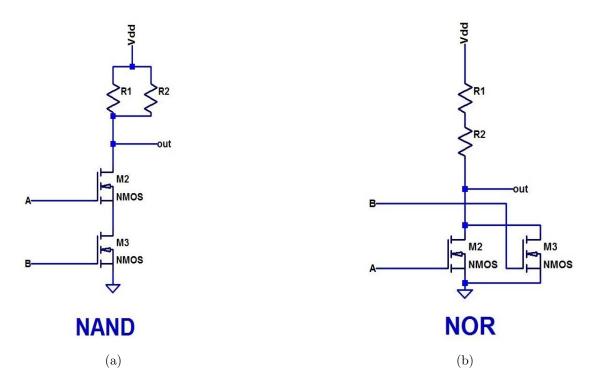

| 6.7  | NMOS logic circuits of NAND and NOR gate transistor level schematics. The                     |     |

|      | original PMOS transistors are replaced by the equivalent resistor. These cir-                 |     |

|      | cuits are tested using the equivalent resistor value which is equal to the stan-              |     |

|      | dard device and $O$ shaped motif, respectively                                                | 145 |

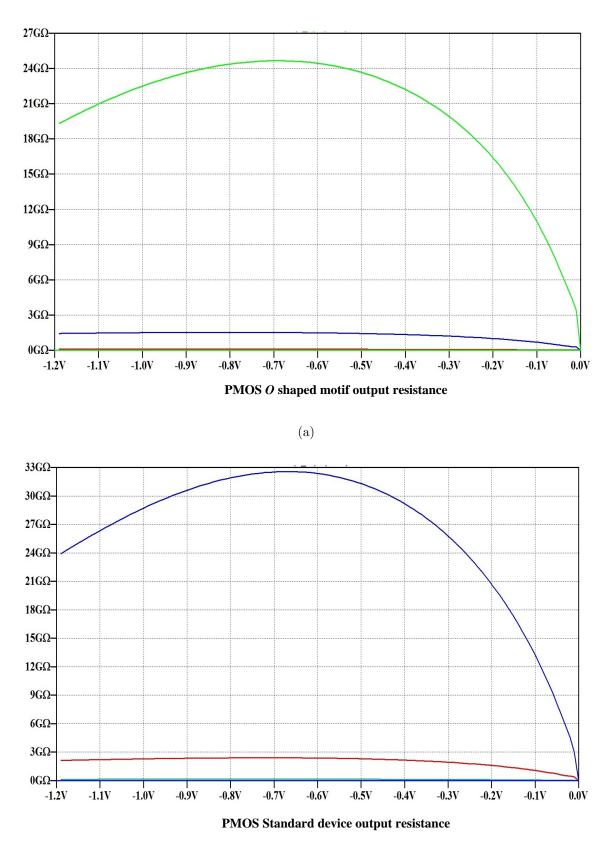

| 6.8  | The PMOS $O$ shaped motif and standard device output resistance value is                      |     |

|      | measured under different drain voltages. Y-axis is output resistance; and X-                  |     |

|      | axis is gate voltage                                                                          | 146 |

| 6.9  | The flow chart of multi-stage evolutionary algorithm                                          | 147 |

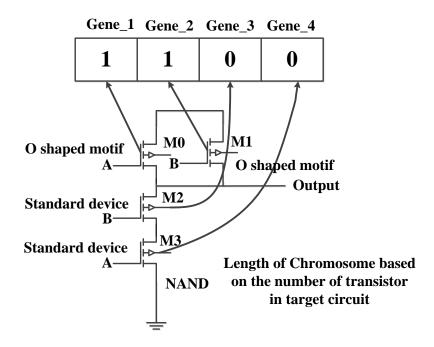

| 6.10 | An example of NAND gate is represented by a genotype structure in first                       |     |

|      | stage. Each transistor is represented a gene in the genotype. The genotype                    |     |

|      | size depends on the number of transistor in circuit                                           | 148 |

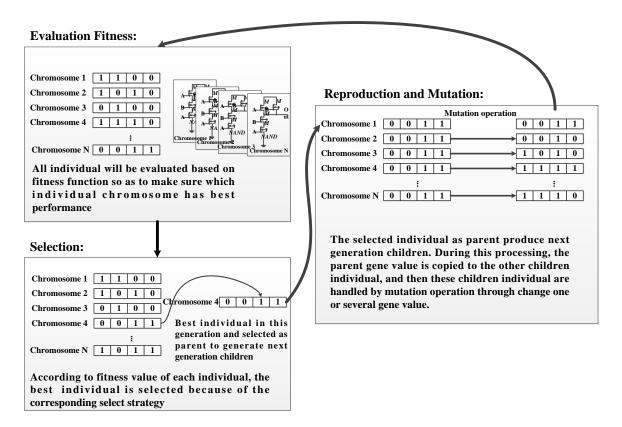

- 6.11 An example of the evolutionary loop, demonstrating the genetic operations. . 149

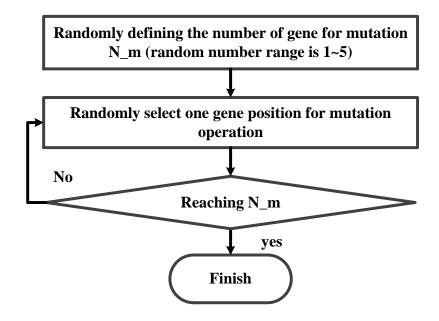

- 6.12 The flow chart of the dynamic genen mutation. The maximum number of gene for mutation is 5; and the minimum number of gene for mutation is 1. . . . 150

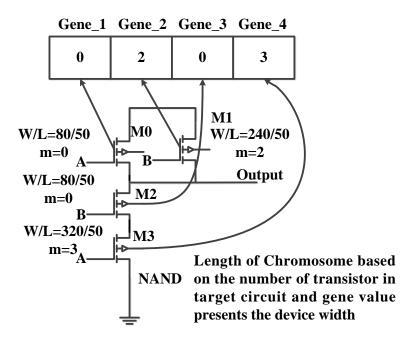

- 6.13 The genotype structure of NAND gate in second stage. In the second stage, the genotype size is the same as in the first stage. Because the gene in genotype represents the motif width, the genotype adapts integer representation. . . . 152

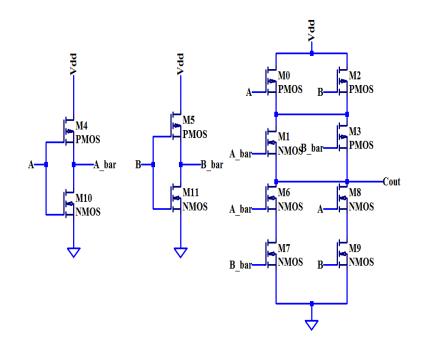

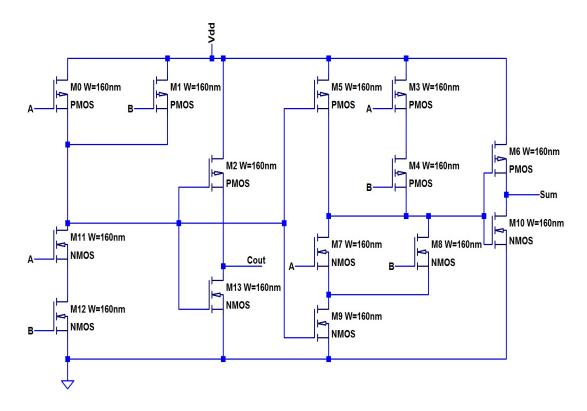

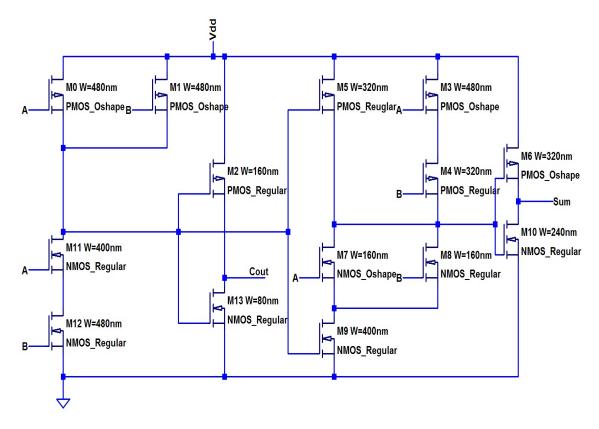

- 6.15 The XOR gate transistor level schematic. XOR gate consists of 12 transistors. 154

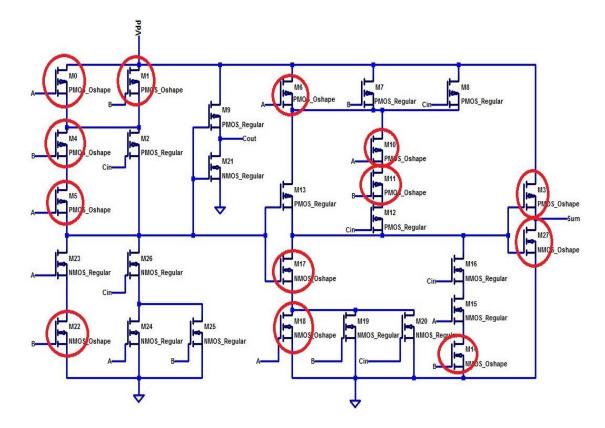

- 6.20 Transistor level evolved circuit schematic of half adder after the first stage optimisation. the evolved transistors replaced by O shaped motif are highlighted by red circle in the circuit.160

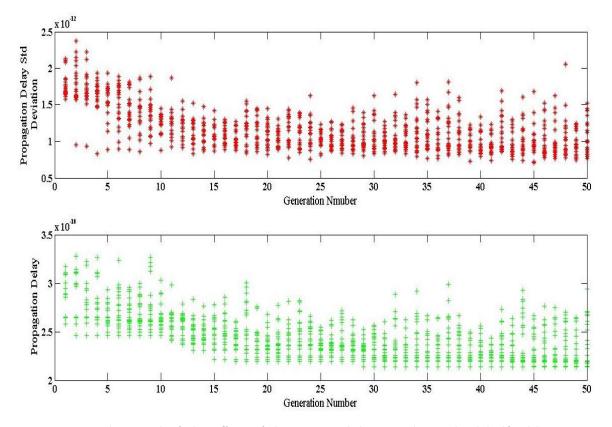

| 6.21 | The trend of the effect of device variability on the evolved half adder circuit      |      |

|------|--------------------------------------------------------------------------------------|------|

|      | performance. Each star in figures represents an individual in the population.        |      |

|      | The upper sub-figure is the standard deviation of propagation delay vs gener-        |      |

|      | ation number. The lower sub-figure is the mean value of propagation delay vs         |      |

|      | generation number                                                                    | 161  |

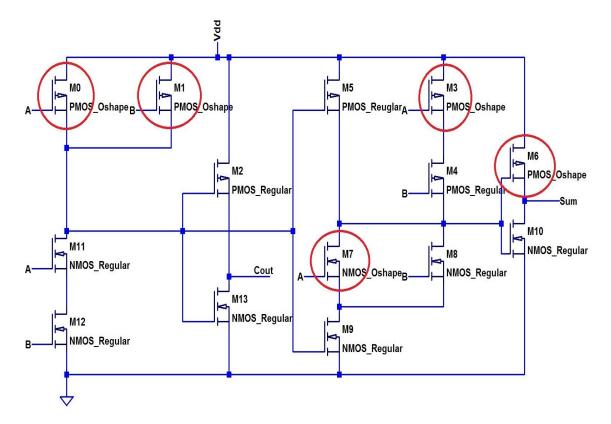

| 6.22 | The final evolved half adder circuit has minimum effect of device variability on     |      |

|      | the circuit performance. The evolved circuit shows that the appropriate motif        |      |

|      | is applied in the specific position with evolved geometry size                       | 162  |

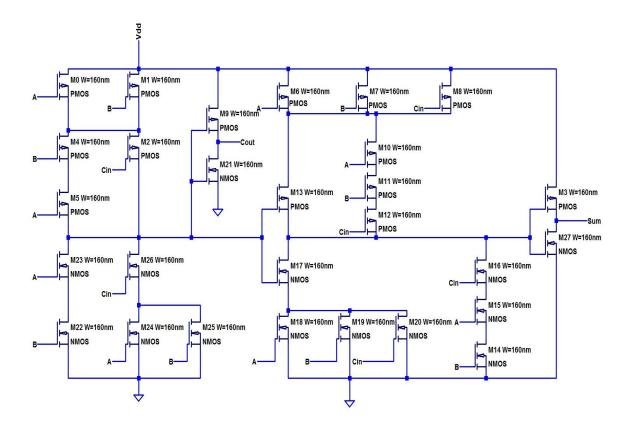

| 6.23 | Transistor level evolved circuit schematic of full adder after the first stage       |      |

|      | optimisation. The evolved transistors replaced by $O$ shaped motif in the circuit    |      |

|      | are highlighted by red circle.                                                       | 164  |

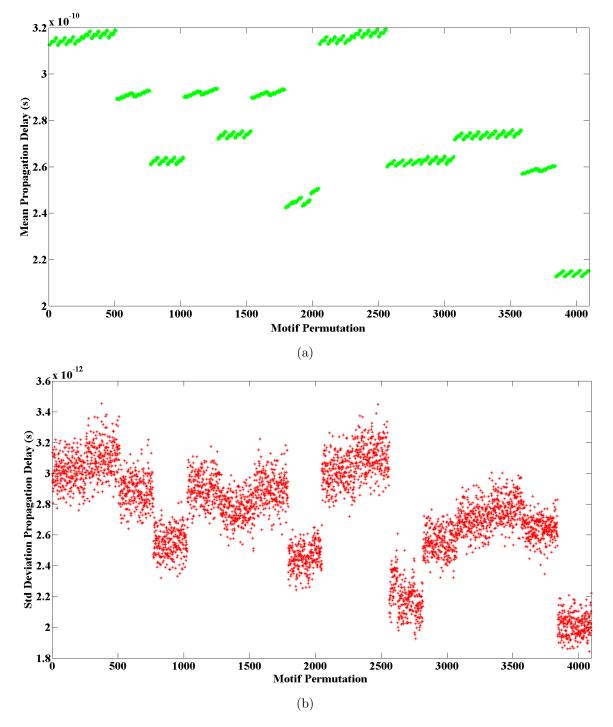

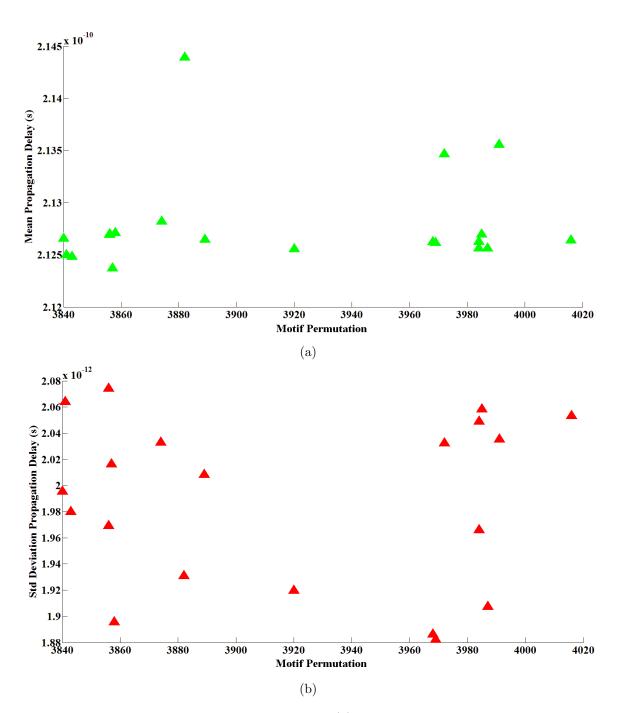

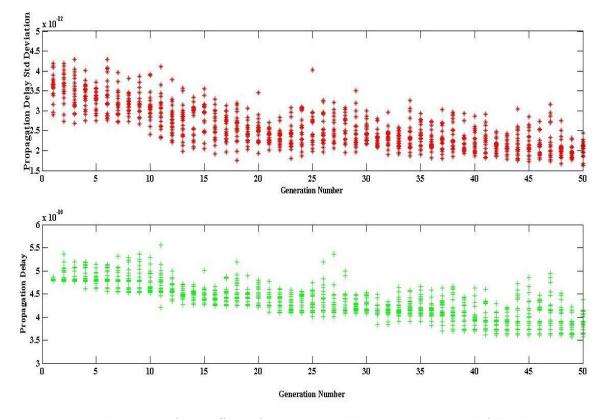

| 6.24 | The trend of the effect of device variability on the evolved full adder circuit per- |      |

|      | formance. Each point represents an individual in the population. The upper           |      |

|      | sub-figure is the standard deviation of propagation delay vs generation num-         |      |

|      | ber. The lower sub-figure is the mean value of propagation delay vs generation       |      |

|      | number. Both the standard deviation and mean value of propagation delay              |      |

|      | have been decreased as generation number increasing. These results prove             |      |

|      | that proposed optimisation method effectively minimise the effect of device          |      |

|      | variability on test circuit performance                                              | 165  |

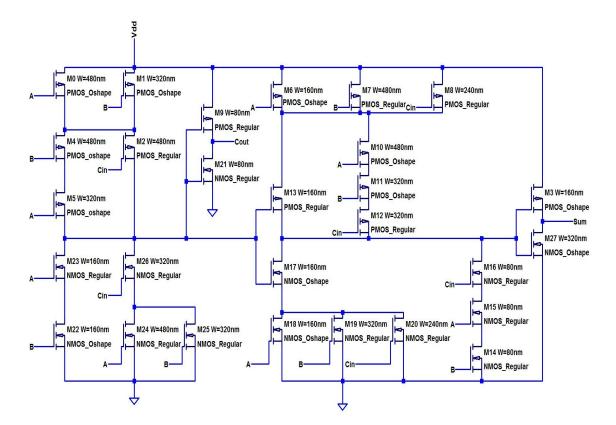

| 6.25 | The final evolved full adder circuit has minimum the effect of device variability    |      |

|      | on the full adder circuit performance. As the number of transistor in the test       |      |

|      | circuit increasing, the evolved full adder circuit shows more complex circuit        |      |

|      | motif combination. This suggests that the proposed optimisation methodology          |      |

|      | will be advantages when performing large scale circuit performance optimisation      | .166 |

# List of Tables

| 2.1 | Influence of scaling on MOS device characteristics                             | 10  |

|-----|--------------------------------------------------------------------------------|-----|

| 2.2 | Influence of random/systematic variation on MOS device parameter $\ldots$ .    | 26  |

| 3.1 | TCAD Device Parameters                                                         | 36  |

| 3.2 | TCAD Device Doping Concentration Parameters                                    | 41  |

| 3.3 | TCAD Device Geometry Parameters                                                | 53  |

| 3.4 | TCAD Device Geometry Parameters                                                | 61  |

| 3.5 | Motifs extraction parameters at high drain voltage                             | 65  |

| 3.6 | Summary of motifs Characteristics                                              | 67  |

| 4.1 | Sketch of the simple GA [99] $\ldots$                                          | 90  |

| 4.2 | Sketch of ES [101]                                                             | 90  |

| 4.3 | Sketch of EP [99]                                                              | 91  |

| 4.4 | Sketch of GP [99]                                                              | 92  |

| 4.5 | Examples of Evolutionary Algorithms in Electronic Circuit Design $\ .\ .\ .$ . | 95  |

| 5.1 | A summary of different SPICE compact models performance and its worked         |     |

|     | on minimum gate length and oxide thickness $[15]$                              | 102 |

| 5.2 | Various regions of operation for MOSFETs                                       | 104 |

| 5.3 | Prerequisite process parameters prior to extraction process                    | 116 |

| 5.4 | Two Step EA Parameters (Reference Deivce)                                      | 117 |

| 5.5 | Two Step EA Parameters ( $O$ Shaped Motif)                                     | 122 |

| 6.1  | The exhaustive set of device combinations for the NAND and NOR logic gates.                  |     |

|------|----------------------------------------------------------------------------------------------|-----|

|      | Mx refers to a specific transistor position in each logic gate (see Figure 6.1).             |     |

|      | At each position, the use of a standard device layout is signified by '0', and               |     |

|      | the use of an $O$ shaped motif is signified by '1'                                           | 133 |

| 6.2  | The exhaust<br>vie AND gate and OR gate circuit combinations $\hfill \ldots \ldots \ldots$ . | 134 |

| 6.3  | NAND gate output delay measurement scenario based on different inputs tran-                  |     |

|      | sient changing scenarios                                                                     | 135 |

| 6.4  | The statistical variability results of the motif permutation in a NAND gate                  |     |

|      | (Groups are shown in Figure 6.3)                                                             | 140 |

| 6.5  | The statistical variability results of the motif permutation in a NOR gate                   |     |

|      | (Groups are shown in Figure 6.4) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                | 140 |

| 6.6  | The statistical variability results of the motif permutation in an AND gate                  |     |

|      | (Groups are shown in Figure 6.5)                                                             | 141 |

| 6.7  | The continued statistical variability results of the motif permutation in an                 |     |

|      | AND gate (Groups are shown in Figure 6.5)                                                    | 142 |

| 6.8  | The statistical variability results of the motif permutation in an OR gate                   |     |

|      | (Groups are shown in Figure 6.6) $\ldots$                                                    | 143 |

| 6.9  | The continued statistical variability results of the motif permutation in an OR              |     |

|      | gate (Groups are shown in Figure 6.6)                                                        | 144 |

| 6.10 | Active gate widths of two device types (having same gate length $L=50 nm$ ).                 |     |

|      | Wider devices are constructed from minimal devices connected in parallel                     | 151 |

| 6.11 | EA evolution parameter in XOR gate optimisation. Although two objectives                     |     |

|      | (mean value of propagation delay and standard deviation of propagation delay)                |     |

|      | are optimised in this experiment, only motif permutation is evolved in order                 |     |

|      | to fairly compare the exhausting test results because the exhausting test only               |     |

|      | test different motif permutations not considering different device size                      | 155 |

| 6.12 | Proposed EA Evolution parameter. Due to the computational overhead of per-                   |     |

|      | forming the a large number of SPICE statistical sample simulation and multi-                 |     |

|      | objective calculation, the corresponding evolution parameter is performed for                |     |

|      | a considerably larger number of the population size and shorter number of                    |     |

|      | generations.                                                                                 | 159 |

| 6.13 | Comparison of evolved half adder solution and reference solutions                | 160 |

|------|----------------------------------------------------------------------------------|-----|

| 6.14 | Comparison of evolved 1-bit full adder solution and reference solutions          | 163 |

| 6.15 | A group of the final best results based on single gene mutation in 50 simulation |     |

|      | runs                                                                             | 163 |

|      |                                                                                  |     |

| B.1  | Variables used in Modeling Threshold Voltage                                     | 182 |

| B.2  | Threshold voltage modelling, sub-threshold swing modelling, and mobility         |     |

|      | modelling in BSIM model parameters                                               | 183 |

| B.3  | Saturation Region Output Conductance Parameters                                  | 184 |

## Acknowledgments

I would like to take the opportunity to express my gratitude towards many people who have assisted me in this work. Firstly, I must give the greatest of thanks to my supervisor, Prof. Andy Tyrrell and co-supervisor, Dr. Martin Trefzer, for their valuable ideas, countless suggestions, support and encouragements throughout the last four years. Particularly, he and Martin devoted a lot of time and patience to the reading and correction of this thesis. I also must thank my colleagues and mentors Dr. James A. Walker and Dr. Simon Bale, for their fruitful suggestions, discussions and progress of my research. I also would like thank to Dr. Scott Roy for his valuable advice and ideas on device research, discussions, support and for helping with my publications reading and correcting.

I would then like to thank everybody else on the PAnDA project and everybody in the Intelligent Systems Group at University of York, for their knowledge and support. Last but not least, I want to thank my family, especially my dad and mum, who have always been there, without their endless support, I could not have finished this.

This work would not have been possible without funding from the EPSRC PAnDA project.

## Declaration

The work presented in this thesis is the author's own work, unless it is stated otherwise. The following items have been previously published during this research.

- Y. Xiao, M. A. Trefzer, J. A. Walker, S. J. Bale and A. M. Tyrrell, Two Step Evolution Strategy for Device Motif BSIM Model Parameter Extraction, 15th IEEE Congress on Evolutionary Computation (CEC14), pp. 2877-2884, Beijing, China, Jul, 2014.

- Y. Xiao, M. A. Trefzer, S. Roy, J. A. Walker, S. J. Bale and A. M. Tyrrell, Circuit Optimization using Device Layout Motifs, 5th European Workshop on CMOS Variability (VARI), pp.1 6, Palma, Spain, Sep, 2014.

- Y. Xiao, J. A. Walker, S. J. Bale, M. A. Terfzer and A. M. Tyrrell, Circuit Design Optimisation Using a Modified Genetic Algorithm and Device Layout Motifs, 11th IEEE International Conference on Evolvable Systems (ICES), pp.1-8, Orlando, USA, Dec, 2014.

- Y. Xiao, S. Roy, S. J. Bale, J. A. Walker, M. A. Terfzer and A. M. Tyrrell, Variationaware Circuit Performance Optimisation Using Multi-Stages Evolutionary Algorithm and Motifs, *IEEE Transactions on VLSI* (Under review).

# Hypothesis

Circuit performance improvement and variability mitigation can be achieved through a combination of evolutionary algorithms and device layout motifs.

### Chapter 1

## Introduction

#### Contents

| 1.1 | Motivation                 | 1 |

|-----|----------------------------|---|

| 1.2 | Aims and Objectives        | 3 |

| 1.3 | Organisation of The Thesis | 3 |

### 1.1 Motivation

Since the first integrated circuit flip-flop with two transistors was built by Jack Kilby in 1958 at Texas Instruments, there has been an unprecedented growth of the semiconductor industry. In 1971, Intel's 4004 microprocessor integrated 2300 transistors [1]. This number increased to 5 billion transistors in Microsoft's Xbox One Main SoC in 2013 [2]. On the economic side, the semiconductor industry business has grown worldwide in sales from \$1 billion in 1970 to \$250 billion in 2007, and has reached \$335.8 billion in 2014 [3]. The driving force behind this incredible growth comes from continuous miniaturisation of transistors and improvements in manufacturing techniques (Figure 1.1 shows that microprocessors' evolution obeys Moore's law [4]). As transistor feature size gets smaller, device become faster, have higher packing density, lower power dissipation and are cheaper to manufacture. However, as process technology scales down beyond 100-nm feature size, the traditional VLSI design approach needs to be modified to cope with the new challenges arising related to process variation, interconnect processing difficulties, and other newly exacerbated physical effects.

Many circuit designers spend much of their effort specifying function with hardware description languages and seldom look at actual transistor characteristics. This results in the isolation of device engineers from circuit design engineers who lack an understanding of the

Figure 1.1: A comparison of the transistor counts in various microprocessors, with a curve showing the projected counts following Moore's predictions of a doubling every 24 months [4].

impact of design upon performance, yield, and manufacturability owing to the fundamental limitations of technology and device physics at the nanometer scale. Thus, it is necessary to propose practical guidelines and methodologies to bridge from physical processing to circuit design to build an understanding of integrated circuits from the bottom up, helping circuit designers to avoid some of the pitfalls due to these technology constraints.

This thesis is concerned with these issues and considers a novel concept based on, 'motif', fundamental geometrical forms that uses these as design units to investigate device/circuit performance and its variability characteristic. The proposed methodology optimises circuits' performance through automatic optimisation of circuits constructed using motif permutations and adjustment of motif geometry. A set of motifs are proposed that provide different layout choices for transistor. Evolutionary algorithms are automatically selected appropriate motif choices for each transistor in the circuit. The whole circuit layout can be seen as different motifs' combination. Various motif permutations lead to the difference in circuit performance. Additionally, motifs' geometry sizes are adjusted by evolutionary algorithms in order to further improve circuit performance and decrease the influence of device variability on circuit performance.

### 1.2 Aims and Objectives

The aim of this thesis is to propose a methodology to optimise circuit performance and examine the problem of variability at atomic levels. In order to achieve this aim, the thesis has the following objectives:

- To propose various novel motifs based on fundamental geometrical form and investigate their characteristic through 3D device layout structure modelling, and atomistic simulation techniques (in Chapter 3);

- To simulate large ensembles of device layout motifs including a major variability source, line edge roughness, in deep sub-micron devices, and perform statistical analysis to find out the influence of intrinsic parameter fluctuations on motifs (in Chapter 3);

- To develop a novel tool based on bio-inspired approach to extract the atomistic device simulation results to generate corresponding compact model so as to bridge device simulation and circuit simulation (in Chapter 5);

- To develop a novel methodology, combining motifs and evolutionary optimisation algorithm, in order to achieve both circuit performance optimisation and variability-aware design (in Chapter 6).

### **1.3** Organisation of The Thesis

The outline of this thesis is organised as follows: Chapter 2 reviews the background associated with device scaling and corresponding challenges that come from lithography limitation, physical effects, and transistors variability. The transistor variability classification, sources of variability, and the impact of variability on device/circuit performance are comprehensively described.

Chapter 3, presents the novel concept, 'motif', and how to investigate its characteristics at the device level. Motif is a generic scheme based on fundamental reused geometrical forms that prove convenient for increasing design regularity and examining the device/circuit problem of atomistic variability. A statistical motifs simulation methodology is introduced to investigate motif characteristics and their relationship with statistical variability. Finally, statistical analysis is carried out to show the distribution of motif statistical parameters.

Chapter 4 gives an outline of the field of evolutionary algorithms, incorporating basic knowledge of evolutionary mechanisms and the main operations in evolutionary algorithms. Additionally, some of the issues related to the application of evolutionary algorithm on VLSI design are described.

Chapter 5 introduces statistical motif compact model generation processes. The extraction process is divided into two stages. The first stage is uniform model extraction that is performed by a novel bio-inspired tool, which uses an incremental evolutionary algorithm to extract model parameters from device simulation results. The second stage is statistical variability generation, where parameter variations following a specific distribution are injected into uniform models to achieve variability-enhanced motif compact model.

Chapter 6 proposes a methodology to combine evolutionary algorithm and motif to achieve circuit performance optimisation. A set of possible motif permutations is tested to build benchmark circuits to find the "appropriate" permutations to achieve the best circuit performance.

Finally, concluding remarks and observations are given in Chapter 7 in addition to suggestions for future work. In order to easily understand the thesis structure, an organisation diagram is drawn in Figure 1.2.

Figure 1.2: The thesis organisation diagram, which summaries main chapters' topics, key observations (represented by  $\triangleright$ ) and points of interest (represented by  $\bullet$ ).

### Chapter 2

# **Transistor Scaling and Variability**

### Contents

| <b>2.1</b> | Scal           | ing of Transistor Device                                    | 8         |

|------------|----------------|-------------------------------------------------------------|-----------|

|            | 2.1.1          | Scaling Principle                                           | 8         |

|            | 2.1.2          | Scaling Challenges                                          | 10        |

|            |                | Lithography Challenges                                      | 10        |

|            |                | Direct Tunneling Gate Leakage Current                       | 12        |

|            |                | Threshold Voltage Variations                                | 12        |

| 2.2        | Trar           | nsistor Variability Classification                          | 15        |

|            | 2.2.1          | Random/Stochastic Variation                                 | 15        |

|            | 2.2.2          | Systematic Variation                                        | 15        |

| <b>2.3</b> | Sour           | cces of Stochastic Variability                              | 17        |