# On a Layered Object—Space Based Architecture for Interactive Raster Graphics

door

Fons Kuijk

geboren op 22 mei 1955 te Haarlem Promotor:

Prof. Dr. L.O. Hertzberger (UvA) Prof. E.H. Blake (University of Capetown) Wiskunde en Informatica Copromotor:

Faculteit:

# Contents

| Co      | Contents |                                                         |    |  |  |

|---------|----------|---------------------------------------------------------|----|--|--|

| Preface |          |                                                         |    |  |  |

| 1:      | Intr     | oduction                                                | 1  |  |  |

|         | 1.1:     | Graphics and Human-Computer Communication               | 1  |  |  |

|         | 1.2:     | Background                                              | 3  |  |  |

|         | 1.3:     | Towards a New Architecture                              | 5  |  |  |

|         | 1.4:     | The STW Research Project on Interactive Raster Graphics | 6  |  |  |

|         | 1.5:     | Outline of the Dissertation                             | 8  |  |  |

| 2:      | Gra      | phics Systems and Interaction                           | 9  |  |  |

|         | 2.1:     | Interactive Graphics: Concepts and Nomenclature         | 9  |  |  |

|         |          | 2.1.1: Scene Specification                              | 10 |  |  |

|         |          | 2.1.2: Image Synthesis                                  | 10 |  |  |

|         |          | 2.1.3: Graphical Input                                  | 12 |  |  |

|         |          | 2.1.4: Graphical Interaction                            | 14 |  |  |

|         | 2.2:     | An Overview on Interaction Tasks                        | 16 |  |  |

|         | 2.3:     | Temporal Aspects of Interaction                         | 19 |  |  |

|         |          | 2.3.1: Animate Response                                 | 20 |  |  |

|         |          | 2.3.2: Computer Animation                               | 22 |  |  |

|         |          | 2.3.3: Discussion                                       | 24 |  |  |

|         | 2.4:     | Dealing with Motion                                     | 25 |  |  |

|         |          | 2.4.1: Temporal Anti-aliasing                           | 25 |  |  |

|         |          | 2.4.2: Adaptive Image Generation                        | 25 |  |  |

|         | 2.5:     | Conclusions                                             | 29 |  |  |

| 3:      | Rast     | er Graphics Hardware                                    | 31 |  |  |

|         | 3.1:     | Introduction                                            | 31 |  |  |

|         | 3.2:     | An Overview on Hardware Elements                        | 32 |  |  |

|         |          | 3.2.1: Display Device                                   | 32 |  |  |

|         |          | 3.2.2: Display Controller                               | 35 |  |  |

|         |          | 3.2.3: Frame Buffer                                     | 36 |  |  |

|         |          | 3.2.4: Graphics Processor                               | 40 |  |  |

|    | 3.3: | Concurrency and Graphics Systems          | 41  |

|----|------|-------------------------------------------|-----|

|    |      | 3.3.1: Introduction                       | 41  |

|    |      | 3.3.2: Architecture Based Classification  | 42  |

|    |      | 3.3.3: Distribution Based Classification  | 43  |

|    |      | 3.3.4: Discussion                         | 46  |

|    | 3.4: | Conclusions                               | 48  |

| 4: | A La | yered Object-Space Based Architecture     | 49  |

|    | 4.1: | Introduction                              | 49  |

|    | 4.2: | Abstract Computational Model              | 51  |

|    | 4.3: | Output Representation                     | 54  |

|    | 4.4: | A Multilayer Computational Model          | 56  |

|    | 4.5: | Discussion                                | 58  |

|    |      | 4.5.1: Hidden Surface Removal             | 60  |

|    |      | 4.5.2: Illumination and Shading           | 61  |

|    |      | 4.5.3: Display Controller                 | 62  |

|    | 4.6: | Conclusions                               | 62  |

| 5: | Deal | ing with Geometry                         | 65  |

|    | 5.1: | Introduction                              | 65  |

|    | 5.2: | Representation of Geometry: the Domain    | 68  |

|    |      | 5.2.1: The Use of Extents                 | 68  |

|    |      | 5.2.2: Area Representation                | 70  |

|    | 5.3: | Efficient Storing of Domains              | 78  |

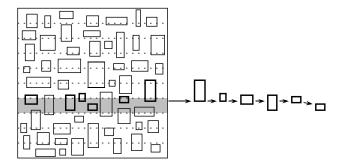

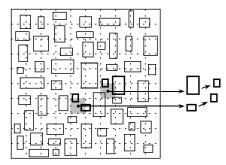

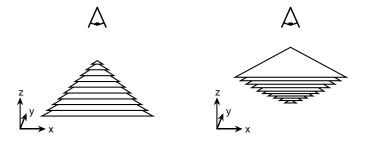

|    |      | 5.3.1: Slice-List Structure               | 79  |

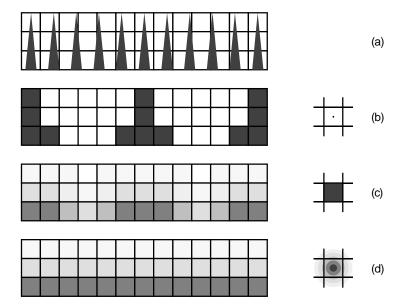

|    |      | 5.3.2: Grid-List Structure                | 82  |

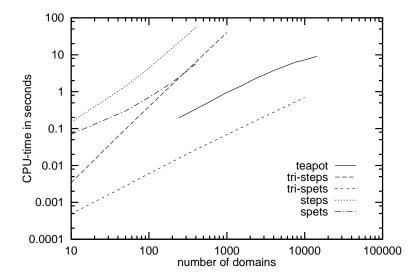

|    |      | 5.3.3: Results                            | 85  |

|    |      | 5.3.4: Conclusions                        |     |

|    | 5.4: | Exact Incremental Hidden Surface Removal  | 105 |

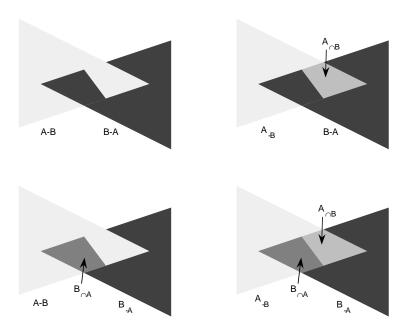

|    |      | 5.4.1: Binary Operations                  | 106 |

|    |      | 5.4.2: Basics of the Algorithm            |     |

|    |      | 5.4.3: Reducing Complexity                |     |

|    |      | 5.4.4: Referencing                        |     |

|    |      | 5.4.5: Adding a Domain                    |     |

|    |      | 5.4.6: Removing a Domain                  |     |

|    |      | 5.4.7: Distributed Hidden Surface Removal |     |

|    |      | 5.4.8: Results                            |     |

|    | 5.5: | Scan-Conversion                           |     |

|    |      | Conclusions                               | 114 |

| 6: |      | nination and Shading of Polygonal Models  | 115 |

|    | 6.1: | Introduction                              | 115 |

|    | 6.2: | Illumination & Shading                    | 116 |

Contents

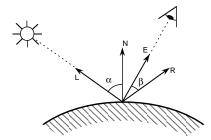

|       |                 | 6.2.1: Illumination Model                             | 116  |

|-------|-----------------|-------------------------------------------------------|------|

|       |                 | 6.2.2: Shading Methods                                | 118  |

|       |                 | 6.2.3: Discussion                                     | 120  |

|       | 6.3:            | Interpolation Across Polygons                         | 122  |

|       |                 | 6.3.1: Vector Interpolation                           | 122  |

|       |                 | 6.3.2: Angular Interpolation                          | 124  |

|       | 6.4:            | Evaluation of the Intensity Components                |      |

|       | 6.5:            | Discussion                                            | 134  |

| 7:    | An (            | Object-Space Display Controller                       | 137  |

|       | 7.1:            | Introduction                                          | 137  |

|       | 7.2:            | Unfolding the Scan-Conversion process                 | 138  |

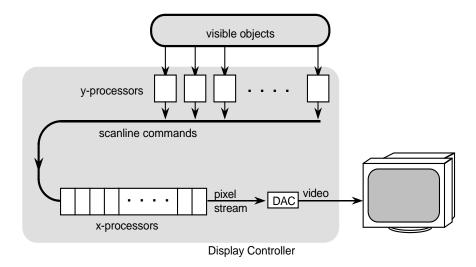

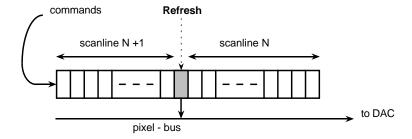

|       | 7.3:            | Architecture of the Display Controller                | 140  |

|       | 7.4:            | The X-Processor Array — or Difference Engine          | 141  |

|       |                 | 7.4.1: Basics of the X-Processor Array                | 142  |

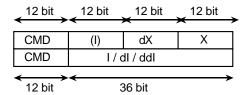

|       |                 | 7.4.2: The Command Set                                | 143  |

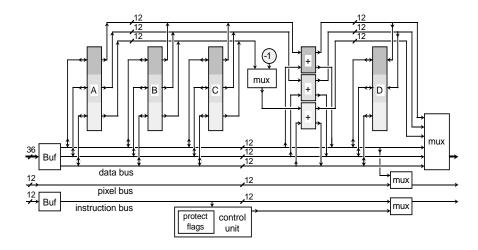

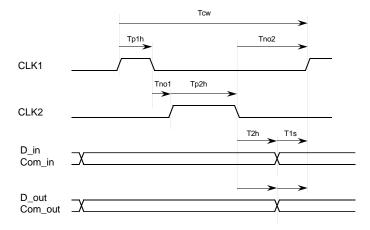

|       |                 | 7.4.3: Implementation of the Difference Engine        | 145  |

|       |                 | 7.4.4: Structural Simulation of the Difference Engine | 149  |

|       |                 | 7.4.5: Features and Estimated Performance             | 152  |

|       |                 | 7.4.6: Virtual Arrays                                 | 155  |

|       | 7.5:            | Driving the Difference Engine                         | 158  |

|       | 7.6:            | Building a Prototype                                  | 159  |

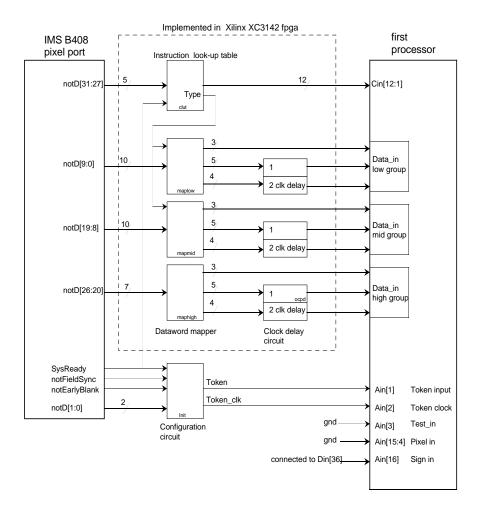

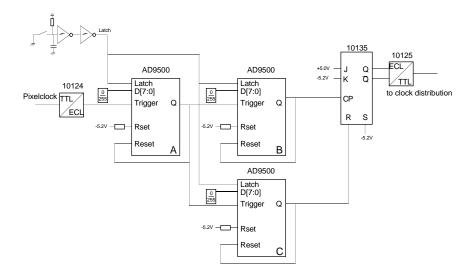

|       |                 | 7.6.1: System Components                              | 160  |

|       |                 | 7.6.2: Board Level Components                         | 163  |

|       |                 | 7.6.3: Physical Design                                | 167  |

|       | 7.7:            | Results                                               | 169  |

|       | 7.8:            | Discussion                                            | 169  |

| 8:    | Conc            | clusions                                              | 171  |

| Ac    | know            | eledgements                                           | 175  |

| Re    | feren           | ces                                                   | 177  |

| Δr    | nend            | ix A: Driving the Difference Engine                   | 201  |

| · × P | _               | A Full Colour System                                  |      |

|       |                 | Bus Arbitration                                       |      |

|       |                 | The Instruction and Colour Buffer                     |      |

|       |                 | The Y-Processor                                       |      |

|       |                 | Conclusions                                           |      |

|       | $\Lambda . J .$ | Concresions                                           | 41 I |

# **Preface**

This dissertation is on the development of an interactive raster graphics system for CAD-type of applications which inherently supports direct manipulation of three-dimensional objects. This feature in particular serves to help the user to understand the three-dimensional geometry of virtual objects as if these objects could be observed and manipulated in the real world.

A graphics system is an essential and conceptually separable part of a workstation. It is a key element for the so-called user interface via which interaction between the application program and the user takes place. The success of the user interface concept and the increased capabilities of workstations stimulated more visually oriented communication. However, each new generation of workstations is expected to be able to handle an increased amount of data and facilitate more demanding visualisation and interaction techniques. This forms the motivation for continuous research on interactive three-dimensional graphics systems for workstations.

The aim of the research described in this dissertation has been to develop a new architecture for an interactive graphics workstation, targeted for displaying three-dimensional polygonal models. Interactivity of a graphics system can be improved by speeding-up the image generation pipeline and/or by reducing the amount of calculation needed to generate successive frames. We concentrated on the latter and found that standard implementations of the image generation pipeline do not provide sufficient functionality for interactive applications.

We concluded that the amount of calculation can be kept low by providing precisely that functionality required for interaction. We state that a layered structure and a consistent raster independent object-space approach are key elements of a more appropriate architecture. The layered structure of the system we propose allows us to make optimal use of incremental algorithms. However, a consequence of this approach is that we have to make use of less common image generation algorithms and non-standard image generation hardware.

For instance, the raster independent object-space paradigm implies that the system requires object-space hidden surface removal. We found that object-space hidden surface removal algorithms can confine update activities needed for incremental changes to just those objects of which the visibility is changed.

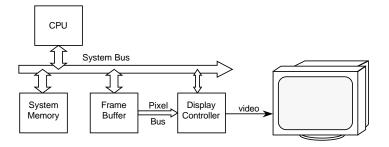

Another consequence is that there is no mandate for a frame buffer. At high update rates a frame buffer becomes a bottleneck and does not bring any extra

functionality for interaction. (For a user, the smallest pick primitive is a visible object, not a pixel.) Leaving out a frame buffer implies that the display controller has to produce the pixels of fully shaded primitives — that may even be illuminated by multiple light sources — at a rate of about 80 Mhz, depending on resolution.

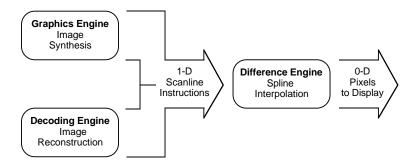

We came up with a two-tier modular structured display controller. A high quality illumination model was formulated that maps directly onto this architecture. Worth noting is that the functionality of the custom modules of the display controller is based on an abstraction of the fundamental aspects of image generation. As a result of this, the architecture does not restrict to a specific type of primitive or a specific type of rendering. Even more so, the architecture has proven to be useful for image reconstruction as well [Marais 93].

*Preface* ix

# Introduction

#### Synopsis.

Communication between a computer and a user is one of the fundamental issues in the discipline of computing. In this chapter the role that interactive graphics plays in human-computer communication is highlighted. The design of interactive graphics systems should not be focussed on computing resources alone, since this often leads to inefficient brute force systems that lack the flexibility required for high speed interaction. This notion triggered the proposal of a research project named "A new Architecture for Interactive Raster Graphics based on VLSI". The objectives and the context of this project are described. Subsequently the outline of the dissertation is sketched.

# 1.1. Graphics and Human-Computer Communication

"This area deals with efficient transfer of information between humans and computers and with information structures that reflect human conceptualisation. Fundamental questions include: What are efficient methods of representing objects and automatically creating pictures for viewing? What are effective methods for receiving input or presenting output? How can the risk of misperception and subsequent human error be minimised? How can graphics and other tools be used to understand physical phenomena through information stored in data sets?" [Denning 89]

This quote refers to the area of Human-Computer Communication. It is one of the nine subareas of the discipline of computing identified in the *Report of the ACM Task Force on the Core of Computer Science* [Denning 89]. The fundamental questions mentioned in this quote illustrate the significance of pictures as an information transfer medium from computers to humans.

The important role visual information exchange plays in Human-Computer Communication is justified by the characteristics of human vision. The human visual system is a most powerful image cognition machine that is able to perceive, analyse, classify and evaluate a great deal of information in real-time [Gro $\beta$ 91]. The processing power of today's super computing systems does not even come near

to the processing power of the human visual system. The human visual system has a high input bandwidth, a well developed ability to recognise patterns and dynamic changes, and an adequate three-dimensional reconstruction capability. Thus, communication via pictures is a natural and powerful way to present information to people.

"Interactive computer graphics thus permits extensive, high-bandwidth user-computer interaction. This significantly enhances our our ability to understand data, to perceive trends, and to visualise real or imaginary objects — indeed, to create "virtual worlds" that we can explore from arbitrary points of view. By making communication more efficient, graphics makes possible higher-quality and more precise results or products, greater productivity, and lower analysis and design costs." [Foley90]

A graphics system 1) gives access to this high performance computer-to-user communication channel by providing the facilities for a computer application to generate pictures. Hardware facilities for graphics based human-computer communication — a high resolution display and a fair amount of computing resources — are standard features of today's desk-top workstations.

The raster graphics system became a key element of the user interface via which interaction of the application program and the user takes place. The 'desk-top metaphor' is an example of a first generation 2D graphics user interface. It allows the user to manipulate electronic documents and folders via windows on the screen much like the user is used to handle hardcopy documents and folders on his desk. These first generation window systems clearly demonstrated the efficiency of direct manipulation and other types of visualised interactive control of computer applications. This successful debut created a demand that positively influenced the evolution in workstation technology we saw in the last decade. In turn, the increasing performance of workstations triggered a demand for higher level and more demanding interaction. As a result we find that today the imperative need for high speed interactive computer graphics is discerned.

"Computer graphics has always been an expensive proposition and its users a demanding, unsatisfied lot—the picture never got on the screen fast enough, or later, never moved fast enough once it got on the screen, and then, the picture was never sharp enough, never realistic enough." [Fuchs 88]

Nowadays, an almost standard requirement is that a workstation should be able to render realistic pictures of user manipulable three-dimensional objects in real-time. Realistic pictures involve high resolution display systems and advanced shading models. Rendering this type of highly complex models (>100K coordinates) in

<sup>1)</sup> In this dissertation the concept 'graphics system' is taken to be an abstraction; in this view a graphics system may share resources with the application and the term graphics system relates to both hardware and software elements.

2. Background

real-time (typically <0.1 seconds) takes considerably more computing resources than offered by present day workstations.

The need for realistic graphics and highly interactive systems, however, is growing in application areas such as design, engineering, scientific visualisation, real-time control systems, simulation, animation and interactive education systems. As a result of experiments with visualisation techniques and an increased understanding of the characteristics of visual perception the added value of dynamically varying pictures has been shown.

Based on these trends it is to be expected that visual communication will continue to play a leading role in human-computer communication. To satisfy the 'demanding, unsatisfied lot', it is not sufficient to rely on developments in hardware technologies alone. In fact these developments put extra strain on graphics systems designers, since increased capabilities of computing systems increase the complexity of applications and consequently increase the demand on performance of graphics systems even more. This justifies the ongoing research effort on interactive graphics systems.

# 1.2. Background

Within the CWI department of Interactive Systems, research has been focussed on fundamental problems occurring in communication between a computer system and the real world, and on the design and construction of systems that provide the mechanism for this communication.

For the group Computer Graphics — one of the three research groups within the department — communication by means of pictures has been and still is the leading theme. This group has a long tradition in research on structuring of information describing pictures. Throughout the years, this resulted in the design of ILP (Intermediate Language for Pictures) [Hagen 80], involvement in the design of GKS (Graphical Kernel System) [ISO85b] and research activities for a STW funded project titled "Raster Graphics Facilities" (NWI14.0130).

Within the department of Interactive Systems, a closely related research theme —human computer interaction — was undertaken to improve basic support for interaction in graphics systems. This research included aspects like control flow, interaction techniques, resource management and graphics support. It resulted in the development of DICE (DIalogue CEll system), a user interface management system [Schouten 90].

In the course of these projects it became apparent that the characteristics of ergonomically acceptable user interfaces are correlated to the characteristics of the underlying hardware. From a user interface implementor's perspective, existing architectures rarely facilitate the appropriate feedback mechanisms in a natural way. This is due to the fact that hardware architectures of current generation 3D raster graphics systems scarcely differ from architectures of 2D raster graphics systems. Systems may be equipped with Z-buffer hardware or transformation coprocessors, however, that does not imply that the evolution to genuine 3D architectures is

completed. One can state that architectures of today's systems and the algorithms used are too much image (= 2D) oriented. Genuine 3D architectures will have to be different. In a sense the success of existing raster graphics systems seems to turn against itself: it is hard to change directions <sup>2)</sup>. It is also hard to fulfill the diversity of interaction requirements of the numerous types of applications we find today. Most existing 'high end' graphics systems are too specific and lack the flexibility required for high speed interaction. This lack of flexibility is manifest in both the static nature of the application interface and the static semantics of the image generation pipeline.

Even the most successful graphics systems provide a fixed collection of primitives, attributes, and storage schemes. A static application interface leads to tedious specifications for those applications that use primitives which do not fall in a system's fixed collection. A lengthy decomposition process must be done by the application in order to use the primitives available in a graphics package. Not only does this make the application more complex, it also degrades the interactive behaviour of the system in case the decomposition becomes part of the interaction process.

All graphics systems define a pipeline through which a primitive passes when it is rendered. The attribute binding and storage of intermediate representations are fixed by the static semantics of the pipeline. Facilities may be provided to access the pipeline at intermediate stages, but this does not guarantee that the amount of calculation involved in interaction tasks are minimised. Intermediate representations may for instance force recalculation of geometric aspects of the primitive in situations where only attributes have been changed. This suggests a reappraisal of the 3D raster graphics pipeline and of the representation of the primitives that pass the pipeline.

This is the setting from which a project proposal emerged. The objective of the proposal, titled "A new Architecture for Interactive Raster Graphics based on VLSI", was the design and realisation of an experimental interactive 3D graphics system. The research focuses mainly on the semantics of the image generation pipeline. The project would familiarise us with less academic but weighty issues of hardware design and at the same time produce a competitive system which would enable further experiments on interaction techniques.

<sup>&</sup>lt;sup>2)</sup> The "2D trap" is being dug deeper and deeper. Adding 3D to a 2D frame buffer was easiest via the Z-buffer. Then came the A-buffer. Finally everything became texture mapping — even the light calculations. The grave has been dug, the coffin is being lowered. It, must be admitted, is a very pretty and realistic coffin and the wisps of mist around the graveyard are very well done. But we want to start out in 3D (i.e., no flat tree bitmaps that are directed towards the viewpoint).

#### 1.3. Towards a New Architecture

The STW <sup>3)</sup> funded project "A new Architecture for Interactive Raster Graphics based on VLSI" (CWI79.1249) has been assigned to the CWI from September 1986 up to April 1993. The project involved the design and implementation of a prototype highly interactive raster graphics workstation. This dissertation covers parts of the work done for this STW funded project. A research group from the Laboratory for Network Theory of the University of Twente participated in this project, in particular for the design of the VLSI components. In a later stage people from the faculty of Mathematics and Computer Science from the University of Amsterdam succeeded in integrating the VLSI components in a test environment.

Central to the approach of the project is an explicit concern about the underlying data structures used to represent geometric objects. This originates from the conviction that only through careful design of appropriate graphic data structures and algorithms one can profitably map software tasks into hardware, specifically into VLSI. These data structures have to be simple to be useful for implementation in VLSI. The same strategy that produced the RISC revolution should be applied here: first analyse, then strive for simplicity.

In the view of this project, interaction is facilitated by exploiting an optimised architecture of the image generation pipeline, associated by a new type of graphics primitive, introduced in [Hagen 86b]. The primitive envisioned, named *pattern*, describes the visual aspects of an area of the image. The representation of a pattern is optimised for the most critical operations that have to be performed on it. New functionality is embedded in the system's architecture to support feedback for interaction. The functionality that is supported by the system will reflect functionality offered by PHIGS [ISO89] and HIRASP [Teunissen 88] but needs extensions to be able to facilitate more advanced interaction techniques. Some of the user interface aspects of this functionality originates from the aforementioned STW project "Raster Graphics Facilities".

"By and large, the designs of commercially available products have been motivated primarily by a bottom-up concern with cost-effective hardware technology that meets performance constraints and not by a more general top-down, 'software-first' strategy based on user requirements. A proper top-down strategy would not only include cost-effectiveness and performance, but would also take into account programmability and extensibility. The preoccupation with hardware is understandable in the light of the concern with performance, as measured only by the number of elements processed per refresh cycle for a flicker-free display." [Foley 82]

From a user requirements perspective the design of a graphics system should preferably be based on a top-down, software-first strategy. In a proper design cycle chronologically the following activities are undertaken:

<sup>&</sup>lt;sup>3)</sup> STW stands for "Stichting voor de Technische Wetenschappen" (that is: Foundation for Technical Sciences).

- characterisation of algorithms, data-structures and requirements;

- construction of a symbolic model;

- simplification and verification of the symbolic model;

- design of a physical system;

- implementation of the physical system;

- testing and maintenance.

Unfortunately, following these steps does not guarantee a 'first-time-right' design. The transition from software (the symbolic model) to hardware (the physical system) is a delicate step. One has to bridge the significant gap between our conception of notations and our conception of devices.

"In software the gap is seen in the comparison of the theoretical complexity of a program and the empirical performance. Calculations based on models at different levels of abstraction can be refined to make estimates of the number of clock cycles required, en route to estimates of run-times in seconds that may be tested. (...)

In hardware the gap is seen in the essential role that timing and performance play in the many notions of specifications and correctness criteria for devices. In a sense, each model of computation for hardware design attempts to bridge, or more accurately, hide this gap." [McEvoy90]

The raw performance of interactive graphics systems is often decisive for the success or failure of a product, for which reason all noteworthy graphics systems are implemented using leading edge technology. Computer graphics has always been strongly influenced by hardware technology. Each step in the evolution of hardware technology made it possible to improve algorithms, improve shading models and increase the complexity of representations.

Due to the everlasting demand for more system performance, a top-down design strategy quickly tends to lead to a design of the 'ultimate' graphics system. Consequently, it is unlikely that for state-of-the-art systems a software-first strategy results in first-time-right abstractions that can be implemented in a cost-effective system, or even worse, that can be implemented at all. Therefore, the realisation of a system (in software as well as in hardware) has to be an iterative process.

#### 1.4. The STW Research Project on Interactive Raster Graphics

The following stages of the project could be distinguished.

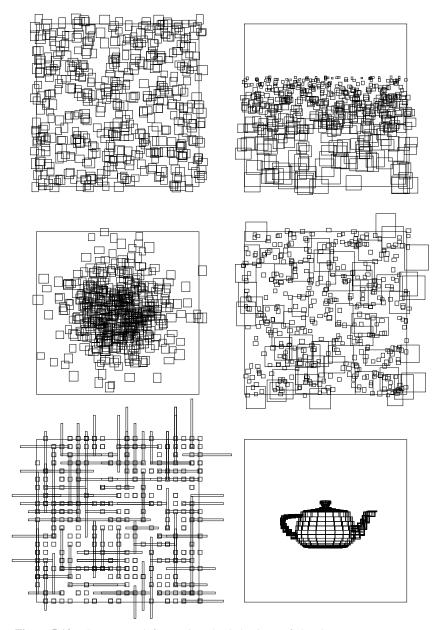

The first part of the project adhered to the software-first strategy. Activities included characterisation of requirements, data-structures and algorithms, in particular the algorithms involved in creation, manipulation and display of patterns. It also involved the construction and verification of a model of computation. Based on this model, critical modules that were candidate for VLSI implementation were identified.

Next the activities involved specification of modules, influenced by more technical and practical conditions. Given the context of the project it was clear that a physical implementation of the model of computation would go with trade-offs between the initial specification and the technological constraints and limited resources we find in an academic environment. A physical implementation of even a simplified version of the model was considered to be of importance to demonstrate the viability of the system, in particular for those parts of the system that outstandingly differ from the conventional.

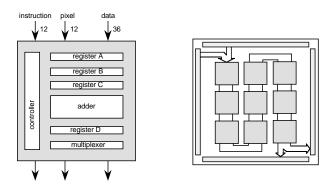

With this awareness in mind, the selection of the modules that could actually be implemented in VLSI was made. As a result, this stage was characterised by a bottom-up concern with hardware technology — though conform the skeleton produced by the preceding top-down design phase. In this phase of the project it became clear that, technologically speaking, the lowest level of the architecture — viz., the display controller — was the most demanding and outstanding element of the architecture. This display controller has a two-phase structure: a level that is resposible for producing the pixels and a level that scans visible objects.

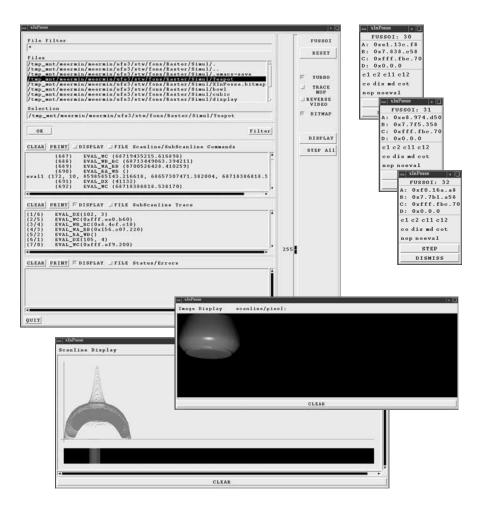

For the first level of the display controller —viz., the real-time pixel generator — no adequate components could be found on the market. For the targeted display resolution, fully shaded pixels have to be produced every 12 ns. Some elements of current general purpose processors may operate at such high rates. However, bus access rates are limited to a rate which is insufficient to sustain even a 25 MHz pixel stream needed for medium resolution displays. Therefore we concluded that the pixel-producing part of the display processor had to be implemented in custom VLSI. The actual design of the chip was done at the University of Twente. At the CWI the instruction set was verified by means of a structural simulator. This simulator both validates the functional design and visualises the results of newly designed graphics algorithms. With help of people from the UvA, the chips are recently integrated in a first version prototype to demonstrate the feasibility and the potential image quality of the system.

The second level of the display controller — viz., the object scanners — is not critical from a technological point of view. For future implementation, custom modules for bus arbitration and buffering purposes are specified and partly designed (but not implemented yet). These modules would serve to integrate an array of general purpose processors with the pixel generator.

#### 1.5. Outline of the Dissertation

So far the STW funded research project has been motivated and placed in context. This dissertation is based on several research activities involved in this project. It should as such not be seen as a report on all the research activities that took place.

Chapter 2 is a survey of graphics systems and interaction. An inventory of interaction mechanisms is presented. Next the temporal aspects of interaction and the use of adaptive algorithms as a potential means to satisfy temporal constraints are discussed. Chapter 3 surveys existing graphics system architectures. Different

strategies to implement multi-processor architectures and characteristics are discussed. In Chapter 4 we find the theses of this work. It is argued that the variety of interaction mechanisms that exist are best served by a hierarchical architecture. A layered object-space architecture is proposed. It is illustrated how such a hierarchical architecture excels in support of interaction. The implications of this model of computation on some fundamental aspects are discussed. Chapter 5 is on consequences of the approach on aspects of geometry. It discusses representation of objects, structures for data storage and geometry based operations — i.e., a hidden surface removal algorithm which can handle incremental changes and scanconversion. The rendering of the visible objects is described in Chapter 6. A reformulated high quality local illumination model is presented that is well suited to be implemented on scan-conversion hardware. Chapter 7 discusses the design and implementation of an object-space display controller — a two-phased architecture which can refresh a display from a structured list of objects. It is shown how this real-time scan-conversion system offers scalability and flexibility. Finally, in Chapter 8 results obtained are evaluated and future work is discussed.

# **Graphics Systems and Interaction**

#### Synopsis.

This chapter is on aspects of graphics systems in relation with interaction. It begins with a survey of the concepts and terminology of both graphics systems and interaction. Next an inventory of basic interaction tasks is made since we suspect a relation between the response time of an interactive graphics system and how well required input can be mapped on interaction facilities available. Following this, temporal aspects of image generation are addressed. Finally we discuss adaptive methods as the potential means to meet timing requirements.

# 2.1. Interactive Graphics: Concepts and Nomenclature

"With interactive graphics, we are largely liberated from the tedium and frustration of looking for patterns and trend by scanning many pages of linear text on line printer listings or alphanumeric terminals." [Foley82]

A computer application may find the need to display an abstract, or realistic entity, called a *scene*. For this purpose, an application makes use of a *graphics system* which provides facilities to:

- specify (or model) a scene in terms of a set of logical graphical elements;

- specify parameters according to which the scene is transformed into an *image*;

- handle *graphical input*.

In this work, the graphics system is taken to be the whole of the language through which a programmer can specify pictures and input handling, and the hard- and software modules needed to generate those pictures and provide that input. An application is considered to be *interactive* if the user has ways to influence the behaviour of the application during the execution of the program.

#### 2.1.1. Scene Specification

A scene is the mathematical representation of what has to be displayed. It is constructed by means of logical graphical elements, called *primitives*. Primitives incorporate two components: the *geometry* and an associated set of *attributes* (or *properties*).

The geometry of a primitive defines a set of points  $(P_{prim})$  in a vector space,  $P_{prim} \subseteq R^n$ . A scene specification language may have many types of primitives, where each type defines a certain basic geometrical form (such as a point, line, filled triangle, etc.). The minimal set of primitive types needed to adequately specify a scene is highly dependent on the type of application. International standard graphics systems such as GKS [ISO85b] and PHIGS [ISO89] offer a common set of graphical primitives.

Attributes specify how the geometry appears on the output medium (line type, transparency, colour, etc.). Each type of primitive has a specific set of attributes. Attributes are not necessarily bound to individual primitive instances, they may be bound to a group of primitives or can even be global.

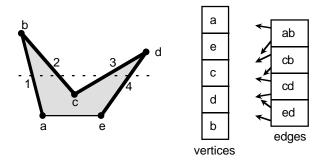

Instances of primitives may be combined to form more interesting graphics objects. Examples of this can be found in graphics systems like ILP [Hagen 80], PHIGS and HIRASP [Teunissen 88]. These systems provide facilities for specification of hierarchically structured objects. The structuring results in a description of the scene in the form of a directed acyclic graph in which the constituent primitives can be found in the leaves of the graph.

#### 2.1.2. Image Synthesis

A scene is mapped onto the *display*- or *image-space*. This mapping includes both geometric and attribute transformations. The geometric transformation, specified by *viewing* parameters, maps the geometry of the primitives ( $\subseteq \mathbb{R}^n$ ) onto a geometry in the two-dimensional image-space ( $\mathbb{Z}^2$ ). The attribute transformation results in a function which assigns a colour intensity to each point of this two-dimensional geometry.

Net result of mapping of the scene onto the display space is a set of *display primitives*, which describe an image. The process to construct an image within the limitations of a display device is known as *rendering*. The type of display primitives in which the image is described depends on the type of display technology in play (plotter, laser printer, CRT, etc.). Due to the limitations of the display device, the rendered image can essentially be no more than an approximation of the picture specified by the scene and mapping parameters.

#### **Logical Model**

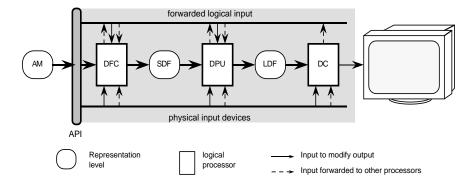

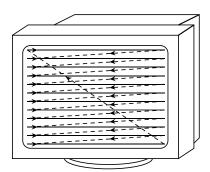

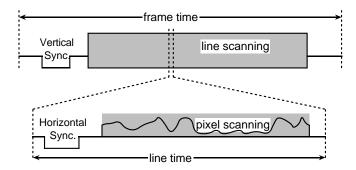

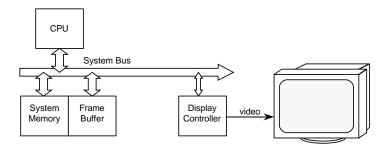

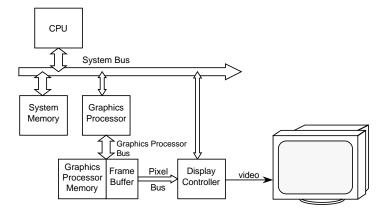

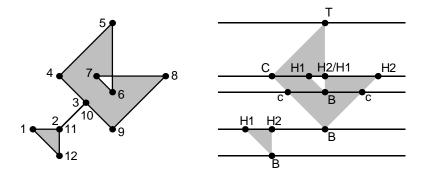

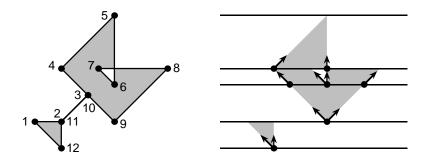

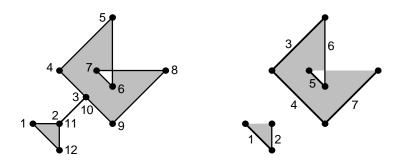

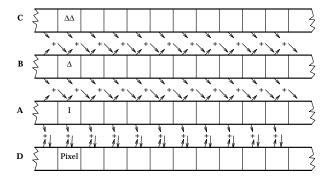

A logical model of the graphics system envisions the mapping of a scene onto the display space as a stepwise process in which primitives travel through a *pipeline* of functional modules [Carlbom 80]. This model distinguishes between the different logical representation levels of the scene that exist in the image synthesis pipeline and the operations applicable to these representations. In this logical model (shown

in Figure 2.1) each module of the pipeline performs an elementary graphical operation on all passing primitives. Each stage in the pipeline maps one logical representation of the scene onto another. Intermediate representations can be stored and made accessible to improve the response time of the system. The inherent display device dependence of the mapping process as a whole is confined to a mere subset of the modules of the pipeline.

**Figure 2.1:** Logical model of the image generation pipeline. AM - Application Model, API - Application Programmer's Interface, DFC - Display File Compiler, SDF - Structured Display File, DPU - Display Processing Unit, LDF - Linear Display File, DC - Display Controller.

#### **Logical Representation**

Application Model. The application model is the representation of a scene as determined by the application program. This scene is presented as a model from which specific graphical images can be composed. The application program can change the scene by editing its representation. Naming of parts of the representation is allowed and can be used to aid editing.

Structured Display File. The structured display file contains only graphical information of the scene, and is composed as a list of output primitives. The graphics system manages the content of the structured display file. The application program has access to this representation level only via the application interface.

Linear Display File. The linear display file contains the representation of the scene in a form designed for optimal refresh speed. For traditional raster displays the linear display file is the so-called 'frame buffer', a buffer in which an image is represented as a pixel pattern. The display holds the visible image.

#### **Logical Processes**

Between each pair of successive representations we find a logical processor. Logical processors accept input parameters by means of which the mapping process can be influenced. The user and/or the application program may indirectly control

these optional parameters.

*Display File Compiler.* The display file compiler maps the application model onto the structured display file. This mapping process can be parameterised, for instance by surface properties.

Display Processing Unit. The display processing unit maps the structured display file onto the linear display file. This computational expensive mapping involves processes like geometric transformations, hidden surface removal calculations, illumination calculations and clipping. The display processing unit can be parameterised by viewing and illumination settings.

Display Controller. The display controller maps the linear display file onto the screen. Also the display controller can be parameterised. For instance, to accommodate window management functions it may be possible to map parameterised portions of the linear display file onto the screen.

#### 2.1.3. Graphical Input

The image synthesis pipeline converts primitives — in terms of elements of the language an application understands — into display device dependent data. The reverse is true for *graphical input*. Graphical input originates from data that comes in via physical input devices. The raw data that input devices produce have to be converted into a more abstract form, that is, in terms of the language of the application.

Numerous input devices have been developed to facilitate graphical input. Examples of input devices are keyboard, tablet, mouse, lightpen, touchscreen, dial and data-glove. Of course these input devices differ in ergonomical aspects like physical dimensions, resolution and input bandwidth. They also produce data that may differ in aspects like range and dimensionality.

#### **Logical Model**

For current graphics systems, the device dependency of input data is hidden by making use of a *logical input model*. In a logical input model, data input takes place via *logical input devices*. The raw, device dependent input data are converted into a set of *input primitives*. Typical types of input primitives that can be found in all graphics systems are commands and geometrical data. The purpose of this abstraction is portability; mapping of device dependent input data onto input primitives is handled completely within the logical input model. Instances of elementary input primitives may be combined and mapped onto more complex input primitives before they are handed over to the application. The logical input model encapsulates all types of physical input devices and associated user actions. In this way, the application is unaware whether geometrical data is produced by a keyboard or by a pointing device.

#### **Logical Input Device**

The logical model of a graphical input device is shown diagrammatically in Figure 2.2. The output of a logical input device is an input primitive. Different classes of logical input devices exist corresponding to different types of input primitives. Each class has a well-defined data type for the measure reported by devices of that class. Current computer graphics standards support the classes: *locator*, *stroke*, *valuator*, *choice*, *pick* and *string* [Rosenthal 82].

The *operating mode* of the device determines when an input primitive is delivered to the user of the device. It specifies the behaviour of the device as seen by both the operator and the using agent. Examples of operating modes commonly supported include the conventional *request*, *sample*, and *event* modes. Support for other modes can be defined as long as they operate within the confines of the model.

There are seven types of operations that can change the state of a logical input device and its component processes. These are: *definition*, *initialisation*, *activation*, *utilisation*, *deactivation*, *termination* and *undefinition*.

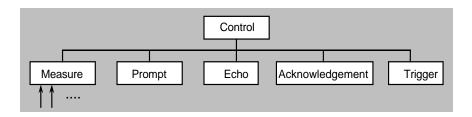

Figure 2.2: Logical model of a graphical input device.

#### **Logical Processes**

A logical input device comprises *measure*, *echo*, *prompt*, *trigger*, and *acknowledgement* processes overseen by a single *control* process. The control process is responsible for the overall operation of the logical input device and its associated component processes. Each of the component processes functions independently which, when acting in concert, can result in the production of an input primitive.

When the logical input device is activated, the *control* process activates the measure, echo, prompt, and trigger processes. The *measure* process continuously maintains a measure value derived from the input data. This includes all computations necessary to map the input data to the measure value. The *echo* process provides continual feedback of the current value of the measure. This feedback is expressed in terms of the output facilities available at the level of abstraction at which the logical input device is defined. The *prompt* process indicates the availability of its associated logical input device. A *trigger* process continuously monitors one or more sets of conditions. When any one of these sets of conditions is satisfied, the trigger is fired. When the trigger firing report is received by the control process, it produces an appropriate input primitive that

— dependent on the operating mode of the device — may contain the measure which was current at the time of the trigger firing. The input primitive is then reported to the agent that is using the logical input device and the *acknowledgement* process is activated. The acknowledgement process informs whether the input report was accepted or rejected by the using agent.

#### 2.1.4. Graphical Interaction

It is good programming practice to clearly separate interaction facilities from the pure application functionality by means of a *user interface*. The user interface is a logical module which handles all transactions between a program and a user. The term user interface will be used to refer to in- and output devices and the software to control these devices. Interaction implies that (re)actions take place at both sides, however, a distinction can be made depending on which side controls the interaction. In the case of *internal control* the user interface is in charge of the interaction. The user is prompted to enter information. In the case of *external control* the user initiates the interaction. In terms of the logical input model the user interface has to set the appropriate operating mode of the input device(s).

To inter-act takes at least two actors. For graphical interaction, one actor — i.e., the user — makes use of input devices to provide information to an application. In turn, the other actor — i.e., the application — makes use of output devices to inform the user. Interaction requires proper feedback: each input action should immediately be "confirmed" by the system. A logical input device may provide an echo which is handled completely within the user interface. For this, the logical input model uses output functionality provided at the same level of abstraction at which the logical input device is defined <sup>1)</sup>. On higher levels of abstraction the application program may become responsible for feedback as well. In that case the actions involved in generating graphical feedback include:

handling of the logical input data; (graphics system)

handling of the input primitives; (application)

possible updates of some application data; (application)

traversing (part of) the graphics pipeline; (graphics system)

update of the refresh buffer. (graphics system)

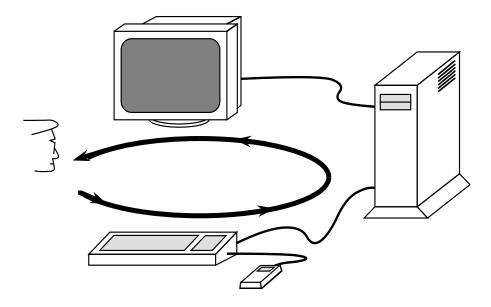

This set of actions make up the *graphical feedback-loop* (see Figure 2.3). Graphical feedback implies that, in one way or another, logical input devices have to be coupled to output facilities. Here we find that the traditional logical input model described in the previous sub-section falls short. The model does not contain special functionality for this purpose. As a result, according to this model, the coupling has to take place in the application program.

It is essential that response on user input is acceptably fast. In fact, response on user input is a key determining factor of the quality of a user interface. The time to

<sup>1)</sup> Examples of this are on-screen input devices provided by the system such as dials, sliders and buttons.

**Figure 2.3:** Graphical feedback loop. User input is processed and results in a visible reaction.

traverse the entire feedback-loop —i.e., the time elapsed between a user input action and the moment the related feedback appears on the screen — is called *response time*. A system's response time depends on several factors. Obvious factors are the amount of processing involved in the feedback-loop and the raw performance of the computing resources. Other factors are operating system related dependencies such as interrupt handling, context switching and the like. This variety of factors illustrate that concentrating on the throughput rate of the graphics pipeline alone is not enough to ensure fast response. It is essential that the amount of processing involved in the feedback loop is minimalised. As will be discussed later, this relates to how effective a user can operate the graphics pipeline, how accessible intermediate representations are, and how these representations relate to the 'real world'.

#### 2.2. An Overview on Interaction Tasks

"...interaction sequences can be decomposed into a series of basic interaction tasks. Each interaction task instance has a set of application requirements, defined by the context of the application in which the task is embedded." [Foley 84]

The interaction tasks referred to in this quote are user-oriented, in the sense that they

are the primitive action units performed by a user. These interaction tasks present a different view on interaction as the hardware- and software-oriented view in the context of logical input devices as presented in § 2.1.3. The relation between interaction tasks and logical input devices should be clear. Logical input devices are part of the means to accomplish basic interaction tasks.

In [Foley 84] Foley et al. classify basic interaction tasks as: *selection, position, orient, path, quantify* and *text*. Beside these basic interaction tasks, they distinguish controlling tasks that modify objects being displayed: *stretch, sketch, manipulate* and *shape*. In their view, manipulate differs from the basic interaction tasks in that the cursor is replaced by an already existing object on the screen. Here the distinction between a cursor and an object is not relevant; the different types of manipulation of an object are assumed to be basic interaction tasks. In this view, the operand of any task may therefore be a cursor as well as a display primitive (or a group of display primitives).

Basic interaction tasks of interest for this dissertation are those tasks that make use of interaction techniques which relate directly to the image generation pipeline, or more specifically: interaction techniques that provide dynamic visual feedback. The important role of these basic interaction tasks in particular should reflect in the design of the architecture. In the next we will confine to these types of basic interaction and controlling tasks.

#### Selection

A user may select from a collection of displayed entities by means of a pointing device, such as a lightpen or a mouse- trackball- tablet- or joystick-controlled cursor. In principle, the types of entities that can be selected may vary from commands in a menu, symbols and icons to display primitives or groups of display primitives. In this analysis we are interested in selection of display primitives and groups of display primitives.

Selecting or *picking* display primitives essentially involves a search of the display file. Selection typically serves to specify the operand of an operation. It is part of almost any interaction dialogue. Primitives may be embedded in a hierarchical structure. Then, selection may occur at different levels of the hierarchical structure. The hierarchical level at which selection takes place is "defined by the context of the application in which the task is embedded". The application should provide the means for the user to climb up and down the hierarchy.

The graphics system has to make clear which of the primitives will be picked upon triggering based on the current position of the selection device, by for example, high-lighting. Such feedback should ensure non-ambiguity to avoid unpleasant surprises. This may seem an obvious and simple requirement, but in practice it may turn out to be quite complicated. To avoid ambiguity, high-lighting of a partly hidden selection should preferably reveal the structure of the complete selection, i.e., including the obscured parts. However, it may be essential to be able to judge that selection in its three-dimensional context, in which case a simple

overlay of the complete structure on the image is unsatisfactory.

Ideally, the echo process finds all display primitives that (partly) obscure the structure and, for instance, makes these primitives (partly) transparent. In any case, the system has to "know" what part of the current pickable item is visible and what part is invisible.

#### **Position**

The user can specify a position by means of a pointing device. The position task may be an open-loop or closed-loop process. For the open-loop technique the visual feedback on the screen serves to show the result of the position task, it does not play a role in specification of the final position. On the other hand, if the position task is a closed-loop process, the user adjusts the position of the operand based on what is shown on the screen until the desired result has been obtained. Therefore the position of the object on the screen will continuously have to be updated <sup>2)</sup>. If the operand is an object rather than a cursor, the task is also know as *dragging*. It may be clear that in this case the requirements on the response of the system are high.

The position task may occur in one, two or three-dimensional space and may be constrained (e.g., along a path or in a plane). Naturally, for proper positioning it is important that feedback ensures non-ambiguity. Consequently, a position task in a three-dimensional space should make it possible to judge the position of the operand in the 3D context. This implies that hidden surfaces have to be removed in real-time, and possibly that display primitives that obscure the operand have to be found and made transparent in real-time as well. In practice we often see that, to avoid such complications, 3D positioning is possible on simplified models only (e.g., wire-frame models).

Panning and zooming are a special kind of position tasks. Add and delete operations can be considered as being position tasks as well. This view is demonstrated for instance in the desk-top metaphor in which deleting of a file is done by dragging the icon representing that file into a trashcan.

#### Orient

The orient task very much resembles the position task. Yet, there are some differences — such as the users perception of orientation and the use of input devices — that make it reasonable to classify orient as a separate type of basic interaction task. The orient task may occur in two or three-dimensional space and may be constrained (e.g., rotation around an axis).

The user may specify an orientation by means of an input device like a dial, a locator or a joystick. The orient task may in principle be an open-loop or closed-loop process. In the latter case, the user adjusts the orientation of the operand until the desired result has been obtained. Like for the closed-loop position task, also for a closed-loop orient task hidden surfaces have to be removed in real-time, and it may be necessary that display primitives that obscure the operand have to be found

<sup>&</sup>lt;sup>2)</sup> More on open and closed loop interaction techniques in § 2.3.1.

and made transparent. This complication does not occur in wire-frame models. Since for the orient task the operand remains at its local position, finding the display primitives that obscure the operand will in general not be as involving as it can be for dragging.

#### Path

A user can specify a path by a series of positions and/or orientations. It is seen as a task different than the position and orient task because in this case the order and relative relation of the positions/orientations is of main interest, not the individual positions/orientations that make up the path.

The user may specify a path by means of a pointing device using techniques similar to those for the position and orient task. The path may be distance-based or time-based. The operand may be a cursor or an object. It is important to be able to judge a path in its 3D context, which implies that, similar to what holds for the position task, hidden surfaces have to be removed in real-time and, possibly, that display primitives that obscure the path have to be found and made transparent in real-time.

#### **Ouantify**

The quantify task serves to input a value, a dimensionless number, that can be bound to any aspect of objects or global entities of the scene. Unlike the interactions tasks listed so far, this does not restrict to geometry related aspects only.

The user may specify a value to quantify a measure by means of, for instance, a valuator or a mouse- or tablet-controlled slider. If the operand is an object by itself, the task is typically a controlling task, rather than a basic interaction task.

#### **Controlling tasks**

The basic interaction tasks listed in the above are different types of manipulations of an operand with respect to the rest of the environment. By means of controlling tasks such as stretch and shape, the user can modify (edit) the operand itself. The user typically operates on a particular feature of the operand only, not affecting remaining features. Examples of this type of manipulation may be deformation of the operand by (re)positioning of a vertex or a control point (for curved surfaces) or variation of an appearance control parameter.

The user may edit an operand by means of a selection, position, orient and/or quantify task. In case the task is an open-loop version, the user adjusts the feature directly until the desired result has been obtained. Continuous feedback of the edit task in a three-dimensional space implies that hidden surfaces have to be removed in real-time in case the feature is part of the geometrical description of the operand. In general, the operand will globally speaking remain at its current local position, so that here also finding the display primitives that obscure the operand is not as involving as it is for dragging. It may be that display primitives that obscure the operand have to be found and made transparent. This complication does not occur in wire-frame models.

If the appearance control parameter of the operand is edited, a closed-loop version of the task can be reduced to a continuous redraw of the operant only, based on the current value of the appearance control parameter.

## 2.3. Temporal Aspects of Interaction

User interfaces are becoming more and more sophisticated due to evolution of both hard- and software. Sophisticated user interfaces should support natural interaction and take into account features of human perception. This leads to *animate response*—that is, response where changes as invoked by the user are visualised by a smooth, natural transition from one state into another. In this sub-section, such temporal aspects of image generation in general, and for animate response in particular are examined.

Motion plays an important role in numerous aspects of human vision. Eyes are in a constant state of movement to generate stimuli needed to see anything at all. Relative motion of objects turns out to be very helpful in our understanding of three-dimensional structures: a change of viewing position generates motion parallax. The human mind is trained to interpret this motion parallax as a measure of distance. The human vision system uses relative motion as a basis of grouping, organising objects that belong together. By exploiting these type of perceptual capabilities of the viewer acquired by years of training in the real 3D world, animate response can improve human computer interaction.

Why should we be concerned about temporal aspects of response, is it not sufficient to let the system simply respond as fast as it can? Systems get faster every day, so if todays workstations are not fast enough yet, systems of the future will be. It is a fact that due to progressing technologies, workstations continue to increase in capacity. As a consequence of this also applications become increasingly more complex. The net result of the increase of capacity may therefore very well be insufficient. More importantly however, responding as fast as possible does not necessarily lead to adequate response.

A system can be too slow, but on the other hand it can also be too fast to be perceived by the human viewer, leaving him in a state of confusion. What is needed is a concern about the temporal aspects of response: the system must be "tuned" to the time frame of the user. This tuning should aim at optimal interaction, taking into account the limited temporal resolution of both the display system and the human vision system. Also, a system may operate within a certain time frame to help the user anticipate to a new situation. The following examples that can be found in some 2D user interfaces may be illustrative.

Low-end systems cannot support dragging of a window with all of its content. Dragging a window with a significant time-lag turns this basically simple task into a tedious exercise: it is next to impossible to place the window at the desired position. A workable solution to get around this problem is to leave the window with its content where it is and let the user drag a simplified representation of the window:

its boundary rectangle. Once the user is satisfied with the new position, the window and its content can be redrawn at the new position. Quality is traded for time.

The visible action upon closing a window, i.e., clearing the screen, can in general be done quite fast. However, it may be better to smoothly lead the user to the new situation by means of a shrinking boundary rectangle moving towards a disk or folder icon. An implicit animation like this gives the user a better idea of what is going on. Here, time is traded for quality.

For animate response in three-dimensional dynamic environments more sophisticated techniques are needed, but basically they have to be of the same nature: adapt to the users time frame.

#### 2.3.1. Animate Response

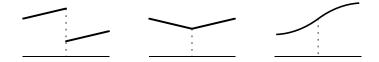

Animate response is the visual response of a system to changes invoked by the user. It is characterised by a smooth, natural transition from one state into another. It is useful to make a distinction between *implicit animation* and *direct manipulation*. These two categories differ in characteristics of the visual feedback of the transition phase, a difference which reflects in the temporal aspects of the interaction.

Implicit Animation. For implicit animation the current state and the explicit specification of a new state implicitly specifies the transition. The transition is an 'open loop' animation. Although certain parameters may affect the characteristics of the transition process, the transition itself is autonomously generated by the system, that is, not directly controlled by the user. The temporal aspects of the transition can in principle be analysed beforehand. The implicit animation can be a natural transition between two 'key-frames' resulting in for instance an animated sequence of a slowly rotating molecule. One may also think of more abstract transitions in which the relation between two by nature different entities can be visualised such as the relation between a window and an icon as just mentioned.

Implicit animation can be employed by traditional command language type of interaction in which objects are manipulated by means of explicit commands, issued for example by typing or by menu selection. Implicit animation serves to 'guide the eye', to make the transition appear more natural. Based on the type and amount of the change, the system should be able to determine how to best animate a transition. Setting of transition parameters may allow the user to specify speed, image quality and other aspects of the transition. Advanced systems would automatically adapt to skill and preferences.

Direct Manipulation. Direct manipulation allows the user to manipulate a visible representation of a virtual model as if it is a real object which is mechanically connected to an input device like a mouse, a light pen, a trackball or a data-glove. In this type of transition process, the user is in direct control over the transition from one state to an a priori unknown final state. In this case, the visualisation process is an essential part of a closed loop between the system and the user. The user handles the input device based on what he sees on the screen. As a result time constraints are strict.

Direct manipulation has already proven to be successful in a well known type of user interface: the desktop metaphor. This type of user interface proved to be a success mainly because it presents a virtual two dimensional environment which is a metaphor of an environment already familiar to the user: the desk. The interface allows the user to manipulate documents (windows) on a screen just as paper documents can be manipulated on a desk.

A similarly natural and intuitive direct manipulation concept can be used in three-dimensional environments. In such artificial realities — also known as virtual environments or cyberspace — the user is free to manipulate simulated three-dimensional objects in a natural way, is free to walk through and interact with imaginary worlds, in short: can be immersed in a virtual model. Based on the direct manipulation concept we can for instance create remote control systems with which a user is able to control remotely in space (hazardous or far away environments), remotely in time (future) or allow control in a different scale (macro- or microworld) [Shneiderman 89].

The most important aspect of *direct* manipulation appears to be *direct* visualisation. If the result of the manipulation is not visualised immediately, the user will not feel immersed in the environment. As stated by Scott Fisher <sup>3)</sup> "the quality of the graphics appears not to be extremely important, as long as the response is good".

# 2.3.2. Computer Animation

Why is a film, a long band of static images, often called a 'movie'? Answering that question also gives an answer to why computer animation is at all possible, using video displays which essentially can display static images only. Apparently the characteristics of the human vision system makes it possible to give a viewer an impression of continuous movement by successively presenting displaced static images or *frames*. This ability is based on two distinct features of the human vision system: *persistance of vision* and the so-called *phi phenomenon* [Gregory 90].

Persistance of vision is the inability of the retina to follow light flashing at a rate above about 50 Hz. Because of this, a movie projector — that presents frames at the standard rate of 24 Hz — raises the flicker rate to 72 Hz by means of a shutter mechanism. The phi phenomenon tells us that the retina system is tolerant with respect to intermitted images provided the jumps in space or time are not too large. It is likely that this ability to tolerate gaps is developed to maintain continuity as objects are hidden briefly behind obstructions, or retinal images behind blood vessels.

Since the impression of continuous movement is lost below a certain frame rate, it is important to know at what range of rates these frames should be generated. As the time interval between successive stimuli is increased, the observer's perception of apparent movement goes through several stages [Goldstein 89]. In an experiment

<sup>&</sup>lt;sup>3)</sup> Panel Virtual Environments and Interactivity: Windows to the Future, SIGGRAPH'89, Boston.

with two flashing lights at a separation in time of about 30-60 msec, partial movement is perceived. At about 60 msec, the lights appear to move continuously from one position to another. At intervals between about 60-200 msec the phi movement is perceived. Movement appears to occur between the two lights, yet it is difficult to actually perceive an object moving in the space between them. Outside the range 30-200 msec we do not percieve movement.

Also the distance in space between the two lights affects the perception of apparent movement. As the distance increases the time interval or the intensity of the flashes must be increased to maintain the same perception of motion.

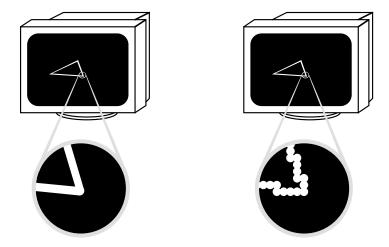

Video displays have a constant refresh rate of 50-100 Hz. Therefore, the maximum frame rate is restricted <sup>4)</sup>. This limitation has effect on visualisation of fast moving objects. The displacement of fast moving objects between two individual frames may become quite large. When these object are displayed just as if they were static, the spatial relation is lost and the impression of watching objects in continuous motion is no longer there. A movie projector however, shows separate frames at a rate as low as 24 frames per second. This rate is sufficient to generate an impression of continuous motion, even of fast moving objects. Why this is so can been found by looking at individual images of fast moving objects on a camera film. The finite exposure time of the film results in blurred images of fast moving objects. Due to *motion blur* the impression of continuous movement is maintained, even at a rate of 24 frames per second. Apparently the human vision system can trade off temporal resolution against spatial resolution.

A number of papers present methods to generate motion blur (also known as temporal anti-aliasing) [Korein 83, Potmesil 83, Max 85, Grant 85]. In these papers it is argued that "animation which simulates motion blur feels more natural" or "motion blur smooths out jerkiness". A more theoretical foundation of why and to what extend motion blur is needed can be found in Blake's thesis on computing adaptive detail [Blake 89].

Blake's study aims at reducing the computational complexity of computer animation by computing just what is needed to produce convincing pictures. The thesis is centered around two metrics, a spatial (static) priority: "objects further away from the viewpoint are visually less important to the picture than those closer by" and a temporal (dynamic) priority: "objects moving quickly with respect to the observer need to be redrawn more often than those at rest". These intuitive formulations are further developed and extended with the notion that human vision introduces a

<sup>&</sup>lt;sup>4)</sup> A "frame" should be seen as a virtual picture which can be displayed for several refresh cycles. The *frame rate* is the rate at which successive, different frames are displayed. It should not be confused with the *refresh rate*, which is constant and is dictated by the persistence time of the display medium. (This is analogous to the movie projector that displays frames at a rate of 24 Hz but flickers at a rate of 72 Hz.) Since frames can be swapped only just before the start of a new refresh cycle, the frame rate can never exceed the refresh rate.

trade-off between temporal and spatial resolution. These are the basics for arriving at measures to determine to which extent detail can be left out without being noticeable by a viewer.

Changing images are a function of two space variables and of time. A Fourier transformation of this function results in a spectrum, a function of temporal and spatial frequencies. This function is non-zero in a limited domain only. The effect of motion on this spectrum is that it is sheared in the temporal frequency dimension. The amount of shear is proportional to the velocity of the object components in the two dimensional image. The human vision system is limited in spatial and temporal frequencies by the various transmission systems between our mind and the outside world, resulting in a so-called window of visibility [Watson 86]. Since the spectrum of moving objects is sheared, some spatial frequencies which would fall inside the window of visibility for static objects, may fall outside this window when these objects are in motion. Removing the spatial frequencies that fall outside the window of visibility is equivalent with removing details of the moving object that cannot be perceived by the human vision system. These spatial frequencies in combination with the frame rate of the display system appears in aliased form, causing the unnatural or jerky motion mentioned above.

Blake remarked that Fourier analysis is useful for analyzing a problem and obtaining insight into what is happening. In practice, however, computations and algorithms are less likely to use Fourier techniques directly. He argues that optic flow analysis as introduced by Gibson [Gibson 79] can be used to obtain a measure of the velocity and/or distortion of object components in the image. This measure can be used to determine the amount of detail needed. It indicates which spatial frequencies have to be left out, or equivalently, to what extend the image should be motion blurred.

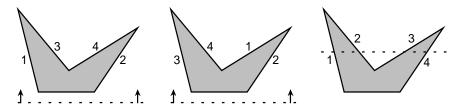

Finally, Blake concludes that for planar objects, four orders of optic flow effects result in four orders of frame to frame coherence. In decreasing order of coherence these orders are:

- no displacement;

- translation in the image plane;

- linear transformation in the image plane (shear, rotation, scaling);

- all other, non-linear transformations.

To be able to exploit these types of frame to frame coherence it is necessary to maintain a relation between objects and their projection onto the image plane.

#### 2.3.3. Discussion

The major issue of computer animation is how to convince the viewer, to make him see what he is meant to see. Often images are simply rendered at the highest — and constant — quality level that is possible. For real-time animation systems this requires a major exertion which can hardly be maintained by costly specialised systems — such as flight simulators — and then, for well-defined situations only.

Animation production involves three separable tasks: modeling, animation (i.e., the design of the choreography) and rendering. Animation production is a compute intensive process which may — and, due to the separability, can — take orders of

magnitude more time than the real-time display of the animation itself. This is unlike animate response, where animation and rendering by definition occur in real-time. In spite of this difference in character, computer animation may still teach us how to deal with certain temporal aspects such as limitations enforced by the display system and the human vision system.

In the process of computer animation production, limited computing resources can be traded against production time. This is quite different from what we find in an interactive environment of which the main device necessarily has to be: "the quality of the graphics is not extremely important, as long as the response is good". The main objective for animate response is real-time display of continuous motion, even if one has to deal with complex structures. For animate response, the limit on computing resources necessarily has to be compensated by a reduction of image quality, but then preferably in a reasoned way. This issue will be addressed in the next section.

# 2.4. Dealing with Motion

In the above, we concluded that for animate response two constraints may complicate the visualisation of continuous motion: the limit on the frame rate as dictated by the display system and the limited capacity of computing resources. The net result of both limits is the same: temporal aliasing may become visible. Depending on its cause, temporal aliasing can be prevented by temporal antialiasing or by reduction of the cost of image generation. As has been mentioned before there are several techniques for temporal anti-aliasing. The cost of image generation can be scaled by so-called adaptive image generation techniques. In the next we will examine their usability for animate response.

#### 2.4.1. Temporal Anti-aliasing

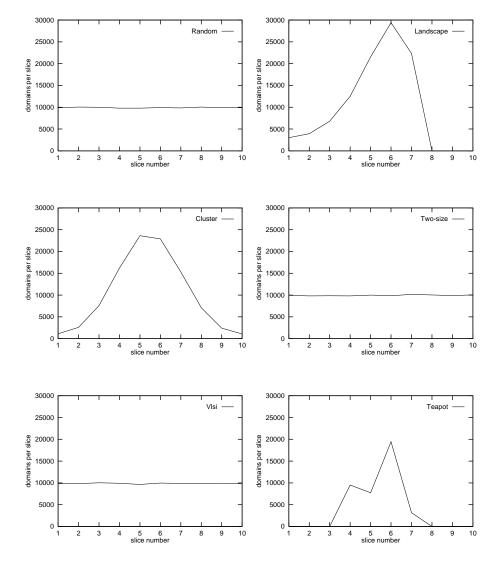

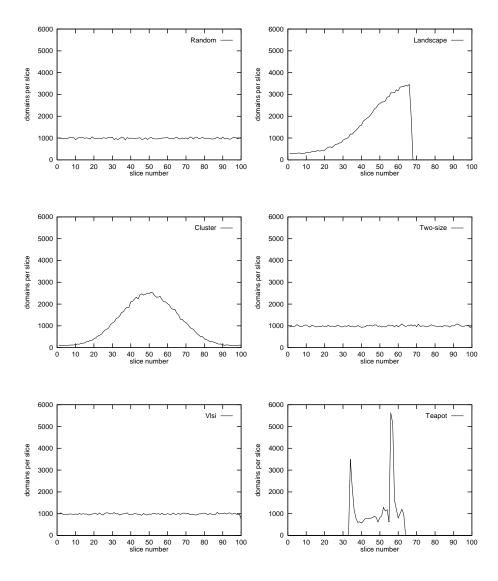

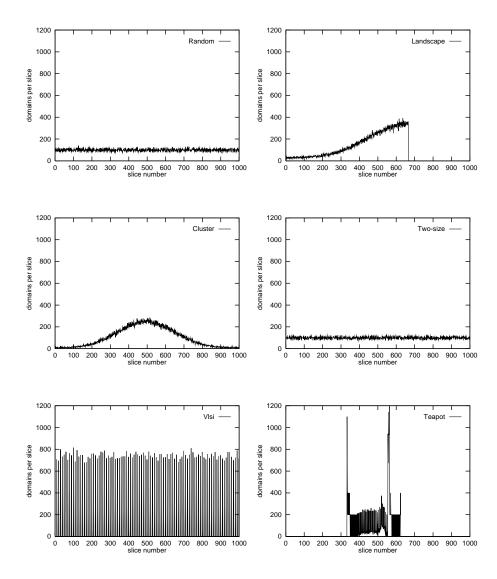

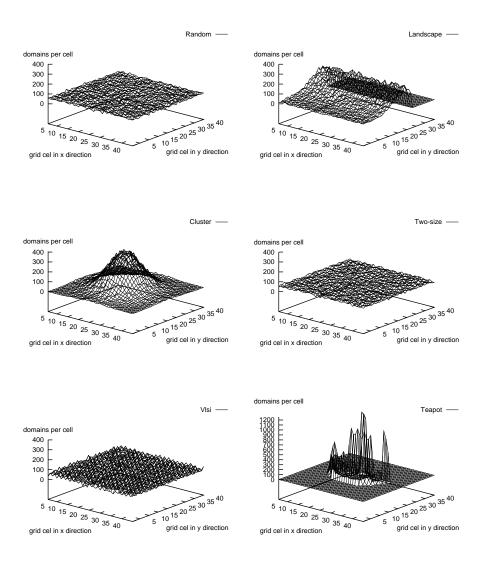

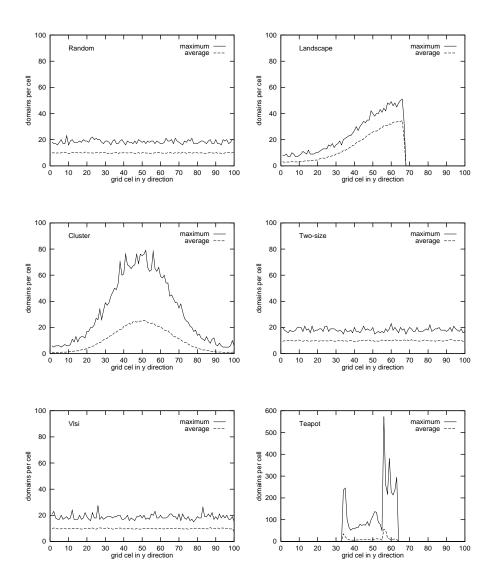

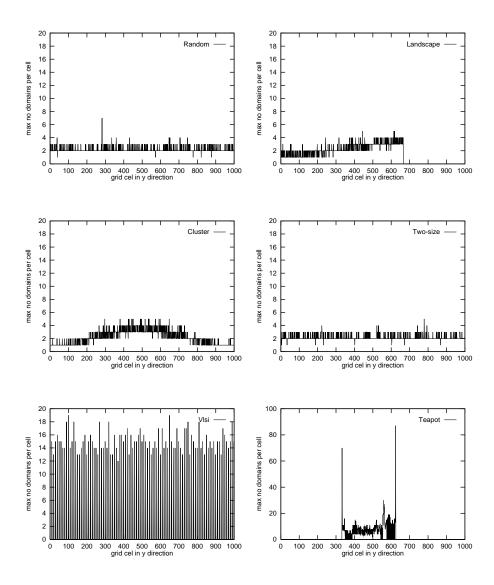

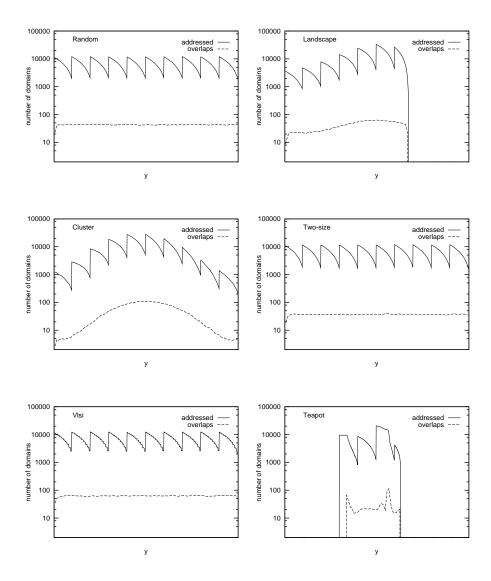

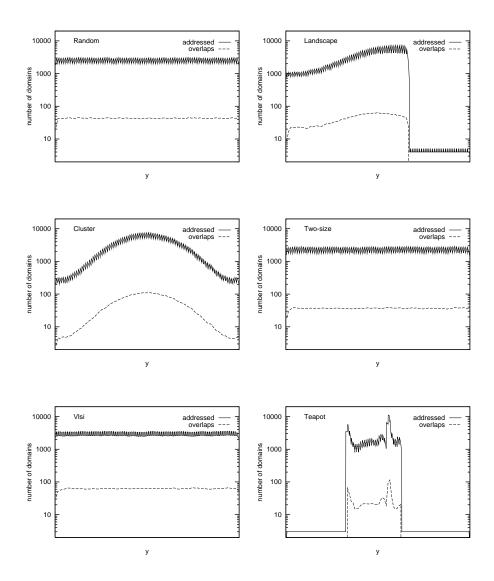

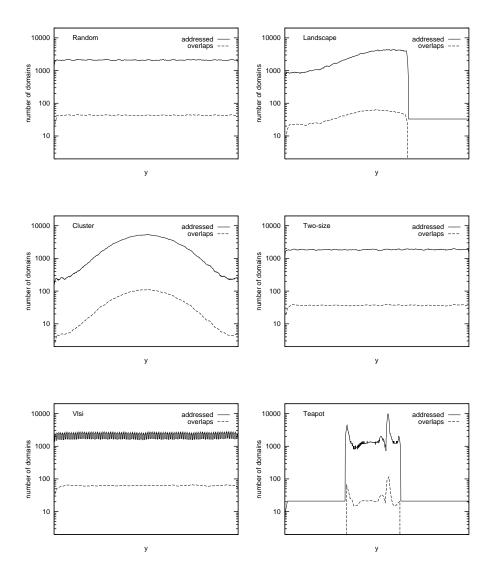

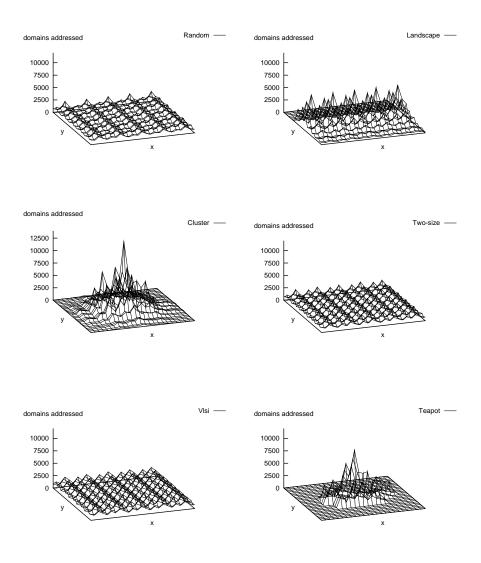

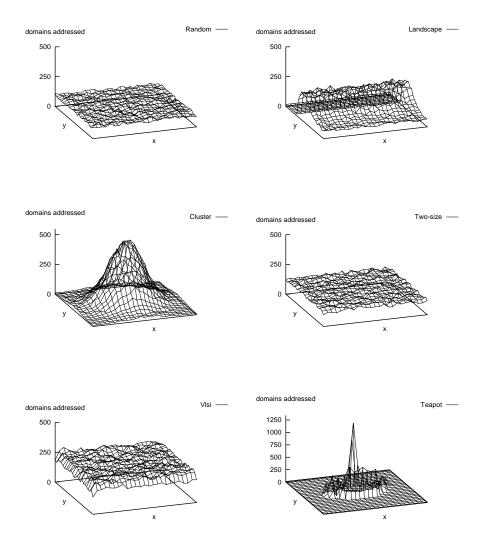

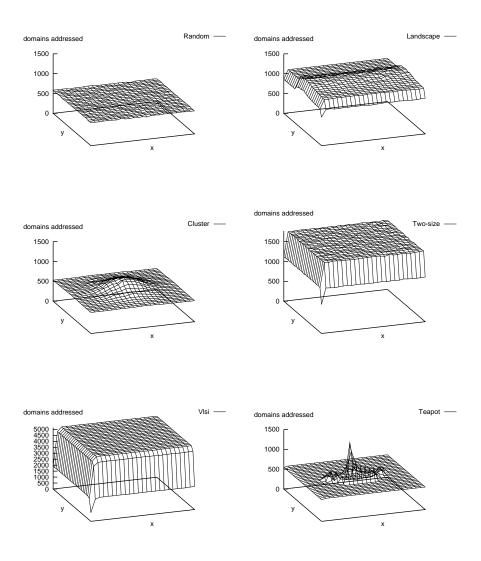

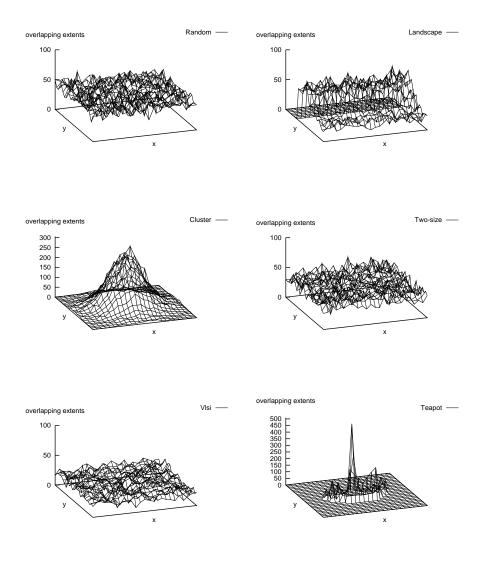

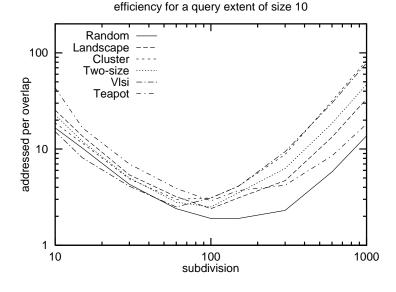

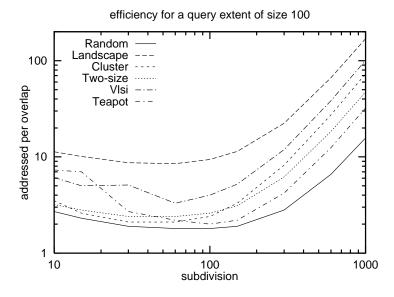

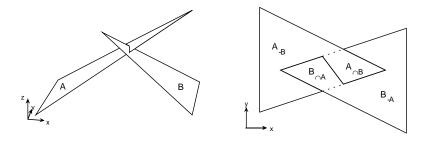

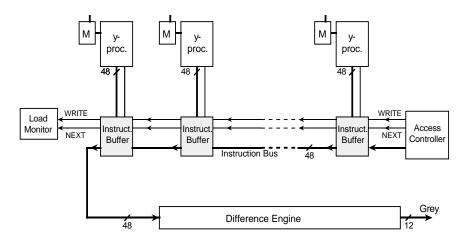

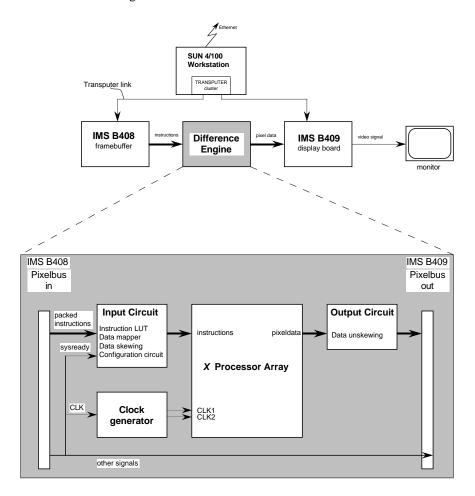

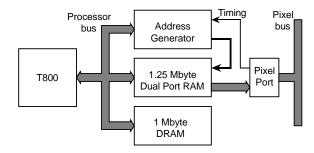

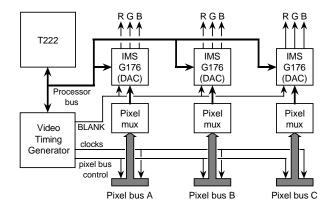

Existing temporal anti-aliasing methods [Korein 83, Potmesil 83, Grant 85] are based on supersampling techniques. As a result, the computational cost of one temporal anti-aliased frame is much more than the cost of one aliased frame. Also the more efficient method as presented by Max [Max 85] adds computation cost to each frame. This may not seem surprising. However, one should realise that —as mentioned in § 2.3.2— temporal anti-aliased images contain less detail: the high spatial frequencies are filtered out. One could argue that therefore, temporal anti-aliasing should save rather than add computational costs. It is surprising that as of yet there are no methods that are able to make use of this.