## **Technological University Dublin** ARROW@TU Dublin

Doctoral **Engineering**

2013-1

# Power Quality Improvement of Distributed Generation Integrated Network with Unified Power Quality Conditioner.

Shafiuzzaman Khan Khadem Technological University Dublin, skkhadem@gmail.com

Follow this and additional works at: https://arrow.tudublin.ie/engdoc

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Khadem, K. S. (2013) Power Quality Improvement of Distributed Generation Integrated Network with Unified Power Quality Conditioner. Doctoral Thesis, Technological University Dublin. doi:10.21427/ D7KS4X

This Theses, Ph.D is brought to you for free and open access by the Engineering at ARROW@TU Dublin. It has been accepted for inclusion in Doctoral by an authorized administrator of ARROW@TU Dublin. For more information, please contact yvonne.desmond@tudublin.ie, arrow.admin@tudublin.ie,

brian.widdis@tudublin.ie.

# Power Quality Improvement of Distributed Generation Integrated Network with Unified Power Quality Conditioner

## MD. SHAFIUZZAMAN KHAN KHADEM, BSc, MSc

A thesis submitted for the Degree of Doctor of Philosophy to the Dublin Institute of Technology

Under the supervision of

Dr Malabika Basu and Dr Michael Conlon

School of Electrical Engineering Systems,

Dublin Institute of Technology,

Republic of Ireland

January 2013

Dedicated to my Late Parents Wife and Children

## **Abstract**

With the increased penetration of small scale renewable energy sources in the electrical distribution network, maintenance or improvement of power quality has become more critical than ever where the level of voltage and current harmonics or disturbances can vary widely. For this reason, Custom Power Devices (CPDs) such as the Unified Power Quality Conditioner (UPQC) can be the most appropriate solution for enhancing the dynamic performance of the distribution network, where accurate prior knowledge may not be available. Therefore, the main objective of the present research is to investigate the (i) placement (ii) integration (iii) capacity enhancement and (iv) real time control of the Unified Power Quality Conditioner (UPQC) to improve the power quality (PQ) of a distributed generation (DG) network connected to the grid or microgrid. The following developments have been achieved through this PhD research;

## (i) Placement of UPQC in DG network

A proper placement of a UPQC has been identified in a DG integrated grid connected microgrid network, together with the feedback sensors to cope with the bidirectional power flow without compromising the power quality controlling features. In the presence of DG sources and a UPQC in an active distribution network, the following issues have been analysed;

- (a) the placement of a UPQC and its sensors in the network,

- (b) impact of the sensor placement on the UPQC control to perform the specified task,

- (c) performance of UPQC with bi-directional power flow in the network and

- (d) the advantages of DG inverter in the presence of UPQC

Depending on the location and integration technique of DG sources as well as locating of the UPQC sensors which is based on its control technique, a new placement arrangement and integration method of the UPQC at the point of common coupling (PCC) have been identified.

## (ii) UPQC<sub>uG</sub> - a new integration method

A new integration method of the UPQC has been developed: that can help the DGs to deliver quality power in the case of islanding and help to reintegrate with the grid seamlessly postfault. Islanding detection and reconnection techniques, together with associated control schemes, have featured in the conventional UPQC system. Hence, it is termed UPQC<sub>µG</sub>. The advantages of the proposed UPQC<sub>µG</sub> configuration and integration system are to compensate voltage interruptions in addition to voltage sags/swells, and harmonic and reactive power compensation in the interconnected mode. The DG Inverter with storage supplies the active fundamental power only and the shunt part of the UPQC compensates the reactive and harmonic power of the load during both interconnected and islanding mode. Therefore, the system can work both in interconnected and islanded mode. The advantage of the DG Inverter is that it does not require to be disconnected during the islanded mode and hence the islanding detection and reconnection technique need no longer be a part of the inverter. In all conditions, the DG Inverter only provides the active power to the load and grid. Thus it reduces the control complexity of the DG inverter as well as improves the PQ of the microgrid.

## (iii) Capacity enhancement

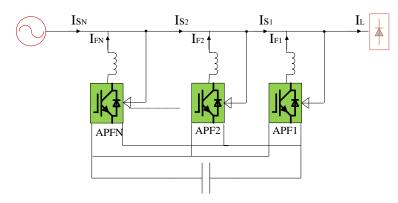

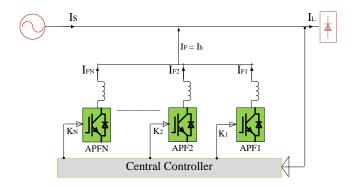

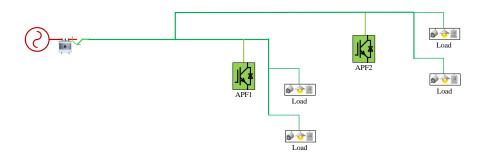

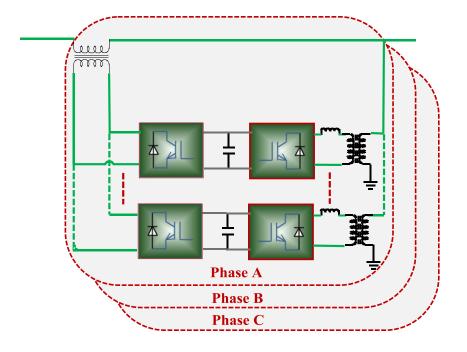

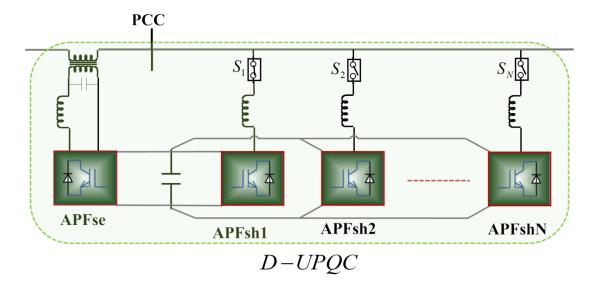

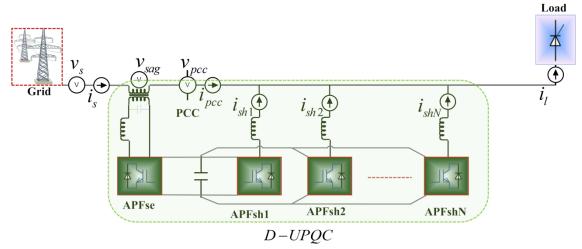

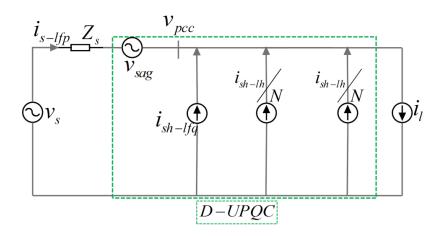

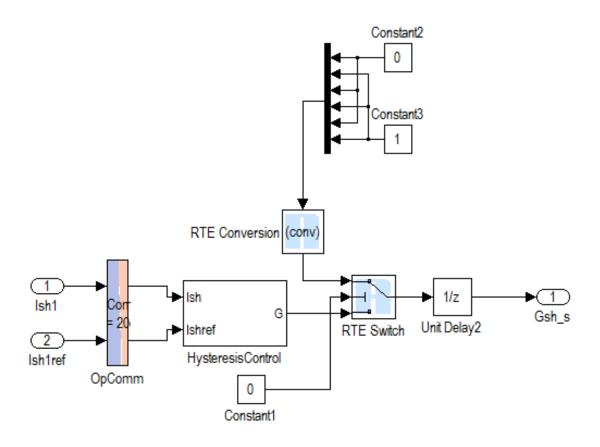

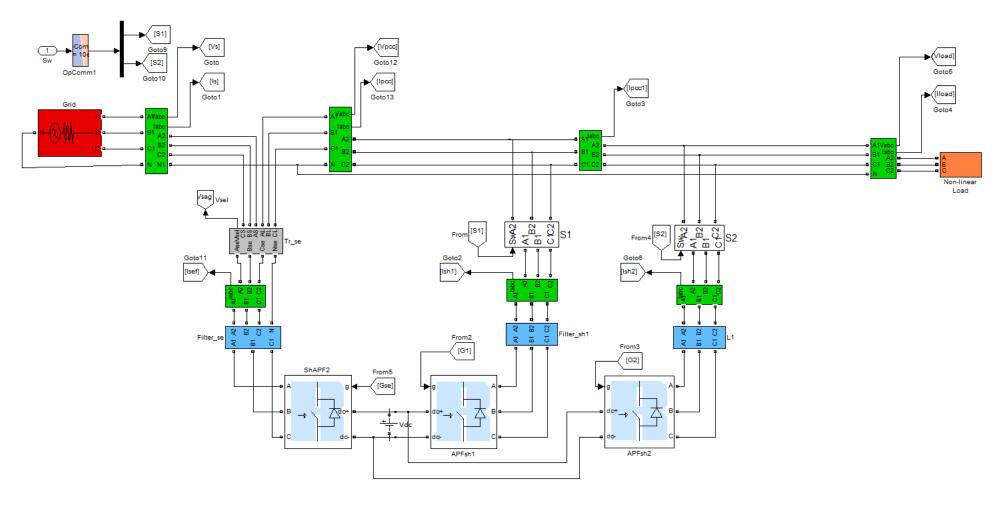

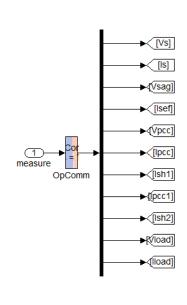

A novel method of capacity enhancement and operational flexibility of the UPQC at a distribution network level has been proposed, providing modularity and redundancy for better efficiency and reliability. For high current compensation at a low voltage distribution level, multiple Shunt APF units in modular and distributed mode, connected with a common dc linked capacitor, can be a solution to develop a Distributed UPQC (D-UPQC). This novel method is proposed here for the D-UPQC system where the multiple shunt APF units are based on hysteresis current control and operated in a power sharing mode. The related design and control issues are also discussed.

## (iv) **Design and control**

Implementation of the proposed integration and capacity enhancement methods, and the modification in design with an advanced and real time control strategy have been developed. As a part of design and integration, issues including capacity enhancement and operational flexibility, the detailed switching dynamics with a parameter selection procedure for the APF<sub>sh</sub> unit has been studied. Active power loss associated with the design parameters has also been analyzed as a rating requirement of the shunt APF unit. Control methods for parallel operation of multiple APF units are also discussed. Due to the common DC link, a circulating current could flow within the APF units. In the case of hysteresis control with multiple APF units, the design issues have been discussed for the proper selection of design parameters to reduce the circulating current flow.

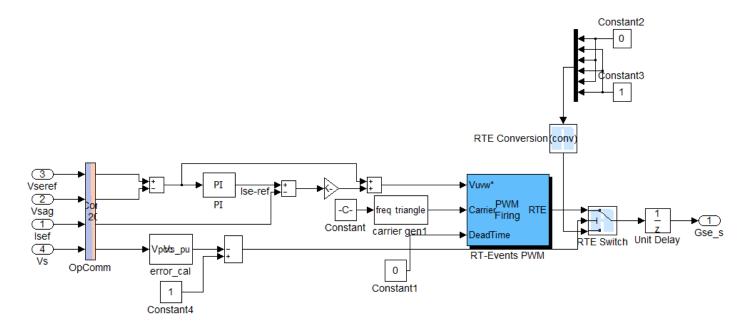

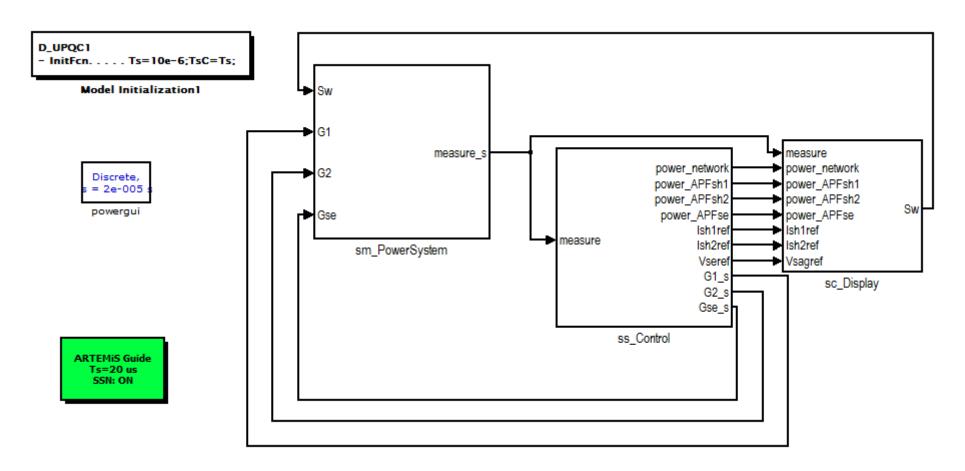

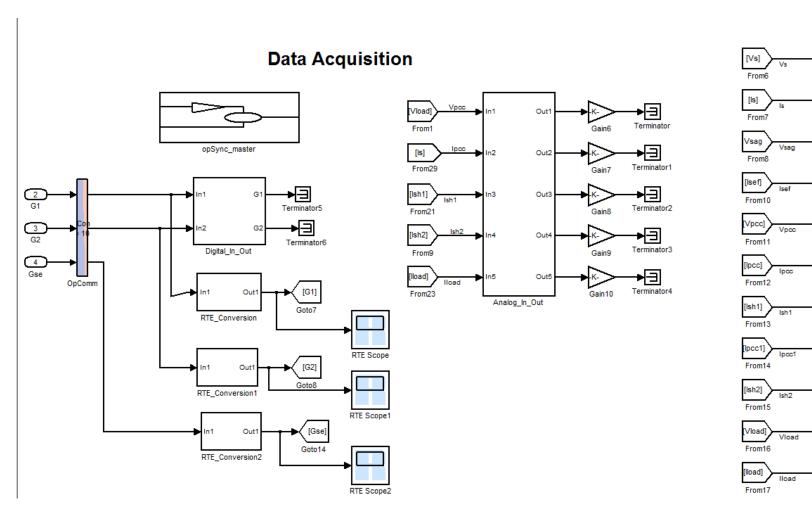

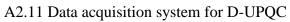

The required active distribution network has been designed in MATLAB using SimPowerSystems and RT-LAB tools. A real-time simulation environment in a SIL (software-in-loop) configuration with a hardware synchronization mode, has been developed using the real-time simulator from OPAL-RT. The performance of the proposed UPQC $_{\mu G}$  and D-UPQC method have been tested in real-time.

I certify that this thesis which I now submit for examination for the award of the Degree of Doctor of Philosophy, is entirely my own work and has not been taken from the work of others save and to the extent that such work has been cited and acknowledged within the text of my work.

This thesis was prepared according to the regulations for postgraduate study by research of the Dublin Institute of Technology and has not been submitted in whole or in part for an award in any other Institute or University.

The work reported on in this thesis conforms to the principles and requirements of the Institute's guidelines for ethics in research.

The Institute has permission to keep, to lend or to copy this thesis in whole or in part, on condition that any such use of the material of the thesis be duly acknowledged.

| Signature | Date |

|-----------|------|

|-----------|------|

Candidate

## Acknowledgements

All praise to almighty Allah who has given me the opportunity to carry out the research work successfully for the award of the Degree of Doctor of Philosophy. I express my sincere gratitude also to all of those people who directly and indirectly helped me for the completion of this task. This PhD thesis constitutes the work that I have carried out at the School of Electrical Engineering Systems, Dublin Institute of Technology, Ireland.

I take this opportunity to express my deep sense of gratitude to my research supervisors Dr Malabika Basu and Dr Michael Conlon for their inspiring and stimulating guidance, invaluable thought provoking suggestions, constant encouragement and unceasing enthusiasm at every stage of this research work.

I thank all of the members of Dublin Institute of Technology, and in particular Dr Eugene Coyle, Dr Jayanti N Ganesh, Mr Michael Farrell and Mr Kevin Gaughan, for their permanent support during my stay in Ireland.

Many thanks to my colleagues Nasif Shams, Dr Moin Hanif, Dr Umakant Dwivedi, Lubna Mariam, Benish K Paelly for their valuable suggestions, excellent cooperation and encouragement during the course of my PhD work.

I also wish to thank Mr Terence Kelly, Mr Michael Feeney and Mr Finbarr O'Meara for their help in carrying out experimental work.

Finally, I would like to extend my deepest gratitude and personal thanks to those closest to me. In particular, I am extremely grateful to my wife Lubna Mariam for tolerating my long hours of absence from home, for her sacrifice, patience and excellent cooperation during the entire period of this research work. Her loving, caring and sacrificing attitude has been the driving force in this endeavour and, no words of thanks are enough.

#### **Abbreviations**

APF Active Power Filter

CPD – Custom Power Device

CSI \_ Current Source Inverter

DAFS \_ Distributed Active Filter System

DG Distributed Generation

DFIG \_ Double-Fed Induction Generator

DSP – Digital Signal Processor

DSTATCOM – Distribution Static Compensator

D-UPQC \_ Distributed Unified Power Quality Conditioner

DVR – Dynamic Voltage Restorer

EMC \_ Electromagnetic Compatibility

EPS – Electric Power System

EU \_ European Union

FLL \_ Frequency Locked Loop

GTO \_ Gate Turn Off Thyristor

HIL – Hardware-in-Loop

HPF – High Pass Filter

HDS Harmonic Detection Sensors

IGBT – Insulated Gate Bipolar Transistor

IEEE – Institute of Electrical Engineers

IEC – International Electrotechnical Commission

LPF – Low Pass Filter

PCC – Point of Common Coupling

PI – Proportional Integral

PLL – Phase Lock Loop

PQ \_ Power Quality

PWM – Pulse Width Modulation

RCP – Rapid Control Prototype

SIL – Software-in-Loop

SPWM – Sinusoidal Pulse Width Modulation

SSB – Solid-state Breaker STATCOM – Static Compensator

THD – Total Harmonic Distortion

TDD - Total Demand Distortion

UPQC – Unified Power Quality Conditioner

UPS – Uninterruptible Power Supply

VSI – Voltage Source Inverter

# Table of Content

| Abstract        |                                                         | 1    |

|-----------------|---------------------------------------------------------|------|

| Acknowledgem    | ents                                                    | v    |

| Abbreviations   |                                                         | vi   |

| List of Figures |                                                         | xiii |

| List of Tables  |                                                         | xix  |

| List of Symbols |                                                         | XX   |

| Chapter 1 - Int | roduction                                               | 1    |

|                 | nd                                                      |      |

| 1.1.1 Distri    | buted Generation (DG) and Microgrid (µGrid)             | 2    |

|                 | r Quality (PQ) issues in DG or Microgrid (μGrid) system |      |

| 1.1.2.1         | Solar photovoltaic (PV) system                          |      |

| 1.1.2.2         | Wind energy system                                      |      |

|                 | Anti-islanding                                          |      |

|                 | of PQ and mitigation techniques                         |      |

| 1.1.4 Custo     | om Power Devices (CPDs)                                 | 8    |

| 1.1.5 Real-     | time performance study                                  | 11   |

| 1.2 Research    | Objectives                                              | 12   |

| 1.3 Research    | Contribution                                            | 13   |

| 1.4 Outline of  | f the Thesis                                            | 17   |

| Chanter 2 - De  | sign and Control Strategies of Custom Power Devices     | 19   |

|                 | on                                                      |      |

|                 | Shunt Active Power Filter (APF <sub>sh</sub> )          |      |

|                 | ing principle                                           |      |

|                 | hing dynamics                                           |      |

|                 | lation of design parameters                             |      |

| 2.2.3.1         | Switching frequencies (f <sub>sw</sub> )                |      |

| 2.2.3.2         | Interfacing inductor (L <sub>sh</sub> )                 |      |

| 2.2.3.3         | Hysteresis band (h)                                     |      |

| 2.2.3.4         | DC link voltage (V <sub>dc</sub> )                      |      |

| 2.2.3.5         | DC link capacitor (C <sub>dc</sub> )                    |      |

| 2.3 Design of   | Series Active Power Filter (APF <sub>se</sub> )         |      |

|                 | ion transformer                                         |      |

| 2.3.2 Interf    | acing inductor / Low pass filter (LPF)                  | 34   |

| 2.3.3 DC li     | nk capacitor and energy storage device                  | 36   |

| 2.4 Design of    | Unified Power Quality Conditioner (UPQC)                  | 36  |

|------------------|-----------------------------------------------------------|-----|

| 2.5 Control St   | trategies                                                 | 37  |

| 2.5.1 Shunt      | Active Power Filter (APF <sub>sh</sub> )                  | 38  |

| 2.5.2 Series     | Active Power Filter (APF <sub>se</sub> )                  | 40  |

| 2.5.3 Unifie     | ed Power Quality Conditioner (UPQC)                       | 41  |

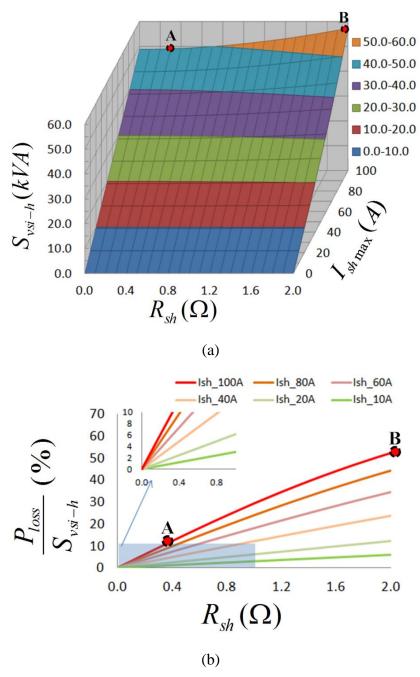

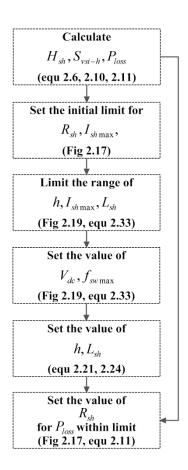

| 2.6 Selection    | of design parameters for a 3-ph, 3-wire APF <sub>sh</sub> | 44  |

| 2.6.1 Select     | tion of hysteresis band, h                                | 47  |

| 2.6.2 Limit      | on the I <sub>shmax</sub>                                 | 48  |

| 2.6.3 Select     | tion of V <sub>dc</sub>                                   | 50  |

| 2.6.4 Select     | tion of C <sub>dc</sub>                                   | 51  |

| 2.6.5 Verifi     | cation of switching dynamics and frequencies              | 52  |

| 2.7 Conclusio    | n                                                         | 54  |

|                  |                                                           |     |

| •                | egration and Placement of UPQC in DG Integrated Network   |     |

|                  | on                                                        |     |

| _                | n of UPQC                                                 |     |

|                  | - UPQC) <sub>DC-linked</sub>                              |     |

|                  | $(C-DG)_{Separated}$                                      |     |

|                  | analysis                                                  |     |

|                  | ection of DG Source with Electric Power Systems           |     |

|                  | t of UPQC in DG Network                                   |     |

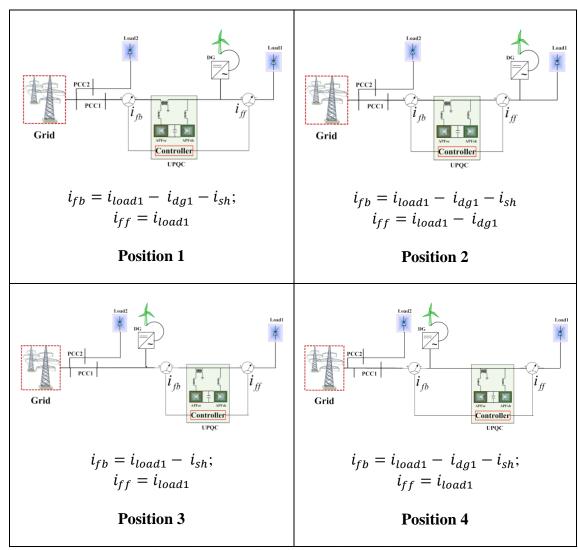

| 3.4.1 Placer     | ment of UPQC and its current feedback sensors             | 67  |

| 3.4.1.1          | Position 1                                                | 67  |

| 3.4.1.2          | Position 2                                                | 68  |

| 3.4.1.3          | Position 3                                                | 69  |

| 3.4.1.4          | Position 4                                                | 69  |

| 3.4.2 Impac      | et on UPQC control                                        | 69  |

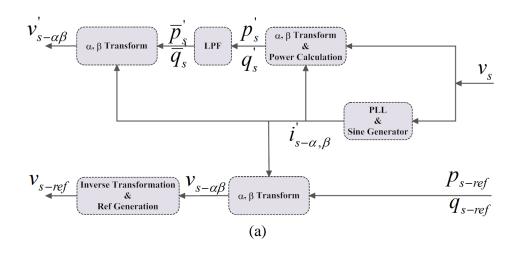

| 3.4.2.1          | Generation of reference current                           | 72  |

| 3.4.2.2          | Harmonic current compensation                             | 74  |

| 3.4.2.3          | THD at PCC1                                               | 76  |

| 3.4.2.4          | TDD at PCC1                                               | 77  |

| 3.4.3 Perfor     | rmance of UPQC with bi-directional power flow             | 79  |

| 3.4.4 Advar      | ntages of DG sources/µGrid systems                        | 84  |

| 3.5 Conclusio    | n                                                         | 84  |

|                  |                                                           |     |

| _                | rallel Operation of Inverters and Active Power Filters in | 0.= |

|                  | neration Systems                                          |     |

|                  | onof Parallel Operation of Inverter                       | 85  |

| 4.7. Principle ( | DEFALABEL COETAHOR OF INVESTEE                            | Xh  |

| 4.3 Control Strategies in Parallel O | peration of Inverter                   | 88  |

|--------------------------------------|----------------------------------------|-----|

| 4.3.1 Active load sharing / currer   | nt distribution                        | 89  |

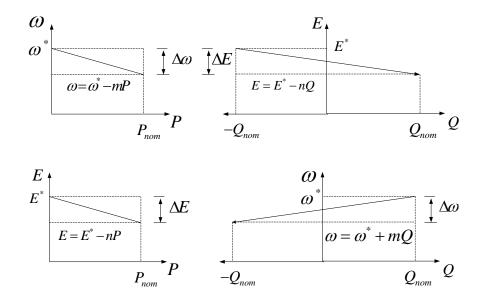

| 4.3.2 Droop control                  |                                        | 90  |

| 4.3.3 Outcomes                       |                                        | 91  |

| 4.4 Working Principle of Droop Co    | ontrol Method                          | 92  |

| 4.5 Control Strategies in Parallel O | peration of APF                        | 95  |

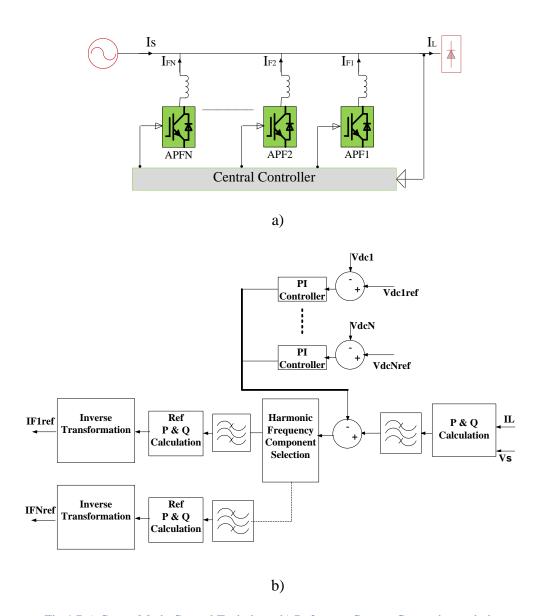

| 4.5.1 Frequency splitting (FS) / C   | Centre mode control (CMC)              | 96  |

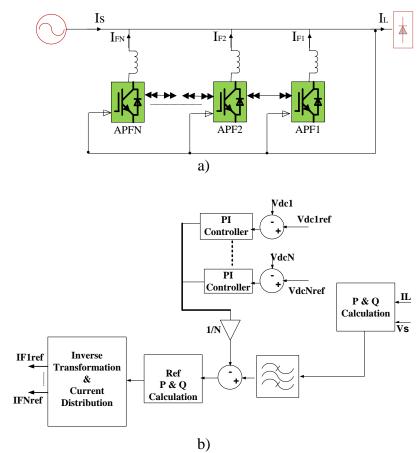

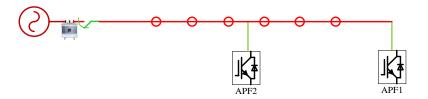

| 4.5.2 Power splitting (PS) / Distr   | ibuted control (DC)                    | 97  |

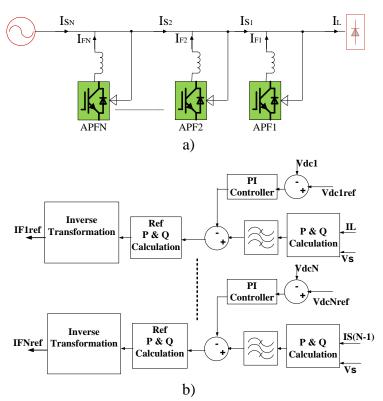

| 4.5.3 Capacity limitation control    | (CLC) / Master – Slave control (MSC)   | 98  |

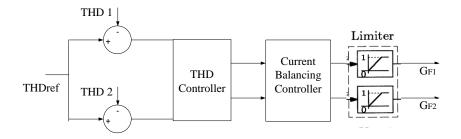

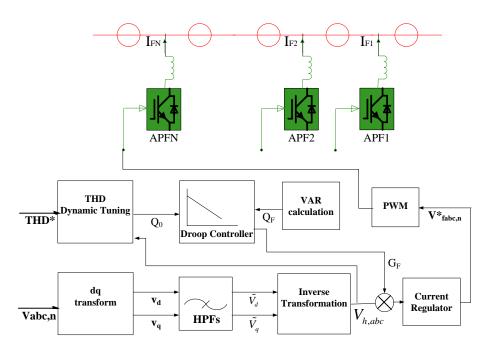

| 4.5.4 THD based cooperative cor      | ntrol                                  | 104 |

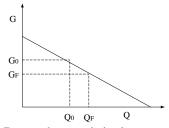

| 4.5.5 Droop control for APF          |                                        | 105 |

| 4.5.5.1 Voltage harmonics            | control                                | 105 |

| 4.5.5.2 Current harmonics of         | control                                | 106 |

| 4.5.5.3 Droop control for m          | ultiple parallel APF                   | 106 |

| 4.6 Conclusion                       |                                        | 108 |

|                                      |                                        |     |

|                                      | osal for Integration of UPQC in DG Con |     |

|                                      | work                                   |     |

|                                      |                                        |     |

| •                                    |                                        |     |

| •                                    |                                        |     |

| C I                                  |                                        |     |

|                                      |                                        |     |

|                                      | ion                                    |     |

|                                      |                                        |     |

|                                      |                                        |     |

|                                      |                                        |     |

| -                                    |                                        |     |

|                                      | n (PSD)                                |     |

| •                                    | eC)                                    |     |

|                                      | C)                                     |     |

|                                      |                                        |     |

| _                                    | nnection (SynRec)                      |     |

| -                                    | G-I                                    |     |

| ·                                    | G <sub>-IR</sub>                       |     |

|                                      | O-IK                                   |     |

|                                      |                                        |     |

|                                      |                                        | 141 |

| 5.5.1.2        | Reverse-flow mode                                       | 142 |

|----------------|---------------------------------------------------------|-----|

| 5.5.2 Island   | ded Mode                                                | 144 |

| 5.5.3 Reco     | nnection                                                | 146 |

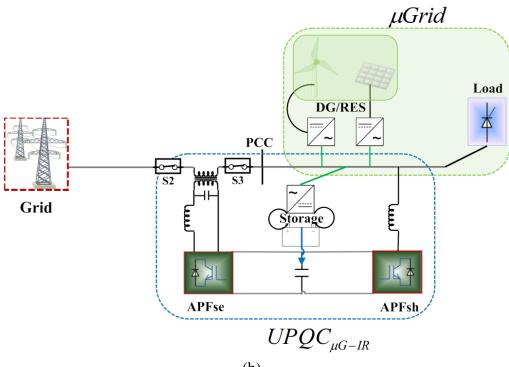

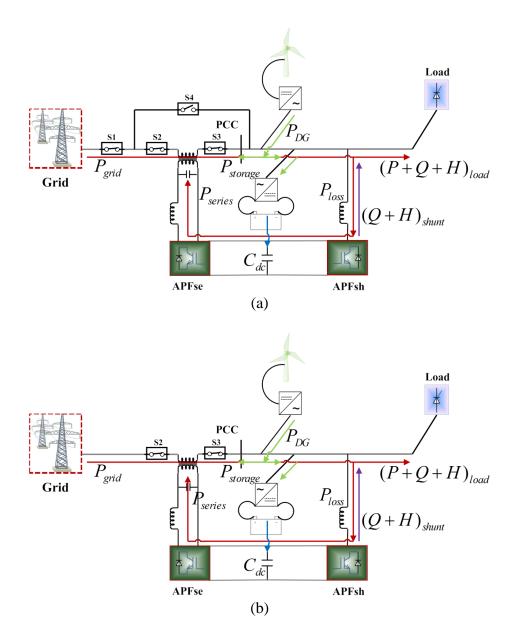

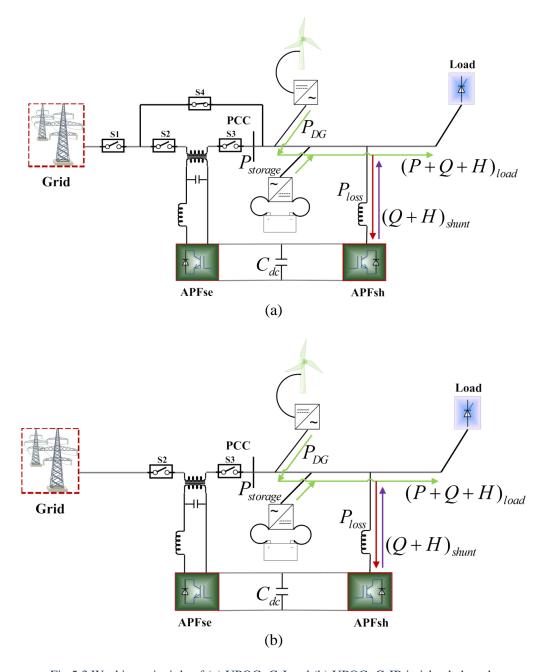

| 5.5.4 Powe     | r Flow                                                  | 148 |

| 5.6 Simulation | on Study - UPQC <sub>μG-IR</sub>                        | 149 |

| 5.6.1 Interd   | connection mode                                         | 152 |

| 5.6.1.1        | Forward-flow mode                                       | 152 |

| 5.6.1.2        | Reverse-flow mode                                       | 153 |

| 5.6.2 Island   | ded Mode                                                | 155 |

| 5.6.3 Reco     | nnection                                                | 156 |

| 5.6.4 Powe     | r Flow                                                  | 159 |

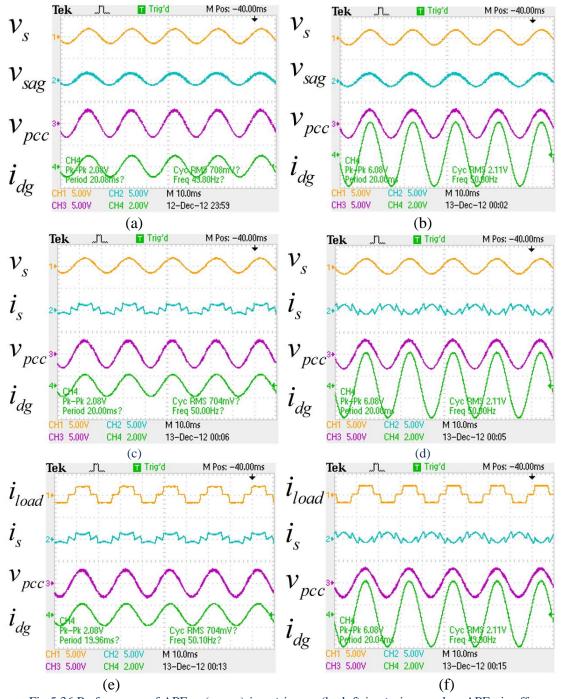

| 5.7 Hardware   | Results                                                 | 159 |

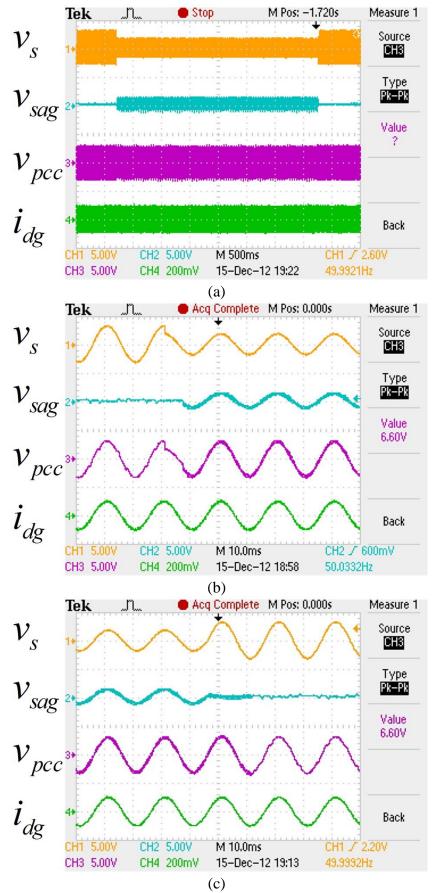

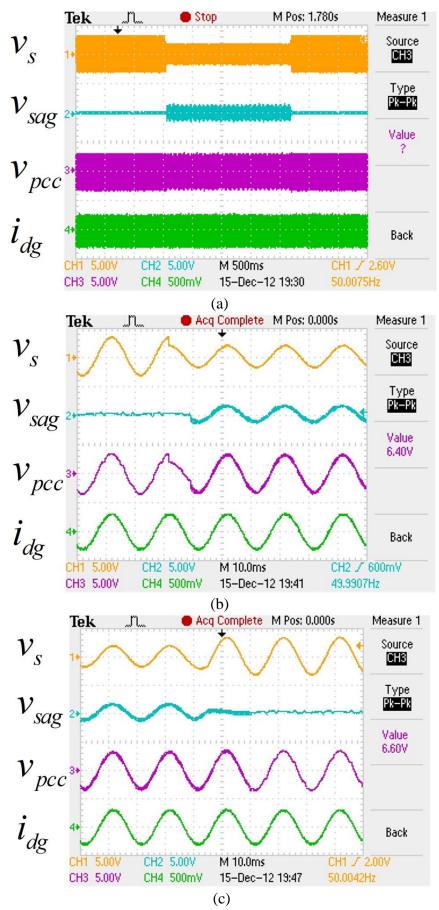

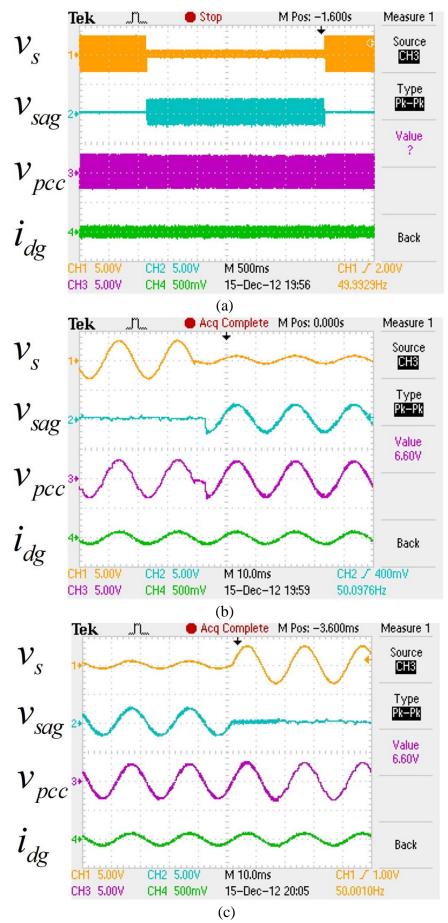

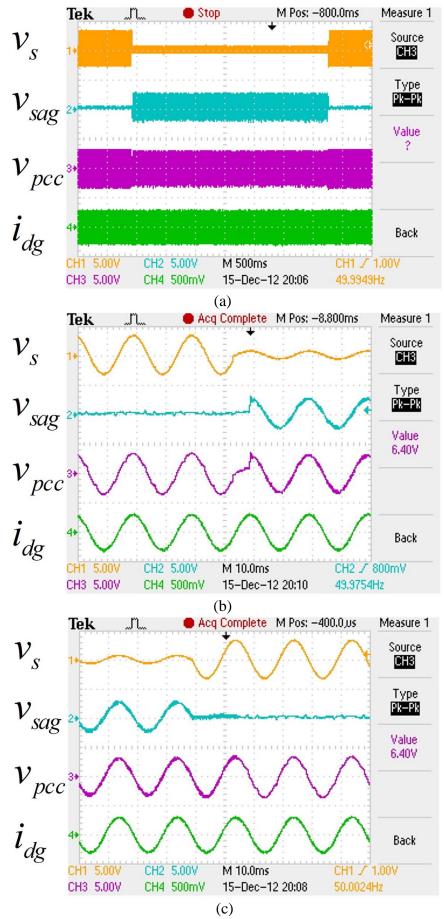

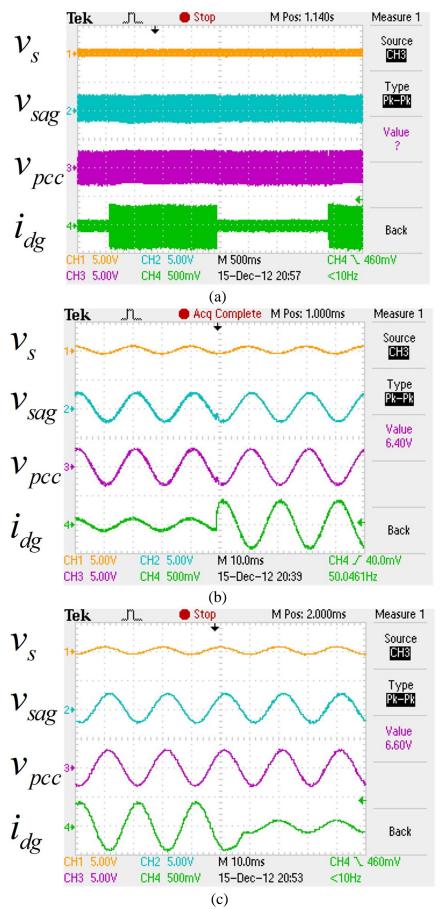

| 5.7.1 Interc   | connected mode                                          | 160 |

| 5.8 Conclusio  | on                                                      | 168 |

|                | stributed UPQC - A Way to Enhance Capacity and Achei    |     |

|                | ion                                                     |     |

| 6.2 Centralise | ed and Distributed Systems                              | 170 |

|                | ations of centralized system (APF)                      |     |

|                | ibuted/Multi-unit parallel approach                     |     |

|                | enhancement techniques                                  |     |

| 6.4 Distribute | ed - UPQC (D-UPQC)                                      | 173 |

| _              | gn Issues                                               |     |

| 6.4.1.1        | APF <sub>se</sub>                                       |     |

| 6.4.1.2        | APF <sub>sh</sub>                                       |     |

| 6.4.1.3        | DC link Capacitor                                       | 180 |

| 6.4.2 Contr    | rol issues                                              |     |

| 6.4.2.1        | Model for circulating current (CC) flow                 |     |

| 6.4.2.2        | Control issues for the circulating current (CC) flow    | 185 |

| 6.4.2.3        | Selection of control method for APF <sub>sh</sub> units | 186 |

| 6.4.2.4        | Control of switches                                     | 186 |

| 6.4.3 Simu     | lation Study                                            | 186 |

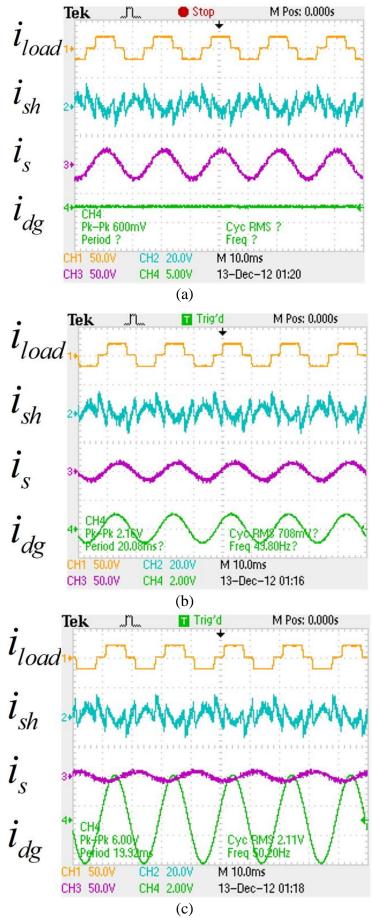

| 6.4.4 Hard     | ware Results                                            | 195 |

| 6.5 Conclusion | on                                                      | 195 |

| -              | onclusions and Future Work                              |     |

| 7.1 Conclusio  | ons                                                     | 198 |

| 7.2 Future we  | orke                                                    | 201 |

| Reference           |     |

|---------------------|-----|

| Appendix1           | 213 |

| Appendix2           | 215 |

| List of Publication | 227 |

# **List of Figures**

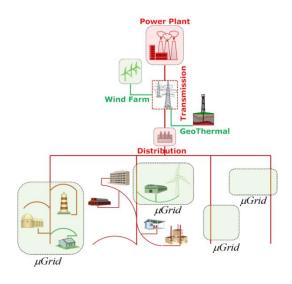

| Fig 1.1 A Typical DG connected distribution system with μGrid                                                                                                                                           | 3          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

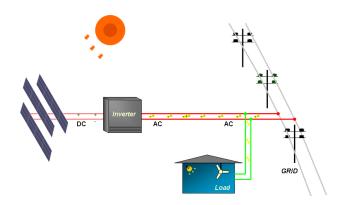

| Fig 1.2 General structure of grid-connected PV system                                                                                                                                                   | 5          |

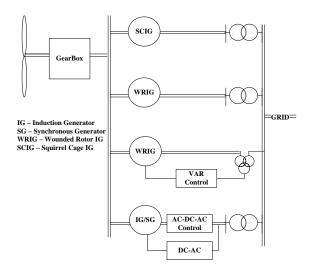

| Fig 1.3 Different types of wind energy system                                                                                                                                                           | 5          |

| Fig 1.4 Extrapolation of PQ cost to EU economy in LPQI surveyed sectors [21] .                                                                                                                          | 8          |

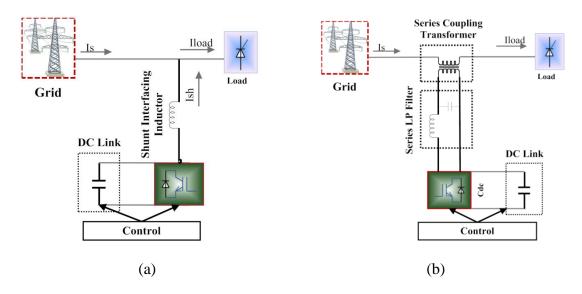

| Fig 1.5 System configuration of (a) DSTATCOM and (b) DVR                                                                                                                                                | 9          |

| Fig 1.6 System configuration of UPQC                                                                                                                                                                    | 10         |

| Fig 1.7 Real-time simulation structure in SIL configuration (a) software synchron                                                                                                                       | nization   |

| and (b) hardware synchronization mode                                                                                                                                                                   | 12         |

| Fig 2.1 a) Voltage source and b) Current source Shunt Active Power Filter [26]                                                                                                                          | 21         |

| Fig 2.2 (a) A 3-phase 3-wire power system with APF <sub>sh</sub> ; (b) Power transfer from A                                                                                                            | $APF_{sh}$ |

| to the PCC                                                                                                                                                                                              | 22         |

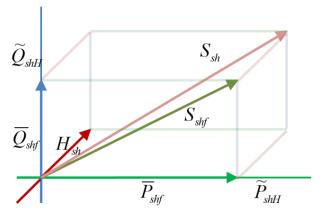

| Fig 2.3 Power tetrahedron diagram for APF <sub>sh</sub>                                                                                                                                                 | 24         |

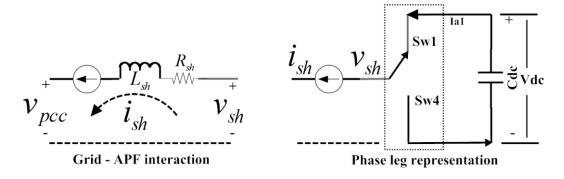

| Fig 2.4 Compensating power exchange between the Grid and shunt APF and the                                                                                                                              | phase      |

| leg representation for Phase A.                                                                                                                                                                         | 26         |

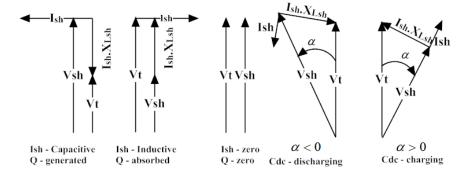

| Fig 2.5 Vector diagrams clarifying the working principle of shunt APF system                                                                                                                            | 26         |

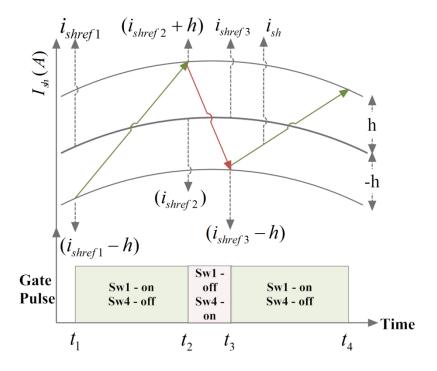

| Fig 2.6 Switching dynamics of a hysteresis based current controller                                                                                                                                     | 27         |

| Fig 2.7 a) Switching configuration of VSI and output waveform for (a,b) 1-phase                                                                                                                         | , 1-leg;   |

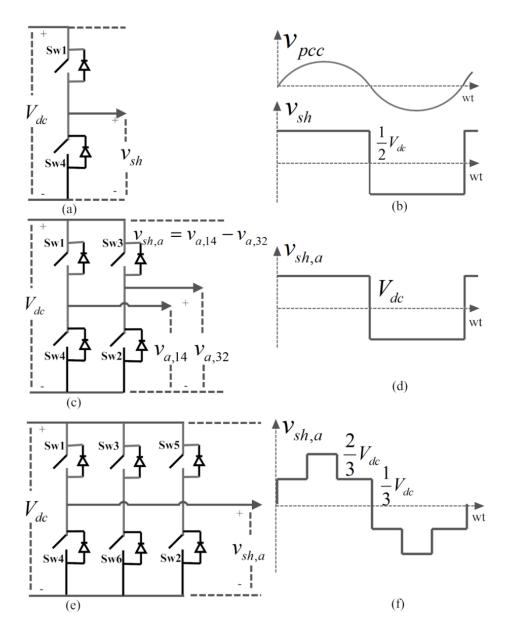

| (c,d) 1-phase, H-bridge and (e,f) 3-phase 3-leg                                                                                                                                                         | 30         |

| Fig 2.8 a) Distribution system with fault and b) vector diagram of voltage sag with                                                                                                                     | th         |

| phase jump and the used definition of pre-sag, sag and missing voltage                                                                                                                                  | 33         |

| Fig 2.9 Placement of LPF in APFse                                                                                                                                                                       | 35         |

| Fig 2.10 Equivalent circuit of single phase series APF                                                                                                                                                  | 36         |

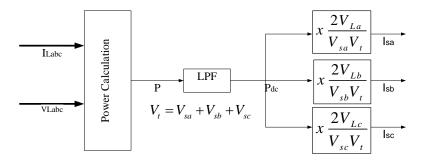

| Fig 2.11 Block diagram of Synchronous Detection Method                                                                                                                                                  | 39         |

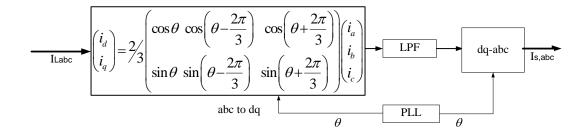

| Fig 2.12 Block diagram of d-q synchronous frame method                                                                                                                                                  | 39         |

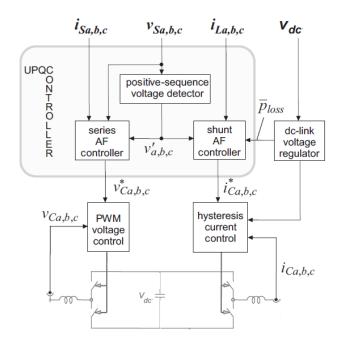

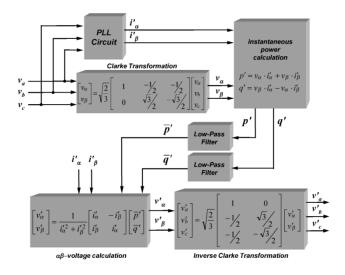

| Fig 2.13 Functional block diagram of the UPQC controller                                                                                                                                                | 43         |

| Fig 2.14 Positive sequence detection [26]                                                                                                                                                               | 43         |

| Fig 2.15 PWM voltage control with minor feedback control loops                                                                                                                                          | 43         |

| Fig 2.16 A 3-ph, 3-wire D-STATCOM connected to the grid and load at PCC                                                                                                                                 | 45         |

| Fig 2.17 (a) Relation between Actual VSI rating ( $S_{vsi-h}$ ), $R_{sh}$ and $I_{sh}$ ; (b) correspond                                                                                                 | ıding      |

| loss of inverter                                                                                                                                                                                        | 46         |

| Fig 2.18 Design parameters selection procedure for APF <sub>sh</sub>                                                                                                                                    | 47         |

| Fig 2.19 Selection of $h$ to maintain $THD_{Is}$ within IEEE standard                                                                                                                                   | 48         |

| Fig 2.20 (a) Relation between $f_{swmax}$ and $L_{sh}$ for the variation of $m$ and $I_{shmax}$ ; (b) Fig 2.20 (a) Relation between $f_{swmax}$ and $L_{sh}$ for the variation of $m$ and $I_{shmax}$ ; | Relation   |

| between $I_{shmax}$ and $L_{sh}$ for the variation of $m$ and $h$ .                                                                                                                                     | 49         |

| Fig 2.21 THDIs (%) for different values of m, obtained from simulation result for a               |

|---------------------------------------------------------------------------------------------------|

| system to compensate $I_{shmax} = 10$ to 20A using hysteresis band, $h$ as a) 5%, b) 10% and      |

| c) 20%50                                                                                          |

| Fig 2.22 Reduction of $P_{loss}$ with the increase of $f_{swmax}$ while the other parameters are  |

| constant51                                                                                        |

| Fig 2.23 Relation between z and S to calculate the $C_{dc}$ for m = 1.8 and 2.052                 |

| Fig 2.24 (a) One complete cycle of an APF in compensating mode, (b) showing the                   |

| values of design related parameters to calculate the maximum switching frequencies,               |

| $f_{swmax}$ and c) one of the minimum frequency, $f_{swmin}$ at close to 90 deg of supply voltage |

| condition53                                                                                       |

| Fig 3.1UPQC with DG connected to the DC link                                                      |

| Fig 3.2 (DG-UPQC) <sub>DC-linked</sub> System operation concept (a) Interconnected mode; (b)      |

| Islanding mode [75]                                                                               |

| Fig 3.3 Grid connected wind energy system with UPQC59                                             |

| Fig 3.4 Interconnection of DG sources with EPS and PCC61                                          |

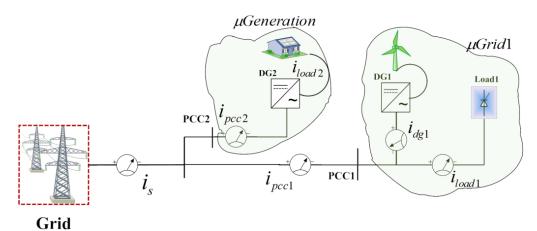

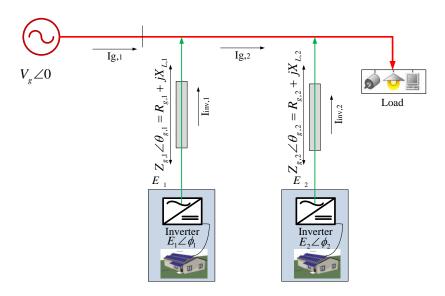

| Fig 3.5 Distributed Generation (DG) Integrated Network                                            |

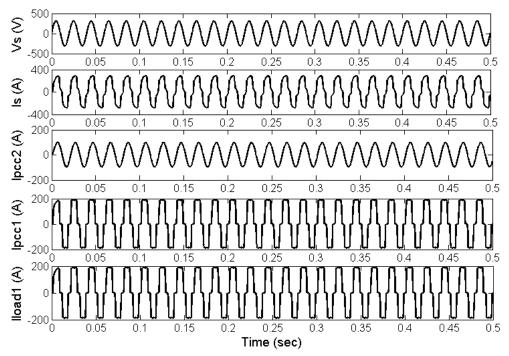

| Fig 3.6 Waveforms of the $iload1$ , $ipcc1$ , $ipcc2$ and $is$ when $idg1 = 0$ and $idg2 = 0$     |

| 63                                                                                                |

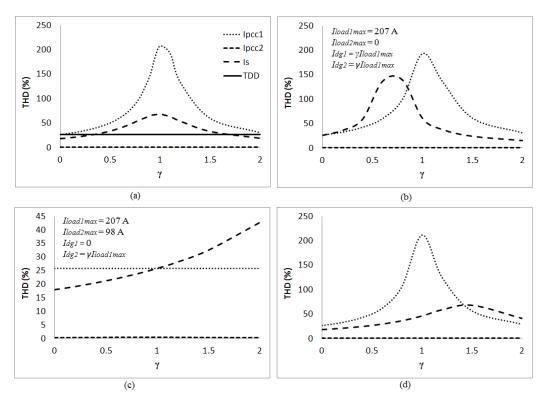

| Fig 3.7 Effect of $idg$ on the calculation of THD at different points65                           |

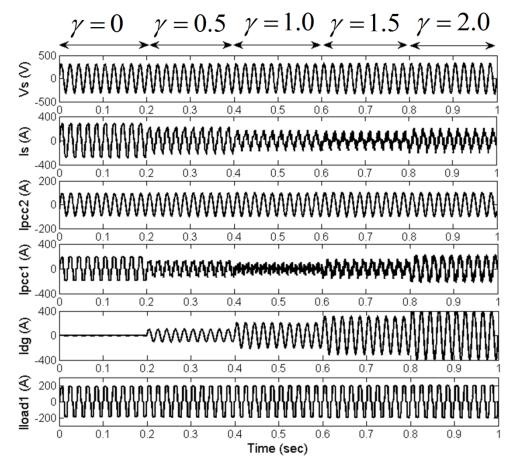

| Fig 3.8 Waveforms of the $iload1$ , $ipcc1$ , $ipcc2$ and $is$ when $Idg1$ varies from (0 to 2)   |

| of $lload1$ fmax and $iload2 = 0$ 65                                                              |

| Fig 3.9 Placement of UPQC in DG integrated network                                                |

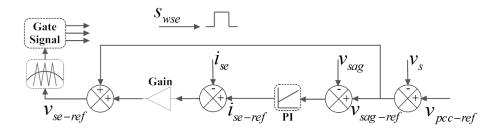

| Fig 3.10Generation of (a) source voltage reference and (b) control of series part of              |

| UPQC                                                                                              |

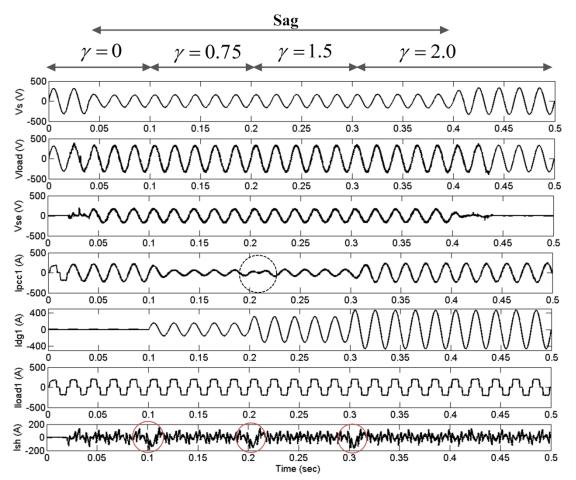

| Fig 3.11Performance of UPQC during voltage sag in position 271                                    |

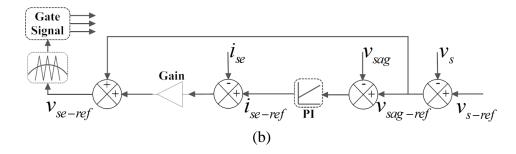

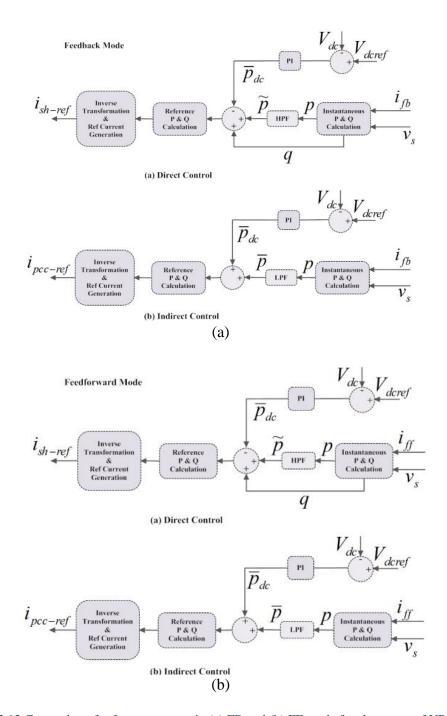

| Fig 3.12 Generation of reference current in (a) FB and (b) FF mode for shunt part of              |

| UPQC                                                                                              |

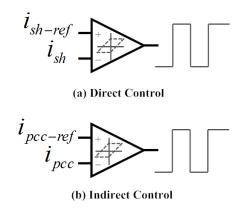

| Fig 3.13 Hysteresis control to generate the gate pulses for shunt part of UPQC74                  |

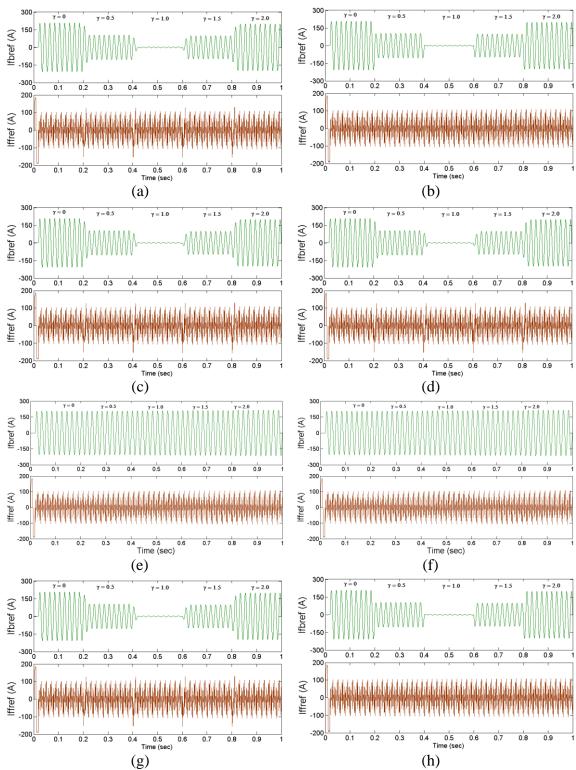

| Fig 3.14 Generation of Reference Current in Position1 - (a) FB and (b) FF sensor; in              |

| Position 2 - (c) FB and (d) FF sensor; in Position 3 - (e) FB and (f) FF sensor; in               |

| Position 4 - (g) FB and (h) FF sensor                                                             |

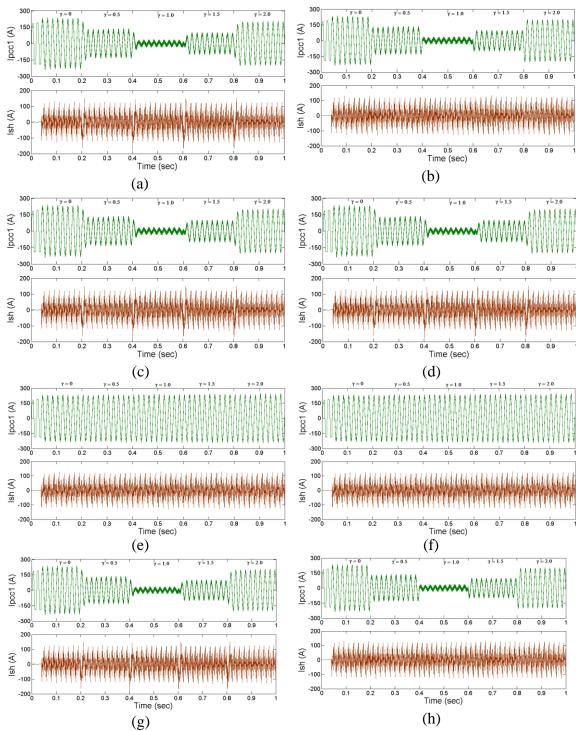

| Fig 3.15 Harmonic Current compensation in Position1 - (a) FB and (b) FF mode; in                  |

| Position 2 - (c) FB and (d) FF mode; in Position 3 - (e) FB and (f) FF mode; in Position          |

| 4 - (g) FB and (h) FF mode                                                                        |

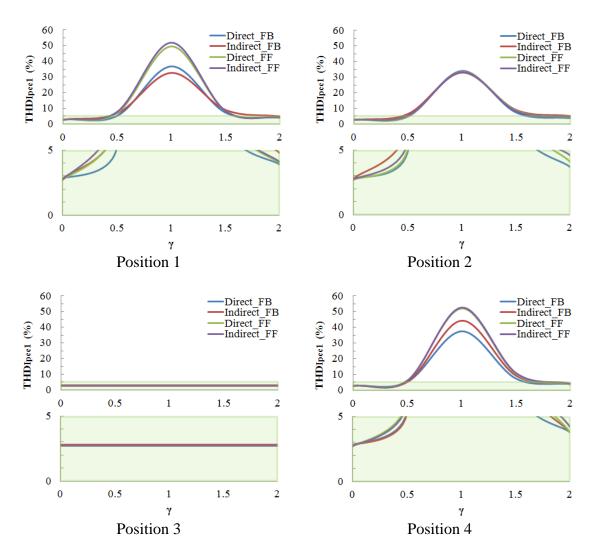

| Fig 3.16 THD @ ipcc1 for all position and control of UPQC in presence of DG source.        |

|--------------------------------------------------------------------------------------------|

| Lower part of each figure is the zoomed-in-version of the upper shaded part78              |

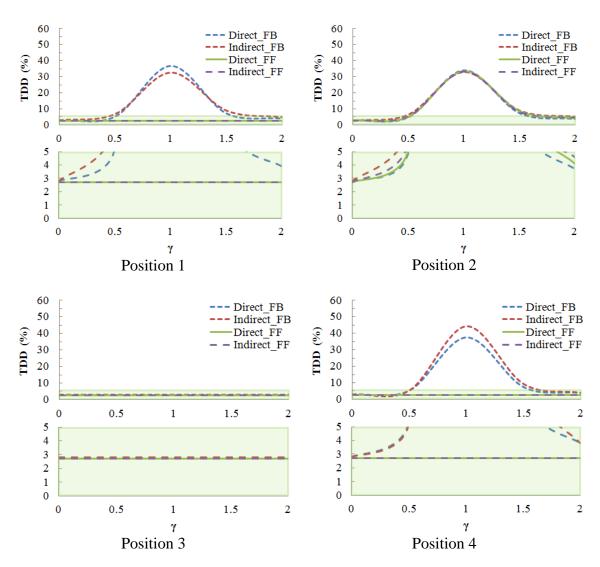

| Fig 3.17 TDD for all position and control of UPQC in presence of DG source79               |

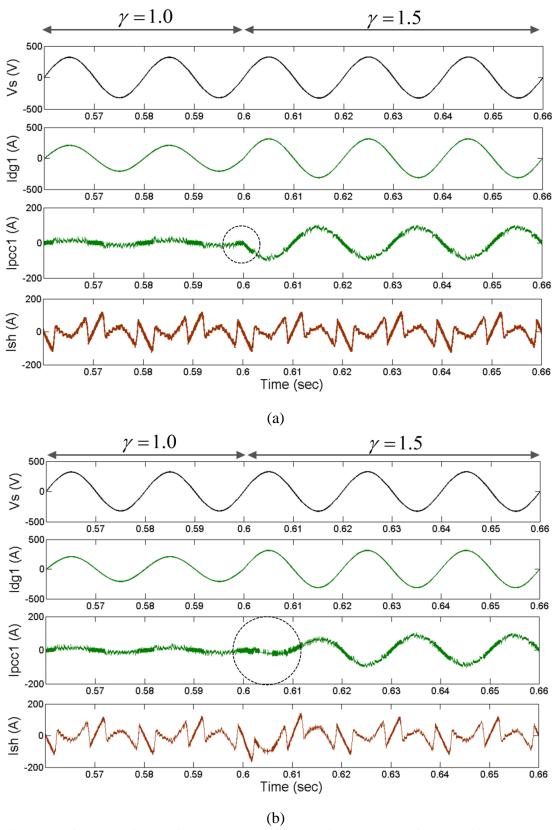

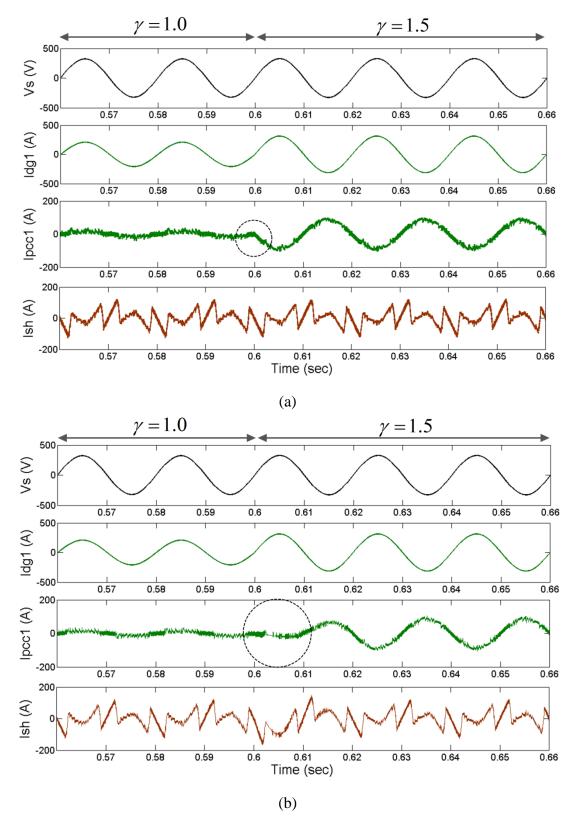

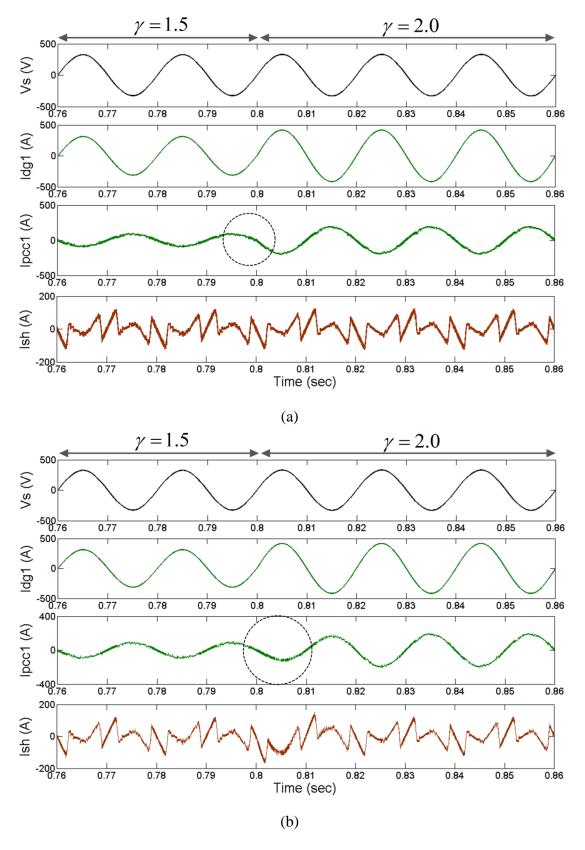

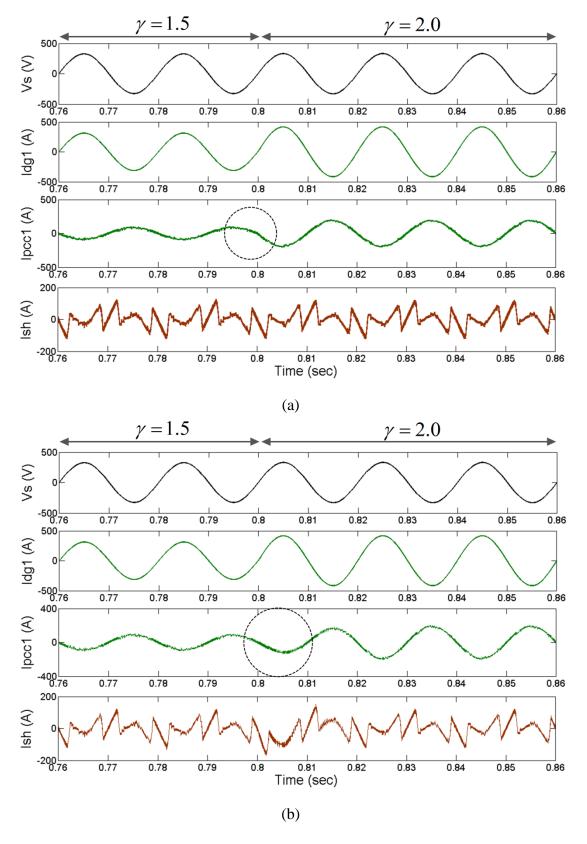

| Fig 3.18 Performance of UPQC in reverse current flow ( $\gamma > 1$ ) and FF mode for (a)  |

| Position 1 and (b) Position 2 with direct control;                                         |

| Fig 3.19 Performance of UPQC in reverse current flow ( $\gamma > 1$ ) and FF mode for (a)  |

| Position 1 and (b) Position 2 with indirect control                                        |

| Fig 3.20 Performance of UPQC in reverse current flow $(idg > iload)$ with dynamic          |

| change of $idg$ and FF mode for (a) Position 1 and (b) Position 2 with direct control82    |

| Fig 3.21 Performance of UPQC in reverse current flow ( $idg > iload$ ) with dynamic        |

| change of $idg$ and FF mode for (a) Position 1 and (b) Position 2 with indirect control 83 |

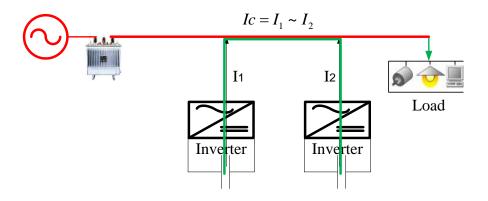

| Fig 4.1 Equivalent circuit of parallel inverter connected to the grid                      |

| Fig 4.2 Circulating current flow between the parallel inverters                            |

| Fig 4.3 a) Regenerative control structure to avoid dc-link overvoltage / to prevent        |

| circulating current; b) passive control using isolation transformer                        |

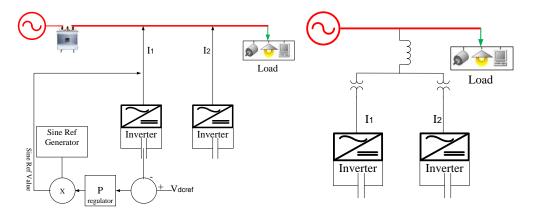

| Fig 4.4 Inverter connected to the grid (droop control)94                                   |

| Fig 4.5 Static droop characteristics                                                       |

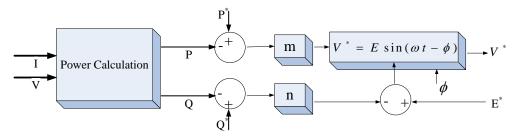

| Fig 4.6 A simple block diagram of P/Q droop controller                                     |

| Fig 4.7 a) Centre Mode Control Technique; b) Reference Current Generation technique        |

| 97                                                                                         |

| Fig 4.8 a) Distribute Control Technique; b) Reference Current Generation technique98       |

| Fig 4.9 a) Capacity Limitation Control Technique; b) Reference Current Generation          |

| technique                                                                                  |

| Fig 4.10 Parallel inverters with common dc link capacitor                                  |

| Fig 4.11 Parallel operation of APF with a combination of central control and capacity      |

| limitation                                                                                 |

| Fig 4.12 Parallel operation of APFs with different feeder                                  |

| Fig 4.13 a) A radial power distribution system with active power filter; b) a simple       |

| control circuit of the shunt APF as a voltage harmonic compensator102                      |

| Fig 4.14 Block diagram of cooperative control                                              |

| Fig 4.15 Droop characteristics between G – Q                                               |

| Fig 4.16 Distributed APFs System                                                           |

| Fig 4.17 A Dynamic tuning of THD for DAFS                                                  |

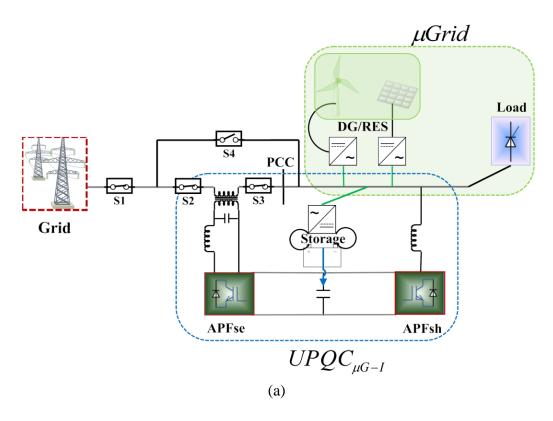

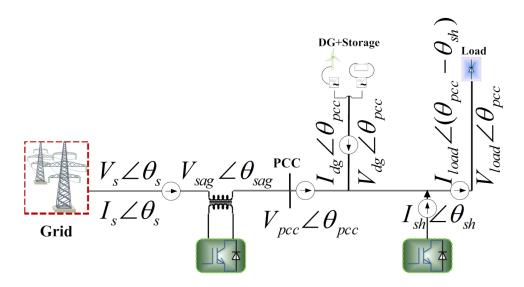

| Fig 5.1 Integration technique of the proposed UPQC <sub>IIG</sub>                          |

| Fig 5.2 Working principle of (a) UPQCμG-I and (b) UPQCμG-IR in interconnected                                          |

|------------------------------------------------------------------------------------------------------------------------|

| mode                                                                                                                   |

| Fig 5.3 Working principle of (a) UPQCμG-I and (b) UPQCμG-IR in islanded mode.116                                       |

| Fig 5.4 Fundamental frequency representation of proposed system117                                                     |

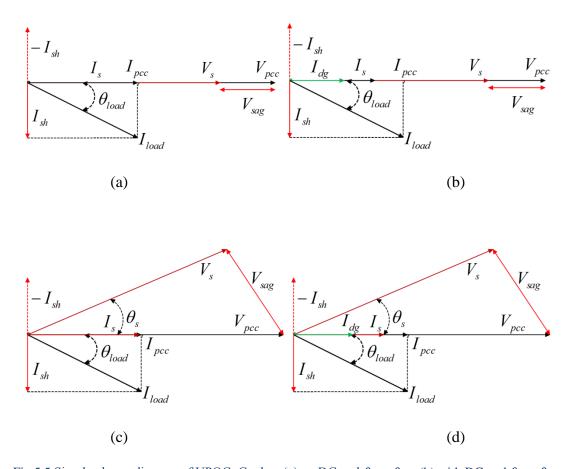

| Fig 5.5 Simple phasor diagram of UPQC $\mu$ G when (a) no DG and $\theta s = \theta pcc$ (b) with                      |

| DG and $\theta s = \theta pcc$ (c) no DG and $\theta s \neq \theta pcc$ (d) with DG and $\theta s \neq \theta pcc$ 118 |

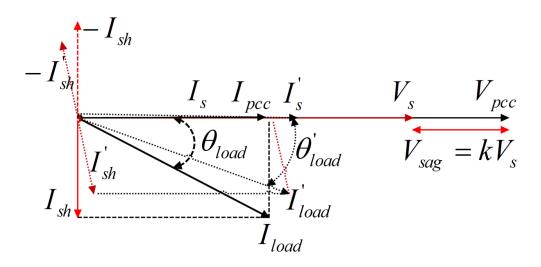

| Fig 5.6 Phasor diagram of UPQC during in phase voltage sag compensation119                                             |

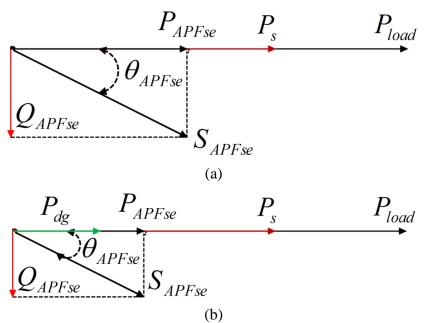

| Fig 5.7 Phasor diagram for active power exchanges in the proposed system (a) in                                        |

| absence of DG source and (b) in presence of DG source and / or storage120                                              |

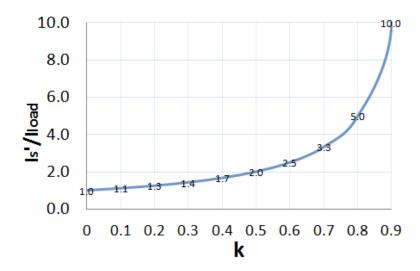

| Fig 5.8 Relation between source current, load current and $k$ for voltage sag                                          |

| compensation121                                                                                                        |

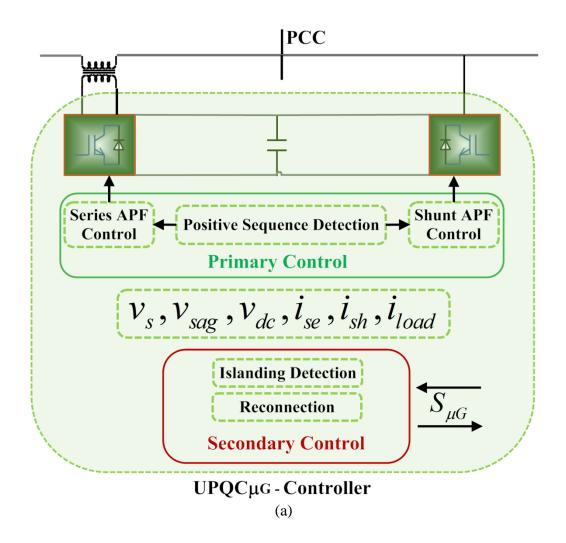

| Fig 5.9 Block diagram of proposed UPQC $_{\mu G}$ a) Controller, b) UPQC $_{\mu G\text{-}I}$ - Control                 |

| method and                                                                                                             |

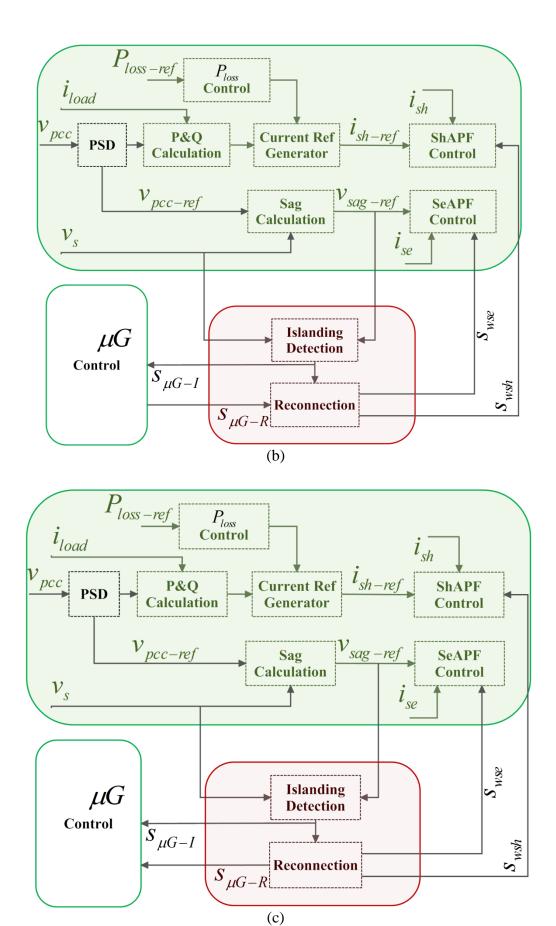

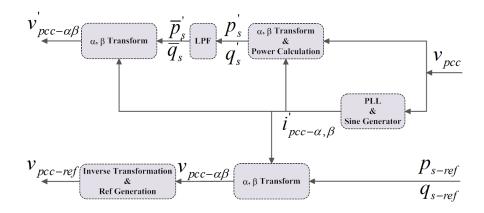

| Fig 5.10 Positive Sequence detection and Reference source voltage generation126                                        |

| Fig 5.11 Generation of reference voltage for series VSI and Series APF control127                                      |

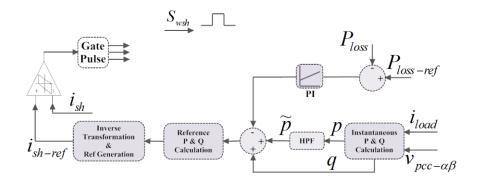

| Fig 5.12 Generation of reference current for shunt VSI and Shunt APF control127                                        |

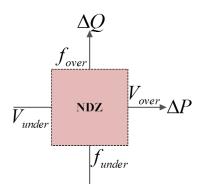

| Fig 5.13 Non-detection Zone                                                                                            |

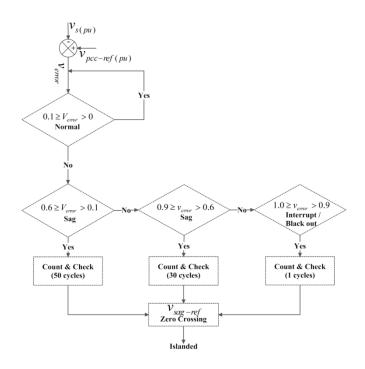

| Fig 5.14 Islanding detection algorithm                                                                                 |

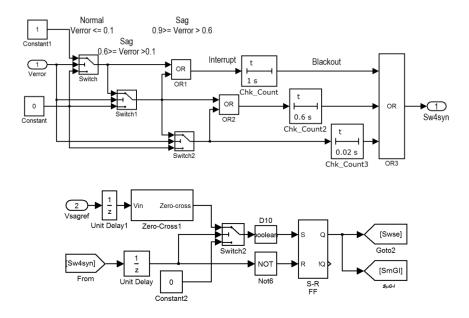

| Fig 5.15 Development of Islanding detection method in simulink                                                         |

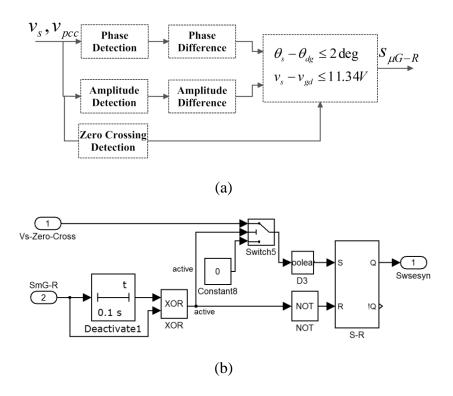

| Fig 5.16 Synchronization method for reconnection and signal generation: (a) in DG                                      |

| inverter                                                                                                               |

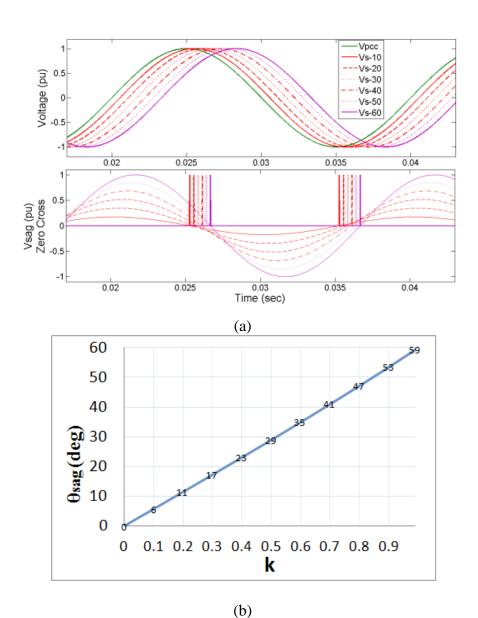

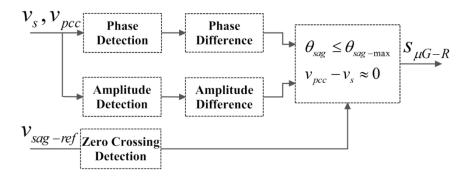

| Fig 5.17 (a) Relation between $V_s$ , $V_{pcc}$ and $V_{sag}$ and the point of zero-crossing; (b)                      |

| relation between acceptable limit of $\theta_{sag-max}$ for possible voltage sag (k) during                            |

| reconnection                                                                                                           |

| Fig 5.18 Logical condition for reconnection method                                                                     |

| Fig 5.19 Development of reconnection method in MATLAB137                                                               |

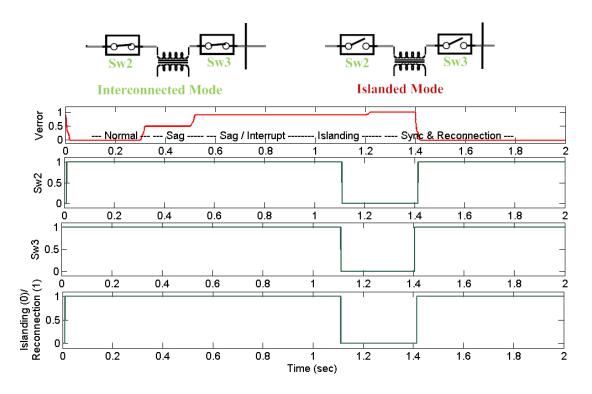

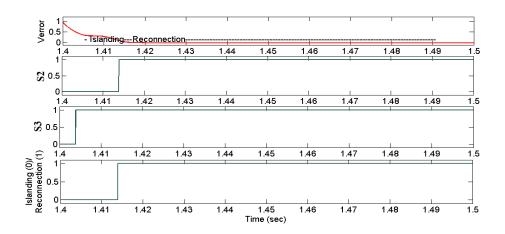

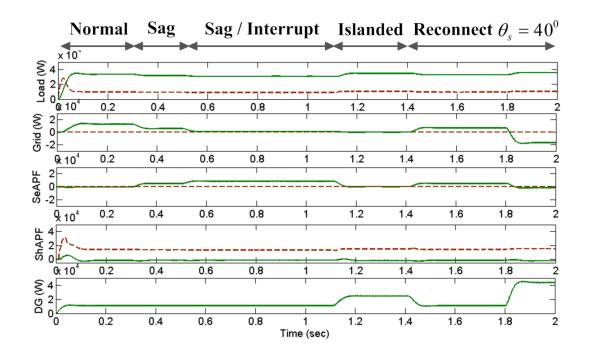

| Fig 5.20 Switching positions during the operation from 0 to 2 sec                                                      |

| Fig 5.21 Complete performance of $UPQC_{\mu\text{G-I}}$ during interconnected and islanded mode,                       |

| (a) voltage waveform and (b) current waveforms at difference conditions and positions                                  |

| in the network140                                                                                                      |

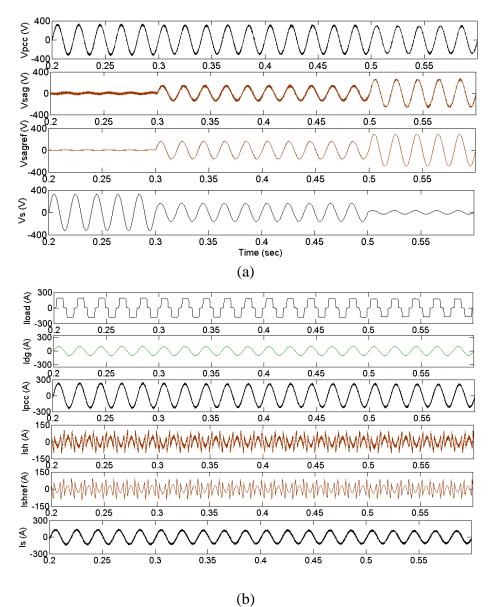

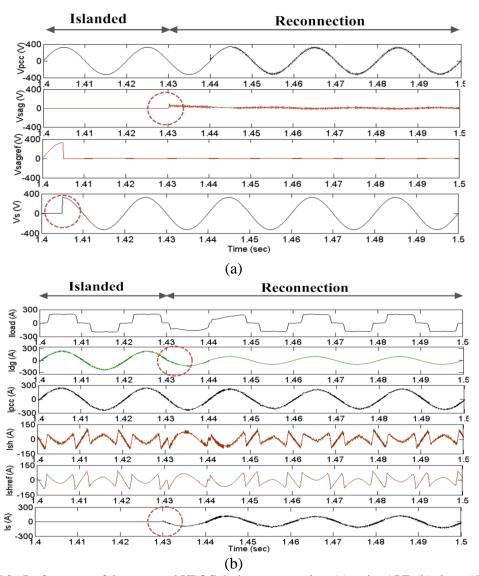

| Fig 5.22 Performance of the proposed $UPQC_{\mu G}$ ; a) series APF and b) shunt APF; from                             |

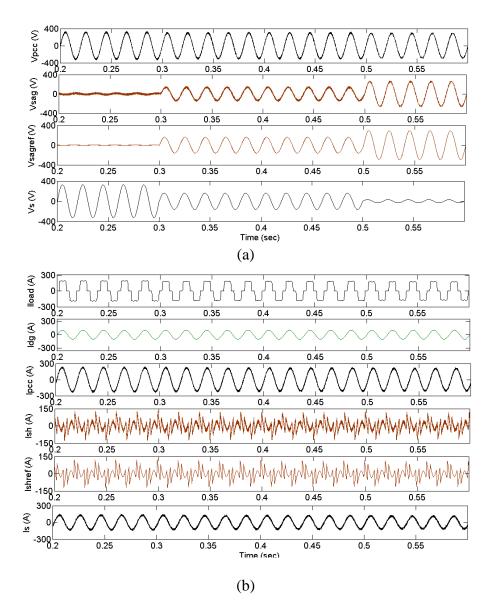

| 0.2 to 0.6 sec during interconnected and forward flow mode                                                             |

| Fig 5.23 Performance of the proposed UPQC $_{\mu G}$ ; a) series APF and b) shunt APF; during                          |

| interconnected and reverse flow mode                                                                                   |

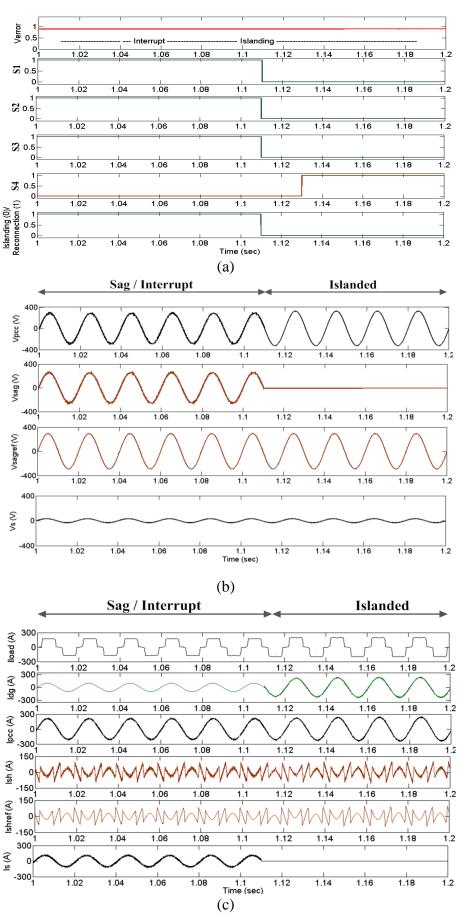

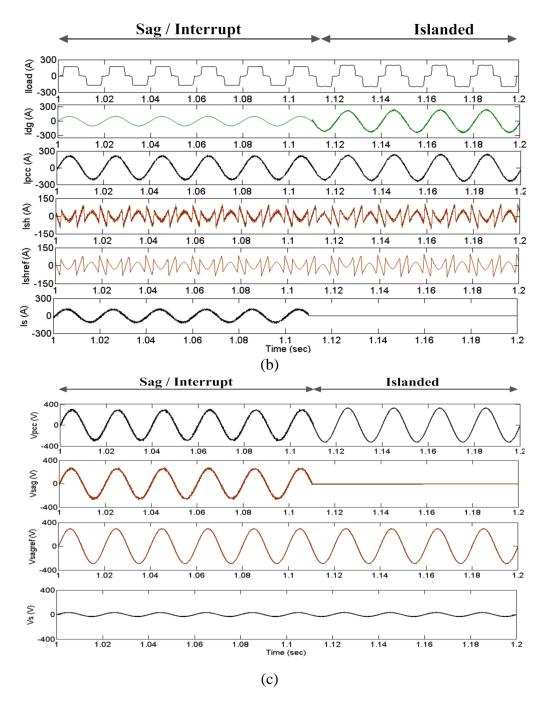

| Fig 5.24 Performance of the proposed UPQC $_{\mu G}$ ; (a) switching condition; b) series APF;       |

|------------------------------------------------------------------------------------------------------|

| c) shunt APF during islanded mode                                                                    |

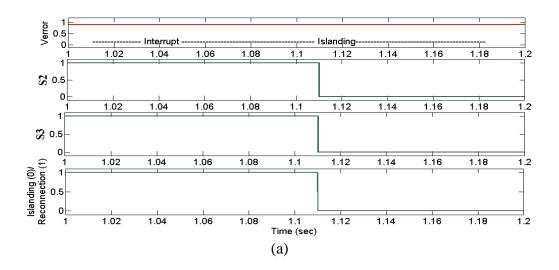

| Fig 5.25 Condition of different signals for reconnection process based on Fig 5.19147                |

| Fig 5.26 Performance of the proposed UPQC during reconnection, (a) series APF, (b)                   |

| shunt APF147                                                                                         |

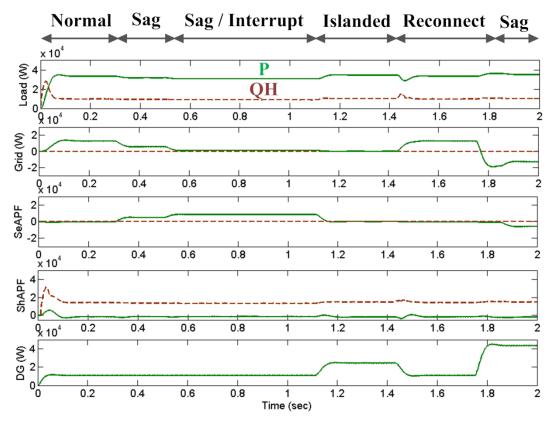

| Fig 5.27 Power flow during the simulation time                                                       |

| Fig 5.28 Switching positions during the operation from 0 to 2 sec                                    |

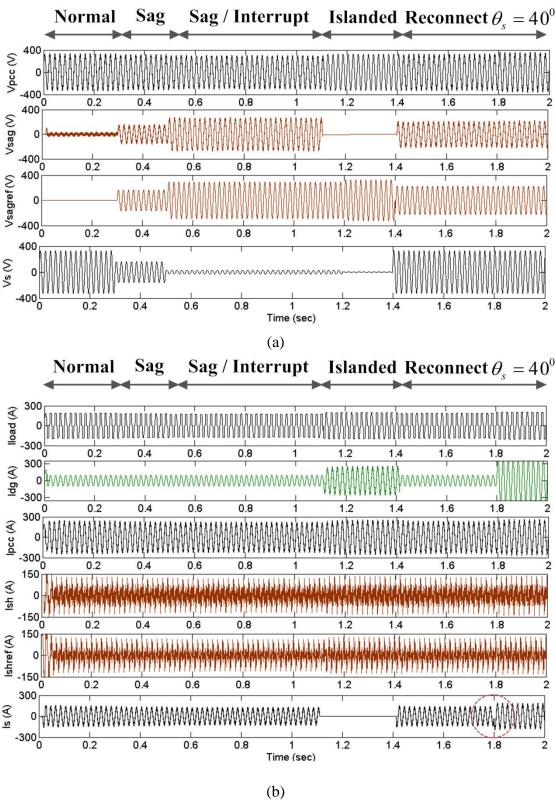

| Fig 5.29 Complete performance of $UPQC_{\mu\text{G-I}}$ during interconnected and islanded mode,     |

| (a) voltage waveform and (b) current waveforms at difference conditions and positions                |

| in the network                                                                                       |

| Fig 5.30 Performance of the proposed $UPQC_{\mu G}$ ; a) series APF and b) shunt APF; from           |

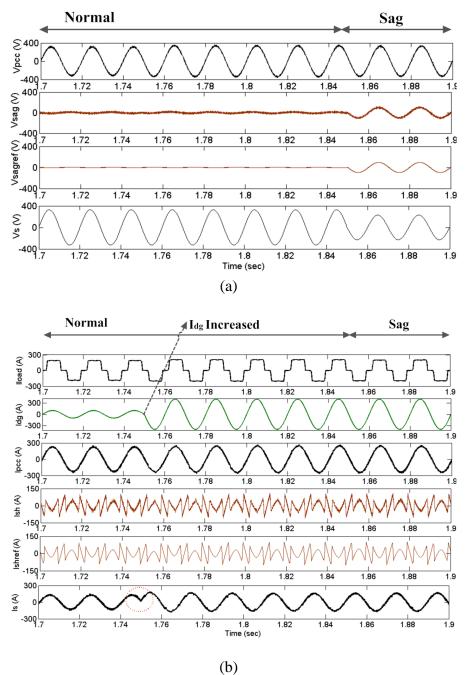

| 0.2 to 0.6 sec during interconnected and forward flow mode                                           |

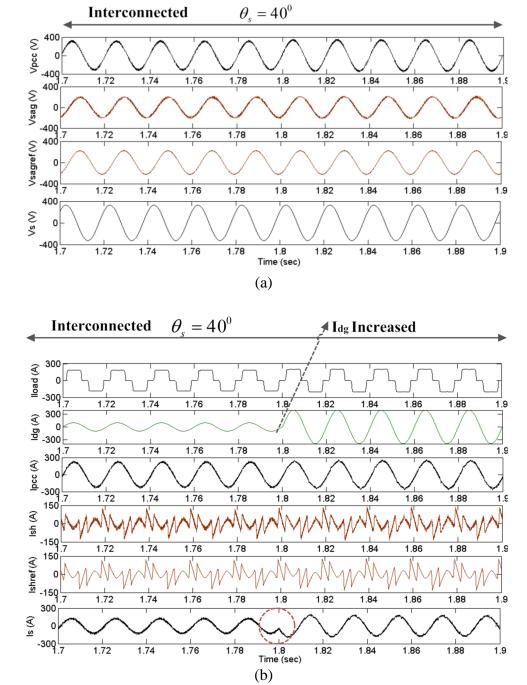

| Fig 5.31 Performance of the proposed UPQC $_{\mu G}$ ; a) series APF and b) shunt APF; during        |

| interconnected and reverse flow mode                                                                 |

| Fig 5.32 Performance of the proposed $UPQC_{\mu G}$ ; a) switching condition, b) shunt APF           |

| and (c) series APF; during islanded mode                                                             |

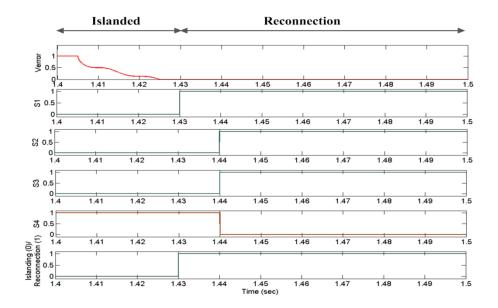

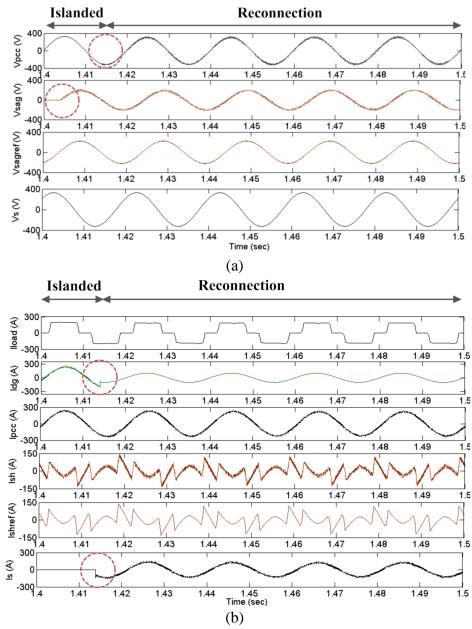

| Fig 5.33 Condition of different signals for reconnection process based on Fig 5.19158                |

| Fig 5.34 Performance of the proposed UPQC during reconnection, (a) series APF, (b)                   |

| shunt APF                                                                                            |

| Fig 5.35 Power flow during the simulation time                                                       |

| Fig 5.36 Performance of APF <sub>se</sub> ; (a, c, e) $idg < iloadf$ ; (b, d, f) $idg > iloadf$ when |

| APF <sub>sh</sub> is off160                                                                          |

| Fig 5.37 Performance of APFse in forward flow condition (a) compensating voltage sag                 |

| (40%), (b) during pre-sag and (c) post -sag condition                                                |

| Fig 5.38 Performance of APFse in reverse flow condition (a) compensating voltage sag                 |

| (40%), (b) during pre-sag and (c) post -sag condition                                                |

| Fig 5.39 Performance of APFse in forward flow condition (a) compensating voltage sag                 |

| (80%), (b) during pre-sag and (c) post -sag condition                                                |

| Fig 5.40 Performance of APFse in reverse flow condition (a) compensating voltage sag                 |

| (80%), (b) during pre-sag and (c) post -sag condition                                                |

| Fig 5.41 Performance of APFse in forward-reverse flow condition and compensating                     |

| voltage sag (80%) (a) dynamic change of $idg$ (b) $idg$ increasing: forward-reverse, (c)             |

| idg decreasing: reverse-forward flow                                                                 |

| Fig 5.42 Performance of APF <sub>sh</sub> (a) during $idg = 0$ , (b) forward flow (c) reverse flow   |

| mode                                                                                                 |

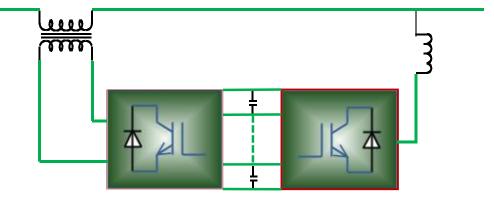

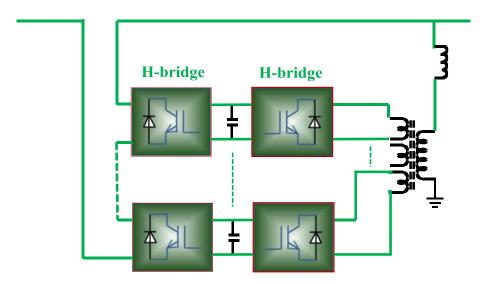

| Fig 6.1 Multi-level Converter based UPQC                                                                              |

|-----------------------------------------------------------------------------------------------------------------------|

| Fig 6.2 Series transformer-less Multi-module H-bridge                                                                 |

| Fig 6.3 Modular approach of UPQC based on power cells                                                                 |

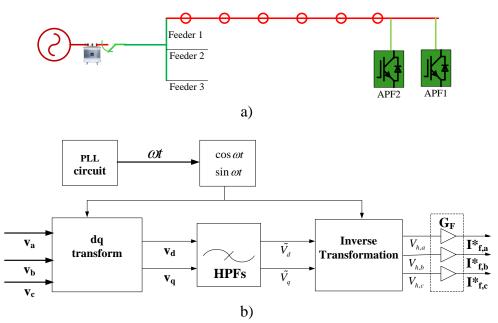

| Fig 6.4 Configuration of the proposed Distributed UPQC (D-UPQC)174                                                    |

| Fig 6.5 Working diagram of the D-UPQC with an electrical network175                                                   |

| Fig 6.6 Equivalent electrical circuit of the system shown in Fig 7.5175                                               |

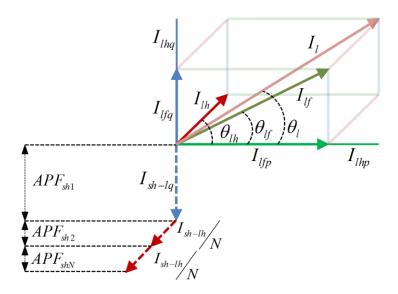

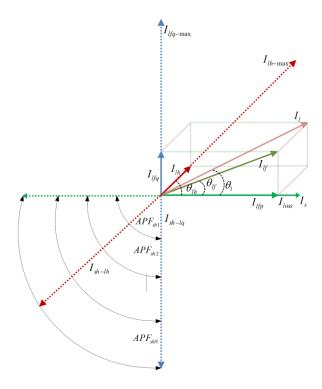

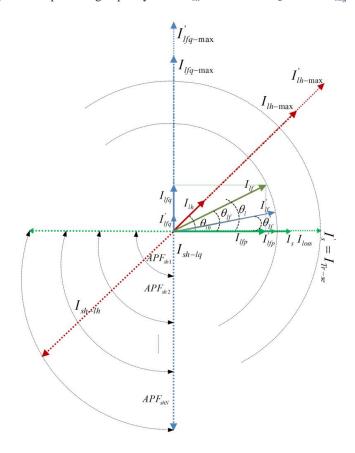

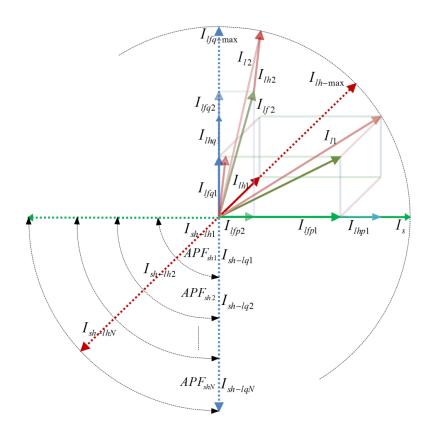

| Fig 6.7 Tetrahedron diagram of the load current and the compensating part of the $\mbox{APF}_{\mbox{\scriptsize sh}}$ |

| units                                                                                                                 |

| Fig 6.8 Compensating capacity of APF <sub>sh</sub> for the D-UPQC when $V_{sag} = 0$ ;                                |

| Fig 6.9 Compensating capacity of APF <sub>sh</sub> for the D-UPQC when $V_{sag} = kV_s$ 177                           |

| Fig 6.10 Compensating strategy of APF $_{sh}$ units for the D-UPQC                                                    |

| Fig 6.11 Single line diagram of a 3ph 2 units APF <sub>sh</sub> with common DC-link presenting                        |

| CC flow                                                                                                               |

| Fig 6.12 Possible mode of operation between two APF units to calculate circulating                                    |

| current                                                                                                               |

| Fig 6.13 Circulating current flow when 3 APF units work in parallel184                                                |

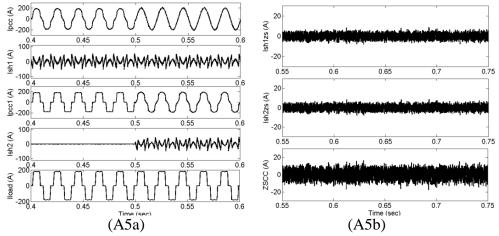

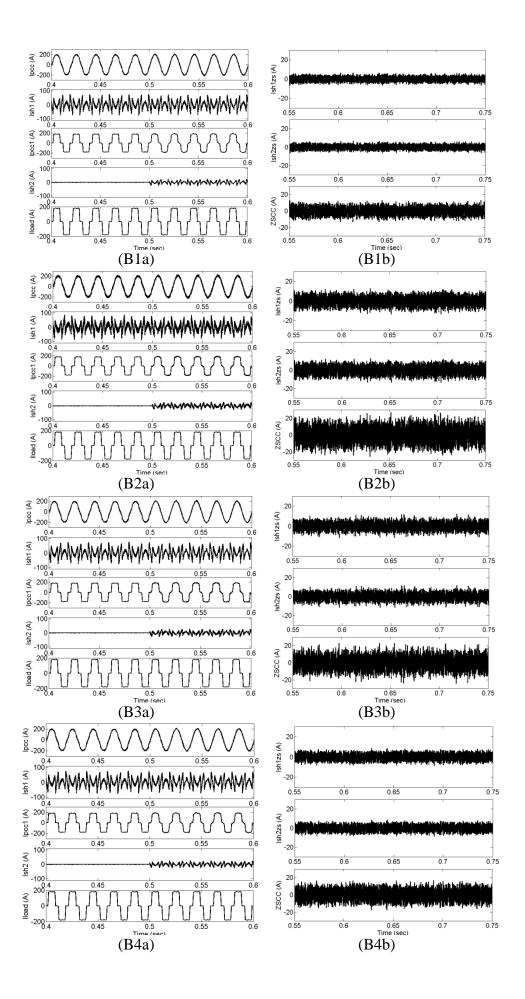

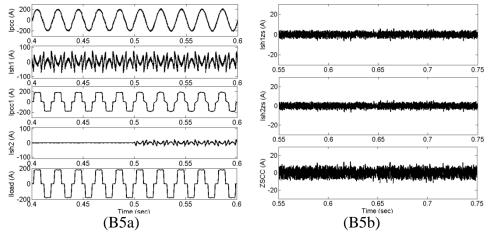

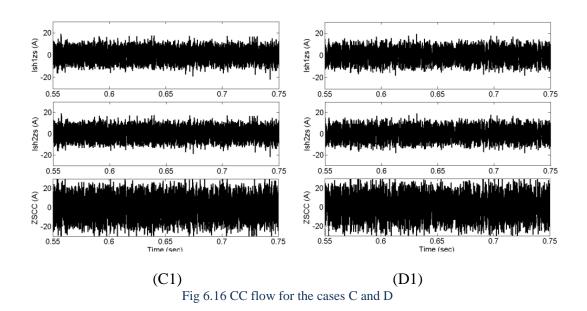

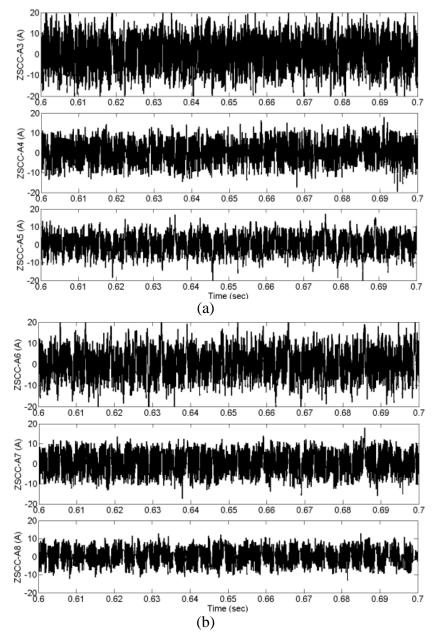

| Fig 6.14 Performance of $APF_{sh}$ for the cases (A1 - A5) and the corresponding CC flow                              |

|                                                                                                                       |

| Fig 6.15 Performance of $APF_{sh}$ for the cases (B1 - B5) and the corresponding CC flow                              |

|                                                                                                                       |

| Fig 6.16 CC flow for the cases C and D                                                                                |

| Fig 6.17 ZSCC comparison between the cases for (a) A3, A4, A5 and for (b) A6, A7,                                     |

| A8193                                                                                                                 |

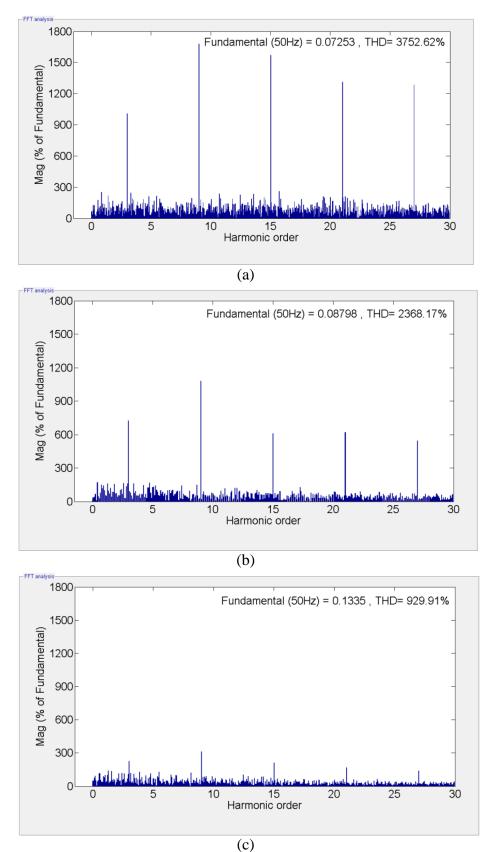

| Fig 6.18 FFT analysis for the cases (a) A6, (b) A7 and (c) A8                                                         |

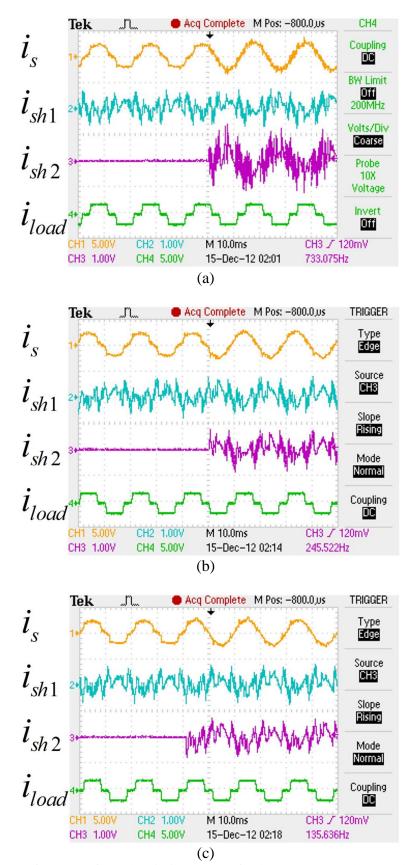

| Fig 6.19 Performance of APFsh units in D-UPQC for the cases (a) A6, (b) A7 and (c)                                    |

| A8196                                                                                                                 |

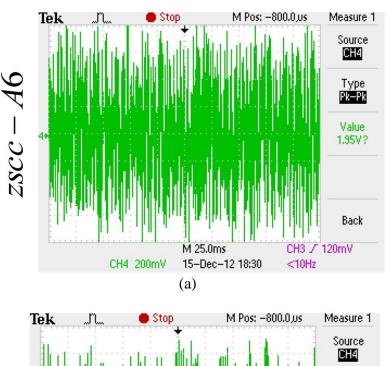

| Fig 6.20 ZSCC flow for the cases of (a) A6, (b) A7 and (c) A8197                                                      |

## **List of Tables**

| Table 1.1 - Categories of PQ Problems                                                                              | 4      |

|--------------------------------------------------------------------------------------------------------------------|--------|

| Table 1.2 PQ problems related to DG systems                                                                        | 7      |

| Table 2.1 Initial maximum limit for some of the design parameters                                                  | 45     |

| Table 2.2 Values of $I_{shmax}$ and $L_{sh}$ for different $V_{dc}$ condition at $f_{swmax} = 20 \text{kHz} \dots$ | 49     |

| Table 2.3 Design parameters of a Shunt APF for the verification study of switching                                 | ,      |

| frequencies                                                                                                        | 54     |

| Table 3.1 Comparative analysis of integration techniques of UPQC in DG system                                      | 59     |

| Table 3.2 Maximum harmonic current distortion [IEEE 1547, IEEE 519]                                                | 61     |

| Table 3.3 When $idg1 = 0$ and $idg2 = 0$ ; UPQC is not working                                                     | 63     |

| Table 3.4 Overall DG network parameters for the simulation                                                         | 67     |

| Table 3.5 Required Current Sensors                                                                                 | 72     |

| Table 3.6 Impact of UPQC sensors and DG source on reference current generation.                                    | 74     |

| Table 3.7 When UPQC is working; $idg1 = 0$ and $idg2 = 0$ ;                                                        | 77     |

| Table 4.1 Output impedance impact over power flow controllability [104]                                            | 95     |

| Table 4.2 Comparative analysis of parallel APFs controlling scheme with topologic                                  | es 103 |

| Table 5.1 DG response to abnormal utility conditions [6, 8]                                                        | 129    |

| Table 5.2 Typical characteristics of electrical grid voltage phenomena [IEEE 1159-                                 | •      |

| 1995]                                                                                                              | 130    |

| Table 5.3 Synchronization parameter limits for synchronous interconnection to an l                                 | EPS    |

| [8]                                                                                                                | 133    |

| Table 5.4 Overall network parameters for the simulation                                                            | 138    |

| Table 5.5 Timeline of the Operating Conditions                                                                     | 138    |

| Table 5.6 Timeline of the Operating Conditions                                                                     | 149    |

| Table 6.1Advantages and disadvantages of different capacity enhancement techniques                                 | ues    |

|                                                                                                                    | 173    |

| Table 6.2 A: $IAPFsh1 = IAPFsh2 = 0.5 * Ilqh - max$ and $Ilqh - max = 100A$                                        | 187    |

| Table 6.3 B: $IAPFsh1 = 0.75 * Ilqh - max$ ; $IAPFsh2 = 0.25 * Ilqh - max$ and                                     | l      |

| $Ilqh - max = 100A \dots$                                                                                          | 189    |

| Table 6.4 C: $IAPFsh1 = 0.6 * Ilqh - max$ ; $IAPFsh2 = 0.4 * Ilqh - max$ ; and                                     |        |

| $Ilqh - max = 100A \dots$                                                                                          | 191    |

| Table 6.5 D: $IAPFsh1 = 0.6 * Ilqh - max$ ; $IAPFsh2 = 0.4 * Ilqh - max$ ; and                                     |        |

| $Ilgh - max = 200A \dots$                                                                                          | 191    |

## List of Symbols

| $v_s, v_g$                        | Instantaneous Source / supply Voltage                        |

|-----------------------------------|--------------------------------------------------------------|

| $i_{_S}$                          | Instantaneous Source / supply Current                        |

| p, P, q, Q                        | Instantaneous active and reactive powers                     |

| $\overline{p}$ , $\overline{q}$   | Average active and reactive powers (dc values)               |

| $\widetilde{p}$ , $\widetilde{q}$ | Ripple active and reactive powers (ac values)                |

| $v_{\alpha}$ , $v_{\beta}$        | Voltages in the $\alpha$ - $\beta$ frame                     |

| $i_{lpha},\;i_{eta}$              | Currents in the $\alpha$ - $\beta$ frame                     |

| $i_d,\;i_q$                       | Currents in synchronous reference frame                      |

| $\overline{V_{_t}}$               | Voltage at the point of common coupling (PCC) in vector form |

| $v_l$                             | Instantaneous load voltage                                   |

| $V_{sh}$                          | Instantaneous voltage injected by the series active filter   |

| $v_t$                             | Instantaneous voltage at the PCC                             |

| $i_{s,ref}$                       | Supply reference current                                     |

| $oldsymbol{i}_{sh,ref}$           | Shunt active filter reference current                        |

| $C_{dc}$                          | DC link capacitor                                            |

| $m_a$                             | Amplitude modulation ratio                                   |

| $V_{dc}$                          | dc link voltage                                              |

| $V_{\it dc,ref}$                  | Reference dc link voltage                                    |

| $Q_{\mathit{sh}}$                 | Single-phase Reactive Power                                  |

| $L_{sh}$                          | Shunt Interfacing Inductor                                   |

| Н                                 | Hysteresis band                                              |

| $E_1$                             | Inverter Output Voltage                                      |

| f                                 | Grid frequency [Hz]                                          |

| $Z_{g}$                           | Magnitude of the grid impedance $[\Omega]$                   |

| $	heta_{g}$                       | Grid impedance angle [deg]                                   |

| ω                                 | Angular frequency of the output voltage [rad/s]              |

| <b>O</b> *                        | Reference angular frequency [rad/s]                          |

| ως                                | Cut-off angular frequency [rad/s]                            |

|                                   |                                                              |

| ωο | Resonant frequency [rad/s]  |  |  |

|----|-----------------------------|--|--|

| m  | Phase droop coefficient     |  |  |

| n  | Amplitude droop coefficient |  |  |

# **Chapter 1**

## Introduction

## 1.1 Background

Centralized power generation systems are facing the twin constraints of shortage of fossil fuel and the need to reduce emissions. Therefore, emphasis has increased on distributed generation (DG) networks with integration of renewable energy systems into the grid or on isolated microgrids (µGrid). This leads to energy efficiency and reduction in emissions. This can also reduce the long transmission line electrical power losses. With the increase of renewable energy penetration in the grid, power quality (PQ) challenges of the medium to low voltage power distribution system is becoming a major area of interest. Most of the integration of renewable energy systems to the grid takes place with the aid of power electronics converters. The main purpose of the power electronic converters is to integrate the DG to the grid in compliance with PQ standards. However, high frequency switching of inverters can inject additional harmonics to the systems, creating major PQ problems if not implemented properly. On the other hand, Custom Power Devices (CPD) such as STATCOM (Static compensator), DVR (Dynamic Voltage Restorer) and UPQC (Unified Power Quality Conditioner) are the latest development of interfacing devices between the distribution supply (grid) and consumer appliances. This class of equipment is designed to overcome voltage/current disturbances and improve the power quality by compensating the reactive and harmonic power generated or absorbed by the load. Therefore, the aim of the present research to explore the power quality improvement of distributed generation integrated networks with a unified power quality conditioner.

The rest of this section describes briefly the related issues of this research includes DG and microgrids, power quality problems, mitigation techniques, CPDs and real-time simulation. The remainder of this chapter is outlined as follow: Research objectives are described in section 1.2 which is followed by the research contribution in section 1.3. Section 1.4 is the details of the structure and content of the remaining chapters.

## 1.1.1 Distributed Generation (DG) and Microgrid (µGrid)

Distributed generation (DG) is the term often used to describe small-scale electricity generation, but there is no consensus on how DG should be defined. In some cases, DG is defined on the basis of the voltage level, whereas elsewhere the definition is based on the principle that DG is connected to circuits from which consumer loads are supplied directly. Usually DG is classified according to its different types and operating technologies. A detailed description of the types, technologies, applications, advantages and disadvantages of every available resource and technology is given in [1].

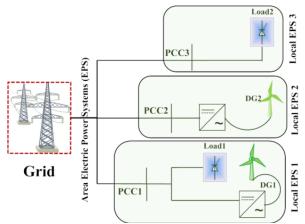

Fig 1.1 shows a typical DG connected μGrid system. Some of the benefits of this system are pointed out in [1, 2]. Although the benefits of DG includes voltage support, diversification of power sources, reduction in transmission and distribution losses and improved reliability, PQ problems are also of growing concern. Solar and wind energy are the most promising DG sources and their penetration level in the grid is also on the rise. Therefore, the study here is limited to the PQ disturbances due to solar and wind energy systems connected to the grid or μGrid system.

Fig 1.1 A Typical DG connected distribution system with μGrid

## 1.1.2 Power Quality (PQ) issues in DG or Microgrid (µGrid) system

Approximately 70 to 80% of all PQ related problems can be attributed to faulty connections and/or wiring [2]. Power frequency disturbances, electromagnetic interference, transients, harmonics and low power factor are the other categories of PQ problems (shown in Table 1.1) that are related to the source of supply and types of load [3]. Among these events, harmonics are the most dominant. The effects of harmonics on PQ are specially described in [2, 5]. According to the IEEE, harmonics in the power system should be limited in two ways; limit the harmonic current that a user can inject into the utility system at the point of common coupling (PCC) or limit the harmonic voltage that the utility can supply to any customer at the PCC. Details of these limits can be found in [5]. The IEC (International Electro-technical Commission) and the EU uses the term EMC (Electromagnetic Compatibility) which is "the ability of an equipment or system to function satisfactorily in its electromagnetic environment without introducing intolerable electromagnetic disturbances to anything in that environment" [6,7]. Again, the DG interconnection standards are to be followed when considering PQ, protection and stability issues [8]. Among the DG sources, PQ issues

related to solar and wind energy systems are the major concerns here. Therefore, a brief discussion has been introduced here.

Table 1.1 - Categories of PQ Problems

| Power Freq  | Electro-Magnetic   | Transient       | Harmonics   | Electrostatic        | Power       |

|-------------|--------------------|-----------------|-------------|----------------------|-------------|

| Disturbance | Interference       |                 |             | Discharge            | Factor (PF) |

| i. Low Freq | i. High freq       | i. Fast, short- | i. Low freq | i. Current flow with | i. Low PF   |

| phenomena   | phenomena          | duration event  | phenomena   | different potentials | causes      |

|             |                    |                 |             |                      | equipment   |

| ii. Produce | ii. Interaction    | ii. Produce     | ii. Produce | ii. Caused by direct | damage      |

| Voltage sag | between electric   | distortion like | waveform    | current or induced   |             |

| / swell     | and magnetic field | notch, impulse  | distortion  | electrostatic field  |             |

## 1.1.2.1 Solar photovoltaic (PV) system

Though the output of a PV panel depends on solar intensity and cloud cover, the PQ problems depend not only on irradiation but also on the overall performance of the solar photovoltaic system. This includes the PV modules, the filtering and the inverter controlling mechanism. Studies presented in [9], show that the short fluctuation of irradiance and cloud cover play an important role for low-voltage distribution grids with high penetration of PV. Concerning DG, voltage disturbances can cause the disconnection of inverters from the grid and therefore result in loss of energy supplied. Also, consideration of the long term performance of grid-connected PV systems shows a remarkable degradation of efficiency due to the variation of the source and performance of the inverter [10].

The general block diagram of a grid connected PV system is shown in Fig 1.2. Centralized or decentralized operation of PV systems can also be used and the overview of these PV-Inverter-Grid connection topologies along with their advantages and disadvantages are discussed in [10].

These power electronics converters, together with the operation of non-linear appliances, inject harmonics to the grid. In addition to the voltage fluctuation due to irradiation changes, cloud cover or shading effects can make the PV system unstable in

terms of grid connection. Therefore, this needs to be considered in the controller design for the inverter [11-14].

Fig 1.2 General structure of grid-connected PV system

## 1.1.2.2 Wind energy system

Fig 1.3 shows a simplified representation of some of the common types of wind energy systems. From the design perspective, some configurations involve the generators being directly connected to the grid through a dedicated transformer while others incorporate power electronic interfaces. Recent analysis and study [15] shows that the impact of the yaw error and horizontal wind shear on the power (torque) and voltage oscillations is more severe than the effects due to the tower shadow and vertical wind shear.

Fig 1.3 Different types of wind energy system

A literature survey [16] of the new grid codes adopted for wind power integration has identified the problems of integrating large amounts of wind energy to the electric grid. It suggests that new wind farms must be able to provide voltage and reactive power control, frequency control and fault ride-through capability in order to maintain system stability. An overview of the developed controllers for the converter of grid connected system has also been discussed in [17] and showed that the DFIG has now the most efficient design for the regulation of reactive power and the adjustment of angular velocity to maximize the output power efficiency. However, the drawbacks of converter-based systems are harmonic distortions injected into the system.

## 1.1.2.3 Anti-islanding

Anti-islanding is one of the important issues for grid-connected DG systems. A major challenge for the islanding operation and control schemes is the protection coordination of distribution systems with bidirectional flows of fault current. This is unlike the conventional over-current protection for radial systems with unidirectional flow of fault current. Therefore extensive research has been carried out and an overview of the existing protection techniques with islanding operation and control, for preventing disconnection of DGs during loss of grid, has been discussed in [18].

In terms of DG connected grid or µGrid systems, however, DG integration includes some level of power electronics to improve controllability and operating range. Whatever connection configuration is used, each DG system itself has an effect on the PQ of the distribution or transmission system. These PQ problems related to the most commonly used DG systems (solar, wind, hydro and diesel) are given in Table 1.2 [19]. Here it shows that wind energy systems can potentially introduce higher PQ problems than the other forms of generation level. Diesel generator goes a superior perform but has highest green house gas emissions.

Table 1.2 PO problems related to DG systems

| PQ Problems        | Wind<br>Energy | Solar<br>Energy | Micro/<br>Small<br>Hydro | Diesel |

|--------------------|----------------|-----------------|--------------------------|--------|

| Voltage Sag/Swell  | •              |                 | •                        | •      |

| Over/Under Voltage | •              |                 |                          | •      |

| Voltage Unbalance  |                | •               |                          |        |

| Voltage Transient  | •              |                 |                          |        |

| Voltage Harmonics  | •              | •               | •                        |        |

| Flicker            | •              | •               |                          | •      |

| Current Harmonics  | •              | •               | •                        |        |

| Interruption       | •              | •               |                          |        |

## 1.1.3 Cost of PQ and mitigation techniques

The impacts of power quality are usually divided into three broad categories: direct, indirect and social. The detail of these impacts has been described in [20]. A recent survey [21] reported PQ costs for EU-25 countries exceeds €150bn where industry accounts for over 90% of this wastage. Dips and short interruptions account for almost 60% of the overall cost to industry and 57% for the total sample. Fig 1.4 shows the PQ costs for the EU-25 countries by sector. At the same time it is necessary to consider the impact of DG in terms of the cost of power quality. In [22], a method to evaluate the dip and interruption costs due to DG into the grid has been proposed.

There are two ways to mitigate the effects of power quality problems - either from the customer side or from the utility side. The first approach is called load conditioning, which ensures that the equipment is less sensitive to power disturbances, allowing operation even under significant voltage distortion. The other solution is to install line conditioning systems that suppress or counteract the power system disturbances. Several devices including flywheels, super-capacitors and other energy storage systems, constant voltage transformers, noise filters, isolation transformers, transient voltage surge suppressors, harmonic filters are used for the mitigation of specific PQ problems. Custom power devices (CPD) such as STATCOM, DVR and UPQC are capable of

mitigating multiple PQ problems associated with utility distribution and end user appliances.

Fig 1.4 Extrapolation of PQ cost to EU economy in LPQI surveyed sectors [21]

## 1.1.4 Custom Power Devices (CPDs)

The Custom Power (CP) concept was first introduced by N.G. Hingorani in 1995 [23]. Custom Power embraces a family of power electronic devices, or a toolbox, which is applicable to distribution systems to provide power quality solutions. This technology has been made possible due to the widespread availability of cost effective high power semiconductor devices such as GTO (gate turn-off thyristor) and IGBT (insulated-gate bipolar transistor), low cost microprocessors or microcontrollers and techniques developed in the area of power electronics.

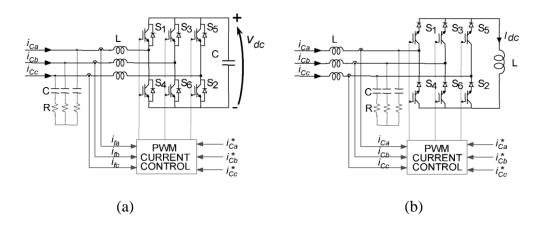

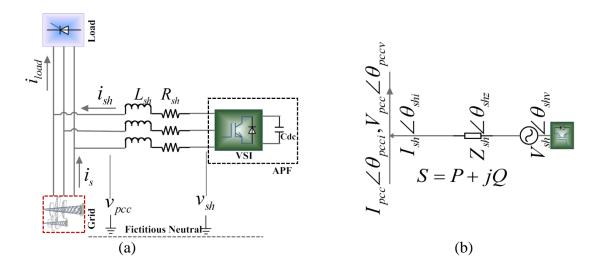

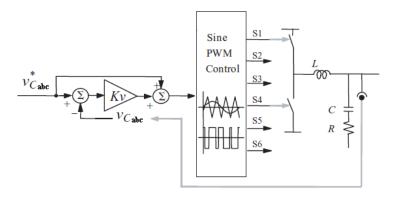

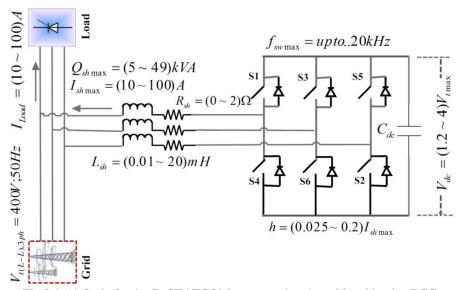

DSTATCOM (Distribution STATCOM) is a shunt-connected custom power device specially designed for power factor correction, current harmonics filtering, and

load balancing. It can also be used for voltage regulation at a distribution bus level [24]. It is often referred to as a shunt or parallel active power filter (APF $_{sh}$ ) and it consists of a voltage or a current source PWM converter, as shown in Fig 1.5(a). It operates as a current controlled, voltage source and compensates current harmonics by injecting the harmonic components generated by the load but phase shifted by 180 degrees.

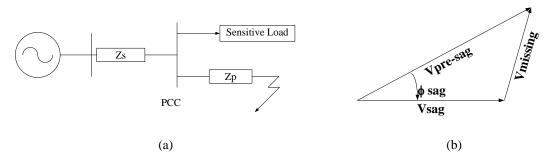

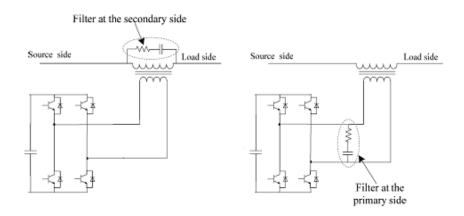

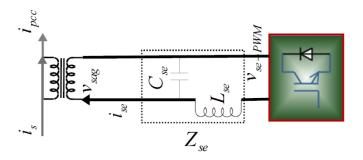

The DVR is a series-connected custom power device to protect sensitive loads from supply side disturbances (except outages). It can also act as a series active power filter (APF<sub>se</sub>), isolating the source from harmonics generated on the load side. It consists of a voltage-source PWM converter equipped with a dc capacitor and connected in series with the utility supply voltage through a low pass filter (LPF) and a coupling transformer [25] as shown in Fig 1.5(b). This device injects a set of controllable ac voltages in series and in synchronism with the distribution feeder voltages such that the load-side voltage is restored to the desired amplitude and waveform, even when the source voltage is unbalanced or distorted.

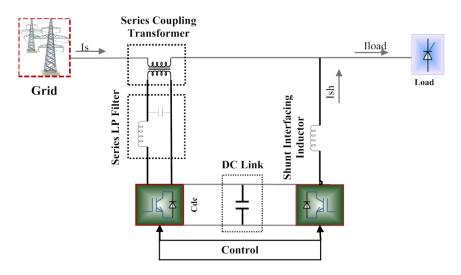

Fig 1.5 System configuration of (a) DSTATCOM and (b) DVR

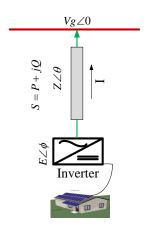

UPQC is the integration of series and shunt active filters, connected back-to-back on the dc side and sharing a common DC capacitor [26] as shown in Fig 1.6. The

series component of the UPQC is responsible for mitigation of the supply side disturbances: voltage sags/swells, flicker, voltage unbalance and harmonics. It inserts voltages so as to maintain the load voltages at a desired level; balanced and distortion free. The shunt component is responsible for mitigating the current quality problems caused by the consumer: poor power factor, load harmonic currents, load unbalance etc. It injects currents in the ac system such that the source currents become balanced sinusoids and in phase with the source voltages.

Fig 1.6 System configuration of UPQC

Recent trends in the power generation and distribution system shows that the penetration level of DG into the grid has increased considerably. End user appliances are becoming more sensitive to power quality conditions. Extensive research on CPDs for the mitigation of PQ problems is also being carried out. CPDs can find significant application in integrating solar and wind energy sources to the grid. They play an important role in the concept of the custom power park in delivering quality power at various levels.

## 1.1.5 Real-time performance study

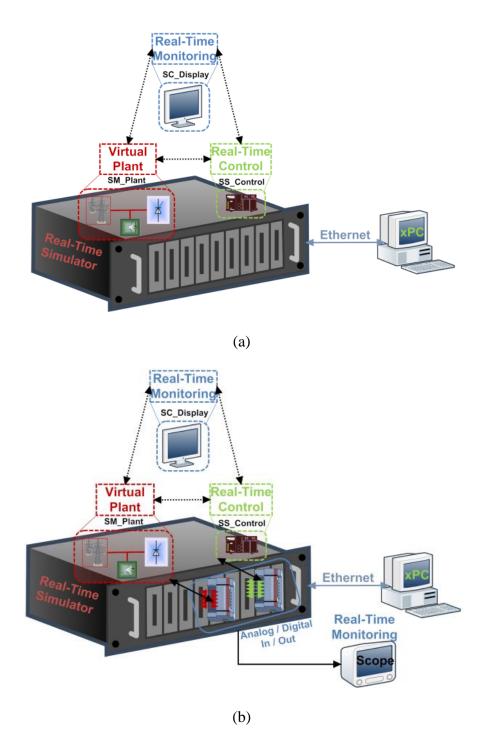

With the advancement of technology, real-time performance of any system can be observed using a real-time simulator. Instead of developing the complete actual system at full capacity, either the controller/system can be modelled in software or can be built in hardware or can be a combination of both. In real-time simulation, the accuracy of the computations depends upon the precise dynamic representation of the system and the processing time to produce the results. In fact, the processing time at a given time-step must be shorter than the real clock time duration. Real-time simulators are typically used in three different application categories [27]:

- (i) Rapid Control Prototype (RCP): Here the controller is implemented using a real-time simulator and is connected to the physical plant.

- (ii) Hardware-in-Loop (HIL): In that case, a physical controller is connected to a virtual plant executed on a real-time simulator, instead of to a physical plant.

- (iii) Software-in-loop (SIL): Here, both the controller and the plant can be simulated in real-time in the same simulator. In that case, the simulator must be more powerful. SIL can also be a combination of RCP and HIL.

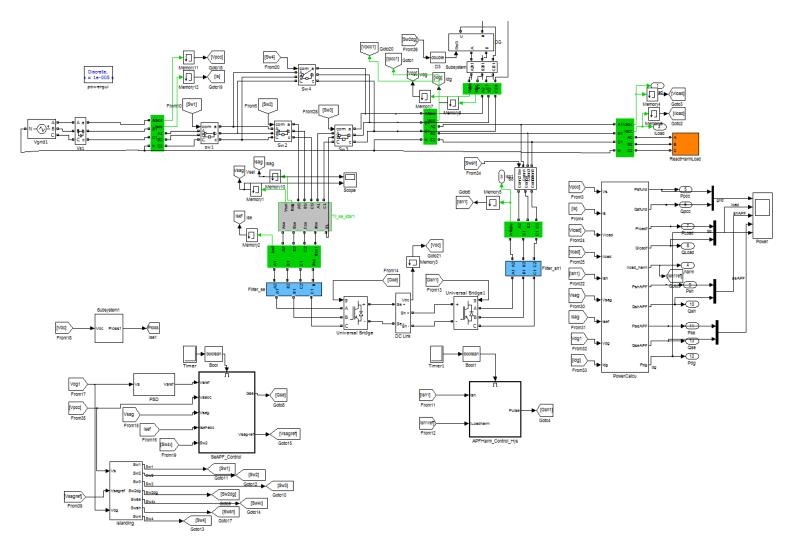

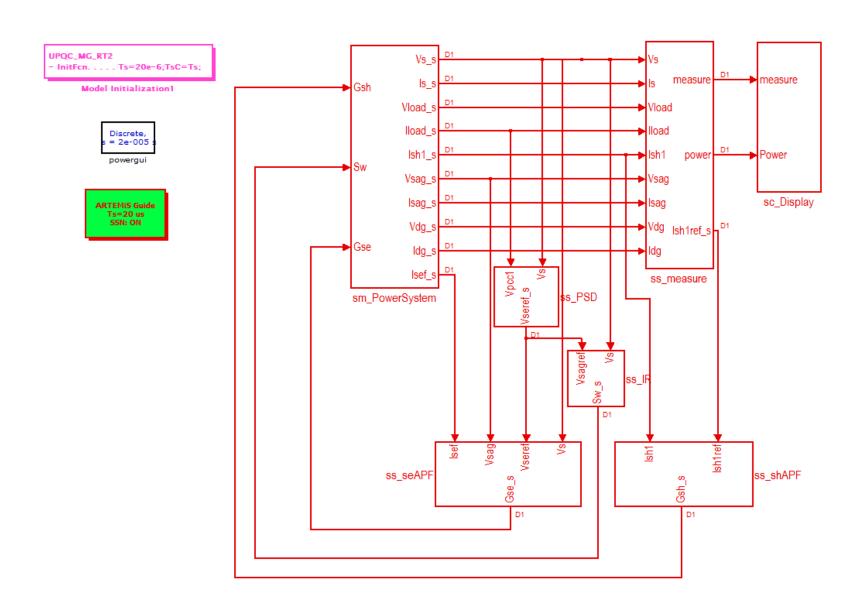

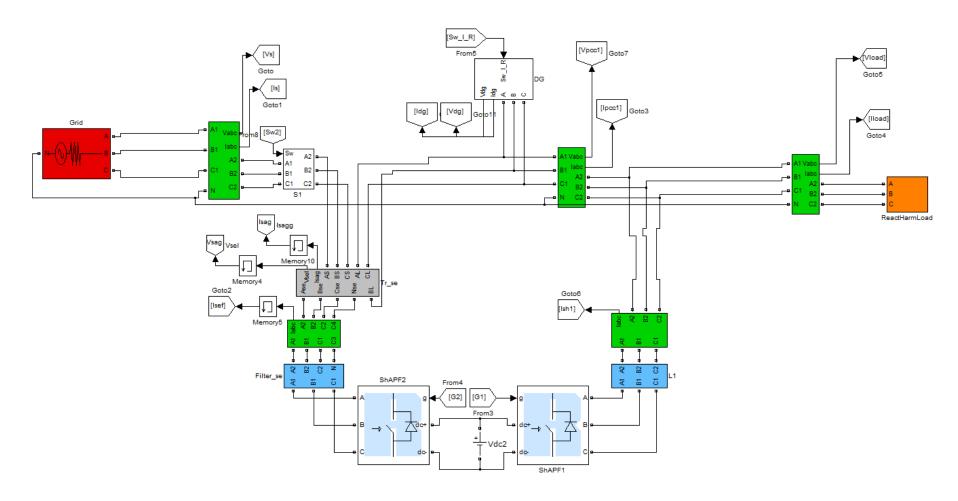

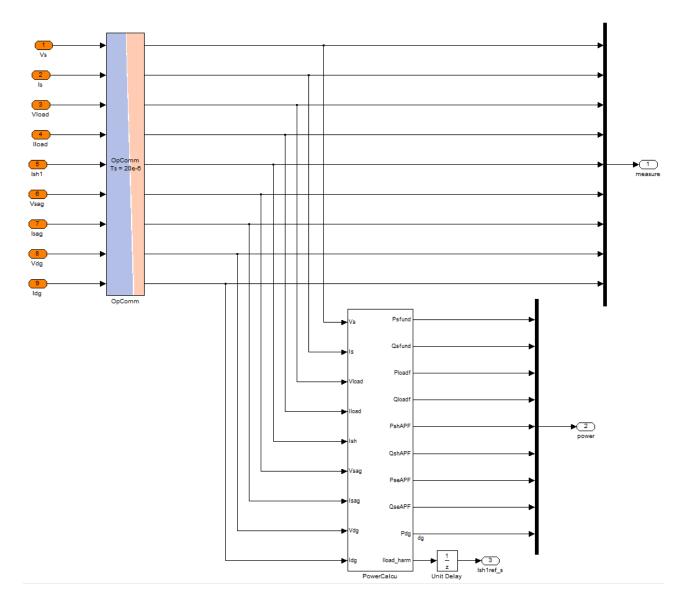

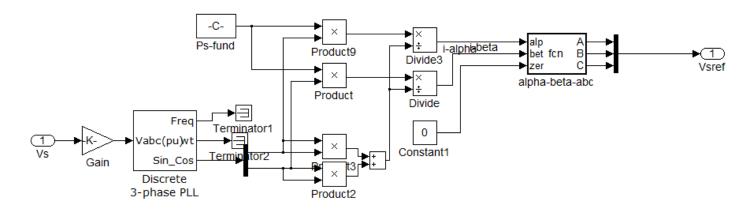

Fig 1.7 shows the real-time simulation structure in a SIL configuration used to develop the real-time environment by OPAL-RT. With the combination of MATLAB SPS (Sim Power System) from MATHWORKS and the RT-LAB toolbox from OPAL-RT, the real-time model of the power system and controller is developed for the real-time simulator. The developed model is then re-arranged to Master (SM\_ ) and Slave (SS\_ ) subsystems to obtain the real performance virtually in Console (SC\_ ), as shown in Fig 1.7(a), or through the real scope, as shown in Fig 1.7(b). The hardware synchronization mode can also be used for RCP/HIL or a combination with SIL.

Fig 1.7 Real-time simulation structure in SIL configuration (a) software synchronization and (b) hardware synchronization mode

## 1.2 Research Objectives

With the increased penetration of small scale renewables in the electrical distribution network, maintaining or improving power quality has become more critical than ever where the level of voltage and current harmonics or disturbances can vary

widely. For this reason, Custom Power Devices (CPDs) such as the Unified Power Quality Conditioner (UPQC) can be the most appropriate solution for the dynamic performances of the distribution network, where prior knowledge of disturbances may not be accurately known.

Therefore, the main objective of the present research is to investigate

- (i) the placement

- (ii) integration

- (iii) capacity enhancement and

- (iv) real time control

of the Unified Power Quality Conditioner (UPQC) to improve the power quality (PQ) of a distributed generation (DG) network connected to the grid or microgrid (μGrid).

# 1.3 Research Contribution

The research work described here to achieve the objectives mentioned in the previous section has led to the following contribution and developments;

- (i) Literature review dealing with the following

- Power quality issues related to DG integrated network

- Design and control of Custom Power Devices (CPDs)

- Application of CPDs in a DG network

- Parallel operation of Inverter and APF

- Placement and Integration of UPQC in the DG network

- Capacity extension of UPQC

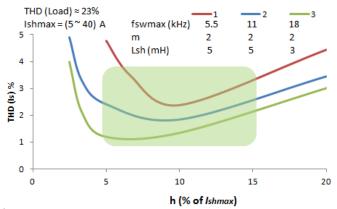

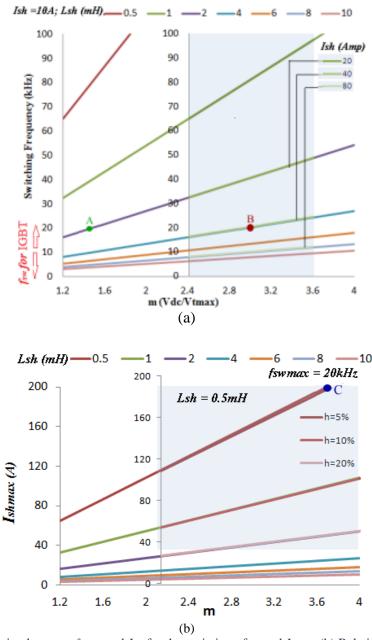

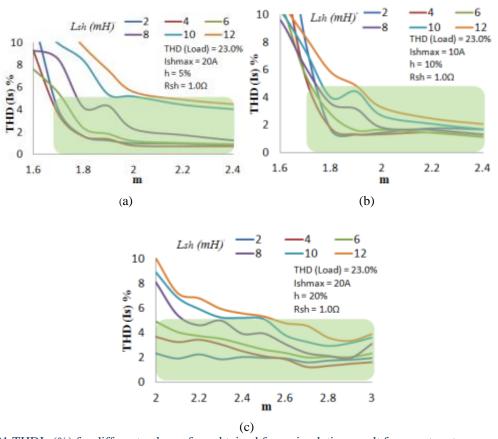

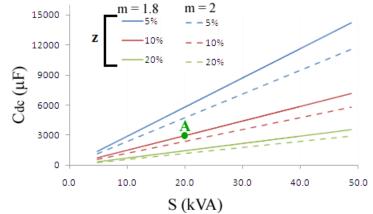

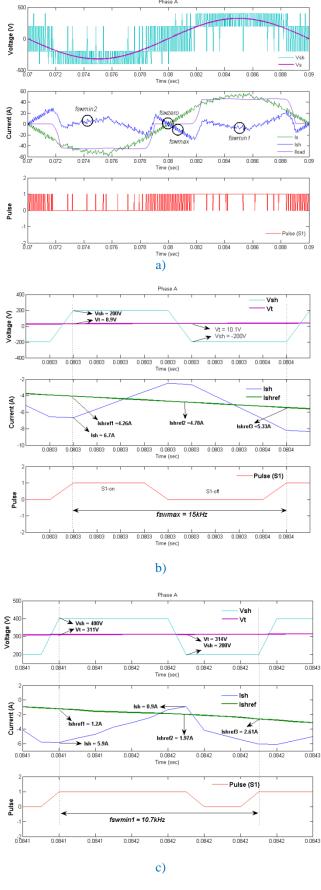

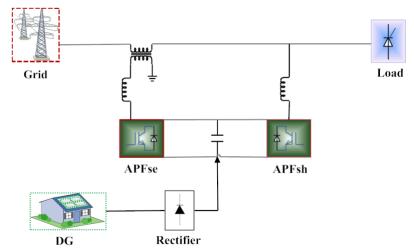

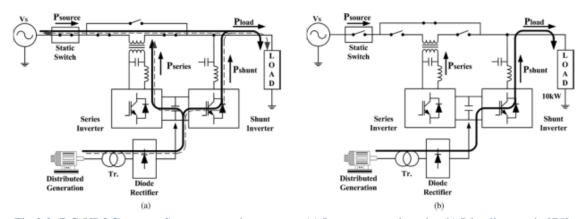

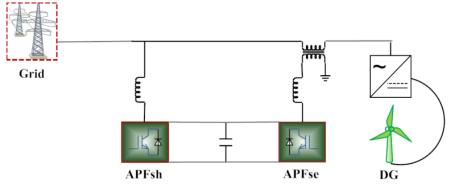

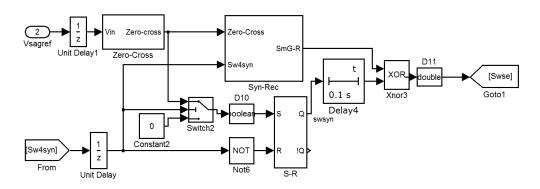

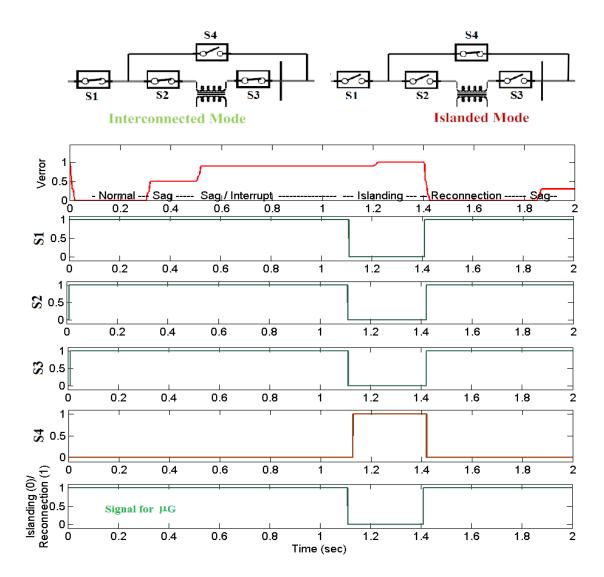

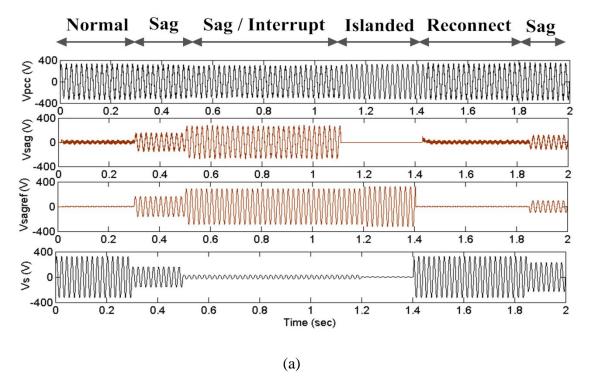

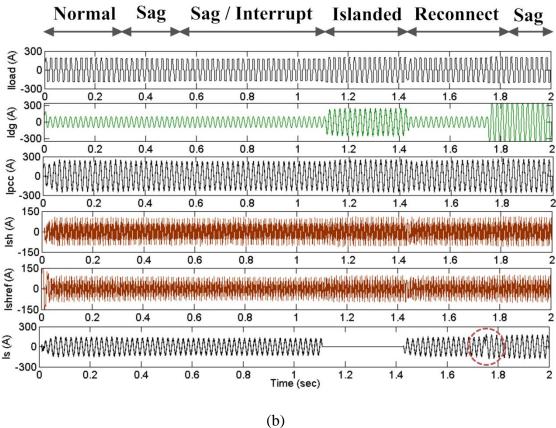

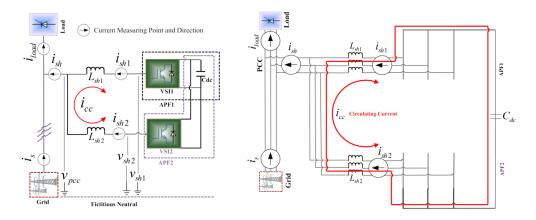

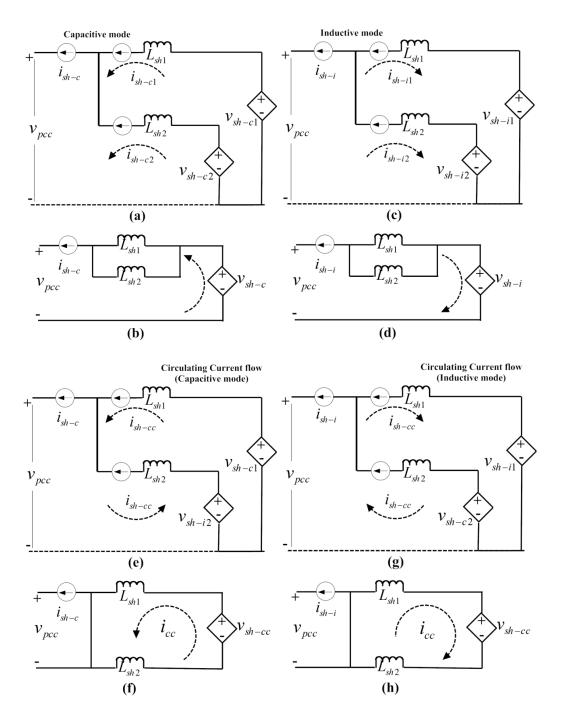

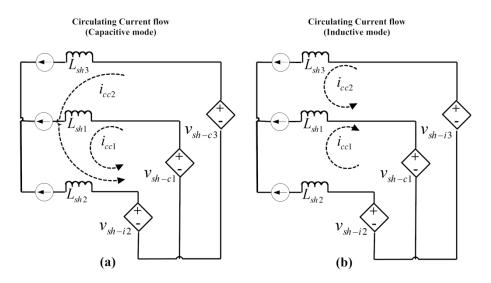

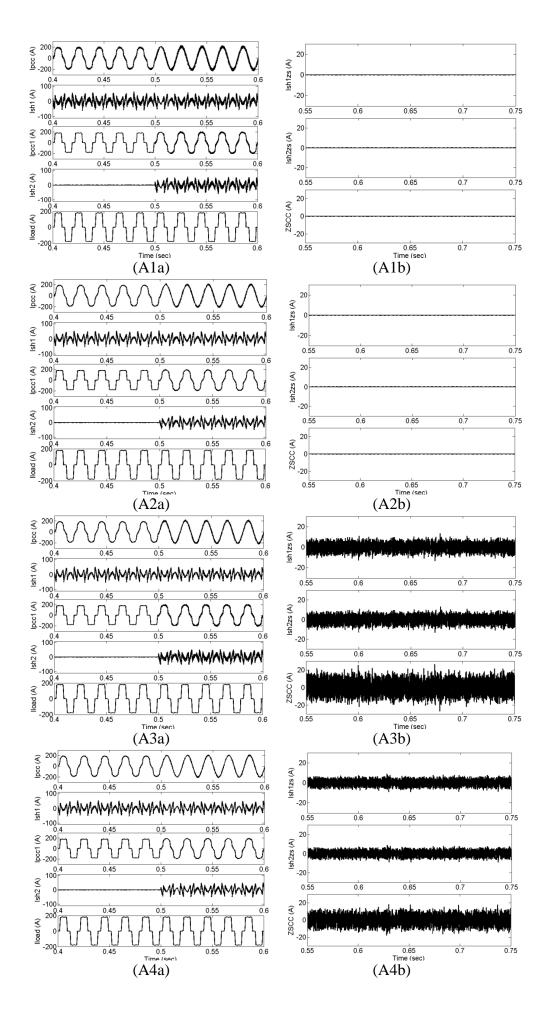

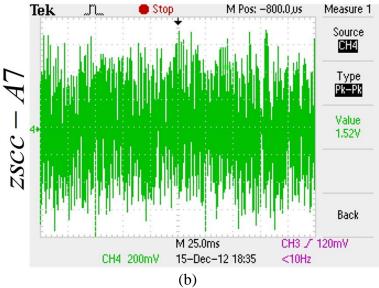

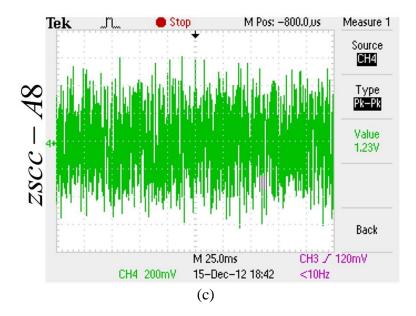

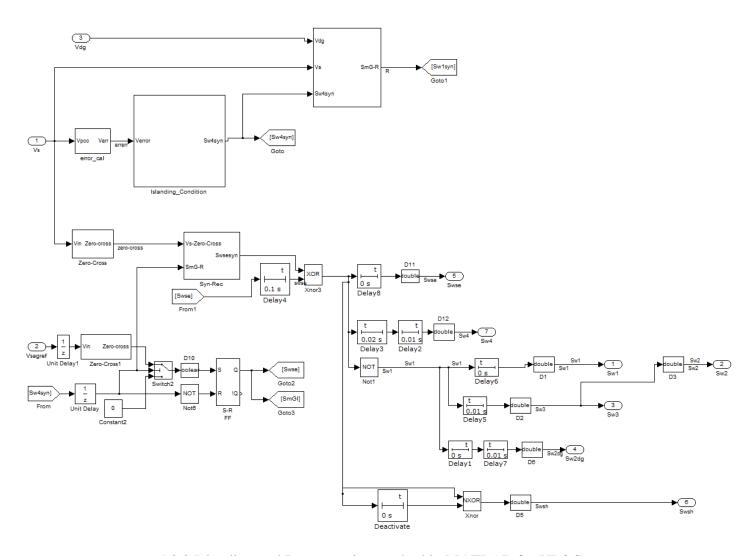

# (ii) Design of D-STATCOM / Shunt APF