## Final Project Report

## Universitat Politecnica de Catalunya

Departament d'Enginyeria Electronica

in cooperation with

## **Technical University of Lodz**

Faculty of Electrical, Electronic, Computer and Control Engineering

# Design of a charge injection compensation system for MEMS electrostatic actuators

by

Kamil Karliński

index nr. 131180

Supervisors:

Daniel Fernández, Ph.D.

Jordi Madrenas, Asoc. Prof.

Barcelona 2010

Yesterday is history.

Tomorrow is a mystery.

And today?

Today is a gift.

That's why we call it the present.

~Babatunde Olatunji

## To my dear parents,

# Moriola and Jan Karlińscy

and my crazy siblings

Mateusz and Kasia

## Acknowledgements

Unconditional thanks goes to my supervisors *Jordi Madrenas* and *Daniel Fernández*. First of all for accepting me as their student. Then for all the highly intelligent conversations along the way through this project. For every heavy step in the creative process of this project. And for patience in answering my question and explaining the basic of electronics sometimes. My courage was always increased after a discussion with my supervisors. These conversations are, without any doubt, the main reason that this project is now completed.

## **Abstract**

The main goal of this project is to implement and experimentally verify various control algorithms for MEMS electrostatic actuators. Those algorithms include a charge injection compensation subsystem.

The hardware platform consists of some MEMS electrostatic actuators, a front-end sensing system (comprising a full-custom mixed-signal integrated circuit designed at UPC and a high-speed A/D converter) and a Xilinx FPGA for algorithm coding.

The work involves the following:

- Understanding the working principle of the hardware platform and the issues related to MEMS electrostatic actuators.

- Improve the hardware platform, if required by the control algorithm. This might involve some simple PCB design and test with laboratory instrumentation.

- Algorithm implementation in VHDL. This includes the signal-processing algorithms and also the ancillary routines for I/O data extraction and signal visualization.

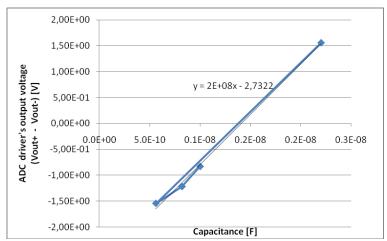

Capacitance of MEMS electrostatic actuators were measured under different voltages conditions. It was found that positive voltage stress caused negative charging of the dielectric whereas negative voltage stress caused positive charging of the dielectric. This is consistent with the nature of traps in the silicon oxynitride dielectric used for the switches.

Report is divided into three parts, the first chapter is devoted to the description to the MEMS word. The chapter is devoted a small multiplexing board design description. And finally chapter 3 introduce a development of a VHDL code to control all system.

## **Contents**

| Α | bstract   |                                                 | ix         |

|---|-----------|-------------------------------------------------|------------|

| C | ontents . |                                                 | xi         |

| 1 | Intro     | duction                                         | 1          |

|   | 1.1       | Overview                                        | 1          |

|   | 1.2       | Actuators: Transducers with Mechanical Output   | 1          |

|   | 1.3       | Theoretical background                          | 2          |

|   | 1.4       | Manufacture process                             | 3          |

|   | 1.5       | Characterization of dielectric charging in MEMS | 4          |

|   | 1.6       | Controlling the charge                          | 5          |

| 2 | Hard      | ware                                            | 7          |

|   | 2.1       | Overview                                        | 7          |

|   | 2.2       | Delirium-I-feael                                | 7          |

|   | 2.2.1     | Jumpers                                         | 10         |

|   | 2.2.2     | Potentiometers                                  | 13         |

|   | 2.2.3     | Connections                                     | 14         |

|   | 2.3       | MEMS actuators board                            | 16         |

|   | 2.4       | Multiplexing board                              | 17         |

|   | 2.4.1     | General description                             | 17         |

|   | 2.4.2     | Operational amplifier                           | 19         |

|   | 2.4.3     | Multiplexers                                    | 22         |

|   | 2.4.4     | Negative voltage calculation                    | <b>2</b> 5 |

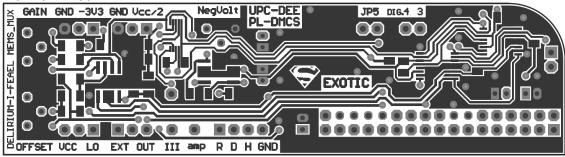

|   | 2.4.5     | Printed circuit boards                          | <b>2</b> 5 |

|   | 2.4.6     | Jumpers                                         | 27         |

| 3 | Algo      | rithm implementation                            | <b>2</b> 9 |

|   | 3.1       | Overview                                        | 29         |

|   | 3.2       | Codes description                               | <b>2</b> 9 |

|   | 3.2.1     | ASM chart                                       | <b>2</b> 9 |

|   | 3.2.2     | Clocks in design                                | 31         |

|   | 3.2.3     | Important instantiates                          | 33         |

|   | 3.2.4     | Averaging as a low-pass filter                  | 35         |

|   | 3.2.5     | State machine description                       | 38         |

|   | 3.2.6     | Do files                                        | 42         |

|   | 3.2.7     | Program – user communication                    | 42         |

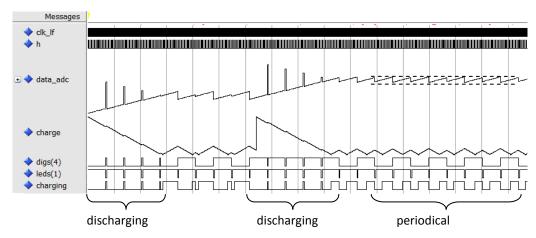

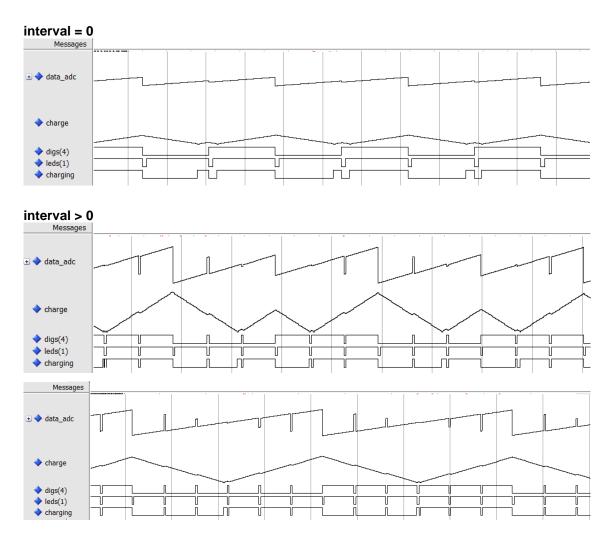

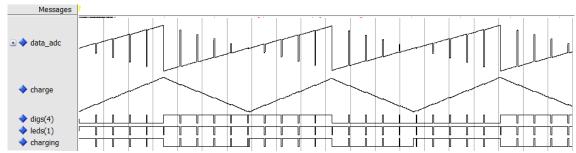

|   | 3.3       | Simulation                                      | 44         |

|   | 3.4       | Measurements                                    | 47         |

| 4 | Conc      | lusion                                          | 51         |

| _ | D:hl:     | a grander                                       | F3         |

| Appendixes                           | 54 |

|--------------------------------------|----|

| A – DELIRIUM-I-FEAEL documentation.  | 54 |

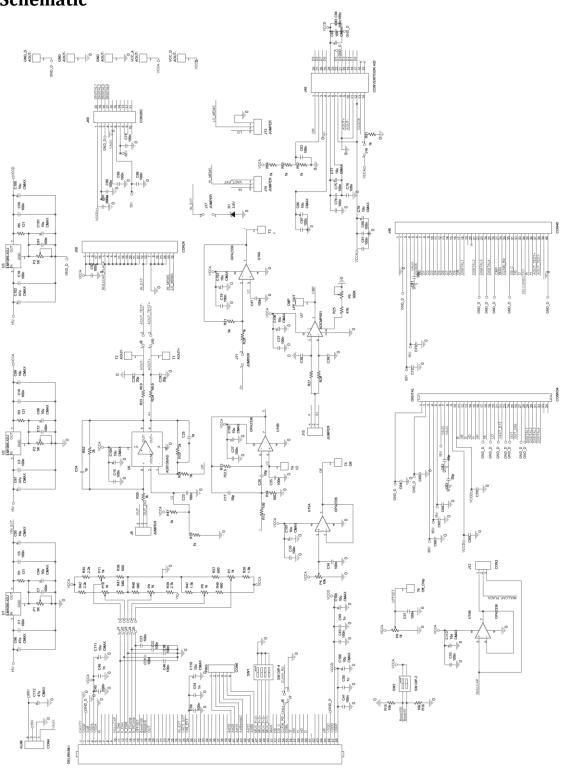

| Schematic                            | 54 |

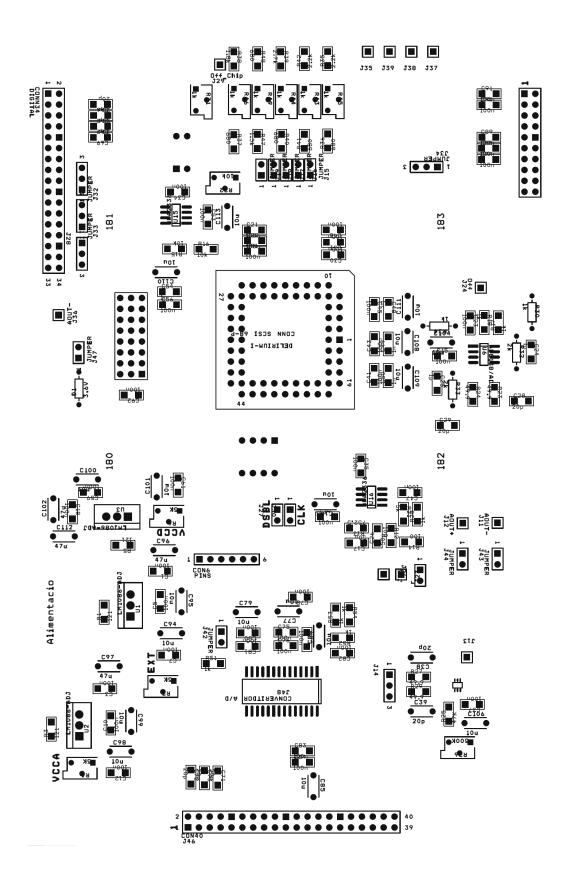

| Reference Design Assembly Drawing    | 55 |

| B – Multiplexing board documentation | 56 |

| Schematic                            | 56 |

| Reference Design Assembly Drawing    | 57 |

| Bills of materials                   | 58 |

| C – A MEMS actuators floor-plan      | 59 |

| D – Source codes                     | 60 |

| MEMS_ChargeInReduce.vhd – top level  | 60 |

| dsp.vhd66                            |    |

| misc.vhd                             | 69 |

| Display.vhd                          | 70 |

| TB_MEMS_ChargeInReduce.vhd           | 72 |

| sim.do 74                            |    |

|                                      |    |

## 1 Introduction

#### 1.1 Overview

In this chapter there will be briefly presented a theoretical background of MEMS electrostatic actuators.

#### 1.2 Actuators: Transducers with Mechanical Output

An actuator is a device that converts energy from one form, such as electrical, mechanical, thermal, magnetic, chemical, and radiation energy, into the mechanical form. [12] (For example, resistive heating elements convert electrical energy into bending of a bimorph microstructure.) In some cases, a microactuator may convert energy into intermediate forms before resulting in the final mechanical output (such as inductively coupled heating elements, which convert electrical energy first into magnetic energy before finally resulting in thermal energy serving to deflect a microelement). Such devices are said to be based on tandem transduction [17].

**Table 1.1 Transduction Methods**

|              | Output signal                   |                                   |  |  |  |  |  |  |

|--------------|---------------------------------|-----------------------------------|--|--|--|--|--|--|

| Input signal | Mechanical                      | Electrical                        |  |  |  |  |  |  |

| Mechanical   | Fluidics, acoustics             | Piezoresistive                    |  |  |  |  |  |  |

| Electrical   | Electrostatics, electromagnetic | Langmuir probe, transformer       |  |  |  |  |  |  |

| Thermal      | Thermal expansion               | Pyroelectric                      |  |  |  |  |  |  |

| Magnetic     | Magnetometer                    | Magnetoresistance                 |  |  |  |  |  |  |

| Chemical     | ChemAbsorber                    | Ionization, ChemFET, ChemResistor |  |  |  |  |  |  |

Electrical microactuators are by far the most common and diverse type of microactuator. This is primarily because of the ease with which most electrical microactuators can be produced using conventional microfabrication processes and materials. Examples of electric microactuators include static, resonant, rotary, and stepper-motor configurations. Electrical microactuators can be driven by an electrical-to-mechanical conversion that makes use either of the direct electrostatic forces between charged objects or a piezoelectric material that can mediate the

energy transformation. Electrostatic and piezoelectric transduction mechanisms, the physical relationships involved, the material properties that govern their operation.

#### 1.3 Theoretical background

Electrostatic forces are commonly observed even on the macroscale during everyday activities, such as combing dry hair or drying clothes. The discovery of elemental charge and the concept of electric fields have led to an understanding of electrostatic energy and the forces acting between objects charged to a different extent.[1]

In the literature there are a lot of equations which allow to calculate a magnetic fields, and forces between plate as well [6] [12]. All of them base on well know Gauss's and Maxwell's laws. Important thing in the actuators analysis is amount of energy that is require to charge a plate and move them in any other position. Because in the project there will be only consider the effect of charge injection into between plate space, only derivation of accumulated charge will be given.

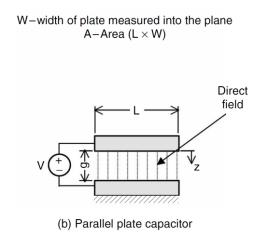

Figure 1.1: Generic electrostatic actuator

The capacitance of the generic structure shown in Figure 1.1 is given by:

$$C = \frac{\varepsilon_r \varepsilon_0 A}{g} \tag{1.1}$$

where

$\varepsilon$  = permittivity of material between the parallel plates (free space permittivity 8.85 · 10<sup>-12</sup> F/M)

A = plate area

g = gap between the plate

For a variable parallel plate capacitor, the movable plate moves normally to the fixed plate as defined by the coordinate, z. The capacitance for the movable capacitor is

$$C = \frac{\varepsilon_r \varepsilon_0 A}{g - z} \tag{1.2}$$

The charge Q on each plate is proportional to the capacitance C and the voltage V:

$$Q = CV ag{1.3}$$

The equations are given only as to preview, and remind basics, next section focus on manufacture process [15].

#### 1.4 Manufacture process

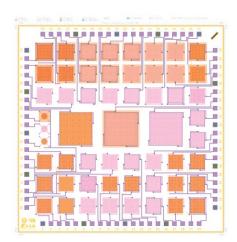

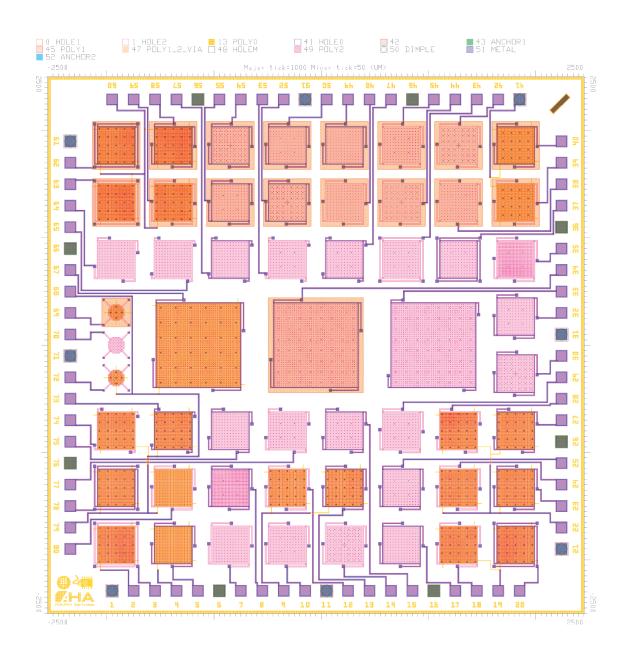

Despite the attractive performance characteristics of MEMS actuators, their commercialization is difficult because of a number of factors such as reliability and packaging cost. In particular, there can be affected by dielectric charging effects such as control-voltage drift and stiction [10]. The dielectric is typically silicon dioxide or nitride formed by plasma-enhanced chemical vapor deposition (PECVD) with a high density (~10<sup>18</sup>/cm<sub>3</sub>) of traps associated with silicon dangling bonds [11]. The board contain a MEMS electrostatic actuator which is depicture in the Figure 1.2 (and in Appendix C – A MEMS actuators floor-plan.) was next manufactured in the Multi-User MEMS Processes, or MUMPs [9]. The main purpose of this board it to provide a lot of MEMS actuators with different capacitance and dynamic characteristic.

Figure 1.2: MEMS actuator chip layout.

The MUMPs process is a commercial program that provides cost-effective, proof-of concept MEMS fabrication to industry, universities, and government worldwide. MEMSCAP offers three

standard processes as part of the MUMPs program: PolyMUMPs, a three-layer polysilicon surface micromachining process: MetalMUMPs, an electroplated nickel process; and SOIMUMPS, a silicon-on insulator micromachining process.

The PolyMUMPs process is a three-layer polysilicon surface micromachining process derived from work performed at the Berkeley Sensors and Actuators Center (BSAC) at the University of California in the late 80's and early 90's. Several modifications and enhancements have been made to increase the flexibility and versatility of the process for the multi-user environment.

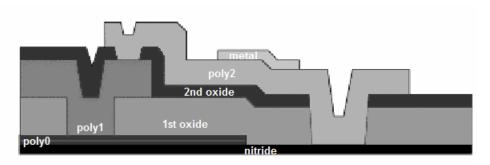

Figure 1.3: PolyMUMPs process cross section

Figure 1.3 is a cross section of the three-layer polysilicon surface micromachining PolyMUMPs process. This process has the general features of a standard surface micromachining process: (1) polysilicon is used as the structural material, (2) deposited oxide (PSG) is used as the sacrificial layer, and silicon nitride is used as electrical isolation between the polysilicon and the substrate [9]. The MEMS board was manufactured in PolyMUMPs technological process.

Knowing basic of manufactures process it is time to explain how the MEMS actuators are built.

## 1.5 Characterization of dielectric charging in MEMS

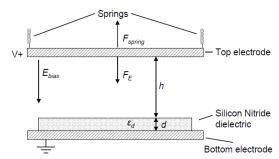

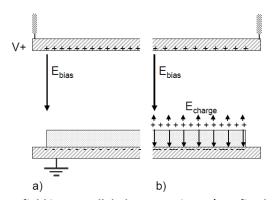

Figure 1.4 shows a schematic representation of an MEMS. The switch consists of two electrodes, of which the top electrode is suspended by tiny springs. The top electrode can be pulled down by applying a voltage across the air gap between the two electrodes. Above a certain voltage, the balance between the attracting electrostatic force and restoring spring force becomes unstable and the switch closes.

Figure 1.4: Schematic representation of an MEMS

The top electrode of a parallel plate capacitor can be pulled down by applying a voltage greater than the pull-in voltage, which is pulled up again by the springs if the voltage is lowered beneath the pull-out voltage.[10]

Figure 1.5 shows how charges are trapped into the MEMS structure.

Figure 1.5: E-field in a parallel plate capacitor. a) No fixed charges in the dielectric. b) Fixed surface charge at height z = d.

The traps are amphoteric [10] so they can be either positively or negatively charged. During switch operation, the electric field across the dielectric can be of the order of 10<sub>6</sub> V/cm causing electrons or holes to be injected into the dielectric and become trapped. With repeated operation, charge gradually builds up in the dielectric resulting in control-voltage drift or stiction.

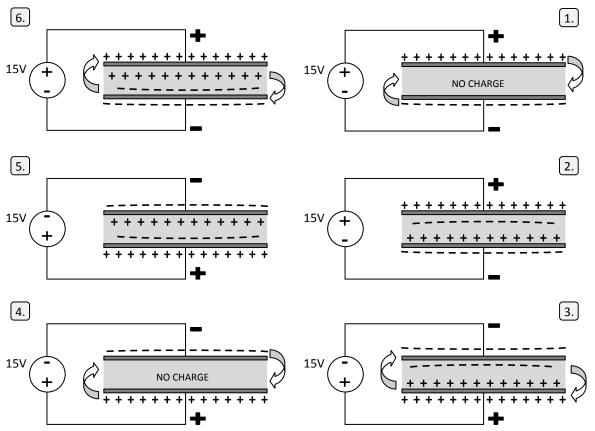

### 1.6 Controlling the charge

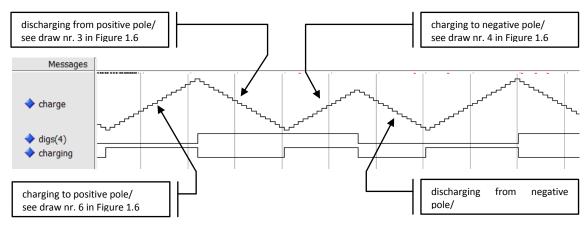

A graph in Figure 1.6 presents how charge is controlled by external source. At the beginning, after turn ON a power supply, there is no any loads inside. Loads pass through the electrode and nested in the space between the plates during the time. This process is very slow and depends on MEMS actuator. Some of them doesn't have such a strong injection. After changing a sequence, which means reverse a divider supply polarity, charge from previous mode is compensated at

first. When actuator is totally discharge, the reverse polarity charging process begin. The list below and figures describe this process more clear from the beginning.

- 1. after power supply turn ON (t = 0).

- 2. after short while working in sequence I.

- 3. while after changing a sequence

- $\left\{ egin{array}{ll} 4. \\ 5. \end{array} \right\}$  presently reside in the sequence II

- 6. while after changing a sequence again to I

Figure 1.6: The charge injection effect

Presented train of thoughts in this section (power supply changes - as charge compensation) was carried out by multiplexers - as part of a executive hardware and state machine as system controlling part. The following chapter describe the first one.

## 2 Hardware

#### 2.1 Overview

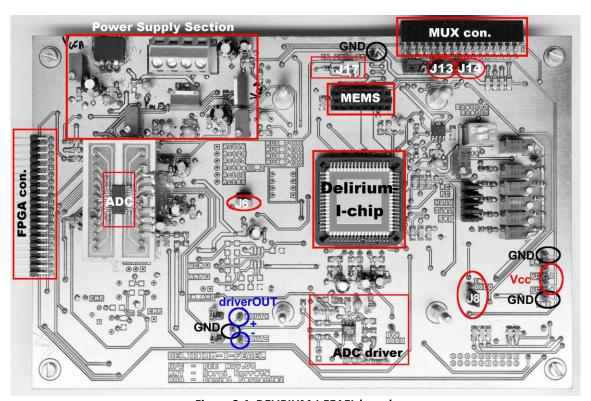

This chapter presents a hardware part of project. Here will be description of boards which were used to test a MEMS chip, and explanation how they were designed. In this chapter there will be shown how to get started with each boards and how to properly configure them. Whole project consist of three printed circuit boards and one Xilinx Spartan-3 Starter Kit [19].

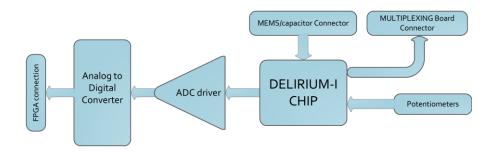

#### 2.2 Delirium-I-feael

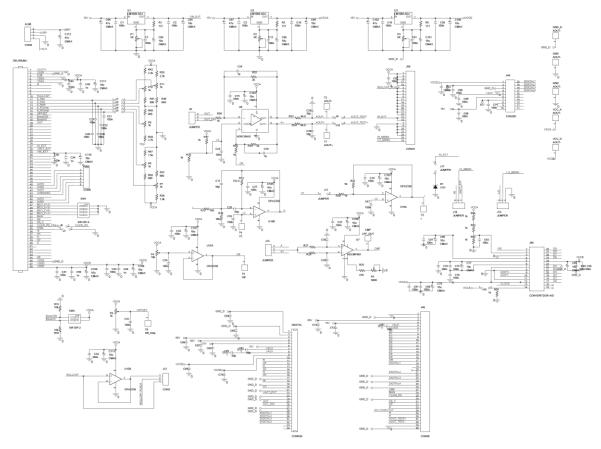

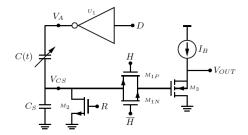

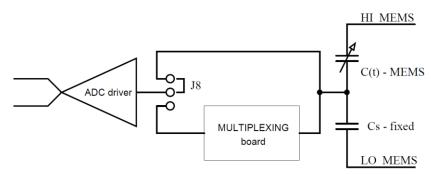

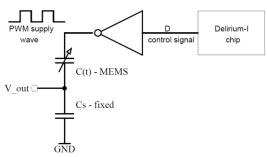

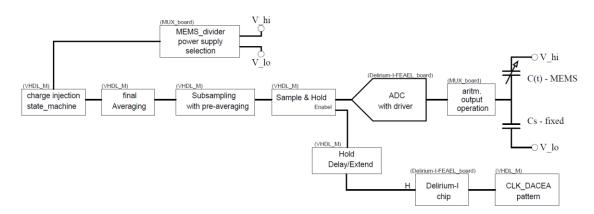

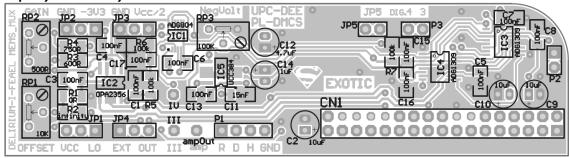

The board was designed by Sergi Gorreta under Daniel Fernandez supervision. It contain a main integrated circuit responsible for generate appropriate signals for measuring the actuator capacitance. The board provides three voltage regulators separated for each power supply, analog to digital converter with differential driver and a big amount of jumpers and potentiometers for tuning and mode selection. Figure 2.1 shows a simple functional block diagram, but the Figure 2.2 their schematic.

Figure 2.1: Simple functional block diagram

Figure 2.2 Delirium-I-FEAEL schematic

Briefly explaining the operation of this board, it should be noted that its heart is the Delirium-I chip, responsible for generating a H, D, and R control signals. The functional diagram of this chip is depictured in the Figure 2.3.

Figure 2.3 Simplified schematic of Delirium-I chip.

The circuit is better understood by analyzing the running sequence of the digital control signals D, R and H. This sequence can be summarized as follows [7]:

o In normal operation, signals D, R and H are equal to 0. In this mode, a high voltage is applied to theupper node of the actuator though the  $U_1$  inverter, the switch  $M_2$  is turned off and the transmission gate  $M_1$  is turned on. Thereby, the output voltage  $V_{\text{OUT}}$  tracks  $V_{\text{CS}}$  by means of the PMOS voltage follower  $M_3$ .

- When a reset is required, the signal H is set to logic 1 (and H to 0). This disconnects the transmission gate M1 so the output voltage VOUT is hold constant regardless of VCS.

- Then, signal R is set to 1, discharging the serial capacitor Cs.

- Next, signal D is set to 1, discharging the electrostatic actuator.

- After both capacitances have been discharged, R is set back to 0 and the capacitances can be charged again.

- o Finally signal D is set back to 0, charging the capacitive divider and, after a short time, signal H is set also to zero, enabling the transmission gate, so the output voltage tracks again Vcs and the sequence is repeated.

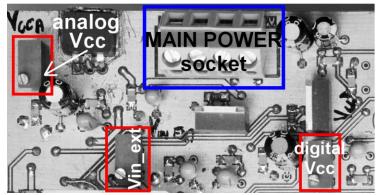

Figure 2.3 shows  $V_{\text{OUT}}$  voltage which provide the current MEMS actuator capacitance. This information is pass through to fully differential amplifier, where it is filtrated and a little bit gained. Then it land in high speed analog to digital converter, and in digital way goes to FPGA circuit, where it is subjected final signal processing. There is also feedback in this circuit, after analyzing it, the FPGA could impact on system operation. This device have control of main chip, and divide supply duty cycle. Figure 2.4 shows the layout of main board and next few section describe their proper configuration, started with jumper.

Figure 2.4: DELIRIUM-I-FEAEL board.

#### **2.2.1 Jumpers**

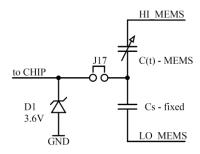

The most important jumper in this circuit is J17, the main objective of it is to prevent the burning of chip. It connects 3.6V Zener diode to a middle node of MEMS system, as depicted in Figure 2.5. That jumper should always be in place during making changes in the fixed capacitor or actuator. Single glitches or short overvoltages, can occur and cause chip damage.

#### **WARNING**

Before making ANY changes with capacitance divider make sure that jumper is closed and power supply is off. After work, also leave the jumper in that position.

Figure 2.5: Jumper J17 application

Jumper J13 and J14 are used for voltage selection for supply a capacitive divider made up of fixed capacitor and MEMS actuator. All possibilities that can be chosen with the help of this jumper are shown in Table 2.1.

| Option       | Jumper J13<br>Setting | Jumper J14<br>Setting | Description                                                                                                                                                        |

|--------------|-----------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |                       |                       | Dependent on selected mode:                                                                                                                                        |

|              |                       |                       | MODE I (positive)                                                                                                                                                  |

|              |                       |                       | +15V                                                                                                                                                               |

| High voltage | ×                     | ×                     | MODE_II (negative)                                                                                                                                                 |

|              |                       |                       | HI_MEMS -11.7V  3.3V LO_MEMS 0v                                                                                                                                    |

|              |                       |                       | Irrespective of selected mode:                                                                                                                                     |

| Low voltage  | ×                     | ×                     | HI_MEMS 0v LO_MEMS always grounded.                                                                                                                                |

|              |                       |                       | This configuration may cause a damage to                                                                                                                           |

| DAMAGE       | ×                     | ×                     | Delirium-I chip in mode_II. The chip is able to work only from 0 to 3.3V voltage range.  In mode_II middle point of capacitive divider provide a negative voltage. |

| 0V_out       | ×                     | ×                     | In this configuration a capacitive divider out is always equal to ground.                                                                                          |

Table 2.1: Capacitive divider voltage configuration

In the Table 2.1 there is one configuration with can cause a damage to circuit. It is because Delirium-I chip was designed to work only with positive voltage. In this case there is a possibility when HI\_MEMS is active with -11.7V, LO\_MEMS is grounded and middle point of divider goes into negative voltage.

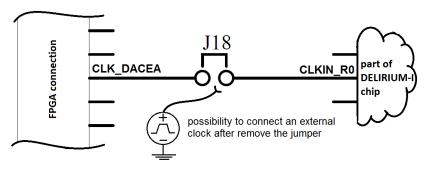

Another jumper in that circuit is marked as J6. It can be used to disconnect Delirium chip's main clock. It is also possible to connect an external clock as showed in the picture.

Figure 2.6: Jumper J18 application.

J8 is a jumper which allow you to chose a correct path output signal from capacitive divider as explained in the Figure 2.7 and Table 2.2.

Figure 2.7: Jumper J8 application.

| Option      | Jumper J8<br>Setting | Description                                                                                                                |

|-------------|----------------------|----------------------------------------------------------------------------------------------------------------------------|

| MEMS_direct | ×                    | This position is used to connect the middle point of divider directly to ADC driver for further processing.                |

| MUX_board   | ×                    | The middle point of divider is led to multiplexing board where a few simple operations are performed depending on the mode |

Table 2.2: J8 configuration

At the beginning of the work the jumper was set only in MEMS\_direct position.

On the right side of this board there are still other jumpers available. By the means of them one can disconnect some potentiometers or measure appropriate current. When the board stops working without no reason it is a good idea to check the currents in the jumpers. Ranges of an allowed currents are gathered in the end of the next section.

#### 2.2.2 Potentiometers

The board provide a several potentiometer to set appropriate value e.g. in the power section there are a possibilities to adjust a power supply voltage. Figure 2.8 shows which power voltage can be set by each potentiometer.

Figure 2.8: Power section description.

|                          |        |        |     |                 | a part of board scheme     |

|--------------------------|--------|--------|-----|-----------------|----------------------------|

| PIN no.                  | 1      | 2      | 3   | 4               | ALIM.                      |

| On board description     | AUX    | GND    | 15V | 60V             | 3 015V<br>2 17 47u<br>CMAX |

| Recommend voltage supply | -11.7V | ground | 15V | NC <sup>1</sup> | CON4 VAUX = 0              |

Table 2.3: Main power connection/socket pin configuration.

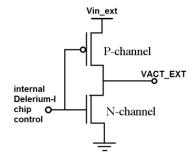

In power supply section a simple National Semiconductor positive voltage regulators are used. Leading feature is a low dropout voltage, a maximum of 1.5V at 1.5A of load current. The circuit marked as LM1086 is available in an adjustable version, which can set the output voltage with only two external resistors included by described potentiometer. A simple application circuit can be founded in datasheet. A good habit is to separate analog and digital power supply. For that

reason the board provide two different voltage regulators, moreover there is another one. This one is used to supply half-bridge PWN generator depicted in Figure 2.9. The signal VACT\_EXT is led to HI\_MEMS pin while – Low voltage – configuration is selected, look in Table 2.1.

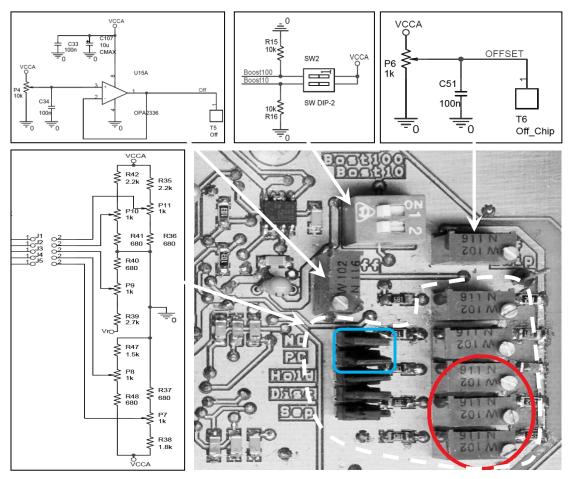

Figure 2.10 depicts a general purpose of the right side potentiometers. The most important of them are located at the

Figure 2.9: PWM half-bridge

<sup>1</sup> NC = NO CONNECT

bottom in row. They are responsible for setting a active width time in H, D, and R signal, what was explained in Introduction.

Figure 2.10: Right side potentiometer application

The Figure 2.10 shows a part of scheme containing a suitable potentiometer. The most important resistors are marked in an ellipse in the figure above. First one from the top provide a duty cycle adjustment in H signal, the middle one is used to set the same property but in D signal, and the last one in R signal. The main purpose of remaining jumpers is to measure and adjust a current. It is important to check it if something happened with the circuit. Two jumpers marked square should conduct current between 50 and  $60\mu A$ , through remaining three current flow should be close to  $2 \mu A$ . Adjusting a current is made by appropriate potentiometer.

#### 2.2.3 Connections

In prototype and research department a fundamental PCB design criterion is to create a easy reconfigurable board. For that reason designing process was not focused on size but on future

usefulness. Several connections, jumpers, ports repeaters and probe pins were placed. This subsection focus on the connectors and theirs pin configuration.

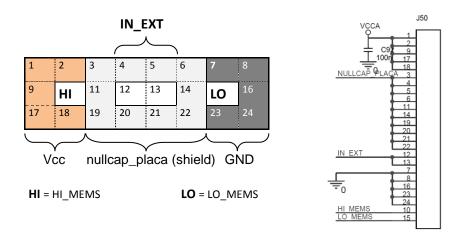

Description start from the female socket marked MEMS in Figure 2.4. It is used to connect a MEMS actuators system or two fixed capacitors. The work with this project began from second option. The Figure 2.11 shows pin signals and part of the scheme containing this component.

Figure 2.11: Pin used on the MEMS connector (CON24)

Another important female connector is used to connect a multiplexing board. It is located on the right side at the top. The multiplexing board will be presented in details in next section. Figure 2.10 presents a pinouts of that connector. There are two abbreviation: V\_ext<sup>[22]</sup> = VACT\_EXT (PWM wave generated from chip) and O\_d<sup>[26]</sup> = OUT\_dig – output from capacitance divider after simple arithmetic operation. OUT<sup>[25]</sup> is output directly from divider. Vaux<sup>[7,8]</sup> a negative voltage supply that goes from main power socket depicted in figure 2.5. Vccd<sup>[9,10]</sup> and Vcca<sup>[34]</sup> are respectively 3.3V digital and analog power supply, as GND<sup>[...]</sup> and GNDA<sup>[33]</sup> are digital and analog ground. R<sup>[11]</sup>, D<sup>[13]</sup> and H<sup>[15]</sup> are MEMS system control signals and nR<sup>[12]</sup>, nD<sup>[14]</sup>, nH<sup>[16]</sup> are theirs negation. There are also multiplexer control signals marked as Dig1<sup>[29]</sup>..Dig4<sup>[32]</sup>.

| 2<br>GND | <sup>4</sup><br>60V | 6<br>15V | 8<br>Vaux | 10<br>Vccd | nR      | nD      | 16<br>nH | 18<br>HI  | LO        |     | <sup>24</sup><br>GND | <sup>26</sup><br>O_d | 28<br>GND | 30<br>Dig2            | Dig4 | Vcca       |

|----------|---------------------|----------|-----------|------------|---------|---------|----------|-----------|-----------|-----|----------------------|----------------------|-----------|-----------------------|------|------------|

| 1<br>GND | 3<br>60V            | 5<br>15V | 7<br>Vaux | 9<br>Vccd  | 11<br>R | 13<br>D | 15<br>H  | 17<br>GND | 19<br>GND | GND | 23<br>GND            | <sup>25</sup><br>OUT | 27<br>GND | <sup>29</sup><br>Dig1 |      | 33<br>GNDA |

Figure 2.12: Pin used in the multiplexing board (CONN34)

The last connector is located at the right edge. It gives a possibility to control the whole system by Xilinx FPGA board. Figure 2.13 presents a pin signals, but only previously not mentioned will be discussed. As before there are a few abbreviations:  $NC^{[19,34]} = no$  connect,  $Cadc^{[6]} = CLOCK$  on main scheme and represents a high speed clock connected to analog-digital converter,  $Cchip = CLKIN_R0$  on main scheme that represents a clock connected to Delirium-I chip with possibility to

adjust the duty cycle to control and measure the MEMS capacitance. The D0<sup>[7]</sup>..D9<sup>[16]</sup> and OR signals come from ADC and are respectively data output bits and out-of-range indicator. AOUT+ and AOUT- are available as output from differential ADC driver, but only after placing the jumpers near to this area.

| 2 | SND | 4<br>15V | 6<br>Cadc | 8<br>D1 | 10<br>D3 | 12<br>D5 | 14<br>D7 | 16<br>D9 | 18<br>Dig1 |    | GND  | GND  | 26<br>GND | 28<br>MAN | 30<br>GND | 32<br>H0 | 34<br>NC | 36<br>H | 38<br>AOUT+ | 40<br>GND |

|---|-----|----------|-----------|---------|----------|----------|----------|----------|------------|----|------|------|-----------|-----------|-----------|----------|----------|---------|-------------|-----------|

| 1 | NDA | 3        | 5         | 7       | 9        | 11       | 13       | 15       | 17         | 19 | 21   | 23   | 25        | 27        | 29        | 31       | 33       | 35      | 37          | 39        |

| G |     | 60V      | Vaux      | D0      | D2       | D4       | D6       | D8       | OR         | NC | Dig2 | Dig3 | Dig4      | CMP       | Cchip     | D0_C     | D        | R       | AOUT-       | GNDA      |

Figure 2.13: Pin used in the FGGA board (CON40)

There is one more connector for ADC but it is not necessary to describe it in details except of indicating where a first pin of ADC should go that is on the right side at the bottom.

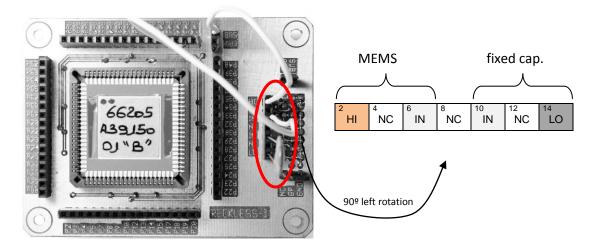

#### 2.3 MEMS actuators board

At this time is worth to mention about another small board which contains only a MEMS socket and few other connectors that allow to select an actuator and insert a fixed capacitor. On that board there are a lot of descriptors to facilitate a work with it, so here not all of them will be explained, only the most important. The board is presented in Figure 2.14, in the same figure the capacitor connector is depicted.

Figure 2.14: MEMS electrostatic actuators board with capacitor connector pin-outs

In this board there is a jumper between CAV and SUB signals, which are respectively the cavity of the chip and the substrate of the MEMS. CAV and SUB should be shorted. Other jumper, "NC" - "GP" - "GND", this is for selecting at which potential the ground plane (GP) should be, if it is connected to nullcap (NC) or directly to ground (GND), during measurements the GP signal should be grounded.

The best way to obtain a good performance with actuator movable plate is to connect signal marked as HI to SUB or CAV and IN signal to ones of pins located around the chip. The MEMS actuators board floor-plane is shown in the Figure 1.2. It can be seen that some of actuators have two and some of them just one available connection. The principle gave at the beginning of this paragraph concerns the second one, with only one lead called anchor. This connection have the same thickness through the entire length.

There is possibility to work with two-leads MEMS but configuration is different and deflection smaller. In this case it is necessary to combine HI signal to POLYO. In tested MEMS board this layers are affixed to paths which are shared with other actuators. This path is also thinner near actuator connection. As an example the pins number in MEMS floor-plan are given: 2, 4, 9, 19, 22, 60, 79 and so on. The second lead (anchor – similar to one-lead actuators) should be connect to IN signal. The 1.4 section presents how MEMS has been constructed, and where exactly POLYO layer is.

Before describing how to choose an adequate fixed capacitor, it is important to mention about turning off a power supply.

#### **WARNING**

Another, faster prevention from burning the MEMS chip is to unplug a power supply.

To see a significant actuator plate movement it is important to choose appropriate fixed capacitor. The best way is to start doing this at 56pF. The fixed capacitor value strongly depend on MEMS capacitance and manufacture process, so the safest way is to start with the large one. After fastening it in a correct socket a chip clock's (not ADC clock) duty cycle should be set to 90%. The next important thing is to not turning on the power supply rapidly but increasing it slowly and observing at the same time ADC driver's differential output. The differential outputs from ADC driver should be approximately equal with properly matched capacitor and 15V power supply.

#### 2.4 Multiplexing board

#### 2.4.1 General description

This part has been completely designed by author of this thesis, of course, after consultation with coordinator. The main purpose is to generate a control PWM waveform in two different voltage

level combinations. The Introduction chapter presents how change a actuator capacitance with duty cycle and why the change of a voltage polarity is necessary.

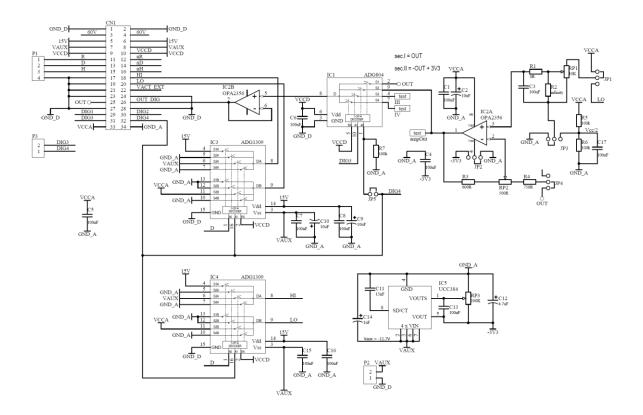

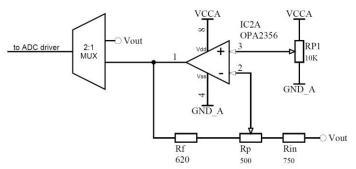

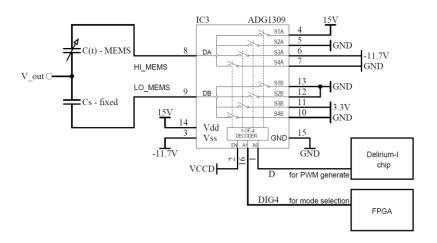

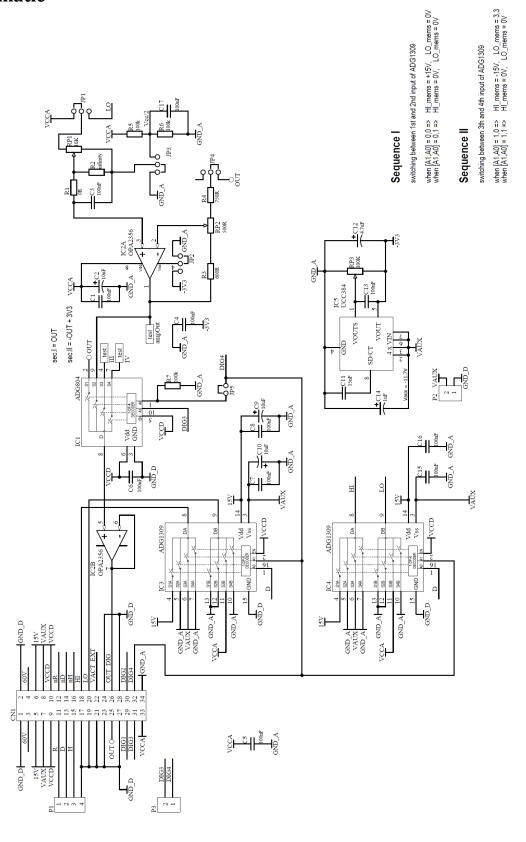

The appendix B – Multiplexing board documentation presents a full user's guide of this board. In this section only a functional part and configuration will be describe. The schematic of this board is presented in Figure 2.15.

Figure 2.15: Multiplexing board's scheme

Through the CN1 connection this board communicate with the rest of system. Among another thing there are two multiplexers to change the capacitive divider supply voltage, and one to choose a divider's output signal path. This path could pass directly through multiplexer or firstly through inverting amplifier and then multiplexer. The output of this multiplexer is connected to voltage follower to match the impedance for both paths. There is negative voltage regulator as well, to generate a split power supply for amplifier to avoid a virtual ground introduction. The amplifier calculations are presented in the next section, and the problem with virtual ground is depicture in Figure 2.18. All multiplexers will be discussed in the 2.4.3 section.

#### 2.4.2 Operational amplifier

A part of project was to design a circuit which should do some basic operations with capacitance divider output. Before pass on to amplifier configuration paragraph, one equation need to be derived. It is important to make the divider's output in seq\_I dependent on the same output in seq\_II. To make it clear less tar at the beginning.

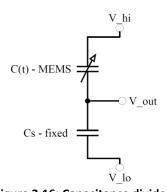

The capacitance of the electrostatic actuator C(t) and the series capacitor  $C_s$  form a capacitive divider circuit. If both capacitances are initially discharged and a voltage  $V_{hi}$  is applied to the upper node of the capacitive divider and  $V_{lo}$  voltage to the lower node, the intermediate voltage  $V_{OUT}$  follows the equation

$$V_{out} = \frac{V_{HI} - V_{LO}}{C_S + C(t)} \cdot C(t) + V_{LO}$$

(2.1)

The Figure 2.16 presents a capacitance divider to demonstrate the equation correctness. The electrostatic actuator is represented as the variable capacitor C(t), the series capacitor as  $C_s$  and the output as  $V_{\text{OUT}}$ .

Figure 2.16: Capacitance divider.

For sequence I, where  $V_{HI}$ =15V and  $V_{LO}$ =0V the output  $V_{OUT}$  is therefore given by:

$$V_{out(I)} = 15V \cdot \frac{C(t)}{C_S + C(t)}$$

(2.2)

For sequence II, where  $V_{HI}$ =-11.7V and  $V_{LO}$ =3.3V output equal to:

$$V_{out(II)} = -15V \cdot \frac{C(t)}{C_s + C(t)} + 3.3V$$

(2.3)

The next step is to determined from equation 2.2 a  $\frac{C(t)}{C_s + C(t)}$  component and insert it to 2.3.

Finally desired relationship amount to.

$$V_{out(II)} = -V_{out(I)} + 3.3V (2.4)$$

As equation 2.4 shows after changing between mode it is necessary to invert a output voltage and add a little offset. This task is performed by Texas Instrument's amplifier, and a scheme is presented in Figure 2.17.

Figure 2.17: A inverting amplifier configuration

This is a simplified version of this amplifier, in original scheme there are also power supply filtering capacitors and many jumpers to select a mode configuration. The next paragraph describe all of them.

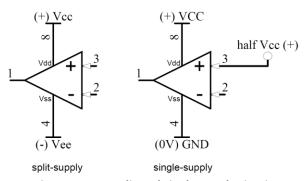

In the past there have been a lot of groups of op-amp circuits, but all of them have split power supply. While designing a single supply amplifier it is necessary to remember about specific conversion. It is not possible to change a supply from slip to single without doing modification in circuit. The next paragraph will explain this conversion. Figure 2.16 present split and single supply amplifier.

Figure 2.18: A split and single supply circuit

The power supply depicture on the left draws consist of positive and equal opposite negative pole. In this case input and output voltage are changed to the ground and swing to a limit of  $V_{\text{OM}}$ , the maximum peak-output voltage swing.

In single supply mode a new concept should be introduced. Virtual ground is a half of positive supply and ground. That is why it is necessary to add this voltage to a input signal. In fact only single supply configuration is used, and this error is compensating by adding a little less offset voltage. To clarify, the slope of input signal is controlling by a gain, and it isn't depend on power supply mode.

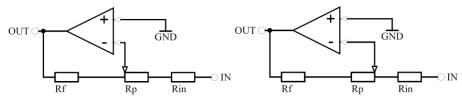

To make a board more useful and flexible the variable gain was designed. The gain range is 0.5 to 1.5, and the calculation is presented below.

Figure 2.19: A adjustable gain on the Left G=0.5 and Right G=1.5.

Simultaneous equations presented below allow to derive all unknowns.

$$\begin{cases} \frac{R_f}{R_{in} + R_p} = 0.5\\ \frac{R_f + R_p}{R_{in}} = 1.5 \end{cases}$$

(2.5)

There are three unknown, for that reason the assignment one of them is necessary. This value should be available in resistance series of types. For the potentiometer's resistance equal  $R_p = 500\Omega$  other values are  $R_{in} = 750\Omega$  and  $R_f = 625\Omega$ . The  $625\Omega$  value doesn't exists in E24 series of types and the nearest is  $620\Omega$ . So finally the gain range for values arrangement presented below is from 0.49 to 1.5.

$$\begin{cases} R_f = 620\Omega \\ R_p = 500\Omega \\ R_{in} = 750\Omega \end{cases}$$

(2.6)

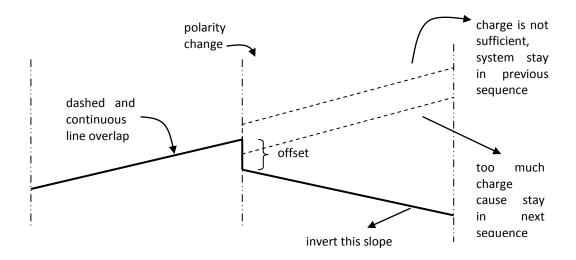

After explanation of all calculation in amplifier section it is time to present works in graphical way. Figure 2.20 presents only a shape without scales and any values. The dashed line present a system work with operational amplifier, but a continuous line without.

Figure 2.20: A charge injection shape with amplifier correction

Bold black line shows the course of the signal directly from the divider. In the sequence I, dashed lines show the possibilities, that may occur after changing the polarity. If stored charge is large enough, the measured capacitance is overstated after switching – this is represented by lower line, but the dashed line above present a behavioral if charge is not sufficient.

It is true that inverting and offset adding could be make by software, but much faster and easier is to do it by analog way.

Now the question arises why, after calibrating the device at the beginning of the work may appear there not enough charge. Answer is that, after the change of polarization, the capacitor is loaded opposite charge which in the next sequence should be re-charged. This situation was better describe in 1.6 Controlling the charge section.

#### 2.4.3 Multiplexers

In this part describe a multiplexers choice to change a voltage polarity. Section takes to consider only two signals: PWM HI\_MEMS supply a capacitance divider and PWM D which is controlled by Delirium-I. The high-voltage logic (+15V) inverter was implemented using the discrete commercial device ICL7667, which allows continuous operation at voltages up to 15 V. This scheme was presented in Figure 2.21.

Figure 2.21: Divider's supply wave generator by inverter

This approach is good for only one mode, just for positive voltage +15V and GND wave. In design -11.7V and 3.3V voltage wave is also needful, so there was a problem to find a negative supply inverters or that circuit was very expensive. The new idea was proposed. Inserted there a symmetrical supply multiplexer solved that problem. More over this multiplexers could be order for free from Analog Device research center. Everything will be perfect but new circuit has a longer turning ON and OFF times. The solution for that problem also was founded by placed parallel two of them. The scheme of new approach was presented below in Figure 2.22. For limpidity a second multiplexer was omitted.

Figure 2.22: Divider's supply wave generator by multiplexer

To calculate the time constants of divider supply circuit, equivalent capacitance should be estimated at first. Substitute capacitance connected in series could be calculated by the formula 2.7, and for  $C_{MEMS} \approx 20 pF$  and  $C_S = 68 pF$ , a  $C_{eq} = 15 pF$ .

$$\frac{1}{C_{eq}} = \frac{1}{C_{MEMS}} + \frac{1}{C_S}$$

$$C_{eq} = \frac{C_{MEMS} \cdot C_S}{C_{MEMS} + C_S}$$

(2.7)

A switching time calculation for both approaches was presented below.

#### Inverter

At Vcc = 15V, the output impedance of the inverter is typically  $R_{out}$  = 7 $\Omega$ . The time constant is derived in formula below.

$$\tau = R_{out} \cdot C_{ea} = 7\Omega \cdot 15 pF = 105 ns \tag{2.8}$$

#### Multiplexer

The output impedance of this multiplexer with dual power supply is typically  $R_{out}$  = 130 $\Omega$ , and time constant is derived below.

$$\tau = R_{out} \cdot C_{eq} = 130\Omega \cdot 15 \, pF = 1.95 us$$

(2.9)

This time has been reduced twice by connected two MUX in parallel. More over there are introduced several modifications in the code to slightly delay the start of sampling, it will be thoroughly explained in the chapter devote to the program.

To choose a right multiplexer a logic level capability is important. The Delirium-I chip was designed to work with TTL level, for that reason the ADG1309 device with 3V, logic-compatible digital input where:  $V_{IH}$  = 2.0 V and  $V_{IL}$  = 0.8 V was selected.

The selected multiplexer has a active high digital input to disconnect all switches. When this signal is low, the device is disabled and all switches are off. When high, Ax logic inputs determine on switches. In project there are no needs to disconnect them so the EN input is shorted to 3.3V.

The controlling signals A0 and A1 allow to select a appropriate input. As it is depicture in documentation block diagram this multiplexer has a 1-of-4 decoder and in fact consists with two identical 4 inputs and 1 outputs multiplexers and at the same time the control Ax signals connect both switches. This is useful to generate a both LO and HI\_MEMS signals concurrently. One of this outputs goes to high point of actuator and another to low of fixed capacitor. This situations is depicture in figure 2.20. Another useful combination was that D signal is connected directly to A0. This makes the PWM generation independent from FPGA, because D is generated by Delirium-I

chip, and only changing between sequence is controlled by FPGA program. This situation is also presented in the Figure 2.22.

### 2.4.4 Negative voltage calculation

To generate a negative supply voltage the UCC384-adj Texas Instrument's linear regulator was used. In this projects it is no necessary to choose high efficiency regulators just to supply one amplifier which can consume less then 20mA current. The adjustable version was placed because of major functionality. The output voltage is defined by equation 2.10.

$$V_{out} = -1.25 \cdot \left(1 + \frac{R_1}{R_2}\right) \tag{2.10}$$

Experience shows that in prototype version it is better to use potentiometer, which allows voltage adjustment in wide range. This solution entails some danger. It is necessary to tune voltage before lead it to circuit.

#### 2.4.5 Printed circuit boards

This section describe a board layout design. There will be presented two version of multiplexing board, and a rules which was kept during designing process. Board were made using a free 30-day trial version of Altium Designer. Despite the fact that this program provides a appreciable library items, sometimes it is needed to add a new one, and the standards are becoming very useful in this. That is why this section shall begin by introduce to the most important of them.

#### a) The CAD Library standard

Standard component package outlines come from industry standard organizations that specialize in component packaging data and standardization of documents and publications. One of the most well known organization is **IPC** – Association Connecting Electronics Industries. IPC is the trade association that brings together all of the company in this industry: PCB designers, PCB manufacturers, PCB assembly companies, suppliers, and original equipment manufacturers.

These standards define all aspects of facing the engineer. Collection of materials created for this project does not meet all of them, since these standards are developed for large companies where the production takes place in series. Although the multiplexing board is not complicated design, and will not be mass produced, it is worth to follow the standards for each project.

Since 1987, when an engineer needed information about the dimensions and ranges footprint tolerance, reached the standard IPC-SM-782. This standard defines the appearance of PCB components for a huge number of standard SMD components, but does not define specifically their names. In 2005 appeared the standard IPC-7351. All libraries included in Altium Designer is made in complying with this standard. At the points below there are listed the most useful standards.

- IPC-2221A: Generic Standard on Printed Board Design

- IPC-2222: Sectional Design Standard for Rigid Organic Printed Boards

- IPC-7351A: Generic Requirements for Surface Mount Design and Land Pattern Standard

- IPC-7251 (draft): Generic Requirements for Through-Hole Design and Land Pattern Standard.

All boards in this project were manufactured in milling process without metallization. That has imposed the following requirements, all tracks, pads, and vias was enlarged.

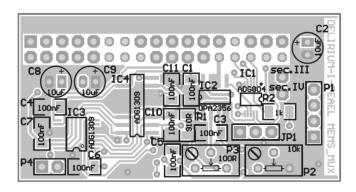

#### b) A first version

This version of the board had a few bugs. The first was its size 52 x 27 mm too small. It was very difficult to make any modification or measurements on the tracks or pins. In addition, in the second mode (negative divider supply), HI\_MEMS and LO\_MEMS signals looked the same as control D signal. Capacitors are not discharged during the reset, however, during the measurement. The layout of the first version is presented below in the figure 2.21.

Figure 2.23: A first version of multiplexing board

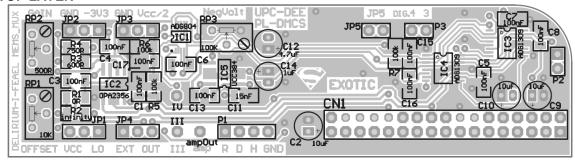

#### c) A second version

Advantages of this board were introduced a numerous descriptions in the cooper. All elements are logically arranged and work with it is more intuitive and requiring no schema. Board is double layer with components of only one side, with the majority of surface mount elements. A vias were hand made with silver steel. All polygon plane were connected to analog ground, provide efficient shielding.

The dimension of new board are:  $100 \times 27$  mm, and rounding in top left corner R = 10 mm. All tracks were placed according to the principle – horizontal on top, vertical at the bottom, then circuit became more clear. The maximum absorbed current is 20 mA so there is no need to increase the thickness of power paths.

#### **TOP LAYER**

#### **BOTTOM LAYER**

Figure 2.24: A two layers of second version of multiplexing board.

### 2.4.6 Jumpers

This section as before, includes a paragraph about the jumpers and their proper configuration. The majority of them comes from amplifier.

Jumper JP1 is used to select on offset voltage. In equation 2.4 this value amount to 3.3V. Therefore, this level could be achieve from power supply or LO\_MEMS signal in the second mode. Assuming that the PWM voltage may be modified equation 2.4 may take the form, and offset could depend on  $V_{LO\ MEMS}$  voltage.

$$\begin{split} V_{out(II)} &= \frac{V_{HI(II)} - V_{LO(II)}}{V_{HI(I)} - V_{LO(I)}} \cdot V_{out(I)} + V_{LO(II)} + V_{LO(I)} \\ V_{out(II)} &= gain \cdot V_{out(I)} + V_{LO} \end{split} \tag{2.11}$$

Jumpers JP2 and JP3 are used to choose a amplifier's supply voltage, split or single. Difference between these modes of supply was discussed in 2.4.2 section.

| Option                                           | Jumper JP2<br>Settings | Jumper JP3<br>Settings | Description                                                                                                                                                     |  |

|--------------------------------------------------|------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Single<br>supply                                 | ×                      | <b>⊠</b>               | This position it is necessary to remember about virtual ground during a measurements.                                                                           |  |

| Slit supply                                      | ×                      | ×                      | This is basic and very useful configuration, amplifier operates in the manner described in every manuals                                                        |  |

| Single<br>supply<br>without<br>ground<br>shifted | ×                      | ×                      | This configuration was used during testing circuit, as it was describe before, gain was adjust separately and offset error was corrected by PR1 potentiometers. |  |

Table 2.4: Amplifier power supply configuration.

The JP4 jumper is useful to test only amplifier operation without reordered circuit. Output of amplifier is available on gold pin marked as out on PCB cooper.

| Option Jumper JP2 Settings |   | Description                                                                                                                                                            |  |

|----------------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Normal mode                | × | In this position the out from capacitance divider are connected to inverting input of amplifier, this is normal operational mode.                                      |  |

| Test mode                  |   | This position is used to test a amplifier correct operation.  There is possible to connect an external signal source – through this jumper and tune a gain and offset. |  |

Table 2.5: The jumper's JP4 purpose

The JP5 jumper is used to disconnect a amplifier. Signal DIG(4) set a sequence mode, when the jumper is in place the multiplexer switch between first and second input depends on current sequence. In sequence II the output from divider is led thought amplifier circuit. If JP5 jumper is removed, the R7 resistor pull off the A0 control input to ground, assuring S1 terminal connect to the output drain D. Which means output from capacitance divider is permanently connected to ADC circuit, and do not depend on current sequence, the amplifier is bypassed.

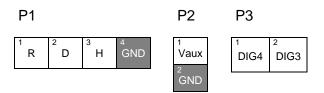

Board provide 3 probe pins to observe a several control signals. All of them are depictured in the Figure 2.25.

Figure 2.25: Pin signal in probe terminals.

# 3 Algorithm implementation

### 3.1 Overview

This chapter presents a hardware description and synthesis with VHDL. At the begging the block diagram will be shown with a description of each state. Then, will be description of all important pieces of code that will be included in the Appendix.

## 3.2 Codes description

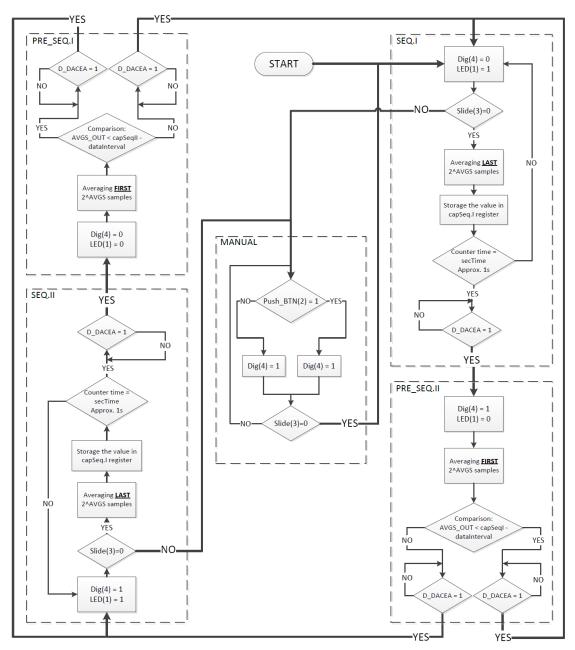

#### 3.2.1 ASM chart

This section present a flow chart of designed algorithm and also describe the most important part.

An FSM (finite state machine) is used to model a system that transits among a finite number of internal states. The transitions depend on the current state and external input. Unlike a regular sequential circuit, the state transitions of an FSM do not exhibit a simple, repetitive pattern.[3]

An FSM is usually specified by an abstract *state diagram* or *ASM chart* (algorithmic state machine chart), both capturing the FSM's input, output, states, and transitions in a graphical representation. The two representations provide the same information. The FSM representation is more compact and better for simple applications. The ASM chart representation is somewhat like a flowchart and is more descriptive for applications with complex transition conditions and actions. The ASM chart of the project is depictured in Figure 3.1.

Figure 3.1: The ASM chart of charge injection algorithm.

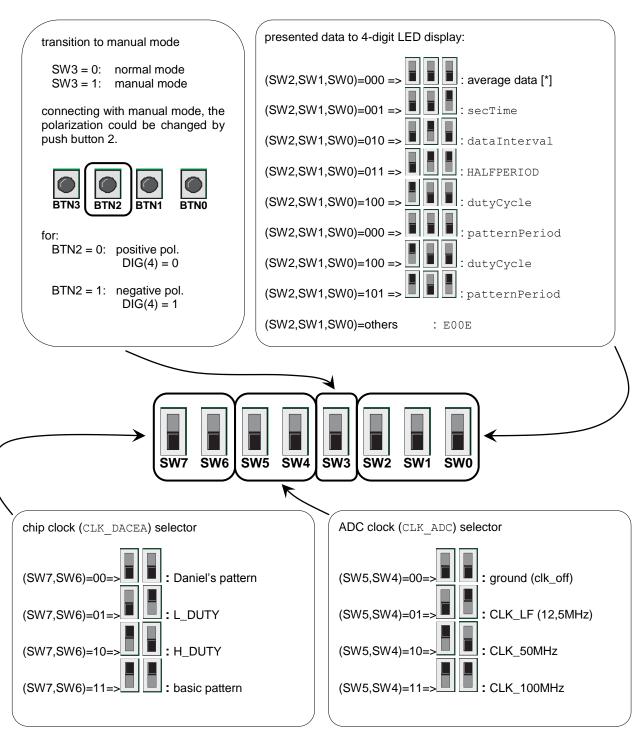

State machine at the beginning of work, consisted of only two states, for readability and ease of troubleshooting there were introduced an additional two states, responsible for making decision in which sequence system should stay to reduce a parasitic phenomenon. There are also another state called manual, which allow to change a sequence with pushing a button. These mode is used to test circuit and to better show a charge injection effect. Program starts work from SEQ.1, and at the beginning the counter start measure a 1s time in order to change a polarity and compare the quantity of charge that has been injected into the structure. Before switching the program have to collect all samples to do average, and wait for high level of D signal. In this state (seq.I) there is also possibility to go to manual mode, by asserting a slide

button high. After meeting all requirements the program pass to pre\_seq.II. Where its main task is to take a decision in which sequence program should stay further, but before that a samples should be averaged. So again collecting all 2<sup>AVGS</sup> samples, do average, and decide. When a decision will be made a next step is to wait for high level of D signal. Operation principle in state seq.II and pre\_seq.II is similar to seq.I and pre\_sqe.I. Anyway for the transparency of the code, separates state have been introduced, thereby increasing the number of flip-flops only by 2. In a simple projects, this number does not play the role, although in larger system it should be take into account as the best code and hardware optimization. Before pass through the main part it is worth to mention about clocks in whole system.

### 3.2.2 Clocks in design

The Spartan-3 Starter Kit board has a dedicated 50 MHz series clock oscillator source but also provide a advanced clocking capabilities as Digital Clock Managers (DCMs) [20]. DCMs optionally multiply or divide the incoming clock frequency (50Mhz) to synthesize a new clock frequency. DCMs also eliminate clock skew, thereby improving system performance. This property has been used in the project to generate digital to analog converter's clock with 100MHz frequency. It is worth to mention that converter belong to family of monolithic, single 3V supply, and 10-bit data resolution, with three different processing speed. In the design the fastest one is used, with 105MSPS (Million Samples Per Second). It means that, the highest frequency which could be apply, amount 100MHz.

The main clock synchronize all processes is called CLK\_IF. It is generated also from DCM instantiate as CLKFX which is an output from Frequency Synthesizer. The Digital Frequency Synthesizer (DFS) provides a wide and flexible range of output frequencies based on the ratio of two user-defined integers, a Multiplier (CLKFX\_MULTIPLY) and a Divisor (CLKFX\_DIVIDE). The output frequency is derived from the input clock (CLKIN) by simultaneous frequency division and multiplication. As it is depicture in the listing 3.1 (in line 126) a first variable depend of SSFACTOR constant, which takes the value 3. Moreover this constant is used to connects a clock frequency with output pattern width. DCM instance is presented in the Listing 3.1.

```

119

120

-- DCM instantiate

121

122

DCM1 : DCM

123

generic map (

124

CLKDV DIVIDE => 10.0, -- Divide by: 1.5,2.0,2.5,3.0,3.5,4.0,4.5,5.0,5.5,6

-- 7.0,7.5,8.0,9.0,10.0,11.0,12.0,13.0,14.0,15.0 or 16.0

125

CLKFX DIVIDE \Rightarrow 2**(SSFACTOR), -- Can be any integer from 1 to 32

126

127

CLKFX MULTIPLY \Rightarrow 2, -- Can be any integer from 1 to 32

CLKIN DIVIDE BY 2 => FALSE, -- TRUE/FALSE to enable CLKIN divide by two...

129

CLKIN PERIOD => 20.0,

-- Specify period of input clock

CLKOUT PHASE_SHIFT => "NONE", -- Specify phase shift of NONE...

130

CLK FEEDBACK => "2X", -- Specify clock feedback of NONE, 1X or 2X

131

DESKEW ADJUST => "SYSTEM SYNCHRONOUS", --

132

SOURCE SYNCHRONOUS,

SYSTEM SYNCHRONOUS or an integer from 0 to 15

133

DFS_FREQUENCY_MODE => "LOW", -- HIGH or LOW frequency...

DLL_FREQUENCY_MODE => "LOW", -- HIGH or LOW frequency mode for DLL

134

135

136

DUTY_CYCLE_CORRECTION => TRUE, -- Duty cycle correction, TRUE or FALSE

FACTORY_JF => X"C080", -- FACTORY_JF Values

PHASE SHIFT => 0, -- Amount of fixed phase shift from -255 to 255

137

138

STARTUP WAIT => FALSE) -- Delay configuration DONE until DCM LOCK,...

139

140

port map (

CLK0 => CLK_50MHz, -- 0 degree DCM CLK ouptput CLK2X => CLK_100MHzI, -- 2X DCM CLK output CLKFX => CLK_LF, -- DCM CLK synthesis out (M/D)

CLK0 => CLK 50MHz,

141

142

143

144

CLKFB => CLK_100MHz, -- DCM clock feedback

145

CLKIN => CLK IN

-- Clock input (from IBUFG, BUFG or DCM)

146

BUF1: BUFG port map (I => CLK_100MHzI, O => CLK_100MHz);

148

```

In the project was being implemented additional clock divider for general purpose. It is used mainly to timing and delays. A Listing 3.2 presented its implementation.

Listing 3.2: General purpose clock divider – MEMS\_CharageInReduce

Another very important clock is a clock that control a chip's operation. In this project there is possible to select one of several output clock patterns. The main of them was designed by Daniel Fernandez and that of the ruts is very extensive, including lot of collateral types, and providing a user intervention.

Due to the lack of accurate documentation and misunderstandings of all inserter protections, a new simple clock, allowing only a period and duty cycle adjust was introduced. It is presented in the , below.

Listing 3.3: General purpose clock divider – MEMS\_ChargeInReduce.vhd.

```

entity MY PATTERN is

177

178

Port (

clk : in std_logic; -- 12,5 MHz clock what means 80ns period

179

180

dutyCycle : in NATURAL range 1 to 1023;

patternPeriod : in natural range 1 to 1023;

181

182

out pattern : out std logic

183

) ;

184

end MY PATTERN;

185

186

architecture Behavioral of MY PATTERN is

187

signal Counter : natural range 0 to 1023 := 0;

188

begin

189

process (clk) begin

190

if rising edge(clk) then

191

if (Counter < patternPeriod) then</pre>

192

Counter <= Counter + 1;

193

else Counter <= 0; end if;</pre>

194

end if;

195

end process;

'1' when Counter < dutyCycle else '0';

196

out_pattern <=

197

end Behavioral;

```

As it was described in the Introduction chapter, a MEMS actuator capacitance could be changed with duty cycle. In the 3.2.7 section there will be description how to do it, but in the first place an important instantiates will be presented.

### 3.2.3 Important instantiates

At the beginning of this section it is worth to mention what is a current information path to be correctly interpreted in order to make a proper decision. The easiest way to present it is to show it on the functional block diagram.

Figure 3.2: A whole system functional block diagram

In the next part there will be explanation for each module, start with Sample & Hold. Instantiate is presented in the Listing 3.4

Listing 3.4: S&H instantiate - MEMS\_ChargeInReduce.vhd.

```

136

- Sample and Hold for ADC data

137

SAHP : entity work.sampleandhold(Behavioral)

138

generic map (n=>11)

139

port map (

140

clk => CLK 100MHz,

141

hold \Rightarrow H \overline{POS},

din => DATA ADC SIGNED,

142

dout => SAHP OUT

143

```

When the hold is high, capacitance was recharged and this kind of information should be separated from other part to prevent glitches among other things. For this reason there was introduced a module responsible for stopping the sampling at the time of capacitance reset. To control the sample and hold module it was used hold signal (H) generated by the chip, but before the signal is subordinate to a small modification. Below there is presented a listing and detail explanation.

Listing 3.5: Hold signal delayed - MEMS\_ChargeInReduce.vhd.

```

136

Delayed of the HOLD (H DACEA) signal

137

HLDP : entity work.delayed stim(Behavioral)

generic map(predelay=>PREHOLD TIME, postdelay=>HPOS TIME, preventive=>'1')

138

139

port map (

140

clk => CLK 100MHz,

inp \Rightarrow H DACEA,

141

142

outp => H POS

143

);

```

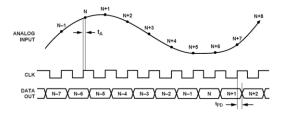

To explain why the signal delay was introduced it is necessary to mention about how converter operation is based. The AD9215 uses a multistage differential pipelined architecture with output error correction, and this of course means that the actual capacitance value are delayed, more over introducing this delay could prevent a short interferences appear after changing a control level. Figure 3.3 present a timing diagram, and demonstrate how ADC process the samples.

Figure 3.3: ADC timing diagram.

### 3.2.4 Averaging as a low-pass filter

In this section there will be averaging function description. At the beginning of project several question arise, one was: how to determine the typical amount, a valid estimate, or the true value of some measured parameter?

In the physical world, it is not easy to do because unwanted random disturbances contaminate measurements. These disturbances are due to both the nature of the variable being measured and the fallibility of our measuring devices. Each time during accurate measurement some physical quantity, a slightly different value was get. Those unwanted fluctuations in a measured value are called noise, and digital signal processing practitioners have learned to minimize noise through the process of averaging. The literature, shows not only how averaging is used to improve measurement accuracy, but that averaging also shows up in signal detection algorithms as well as in low-pass filter schemes [13] [15].

In digital signal processing, averaging often takes the form of summing a series of time-domain signal samples and then dividing that sum by the number of individual samples. Mathematically, the average of N samples of sequence x(n), denoted  $x_{ave}$ , is expressed in the equation 3.1.

$$x_{ave} = \frac{1}{N} \sum_{n=1}^{N} x(n) = \frac{x(1) + x(2) + x(3) + \dots + x(N)}{N}$$

(3.1)

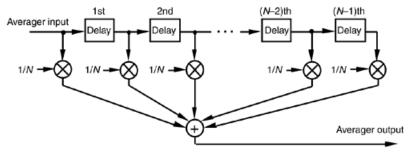

Explaining the process of averaging is worth to mention about one well know filter structure. FIR (Finite Impulse Response) low pass filters given a finite duration of nonzero input values. This filter use addition to calculate their outputs in a manner much the same as the process of averaging uses addition. In fact, averaging is a kind of FIR filter and successive time-domain outputs of an N-point averager are identical to the output of an (N–1)-tap FIR filter whose coefficients are all equal to 1/N. Figure 3.4 shows the discussed idea.

Figure 3.4 An N-point average depicture as a FIR filter

```

213

214

-- Averaging device

215

221

entity averaging is

222

generic ( avgs : integer;

n : integer);

224

225

clk : in std_logic;

din : in STD LOGIC VECTOR (n-1 downto 0);

226

227

dout : out STD LOGIC VECTOR (n-1 downto 0)

228

);

229

end averaging;

231

architecture Behavioral of averaging is

232

233

type samples IS ARRAY ((2**avgs)-1 DOWNTO 0) OF STD LOGIC VECTOR(n-1 downto 0);

signal dataSamples : samples;

234

236 begin

237

process (clk)

238

variable accumulator : STD LOGIC VECTOR (n+avqs-1 downto 0) := (OTHERS => '0');

239

begin

240

if rising_edge(clk) then

241

-- add new sample and detele the last one (Shift right)

242

-- first LSB is deleted, then array is shifted right

-- and the new sample is put in MSB place for index in 0 to (2**avgs)-2 loop

243

244

245

dataSamples(index) <= dataSamples(index+1);</pre>

246

end loop;

dataSamples((2**avgs)-1)<=din;</pre>

247

249

-- average all data in array

250

accumulator := (others=>'0');

251

for index in dataSamples'range loop

252

accumulator := accumulator + ext(dataSamples(index),n+avgs);

253

end loop;

254

dout <= accumulator(n+avgs-1 downto avgs);</pre>

end if;

255

256

end process;

257 end Behavioral;

```

Listing 3.6 presets software implementation of averaging module. Number of samples averaging in one cycle is determine by avgs generic, and amount to 2<sup>avgs</sup> samples. All of them are accumulated in a array at first (line 247). During the time, when new sample arise, array is shifted to the right and new value goes to the MSB (**M**ost **S**ignificant **B**it) place. After that all data in the array are summed into accumulator (lines: 251-253). Division by the number of samples was carried by the logical right shift accumulator register, whose bits are simply moved a number determine by the avgs generic. The n predefined variable specify a data sample's number of bits.

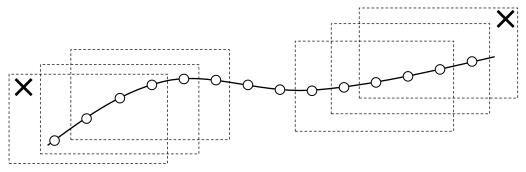

As it was illustrated in the Figure 3.3, to obtain one average sample it is necessary to collect min 2<sup>avgs</sup> data. That figure 3.2 shows more clearly the principal of progressive averaging. A average from rectangles marked with a cross will not be further subjected to process because of incomplete set of samples.

Figure 3.5 An N-point progressive average with prohibited cases

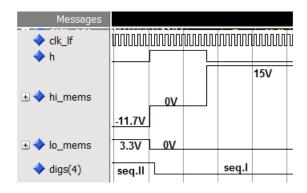

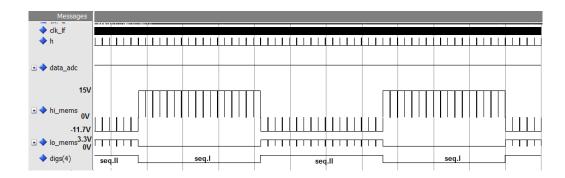

The system have to wait to collect all samples, the special counter was designed for doing that task and it is presented in the listing 3.3, but before discussing this part a short explanation is necessary. Counter is synchronize with CLK\_LF clock, and it could be asynchronous reset by RST signal, or synchronous by assert a slide button high. A DIGS\_int(4) is a signal flag to indicate and control a sequence mode. The different settings of the DIGS\_int(4) bit have the following effects:

```

DIGS_int(4) = '0':

HI_MEMS: 0v ______

LO_MEMS: permanently grounded

DIGS_int(4) = '1':

HI_MEMS: 0v ______

LO_MEMS: 0v ______

```

Due to the possible changes in the number of averaging samples up-down counter was proposed. Collect all samples is indicated by setting a overflow bit in the same counter. Counter declaration is shown in the Listing 3.7.

Listing 3.7 Averaging counter declaration — MEMS\_ChargeInReduction.vhd

signal avgCount : STD\_LOGIC\_VECTOR (AVGS DOWNTO 0) := (others=>'0');

The maximum value amount 2<sup>AVGS+1</sup> not 2<sup>AVGS</sup>, as should be normally. The new concept was introduced. The MSB(Most Significant Bit) is used to indicate, that 2<sup>AVGS</sup> value was counted, when it happen in the next iteration counter just overload, assert meanwhile the avgCount (AVGS) bit.

Listing 3.8: Averaging counter implementation – MEMS\_ChargeInReduction.vhd

```

466

avgCount

467

process (CLK LF, RST) begin

if RST = \frac{1}{1} then

468

469

avgCount <= (others=>'0');

elsif rising edge (CLK LF) then

470

if SLIDE FILT(3) = '0' then

471

if \overline{DIGS}_{int(4)} = '0' then

472

if avgCount(AVGS) = '1' then avgCount <= (others=>'1');

473

474

else avgCount <= avgCount + 1; end if;</pre>

elsif DIGS int(4) = '1' then

475

if avgCount(AVGS) = '0' then avgCount <= (others=>'0');

476

477

else avgCount <= avgCount - 1; end if;</pre>

478

end if;

else

avgCount <= (others=>'0');

480

end if;

481

482

end if:

483

end process;

```

During sequence II, avgCount is counting up, but in sequence I down. For that reason counter have to be loaded to one of limits value. When the avgCount (AVGS) bit is set, it is loaded to maximum (line 473), and when avgCount (AVGS) = 0 counter is cleared (line 476).

After presented all the most important instantiates in the module it is time to show how the state machine was implemented.

### 3.2.5 State machine description

Several approaches can be conceived to design a FSM (Finite State Machine) which consist of lower and upper section. The lower one contains the sequential logic (flip-flops), while the upper section contains the combinational logic. The sequential section in this design has three inputs (CLK LF, RST and state next), and one output (state reg). The Listing 3.9 shows this part.

Listing 3.9: Lower (Sequential) section of state machine – MEMS\_ChargeInReduction.vhd

```

429

-- #####################

430

STATE REG

process (CLK LF, RST) begin

431

if RST = '1' then

432

433

state reg <= seqI;</pre>

434

elsif rising edge (CLK LF) then

if D_DACEA = '1' then

435

436

state_reg <= state_next;</pre>

437

end if;

438

end if;

439

end process;

```

To encode the states of a state machine, there are several available styles. The default style is binary. Its advantage is that it requires the least number of flip-flops. In this case, with n flip-flops (n bits), up to 2<sup>n</sup> states can be encoded. The disadvantage of this encoding scheme is that it requires more logic and is slower than the others. At the other extreme is the onehot encoding style, which uses one flip-flop per state. Therefore, it demands the largest number of flip-flops. In this case, with n flip-flops (n bits), only n states can be encoded. On the other hand, this approach requires the least amount of extra logic and is the fastest.

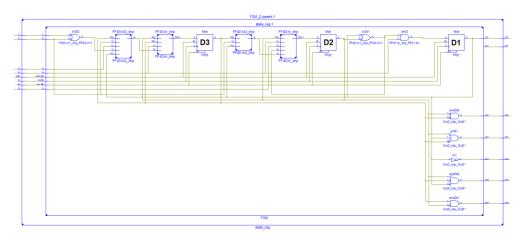

In this design the binary encode style was used, and a number of flip-flops could be calculated from the following equation:  $log_2n$  where n is the number of states. Figure 3.6 confirm that. This is a part of RTL (Register Transfer Level) schematic [4] representation, generated by Xilinx Synthesis Technology (XST) [18]. There are 3 flip-flop marked as D1..D3, to store one of five state possibilities (pre seqI, seqI, pre seqII, seqII and manual).

Figure 3.6: A part of RTL scheme shows state encoding.

Upper section will be discussed separately for each state, start with seqI state which is presented in the Listing 3.10.

Listing 3.10: A seql state - MEMS\_ChargeInReduce.vhd

```

502

SEOUENCE I

503

when seqI =>

504

DIGS_int(4) <= '0';

LEDS (1) <= '1';

505

506

if SLIDE FILT(3) = '0' then

507

if secCount(26 downto 23) = secTime

508

then

509

state_next <= pre_seqII;</pre>

510

else state next <= seqI;</pre>

511

end if:

512

else state next <= manual;</pre>

513

end if;

```

After power ON or reset signal program begin from this state. Here there is also possibility to go to manual mode after set a fourth slide button to high which is represent as SLIDE\_FILT (3) in the program. When a counter secCount which will be presented in next section reach predefined value secTime, the program goes to pre\_seqII state to do comparison. This part is presented in the Listing 3.11.

Listing 3.11: A pre seqll state – MEMS\_ChargeInReduce.vhd

```

515

----- PRE-SEQUENCE II

516

when pre_seqII =>

DIGS_int(4) <= '1';

517

LEDS (1) <= '0';

518

519

if avgCount(AVGS) = '0' then

520

521

\begin{tabular}{ll} \textbf{if} & \texttt{(AVGS\_OUT} & \texttt{capSeqI} & - \texttt{dataInterval)} & \textbf{then} \\ \end{tabular}

522

state next <= seqII;

523

else state next <= seqI;</pre>

524

end if:

else state next <= pre seqII; end if;</pre>

525

```

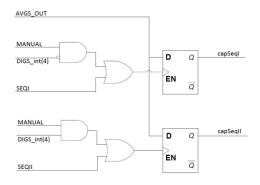

In this state at the beginning the polarization of voltage supply capacitance divider was changed. Next there are collecting a samples to average them, if a sufficient amount was accumulated and permission to average was given program pass to comparison. The state with the lowest ADC data which mean with the lowest MEMS capacitance is chosen. Remaining states (pre seqI, and seqII) operate in the same manner and they are shown in the Listing 3.12.

Listing 3.12: A remaining state: pre seql and seqll - MEMS\_ChargeInReduce.vhd

```

490

PRE-SEQUENCE I

491

when pre seqI =>

DIGS_int(4) <= '0';

492

493

LEDS(1) \leftarrow '0';

494

if avgCount(AVGS) = '1' then

495

496

if (AVGS OUT < capSeqII - dataInterval) then</pre>

497

state next <= seqI;

498

else state next <= seqII;</pre>

499

end if;

500

else state_next <= pre_seqI; end if;</pre>

527

----- SEQUENCE II -----

528

when seqII =>

DIGS int(4) <= '1';

529

530

LEDS (1) <= '1';

531

if SLIDE FILT(3) = '0' then

532

if secCount(26 downto 23) = secTime then

533

534

state_next <= pre_seqI;</pre>

535

else state next <= seqII;</pre>

536

end if:

537

else state_next <= manual;</pre>

538

end if:

```

Listing 3.13 presents a last state in which user can chance supply manually.

Listing 3.13: A manual mode state - MEMS\_ChargeInReduce.vhd

```

540

MANUAL MODE

541

when manual =>

if CLK DIV(20) = '1' then LEDS(1) <= '1';</pre>

542

else LEDS(1) <= '0'; end if;</pre>

543

544

545

if PUSH FILT(2) = '1' then DIGS int(4) <= '1';</pre>

else DIGS int(4) <= '0'; end if;</pre>

547

if SLIDE FILT(3) = '0' then state_next <= seqI;</pre>

548

549

else state_next <= manual; end if;</pre>

```

As it was shown in the Figure 3.1 it is possible to reach this state only form sequence I or II with putting a fourth slide button to high. A throbbing second led LEDS (1) inform about operations in this state. A third push button can be used to change voltage polarity.

Connected with lower section there is another one register which should be described. It is presented in the Listing 3.14.

Listing 3.14: A sequence timer – MEMS\_ChargeInReduction.vhd

```

440

secCount

441

process (CLK LF, RST) begin

if RST = '1' then

442

443

secCount <= (others=>'0');

elsif rising edge (CLK LF) then

444

if SLIDE_FILT(3) = '0' then

445

446

- comment that instead next line put this for sim.

447

if secCount(26 downto 23) = secTime then

secCount <= secCount;</pre>

448

if D_DACEA = '1' then

449

450

secCount <= (others=>'0');

451

end if;

-- elsif secCount = (secTime & B"000" & X"0 0000") - 1 then

452

-- if (SLIDE FILT(4) = '0') then

453

454