*Titol:* Simulació i modelat d'entorns cloud per a experimentació amb machine learning

Volum: 1

Alumne: Jordi Roldán Llinàs

Director/Ponent: Josep Lluís Berral García / Ricard Gavaldà

Mestre

**Departament:** Llenguatges i Sistemes Informàtics

**Data:** 29/06/10

### DADES DEL PROJECTE

Titol del Projecte: Simulació i modelat d'entorns cloud per a experimentació amb machine learning

Nom de l'estudiant: Jordi Roldán Llinàs

Titulació: Enginyeria en Informàtica

Crèdits: 37,5

Director/Ponent: Josep Lluís Berral García / Ricard Gavaldà Mestre

Departament: Llenguatges i Sistemes Informàtics

### MEMBRES DEL TRIBUNAL (nom i signatura)

President: Jorge Castro Rabal

Vocal: Gemma Sese Castel

Secretari: Ricard Gavaldà Mestre

### **QUALIFICACIÓ**

Qualificació numèrica:

Qualificació descriptiva:

Data:

### **Abstract**

Nowadays Cloud computing has emerged as one of the most promising computer paradigms. The idea of selling software as a service has promoted IT enterprises to bet for this new paradigm. Cloud computing aims to power the next generation data centers not only offering software as a service but virtual services like hardware, data storage capacity or application logic. The increasing use of Cloud-based applications will also increase the power dedicated to the data centers that support this Clouds.

Research in Cloud computing requires solutions that have to be tested in real environments. It is difficult and expensive to set up suitable test-beds for large scale cluster applications. Simulation can fulfill the needs that we find in Cloud computing experimentation. A large data center simulator can save lots of time and effort in Cloud investigation.

This project presents the design and development process of some extensions to an existing virtualized data center simulator for Cloud computing research. It is able to reproduce the behaviour of a real Cloud framework and the information that it offers of the execution makes it suitable for testing and investigation purposes.

The final idea of this project was to extend the heterogeneity of the tests that can be run by the simulator to use it as a test-bed for machine learning experimentation.

## Acknowledgements

I would like to express my gratitude to all the people who has made this project possible. I would like to give my sincerely thanks to my advisors Dr. Jordi Torres and Dr. Ricard Gavaldà and specially to my director Josep Lluís Berral García for their time, effort and advices. It has been a great experience I will not forget all the lessons I learned with you.

Many thanks to Iñigo Goiri and Ferran Julià, this project would not have been possible without your help and unconditional support. Thank you for always being there.

Finally, I would like to devote this work to all of my family and friends. Specially to my parents for their unconditional support and patience. Also for the moon which shared with me long nights. You really own a large part of this project.

# Contents

| 1. Introduction                                          | 1  |

|----------------------------------------------------------|----|

| 1.1 Basic knowledge for understanding this project       |    |

| 1.1.1 About Machine Learning and Data Mining             | 1  |

| 1.1.2 About Grid and Cloud computing                     |    |

| 1.1.3 About Virtualization and Virtual Machines (VM's)   | 2  |

| 1.1.4 Service level Agreement (SLA)                      |    |

| 1.2 Origin and Background                                |    |

| 1.3 Motivation                                           |    |

| 1.4 Goals of the project                                 |    |

| 1.5 Functional requirements of the project               |    |

| 1.6 Document organization.                               |    |

| 2. Introducing simulation                                |    |

| 2.1 Types of simulation                                  |    |

| 2.2 Related concepts                                     |    |

| 3. Technology choice                                     |    |

| 3.1 COTSon.                                              |    |

| 3.2 PARSEC                                               |    |

| 3.3 NS2                                                  |    |

| 3.4 VnetUML                                              |    |

| 3.5 Netsim                                               |    |

| 3.6 Omnet++                                              |    |

| 3.7 Conclusion.                                          |    |

| 4 Omnet++                                                |    |

| 4.1 General description.                                 |    |

| 4.2 How it works                                         |    |

| 5. Starting point of the simulator                       |    |

| 5.1 EEFSimV2                                             |    |

| 5.2 Virtualization                                       |    |

| 5.3 Modules.                                             |    |

| 5.3.1 WorkloadGenerator.                                 |    |

| 5.3.2 PlugableScheduler                                  |    |

| 5.3.3 PC                                                 |    |

| 5.3.4 HyperScheduler                                     |    |

| 5.3.5 PowerSupply                                        |    |

| 5.3.6 LocalScheduler                                     |    |

| 5.4 Messages.                                            |    |

| 5.4.1 SimMessage                                         |    |

| 5.5 Other C++ files                                      |    |

| 5.5.1 WorkloadComponent                                  |    |

| 5.5.2 VirtualMachine                                     |    |

| 6. First extension: Change the representation of the CPU |    |

| 6.1 CPU background                                       |    |

| 6.2 Previous representation.                             |    |

| 6.3 Used programs.                                       |    |

| 6.4 CPU experimentation.                                 |    |

| 6.5 CPU modeling                                         | 20 |

| 0.0 01 U IIIUMVIIII                                      |    |

| 6.7 Future work                                                                   |      |

|-----------------------------------------------------------------------------------|------|

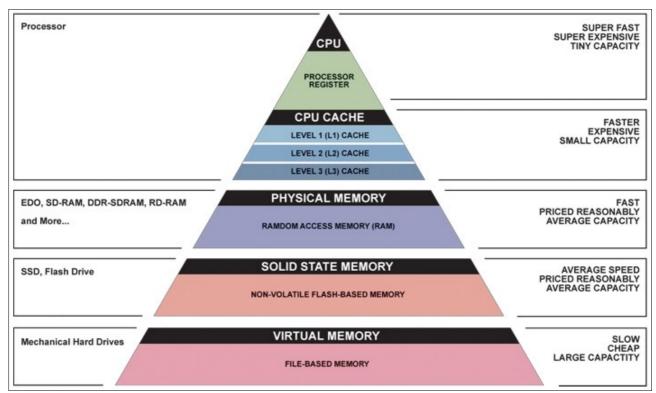

| 7.1 Memory background                                                             |      |

| 7.2 Memory modeling                                                               |      |

| 7.2 Memory modeling                                                               |      |

|                                                                                   |      |

| 7.2.1 First model: Considering all the devices that form the memory hierarchy     |      |

| 7.2.1.1 Used programs                                                             |      |

| 7.2.1.2 Experimentation                                                           |      |

| 7.2.1.3 Conclusion.                                                               |      |

| 7.2.2 Second model: Considering the memory as a full block and supposing that the | CP   |

| consumption and the memory time consumption are independent on each other         |      |

| 7.2.2.1 Used programs                                                             |      |

| 7.2.2.2 Results of the experimentation.                                           |      |

| 7.2.2.3 Conclusion                                                                |      |

| 7.2.3 Third model: Considering the memory as a block and supposing that the CPU   | time |

| consumption and the memory time consumption have dependencies on each other       |      |

|                                                                                   |      |

| 7.2.3.1 Used programs                                                             |      |

| 7.2.3.2 Experimentation.                                                          |      |

| 7.2.3.3 Conclusion                                                                |      |

|                                                                                   |      |

| 7.3 Memory implementation.                                                        |      |

| 7.4 Future work                                                                   |      |

| 8. Third extension: Modeling the network                                          |      |

| 8.1 Network background                                                            |      |

| 8.2 Network modeling                                                              |      |

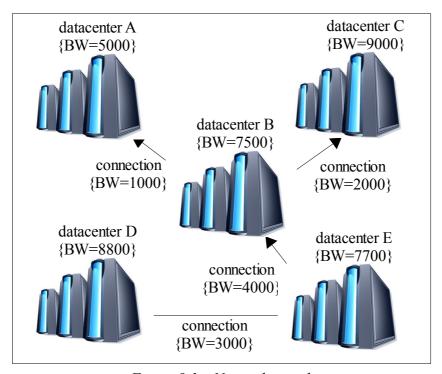

| 8.2.1 Network modelation sample                                                   |      |

| 8.3 Network implementation                                                        |      |

| 8.4 Future work                                                                   |      |

| 9. Fourth extension: Using xml format                                             |      |

| 9.1 Xml background                                                                |      |

| 9.2 Used library                                                                  |      |

| 9.3 Configuration files                                                           |      |

| 9.4 Implementation                                                                |      |

| 9.5 Future work                                                                   |      |

| 10. Evaluation and validation of the simulator                                    |      |

| 11. Schedule of the project                                                       |      |

| 11.1 Original schedule                                                            |      |

| 11.2 Distribution of the workload                                                 |      |

| 11.3 Cost of the project                                                          |      |

| 11.3.1 Human resources.                                                           |      |

| 11.3.2 Hardware, software and resource maintenance                                |      |

| 12. Conclusion                                                                    |      |

| 12.1 Review/summary of the requirements and their achievement                     |      |

| 12.2 Technical conclusion.                                                        |      |

| 12.3 Personal conclusion.                                                         |      |

| BibliographyAnnex A: Source code of the implemented benchmarks                    |      |

# **List of Figures**

| Figure 1.1 - Architecture of the simulator                                                       | 4   |

|--------------------------------------------------------------------------------------------------|-----|

| Figure 1.2 - Main artifacts of the simulation context                                            | 5   |

| Figure 1.3 - Main artifacts of the simulation context mapped into the emotive architecture       | 5   |

|                                                                                                  | 17  |

| Figure 4.2 - NED source editor                                                                   | 17  |

| Figure 4.3 - Simple and compound modules                                                         | 18  |

| Figure 5.1 – Internal architecture of the simulator                                              | 19  |

| Figure 5.2 – Xen architecture                                                                    | 20  |

| Figure 5.3 – The five-state process model                                                        | 24  |

| Figure 6.1 – Pseudo code of the implemented benchmark without memory accesses                    | 28  |

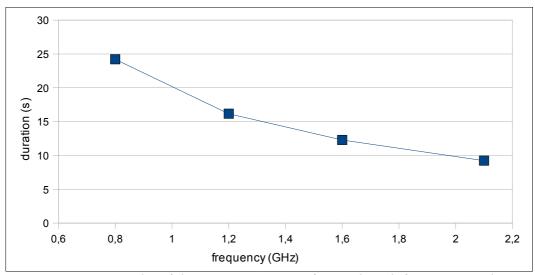

| Figure 6.2 – Results of the execution times of one job with frequency scaling                    | 29  |

| Figure 7.1 – Memory hierarchy                                                                    | 33  |

| Figure 7.2 – Sample of Valgrind output (using Cachegrind)                                        |     |

| Figure 7.3 – Pseudo code of the implemented benchmark with memory accesses                       | 37  |

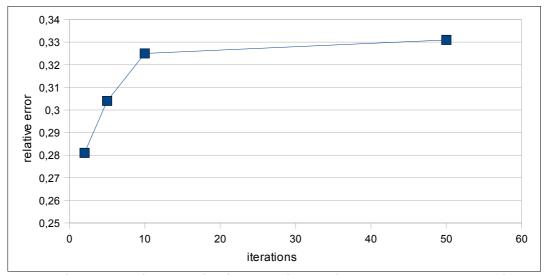

| Figure 7.4 – Relative error between the theoretical an real execution time varying the number of |     |

| iterations                                                                                       |     |

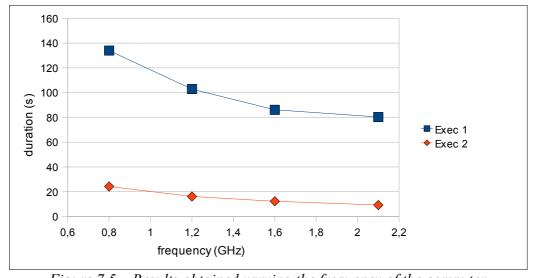

| Figure 7.5 – Results obtained varying the frequency of the computer                              | .41 |

| Figure 7.6 – Sample of Valgrind output (using Lackey)                                            | .44 |

| Figure 8.1 – Network sample                                                                      | 50  |

| Figure 8.2 – Network sample (XML content)                                                        | 51  |

| Figure 8.3 – XML sample                                                                          | 56  |

| Figure 9.1 – hostConfig.xml sample                                                               | 59  |

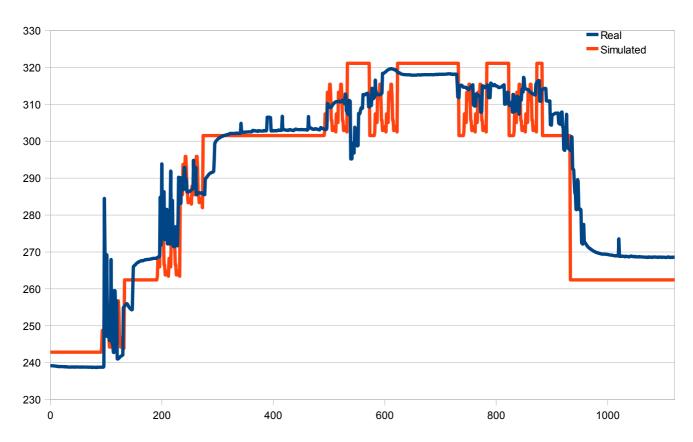

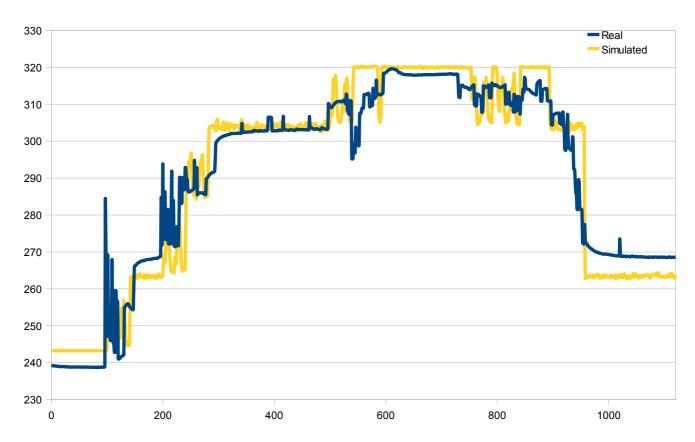

| Figure 10.1 – Real and simulated (by EEFSimV2) results related with the energy consumption of    |     |

| · · · · · · · · · · · · · · · · · · ·                                                            | 62  |

| Figure 10.2 – Real and simulated (by EEFSimV3) results related with the energy consumption of    | •   |

| the cloud (in Watts)                                                                             | 63  |

| Figure 10.3 – Real and both of simulated (by EEFSimV2 and EEFSimV3) results related with the     | 3   |

| energy consumption of the cloud (in Watts)                                                       | 64  |

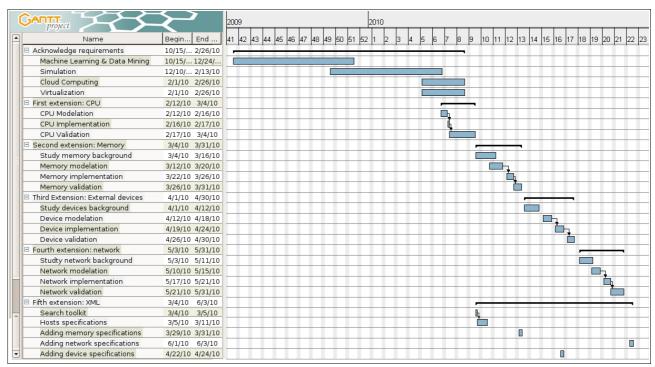

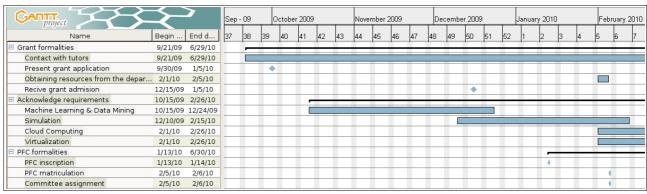

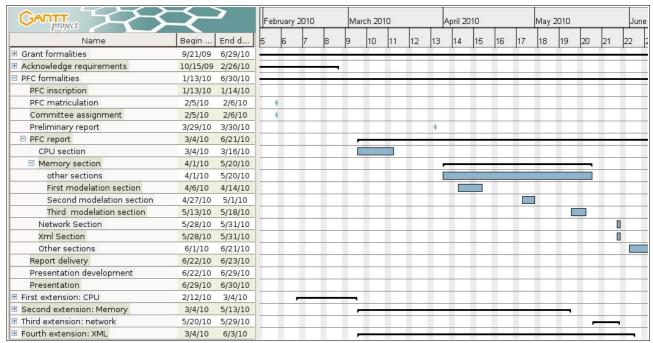

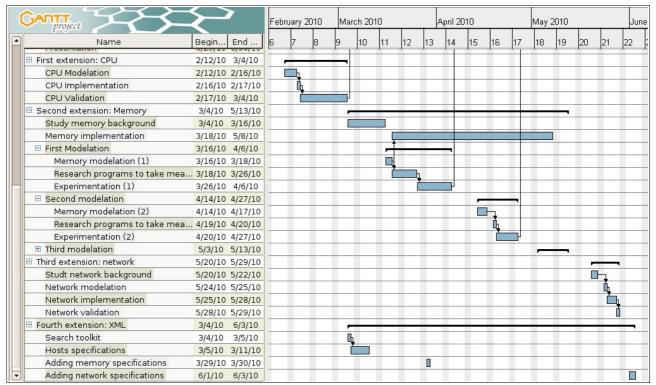

| Figure 11.1 – Gantt chart of the original schedule of the project                                | 66  |

| Figure 11.2 – Gantt chart with the tasks performed during the formalization of the grant         | 67  |

| Figure 11.3 – Gantt chart of the effective work tasks                                            | .68 |

| Figure 11.4 – Gantt chart of the tasks involved with the extensions                              | 69  |

| Figure 11.5 – Gantt chart of the tasks involved last steps of the project                        | .70 |

|                                                                                                  |     |

# **List of Tables**

| Table 5.1 – WorkloadComponent main attributes                                                   | 25 |

|-------------------------------------------------------------------------------------------------|----|

| Table 5.2 – WorkloadComponent main attributes                                                   | 26 |

| Table 6.1 – Results of the execution times of one job with frequency scaling                    | 28 |

| Table 6.2 – CPU parameters and methods                                                          | 30 |

| Table 6.3 – Workload added methods.                                                             | 31 |

| Table 7.1 – Relative error between the theoretical an real execution time varying the number of |    |

| iterations                                                                                      | 37 |

| Table 7.2 – Sample of data required by the model                                                | 39 |

| Table 7.3 – Results obtained varying the ratio                                                  | 40 |

| Table 7.4 – Results obtained varying the latency                                                | 41 |

| Table 7.5 – Results obtained varying the frequency of the computer                              | 41 |

| Table 7.6 – Results obtained while trying to identify memory usage prototypes                   | 44 |

| Table 7.7 – Methods and attributes from Memory class                                            | 45 |

| Table 7.8 – Added methods and attributes to the HyperSched                                      | 46 |

| Table 7.9 – Added methods and attributes to the WorkloadComponent                               | 46 |

| Table 8.1 – Sample of required data for modelating the network                                  | 52 |

| Table 8.2 – Methods and attributes from Memory class                                            | 53 |

| Table 8.3 – Added method to PlugableScheduler                                                   | 54 |

| Table 9.1 – Added method to PlugableScheduler                                                   | 60 |

| Table 10.1 – Results of the validation of the EEFSimV2                                          | 62 |

| Table 10.2 – Results of the validation of the EEFSimV3                                          | 63 |

| Table 11.1 – Human resources costs.                                                             | 71 |

| Table 11.2 – Hardware and maintenance costs                                                     | 71 |

This project is the result of one year investigating and working with a team compound by some teachers and students of post-graduate courses. As it is an extension of some work developed by other students it is important to understand the origin and background that precedes this work.

In this section we describe the origin and background of the project and the facts that motivate the conception and purpose of this work. In the next sections we will survey the work that precedes that project in order to specify our starting point. The investments of some research groups of the university became a simulator which is the essence of that project. The simulator that they developed is our starting point, and all the work we have done is extending its functionalities.

### 1.1 Basic knowledge for understanding this project

There are some important concepts to understand before reading this document. In this section we will explain some topics that are related with some specific disciplines of computer science.

### 1.1.1 About Machine Learning and Data Mining

Machine learning is a scientific discipline that is concerned with the design and development of algorithms that allow computers to learn patterns and behaviors based on empirical data. Machine learning techniques consist, generally, in collecting a training data set from the system with data composed by labeled example instances, and creating a model through some technique (as induction, deduction, reinforcement,..) able to explain these examples, expecting that new data will fit on it. Machine Learning techniques are divided into supervised learning (like classification and regression), unsupervised learning (discovering the relationship between the input data), clustering (finding clusters of examples), reinforcement learning (selecting the best decision from the past experiences feedback).

A major focus of machine learning research is to automatically learn to recognize complex patterns and make intelligent decisions based on data. That is the reason why it is really related with Data mining, which is the process of extracting patterns from data.

### 1.1.2 About Grid and Cloud computing

The grid computing refers to the act of sharing tasks over multiple computers. Grid computing (or the use of a computational grid) is the union of the resources of many computers in a network, usually to a scientific or technical problem that requires a great number of computer processing cycles or access to large amounts of data.

Clouds are vast resource pools with on-demand resource allocation. Cloud computing overlaps some of the concepts of distributed, grid and utility computing, however it does have its own meaning. In fact, they are both used to economize computing by maximizing existing resources.

Cloud computing is accessing resources and services needed to perform functions with dynamically changing needs.

However, the difference between the two lies in the way the tasks are computed in each respective environment. In a grid, one large job is divided (if possible) into many small portions and executed on multiple machines. This characteristic is fundamental to a grid; not so in a cloud. While grid computing also offers a similar facility for computing power, cloud computing is not restricted to just that. A cloud can offer many different services, from web hosting, right down to word processing. In fact, a computing cloud can combine services to present a user with a homogeneous optimized result.

### 1.1.3 About Virtualization and Virtual Machines (VM's)

One of the key technologies in the cloud systems is virtualization, which is a technology that has enabled cost reduction and easier resource management for this type of distributed systems. Virtualization provides isolation between different applications that are sharing the same physical resources. That was the context in which the term Virtual Machine (VM) was established. Virtualization provide the sharing of the underlying physical machine resources using different virtual machines, each running its own operating system. So it offers the image of a dedicated and customized machine to each user, decoupling them from the system software of the underlying resource. The software layer providing the virtualization is called a virtual machine monitor or hypervisor.

### 1.1.4 Service level Agreement (SLA)

Cloud computing is inevitably linked to the Quality of Service Concept. Emerging Cloud applications such as social networking, gaming portals, business applications, content delivery, ... have different Quality of Service (QoS) requirements depending on interaction patterns and time, the way that the service provider offers a given QoS is sealed with a contract: Service Level Agreement (SLA). This contract specifies thinks like the amount of guaranteed memory, CPU or response time among others, and also establishes rewards and penalties for accomplishing or violating such agreements.

SLA creation and negotiation is a very complex process and it is out of the scope of this project, but it is important for us to take it into account in our simulator, for this reason we suppose that the contract negotiation is done before the job arrives at the system. As a consequence of the negotiation we obtain some parameters that are supposed to be estimated from the negotiation and that give us an idea of which are the requirements of the job, allowing us to have a more accurate resource reservation.

### 1.2 Origin and Background

This degree project is developed within a grant from Ministerio de Educación y Ciencia for collaborating with the LSI department in the FIB at UPC. The collaboration consists on helping

Josep Lluís Berral during the current development of his doctoral (PhD) thesis [1]. This thesis is a multidisciplinar work joining two different research areas, autonomic computing and machine learning, directed by two professors of the Technical University of Catalonia, Jordi Torres from the *Departament d'Arquitectura de Computadors* and Barcelona Supercomputing Center, and Ricard Gavaldà from the *Departament de Llenguatges i Sistemes Informàics*. Apart from that, the master thesis developed by Ferran Julià [2] became an important reference because it is in this context where the simulator was developed at first. Given that the project is multidisciplinary, a broad survey is necessarily.

The main goal of Josep Lluís' thesis is to let a complex distributed cloud system manage itself, using intelligent and adaptive techniques though machine learning and data mining. The agent responsible of including this intelligence into the cloud will be an autonomous controller component, capable of obtaining the required knowledge model, predict the system status and apply a set of policies guided by utility functions, in order to improve the performance, stability, adaptability and robustness of the cloud system. For instance, if it predicts that there will be a SLA violation or some system failure it should act in consequence and try to avoid it if possible.

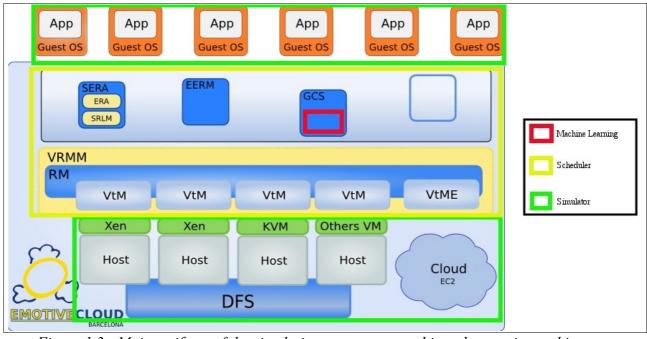

Thee Emotive framework [20] is developed by some research groups of the UPC and the Barcelona Supercomputing Center (BSC-CNS). EMOTIVE abstracts a Cloud architecture using different layers and provides users with basic primitives for supporting the execution of services (features for resource allocation and monitoring, data management, live migration, and checkpointing, etc.). This software will be very useful to meet the need of mine for data of the Josep Lluís controller. Unfortunately we do not have a 5000 hosts grid to play with. Furthermore, one of the pretensions of the Josep Lluís controller is to be tested in heterogeneous cloud systems which would not be solved by having just one grid. We will give more information related with the simulation and our pretensions by using a simulator in Section 2, 'Introducing simulation'.

Ramón Nou, as part of his doctoral thesis [3] studied the relation between the performance and energy consumption of one machine used as a test bed [4]. After he did that study he implemented a simulator called EEFSim (we will call it EEFSimV1) which could simulate the energy consumption of a specified cloud. One of the main goals of emotive is to manage one cloud system minimizing its energy consumption so the directors of the Josep Lluís' thesis decided that it could be possible to use this simulator as a testbed if some extensions were developed, as supporting Virtualization. That solved the infrastructure problem.

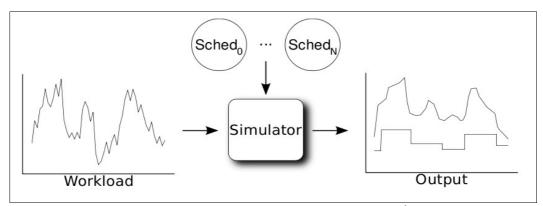

The responsible of developing this new version of the simulator (called EEFSimV2) was Ferran Julià. The main goal of the Ferran Julià master thesis [2] was to understand the low level behaviors that rule a virtualized data center in which the cloud runs over, and to use all that experience in developing a simulator that permits the improve of the resource scheduling techniques introducing innovative green policies. The architecture of EEFSimV2 permits the usage of an external entity, a scheduler, to manage its behavior. This architecture has three different parts (see Figure 1.1). The workload generator, the simulator and the scheduler. The workload generator module sends the jobs to scheduler's core module at the specified arrival time. The scheduler schedule the jobs according to some policy. Any scheduler can be plugged in with the appropriate interface. The simulator simulates the behavior of the specified cloud system according to the schedule decisions and collects all the execution information and prints out the execution's power consumption, scheduling and resource usages statistics.

Figure 1.1 - Architecture of the simulator<sup>1</sup>

As it can be observed, at first appearance it fits the needs of a testbed for Josep Lluís' thesis but as he progressed in his work he noticed that the capabilities of this simulator were too limited for his objectives. The main problem is that one of the major ambitions of Josep Lluís' thesis is to achieve good scheduling of heterogeneous workloads but EEFSimV2 was designed for other purposes so it does not provide much heterogeneity respect its workloads and cloud system specifications. At this moment it is enough to take into account that there is the need of endow EEFSimV2 with more heterogeneity with respect to the tests that it could previously simulate. That is the frame in which my degree project was conceived.

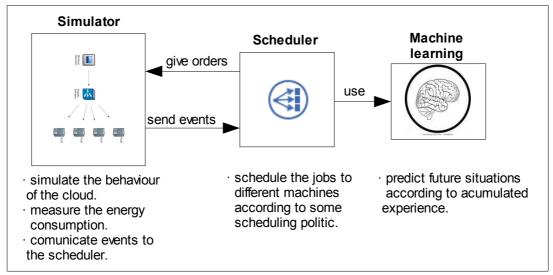

Before we get in detail into the simulator structure, let us take a look at which are the main artifacts that interact in the proposed solution:

- The simulator: It is responsible of performing all the actions demanded by the scheduler. It has all the entities that compose the cloud system. Its function is to simulate the behavior of the cloud system if the actions demanded by the scheduler are performed. Apart from that, it is responsible of providing information relative to the cloud system architecture to the scheduler and giving the data related with the execution such as energy consumption, occupation of the machines during the simulation, etc.

- The scheduler: It is responsible of giving orders to the simulator for scheduling its workload in the different hosts that compose the cloud system. Its scheduling policy can change over time. Another important fact is that it will use the data provided by machine learning elements of the autonomous controller developed by Josep Lluís Berral.

- The autonomous controller: Its responsibility is obtaining the required knowledge, model and predict the system status, and apply a set of policies guided by utility functions.

<sup>1</sup> Image obtained from [2]

Figure 1.2 - Main artifacts of the simulation context

This artifacts are mapped into the emotive architecture as follows.

Figure 1.3 - Main artifacts of the simulation context mapped into the emotive architecture

### 1.3 Motivation

The development of a degree project consist on developing some system demonstrating the knowledge and skills that you have acquired along the degree. I have gone one step beyond. Due to the fact that I have worked in a research environment I have not tried to just develop something based on my previous knowledge. Instead of that, I have tried to keep learning and improving my skills and as a result I have developed some extensions to a simulator which is really avant-garde and unique in the world.

This degree project becomes an opportunity to enforce my communicative and comprehensive skills. As I just said in the introduction I am working with a group of people from interdisciplinary areas of the academy. Furthermore, the main topics of the students with whom I am working are at the very state of the art: cloud computing, virtual machines management, data mining, machine learning and much more. Apart from that, the opportunity of working in a university department has given me the opportunity of seeing how does research work.

Thats the reason why I think that this project has given me experience in one of the fields that university studies does not usually treat (research). It is therefore at the same time a perfect ending for my degree and a perfect beginning to get used to work with a group of people in the research area.

### 1.4 Goals of the project

The main goals of this project are:

- To extend EEFSimV2 for increasing the heterogeneity of not only the workload executed by the cloud but also the declaration of the specifications of the machines that form the cloud. Special effort should be directed to provide a good testbed for the Josep Lluís' doctoral thesis.

- O To develop new modules of the simulator with a cohesive and extensible structure. This simulator is to be used by several research projects within the group so we can assume that it will be modified in the future. It is important to design every new module of the extensions providing the possibility of extending it in the future and with coherence. The maintenance and scalability of the simulator depends on these key features.

- o To redefine the format of some of the documents used for specifying some of the modules of the simulator to acquire a extensible and semantic model of specification.

### 1.5 Functional requirements of the project

To succeed with the goals of the project we agree that the simulator should be able to perform the next requirements:

### 1. Improve the representation of the CPU.

In order to improve the cohesion and scalability of the project we thing that is important to implement a new class to represent the CPU of the hosts that execute the workload of the cloud system. Apart from that we will improve the accuracy of the execution time of one application considering the characteristics related with the CPU of the machine where it is being executed.

### 2. Take into account the memory usage of one task.

This requirement aims to improve the heterogeneity of the workload executed during the simulation. Furthermore, taking into account the memory usage of one application will improve the accuracy of the simulator in respect to the way the resources of the machines are used and the implied time to attend these needs.

### 3. Take into account the usage of external devices of one task.

One of the bottlenecks during the execution time of one application is its usage of external devices as hard disks. The performance of one task could vary depending on its needs respect to that kind of resources. Apart from that, this kind of resources are limited so if more than one application attend to use it at the same time there must be a penalization at its execution time due to that they access sequentially to the device. That requirement will improve the heterogeneity of the workload as well.

### 4. Improve the network representation.

One of the final objectives of that simulator is that it could be used in a commercial environment. The heterogeneity of the different networks and equipments that compound a cloud system is huge. This is the reason why one of the improvements that we need to perform is to bring the possibility of declaring heterogeneous networks. Apart from that we should use its characteristics for calculating the time that is needed to transmit data over it. That will provide more realism at the simulation results.

### 5. Improve the way that some specifications are provided to the simulator.

In order to improve the maintenance tasks of that project and facilitate its scalability is very important to use an appropriate format to specify the configuration files that are used to specify some of the characteristics that are used during the execution of the simulation.

### 1.6 Document organization

The document is structured as follows: Chapter 2 summarizes the relevant features of simulation and describes some of relevant types of simulation that exist. Chapter 3 exposes the work related with the technology choice for develop the simulator. In Chapter 4 we give all the relevant information related with the selected technology: Omnet++. Chapter 4 summarizes the state of the simulator before performing the extensions presented in this degree project. Chapters 6, 7, 8, and 9 expose the work developed for each of the extensions. Chapter 10 give all the information related with the final validation of the simulator, after developing the extensions. In Chapter 11 we describe the schedule and the cost of the project comparing them with the estimation that we did after we began with the development of this project. Finally Chapter 12 collects all my conclusions.

In this section we will justify the decision of using a simulator instead of executing the controller in a real cloud system. First of all we will briefly explain what does the simulation consist on and explain why it is appropriate for use it as a testbed. At the end of this section we will describe the different kinds of existing simulations and their main characteristics.

Simulation in general is to pretend that one deals with a real thing while really working with something that behaves like it. From now on, when the term 'simulation' is used, it refers to a computer simulation, which means an attempt to model a real-life or hypothetical situation on a computer so that it can be studied to see how the system works. There is a huge variety of scenarios that have been studied by simulation. Simulation has become a useful part of modeling many natural systems in physics, chemistry and biology, and human systems in economics and social science (the computational sociology) as well as in engineering to gain insight into the operation of those systems. A good example of the usefulness of using computers for simulation can be found in the field of network traffic simulation. In such simulations, the model behavior will change each simulation according to the set of initial parameters assumed for the environment.

Any real-life system studied by simulation techniques is viewed as a system. The following features of a system are of interest:

- 1. Environment: Each system can be seen as a subsystem of a broader system.

- 2. Interdependency: No activity takes place in total isolation.

- 3. Sub-systems: Each system can be broken down to sub-systems.

- 4. Organization: Virtually all systems consist of highly organized elements or components, which interact in order to carry out the function of the system.

- 5. Change: The present condition or state of the system usually varies over a long period of time.

Some of the variables of the system that are of paramount importance are those used to define the status of the system. Such variables are known as status variables. These variables form the backbone of any simulation model. At any instance, during a simulation run, one should be able to determine how things stand in the system using these variables. Obviously, the selection of these variables is affected by what kind of information regarding the system one wants to maintain.

There are a lot of reasons that can justify using a simulation: security, testing, training, teaching, etc. In general, there are two main reasons to use a simulator. The first one is to predict something before it happens, for instance, weather prediction uses current weather conditions as input into mathematical models of the atmosphere to predict the weather. Although the first efforts to accomplish this were done in the 1920s, it was not until the advent of fast computers and computer simulations that it was feasible to did this with advantage. The second reason is to save money: flying with a simulator is safer and cheaper than building the real airplane. Often it is very costly, dangerous and often impossible to make experiments with real systems. Provided that models are adequate descriptions of reality (they are valid), experimenting with them can save money, suffering, and even time.

The controller that is being designed in Josep Lluís' thesis must interact with a cloud system, that means a cluster of hundreds of different machines. Furthermore the behavior of the controller should be tested in different kinds of clouds. Besides the fact that it is very difficult to find such amount of hardware for research and development, most of times it will not be acceptable to have so many machines, with all the maintenance work and the energy consumption that it involves, only for testing. This kind of infrastructures are usually only used in production systems and using them has an important economic cost.

We though that a simulator would be a suitable and effective solution for our problems, giving us the possibility to reproduce our solutions in real-like data-centers and validate our solutions. In a simulation we could use the data that we modeled from the real system avoiding all the complexity of the real cloud. For instance if we want to know how many time is being executed some application in the cloud system but there is no need of reproducing its output we can just keep it in the system without executing any code. A well designed simulator can provide results accurate enough for our proposals. Furthermore a simulator usually can run on a simple machine and often reduce the test time several times, so that would save lots of energy and time.

### 2.1 Types of simulation

Computer models can be classified according to several independent pairs of attributes, in this section we will describe the different types of simulations that exist considering those attributes. Some of the definitions in this chapter are taken from [25].

### Continuous vs discrete simulation

In some simulations the status of the system changes each time an event occurs. During the time that elapses between two successive events, the system status remains unchanged. In view of this, it suffices to monitor the changes in the system status. Jumping in the time line from one event to the next one optimizes the execution time of the simulation. This kind of simulation is called discrete event simulation

The opposite kind of simulation is the continuous simulation. Continuous simulation concerns the modeling over time of a system by a representation in which state variables change continuously with respect to time. For example, the water level in a reservoir with given in and outflows may change all the time. In such cases "continuous simulation" is more appropriate, although discrete event simulation can serve as an approximation.

### Stochastic vs deterministic simulation

Deterministic models are models which do not contain the element of probability. Examples are: linear programming, non-linear programming and dynamic programming. Stochastic models are models which contain the element of probability. Examples are: queueing theory, stochastic processes, reliability, and simulation techniques.

In simulation, random numbers are used in order to introduce randomness in the model. For instance, if we are able to observe the operational times of a machine over a reasonably long period, we will find that they are typically characterized by a theoretical or an empirical probability

distribution. Therefore, in order to make the simulation model more realistic, one should be able to randomly numbers that follow a given theoretical or empirical distribution.

Simulation techniques rely heavily on the element of randomness. However, deterministic simulation techniques in which there is a no randomness, are not uncommon. Simulation techniques are easy to learn and are applicable to a wide range of problems.

Transient state vs. steady-state simulation

In general, a simulation model can be used to estimate a parameter of interest during the transient state or the steady state.

Let us assume that one is interested in obtaining statistics pertaining to the number of broken down machines of one system. The simulation starts by assuming that the system at time zero is at a given state. This is known as the initial condition. Evidently, the behavior of the system will be affected by the particular initial condition. However, if we let the simulation run for a long period, its statistical behavior will eventually become independent of the particular initial condition. In general, the initial condition will affect the behavior of the system for an initial period of time, say T. Thereafter, the simulation will behave statistically in the same way whatever the initial condition. During this initial period T, the simulated system is said to be in a transient state. After period T is over, the simulated system is said to be in a steady state.

One may be interested in studying the behavior of a system during its transient state. In this case, one is mostly interested in analyzing problems associated with a specific initial starting condition. This arises, for example, if we want to study the initial operation of a new plant. Also, one may be forced to study the transient state of a system, if this system does not have a steady state. Such a case may arise when the system under study is constantly changing (dynamic system).

Typically, a simulation model is used to study the steady-state behavior of a system. In this case, the simulation model has to run long enough so that to get away from the transient state. That means that a steady-state simulation is one in which the measures of performance are defined as limits as the length of the simulation goes to infinity. There is no natural event E to terminate the simulation, so the length of the simulation is made large enough to get "good" estimates of the quantities of interest.

### 2.2 Related concepts

### **Emulation**

In the context of software, an emulator reproduces the behavior of one system on another. It executes, or strives to execute, the same programs as the "original" system, and produces the same results for the same input. It is important that the user of an emulator is not supposed to care *how*. Although a simulation model and an emulation model may look to all intents and purposes the same, and may be built largely with the same building blocks, there are significant differences in usage and operation.

Simulation models are used to test and develop different solutions in order to arrive at a best solution, based on an accepted set of pre-defined metrics. Simulation often provides the impartial judge between experience and new ideas, and allows the user to demonstrate functionality and results in a cost-effective and flexible environment. Simulation results help define the physical layout of a system, its operating limits and its control system. Models are used as a basis for extensive experimentation, often using automatic procedures to determine optimal or robust solutions.

Emulation models are used in a much more precisely defined way; in order to test the operation of the control system under different system loading conditions, and as a risk-free means of training system operators and maintenance staff. Emulation models are not used for experimentation in the same way that simulation models are; they are unsuited to this function as they often execute only in real time.

The emulation model reflects more precisely the system that will be implemented, and as such, can be used to carry out a constrained series of verification procedures to ensure the performance or reaction of the control system. Systems exist to automate the execution of these tests, and to run them in parallel in order to carry out more tests than would be practical on the real system.

#### Virtualization

A common mistake that people not familiar with virtualization make is that they think virtualization is similar to emulation or simulation. The fact of the matter is virtualization is neither emulation or simulation. In Section 1.1.3, 'About Virtualization and Virtual Machines (VM's)', we provide a detailed description of what does virtualization consist on.

There are several features that make an ideal simulation package. Some are properties of the package, such as support, reactivity to bug notification, interface, etc. Some properties come from the user, such as their needs, their level of expertise, etc. For these reasons asking which package is the best one has no use. The first question to be asked is for what purpose you need the software. In this case is for an student-project or research so the used simulator must be robust and enough customizable to permit the implementation of all the capabilities of the simulation purpose. Apart from this, it is also important what it provides: easy input, allow some programming, good framework for creating customized modules, message exchange and supports a discrete, stochastic and transient simulation.

As we said in the introduction, we began our work from a existing simulator (EEFSimV2) which used one simulation package called Omnet++. If we had decided to change the simulation environment it would involve some time for rewriting EEFSimV2 to the new one, but it does not mean that we did not have to contemplate this alternative. In fact, if we had found some simulation package that fits better with our purposes it would involve saving a lot of time in the future.

In this section we describe the alternatives that we considered for developing this project before choosing that Omnet++ is the better one. There are many simulators designed for simulating a network and its behavior. In this section we will describe the main simulators that can be found currently and some of their advantages and disadvantages.

#### 3.1 COTSon

COTSon [19] is a simulator framework jointly developed by HP Labs and AMD. The goal of COTSon is to provide fast and accurate evaluation of current and future computing systems, covering the full software stack and complete hardware models. It targets cluster-level systems composed of hundreds of commodity multicore nodes and their associated devices connected through a standard communication network. COTSon adopts a functional-directed philosophy, where fast functional emulators and timing models cooperate to improve the simulation accuracy at a speed sufficient to simulate the full stack of applications, middleware and Oss.

One of the advantatges of COTSon's functional simulator is that it uses AMD's SimNowTM simulator. The SimNow simulator functionally models most of the existing hardware that can be found on an AMD system. Other companies and partners, including HP, developed their own functional devices for the SimNow platform. Full-system simulation means that all aspects of the system can be analyzed by the simulator. So it can provide a complete accuracy for the devices that it provides.

Another important fact is the methodology that it uses to balance the performance and the accuracy of its simulations. COTSon makes its functional simulator run for a dynamically set interval. This produces a stream of events which are sent to the respective CPU timing models. At the end of the interval, using the metrics from the CPU models (which include the whole memory hierarchy) a new IPC (instructions per cycle) is fed back to the functional simulator. By selecting different

interval sizes, the user can turn the accuracy vs speed relation. Moreover, COTSon's approach couples very well with sampling, enabling the user to select just those intervals which are considered representative or "interesting."

But COTSon has an important drawback for our purposes: in order to simulate a whole cluster, COTSon instantiates several COTSon node simulators, potentially in different host machines. Each of them is a stand-alone application which communicates with the rest via a network mediator. The network mediator acts as a functional network switch, directing network packets to the appropriate COTSon node destination. So it does require a heavy infrastructure, one of the problems we want to avoid.

Despite that, it can be useful when we need some reference, for tuning some of the characteristics of the different devices that we are going to use, such as memory latency or time delay of migrating a virtual machine.

### 3.2 PARSEC

PARSEC [10] (for PARallel Simulation Environment for Complex systems) is a C-based discrete-event simulation language. It adopts the process interaction approach to discrete-event simulation. An object (also referred to as a physical process) or set of objects in the physical system is represented by a logical process. Interactions among physical processes (events) are modeled by timestamped message exchanges among the corresponding logical processes.

One of the important distinguishing features of PARSEC is its ability to execute a discrete-event simulation model using several different asynchronous parallel simulation protocols on a variety of parallel architectures. Although that it is not important from our point of view. The purpose of the simulator is to execute the behavior of a cloud network and collect the information that will be used to schedule the jobs minimizing the energy consumption of the devices without penalizing the performance so much.

Furthermore, it is reported in [2] that there is not much documentation about how to use it. Aparently it is not very popular and not supported by any big enterprise or community.

#### 3.3 NS2

NS2 [11] is a discrete event simulator targeted at networking research. Ns provides substantial support for simulation of TCP, routing, and multicast protocols over wired and wireless (local and satellite) networks.

It is an object oriented simulator, written in C++, with an OTcl interpreter as a frontend. The simulator supports a class hierarchy in C++ (also called the compiled hierarchy), and a similar class hierarchy within the OTcl interpreter (also called the interpreted hierarchy). The two hierarchies are closely related to each other; from the user's perspective, there is a one-to-one correspondence between a class in the interpreted hierarchy and one in the compiled hierarchy. The root of this hierarchy is the class TclObject. Users create new simulator objects through the interpreter; these objects are instantiated within the interpreter, and are closely mirrored by a corresponding object in

the compiled hierarchy.

The interpreted class hierarchy is automatically established through methods defined in the class TclClass. user instantiated objects are mirrored through methods defined in the class TclObject. There are other hierarchies in the C++ code and Otcl scripts; these other hierarchies are not mirrored in the manner of TclObject.

In this case the official website [11] gives more documentation but the purpose of that simulator is more focused in the study the network behavior instead of the hole system.

### 3.4 VnetUML

VNUML (Virtual Network User Mode Linux) is an open-source general purpose virtualization tool designed to quickly define and test complex network simulation scenarios based on the User Mode Linux (UML) virtualization software. VNUML is a useful tool that can be used to simulate general Linux based network scenarios. It is aimed to help in testing network applications and services over complex testbeds made of several nodes (even tenths) and networks inside one Linux machine, without involving the investment and management complexity needed to create them using real equipment.

VNUML tool is made of two main components: the VNUML language used for describing simulations in XML; and the interpreter of the language (vnuml command), that builds and manages the scenario hiding all UML complex details to the user.

A typical working cycle using VNUML is made up of the following phases:

- **Design phase**. First of all, the user must design a simulation scenario. For that, several aspects have to be considered in advance: the number of virtual machines, the topology (network interfaces in each machine and how they are connected), what processes each virtual machine will execute, etc. Note that the whole simulation runs in the same physical machine (named host).

- Implementation phase. Once the simulation scenario has been designed, the user must write the source VNUML file describing it. This is an XML file. There are three kinds of tags in VNUML: structural tags, with few or no semantics; topology tags, used to describe the topology; and simulation tags, used to describe simulation parameters and commands.

- **Execution phase**. Once the user has written the VNUML file, he must run vnumlparser.pl against it in order to build and manage the simulation scenario.

As it can be observed it has some aspects in common with the simulator to be developed: configuration of the devices and topology in XML file and only needs one host. But it does not support much customization, and while it offers several tags they are not enough enough for the purpose of our simulator. Furthermore it only supports Linux and this could penalize the heterogeneity of the cloud system to simulate.

### 3.5 Netsim

NetSim is a versatile tool to simulate and analyze computer networks. With comprehensive

modeling facility, detailed performance reports and enhanced protocol analytics, NetSim offers unmatched power and flexibility. It is very graphic and has some libraries that simulates the behaviour of some protocols used in the networks communications as Gigabit Ethernet and Wireless LAN 802.11 a and g.

Although as it happened with VnetUML, it does not support much customization and the purpose of this simulation is more in a academic line, which means that it is used for giving a practical and graphical point of view about the behavior and metrics of a different network configurations. Furthermore it is proprietary software which means that it would increase the cost of this project and its code is private. It is important to highlight that we did not discard it because it is proprietary software. We discarded it because it does not support much customization.

#### 3.6 Omnet++

OMNeT++ [12] is an object-oriented modular discrete event network simulation framework. OMNeT++ itself is not a simulator of anything concrete, but it rather provides infrastructure and tools for writing simulations. One of the fundamental ingredients of this infrastructure is a component architecture for simulation models. Models are assembled from reusable components termed modules. Well-written modules are truly reusable, and can be combined in various ways. Modules communicate through message passing.

It has all the features we were looking for: easy input, allow some programming, good framework for creating customized modules, message exchange and supports a discrete, stochastic and transient simulation. As it is the selected framework we will give more information about its features and how does it work in Section 4, 'Omnet++'.

### 3.7 Conclusion

Omnet++ is clearly the best of these simulators for our purposes. Omnet++ offer a really customizable environment because it is implemented in C++. Furthermore in the official website [12] we can find a lot of documentation and interesting samples about how to use it.

Other simulation tools like NS2, NetSim and PARSEC are centered in other purpose than creating a customized simulator. NS2 and NetSim are designed for showing the behavior of a network.

VnetUML and COTSON are limited but they can be useful if need to take some measures about the time latency of some of the devices.

4 Omnet++

### 4 Omnet++

As Omnet++ is the selected framework to implement the simulator we should describe its behavior and functionalities. In this section we make emphasis on those aspects of the simulator that will be needed to follow the implementation details of the extensions that we developed during the realization of that project.

### 4.1 General description

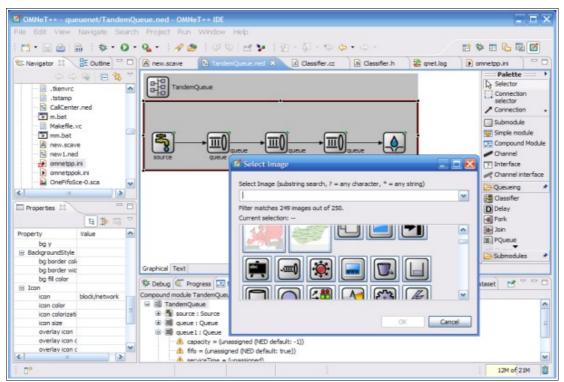

OMNeT++ [12] is an extensible, modular, component-based C++ simulation library and framework, with an Eclipse-based integrated development environment (IDE), with which we are familiarized, and a graphical runtime environment. It is a discrete event simulation environment. Its primary application area is the simulation of communication networks, but because of its generic and flexible architecture, is successfully used in other areas like the simulation of complex IT systems, queueing networks or hardware architectures as well.

OMNeT++ provides a component architecture for models. Components (modules) are programmed in C++, then assembled into larger components and models using a high-level language (NED). Reusability of models comes for free. OMNeT++ has extensive GUI support, and due to its modular architecture, the simulation kernel (and models) can be embedded easily into your applications.

Although OMNeT++ is not a network simulator itself, it is currently gaining widespread popularity as a network simulation platform in the scientific community as well as in industrial settings, and building up a large user community.

The screenshots showed in Figure 4.1 and Figure 4.2 are an example of the two views of a NED component. The first one shows how the modules and submodules can be showed into a graphical and intuitive mode. The second one shows the code behind the module.

OMNeT++ is free for academic and non-profit use, and it is rapidly becoming a preferred simulation platform in the scientific community worldwide.

This framework offer all the features that the simulator needs. The fact that the components are programmed in C++ makes easy to create and parse the xml documents that are used for specifying the workload and the topology of the network. Furthermore high-level language (NED) make it easier to describe the modules. Another important fact is that it had Eclipse-based IDE which is very popular and intuitive. In addition it have two ways of execute the simulation, the first one is with a graphical environment which shows all the messages exchange between the different modules and all the events that are produced during the execution. This one is the best one to debug the behavior of the network. The second one is executed in a shell. This one is faster and is the best alternative to run an execution when you want to collect all the data produced on it.

Figure 4.1 - Graphical NED editor<sup>2</sup>

```

- -

*Terminal.ned

*new1.ned 🔀

^ =

simple Node {

gates:

inout port;

network ExampleNetworkModule extends CallCenter {

parameters:

CallCenter - compound-module type

ExampleNetworkModule - compound-module type

Host - compound-module type

types: // defines locally used ch

RingQueue - compound-module type

channel PPPLink {

SimpleQueue - compound-module type

parameters:

TandemQueue - compound-module type

@display(c="red");

Terminal - compound-module type

like - keyword

double delay = 10us;

0

undefinedError = 23;

1:

module HostX extends Host {

double linkspeed;

};

submodules:

host[100]: HostX;

connections:

host[0].pppPort++ <--> PPPLink <--> host[1].pppPort++;

<

>

Graphical Text

```

Figure 4.2 - NED source editor<sup>3</sup>

<sup>2</sup> Image obtained from http://www.omnetpp.org/home/screenshots.

<sup>3</sup> Image obtained from http://www.omnetpp.org/home/screenshots.

4 Omnet++

### 4.2 How it works

An OMNeT++ model consists in the following parts:

- NED language topology description(s) (.ned files) which describes the module structure with parameters, gates etc. NED files can be written using any text editor, but the OMNeT+ + IDE provides excellent support for two-way graphical and text editing.

- Message definitions (.msg\_files). You can define various message kinds and add data fields to them. OMNeT++ will translate message definitions into full-fledged C++ classes.

- Simple modules sources. They are C++ files, with .h /.cc suffix.

Despite that, there is a special file with .ini extension where the parameters of the different modules can be set.

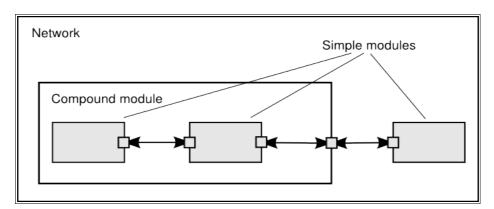

An OMNeT++ model consists in modules that communicate using message passing. The active modules are termed simple modules; they are written in C++, using the simulation class library. Simple modules can be grouped into compound modules and so forth; the number of hierarchy levels is not limited. The whole model, called network in OMNeT++, is itself a compound module.

*Figure 4.3 - Simple and compound modules*<sup>4</sup>

Modules communicate with messages which, in addition to usual attributes such as timestamp, may contain additional data. Simple modules typically send messages via gates, but it is also possible to send them directly to their destination modules.

Modules can have parameters. Parameters can be assigned either in the NED files or the configuration file omnetpp.ini. Parameters may be used to customize simple module behavior, and for parameterizing the model topology.

When the program is started, first of all it reads all NED files containing the model topology and then it reads a configuration file (usually called omnetpp.ini). This file contains settings that control how the simulation is executed, values for model parameters, etc.

<sup>4</sup> Image obtained from http://www.omnetpp.org/doc/omnetpp41/manual/usman.html.

### 5. Starting point of the simulator

As said in the introduction, the simulation presented in this degree project is an extension of the simulator designed in Ferran Julià masther thesis [2], called EEFSimV2. In this section we will explain the main characteristics of EEFSimV2 with a special effort to explain all the underlying technical background concepts. Then we will describe all the modules that compose that first version one by one.

### 5.1 EEFSimV2

This simulator have three main modules: the workload generator, the pluggable scheduler and the grid of hosts that compound the cloud system.

Figure 5.1 – Internal architecture of the simulator<sup>5</sup>

We will describe these modules with detail in Section 5.3, 'Modules', but let us take a first look at the functionalities of each of these modules.

The workload generator is the module that creates the workload that is going to be executed. All the jobs that are going to be executed into the cloud are specified in one file. The workload generator parses that file and generates the corresponding jobs to be dispatched to the pluggable scheduler using messages.

The pluggable scheduler is the module that represents the scheduler which is going to take the decisions about how are scheduled the different VM's that are created for attending each job. It is important to highlight that the scheduler and the pluggable scheduler are not the same. As we say in the introduction, the scheduler is external to the simulator. That module communicates with the scheduler by remote procedure calls, an inter-process communication technology that allows a computer program to call a subroutine or procedure to be executed in another address space (usually

<sup>5</sup> Image obtained from [2]

on another computer on a shared network). Basically it performs three kind of calls: one to notify to the scheduler that a host is added to the grid (used when the host modules are being initialized), one for requesting the creation of a new VM to allocate some job, and a third one for requesting which operations are going to be performed by the simulator (adding, migrating, removing or chekpointing some VM).

The PC are the unique compound module of the EFFSimV2. It has two modules. The PowerSupply which is responsible for collecting the energy consumption of the host and the HyperScheduler which represents the hypervisor that manages the VM's that are going to be executed by the host. In the next section we will explain some important aspects related to the virtualization mechanism and its internal behavior.

#### 5.2 Virtualization

In order to understand better the challenges that involve the creation of a virtualized data center simulator, in this section we will introduce some essential internals of virtualization systems. Notice that these mechanisms play a key role in the structure as they determine the way real CPU is assigned to virtual CPUs and have a great influence on the overall behavior.

The finality of EEFSimV2 was to test some parts of a real Cloud management middleware called emotive [6], developed within J.Torres' group. The emotive framework is built on the Xen [7] virtualization system, so the simulator has to reproduce some of the Xen's internal mechanisms and low level behaviors.

Xen uses a virtualization technique called paravirtualization, which requires the partial modification of the guest operating system. As the guest O.S. is modified, some special operations call hypervisor instead of calling the hardware, and it is the hypervisor who manages the real resources and schedule them among the virtual hosts.

There is a special host in the system, called "dom0" (domain 0), that is always running in the host and that have some special operations that permit controlling the hypervisor. This special module in the O.S. is in charge of creation, destruction and migration of virtual machines.

|   | Apps             | Apps         | Apps         |            |  |  |

|---|------------------|--------------|--------------|------------|--|--|

|   | Guest OS         | Guest OS     |              | Management |  |  |

| Ш | Guest OS Mod     | Guest OS Mod | Guest OS Mod |            |  |  |

|   | Hypervisor (VMM) |              |              |            |  |  |

|   | Hardware         |              |              |            |  |  |

Figure 5.2 – Xen architecture<sup>6</sup>

<sup>6</sup> Image obtained from [2].

The CPU scheduler of EEFSimV2 is based on the Credit Scheduler [13]. The most important to notice from the credit scheduler is the Capabilities and Weight operation modes. With these parameters we can tune the scheduler behavior giving more ore less execution time or priority to the different virtual machines.

The scheduler assigns real CPU to virtual CPUs maintaining the same proportionality than have the "weight" parameter for the virtual machines. Each parameter is set at virtual machine level, so all virtual CPUs of the same virtual machine have the same weight parameter as it happens with the capability parameter. For example, if we have 2 virtual machines with 1 virtual CPU for each one running at the same host, if both have the same weight the real CPU will be shared at 50% for both, but if one have a weight value of 20 and the other of 80, the real CPU will be 20% for the former and 80% for the second. Notice that what is important here is the relation among the two weight values, nor the real value of them, instead of 20 and 80 values we could have 40 and 160 and the result would be the same 20%-80%. The "Capability" parameter fixes the amount of real CPU that one virtual machine can use, so despite of what we calculated from the weight parameter, if the real amount of CPU that is allocated for the virtual machine is grater than the capability the virtual machine will not have more real CPU than the capability. With these two parameters we can adjust dynamically the real CPU that we allocate for each virtual machine thus control the behavior of our system.

#### 5.3 Modules

The modules are the backbone on the simulation in omnet++. In this section we will describe the modules that compose EEFSimV2. We highlight that the general behavior and the main modules of that compose that simulator had been described in Section 5.1, 'EEFSimV2'. This section can be skipped on a first reading.

### 5.3.1 WorkloadGenerator

This module is the one that generates all the workload that will be executed by the network. For doing it in the most practical and extensible way it is generated from a text file. This allows having different kinds of workload in different files. To define the path of the file that contains the specific workload that is going to be used in the execution, this module has a parameter called workload.

The format of the file that contains the workload is as follows:

| #startTime<br>26399<br>26463 | name<br>app22<br>app200 | duration<br>2217<br>514 | userCpu<br>200<br>200 | userMem<br>128<br>128 |  |

|------------------------------|-------------------------|-------------------------|-----------------------|-----------------------|--|

|                              |                         |                         |                       |                       |  |

As can be observed, for each job it defines start time, the name of the application configuration file which should be specified with the same name with a .load extension (for instance, app22.load), duration (in seconds), and user cpu and memory that it requires. The application configuration file must be defined too. It has the following format:

| <pre>#startTime 0</pre> | cpuUsage | memUsage | SLA |

|-------------------------|----------|----------|-----|

|                         | 200      | 128      | 1.2 |

|                         |          |          |     |

The start time represents the time (during the execution of the job) in which the corresponding cpu, memory usage and SLA are valid. So, with this format, for each job, there can be intervals with different cpu and memory usage and SLA.

The WorkloadGenerator loads all the information described in those files and generates entities objects of type WorkloadComponent that are sorted in a queue called vwc (vector workload component). For this moment its enough to understand that a WorkloadComponent represents a job. For more information about this entity refer to Section 5.5.1, 'WorkloadComponent'.

### **5.3.2 PlugableScheduler**

This module is the one that manages communication with the external scheduler which gives the directives to follow in the simulation. For this reason it has some functions that serves as a feed back between the state of both schedulers (the external one and this one).

In this module is where the configuration of the network is performed. It uses two parameters to set the configuration of the computers of the network: the hostConfig and the specsDir. The first one specifies the path of the file that contains the specification of the type of each computer. The format of this file is as follows:

```

#type descriptor

pctinet

...

```

There is one of these descriptors for each PC. This descriptor links to another file. This file can be found in the path setted in the specsDir attribute. The format of this file is:

| #CPUs | <pre>freq Memory(GB)</pre> | boot | migrationIn | migrationOut | IdleBattage | bootPower |

|-------|----------------------------|------|-------------|--------------|-------------|-----------|

| 4     | 3000 4                     | 20   | 7           | 3            | 230         | 275       |

As it can be observed, for each PC we have the following descriptors: its number of CPU's, the frequency of its CPU's, the total amount of RAM memory, the penalty of booting up the machine and migrating in or out some virtual machine (all of them in seconds), and its energy consumption when it is in a idle or booted state.

For the moment, this module is connected to all the PC's that from the cloud which in this version is a grid of computers. This means that there is no possibility of describing different network topologies. Across these connections, this module establishes communication with all the PC's and schedule the workload generated by the WorkloadGenerator.

### 5.3.3 PC

This is a composite model. So its behavior is described more precisely in the next sections, when the submodules that compose it are described. As a first approximation we can analyze the submodules: a PowerSupply and HyperSched. The first one is the responsible of collecting data referred to the energy consumption of the PC. The second one is the responsible of manage and schedule all the virtual machines that are being executed in the PC.

The HyperSched is connected to the PowerSupply. Furthermore, the input and output of the PC are connected to the HyperSched.

### 5.3.4 HyperScheduler

This model represents the hypervisor of the physical machine. It is the responsible of scheduling the virtual machines that are being executed in the PC. Every virtual machine consumes some of the resources (like CPU, memory,...) of the computer. This module computes the proportion of real CPU that is assigned on each of its virtual machines; in the last paragraph of Section 5.2, 'Virtualization', there is a detailed description about how is it done. Every time quantum, HyperSched calculates the amount of CPU that is consumed and sends it to PowerSupply for taking it into account when computing the energy consumption of the device.

As a virtual machine manager, it is responsible of creating, booting, migrating and destroying its virtual machines. The module that represents a virtual machine is LocalScheduler. LocalScheduler's are created dynamically during the simulation so they are not initialized with parameters specified in the '.ini' file, unlike PCs. Of course, there is a connection between the HyperSched and all the virtual machines that it is executing.

### 5.3.5 PowerSupply

As it was anticipated in Section 5.3.3, 'PC', this is one of the submodules of the composed module PC and it serves to calculate the consumption of the PC. It is computed having two parameters into account, the first one is the number of CPU's that are being used and the second one is the global CPU usage. This amount of consumed power is calculated every quantum of HyperScheduler so it is not an estimation, it is an exact figure. This module is directly related with [4].

Observe that it is one of the modules that will need to be changed in the future work, because it does not take into account consumption of the memory and other devices.

### 5.3.6 LocalScheduler

This module represents a virtual machine that is being executed in a HyperScheduler. As it is said in Section 5.3.4, 'HyperScheduler', the HyperScheduler schedule and manage the virtual machines (LocalScheduler's). The main task of this module is to manage and schedule all the jobs that are being executed in this virtual machine. For simulating the execution of the jobs, we will follow an

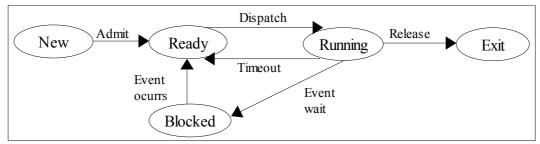

abbreviation of the model that use the operating systems: the five-state process model.

Figure 5.3 – The five-state process model

As we can observe in Figure 5.4, when a job begins its execution, it competes with the other jobs for the resources of the virtual machine. The mechanism used by the operating system for giving the sensation that all the jobs are executed at once is separateing the elapsed time executing the different programs in quantums. One quantum is the period of time that a process is allowed to run uninterruptedly. The scheduler is run once every time slice to choose the next process to run. For implementing that model, we need two different queues: one for the processes that are running and other one for the processes that are blocked. At every quantum of the execution, the processes that are in the running queue are executed and then are swapped with the next ones in the blocked queue.

### 5.4 Messages

In OmNet++, when a module has to communicate something to other modules it has to do it in two steps: the first one is to have a gate that connects it to the receiver module, the second one is to send it a message. So, the messages are used for communication between modules. They can be customized for transporting the required data. In this section we will describe the messages that are used in EEFSimV2.

### 5.4.1 SimMessage