Helsinki University of Technology, Electronic Circuit Design Laboratory

Report 40, Espoo 2005

# Integrated Radio Frequency Synthesizers for Wireless Applications

Rami Ahola

Dissertation for the degree of Doctor of Science in Technology to be presented with due permission of the Department of Electrical and Communications Engineering for public examination and debate in Auditorium S4 at Helsinki University of Technology (Espoo, Finland) on the 1<sup>st</sup> of April, 2005, at 12 o'clock noon.

Helsinki University of Technology Department of Electrical and Communications Engineering Electronic Circuit Design Laboratory

Teknillinen Korkeakoulu Sähkö- ja tietoliikennetekniikan osasto Piiritekniikan laboratorio Distribution:

Helsinki University of Technology

Department of Electrical and Communications Engineering

Electronic Circuit Design Laboratory

P.O.Box 3000

FIN-02015 TKK

Finland

Tel: +358 9 4512271

Fax: +358 9 4512269

Copyright © 2005 Rami Ahola

ISBN 951-22-7563-5 ISSN 1455-8440

Otamedia Oy

Espoo 2005

#### **Abstract**

This thesis consists of six publications and an overview of the research topic, which is also a summary of the work. The research described in this thesis concentrates on the design of phase-locked loop radio frequency synthesizers for wireless applications. In particular, the focus is on the implementation of the prescaler, the phase detector, and the chargepump.

This work reviews the requirements set for the frequency synthesizer by the wireless standards, and how these requirements are derived from the system specifications. These requirements apply to both integer-N and fractional-N synthesizers. The work also introduces the special considerations related to the design of fractional-N phase-locked loops. Finally, implementation alternatives for the different building blocks of the synthesizer are reviewed.

The presented work introduces new topologies for the phase detector and the chargepump, and improved topologies for high speed CMOS prescalers. The experimental results show that the presented topologies can be successfully used in both integer-N and fractional-N synthesizers with state-of-the-art performance.

The last part of this work discusses the additional considerations that surface when the synthesizer is integrated into a larger system chip. It is shown experimentally that the synthesizer can be successfully integrated into a complex transceiver IC without sacrificing the performance of the synthesizer or the transceiver.

**Keywords:** analog integrated circuit, frequency synthesizer, phase-locked loop, CMOS, BiCMOS, wireless communication, radio transceiver, prescaler, phase detector, chargepump, integer-N, fractional-N

#### **Preface**

The work for this thesis was carried out in the Electronic Circuit Design Laboratory of Helsinki University of Technology during 1997-2001, funded by the Technology Development Centre of Finland and Nokia Mobile Phones. The financial support from the Nokia Foundation and the Foundation of Electronics Engineers in Finland is also gratefully acknowledged. During 2000-2001, I also had the privilege to participate in the Graduate School of Electronics, Telecommunications and Automation (GETA), which partially funded the work.

Completing this thesis hasn't been an easy task. As I moved to industry full time in April 2001, I thought that the remaining work for the thesis would be a walk in the park. It wasn't. Finding the motivation and energy to complete the work during evenings and weekends has been a real burden. It has taken a lot of support from colleagues, friends, and especially family to get this work done. I am grateful to you all for that.

I would like to thank my supervisor, Professor Kari Halonen, for the possibility to work on this thesis very independently. His patience with the very slow last phase of the work is also greatly appreciated. I also warmly thank Prof. Mourad El-Gamal and Prof. Timo Rahkonen for reviewing my thesis and for their valuable comments and suggestions.

Thanks belong to all the staff of the laboratory for making it an effective and fruitful research community, and also a pleasant workplace. My colleagues at Spirea deserve thanks for significantly broadening my view of IC design.

Big thanks to all of my friends for keeping me busy with other things. When lacking motivation for writing, there was always something else to do. Sometimes the lack of motivation might even have been a consequence of having something else to do. Whichever way it was, thank you for standing by me.

My parents, Marketta and Jorma, deserve my gratitude for supporting me throughout my life. Curiosity for everything, a positive look at life, and the will to complete things I've started are only a few of the good things I've learned from you.

Finally, my warmest thanks to my dear wife Essi. Without your support I would never have finished this work. Thank you for sharing both the good and the difficult moments with me.

Rami Ahola Helsinki, April 2005

## **Table of contents**

| A | bstract                                       |                                   | i   |

|---|-----------------------------------------------|-----------------------------------|-----|

| P | reface                                        |                                   | iii |

| T | able of con                                   | ntents                            | v   |

| S | ymbols and                                    | d abbreviations                   | vii |

| L | ist of publi                                  | ications                          | x   |

| S | ummary of                                     | f publications                    | xi  |

| 1 | Introdu                                       | ection                            | 1   |

|   | 1.1 Backg                                     | ground                            | 1   |

|   | 1.2 Resea                                     | arch contribution                 | 2   |

|   | 1.3 Organ                                     | nization of the thesis            | 2   |

| 2 | Freque                                        | ncy synthesizers in radio systems | 3   |

|   | 2.1 Radio                                     | transceiver architectures         | 3   |

|   | 2.2 Freque                                    | ency synthesis techniques         | 4   |

|   | 2.2.1                                         | Direct analog synthesis           | 5   |

|   | 2.2.2                                         | Direct digital synthesis          | 6   |

|   | 2.2.3                                         | Indirect analog synthesis         | 7   |

|   | 2.2.4                                         | Hybrid synthesizers               | 8   |

| 3 | Freque                                        | ncy synthesizer requirements      | 9   |

|   | 3.1 Functional requirements                   |                                   | 10  |

|   | 3.2 Phase noise at small offset frequencies   |                                   | 11  |

|   | 3.3 Phase                                     | noise at large offset frequencies | 12  |

|   |                                               | noise in OFDM systems             |     |

|   | 3.5 Spurio                                    | ous tones                         | 17  |

|   | 3.6 Harmo                                     | onic tones                        | 20  |

|   | 3.7 Settlin                                   | ng time                           | 22  |

|   | 3.8 Other                                     | requirements                      | 23  |

| 4 | Fraction                                      | nal-N phase-locked loops          | 25  |

|   | 4.1 Proble                                    | ems of integer-N synthesizers     | 25  |

|   | 4.2 Advantages of fractional-N over integer-N |                                   |     |

|   | 4.3 Problems of fractional-N synthesizers     |                                   |     |

|   | •                                             | cancellation techniques           |     |

|   | 4.4.1                                         | Analog compensation               | 27  |

|   | 4.4.2                                        | Dithering                                   | 28 |

|---|----------------------------------------------|---------------------------------------------|----|

|   | 4.4.3                                        | $\Delta\Sigma$ -modulation                  | 29 |

|   | 4.4.3.1                                      | Fundamentals                                | 29 |

|   | 4.4.3.2                                      | Cascaded (MASH) modulators                  | 31 |

|   | 4.4.3.3                                      | Multibit single-loop modulators             | 33 |

|   | 4.4.4                                        | Direct modulation of the synthesizer        | 34 |

| 5 | PLL buil                                     | ding blocks                                 | 37 |

|   | 5.1 Prescale                                 | эг                                          | 37 |

|   | 5.1.1                                        | Fixed modulus prescalers                    | 37 |

|   | 5.1.2                                        | Dual modulus prescalers                     | 38 |

|   | 5.1.2.1                                      | Conventional dual modulus architecture      | 38 |

|   | 5.1.2.2                                      | Phase switching architecture                | 41 |

|   | 5.1.3                                        | Multiple modulus prescalers                 | 42 |

|   | 5.2 Phase fr                                 | requency detector                           | 43 |

|   | 5.2.1                                        | Multiplier-type phase detectors             | 43 |

|   | 5.2.2                                        | The XOR gate as a phase detector            | 44 |

|   | 5.2.3                                        | Phase frequency detectors                   | 45 |

|   | 5.3 Charger                                  | pump                                        | 46 |

|   | 5.4 Loop fil                                 | lter                                        | 47 |

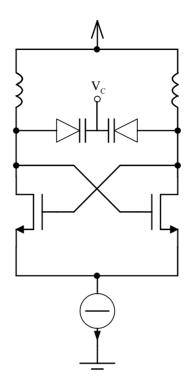

|   | 5.5 Voltage-controlled oscillator            |                                             | 48 |

|   | 5.6 Noise co                                 | ontributions of the building blocks         | 50 |

|   | 5.7 Power d                                  | lissipation of the building blocks          | 52 |

| 6 | Synthesiz                                    | zers in integrated systems                  | 55 |

|   | 6.1 Local of                                 | scillator pulling                           | 55 |

|   | 6.2 Frequen                                  | ncy stability during switching transients   | 56 |

|   | 6.3 Spuriou                                  | s tones caused by coupling                  | 57 |

|   | 6.4 Coupling of LO harmonics to other blocks |                                             | 58 |

|   | 6.5 Couplin                                  | g of LO reference frequency to other blocks | 58 |

| 7 | Summary of publications 6                    |                                             |    |

| 8 | Conclusion                                   | ons                                         | 63 |

| 9 | Riblingra                                    | nhv                                         | 65 |

## Symbols and abbreviations

## **Symbols**

$B_{channel}$  Bandwidth of the channel  $B_{PLL}$  Bandwidth of the PLL  $C_{GD}$  Gate-to-drain capacitance  $C_{GS}$  Gate-to-source capacitance

$D_{SNR}$  Degradation in signal-to-noise ratio

$E_S$  Energy of the symbol  $f_{OUT}$  Output frequency  $f_{ref}$  Reference frequency Unity gain frequency

$f_{VCO}$  VCO frequency

$G_F(s)$  Transfer function of the loop filter

$I_{CP}$ ,  $I_P$  Chargepump current

$K_{PD}$  Gain of the phase detector

$K_{VCO}$  Gain of the voltage-controlled oscillator

$L_{close-in}$  Close-in phase noise of the PLL

L<sub>int</sub> Integrated phase noiseN Loop division ratio

$N_0$  Noise level

$P_{wanted}$  Power of the wanted signal  $P_{unwanted}$  Power of the interfering signal

$S_{IF}$  Spectrum of the intermediate frequency signal

$S_{LO}$  Spectrum of the local oscillator signal  $S_{RF}$  Spectrum of the radio frequency signal

$t_{sw}$  Switching time

$V_C$ ,  $V_{CTRL}$  Control voltage of the VCO

$V_{GD}$  Gate-to-drain voltage  $V_{GS}$  Gate-to-source voltage  $\delta$  Absolute frequency error

$\Delta\theta_e$  Phase error

$\xi$  Damping factor

$\omega_c$  Crossover frequency

$\omega_n$  Natural frequency

$\omega_{ref}$  Reference frequency (in rad/s)

#### **Abbreviations**

ADC Analog-to-digital converter

BAW Bulk acoustic wave

BER Bit error rate

BiCMOS Bipolar complementary metal-oxide-semiconductor

CDMA Code division multiple access

CMOS Complementary metal-oxide-semiconductor

DAC Digital-to-analog converter

DC Direct current, zero frequency

DCS Digital Communications System

DDS Direct digital synthesizer

DQPSK Differential quadrature phase shift keying

DSL Digital subscriber line EVM Error vector magnitude

FET Field effect transistor

FFT Fast Fourier transform

GFSK Gaussian frequency shift keying

GMSK Gaussian minimum shift keying

GSM Groupe Spéciale Mobile

Global System for Mobile Communications

HDTV High definition television

IC Integrated circuit

ICI Inter-carrier interference

IEEE Institute of Electrical and Electronics Engineers

IF Intermediate frequency

IFFT Inverse fast Fourier transform

LAN Local area network

LNA Low noise amplifier

LO Local oscillator

OFDM Orthogonal frequency division multiplexing

OQPSK Offset quadrature phase shift keying

PCB Printed circuit board

PDC Personal digital communications

PFD Phase frequency detector

PLL Phase-locked loop ppm Parts per million

QAM Quadrature amplitude modulation

QPSK Quadrature phase shift keying

RF Radio frequency

rms Root mean square

ROM Read-only memory

SAW Surface acoustic wave

SNR Signal-to-noise ratio

SOI Silicon on insulator

TDMA Time division multiple access

VCO Voltage-controlled oscillator

WCDMA Wideband code division multiple access

WLAN Wireless local area network

WPAN Wireless personal area network

## List of publications

- P1 Ahola, R., Vikla, J., Lindfors, S., Routama, J., Halonen, K., "A 2 GHz Phase-Locked Loop Frequency Synthesizer with On-Chip VCO", Analog Integrated Circuits and Signal Processing, Vol. 18, No. 1, pp. 43-54, January 1999.

- P2 Ahola, R., Routama, J., Lindfors, S., Halonen, K., "A Novel Phase Detector with No Dead Zone and a Chargepump with Very Wide Output Voltage Range", Proceedings of the 1998 European Solid-State Circuits Conference, pp. 352-355, The Hague, The Netherlands, 1998.

- P3 Ahola, R., Halonen, K., "A 2 GHz  $\Delta\Sigma$  Fractional-N Frequency Synthesizer in 0.35μm CMOS", Proceedings of the 2000 European Solid-State Circuits Conference, pp. 472-475, Stockholm, Sweden, 2000.

- **P4** Ahola, R., Halonen, K., "A 1.76-GHz 22.6-mW ΔΣ Fractional-N Frequency Synthesizer", IEEE Journal of Solid-State Circuits, Vol. 38, No. 1, pp. 138-140, January 2003.

- P5 Ahola, R., Halonen, K., "A 4 GHz  $\Delta\Sigma$  Fractional-N Frequency Synthesizer", Analog Integrated Circuits and Signal Processing, Vol. 34, No. 2, pp. 77-88, February 2003.

- P6 Ahola, R., Aktas, A., Wilson, J., Rama Rao, K., Jonsson, F., Hyyryläinen, I., Brolin, A., Hakala, T., Friman, A., Mäkiniemi, T., Hanze, J., Sandén, M., Wallner, D., Guo, Y., Lagerstam, T., Noguer, L., Knuuttila, T., Olofsson, P., Ismail, M., "A Single Chip CMOS Transceiver for 802.11a/b/g Wireless LANs", IEEE Journal of Solid-State Circuits, Vol. 39, No. 12, pp. 2250-2258, December 2004.

## **Summary of publications**

This chapter gives a brief overview of each publication and the author's contribution in them. The author was responsible for all the work related to publications [P2]-[P5].

#### P1 A 2 GHz Phase-Locked Loop Frequency Synthesizer with On-Chip VCO

This paper presents an integer-N PLL design in a 0.5 µm BiCMOS process. The prescaler is based on the conventional dual-modulus architecture, and employs traditional ECL-type flip-flops. The first versions of the proposed new phase detector and chargepump topologies are presented in this paper as well. The chip also includes an integrated VCO, which was designed completely by Mr. Jyrki Vikla. Except for the VCO, the entire work was done by the author.

# P2 A Novel Phase Detector with No Dead Zone and a Chargepump with Very Wide Output Voltage Range

This paper provides a more detailed analysis of the proposed new phase detector and chargepump topologies. Improved versions of both were designed, and experimental results are presented.

#### P3 A 2 GHz ΔΣ Fractional-N Frequency Synthesizer in 0.35 μm CMOS

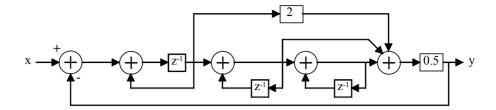

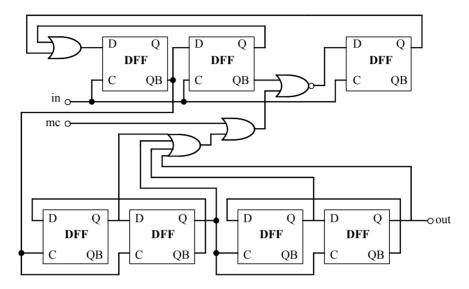

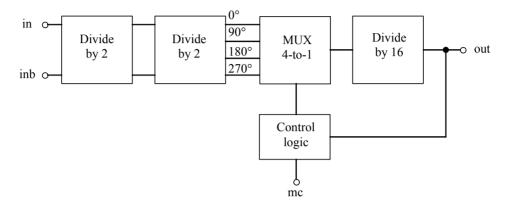

This paper describes the first  $\Delta\Sigma$  fractional-N synthesizer designed in this work. The synthesizer employs the phase detector and chargepump topologies developed previously. The prescaler uses the phase-switching architecture, and is designed completely in CMOS. A new D flip-flop topology allows it to function up to input frequencies of over 2 GHz. The prescaler implements eight possible moduli (64...71) that are controlled by an on-chip digital MASH 1-1-1  $\Delta\Sigma$ -modulator. The design is done in a 0.35  $\mu$ m CMOS process, and the experimental results show good performance.

#### P4 A 1.76-GHz 22.6-mW ΔΣ Fractional-N Frequency Synthesizer

This paper is based on the same chip as [P3], so the building blocks are the same as above. However, the experimental setup was rebuilt and some of the measurements redone for this paper. This has removed some peculiarities in the experimental results presented in [P3]. The results presented in this paper are state of the art: the close-in phase noise is -81dBc/Hz at an offset frequency of 10 kHz, and the spurious level is lower than -85 dBc.

#### P5 A 4 GHz ΔΣ Fractional-N Frequency Synthesizer

This paper provides a more detailed theoretical analysis of the close-in phase noise requirements of the synthesizer in different systems. It employs the same phase detector and chargepump topologies as the previous papers, but provides a more detailed discussion on the tradeoffs in their design. This design also includes a BiCMOS prescaler based on the phase-switching architecture, implementing eight moduli (128...135). The prescaler operates up to an input frequency of 4.3 GHz. The experimental results show that the design works relatively well, although the performance is not as good as that of the 2 GHz synthesizer presented in [P4].

#### P6 A Single Chip CMOS Transceiver for 802.11a/b/g Wireless LANs

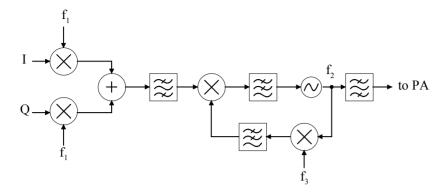

This paper describes a complete transceiver chip that fulfills the IEEE 802.11 a, b, and g standards. The key features of the chip include a new dual conversion architecture that avoids image rejection filtering, and an extremely flexible interface towards the baseband chip, allowing the chip to operate with multiple different baseband chips. In addition to these features, this chip also had challenging frequency synthesizer design requirements. The chip includes two PLLs that have to operate simultaneously with each other, and with a multitude of other circuit blocks on the same die. Even the reference crystal oscillator is integrated on the same chip. The experimental results show excellent PLL performance; the two PLLs have a combined integrated phase noise of -34 dBc, which equals an rms phase error of 1.1°.

In this part of the work, the author was responsible for specifying the requirements of the blocks, including the PLLs. The author was also responsible for interface and integration issues that are inevitably faced when integrating an entire system on a single chip. In addition to these, the author had the responsibility for the technical management of the entire project, including detailed reviewing of all the blocks. The paper itself is completely written by the author.

#### 1 Introduction

## 1.1 Background

The growth of mobile telecommunications has been extremely rapid during the last decade. The cellular phone penetration rates in Finland have gone from 20% in 1995 to almost 100% in 2004. In July 2004, Sweden was the first country to exceed 100% penetration, i.e. there are more cell phone subscriptions than there are people. But not only has the market for mobile speech grown; during the last couple of years, all kinds of previously wired connections between home and office appliances have gone wireless as well. The cellular phone has a calendar function that synchronizes automatically with the desktop calendar through a Bluetooth connection, the laptop computer accesses the Internet through a WLAN connection, the wireless mouse sends information to the desktop computer through a proprietary wireless connection, etc.

The wireless connections come in a vast variety of flavors, depending on the application. Smooth web browsing requires data rates thousands of times higher than monitoring the temperature in an apartment. On the other hand, a cellular phone requires at least hundreds of times longer range than a wireless mouse. There is a multitude of different wireless standards for different applications. However, common to almost all of these standards is that the data to be transferred is somehow modulated on a radio frequency (RF) carrier, and the modulated signal is then transmitted over the air, and received and demodulated in the receiving end. In both the transmitting and the receiving end, an accurate RF carrier signal must be generated. Therefore, a radio frequency synthesizer is always required, regardless of the wireless standard.

More recently, the digital convergence has presented additional challenges to the design of the radio transceivers, including the frequency synthesizers. One handheld unit may now include for example a dual-mode, quad-band cellular phone, a Bluetooth radio, and a WLAN radio. From a cost point of view, it would of course be beneficial to share as much of the hardware as possible between the different radio standards. Sharing parts of the hardware, however, often means that the chosen shared component is not the optimal one for all the standards. As an example, the crystal oscillator might be shared between all the radio standards in the above example. The same crystal oscillator frequency will not be optimal for all standards, though, resulting in more challenging frequency synthesizer design.

As the wireless standards evolve, users expect higher and higher data rates. The available frequency spectrum is limited, though. Therefore, the new standards must employ more complex modulation types to increase the number of bits transmitted over a fixed bandwidth. The more complex modulation types, however, normally require a higher signal-to-noise ratio as well, resulting in tougher requirements for the analog building blocks of the radio.

Although the advances in the performance of integrated radio frequency synthesizers have been overwhelming in the recent years, there is still a lot of work to be done in the field. The digital convergence and the ever more complex standards keep pushing the requirements of the synthesizer further and further.

#### 1.2 Research contribution

The research described in this thesis focuses on the design of radio frequency synthesizers for wireless applications. Both integer-N and fractional-N phase-locked loop (PLL) designs are presented and discussed. In the case of fractional-N PLLs, the different methods for reducing the fractional spurs are discussed. On the circuit level, the work focuses on three key building blocks of the PLL, namely the prescaler, the phase detector, and the chargepump.

In the prescaler designs, the main focus has been on implementing the required functionality with as low power as possible. In the fractional-N designs, different methods to implement multiple moduli were studied as well. In the phase detector design, the focus has been on finding new ways of eliminating the dead zone problem. The new phase detector topology presented in this thesis has been awarded both Finnish and U.S. patents. The chargepump designs presented in this thesis have focused on developing new topologies that would maximize the usable output voltage range. The presented PLLs prove that the designed building blocks can be combined to form a radio frequency synthesizer with state-of-the-art performance.

The last part of this thesis concentrates on the additional challenges that emerge when the RF synthesizer is integrated as a part of a much larger transceiver IC. The possible negative effects caused to the PLL by the rest of the system are analyzed, as well as the interference caused by the PLL to the rest of the system.

## 1.3 Organization of the thesis

This thesis is divided into two parts. In the first part, an introduction to the issues of integrated radio frequency synthesizer design is given to summarize the work that has been carried out. In Chapter 2, different radio transceiver architectures are briefly introduced, mainly to put the rest of the work into context. Also, different frequency synthesis techniques are reviewed. The various requirements set by the wireless standard on the frequency synthesizer are examined in Chapter 3. Chapter 4 introduces the special issues encountered when going from integer-N PLLs to fractional-N PLLs. In Chapter 5, the building blocks of a PLL are discussed. Different implementation alternatives are introduced, and some of the previously published work is reviewed. Finally, Chapter 6 focuses on the additional issues when the synthesizer is integrated into a larger system on a chip. The second part of this thesis contains the published papers.

## 2 Frequency synthesizers in radio systems

The first part of this chapter will briefly introduce different radio transceiver architectures that have been used in recent years. The main focus is not on the properties of different architectures, but in motivating the rest of this work. The second part of the chapter will introduce shortly different methods to generate a tunable local oscillator signal. Although the focus in the rest of this work is on phase-locked loops, other methods of completing the same task are also reviewed.

#### 2.1 Radio transceiver architectures

Since Edwin H. Armstrong presented his superheterodyne radio receiver in the 1920's [17], several different architectures for implementing both the receiver and the transmitter sides of it have been developed. Most of them share the need for a tunable *local oscillator* signal, i.e. a signal whose frequency can be accurately set. The different architectures are discussed in a number of textbooks [18][19], and will be explained here only briefly for the sake of completeness and to motivate the work. In short, the required frequency selectivity can be implemented either by tuning the local oscillator frequency or by tuning the intermediate frequency (IF) filter. The IF filter is usually a passive surface acoustic wave (SAW) filter, and thus not tunable, which leaves a tunable local oscillator as the only choice.

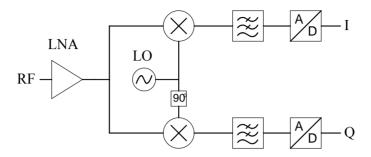

The most widely used receiver architecture, the superheterodyne receiver, is shown in Figure 2.1. The received signal is first amplified and filtered to suppress the image frequency, and then downconverted to an intermediate frequency. The actual frequency selectivity is then implemented with the IF bandpass filter. Now, achieving the required selectivity at the IF frequency (usually from tens to more than one hundred MHz) has at least up to date been possible only with a discrete (SAW, BAW, etc.) filter, which is by nature centered on a fixed frequency. To be able to downconvert all desired frequencies to a fixed IF frequency, the LO signal must be tunable.

Figure 2.1 The superheterodyne receiver architecture.

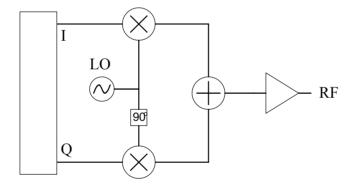

Although the superheterodyne architecture is still used in most of the world's radio receivers, it is very poorly integrable due to the SAW filters. Therefore, the research in recent years has focused on alternative receiver architectures, mainly the direct conversion receiver (Figure 2.2), which can be completely integrated on a single die [20]. Now, the received signal is converted directly down to around DC, and the

bandpass filtering that caused problems in the superheterodyne architecture is translated into lowpass filtering. Again, to be able to downconvert all the desired radio frequencies to the same frequency (DC), the LO signal must be tunable.

Figure 2.2 The direct conversion receiver architecture.

The transmitter part of a radio is much more straightforward than the receiver. Basically, the signal to be transmitted can be upconverted in one or more steps, the one-step or direct conversion approach (Figure 2.3) being dominant in today's radio transmitters. Again, to be able to upconvert the modulated baseband signal to the desired RF frequency, the LO signal must be tunable.

Figure 2.3 The direct conversion transmitter architecture.

## 2.2 Frequency synthesis techniques

Several different frequency synthesis techniques have been presented in the literature over the years. They can be quite clearly divided into three separate categories, namely direct analog synthesis, direct digital synthesis, and indirect analog synthesis. In this context, "indirect" refers to a system based on some kind of a feedback action, whereas "direct" refers to a system having no feedback.

The three categories of frequency synthesis techniques will be introduced in the following three sections. The fourth section will introduce different combinations of these techniques.

#### 2.2.1 Direct analog synthesis

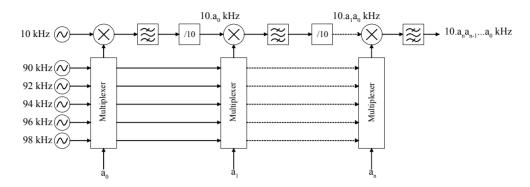

Figure 2.4 The block diagram of a direct analog synthesizer.

Figure 2.4 shows an example of a direct analog synthesizer [21]. The frequency resolution is achieved by mixing signals of certain frequencies, and then dividing the resulting frequency down. Theoretically, this process can be repeated arbitrarily many times to achieve a finer frequency resolution.

Advantages of the direct analog synthesis are very fast switching times and, in theory, arbitrarily fine frequency resolution. However, this technique requires a very large amount of hardware, as can clearly be seen even from the simple example block diagram (Figure 2.4). Also visible in the figure is the fact that the synthesized frequency is lower than the highest input frequency (in this example, approximately an order of magnitude lower). Therefore, the use of direct analog synthesis techniques in high-frequency applications is severely limited.

Also noise is a problem in direct analog synthesis. To achieve a reasonably low-noise output signal, all input frequencies (left side of Figure 2.4) will have to be low-noise crystal oscillators, resulting in a lot of external components. Moreover, all the mixers, bandpass filters, and dividers are in the signal path, meaning that their noise will also contribute to the phase noise in the synthesized frequency.

For the reasons mentioned above, the use of direct analog synthesizers is limited to low frequencies and to applications that are not too sensitive to noise. Even in these applications, they are relatively expensive compared to the synthesis techniques presented in the following sections. Therefore, very few direct analog synthesizers, if any, are used in commercial applications.

#### 2.2.2 Direct digital synthesis

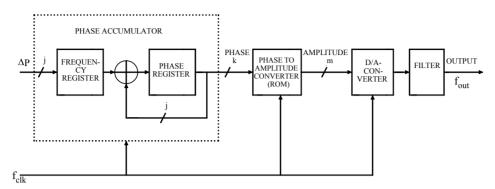

Figure 2.5 The block diagram of a direct digital synthesizer.

Figure 2.5 shows the basic principle of direct digital synthesis [23]. The desired output frequency is fed to the phase accumulator as a digital word. The phase accumulator increments its output value by this word once every clock cycle. When the full scale of the accumulator is reached, it wraps around. The output of the phase accumulator is thus a digital ramp signal, whose period is the same as that of the desired output frequency. In other words, the phase accumulator output contains information about the instantaneous phase of the synthesized frequency.

The amplitude of a sinusoidal signal at different phase values is stored in the sine readonly memory (ROM). The instantaneous phase of the desired output signal is used as the address to the ROM, and the output is the instantaneous amplitude of the synthesized signal.

To get an analog output signal, the amplitude information has to be converted to the analog domain in the digital-to-analog converter (DAC). The output of the DAC contains a lot of spurious tones, harmonics, etc., that have to be filtered out before the signal can be used. The smoothing filter in the output of the DAC attenuates the harmonics to an acceptable level, but the in-band spurious tones still remain. Their frequencies are predictable, but as they are in the signal band, they will not be attenuated by the filter.

Direct digital synthesis has some very strong advantages. It has arbitrarily fine frequency resolution and a very high switching speed. Also, different phase, frequency, and amplitude modulations can be implemented in the digital domain, and require only a small amount of extra hardware. Due to the fact that most of the signal processing is done in the digital domain, direct digital synthesis also lends itself very well to full integration in a CMOS or BiCMOS technology.

Until recently, the main disadvantage of direct digital synthesis has been the speed requirement and the huge power dissipation in the digital parts of the circuit, i.e. the phase accumulator and the sine ROM. However, with modern deep submicron CMOS technologies, the power dissipation has been dramatically reduced, and the achievable

speed has become fairly high. Now, the bottleneck in the direct digital synthesizer is the DAC. Demands on the DAC clock frequency, resolution, and linearity are overwhelming. This limits the use of direct digital synthesizers in high-frequency applications. However, they have become de facto standard in high-performance low-frequency signal generators (e.g. [22]). Recently, they have also found use in cellular base station applications.

Direct digital synthesis has been applied to quite a few commercial products, as well as investigated widely in the literature. Good examples of the strong sides of the technique are a frequency resolution of 0.0349 Hz in [23], the modulation capabilities in [24], and the generation of multiple modulated carriers in [25]. On the other hand, some examples of the downsides have also been published: a power dissipation of 3 W in [26], and a spur level as high as -30 dBc in [27].

#### 2.2.3 Indirect analog synthesis

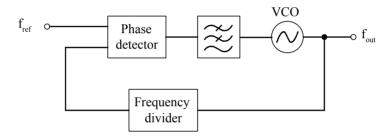

Figure 2.6 The block diagram of a simple phase-locked loop.

Figure 2.6 shows the block diagram of the phase-locked loop, i.e. an indirect analog synthesizer, at its simplest. Here, the synthesis is based on the feedback action of the loop. The output frequency is divided down in the frequency divider. The phase of the output signal of the divider is compared with the phase of a reference signal in the phase detector. The output of the phase detector is lowpass filtered to generate a control voltage for the voltage-controlled oscillator (VCO). If the phase of the frequency divider output lags the phase of the reference frequency, the phase detector steers the VCO to a higher frequency, and vice versa.

Indirect analog synthesis, or the phase-locked loop, is the most suitable technique for the synthesis of high-frequency sinusoidal signals. No block has to operate at a frequency higher than the output frequency. Also, the only component that is necessarily external is the reference frequency oscillator (or at least the crystal used as the resonator in the oscillator).

The basic configuration of the phase-locked loop (PLL) has a few disadvantages, too. For example, the frequency resolution equals the reference frequency. On the other hand, the loop bandwidth has to be significantly lower than the reference frequency, which results in relatively slow switching. Thus, the finer the frequency resolution of the PLL, the slower the switching speed.

#### 2.2.4 Hybrid synthesizers

In addition to the three basic synthesis techniques introduced above, several modifications or combinations of them have been published. Most of these synthesizers are modifications of the PLL, aiming to allow a wider loop bandwidth and a finer frequency resolution than the basic principle.

The interpolating PLL synthesizer [28] uses controllable delay lines in front of the phase detector inputs, allowing a frequency step smaller than  $f_{ref}$ . However, the measured results [29] show that imperfections in the delay lines generate spurious tones, and the noise of the delay line adds to the total synthesizer noise, increasing the noise floor of the synthesizer.

Several multi-loop architectures have also been proposed. The simplest approach would be to generate the reference frequency to the main loop by another phase-locked loop [30]. The bandwidth of the main loop can be increased without loosing frequency resolution, if the reference loop is programmable, too. The drawback of this architecture is that the close-in phase noise will be the product of the phase noise contributions of the two loops. However, with careful design, reasonably low noise levels have been demonstrated [31].

Also, much more complicated multi-loop architectures have been published [32]. In addition to the huge complexity (several bandpass filters, mixers, etc.), the performance of this synthesizer is quite limited, and it is quite useless in practical applications.

Another proposed hybrid solution is generating the reference frequency of the phase-locked loop by a direct digital synthesizer [33]. The DDS allows a fine frequency resolution while the bandwidth of the PLL is relatively large. However, all the spectral impurities in the output of the DDS will appear in the output of the synthesizer multiplied by the loop division ratio. Thus, the output of the DDS must be bandpass filtered, adding to the synthesizer's complexity.

Although none of the above solutions has yet gained widespread acceptance as a 'good' solution, some of them seem quite promising, and worth further investigation.

## 3 Frequency synthesizer requirements

The principle of phase-lock was invented a long time ago. The first publication that can be clearly identified as a description of a phase-locked loop is de Bellescize's article "La Reception Synchrone", dating back to 1932 [34]. However, there were practically no applications for PLL's until they became necessary in synchronizing the red, green and blue color sweeps in television receivers in the 1940's and 1950's [35][36][37]. Today, phase-locked loops are used in innumerable applications ranging from data regeneration circuits in subscriber line interfaces to frequency synthesizers in microprocessors, radio transceivers, etc. Some very comprehensive books on the theory of phase-locked loops have been published over the years (e.g. [38][39][40][41]). The basic theory will not be discussed in more detail in this work

This chapter deals with the requirements set on the frequency synthesizer by modern telecommunications systems. The implications of these requirements on the synthesizer design will be viewed from a phase-locked loop point of view, but the actual requirements can be generalized to any kind of frequency synthesizer.

The radio receiver or transmitter, in which the frequency synthesizer is used, is typically a part of a larger radio system. These systems, e.g. GSM, DCS-1800 or Bluetooth, are accurately specified to ensure interoperability between radio units from different manufacturers.

For the receiver, the purpose of the specifications is to ensure that the receiver is able to receive the wanted signal correctly in an environment where other users of the frequency spectrum are causing interference. The specifications typically include the minimum power of the wanted signal that the receiver should still be able to receive correctly ("correctly" in this context meaning reception with a bit error rate (BER) smaller than a specified maximum). Also specified are the interfering signals that the receiver is required to tolerate while still correctly receiving the wanted signal. The interferers can be much higher in power than the wanted signal. For example in the DCS-1800 system, the interfering signal can be as much as 66 dB higher than the wanted signal.

For the transmitter, the purpose of the specifications is to restrict the amount of interference caused by the transmitter to other users of the frequency spectrum, and to ensure that the quality of the transmitted signal is good enough to be received correctly with a receiver fulfilling the specifications of the same system. Typically, the specifications include a *spectral mask*, i.e. the maximum power level of the components of the transmitted spectrum at different offset frequencies. The frequency accuracy of the transmitted signal is also normally specified. Depending on the type of modulation used, a measure of the modulation quality is also specified. In phase modulated systems, e.g. GSM, this is typically the maximum phase error of the actual transmitted signal with respect to the ideal one. In more complex modulation types, the typical measure of modulation quality is error vector magnitude (EVM), which takes into account both the phase error and the amplitude error of the actual transmitted signal with respect to the ideal one.

This chapter will introduce the specifications relevant for frequency synthesizer design in more detail. The translation of the specifications of the radio system to the specifications of the frequency synthesizer will be explained. Most of the examples in this chapter will be based on the specifications for the DCS-1800 system [42]. When the requirement is specific to an OFDM system, the specifications of the IEEE 802.11a wireless LAN system [46] are used.

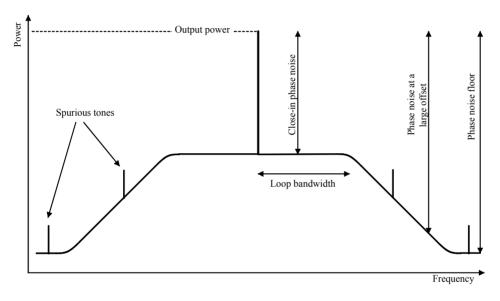

The output signal of an ideal frequency synthesizer is a pure sinusoid, i.e. a delta function in the frequency domain. The output spectrum of a real synthesizer, however, consists of a number of nonideal components in addition to the sinusoidal component. Figure 3.1 illustrates these components, as well as other parameters, whose specifications will be derived in the following sections.

Figure 3.1 Nonideal components in the output spectrum of a PLL frequency synthesizer.

## 3.1 Functional requirements

The basic requirement set for a frequency synthesizer by any telecommunications system is that the synthesizer must be able to generate all required frequencies with a sufficient accuracy. In other words, the synthesizer must be able to cover the entire frequency range of the system, it must be able to generate the channel frequencies required by the system, and the frequency accuracy of the synthesizer must be good enough.

The frequency range is mainly a design parameter for the VCO and the prescaler. The channel spacing requirement sets the frequency resolution of the synthesizer, and is thus an important parameter in the selection of the synthesizer architecture. The frequency accuracy requirement has different consequences for an integer-N PLL than for a fractional-N PLL. For an integer-N PLL, the accuracy requirement merely sets the limit to when the loop can be considered locked, and thus affects the switching time specification. For a fractional-N PLL, the frequency accuracy requirement may also

come into play in determining the minimum word length of the frequency control word. If the fractional frequencies generated are not exactly coincident with the channel center frequencies, then the frequency resolution must be fine enough to keep the frequency error still within specifications.

In the DCS-1800 system, the frequency range is 1710...1880 MHz, and the channel spacing is 200 kHz. The carrier frequency must be accurate to within 0.1 ppm (171 Hz).

#### 3.2 Phase noise at small offset frequencies

Many of today's telecommunications systems, e.g. GSM, use phase modulation techniques. In these systems, it is essential that the received symbols have a low enough phase error to maintain a useful bit error rate. Therefore, a maximum phase error is normally specified for the transmitted signal. Typically, both root mean square (rms) and peak phase error limits are specified. In the DCS-1800 case, the specified limits are 5 degrees rms, and 20 degrees peak phase error.

In systems employing more complex modulation schemes, e.g. quadrature amplitude modulation (QAM), error vector magnitude (EVM) is used as a measure of modulation quality. Not only phase error, but also amplitude noise, distortion, quadrature mismatch, etc., contribute to the EVM. Therefore, the maximum phase error can not be determined directly from the standards. The specification is a tradeoff between the phase error and other nonidealities.

In the transmitter, the major contributor to the phase error is the frequency synthesizer generating the local oscillator frequency. The close-in phase noise manifests itself as random fluctuations in the phase of the local oscillator signal, which then translate directly to fluctuations in the phase of the transmitted signal, i.e. random phase error.

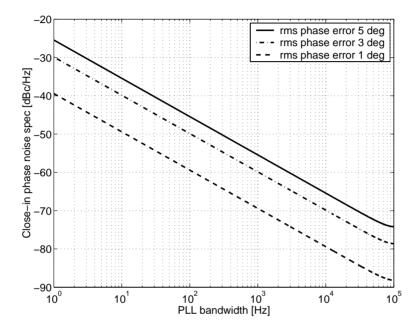

Let us assume that the frequency synthesizer is a second-order PLL, i.e. the phase noise rolloff is -40 dB per decade for offset frequencies beyond the loop bandwidth. Let us also assume that the phase noise floor of the synthesizer is low enough to be ignored as a contributor to the total integrated noise. This assumption is only valid for narrow band systems, where the PLL bandwidth is only about an order of magnitude smaller than the channel bandwidth. Let us denote the phase noise at small offset frequencies by  $L_{close-in}$ , the phase-locked loop bandwidth by  $B_{PLL}$ , and the channel bandwidth of the system in question by  $B_{channel}$ . We can now approximate the square of the phase error with

$$\phi_e^2 \approx \int_{-B_{channel}/2}^{-B_{PLL}} L_{close-in} \left( \frac{-B_{PLL}}{f} \right)^4 df + \int_{-B_{PLL}}^{B_{PLL}} L_{close-in} df + \int_{B_{PLL}}^{B_{channel}/2} L_{close-in} \left( \frac{B_{PLL}}{f} \right)^4 df.$$

(3.1)

Solving for the close-in phase noise, we get

$$L_{close-in} \le \frac{3}{8} \frac{\phi_e^2 B_{channel}^3}{B_{PLL} \left( B_{channel}^3 - 2B_{PLL}^3 \right)}$$

(3.2)

Equation (3.2) shows that increasing the PLL bandwidth leads to a tighter specification for the close-in phase noise. In the DCS-1800 system, for example, the channel bandwidth is 200 kHz, and the maximum rms phase error is 5 degrees. In practice, a portion of the total phase error has to be allocated to other sources of error. The maximum close-in phase noise as a function of the PLL bandwidth is plotted in Figure 3.2 for three different values of phase error contribution from the synthesizer.

Figure 3.2 The maximum close-in phase noise versus the loop bandwidth for three different rms phase error specifications.

For example, allocating 3 degrees of the total phase error for the frequency synthesizer (the middle curve), and assuming a PLL bandwidth of 20 kHz, which would be a typical value for a DCS-1800 integer-N PLL, the close-in phase noise of the synthesizer has to be below -73 dBc/Hz.

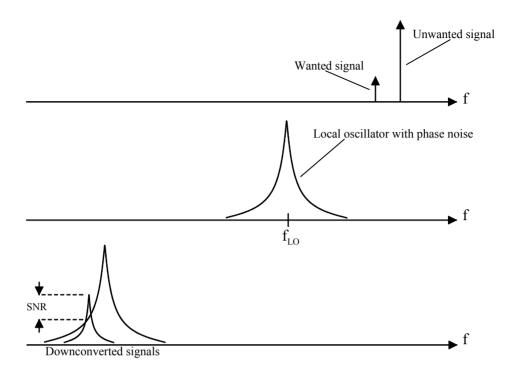

## 3.3 Phase noise at large offset frequencies

The phase noise of the frequency synthesizer at large offset frequencies is almost always specified. The reason for this is a phenomenon commonly referred to as *reciprocal mixing*. The phase noise tail of the local oscillator signal mixes with undesired interfering signals, and the mixing result ends up at the same intermediate frequency as the wanted signal, thus impairing the signal-to-noise ratio. The reciprocal mixing phenomenon is illustrated in Figure 3.3.

Figure 3.3 Reciprocal mixing.

The spectrum converted to the intermediate frequency can be represented as the convolution of the received RF spectrum and the spectrum of the local oscillator signal (Equation (3.3)).

$$S_{IF}(\omega) = S_{RF}(\omega) \otimes S_{IO}(\omega) \tag{3.3}$$

Since the interfering component can be much stronger than the wanted signal, the phase noise power of the local oscillator at the same offset frequency must correspondingly be much lower to maintain a useful signal-to-noise ratio of the downconverted signal. The specification for the local oscillator power at a given offset frequency can be derived from the power levels of the wanted signal and the interfering signal, and the signal-to-noise ratio required to guarantee signal reception at the desired bit error rate:

$$L(\Delta f) \le P_{wanted} - P_{unwanted} - SNR_{required} - 10 \cdot \log(B_{channel})$$

(3.4)

The last term of the equation is an approximation, assuming that the mean value of the phase noise over the channel bandwidth can be approximated with the phase noise value at the center point of the channel.

In the DCS-1800 system blocking specifications, the wanted signal is 3 dB over the reference sensitivity level, i.e. at -99 dBm. The largest allowed blocking signals are -43 dBm, -33 dBm, and -26 dBm at offset frequencies of 600 kHz, 1.6 MHz, and 3.0 MHz, respectively. Detecting the GMSK modulated signal with a 0.1% BER requires a signal-

to-noise ratio of approximately 8 dB, and the channel bandwidth is 200 kHz. Inserting these values into Equation (3.4) leads to the phase noise specifications shown in Table 3.1.

**Table 3.1:** Phase noise specifications for the DCS-1800 system.

| Offset frequency | Phase noise requirement |  |

|------------------|-------------------------|--|

| 600 kHz          | -117 dBc/Hz             |  |

| 1.6 MHz          | -123 dBc/Hz             |  |

| 3.0 MHz          | -134 dBc/Hz             |  |

In practice, a few decibels of safety margin have to be added. Phase noise specifications shown in the literature for the DCS-1800 system are typically in the range of -120...-123 dBc/Hz at a frequency offset of 600 kHz.

At large offset frequencies, the phase noise properties of a PLL based frequency synthesizer are normally dominated by the voltage-controlled oscillator, since the noise from the rest of the loop components is lowpass filtered. However, in the case of  $\Delta\Sigma$  fractional-N synthesizers, the shaped quantization noise from the  $\Delta\Sigma$ -modulator increases with frequency offset, and may dominate over VCO phase noise at large offset frequencies unless properly filtered.

The phase noise specifications shown in Table 3.1, especially the specification at 600 kHz offset frequency, are quite tough for a VCO. State-of-the-art performance examples are -129 dBc/Hz for a discrete VCO [50], and -125 dBc/Hz for an integrated one [51]. Due to the better performance, most cellular products today use discrete VCO's. However, the push towards smaller devices has supported a vast research in the field of integrated VCO's, and the state-of-the-art is fairly close to being commercially usable.

## 3.4 Phase noise in OFDM systems

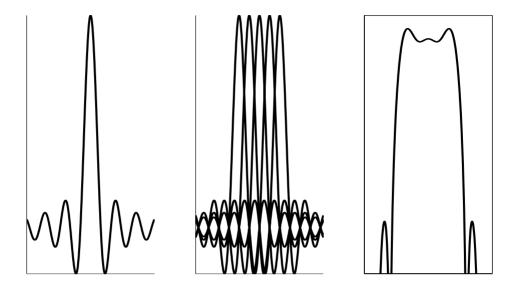

In orthogonal frequency division multiplexing (OFDM), the data stream to be transmitted is divided into multiple data streams with lower bit rates. Each low bit rate data stream is then individually modulated on a subcarrier, and the subcarriers are combined to form the OFDM signal. The subcarriers are spectrally orthogonal, i.e. at the center frequency of a subcarrier, all other subcarriers have spectral nulls (see Figure 3.4). Ideally, each subcarrier can then be demodulated with no interference from the other subcarriers. A more comprehensive analysis of the OFDM signals and systems can be found for example in [43].

Figure 3.4 A single OFDM subcarrier in frequency domain (left), a combination of multiple subcarriers (middle), and the combined power of the subcarriers in logarithmic scale (right).

In comparison with other modulation types at the same data rate, OFDM signals are extremely tolerant against multipath fading channels, as well as narrowband interferers. However, the FFT and IFFT operations required for modulating and demodulating the OFDM signal are computationally very heavy, and only recent advances in digital technology have made it possible to use OFDM in practical applications. Currently, OFDM is used as the modulation format in the xDSL systems [44], high-definition television (HDTV) systems [45] as well as in the IEEE 802.11a and 802.11g wireless LAN systems [46][47].

One of the largest drawbacks of OFDM is its relatively high sensitivity to phase noise. However, the phase noise of the local oscillator signal affects the OFDM systems in a slightly different way than it affects single-carrier systems. The channels are typically very wide (e.g. 20 MHz in IEEE 802.11a [46]), and thus the mixing of the neighboring channels with the LO phase noise tail is not a problem. Practically any local oscillator will have low enough phase noise at an offset of 20 MHz. The wanted signal, however, now consists of several subcarriers. Phase noise at small offset frequencies (<10% of the subcarrier spacing) can be considered common to all subcarriers, and is relatively easy to handle by means of tracking techniques or differential detection. Phase noise at larger offset frequencies, however, will introduce inter-carrier interference (ICI), i.e. the subcarriers will not be perfectly orthogonal any more. The mixing products of each subcarrier and the phase noise tail of the LO signal will end up on top of every subcarrier, thus impairing the signal-to-noise ratio of the other subcarriers.

Analytically determining the LO phase noise specification for an OFDM system is not as straightforward as it is for single-carrier systems. In [48], it is assumed that the free-

running (i.e. not phase-locked) local oscillator has a Lorentzian phase noise spectrum given by

$$L(\Delta f) = \frac{1/\pi f_{-3dB}}{1 + \left(\frac{\Delta f}{f_{-3dB}}\right)^2},\tag{3.5}$$

where  $f_{-3dB}$  is the -3 dB bandwidth of the oscillator. It is shown in [48] that the degradation in signal-to-noise ratio caused by the phase noise spectrum of Equation (3.5) can be approximated with

$$D_{SNR} \approx \frac{11}{6\ln 10} 4\pi f_{-3dB} T \frac{E_S}{N_0},\tag{3.6}$$

Where 1/T is the spacing of the OFDM subcarriers in the frequency domain, and  $E_S/N_0$  depends on the modulation type of the subcarriers.

For the fastest data rate of the IEEE 802.11a WLAN system (54 Mbit/s), the subcarriers are 64-QAM-modulated, requiring an  $E_S/N_0$  of 19dB to achieve a bit error rate less than  $10^{-6}$ . The subcarrier spacing is 312.5 kHz. Using these values, and requiring that the SNR degradation must be negligible (less than 0.1 dB), we can calculate the maximum -3 dB bandwidth of the oscillator to be 39 Hz. According to Equation (3.5), this corresponds to a phase noise of -109 dBc/Hz at an offset of 1 MHz from the carrier.

The Lorentzian phase noise model in [48] assumes a free-running oscillator. In practice, however, the oscillator is always locked to a stable reference frequency by means of a phase-locked loop. The phase noise spectrum will no longer follow the simple Lorentzian model, but will have a shape resembling that in Figure 3.1. A first order approximation for the phase noise specification can be derived by requiring that the total integrated phase noise power of the PLL must be equal to the integrated phase noise power of a Lorentzian oscillator with a bandwidth of 39 Hz. As explained earlier, the phase noise at offsets smaller than 10% of the subcarrier spacing is essentially common to all subcarriers, and does not contribute to the ICI. Therefore, it should also be removed before the integration to get correct results. Integrating Equation (3.5), we get

$$L_{\text{int}} = \int_{f_1}^{f_2} \frac{\frac{1}{\pi f_{-3dB}}}{1 + \left(\frac{f}{f_{-3dB}}\right)^2} df = \frac{\pi}{2} \left[ \text{atan} \left(\frac{f_2}{f_{-3dB}}\right) - \text{atan} \left(\frac{f_1}{f_{-3dB}}\right) \right]$$

(3.7)

Using, again, the IEEE 802.11a WLAN system as an example, the phase noise of the LO signal should thus be integrated from approximately  $f_1$ =30 kHz (<10% of the subcarrier spacing of 312.5 kHz) to  $f_2$ =20 MHz (channel spacing). These values result in an integrated phase noise specification of –27 dBc.

For a practical PLL, the total integrated phase noise is a much more useful specification than the bandwidth of the Lorentzian model. The phase noise can easily be measured and integrated to check if the device performance meets the requirements.

In addition to [48], a few other attempts have been made to analytically quantify the effects of the local oscillator phase noise on an OFDM signal. For instance in [49], the LO signal is no longer modeled as a free-running oscillator, but an assumption of a PLL-like phase noise spectrum is used. However, several simplifications and assumptions are still used that degrade the generality of the analysis; the phase noise close to the carrier is not removed, although it will result in a phase error common to all carriers that can be easily corrected for. Also, the analysis does not take into account the fact that the first and the last subcarriers will contribute less to the total noise due to the fact that half of their phase noise will not overlap other subcarriers. This assumption will be reasonably accurate when the number of subcarriers is very large (e.g. 8192 in the HDTV system), but for a smaller number of subcarriers (e.g. 52 in the IEEE 802.11a WLAN standard) the error will be larger. All in all, it can be said that no model accurately and generally predicting the effects of local oscillator phase noise on an OFDM signal has been published to date.

## 3.5 Spurious tones

Spurious tones are unwanted components in the frequency synthesizer output spectrum that are not noise-like. The VCO is essentially a frequency modulator, and periodic signals at the VCO control line will result in an output signal with discrete FM sidebands.

The requirement for the maximum spurious power derives from the blocking specification of the telecommunications system. A spurious tone at a given offset mixes the neighboring channel at the same offset down to on top of the wanted channel. The spurious power must therefore be low enough to provide an adequate signal-to-noise ratio (SNR) in the output of the receiver.

Telecommunications systems normally have different blocker power specifications for different offset frequencies. Also, the reference sensitivity level and the SNR required depend on the system. In the DCS-1800 system, the wanted signal is 3 dB above the reference sensitivity level of -102 dBm, and the SNR required is approximately 8 dB. The blocker at 600 kHz offset, for example, can be as high as -43 dBm, leading to a maximum spurious power of -64 dBc. Table 3.2 shows the maximum spurious power levels at different offset frequencies for a synthesizer in a DCS-1800 mobile station receiver.

*Table 3.2:* Spurious power specifications for DCS-1800.

| Offset frequency                                          | Maximum spurious power |  |

|-----------------------------------------------------------|------------------------|--|

| $600 \text{ kHz} \le f_{\text{offset}} < 800 \text{ kHz}$ | -64 dBc                |  |

| $800 \text{ kHz} \le f_{\text{offset}} < 1.6 \text{ MHz}$ | -64 dBc                |  |

| $1.6 \text{ MHz} \le f_{\text{offset}} < 3.0 \text{ MHz}$ | -74 dBc                |  |

| $f_{offset} \ge 3.0 \text{ MHz}$                          | -81 dBc                |  |

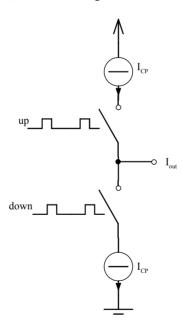

A number of nonidealities in the PLL itself will generate interfering signals in the VCO control line. All of these phenomena will result in periodic signals at the PLL reference frequency, and thus in spurs at an offset of  $f_{ref}$  from the carrier. The dominant spurious-generating nonidealities in a typical PLL are mismatch between the up and down currents in the chargepump and charge injection through the switches in the chargepump. Also, the leakage currents of the chargepump and the VCO may be significant contributors.

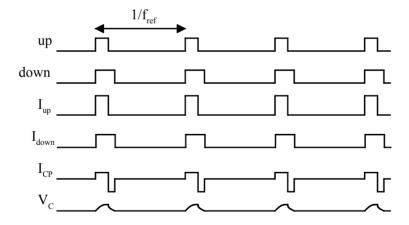

Figure 3.5 shows how the mismatch between the up and down currents in the chargepump results in a periodic signal in the VCO control line. In this case, the up current is slightly larger than the down current. The PLL feedback mechanism tries to keep the mean value of the VCO control voltage ( $V_C$ ) constant, and therefore the down pulses from the phase detector will be slightly longer to compensate for the smaller current. The resulting net output current of the chargepump ( $I_{CP}$ ) is then low pass filtered in the loop filter. Despite of the filtering, the VCO control voltage still clearly shows a periodic beat at the reference frequency, which will in turn result in spurious tones.

Figure 3.5 Periodic signal generated by the chargepump mismatch.

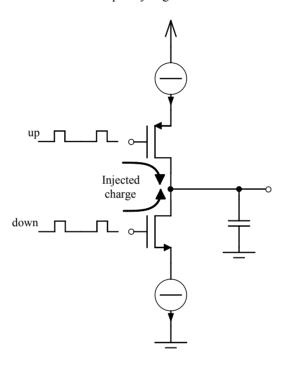

The charge injection through the chargepump switches is illustrated in Figure 3.6. The digital up and down signals from the phase detector will have relatively fast rise and fall times, and thus harmonic components at very high frequencies. Some of these high-

frequency components will be injected to the chargepump output node through the gate-source and gate-drain capacitances ( $C_{GS}$  and  $C_{GD}$ ) of the switch transistor. The capacitances  $C_{GS}$  and  $C_{GD}$  depend on the gate-to-source and gate-to-drain voltages  $V_{GS}$  and  $V_{GD}$ , respectively. Therefore, the charges injected through the up and down switches will depend on the chargepump output voltage. The up and down charges will be equal for one single output voltage value. For all other output voltages, there will be a net charge injected to the output of the chargepump. The PLL will compensate for this excess charge very much in the same way as the chargepump mismatch in Figure 3.5, and a periodic beat at the reference frequency is generated.

Figure 3.6 Charge injection in the chargepump switches.

The third phenomenon typically generating reference spurs is the loop filter leakage. When the PLL is locked, the chargepump is neither pumping up nor down for most of the time. Ideally, a chargepump in this state represents an infinite impedance towards the loop filter. Likewise, the input impedance of the VCO control node is ideally infinite. In practice, however, both the chargepump switches and the VCO control node (typically connected to a varactor diode) will have finite impedances, and there will be a small leakage current that will change the control voltage of the VCO slightly either up or down. The PLL will compensate for the leakage, and thus a periodic beat at the reference frequency is again generated. In PLL's using a discrete loop filter, the leakage currents are normally not a problem. The loop filter capacitors are very large, and a small leakage current will change the loop filter voltage only negligibly. In fully integrated PLL's, however, the leakage may become a problem, since the loop filter capacitors are significantly smaller due to integration limitations.

Quantifying the mechanisms explained above is very difficult, since the spurious power will depend on the actual shape of the interfering waveform. An approach that is relatively accurate and gives useful insight to the problem is given in [19]. It is first assumed that the disturbance on the VCO control line appears as narrow, rectangular pulses having a width  $\Delta t$  and a height  $\Delta V$ . Inserting the Fourier series expansion of the rectangular waveform into the time domain representation of the VCO output waveform yields the following equation for the VCO output:

$$v_{out}(t) = V_0 \cos \left[ \left( \omega_0 + K_{VCO} \frac{\Delta V \Delta t}{T_{ref}} + K_{VCO} V_{CTRL} \right) t \right]$$

$$- K_{VCO} \left[ V_{CTRL} \sum_{n \neq 0} \frac{a_n}{n \omega_{ref}} \sin \left( n \omega_{ref} t + \theta_n \right) \right] \sin \left[ \left( \omega_0 + K_{VCO} \frac{\Delta V \Delta t}{T_{ref}} + K_{VCO} V_{CTRL} \right) t \right]$$

(3.8)

Equation (3.8) indicates sidebands at  $\pm n\omega_{ref}$  from the carrier, where  $\omega_{ref}$  is the phase comparison frequency. Typical approaches to reducing the problem are using large capacitors in the loop filter (to keep  $\Delta V$  to a minimum), and minimizing  $K_{VCO}$  to minimize the modulation index. However, both remedies have their downsides as well: increasing the loop filter capacitance requires increasing the chargepump current proportionally;  $K_{VCO}$  cannot be lowered indefinitely, because the tuning range still needs to cover the desired frequencies plus process, temperature and supply voltage variations.

Table 3.3 shows the reported spurious powers from a few recently published radio frequency synthesizers. Clearly, with a careful design, the spurious specifications of the DCS-1800 system can be met with a margin.

| Author              | Spurious power                                   | Offset frequency  | Туре                       |

|---------------------|--------------------------------------------------|-------------------|----------------------------|

| Rategh et al. [52]  | -45dBc                                           | 11MHz             | Integer-N PLL              |

| Yan et al. [31]     | -79.5dBc                                         | 1.6MHz            | Dual-loop integer-N<br>PLL |

| De Muer et al. [53] | -75 dBc (ref spur)<br>-100 dBc (fractional spur) | 500 kHz<br>26 MHz | Fractional-N PLL           |

| This work [P4]      | -85 dBc                                          | 400 kHz           | Fractional-N PLL           |

| Saul et al. [27]    | -30dBc                                           | N/A               | Direct digital synthesizer |

**Table 3.3:** Spurious power levels of published frequency synthesizers.

#### 3.6 Harmonic tones

Harmonic tones, i.e. signal components at integer multiples of the carrier frequency, are practically always present at the output of the voltage-controlled oscillator. If the output signal is not perfectly sinusoidal, it will always have some power at the harmonic frequencies. The harmonics as such are seldom a critical design parameter for the

system, since the frequencies are typically far outside the band of interest. However, the harmonic content at the output of the local oscillator does affect the quadrature generation, and thus the harmonics must be kept below a certain limit.

Most modern radio systems require quadrature LO signals, i.e. signals with a 90 degree phase difference with respect to each other, to be generated for both the receiver and the transmitter. Any deviation from exactly 90 degrees will deform the signal constellation, and thus adversely affect the bit error rate of the system. The quadrature signals are typically generated either by a passive RC-CR network or by a divide-by-two circuit, both of which are sensitive to the harmonic content of the input signal.

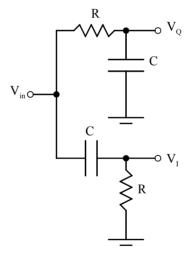

Perhaps the simplest way to generate quadrature signals is to use a passive RC-CR network, the simplest version of which is depicted in Figure 3.7. The signal in the upper branch is shifted by -45° and the signal in the lower branch by +45°, resulting in a phase difference of 90° between the outputs. A single RC-stage gives the desired, symmetrical amplitude and phase response only at a single frequency. Therefore, multistage polyphase filters with wider bandwidth are typically used in practice. However, as shown in [54], the output phase of the polyphase filter is very sensitive to the harmonics of the input signal. Harmonics will shift the zero crossings of the differential signal, thus corrupting the phase relationship of the outputs.

*Figure 3.7* A simple RC-CR network generating quadrature signals.

Another frequently used method for quadrature generation is frequency division. Dividing the input frequency by two with a standard master-slave flip-flop will result in signals with 90° phase difference between the master and the slave latch outputs. The major drawback of this technique, however, is the fact that the VCO and the frequency divider now need to run at twice the local oscillator frequency, which will increase the power dissipation of the synthesizer, or may even be impossible due to technology limitations. The phase accuracy is also dependent on the symmetry of both the frequency divider itself and the loads seen by the divider. Any mismatch will introduce a phase error in the output. The frequency division technique is also sensitive to the harmonic

content of the input signal. The phase accuracy is dependent on having an input signal with exactly 50% duty cycle. Any second harmonic present in the VCO output will deviate the duty cycle from 50%, and will thus introduce a phase error. However, if the VCO is on the same chip with the frequency divider, the signal between the two is likely to be differential, and thus it will have a very low second harmonic.

## 3.7 Settling time

In modern telecommunications systems, the synthesizer often has strict requirements for settling time, defined as the time it takes for the synthesizer to settle to a given accuracy after a frequency step. In time division multiple access (TDMA) systems, the settling time specification is mostly due to the desire to use the same synthesizer for both transmit and receive modes, thus saving power and area. In frequency hopping systems, the relatively frequent changing of the channel frequency is used to make sure that enough packets are received correctly even if a part of the frequency band would be blocked by strong interferers. Independent of the reason for changing the transmit or receive frequency, the system specifications usually set a limit on how fast this needs to be done, and this can be directly translated into a synthesizer settling time requirement.

In the phase-locked loop, being a low-pass control system by nature, the settling time is always inversely proportional to the loop bandwidth. Other constraints, such as stability, reference suppression, and close-in phase noise normally set the upper limit for the loop bandwidth. On the other hand, the settling time specification typically sets the fundamental lower limit.

Using the standard notation of feedback theory, a second-order loop has a closed-loop transfer function of

$$H(s) = \frac{2\xi\omega_n s + \omega_n^2}{s^2 + 2\xi\omega_n s + \omega_n^2},\tag{3.9}$$

where  $\xi$  is the damping factor, and  $\omega_n$  is the natural frequency. From the step response of the closed-loop transfer function we can derive the minimum required natural frequency for the loop to settle within a given maximum relative frequency error  $\delta$  (absolute frequency error divided by the total frequency step) in a given switching time  $t_{sw}$  to be

$$\omega_n = \frac{-\ln\left(\delta\sqrt{1-\delta^2}\right)}{\xi t_{sw}}.$$

(3.10)

Assuming the damping factor  $\xi$  to have a value of 0.707 (optimal value in most cases), we can express the minimum loop crossover frequency as

$$\omega_c = \frac{-\ln\left(\frac{\delta}{\sqrt{2}}\right)}{t_{\text{sw}}}.$$

(3.11)

In a DCS-1800 handset, the maximum frequency step occurs when switching from the lowest transmit channel to the highest receive channel, and is equal to 170 MHz. The frequency has to settle within  $\pm 0.1$  ppm, i.e. 180 Hz, in three time slots, i.e. 1730.7  $\mu$ s. To leave some margin, we use a switching time requirement of 1500  $\mu$ s, resulting in a minimum loop bandwidth of 1.5 kHz.

While the handset settling time requirements are relatively relaxed, a base station synthesizer needs to settle significantly faster. In the worst case, the base station communicates with a different handset during every time slot, having only the guard time between slots (30.5 µs) for channel switching. Based on Equation (3.11), this would give a minimum loop bandwidth of 462 kHz. However, with a channel spacing of 200kHz, the reference feedthrough requirement typically sets the maximum loop bandwidth to approximately 20kHz. These conflicting requirements call for more complex frequency generation techniques. A typical method in base stations is the so called ping-pong synthesizer. The base station has two separate synthesizers, allowing one to switch to a new channel during a time slot, while the other one is being used. During the slot guard time, the synthesizers switch roles, and during the next slot, the other synthesizer is used.

## 3.8 Other requirements

In addition to the performance requirements set by the radio system, there are requirements set on the frequency synthesizer by the commercial aspects of the product. Especially in mobile applications, size and battery life time play a very important role in marketing the product. For the IC designer, these requirements can be reduced to power dissipation and external component count.

The battery life time is an increasingly important parameter in mobile applications. For instance in GSM handsets, the typical standby times have increased from 18 hours (Nokia 880) to 430 hours (Nokia 6310) in the last ten years. At the same time, the handsets, and consequently their batteries, have become significantly smaller and lighter. The power that is available to implement a function, for example frequency synthesis, has decreased dramatically.

As the integrated circuits in a mobile device contain larger and larger functional entities, the size of the entire device is more and more determined by the number of external components required by the IC's. For example, the Nokia 6161 cell phone has a printed circuit board area of 40 cm<sup>2</sup>, which contains only 15 integrated circuits but a total of 405 external passive components (232 capacitors, 149 resistors, and 24 inductors) [55]. It is obvious that the board area and thus the minimum achievable phone size is determined by the number of passives, not the number of IC's. Therefore, minimizing the number of external components should be a very important design target in any IC design project.

# 4 Fractional-N phase-locked loops

Conventional integer-N PLL synthesizers divide the output frequency by an integer number to produce the phase comparison frequency. Consequently, the output frequency can only be an integer multiple of the phase comparison frequency. This limitation can be very troublesome in some applications, as will be further explained in Section 4.1.

A solution to the problems posed by the integer division is the fractional-N phase-locked loop. In a fractional-N loop, the divisor *N* is not constant, but varies between integer values in such a way that the average divisor can be a fractional number. This approach has several advantages that are discussed in Section 4.2.

Although the fractional division eliminates some of the problems caused by integer division, it also creates new problems. These will be discussed in Section 4.3, and some proposed solutions to these problems in Section 4.4.

## 4.1 Problems of integer-N synthesizers

In most digital telecommunications systems, the channel spacing is very small compared to the carrier frequency, e.g. 200 kHz in GSM and DCS-1800, or 25 kHz in the Japanese PDC system. To be able to synthesize all the required channel frequencies, the reference frequency of an integer-N synthesizer must be equal to or smaller than the channel spacing. This leads to very high values for the divisor *N*. For example in the DCS-1800 system, the carrier frequency is between 1710 and 1880 MHz, resulting in *N* varying from 8550 to 9400.

The large division ratio leads to a need for an extremely high quality reference. The noise transfer function from the reference to the output multiplies the reference noise by N at offset frequencies smaller than the loop bandwidth. An N of 9400 means that the reference noise close to the carrier is amplified by almost 40dB. To make sure that the reference oscillator does not dominate the performance of the entire synthesizer, its specifications must be at least 50-60dB tougher than the specifications for the voltage-controlled oscillator. In practice, this means that the reference must be a high-quality crystal oscillator. The noise of the phase detector is amplified by the same factor as the reference noise, and therefore the phase detector noise must be very low as well. However, phase detectors are typically not very noisy, and the crystal oscillator noise normally always dominates over the phase detector noise.

The fact that the reference frequency must be very low leads to several difficulties. In all real PLL's the reference frequency is to some extent fed through to the output, causing spurious tones at offsets of  $\pm n \cdot f_{ref}$  from the carrier frequency. These spurious tones lie in the middle of the adjacent channels, and thus must be suppressed as much as possible. To guarantee enough of suppression, the loop bandwidth must be kept below approximately one tenth of the reference frequency.

When switching from one channel to another, the switching time of the synthesizer is inversely proportional to the loop bandwidth, i.e. the smaller the loop bandwidth, the longer the switching time. Together, the specifications for the reference suppression and

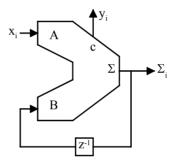

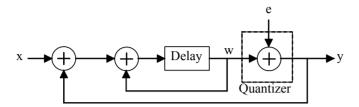

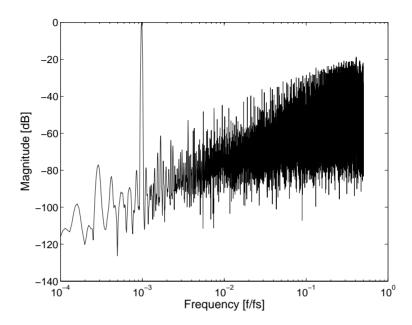

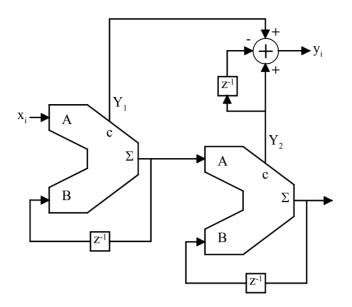

the switching time strongly limit the choice of the loop bandwidth. The bandwidth must be small enough to suppress the reference feedthrough. On the other hand, the loop bandwidth must be large enough to allow fast switching. In some systems, the range of possible loop bandwidths between these bounds can be very small or even nonexistent.