NAIST-IS-DD0561211

## **Doctoral Dissertation**

## Studies on Core-Based Testing of System-on-Chips Using Functional Bus and Network-on-Chip Interconnects

Fawnizu Azmadi Hussin

September 18, 2008

Department of Information Processing Graduate School of Information Science Nara Institute of Science and Technology

A Doctoral Dissertation submitted to Graduate School of Information Science, Nara Institute of Science and Technology in partial fulfillment of the requirements for the degree of Doctor of ENGINEERING

Fawnizu Azmadi Hussin

Thesis Committee:

Professor Hideo Fujiwara(Supervisor)Professor Yasuhiko Nakashima(Co-supervisor)Associate Professor Michiko Inoue(Co-supervisor)Assistant Professor Tomokazu Yoneda(Co-supervisor)

## Studies on Core-Based Testing of System-on-Chips Using Functional Bus and Network-on-Chip Interconnects\*

Fawnizu Azmadi Hussin

#### Abstract

The tests of a complex system such as a microprocessor-based system-onchip (SoC) or a network-on-chip (NoC) are difficult and expensive. In this thesis, we propose three core-based test methods that reuse the existing functional interconnects-a flat bus, hierarchical buses of multiprocessor SoC's (MPSoC), and a NoC-in order to avoid the silicon area cost of a dedicated test access mechanism (TAM). However, the use of functional interconnects as functional TAM's introduces several new problems.

During tests, the interconnects-including the bus arbitrator, the bus bridges, and the NoC routers-operate in the functional mode to transport the test stimuli and responses, while the core under tests (CUT) operate in the test mode. Second, the test data is transported to the CUT through the functional bus, and not directly to the test port. Therefore, special core test wrappers that can provide the necessary control signals required by the different functional interconnect are proposed. We developed two types of wrappers, one buffer-based wrapper for the bus-based systems and another pair of complementary wrappers for the NoCbased systems.

Using the core test wrappers, we propose test scheduling schemes for the three functionally different types of interconnects. The test scheduling scheme for a flat bus is developed based on an efficient packet scheduling scheme that minimizes both the buffer sizes and the test time under a power constraint. The scheduling

<sup>\*</sup> Doctoral Dissertation, Department of Information Processing, Graduate School of Information Science, Nara Institute of Science and Technology, NAIST-IS-DD0561211, September 18, 2008.

scheme is then extended to take advantage of the hierarchical bus architecture of the MPSoC systems. The third test scheduling scheme based on the bandwidth sharing is developed specifically for the NoC-based systems. The test scheduling is performed under the objective of co-optimizing the wrapper area cost and the resulting test application time using the two complementary NoC wrappers.

For each of the proposed methodology for the three types of SoC architecture, we conducted a thorough experimental evaluation in order to verify their effectiveness compared to other methods.

#### **Keywords**:

Wrapper design, functional TAM, SoC test scheduling, NoC-reuse

## List of Publications

### Journal Paper

- Fawnizu Azmadi Hussin, Tomokazu Yoneda, Alex Orailoglu and Hideo Fujiwara, "Scheduling power-constrained tests through the SoC functional bus," IEICE Transactions on Information and Systems, Vol. E91-D, No. 3, pp. 736-746, Mar. 2008.

- Fawnizu Azmadi Hussin, Tomokazu Yoneda and Hideo Fujiwara, "NoCcompatible wrapper design and optimization under channel bandwidth and test time constraints," IEICE Transactions on Information and Systems, Vol. E91-D, No. 7, pp. 2008–2017, July 2008.

- Fawnizu Azmadi Hussin, Tomokazu Yoneda and Hideo Fujiwara, "On NoC bandwidth sharing for the optimization of area cost and test application time," IEICE Transactions on Information and Systems, Vol. E91-D, No. 7, pp. 1999–2007, July 2008.

### International Conferences (Reviewed)

- Fawnizu Azmadi Hussin, Tomokazu Yoneda, Alex Orailoglu and Hideo Fujiwara, "Power-constrained SoC test schedules through utilization of functional buses," 24th IEEE International Conference on Computer Design (ICCD'06), pp. 230-236, Oct. 2006.

- 2. Fawnizu Azmadi Hussin, Tomokazu Yoneda, Alex Orailoglu and Hideo Fujiwara, "Core-based testing of multiprocessor system-on-chips utilizing hier-

archical functional buses," 12th Asia and South Pacific Design Automation Conference 2007 (ASP-DAC'07), pp. 720–725, Jan. 2007.

- 3. Fawnizu Azmadi Hussin, Tomokazu Yoneda and Hideo Fujiwara, "Optimization of NoC wrapper design under bandwidth and test time constraints," 12th IEEE European Test Symposium (ETS'07), pp. 35–40, May 2007.

- 4. Fawnizu Azmadi Hussin, Tomokazu Yoneda and Hideo Fujiwara, "Area overhead and test time co-optimization through NoC bandwidth sharing," IEEE 16th Asian Test Symposium (ATS'07), pp. 459–462, Oct. 2007.

### **Technical Reports**

- Fawnizu Azmadi Hussin, Tomokazu Yoneda, Alex Orailoglu and Hideo Fujiwara, "Power-conscious microprocessor-based testing of system-on-chip," Technical Report of IEICE (VLD2006-6), Vol. 106, No. 32, pp. 25–30, May 2006.

- Fawnizu Azmadi Hussin, Tomokazu Yoneda and Hideo Fujiwara, "NoC wrapper optimization under channel bandwidth and test time constraints," Technical Report of IEICE (DC2006-80), Vol. 106, No. 528, pp. 1–6, Feb. 2007.

### Award

1. IEEE Kansai Section Student Paper Award, Feb. 2008.

# For my wife, who offered me unconditional love and support throughout the course of this thesis.

Fazleen Mustapha

And to my son, may you be inspired.

Faheem Fawnizu

"We choose to go to the moon."

"We choose to go to the moon in this decade and do the other things, not because they are easy, but because they are hard, because that goal will serve to organize and measure the best of our energies and skills, because that challenge is one that we are willing to accept, one we are unwilling to postpone, and one which we intend to win, and the others, too."

-John Fitzgerald Kennedy, September 12, 1962

Some things are worth doing not because they are easy, but because they are hard.

# Contents

| 1                  | Int | roduction 1                                                | L |

|--------------------|-----|------------------------------------------------------------|---|

|                    | 1.1 | The Trend Toward a Core-based Test Methodology             | L |

|                    | 1.2 | System-on-Chip Architecture                                | 2 |

|                    | 1.3 | Scan-based Testing of Embedded Cores                       | 7 |

|                    |     | 1.3.1 Core Test Architecture                               | ) |

|                    | 1.4 | Reuse of Functional Interconnects as TAM                   | 3 |

|                    |     | 1.4.1 Impact on the Design Flow                            | 3 |

|                    | 1.5 | Contributions of This Thesis                               | 7 |

|                    | 1.6 | Thesis Organization                                        | } |

| $\mathbf{\hat{2}}$ | Wra | opper Design and Test Scheduling for System-on-Chips Using |   |

|                    |     | inctional Bus 21                                           |   |

|                    | 2.1 | Introduction                                               |   |

|                    | 2.2 | Related Work                                               | F |

|                    | 2.3 | Motivation                                                 | 7 |

|                    | 2.4 | Technical Overview                                         |   |

|                    | 2.5 | Test Support Architecture                                  | ì |

|                    |     | 2.5.1 Wrapper Scan Chain Design                            | 5 |

|                    |     | 2.5.2 Operation of the Buffer-based Test Architecture 35   | ) |

|                    | 2.6 | Packet Delivery Scheduling Algorithm                       | ) |

|                    |     | 2.6.1 Terminology                                          | ) |

|                    |     | 2.6.2 Power and Heat Dissipation Problem                   | ) |

|                    |     | 2.6.3 Scan Frequency Reductions                            |   |

|                    |     | 2.6.4 Forming Non-Overlapping Test Groups                  | ł |

|                    |     | 2.6.5 Buffer Sizes                                         |   |

|   |     | 2.6.6   | PAcket Set Scheduling (PASS) Algorithm                    | 45   |

|---|-----|---------|-----------------------------------------------------------|------|

|   | 2.7 | Advant  | ages of the Buffer-based Wrapper                          | 54   |

|   |     | 2.7.1   | Bandwidth Matching with Low Speed Testers                 | 55   |

|   | 2.8 |         | mental Results                                            | 55   |

|   | 2.9 | -       | sion                                                      | 64   |

| 3 | Tes | t Sched | uling for Multiprocessor SoC's with Hierarchical Buse     | s 67 |

|   | 3.1 | Introdu | uction                                                    | 67   |

|   | 3.2 | Model   | of Multiprocessor System-on-Chips (MPSoC)                 | 69   |

|   |     | 3.2.1   | Data Transfer Between Cores and Processors                | 70   |

|   | 3.3 | Scope   |                                                           | 71   |

|   | 3.4 | Buffer- | Based Test Architecture                                   | 73   |

|   | 3.5 | Test Sc | heduling Methodology                                      | 76   |

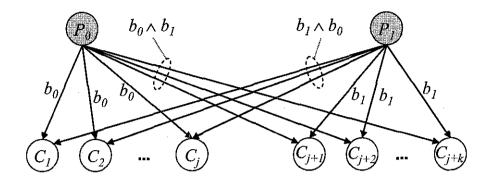

|   |     | 3.5.1   | Resource Graph                                            | 77   |

|   |     | 3.5.2   | Test Configuration Graph (TCG)                            | 79   |

|   |     | 3.5.3   | Equivalent Test Configuration Graphs                      | 81   |

|   |     | 3.5.4   | Eliminating the Obviously Redundant Test Configurations   | 82   |

|   |     | 3.5.5   | Test Group Formation Under Power-Constrained Test Schedu  | l-   |

|   |     |         | ing                                                       | 84   |

|   |     | 3.5.6   | Complexity of Packet Set Scheduling for MPSoC             | 91   |

|   | 3.6 | Optimi  | zing the PASS Algorithm for Hierarchical Bus MPSoC's      |      |

|   |     | (MPPA   | ASS)                                                      | 94   |

|   |     | 3.6.1   | Motivation for Incorporating the Hierarchy Information in |      |

|   |     |         | the Packet Delivery Sequence                              | 96   |

|   |     | 3.6.2   | Improving PASS Schedule through Random Permutation .      | 98   |

|   |     | 3.6.3   | Simulation Environment and Procedures for the Test Data   |      |

|   |     |         | Transportation in Hierarchical Bus MPSoC's                | 101  |

|   | 3.7 | Experir | mental Results                                            | 104  |

|   | 3.8 | Conclus | sion                                                      | 109  |

| 4 | Net | work-o  | n-Chip Interconnect Architecture                          | 111  |

|   | 4.1 | Introdu | action                                                    | 111  |

|   | 4.2 | NoC C   | ommunication Services                                     | 114  |

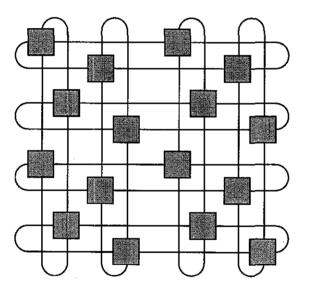

|   | 4.3 | Networ  | k Topologies                                              | 116  |

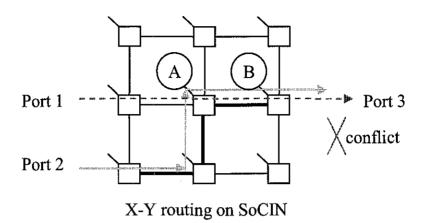

|   |     | 4.3.1  | NoC Routing and Forwarding                                                                        | 117 |

|---|-----|--------|---------------------------------------------------------------------------------------------------|-----|

|   | 4.4 | NoC 4  | Architectures                                                                                     | 120 |

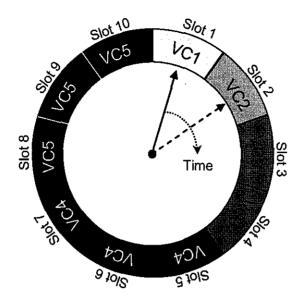

|   |     | 4.4.1  | SoCIN Network Architecture                                                                        | 120 |

|   |     | 4.4.2  | Æthereal NoC Architecture                                                                         | 122 |

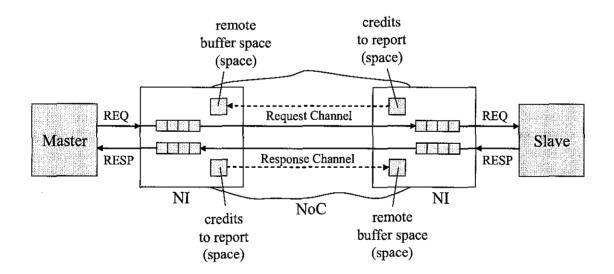

|   |     | 4.4.3  | IP Core Model for Æthereal NoC                                                                    | 125 |

| 5 | No  | C-com  | patible Wrapper Design and Optimization                                                           | 127 |

|   | 5.1 | Introd | luction $\ldots$ | 127 |

|   | 5.2 | Relate | ed Work                                                                                           | 129 |

|   | 5.3 | NoC I  | Reference Model                                                                                   | 130 |

|   | 5.4 | IEEE   | Std. 1500 Wrapper Architecture                                                                    | 131 |

|   | 5.5 | NoC-c  | compatible Wrapper Architecture                                                                   | 133 |

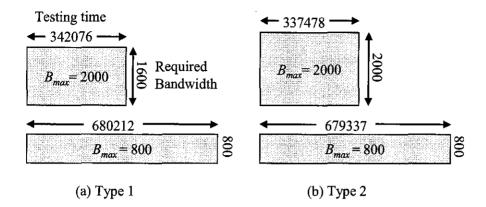

|   |     | 5.5.1  | Type 1 NoC-compatible Wrapper: Interfacing the PDI/PDO                                            |     |

|   |     |        | Ports to the Scan Chains                                                                          | 134 |

|   |     | 5.5.2  | Type 1 NoC-compatible Wrapper: Inefficient NoC Band-                                              |     |

|   |     |        | width Utilization                                                                                 | 140 |

|   |     | 5.5.3  | Type 2 NoC-compatible Wrapper: Optimizing the NoC                                                 |     |

|   |     |        | Bandwidth Utilization                                                                             | 141 |

|   | 5.6 | Optim  | nization of the NoC-compatible Wrappers                                                           | 144 |

|   | 5.7 | Exper  | imental Results                                                                                   | 147 |

|   | 5.8 | Conch  | usion                                                                                             | 154 |

| 6 | No  | C Test | Scheduling Through Bandwidth Sharing                                                              | 157 |

|   | 6.1 | Introd | luction                                                                                           | 157 |

|   | 6.2 | Overv  | iew of the Proposed Bandwidth Sharing Scheme                                                      | 160 |

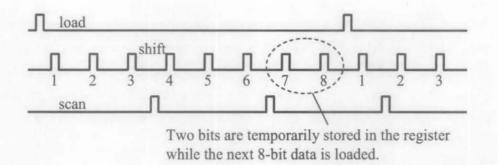

|   | 6.3 |        |                                                                                                   | 161 |

|   | 6.4 |        | and IP Core Models                                                                                | 164 |

|   | 6.5 |        | Test Scheduling                                                                                   | 165 |

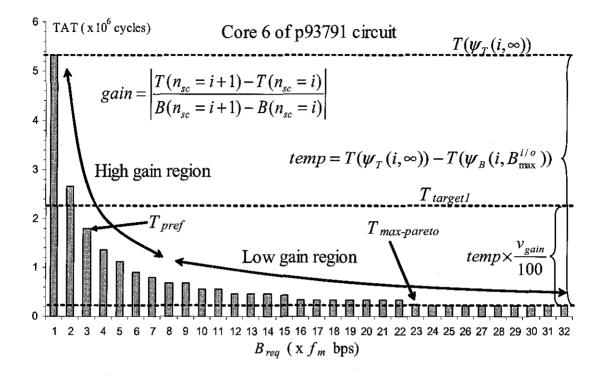

|   |     | 6.5.1  | Characteristics of NoC-compatible Wrappers                                                        | 166 |

|   |     | 6.5.2  | Test Scheduling through NoC Bandwidth Sharing                                                     | 167 |

|   |     | 6.5.3  | Optimum Wrapper under Bandwidth Constraint                                                        | 171 |

|   |     | 6.5.4  | Cost Function for Wrapper Optimization                                                            | 171 |

|   |     | 6.5.5  | Lower Bound on Test Time                                                                          | 173 |

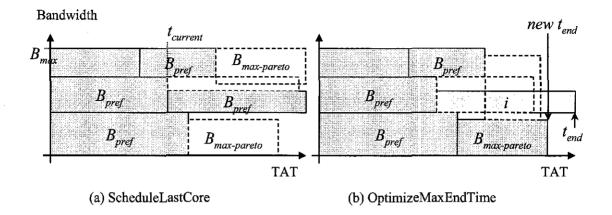

|   |     | 6.5.6  | Schedule Optimization through Rectangle Packing                                                   | 175 |

|   |     |        |                                                                                                   |     |

|   | 6.6  | Experimental Results    | 180 |

|---|------|-------------------------|-----|

|   | 6.7  | Conclusion              | 184 |

| 7 | Con  | clusion and Future Work | 185 |

|   | 7.1  | Summary of the Thesis   | 185 |

|   | 7.2  | Future Work             | 187 |

|   | Ackı | nowledgments            | 189 |

|   | Bibl | iography                | 192 |

# List of Figures

| 1.1  | System design and test flow for dedicated TAM approach | 5  |

|------|--------------------------------------------------------|----|

| 1.2  | A microprocessor-based SoC                             | 6  |

| 1.3  | Core-based SoC architecture                            | 8  |

| 1.4  | Definitions of TAM and wrapper.                        | 9  |

| 1.5  | Core-based SoC with DfT                                | 10 |

| 1.6  | IP core and 1500 wrapper                               | 11 |

| 1.7  | Single scan chain configuration.                       | 12 |

| 1.8  | Alternative representation of a 1500-wrapped core.     | 13 |

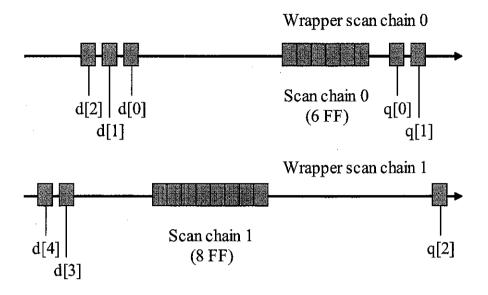

| 1.9  | Two wrapper scan chains configuration                  | 14 |

| 1.10 | Three wrapper scan chains configuration                | 15 |

| 1.11 | System design and test flow for interconnect reuse     | 17 |

| 2.1  | Cost of silicon vs. cost of test.                      | 22 |

| 2.2  | Packet-based test data transportation.                 | 28 |

| 2.3  | Buffer-based test architecture.                        | 28 |

| 2.4  | Effect of repetitive packet delivery sequence          | 29 |

| 2.5  | ATE interface through a TIC.                           | 32 |

| 2.6  | Core test architecture.                                | 34 |

| 2.7  | Break down of the scan chain architecture              | 36 |

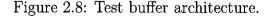

| 2.8  | Test buffer architecture.                              | 37 |

| 2.9  | Variable frequency scheduling                          | 43 |

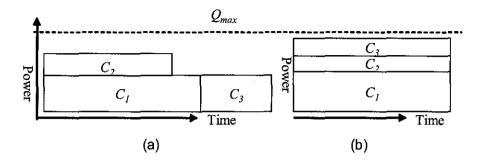

| 2.10 | Non-overlapping test groups                            | 44 |

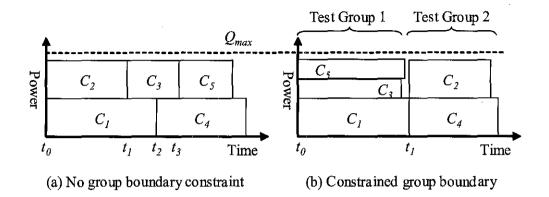

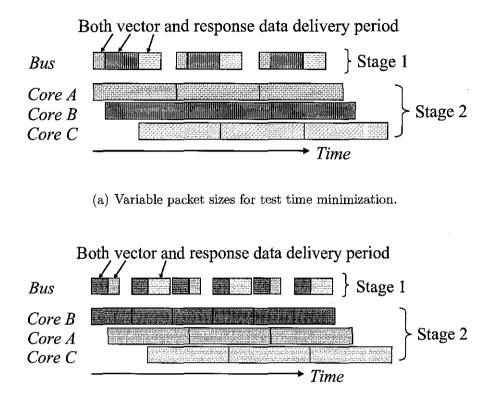

| 2.11 | Packet size and test time optimization                 | 46 |

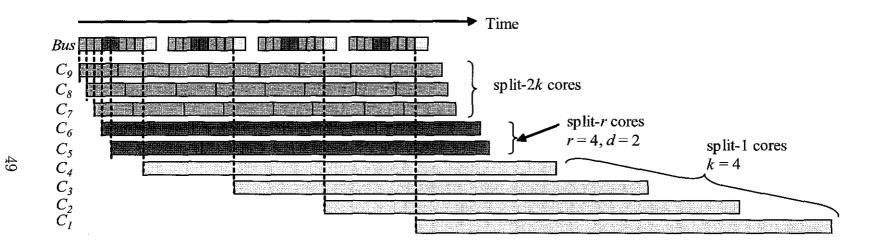

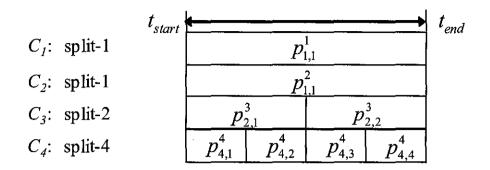

| 2.12 | Packet set scheduling algorithm                        | 49 |

| 2.13 | Normalizing the packet's loading time.                 | 53 |

| 2.14 | Packet set delivery sequence                           | 53 |

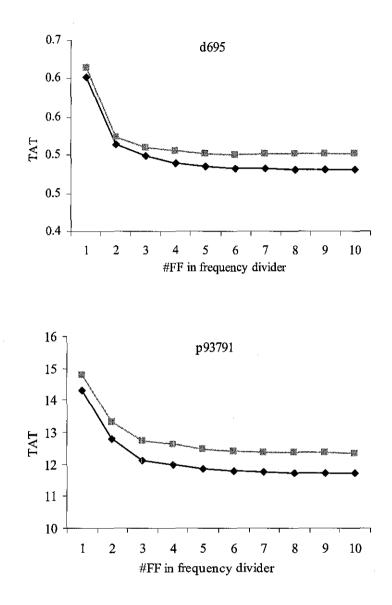

| 2.15 | Bandwidth matching mechanism                                           |

|------|------------------------------------------------------------------------|

| 2.16 | TAT vs. cost of frequency divider                                      |

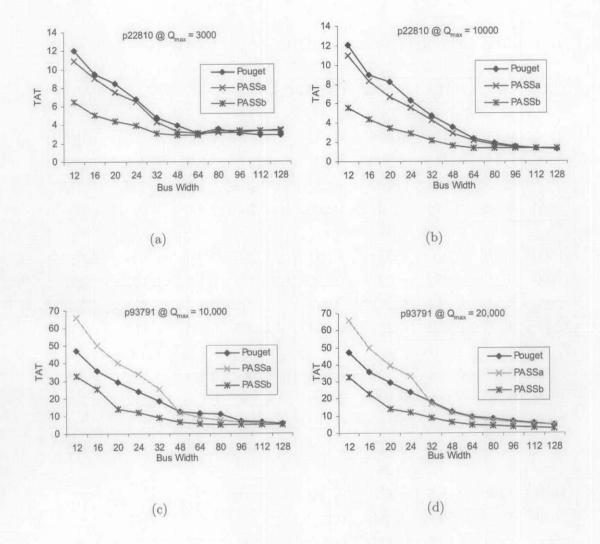

| 2.17 | TAT vs. bus width                                                      |

| 2.18 | TAT vs. buffer size                                                    |

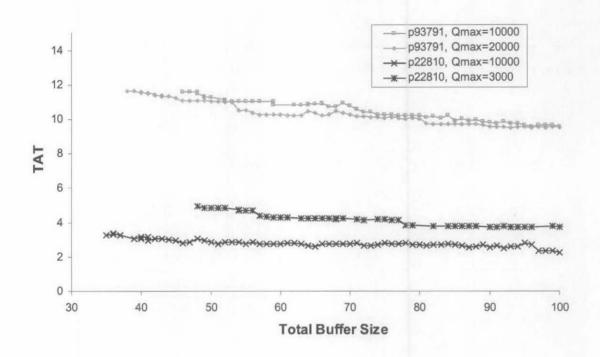

| 2.19 | TAT reduction through bus frequency scaling                            |

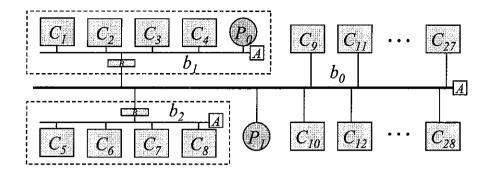

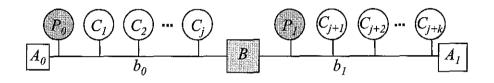

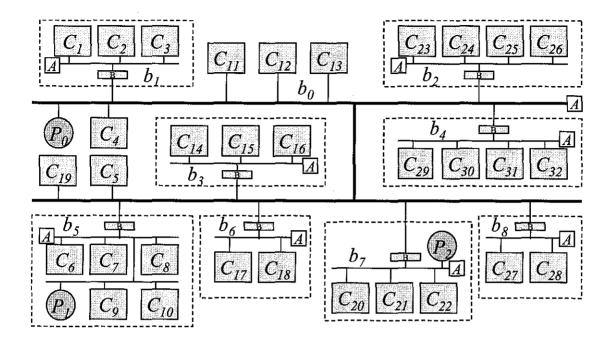

| 3.1  | General MPSOC architecture                                             |

| 3.2  | General MPSoC architecture                                             |

| 3.3  | Example of a round-robin scheduling                                    |

| 3.4  | An example hierarchical bus MPSoC                                      |

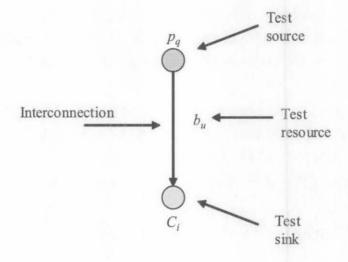

| 3.5  | Components of a resource graph                                         |

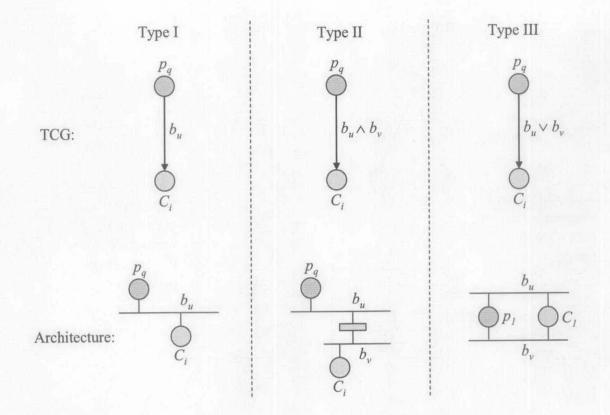

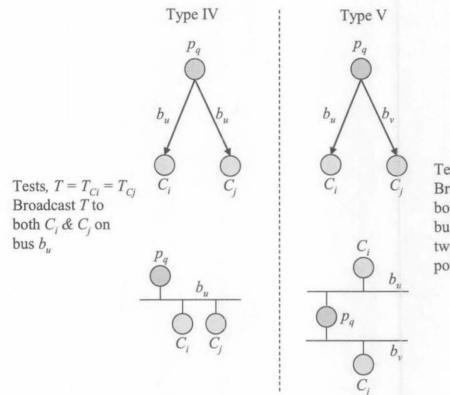

| 3.6  | Unicast-based test configurations graphs                               |

| 3.7  | Broadcast-based test configurations graphs                             |

| 3.8  | Equivalent test configuration graphs                                   |

| 3.9  | Power-constrained test grouping for a bus segment                      |

| 3.10 | TCG selection procedure                                                |

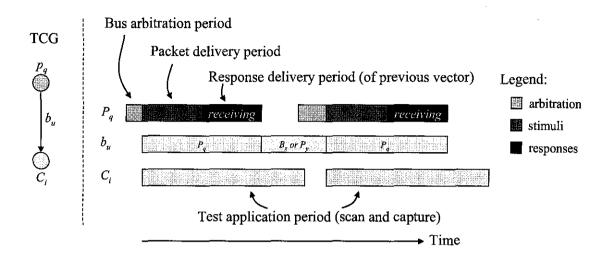

| 3.11 | Packet delivery timing (local bus transfer)                            |

| 3.12 | Packet delivery timing (through a non-transparent two-port bridge). 93 |

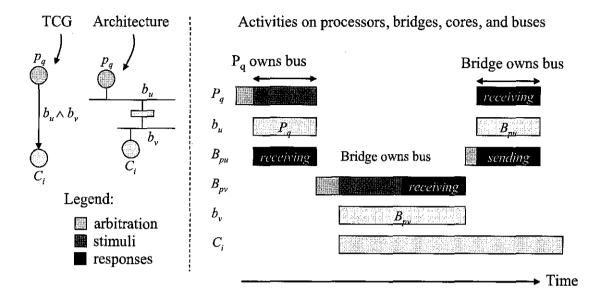

| 3.13 | Packet delivery timing (bus activities)                                |

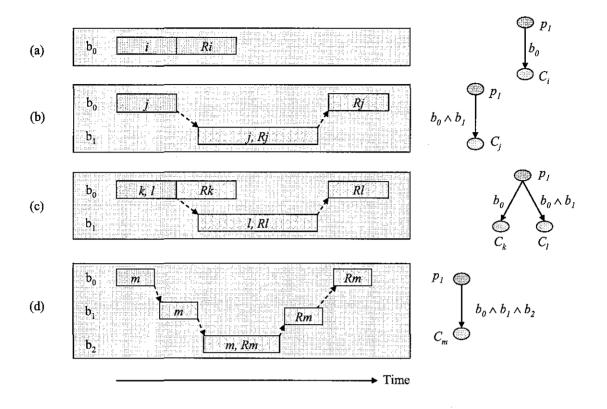

| 3.14 | PASS packet delivery sequence                                          |

| 3.15 | Contention in hierarchical-bus MPSoC                                   |

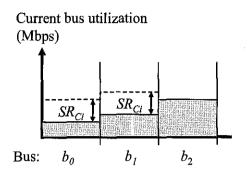

| 3.16 | Increasing the efficiency of bus utilization                           |

| 3.17 | Optimizing the packet delivery sequence (MPPASS) 100                   |

| 3.18 | Event-driven data transfer simulator                                   |

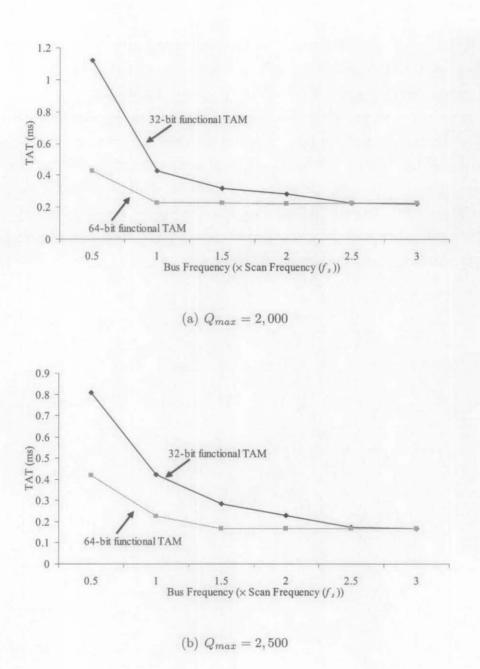

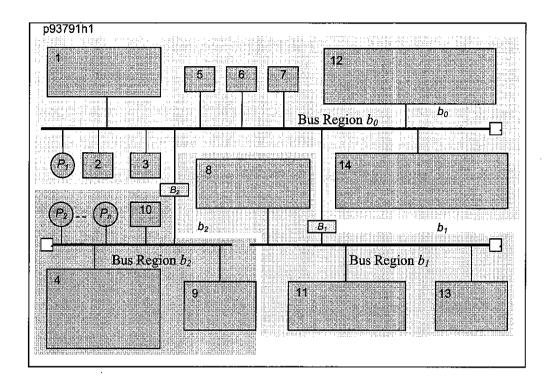

| 3.19 | Modified benchmark circuits                                            |

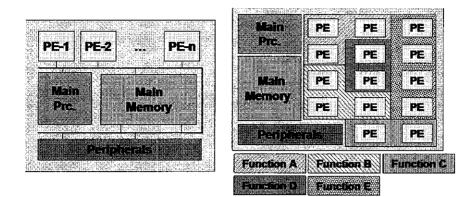

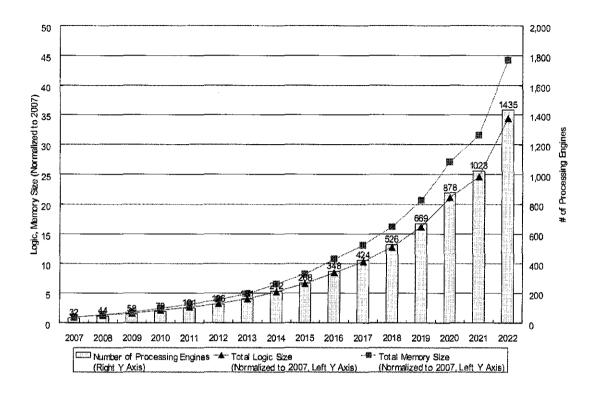

| 4.1  | ITRS 2007's SoC consumer architecture template                         |

| 4.2  | ITRS 2007's SoC consumer design complexity trend 113                   |

| 4.3  | Abstract data communication model                                      |

| 4.4  | Transparent services of the NoC                                        |

| 4.5  | Mesh network topology                                                  |

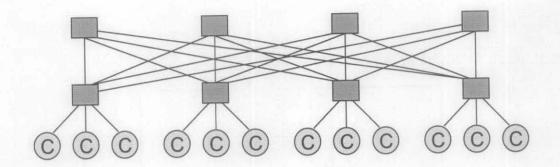

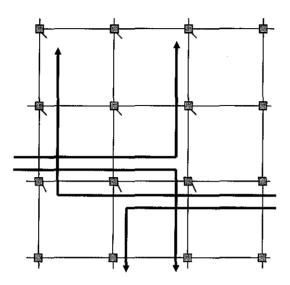

| 4.6  | Fat-tree topology                                                      |

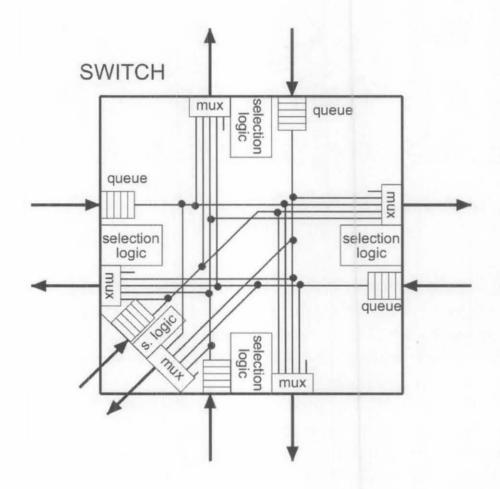

| 4.7  | NoC switch architecture                                                |

| 4.8  | XY-routing algorithm                                                   |

| 4.9  | TDM-based bandwidth allocation scheme.             | 123 |

|------|----------------------------------------------------|-----|

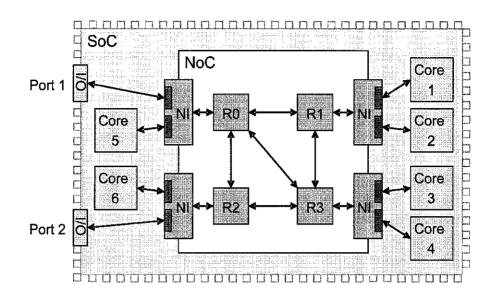

| 4.10 | SoC model based on the Æthereal NoC                | 124 |

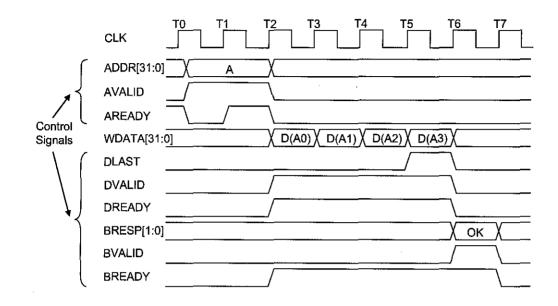

| 4.11 | Transaction-based on-chip communication.           | 125 |

| 4.12 | IP core model                                      | 126 |

| 5.1  | IP core model                                      | 131 |

| 5.2  | IEEE 1500 wrapper scan chain elements.             | 133 |

| 5.3  | Functional data port-based wrapper scan chain.     | 136 |

| 5.4  | Type 1 NoC-compatible wrapper                      | 138 |

| 5.5  | Wrapper boundary cells.                            | 139 |

| 5.6  | Scan rate and required bandwidth of Type 1 wrapper | 141 |

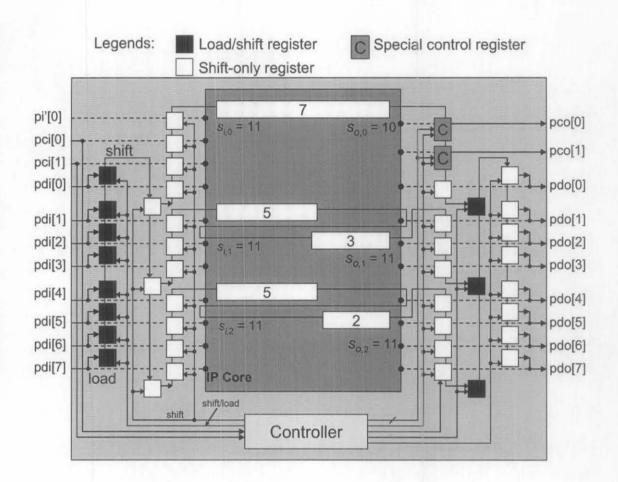

| 5.7  | Type 1 NoC-compatible wrapper                      | 142 |

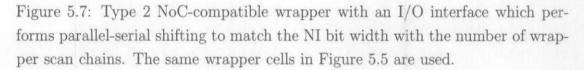

| 5.8  | Control signals for Type 2 wrapper.                | 143 |

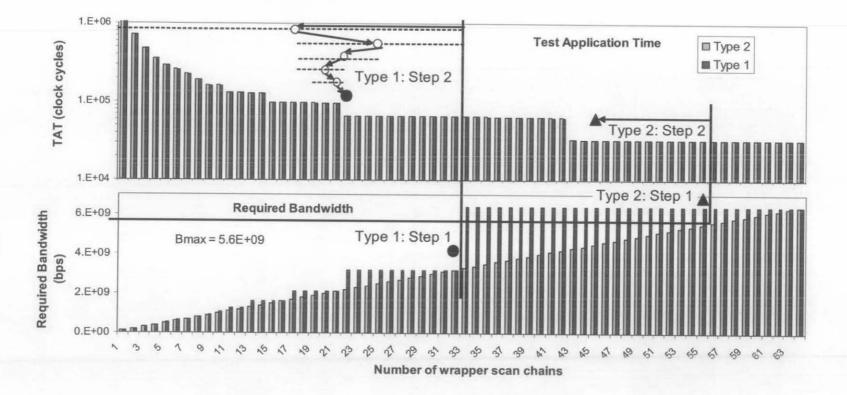

| 5.9  | Test schedule optimization scheme.                 | 145 |

| 5.10 | NoC-compatible wrapper optimization.               | 146 |

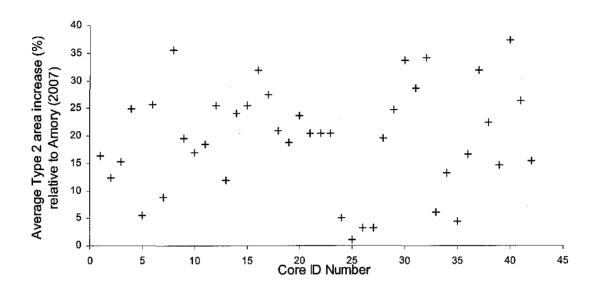

| 5.11 | Area comparison for Type 2 wrapper.                | 154 |

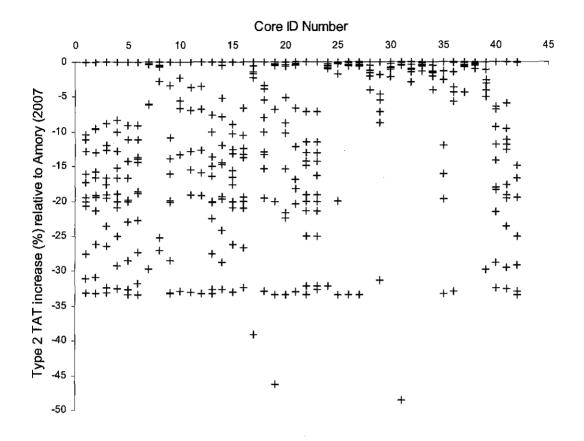

| 5.12 | TAT comparison for Type 2 wrapper                  | 155 |

| 6.1  | Dedicated path test methodology.                   | 158 |

| 6.2  | Bandwidth sharing methodology.                     | 159 |

| 6.3  | Basic-cell groups for router testing.              | 162 |

| 6.4  | Wrapper configurations for dedicated path approach | 163 |

| 6.5  | SoCIN-based NoC architecture for d695 [1].         | 163 |

| 6.6  | SoC model based on the Æthereal NoC                | 165 |

| 6.7  | IP core model interfaced to the NI port.           | 166 |

| 6.8  | NoC-based SoC model                                | 169 |

| 6.9  | Master-slave communication model                   | 169 |

| 6.10 | Representing tests as rectangles                   | 175 |

| 6.11 | High and low gain regions.                         | 178 |

| 6.12 | Test schedule optimization                         | 180 |

# List of Tables

| 2.1 | Selected benchmark circuits                                              | 57  |

|-----|--------------------------------------------------------------------------|-----|

| 2.2 | Experimental setup.                                                      | 59  |

| 2.3 | Test application time of h953                                            | 60  |

| 2.4 | Test application time of d695                                            | 62  |

| 2.5 | Performance comparison of several approaches                             | 63  |

| 2.6 | Average buffer size vs. TAT                                              | 63  |

| 3.1 | TAT of IPASS vs. TAM.                                                    | 107 |

| 3.2 | IPASS vs. dedicated TAM                                                  | 108 |

| 3.3 | Flat bus p22810h1                                                        | 109 |

| 3.4 | Hierarchical bus MPSoC (p22810h2)                                        | 110 |

| 3.5 | Average input buffer sizes per core                                      | 110 |

| 5.1 | TAT comparison for Core 6.                                               | 149 |

| 5.2 | TAT comparison for Core 17                                               | 150 |

| 5.3 | TAT comparison for a small circuit.                                      | 151 |

| 5.4 | TAT comparison for Core 6 of p93791.                                     | 151 |

| 5.5 | TAT comparison for Core 17 of p93791                                     | 152 |

| 5.6 | Wrapper optimization results.                                            | 152 |

| 5.7 | List of ITC'02 benchmark cores                                           | 153 |

| 6.1 | Type 1 and Type 2 wrapper characteristics.                               | 167 |

| 6.2 | Area overhead comparison between Type 1 and Type 2 wrappers.             | 181 |

| 6.3 | TAT for several hardware cost $(\beta)$ and time cost $(\alpha)$ weights | 181 |

| 6.4 | TAT for several $B_{max}^{i/o}$ . $[\alpha = 1, \beta = 0]$              | 183 |

| 6.5 | Dedicated path versus shared bandwidth                                   | 184 |

## Chapter 1

## Introduction

## 1.1 The Trend Toward a Core-based Test Methodology

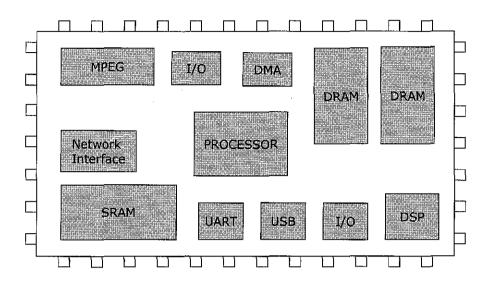

Tests of an integrated circuit are required in order to weed out the bad chips from the good ones. Chip test is an expensive process in the manufacturing of an integrated circuit. From the design perspective, in order to keep up with the Moore's Law in terms of design complexity and the transistor counts, chip designers break the designs into independent subsystem blocks (commonly known as intellectual property (IP) cores). Each subsystem can be a simple combinational logic or can be as complex as a multi-core microprocessor. Such design style is called a System-on-a-Chip (SoC).

System designers are adapting to the SoC design methodology because of its efficiency compared to the traditional system-on-board approach. The main benefit of the SoC approach is that it can drastically shorten the design cycle by allowing pre-designed cores and their associated test sets to be reused. The International Technology Roadmap for Semiconductors (ITRS) 2007 Edition [2] describes the *Increasing Device Integration* trends as one of the Key Drivers in the Test and Test Equipment section.

"... Increased device integration forces a re-integration of test solutions to maintain scaling of test costs and product quality. The optimized test solutions for stand-alone RAMs, cores, and other blocks typically do not scale linearly without modification, additional DFT, or new partitioning to the integrated device test solutions. In particular, additional DFT in-die or even in-package may be required to provide access to and testing of embedded blocks and cores..." -ITRS, 2007 Edition

Most of the industrial practitioners today does not yet embrace the corebased test approach as mentioned and recommended in the ITRS report. The preferred solution is still to flatten the core-based hierarchical design and apply the traditional test scheme—apply ATPG and test of the SoC as a single, flat, and extremely large and complex design. However, it makes more sense to consider core-based testing as the design complexity increases. This is particularly true when some of the embedded IP cores are outsourced from external IP providers. For that purpose, the IEEE 1500 standard [3, 4] was developed to support this core-based test reuse methodology.

Before discussing further the test methodology proposed in this dissertation, we will first look at the target SoC architecture and the test approach for the individual embedded logic core.

### **1.2** System-on-Chip Architecture

We can find several slightly different definitions of a system-on-a-chip. It is loosely defined as an entire system integrated on a single chip. It may include one or more cores with user-defined logic (UDL) integrated by the core user or system integrator. The general idea is that a SoC technology includes the design, manufacturing and packaging of all the necessary electronic circuits and parts for a complete "system" (such as the chips for cell phones or digital cameras) on a single integrated circuit. In the previous generation system-on-board (SoB), each functional module is designed, manufactured, packaged, and tested as an independent component or chip. Each fault-free packaged chip is soldered to the board during the board assembly stage to make a complete system.

Compared to the SoC, the SoB form factor is much larger. Furthermore, SoB

design cannot take advantage of the shorter design cycle and higher cost efficiency of the SoC. The power dissipation as well as the inter-chip interconnect delay is much larger, thereby affecting the overall SoB's system performance. The interchip delay, which goes through the die-to-package wire-bonding and the I/O pad, is much larger compared to the inter-core delay (through the metal layers) of the SoC.

Different from that of SoC's, the tests of the individual chip in the SoB is performed by the chip manufacturer, and not the system integrator. The system integrator obtains each packaged chip (either from an external manufacturer or a separate design department from the same company) after it is tested and certified fault-free. Therefore, the system integrator does not have to worry about individual chip tests.

With SoC design technique, the whole SoB design can now be integrated onto a single chip. Even the passive components (capacitors and resistors) can be fabricated onto the same die. Instead of using a fabricated and tested chip as one of the modules, a system integrator uses a pre-fabricated module as part of the design. The module can either be obtained (purchased or licensed) from an outside source as an intellectual property (IP) core or designed separately by the same design group or different design group within the same company. The important characteristic of the SoC is the fact that the system is built from multiple smaller subsystems, which can be designed independently.

Each subsystem/module/core can be in various forms. Depending the format, the test engineer has different levels of freedom when dealing with the tests of the complete system. The following describes the three most common forms of an IP core.

- Soft core is a predesigned block of functional logic such as a macro, megacell, or memory with a register transfer level (RTL) representation. Soft cores are inherently process technology independent. With soft cores, the system integrator has the most freedom, both in terms of design integration and test.

- *Firm core* is a predesigned block of functional logic such as a macro, megacell, or memory that has a process technology-dependent netlist representation and may be amenable to some modification. It is typically in the

form of a synthesized gate-level netlist.

• *Hard core* is a predesigned block of functional logic such as a macro, megacell, or memory that has a physical implementation that cannot be modified, in the form of a completed layout. In this case, the IP provider is responsible to insert the design-for-testability (DfT) circuits into the core design (as shown by the three parallel core design flow in Figure 1.1); this includes the tasks of forming the scan chains and generating the test environment (test vectors/data and test configurations), and to provide the test environment for the IP core to the system integrator. In this case, the system integrator has no choice but to use the test information from the IP provider.

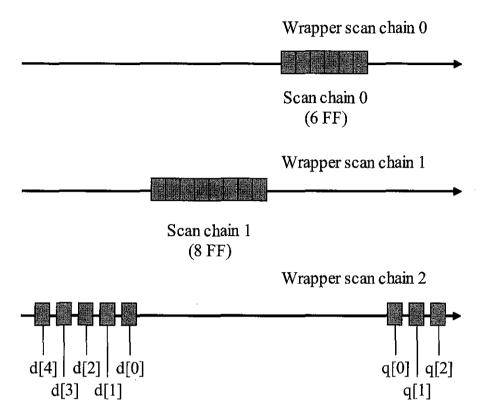

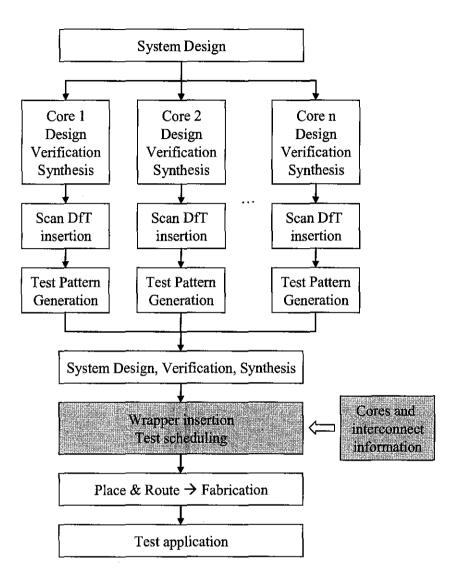

Figure 1.1 shows the design flow for a complete SoC system. The test flow included into the design flow assumes a dedicated TAM based architecture. After the system design, verification, and synthesis, the test access mechanism and core wrappers are added to the synthesized netlist. The system-level core information is used during this process. Depending on the methodology, the test scheduling step is performed concurrently with the TAM and wrapper design, or after its completion.

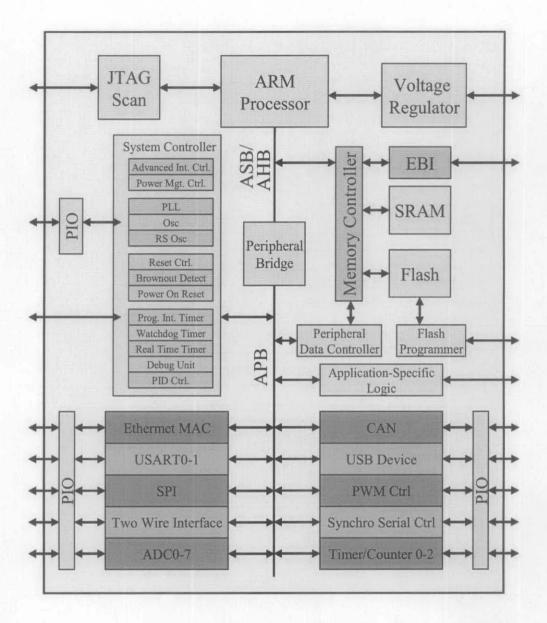

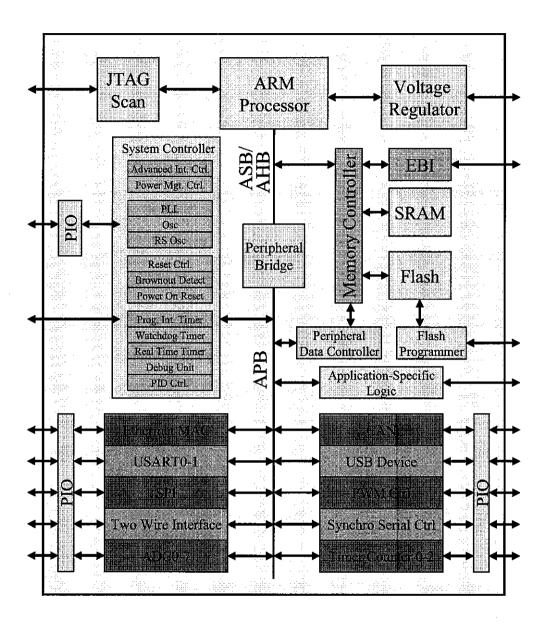

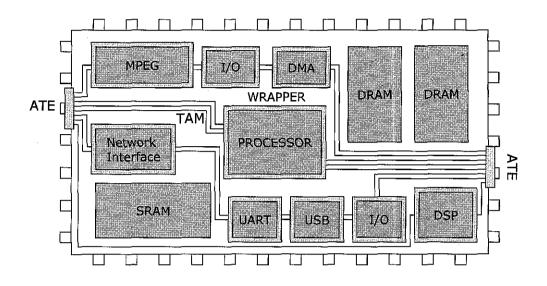

Figure 1.2 illustrates a complex system-on-a-chip which consists of an embedded ARM processor, memory (SRAM and Flash), and a host of supporting logic blocks. In addition, all these subsystems are connected together by a system bus (ASB/AHB) and a peripheral bus (APB). Together, they make up a complete functional system.

To test this hierarchical system, one way of doing it is by synthesizing the whole system to get a flat and large gate-level netlist. This is possible when the cores are either soft or firm formats. A hard core is not flexible and cannot be flattened with the rest of the system. After synthesis, the netlist is fed to a scan insertion tool which will convert all flip-flops into scan flip-flops, assuming a full-scan architecture is desired. The scan flip-flops are connected together into one or more scan chains. From here, the flip-flops (or scan flip-flops) can be isolated from the combinational logic circuits. The process continues by applying an automatic test pattern generation (ATPG) tool to the combinational parts of the design. These generated test patterns are then applied to the circuit using a boundary scan mechanism.

4

Figure 1.2: A microprocessor-based system-on-a-chip based on the ARM bus architecture.

- The simultaneous test application of the whole circuit might cause an excessively large test power dissipation. The test power is normally larger than the power dissipation during the intended normal operations

- It is common for a system to contain multiple instances of an IP core such

Figure 1.2: A microprocessor-based system-on-a-chip based on the ARM bus architecture.

- The simultaneous test application of the whole circuit might cause an excessively large test power dissipation. The test power is normally larger than the power dissipation during the intended normal operations

- It is common for a system to contain multiple instances of an IP core such

as memory and peripheral controllers. This test approach cannot take advantage of the duplicity in terms of

- the potential of reducing the storage requirement in the external automatic test equipment (ATE) by utilizing identical sets of the test stimuli and responses.

- the potential of reducing the test generation time because the same test data can be used for multiple identical IP cores. Some IP cores do not require this process if the IP providers include the test environment as part of the IP cores. Test environment provided by the IP provider is typically of higher qualify because they have a more intimate knowledge of the functionalities of the IP cores.

- the potential of shortening the test application time by simultaneously scanning in the test data in parallel for multiple identical IP cores.

For many years, the academic and industrial research community have been working on the core-based test application strategy for the SoC. In the following chapters, we will review some of the existing SoC test strategies and elaborate our proposed strategies to take advantage of the hierarchical nature of the SoC. In this chapter, we begin by laying the foundation by looking at the scan based test strategy for each individual IP core

### 1.3 Scan-based Testing of Embedded Cores

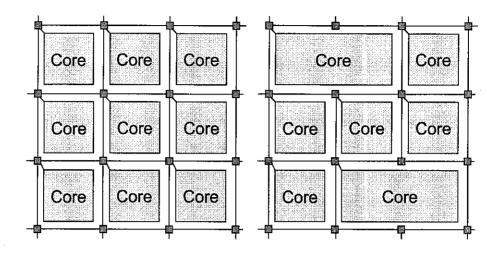

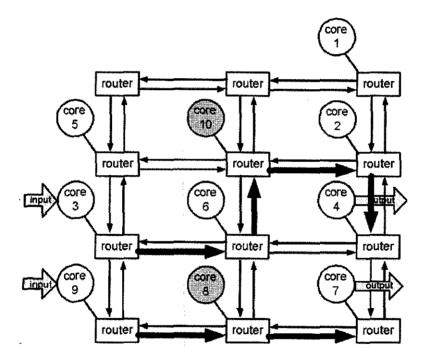

Figure 1.3 shows a simplified representation of a SoC with twelve cores without the interconnects. Like Figure 1.2, the IP cores are functionally connected to each other through a system of interconnects such as a flat or hierarchical bus. However, because the conventional test scheme that will be analyzed subsequently does not use the interconnects as part of its test architecture, we omit the interconnects from the SoC representation for clarity.

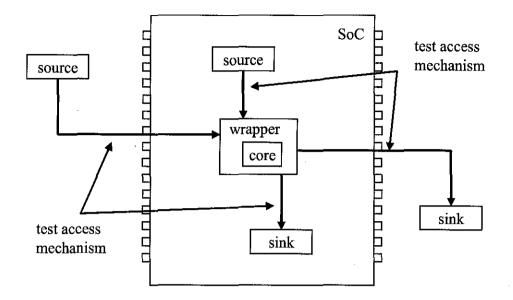

**Definition 1.1** A *test access mechanism* (TAM) is a feature of an SoC design that enables the delivery of test data to and from cores or core wrappers. It is a mechanism for moving stimuli to and observing responses from a core or user-defined logic (UDL) during nonfunctional or test mode. The signals may

Figure 1.3: A simplified representation of the core-based SoC architecture without the functional bus interfaces.

be propagated to and from a core, from either embedded circuitry or from the primary inputs and outputs of the system chip [4] (Figure 1.4).

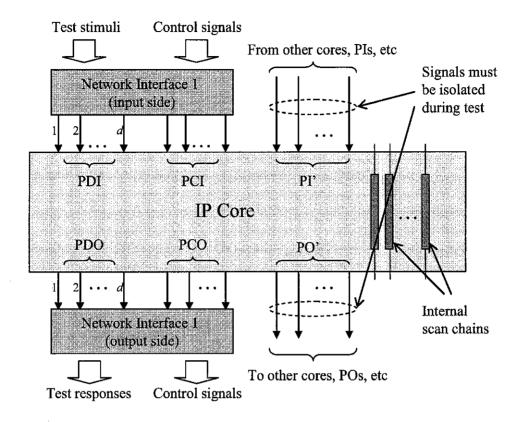

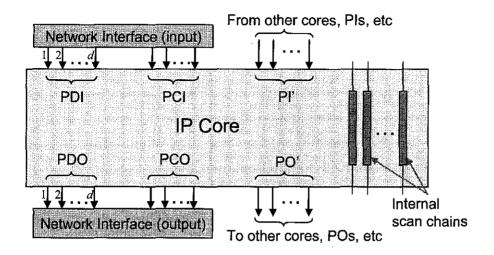

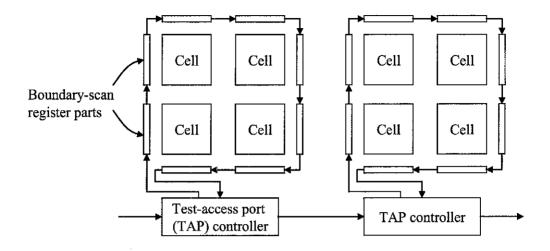

In order to enable core-based testing, a network of these test access mechanisms (TAM) are added to the system (Figure 1.5). A TAM consists of two parts. One part for the actual test data transportation and one part that control the test data transportation. The TAM wires provide a direct pathway between an ATE and the IP core under test (CUT). The test vectors are transported to the CUT from the ATE input on the left side, applied to the CUT to obtain the test responses, then the test responses are transported out of the chip through the TAM wires on the right side back to the ATE for comparison with the expected test responses. In the example, the memory blocks (SRAM, DRAM) are ignored since they are normally and more effectively tested using dedicated memory test techniques such as memory built-in-self-test (memory BIST). Therefore, the tests of memory blocks are not considered.

Figure 1.4: Test source and sinks interfaced to the core by means of a TAM and a wrapper. Illustration based on [5], reproduced with permission.

#### **1.3.1** Core Test Architecture

**Definition 1.2** A core *wrapper* is a circuitry added around an embedded core to facilitate test reuse and to interface between a test access mechanism (TAM) and the embedded core [4] (Figure 1.4). Test reuse is the ability to apply a predetermined test pattern associated with a core after this core has been integrated into an SoC. Test reuse is a consequence of design reuse and often requires the adaptation of a test protocol to reflect the core's new environment within an SoC. The use of core wrappers allow these test patterns to be reused in the environment of an SoC.

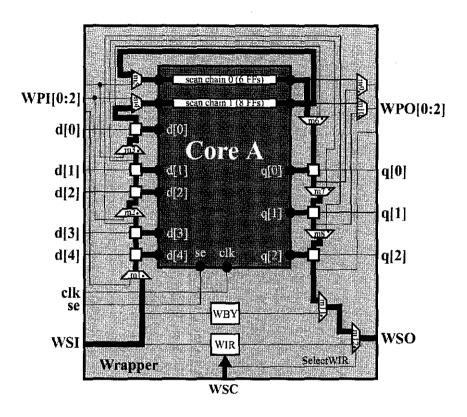

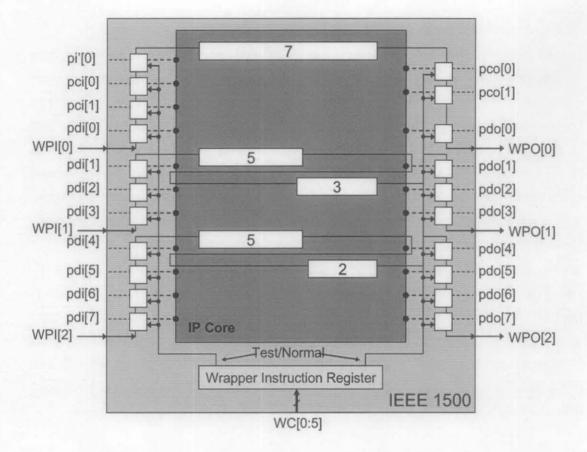

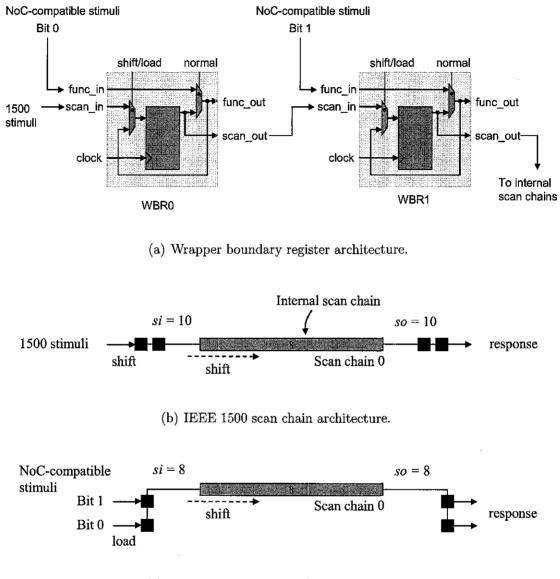

Figure 1.6 illustrates a Core A wrapped in the IEEE 1500 standard wrapper. The wrapper consists of several components. The wrapper boundary registers (WBR) act as input and output buffers. In Figure 1.6, five input wrapper boundary registers are located between the wrapper boundary inputs (d[0]-d[4] labels on the outside) and the Core A's primary inputs (d[0]-d[4] labels inside Core A). Similarly, three WBR's are located at the outputs (q[0]-q[2]).

Figure 1.5: The SoC in Figure 1.3 after the core-based test architecture is inserted. The test access mechanism (TAM) provides external access to the embedded cores and the core wrappers provide test control and access to each individual core.

The second component is the wrapper instruction register (WIR), which accepts several predefined instructions from the WSC input. These instructions are used to set the wrapper modes. In the normal mode, the WBR selects the functional inputs (d[0]-d[4]) and outputs (q[0]-q[2]), respectively. In the test mode, the WBR selects the scan inputs (WSI input in Figure 1.6). Figure 1.6 shows the serial INTEST mode, where the wrapper is configured with one long scan chain to provide test stimuli (from WSI input) and to capture test responses (from WSO output) for Core A, hence the name INTEST (or internal test) mode.

Other test modes are parallel test mode (using the WPI and WPO), which can provide wider TAM access for shorter test application time, and bypass mode (using the WBY register), which is used when multiple cores are sharing the same TAM wires as shown in Figure 1.5. By setting bypass mode for all cores except one, each core can be tested sequentially using the shared TAM wires. This is used when limited number of TAM wires are available. In addition, the wrapper serial input (WSI) is typically used to connect serially all the cores in the SoC using a single wire. The WSI input is used to update the wrapper instruction register

Figure 1.6: An IP core wrapper in the 1500 standard wrapper [4]. The wrapper is configured with the serial INTEST mode.

(WIR) of the target core. In the bypass mode, the bypass register eliminates all the boundary registers from the serial scan path to shorten the time to update the WIR.

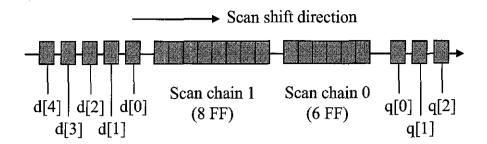

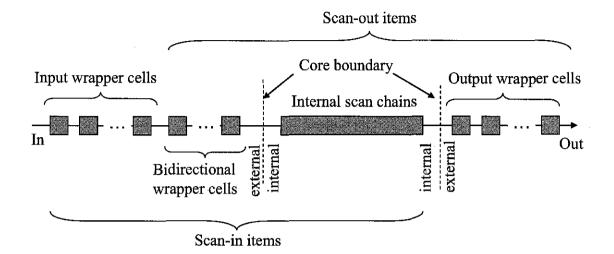

Using the example in Figure 1.6, we can extract the single wrapper scan chain structure as shown in Figure 1.7. The wrapper scan chain consists of five WBR for the primary inputs d[4:0], 8+6=14 scan cells from the two 8- and 6-bit-long internal scan chains, and three WBR for the primary outputs q[2:0]. All together, the scan chain is 22 bits long. For this wrapper configuration, a pair of test vector and response of 19-bit and 17-bit long, respectively, are required. In other words, the scan-in depth  $(si_0)$  and the scan-out depth  $(so_0)$  for the wrapper configuration are 19-bits and 17-bits respectively. This concept is explained next.

The tests of an IP core can be broken down into three stages.

Figure 1.7: The single scan chain architecture from the serial intest wrapper configuration of Figure 1.6.

- 1. Stage 1 [Scan-in stage]: The test stimuli are loaded (or scanned-in) to the primary input WBR's (5 bits) and the internal scan chains (14 bits). The primary output WBR's do not require test stimuli because they are on the output side of the circuit under test (CUT), the combinational logic in Figure 1.8.

- 2. Stage 2 [Capture stage]: The test stimuli are applied to the CUT by applying a clock cycle. After this stage, the contents of the internal scan chains and the primary outputs WBR's, are updated to reflect the next state of the CUT, which is also called the test response. The contents of input WBR's are unchanged.

- 3. Stage 3 [Scan-out stage]: The test response, which consists of the contents of the internal scan chains (14 bits) and the primary output WBR's (3 bits) are unloaded (or scanned-out) of the scan chain to be compared to the expected response. If the circuit response and the expected response match for every test stimuli, the circuit is considered fault-free.

The total test application time for the single test stimuli is 19 + 1 + 17 = 37clock cycles. If the test set consists of two test stimuli  $v_0$  and  $v_1$  (where  $v_0$  is applied before  $v_1$ , and the number of test stimuli is  $n_v = 2$ ), the scan-in stage of  $v_1$  can be overlapped with the scan-out stage of  $v_0$ . Since the scan-in depth is larger than the scan-out depth by two bits in this example, the extra 2-bits scanned-out (at the output of the scan chain) during the scan-in of  $v_1$  are ignored. On the other hand, if the scan-in depth is shorter than the scan-out depth by n

Figure 1.8: Alternative representation of the 1500-wrapped core in Figure 1.6. The IP core is divided into scan flip-flops and combinational logic components.

bits, the second test stimuli must be reformatted to accommodate the artificially elongated scan-in cycle (or simply scan cycle), by padding it with n dummy bits during the first n scan cycles. When the scan-in and scan-out stages are overlapped, the number of scan cycles follow the larger of the two. As a result, the test application time (TAT) for  $n_v$  test stimuli/response pairs for a single scan chain architecture in Figure 1.7 can be written as

$$TAT = (max\{si_0, so_0\} + 1) \times n_v + min\{si_0, so_0\}$$

(1.1)

Figure 1.9: The multiple scan chain architecture for Core A in Figure 1.6.

The following description is applicable to the example in Figure 1.7. The first term, max(...), represents the first scan-in cycle and the overlapped scan cycle(s), plus a single capture cycle for each test stimuli. The second term, min(...), represents the final shorter scan-out cycle. Using equation 1.1, the test application time for the example in Figure 1.7 is 57 clock cycles.

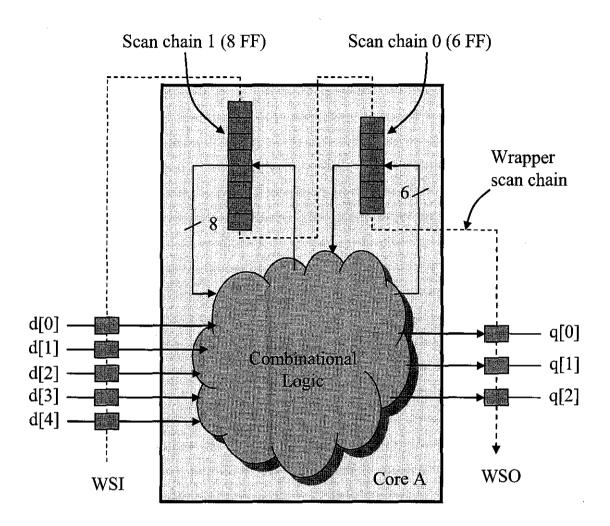

For multiple wrapper scan chains, the scan-in depths and scan-out depths for each scan chain can be arbitrary. One possible two-scan chain configuration for the same IP core in Figure 1.6 is shown in Figure 1.9. The scan in-depths of wrapper scan chains (wsc) 0 and 1 are  $si_0 = 9$  and  $si_1 = 10$ , respectively. The scan-out depths are  $so_0 = 8$  and  $so_1 = 9$ , respectively. Because the scan-in operation takes place simultaneously for both wsc 0 and wsc 1, the larger of the scan-in depths,  $si_1$ , dominates. Therefore, the overlapped scan-in and scan-out operations take 10 clock cycles. During the final scan-out operation, the number of scan-out clocks is determined by the dominant scan-out depth,  $so_0 = 9$ .

In general, we can define the maximum scan-in depth for all k wrapper scan chains,  $si = max\{si_0, si_1, ..., si_k\}$ , and the maximum scan-out depth, so =

Figure 1.10: Three scan chains architecture for Core A in Figure 1.6. Wrapper scan chain 1 dominates the test application time, therefore larger number of scan chains will not reduce the test time any further.

$max\{so_0, so_1, ..., so_k\}$ . The generalized test application time is given by

$$TAT = (max\{si, so\} + 1) \times n_v + min\{si, so\}$$

$$(1.2)$$

Using equation 1.2, the test application time for the two-scan-chain wrapper configuration in Figure 1.9 with  $n_v = 2$  is 31 clock cycles. For three (Figure 1.10) or more wrapper scan chain configurations, the test application time would be 26 clock cycles because the fixed 8-bit internal scan chain dominates.

### **1.4** Reuse of Functional Interconnects as TAM

The discussions in Section 1.3.1 (Figures 1.5 and 1.6) relate primarily to the concept of a test access mechanism that are added to the chip purely for the use during the test application (i.e. it is only used during the nonfunctional or test mode). There are a lot of research on SoC core-based testing that are relying on the nonfunctional or dedicated TAM. Only a small number of papers considered core-based tests without the dedicated TAM. These related research are highlighted in Chapter 2.

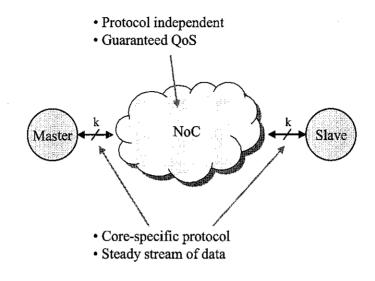

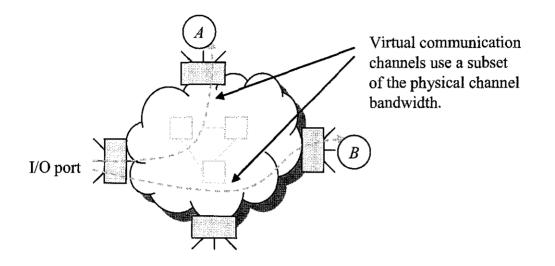

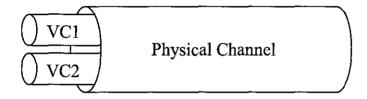

Our work concentrates only on the reuse of functional interconnects as TAM during the test application. The functional interconnects are sometimes called existing interconnects or functional TAM. Unfortunately, these functional interconnects come in various flavors. Bus-based interconnects (hierarchical or non-hierarchical) are the most common. The most recent type of SoC interconnect, the network-on-chip (NoC), has also been considered for high bandwidth requirements. This work considers these three types of functional interconnects as TAM's and develops the necessary support architecture and the corresponding test scheduling algorithms for each case.

#### **1.4.1** Impact on the Design Flow

In Figure 1.1, the design and test flow for the dedicated TAM based test scheme is illustrated. During the process of TAM and wrapper insertion and test scheduling, only the information on the embedded cores is required. For core tests, interconnect information is not required because of the addition of test access mechanisms. The details on the functional interconnect architecture is required only for the interconnect testing.

Figure 1.11 shows the revised design and test flow when reusing the functional interconnect for test data transportation instead of the dedicated TAM. The impact on the design flow is very minimal. The same steps are followed, except during the system-level DfT insertion and test scheduling. The functional interconnect information is required for the wrapper design and test scheduling.

Figure 1.11: System design and test flow for interconnect reuse.

### 1.5 Contributions of This Thesis

This thesis makes three main contributions to the problem of core-based testing of a system-on-chip by reusing the existing SoC interconnect. This thesis focuses on the wrapper design and insertion, and test scheduling, as shown by the grayed blocks in the design and test flow in Figure 1.11. The shared characteristic of all our proposed approaches is that they utilize the existing functional interconnects/interfaces for test purposes. The first step of our research targets the most basic interconnect—the non-hierarchical or flat bus architecture. This is followed by the more advanced hierarchical buses. Finally, we target the new *smart* interconnect called network-on-chip, which is based on the packet-switched Internet protocol network architecture.

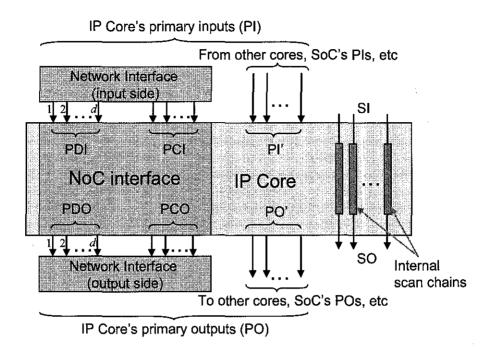

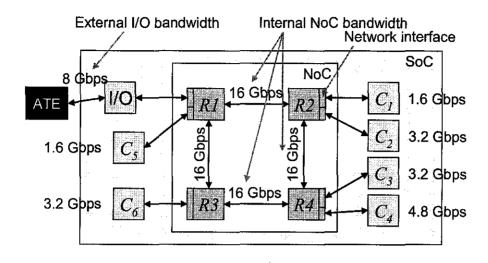

Our first contribution is that several variations of core test wrappers for functional interconnect reuse are proposed for specific types of SoC interfaces. We propose an improved version of a core wrapper for bus-based SoC based on the novel buffer-based wrapper architecture by Larsson, *et al.* [6]. Another pair of core test wrappers are designed for a NoC-based SoC, that takes advantage of the NoC communication services, specifically the bandwidth reservation scheme. In addition, the bandwidth matching architecture integrated with the wrapper eliminates the problem present in the wrapper proposed by Amory *et al.* [7].

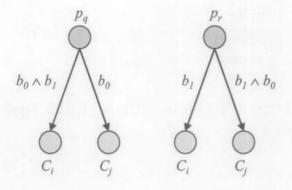

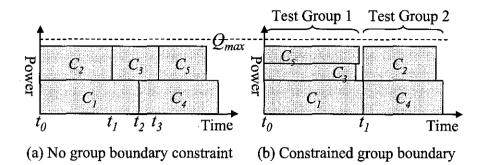

Second, the thesis proposes the concept of test configuration graphs (TCG), which can be used to systematically and effectively schedule the available resources in a hierarchical bus and multiprocessor system. We proposed five basic types of test configuration graphs, from which any other configuration can be derived. The TCG's are used in the test scheduling algorithm as an effective measure to balance the loads on various bus segments for the test scheduling problem of hierarchical bus based MPSoC.

Third, we are the first to propose a test data transportation scheme that utilizes the NoC effectively, by means of bandwidth sharing. The proposed method drastically reduced the test application time compared to the previously proposed test method for a NoC-based system. Such achievement is made possible by the use of our enhanced NoC-compatible wrappers.

### **1.6** Thesis Organization

This thesis is organized as follows. The current chapter (Chapter 1) provides a description on the fundamental problems of core-based scan testing of systemon-chips. The problems can be summarized as

• the problem of test access to the deeply embedded cores to provide the test stimuli and to retrieve the test responses, and

• the problem of test time minimization through proper core test scheduling schemes.

Chapter 1 provides a strong motivation for the test data transportation problem in the core-based SoC testing to be mitigated by using the functional interconnects, rather than by using dedicated TAM's. In doing so, the unnecessary area costs and additional routing congestion of the dedicated TAM can be avoided completely.

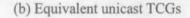

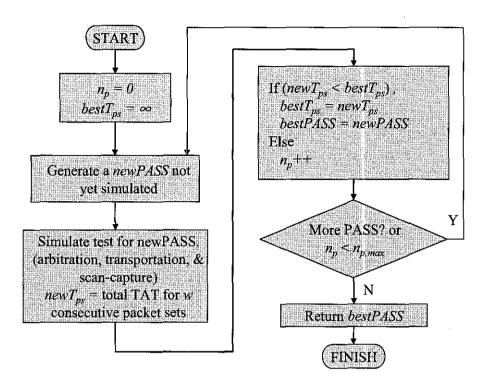

Chapter 2 begins by considering the test access and test scheduling problems for SoC's with a flat bus (i.e. non-hierarchical) interconnect architecture. The single flat bus poses a problem in minimizing the test application time because of its shared-and-broadcast nature. This shared architecture limits the core test scheduling to a test-one-at-a-time sequential test scheme. To overcome this problem, a buffer-based wrapper architecture is proposed. The addition of buffers allows the shared bus to be used efficiently by means of a packet-based test data transportation, which utilizes the time domain multiplexing (TDM) scheme. The benefit of using the buffer-based test wrapper together with the functional bus on the test application time is evident, as shown by the experimental results presented in this chapter. The proposed test scheduling scheme using the packetbased data transmission is called PAcket Set Scheduling (PASS).

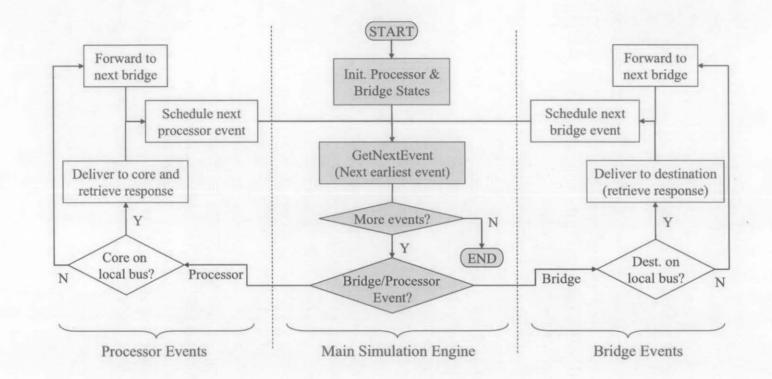

Chapter 3 leads off with a discussion on multiprocessor SoC's (MPSoC) with hierarchical buses. It continues with some explanation on why the PASS algorithm (which was developed specifically for a non-hierarchical bus) does not work efficiently for a hierarchical bus system. This chapter proceeds to address the shortcoming of PASS scheme with an integrated test scheduling methodology called Multi-Processor PASS (MPPASS) for multiprocessor SoC's. As part of the MPPASS scheme, the concept of Test Configuration Graphs (TCG) that represent the MPSoC test architecture is introduced. In short, this chapter expands the methodology proposed in Chapter 2 to be applied to the more generalized MPSoC architecture.

Chapter 4 begins with a brief introduction on the Network-on-Chip (NoC) interconnect architecture. This chapter gives the basic characteristics of NoC topologies, NoC routers, and data switching techniques. Two network-on-chip interconnect architectures—SoCIN and Æthereal—most commonly used in the

core wrapper design and core-based test scheduling problems are described.

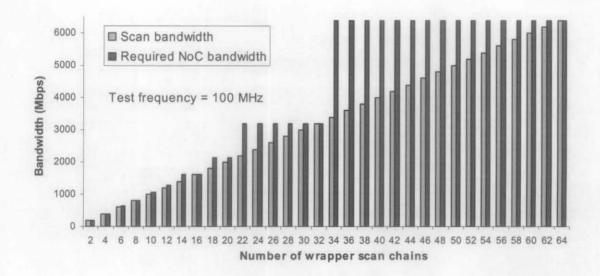

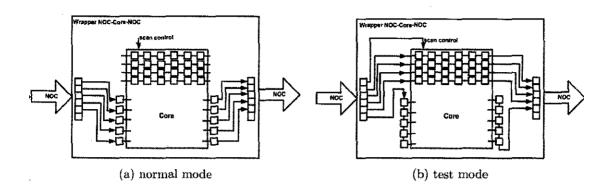

In Chapter 5, we start by explaining the limitations of the standard IEEE 1500 wrapper, which cannot be used when the NoC interconnect is used as a test access mechanism. The analysis of these 1500 wrapper limitations provides us with the necessary information to construct NoC-compatible wrappers. In order to optimize the bandwidth utilization and minimize the test application time while also minimizing the area cost, two types of NoC-compatible wrappers are constructed. The first wrapper incurs minimal area cost, but wastes the NoC bandwidth under some test configurations. The second wrapper complements the bandwidth-inefficient characteristic of the first wrapper by using more hardware, thus higher area cost.

Having the two wrapper options allows the test designers to balance between area cost minimization and test time minimization in the test scheduling scheme in Chapter 6. The experimental results presented in this chapter evaluates this trade-off. Chapter 6 continues the discussion on NoC-reuse-based test scheduling using a bandwidth sharing scheme—a novel test scheduling technique proposed in this chapter. Compared to other dedicated path-based test scheduling, the dedicated path approach is much more efficient in reducing the test application time, especially with a limited number of I/O ports.

In Chapters 2, 3, 5, and 6, several experimental results are presented and explained to verify the effectiveness of the proposed techniques. Finally, Chapter 7 summarizes the research results presented in this dissertation and highlights some of the important results followed by a brief mention of possible future works.

## Chapter 2

# Wrapper Design and Test Scheduling for System-on-Chips Using a Functional Bus

## 2.1 Introduction

System designers are adapting to the system-on-chip (SoC) design methodology because of its efficiency compared to the traditional system-on-board approach. The SoC design technique and its characteristics are briefly described in Chapter 1. The main benefit of the SoC approach is that it can drastically shorten the design cycle by allowing pre-designed cores and their associated test set to be reused. To enable the plug-and-play reuse of tests together with the cores, the IEEE 1500 standard [3, 4] was developed and used by many IP core providers and system designers.

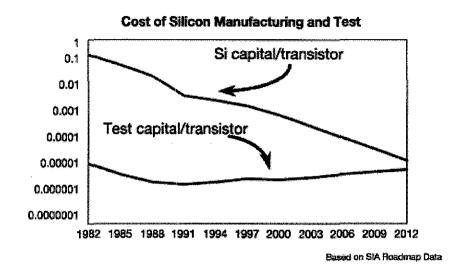

The rapid increase in VLSI design in terms of its functionality as well as the gate/transistor count helps in reducing the design cost. With every new improvement in the manufacturing technology, the cost of fabricating each transistor decreases in inverse exponential fashion (Figure 2.1). The test costs however has been kept almost constant throughout the years. Without a revolution in the way the chips are tested, the costs of a chip will soon be dominated by the test costs.

Furthermore, the use of SoC design methodology introduces several new prob-

Figure 2.1: Comparison between the cost of silicon and the cost of test of VLSI circuits over a 30-year period.

lems and challenges in testing [8]. First, the cores that are embedded deep inside the silicon chip require a Test Access Mechanisms (TAM) for test data transportation. Several TAM architectures have been proposed such as TestRail [9], Virtual TAM [10], and TAM's based on transparency [11].

Second, the SoC's core-based design requires a mechanism to isolate the cores during test. This is achieved by the use of core wrappers [3, 9]. Third, the cores can either be tested sequentially at the cost of longer test application time, or in parallel at the cost of larger area overhead and power dissipation. In this regard, various test scheduling solutions have been proposed [6, 12–50]. The core test scheduling approaches proposed by [13–21, 27] rely on a dedicated TAM. This extraneous TAM is consistently added to the SoC for the sole purpose of delivering the test vectors from external automatic test equipment (ATE) to the core under test (CUT). In general, the test application times resulting from these approaches are bounded by the lower bound derived in [21].

Among these approaches, various optimization methods stand out such as using *k*-tuples to represent a test schedule [29], 2D-bin packing [17, 19, 51], 3D-bin packing [13], several types of linear programming [30–32], simulated annealing

[33], preemptive scheduling [14, 34], and a schedule based on the TAM-routing cost [35], a DFT selection algorithm [36], a wrapper/TAM co-optimization [12], and a multi-frequency TAM [37]. In order to further minimize the test application time, reconfigurable wrapper [14], virtual/reconfigurable TAM [16, 38, 39], test vector sharing and broadcasting [27, 52], and defect-probability driven [40, 41] approaches have also been proposed.

Taking into account the special characteristics and limitations of the SoC chip, power-constrained scheduling [17, 18, 34, 42–46], layout-constrained scheduling [47] and test scheduling for multi-clock domain SoC's [15] and hierarchical SoC's [19, 48–50] are also important. Equally important is the work on test planning and design space exploration [20, 53] which tackle the test problem at an earlier stage. All these test scheduling and optimization works rely on the introduction of a dedicated and extraneous TAM for the test data transportation.

Regardless of how efficient the test schedule optimization, wrapper optimization, or TAM optimization algorithms are, the idea of adding a dedicated TAM for test data transportation by itself requires considerable area overhead. In addition, the long TAM wires increase the routing congestion. With small feature sizes below 90 nm, the long wires are highly potential spots of production defects. Defects in TAM's would prevent any cores from being properly tested, thereby affecting yield. To avoid relying on TAM's, the existing functional communication architecture should be used as an alternative to the extraneous TAM for testing purposes. The test scheduling methods proposed in [13–21, 27] cannot be applied to this new problem, which has a single shared bus where each bus wire cannot be individually assigned according to the optimum test schedule. Cores can only be tested sequentially by using all functional bus bit width.

In order to maximally reuse the existing chip resources for testing, the authors in [22] described a method based on consecutive transparency, where test access paths are formed by creating transparent paths through existing functional connections between the SoC cores, thereby reusing most of the existing interconnects. However, the drawback of the proposed approach is that it is intrusive; sometimes, establishing the paths requires modification to the core internals, which might affect the critical paths of the cores.

Several test strategies which utilize the functional bus [6, 23-26, 28] have

been proposed; they are further discussed in Section 2.2. However, these methods do not consider the test scheduling at the packet level, which is necessary when reusing the functional buses for test data transportation. In this chapter, we introduce our proposed approach [54, 55], which explicitly schedules the transportation of data packets through the functional bus that carry the test vectors and responses. The test application times are obtained through complete packet-level simulations of the test data transportation. The proposed approach is unique because of the explicit packet transportation schedule, in addition to its ability to make use of the functional bus effectively.

We begin with a review of some works related to the bus reuse strategy in Section 2.2. In Section 2.3, a motivational example is given, followed by a brief technical overview in Section 2.4. In Section 2.5, the support architecture design for the efficient utilization of the functional bus during testing is described. Section 2.6 elaborates the methodology to develop an efficient test schedule using the functional bus. In Section 2.8, we thoroughly evaluate our methodology experimentally. Finally, a brief set of conclusions is offered in Section 2.9.

## 2.2 Related Work

This section describes some works on the utilization of the existing functional interconnect rather than an added interconnect as TAM. To differentiate the two types of test data transportation approaches, we define the following terminologies:

**Definition 2.1** Dedicated TAM is a set of dedicated wires that are added to the SoC for the test data transportation between an ATE and all the SoC cores during nonfunctional or test mode.

**Definition 2.2** Functional TAM refers to the existing SoC's functional interconnects which are transformed and reused for the test data transportation during the nonfunctional or test mode.

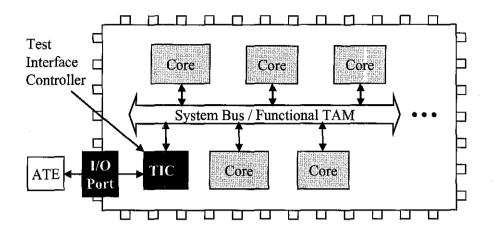

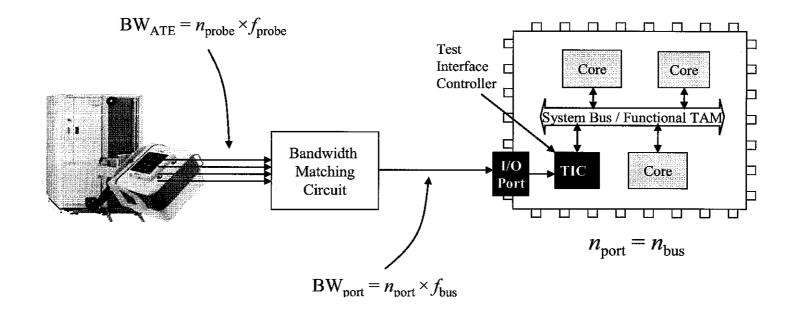

Among the earliest literature on the use of functional TAM's for SoC testing stands out the paper by Papachristou *et al.* [24], in which, an embedded microprocessor is used as the test controller. The test data from an external tester are loaded into the embedded memories through a direct memory access controller (DMA) and delivered to the core under test by the embedded processor through the functional interconnect. The test responses are evaluated by embedded signature analyzers in order to minimize the load on the processor and the interconnect.

A more comprehensive methodology on the functional TAM approach was discussed by Harrod [23]. The paper discussed the test application strategy for various types of test requirements for the embedded Intellectual Property (IP) cores. Test access to the Core-Under-Test (CUT) is provided by the Test Interface Controller (TIC), which is part of the AMBA specifications. An external ATE is used to deliver the test vectors through the TIC interface. At each core, a test wrapper is required to isolate the core from its surrounding.

Krstic *et al.* [25] presented a similar methodology, where the embedded processor first tests itself by executing a set of instructions using a software-based self test (SBST) methodology [56]. Subsequently, the processor tests the bus and the other IP cores. Huang *et al.* [26] presented a similar core-based test approach for PCI bus based SoC's. The test application is performed by the test support architecture at every CUT. Software-based weighted random patterns [57] are generated for each CUT. These approaches [23–26], however, do not propose a test scheduling technique for a complete SoC to show their effectiveness. To enhance the software-based test generation, a specialized set of test instructions is also introduced [58].

Larsson *et al.* [6] proposed a buffer-based test support architecture to enable parallel testing of core-based SoC's. As opposed to the embedded processor-based approach by [24–26], the test control is performed by an embedded finite state machine based controller which costs additional hardware, proportional to the volume of the test data.

All the proposed methods [6, 23–26] target the structural test of the logic cores. The tester (an embedded processor or an external tester) utilizes the functional buses to transfer the structural test vectors to the respective CUT's. The authors in [58] targets the functional tests of embedded processor and logic cores by implementing an instruction-level design-for-testability (DfT) and specialized

test instructions to aid in increasing the fault detection and shortening the test application time.

The use of packet-switching architecture for core-based testing has been proposed by Aktouf [59] for a multiprocessor system with a homogeneous networkbased architecture. Vermeulen *et al.* [60] shows that an NoC can be effectively reused for core testing as well as system verification. Several NoC-reuse based test strategy have been published in the recent years, among them are from Cota *et al.* [61], Amory *et al.* [62], and Liu *et al.* [63]. All these approaches, however, do not propose an explicit transportation schedule for each test packet; instead, dedicated access paths are allocated assuming that the test data and response packets can be streamed between the tester to the CUT's. Applying these approaches on a shared functional bus results in a sequential testing of the SoC cores.

Nahvi *et al.* [64] proposed a Test Access Mechanism (TAM) architecture based on a packet switching communication network, called NIMA (Novel Indirect and Modular Architecture). NIMA provides access to the cores for test data delivery by means of multi-level routers and communication channels similar to bus-based TAM's. Packet delivery is achieved by breaking the test data into smaller units called packets, each of which containing the necessary control information required to successfully deliver the data through the routers. Typical control information includes the synchronization bits, the destination address, and the length of the address field. Initial analysis of the packet routing architecture shows an improvement in terms of core access time and the total wire length as compared to the bus-based TAM's.

A hybrid TAM architecture which uses the existing functional bus in addition to extra TAM's was proposed in [27]. In this approach, the functional bus is converted into a bundle of TAM's, by adding some logic to make the bus wires controllable and observable to external testers. As a result, each functional bus wire can be individually controlled and assigned to cores for the test data transportation, similar to the added TAM. To further minimize the test application time by optimizing TAM utilization, shared test vectors are broadcast to multiple cores. In [26], the authors propose a test interface architecture between PCI buses and CUT's. The CUT's are tested using pseudo-random test vectors, generated by the embedded processor. In [6], a buffer interface between a functional bus and a CUT is proposed, while the control of test application is performed by a Finite State Machine (FSM) based controller. The hardwired controller has in [6] has two main weaknesses compared to our approach: (1) the area cost is proportional to the the volume of test data, and (2) the FSM-based test schedule is fixed, making it impossible to change. This flexibility is especially important during the hardware debugging stage. The test responses, on the other hand, are not transported through the bus to the test sink. Instead, they are compressed by local embedded multiple input signature registers (MISR), which could cause aliasing. Furthermore, the MISR's incur hardware overhead.

Due to the use of MISR's, the test application time of [6] should, in most cases, be shorter than our approach, which transports the test responses back to the tester. However, the use of software-based test program in our proposed approach has the advantage of being flexible, and does not incur hardware overhead other than the buffers. The role of the FSM-based test controller in [6] can be replaced by an external tester or an embedded processor. This is further discussed in Section 2.4

In this chapter, we illustrate our power-constrained SoC testing approach which utilizes the functional TAM for the test data transportation. In order to take advantage of the functional TAM, we approach the problem from two angles, namely, a support architecture design framework and an algorithmic framework. In the process, we show how our approach greatly simplifies the test program, one of the primary strengths and differentiators of our proposed methodology. Such a simplification is attained through the support of an efficient test architecture, which includes appropriate timing control circuitry.

## 2.3 Motivation

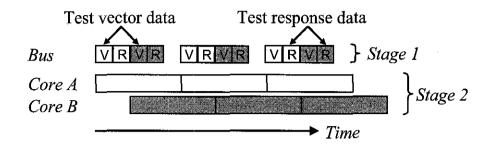

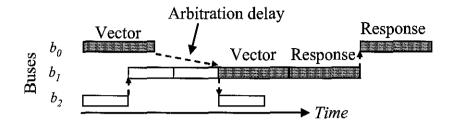

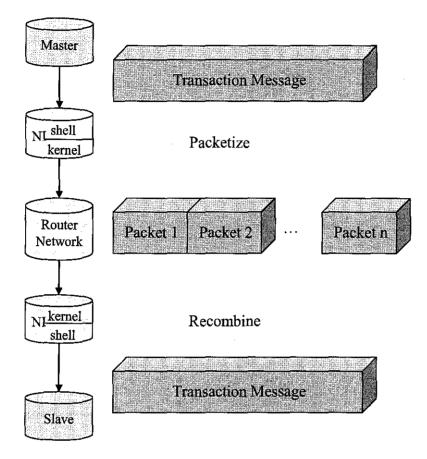

Let us look at some of the possible scenarios regarding packet based test delivery utilizing the shared functional TAM. To ease description, let us denote each of the small test data units as a *test packet*. Figure 2.2 illustrate a sequence of

Figure 2.2: Test data transportation using packet-based delivery on the functional TAM. An R packet carrying the test response data is returned to tester after every V packet, which carries test vector data.

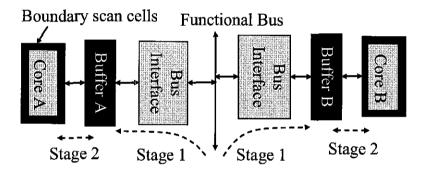

Figure 2.3: Buffer-based test architecture enables parallel test application while utilizing a shared functional TAM.

events when test packet are transported between a tester and two CUT's, *Core* A and *Core* B, which are interfaced to the functional TAM through dedicated local buffers *Buffer* A and *Buffer* B, respectively, in Figure 2.3. *Bus* and *Core* A/B represent the activities on the functional TAM and at the CUT, respectively. Once a packet carrying test vector data,  $v_t$ , (labeled V) is received by the local buffer, the test response packet (labeled R) from a previous test vector,  $v_{t-1}$  is returned in the next time slot.

The *Round-robin* packet delivery schedule in Figure 2.2 is a reasonable first attempt at scheduling the test delivery because of its fair allocation of the bus.

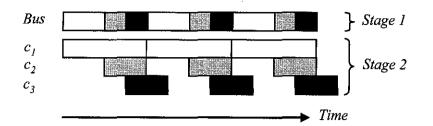

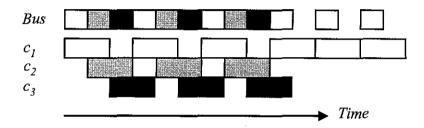

Figure 2.4: Effect of repetitive packet delivery sequence for different packet sizes.

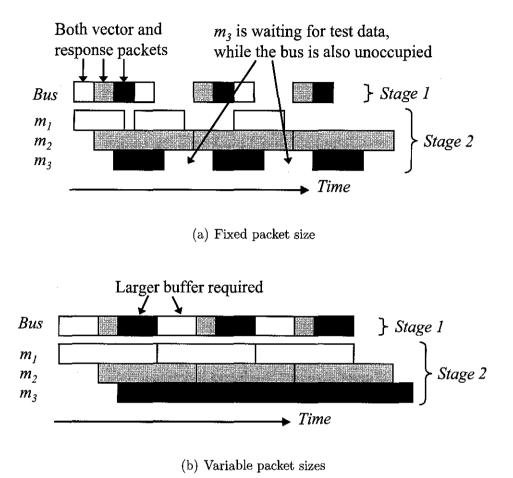

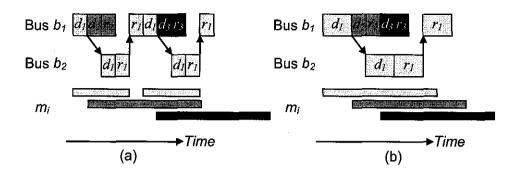

Figure 2.4(a) shows a similar delivery pattern for three unidentical CUT's  $C_1$ ,  $C_2$ , and  $C_3$ . For each CUT  $c_i$ , each packet will go through two separate stages of transfer (illustrated by Figure 2.3). First, it is delivered from a tester to the buffer through the functional TAM (labeled *Bus* in Figure 2.4, where each time slot represents both V and R packets). On the second stage, the packet is transferred from the buffer into the scan chains (labeled  $c_i$  in Figure 2.4 to illustrate the concurrent activities of all CUT's  $c_i$  in stage 2). A test response packet is returned to the tester after every successful reception of a test vector packet by the buffer.

Stage 1 of the subsequent test packet for a CUT can only begin, to avoid buffer overflow, after stage 2 of the previous test packet for that CUT has been completed. Furthermore, since stage 1 uses a common bus, only one test packet can be in stage 1 at any given time. Stage 1 and stage 2 are also referred to as *test delivery* and *test application*, respectively, for the test packet.

Figure 2.4(a) shows CUT  $C_3$  idle, waiting for test data because the test packet for  $C_3$  cannot be delivered until the test packet for  $C_2$  has been delivered. However, the test packet for  $C_2$  cannot be delivered until the test application of the previous packet of  $C_2$  has been completed. Consequently,  $C_3$  is starved for test data and at the same time the bus remains idle while waiting for  $C_2$  to complete test application even though  $C_3$  needs test data. An analogous situation holds for  $C_1$ . CUT  $C_2$ , on the other hand, always receives its test data in a timely manner at the expense of starving  $C_1$  and  $C_3$ .

The problem can be remedied by increasing the packet size for  $C_1$  and  $C_3$ , as in Figure 2.4(b). However, this quick fix implies that larger buffer spaces are required for  $C_1$  and  $C_3$  to store the larger packet sizes. We can reduce packet sizes for all cores, but the minimum packet size for each core is constrained by the core with the smallest packet size (i.e.  $C_2$ ). Further reduction in packet sizes for  $C_1$  and  $C_3$  would reintroduce the problem illustrated in Figure 2.4(a). The two scenarios illustrated by Figure 2.4 above are not the only optimization problems that have to be solved to make core-based testing using the functional TAM attractive. An additional challenge stems from the fact that packet sizes cannot be arbitrary, because data delivery is conducted through a discrete number of bus wires.

Figure 2.3 shows the buffer interface between the bus and the core, which is considered in this chapter. There are several different variables that can affect test scheduling—bus frequency, bus width, scan frequencies, number of scan chains, and volume of test data for each core. All these variables contribute to the efficiency of the test schedule.

## 2.4 Technical Overview

Even though a functional TAM and a dedicated TAM may be similar in many ways, the underlying issues that need to be considered are completely different. We can broadly categorize them into two:

- Support architecture for test data delivery

- Algorithmic framework for efficient test scheduling

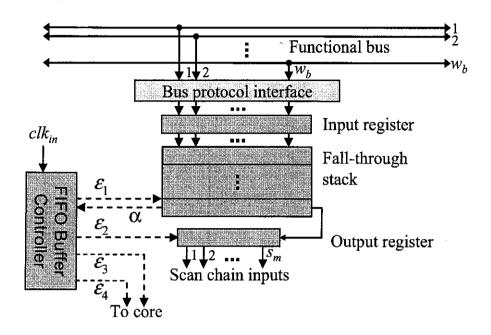

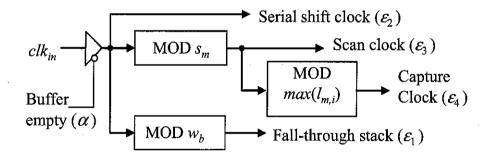

A functional TAM differs from a dedicated TAM because every functional TAM wire is connected to every embedded core; it cannot be committed to multiple cores simultaneously like a dedicated TAM by assigning subsets of TAM wires to different cores. Without a buffer-based test support mechanism (Figure 2.3) similar to the test buffer in [6, 26], only one core can be tested at a time. Furthermore, in the conventional approach of dedicated TAM-based SoC testing, test control timing, including scan and capture clock generation, is provided by the external ATE. Therefore, the synchronization of test vector availability at the scan input and scan/capture clock generation is trivial since the ATE retains full control of all the event sequences for every core under test. When utilizing the functional TAM, this control timing needs to be performed on-chip, posing a research challenge, which we subsequently address in this chapter.

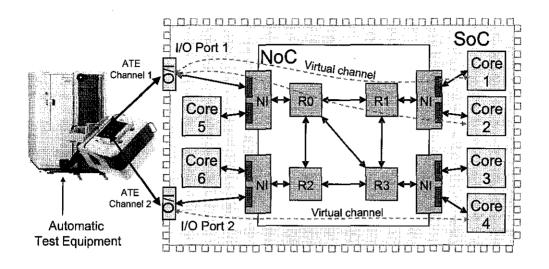

The test source/sink to a functional TAM can either be an external ATE or an internal programmable block. Unlike dedicated TAM's, the ATE cannot be connected directly to the functional TAM wires, but through a test interface port shown in Figure 2.5. For example, ARM's AMBA [65] bus architecture provides a Test Interface Controller (TIC), which communicates to the ATE and the CUT using the functional read/write transactions. The TIC acts as an intermediary by relaying the the vector data packets from the ATE to the CUT and vice versa for the response packets.

In order to utilize the programmable core as a test source/sink, several issues need to be resolved, which among others include testing of the programmable core itself, and loading of the test stimuli to and and offloading of the test responses from the programmable core. In this chapter, we will utilize an external ATE (connected through a TIC) as a test source and sink, therefore. these issues regarding the programmable core are not addressed here.

Figure 2.5: Interfacing an ATE through a Test Interface Controller (TIC) port for a functional mode test data transfer through the functional TAM.

Test scheduling that enables the reuse of the functional bus as functional TAM's involves three steps. First, breaking the test set into subsets capable of efficiently utilizing the bus. Second, scheduling all tests for every core with the objective of test time minimization, and third, generation of a test program which will execute in real-time by the tester to perform test application for all the SoC cores. In order for the benefits of utilizing the functional TAM for testing to outweigh its counterparts in the dedicated TAM approach, the test architecture needs to support the algorithmic framework, and vice versa. Otherwise, problems such as bus underutilization arise because of the required arbitration between different cores, and improper test schedules causing certain cores to starve of test data while other cores may be hogging the bus, resulting in prolonged test application time.

Test data overflow/underflow is a particularly serious potential problem, unless the necessary timing synchronization or interlock between the tester and the cores under test is provided. The test support architecture should be designed to also provide timing synchronization, while minimizing the hardware overhead.

## 2.5 Test Support Architecture

Buffer based test architecture was proposed by [6] in order to enable concurrency of core-based testing using a shared functional TAM. Our general test architecture with buffers similar to [6] is shown in Figure 2.3 with the corresponding test delivery and test application timing diagram similar to Figure 2.4.

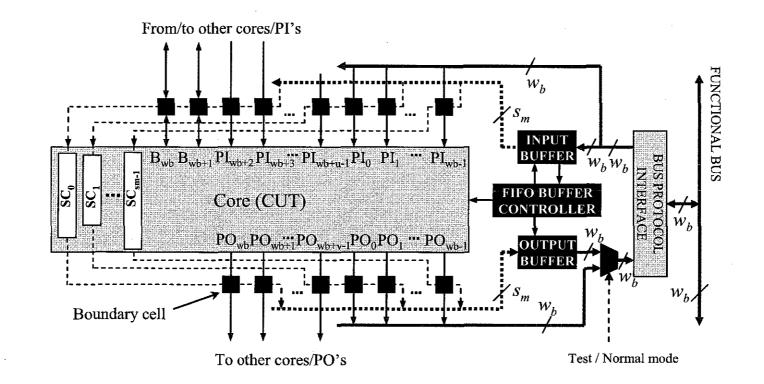

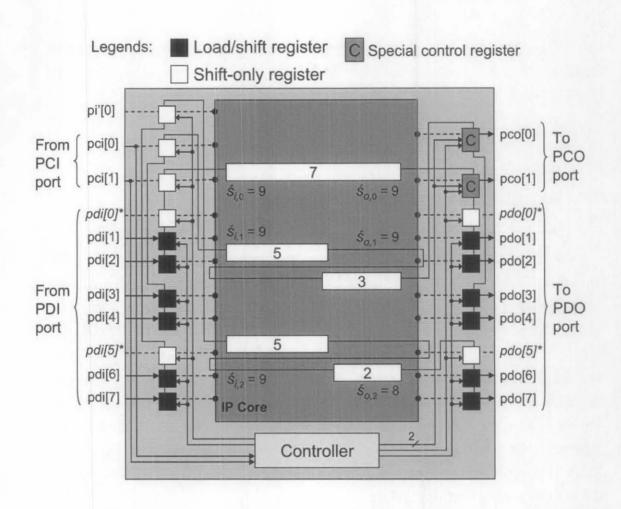

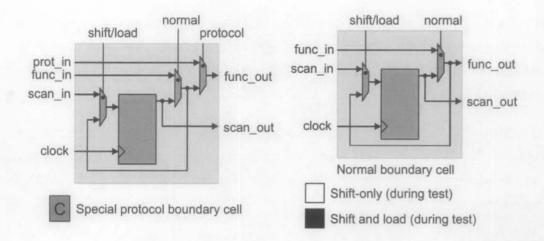

Figure 2.6 shows the detailed architecture of the interface between the functional TAM and the core through the functional bus protocol interface. Both the functional connections (solid lines) and design-for-testability (DFT) connections (dotted lines) are shown. The components shown in solid black shading are the proposed buffer-based DFT architecture. Boundary cells (BC) are added to the core PI/PO's in order to isolate the core during test. The wrapper scan chains are formed by chaining the input BC's, internal scan chains (ISC), and output BC's, in that precise order. Bidirectional I/O's are treated similarly to the ISC's since the BC's scan inputs, and not functional inputs, are used. Bidirectional I/O's are not shown in Figure 2.6 to avoid clutter.

The next section (2.5.1) explains one of the most popular methods of forming the wrapper scan chains that minimize the test application time under given constraints. The concept of scan chain design is important in order to completely understand and appreciate the core wrapper design.

## 2.5.1 Wrapper Scan Chain Design

The authors in [66] provided a detailed analysis on test time for three types of scan chain architecture, namely *multiplexing*, *daisychain* and *distribution* architectures. The fundamental concept of test time minimization through scan chains design can be summarized here.