# UNIVERSIDAD CARLOS III DE MADRID ESCUELA POLITÉCNICA SUPERIOR

# INGENIERÍA TÉCNICA INDUSTRIAL: ELECTRÓNICA INDUSTRIAL

## PROYECTO FIN DE CARRERA

# IMPLEMENTACIÓN HARDWARE DE ALGORITMOS CRIPTOGRÁFICOS PARA RFID

AUTOR: HUGO IZQUIERDO DONOSO TUTOR: ENRIQUE SAN MILLAN HEREDIA

FEBRERO DE 2009

#### **INDICE**

| $\mathbf{C}$ | APÍTULO 1: INTRODUCCIÓN DEL PROYECTO        |    |

|--------------|---------------------------------------------|----|

| 1.           | OBJETIVO DEL PROYECTO                       | 11 |

| C            | APÍTULO 2: TECNOLOGÍA RFID                  |    |

| 2.           | TECNOLOGÍA RFID                             | 15 |

|              | 2.1 FUNCIONAMIENTO RFID                     |    |

|              | 2.1.2 LA ETIQUETA RFID                      |    |

|              | 2.1.3 EL LECTOR RFID                        | 20 |

|              | 2.1.4 <u>COLISIONES</u>                     | 21 |

|              | 2.1.5 FRECUENCIAS EN RFID                   | 21 |

|              | 2.1.6 <u>ÁREAS DE APLICACIÓN PARA RFID</u>  | 23 |

|              | 2.1.7 CONCLUSIONES                          | 24 |

|              | 2.2 PROTOCOLO SLAP                          | 25 |

|              | 2.2.2 <u>TABLA DE NOTACION</u>              | 25 |

|              | 2.2.3 <u>DISEÑO DEL PROTOCOLO</u>           | 26 |

|              | 2.2.4 <u>ANALISIS DE SEGURIDAD</u> .        | 29 |

|              | 2.2.5 CONCLUSION                            | 30 |

|              | 2.3 <u>MULTIPLICACIÓN MODULAR</u>           | 31 |

|              | 2.3.2 INTRODUCCIÓN MULTIPLICACIÓN MODULAR   | 31 |

|              | 2.2.3 METODO DE KARATSUBA-OFMAN             | 32 |

|              | 2.3.4 <u>MULTIPLICACIÓN DE BOOTH</u>        | 33 |

|              | 2.3.5 COMPARACIÓN BOOTH - KARATSUBA         | 37 |

|              | 2.3.6 <u>METODOS DE REDUCCIÓN DE BARRET</u> | 40 |

|              | 2.3.7 <u>MÉTODO BOOTH - BARRET</u>          | 42 |

|              | 2.3.8 ALGORITMO DE MONTGOMERY               |    |

|              | 2.3.9 ALGORITMO SISTOLIC-MONTGOMERY         | 49 |

|              | 2.3.10 COMPARACIÓN SISTOLIC - ITERATIVO     | 51 |

|              | 2.3.11 <u>RESUMEN</u>                       | 52 |

|              | 2.4 <u>LENGUAJE VHDL</u>                    | 54 |

|              | 2.4.2 <u>INTRODUCCIÓN VHDL</u>              | 54 |

|              | 2.4.3 PROGRAMAS UTILIZADOS                  | 55 |

|              | 2.4.4 TEST-BENCH                            | 57 |

## CAPÍTULO 3: IMPLEMENTACIÓN DE ALGORITMOS IMPLEMENTACIÓN DE ALGORITMOS......61 3.1 <u>MULTIPLICACION COMBINACIONAL</u> 61 3.1.6 RESULTADOS CIRCUITO COMBINACIONAL ...... 67 3.2.3 IMPLEMENTACION EN VHDL......71 3.3 KARATSUBA-OFMAN......82 3.3.2 <u>ALGORITMO</u> ...... 82 3.3.3 IMPLEMENTACIÓN ...... 83 3.4.2.2 IMPLEMENTACIÓN EN VHDL BARRET1......96 3.4.3.2 IMPLEMENTACIÓN EN VHDL ...... 103

| 3.6.2 <u>ALGORITMO</u>                            | 125 |

|---------------------------------------------------|-----|

| 3.6.3 <u>IMPLEMENTACIÓN EN VHDL</u>               | 128 |

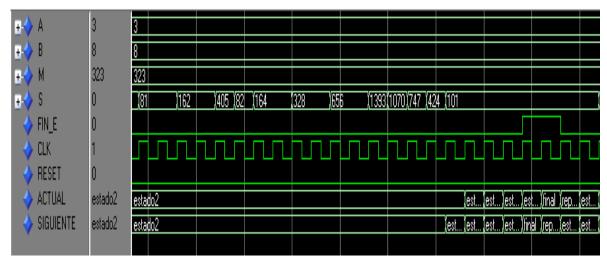

| 3.6.4 <u>SIMULACION</u>                           | 129 |

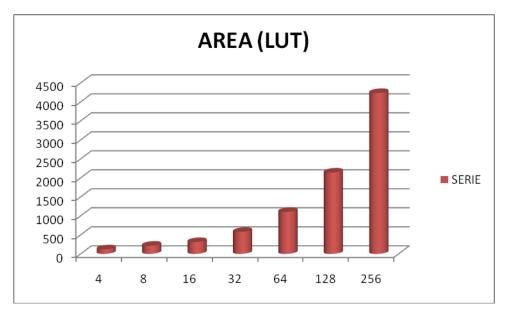

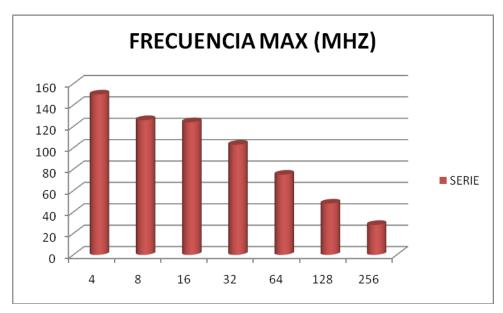

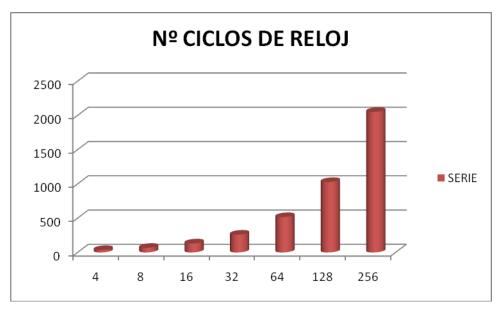

| 3.6.5 <u>SINTESIS</u>                             | 130 |

| 3.6.6 RESULTADOS                                  | 132 |

| 3.7 <u>CONCLUSIÓN DE RESULTADOS</u>               | 136 |

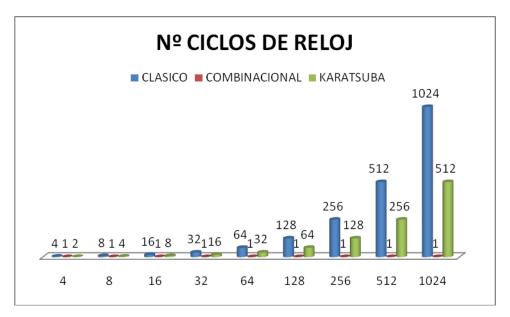

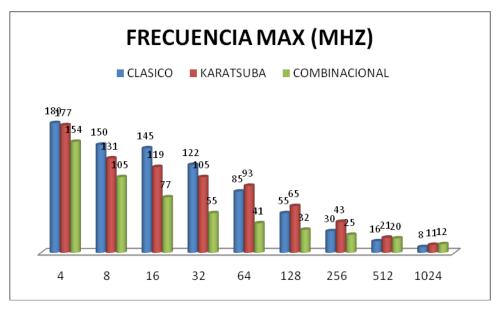

| 3.7.2 CONCLUSIÓN COMBINACIONAL CLASICO KARATSUBA  | 136 |

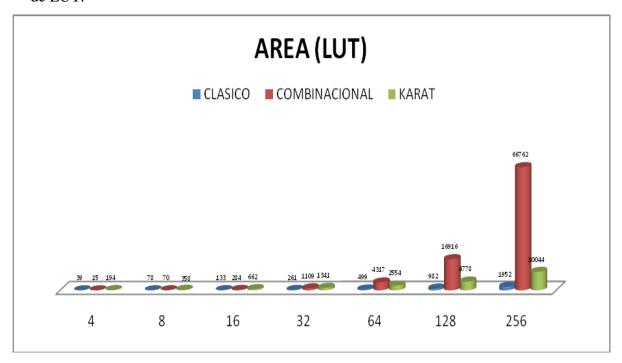

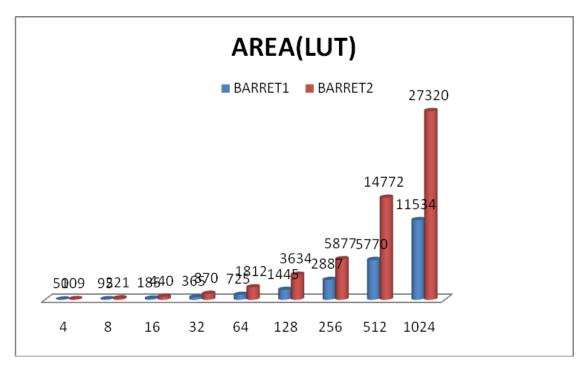

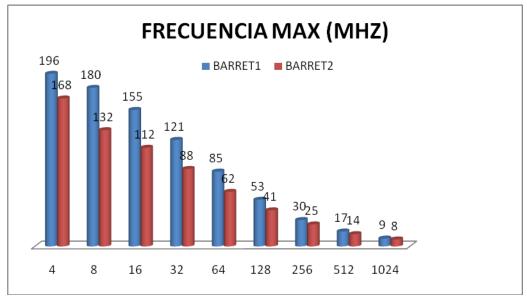

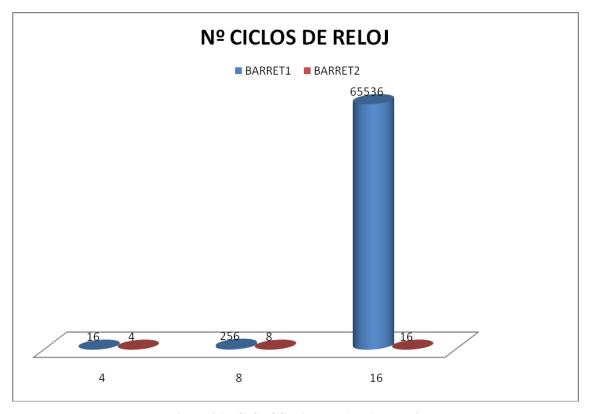

| 3.7.3 CONCLUSIÓN DE RESULTADOS BARRET             | 138 |

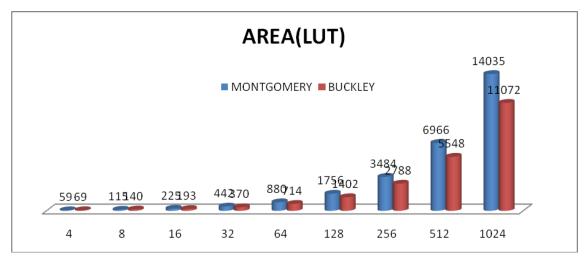

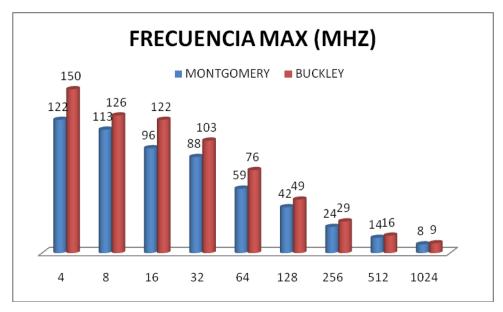

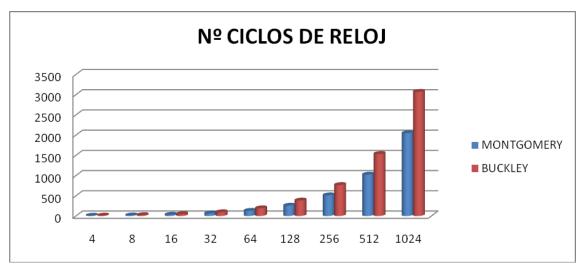

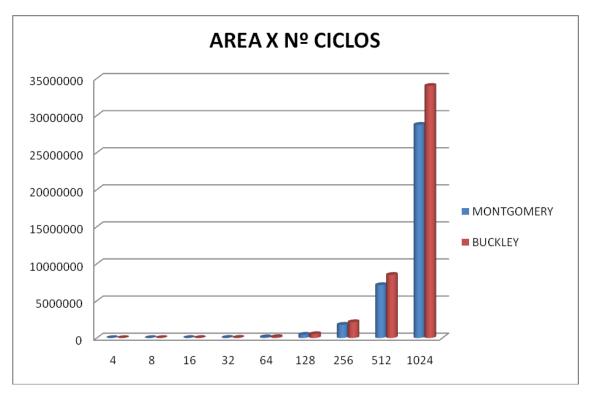

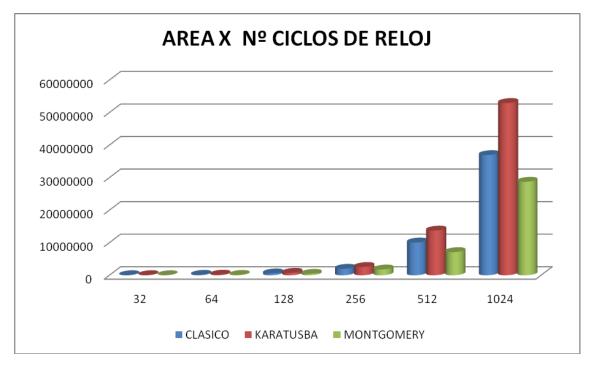

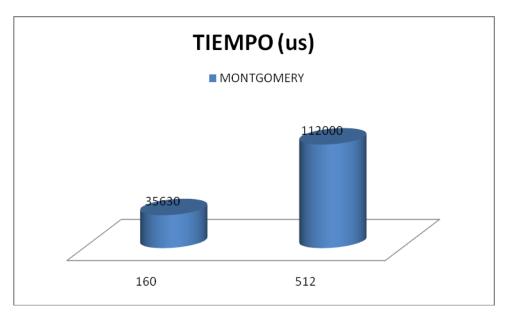

| 3.7.4 CONCLUSIÓN RESULTADOS BUCKLEY-MONTGOMERY    | 140 |

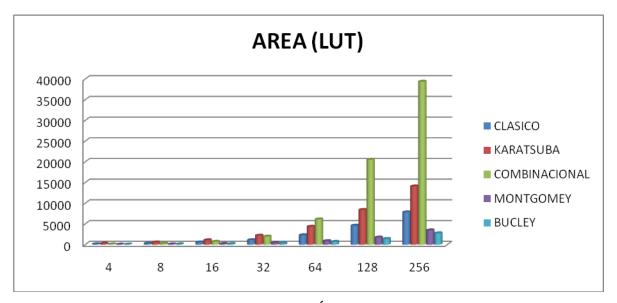

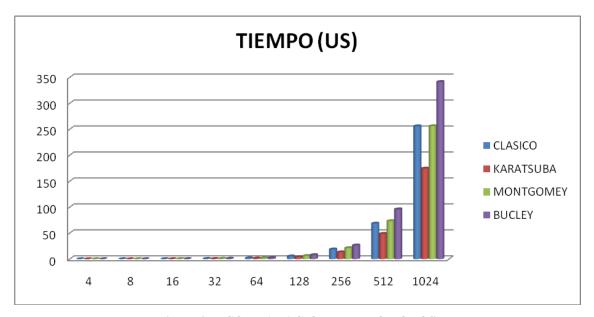

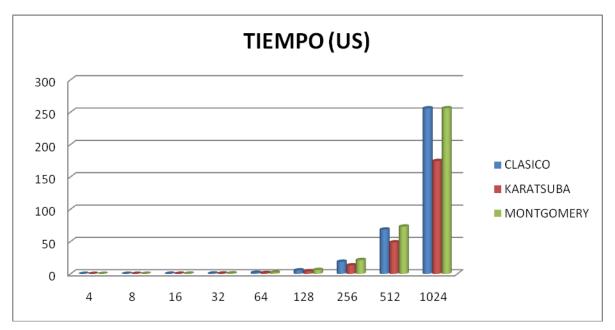

| 3.7.5 CONCLUSIÓN MULTIPLICACIÓN MODULAR           | 143 |

|                                                   |     |

| CAPÍTULO 4: GENERADOR DE NÚMEROS ALEATORIOS       |     |

| 4. IMPLEMENTACIÓN GENERADOR DE NUMEROS ALEATORIOS | 150 |

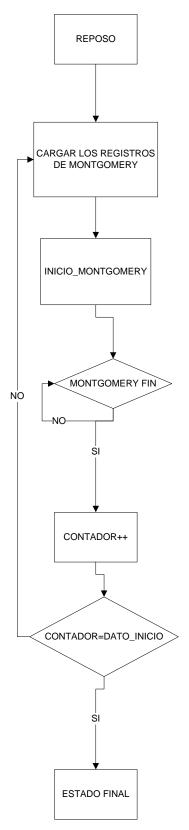

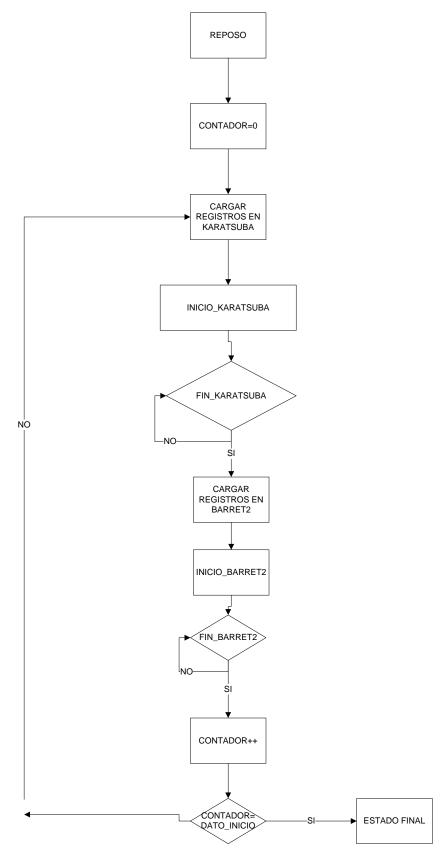

| 4.2 BLUM BLUM AND SHUB =>MONTGOMERY               | 153 |

| 4.2.2 <u>IMPLEMENTACIÓN EN VHDL</u>               | 153 |

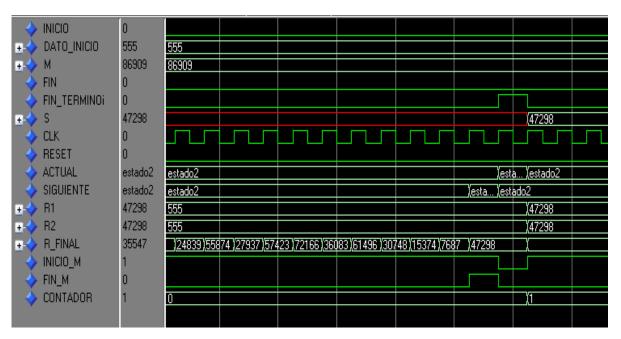

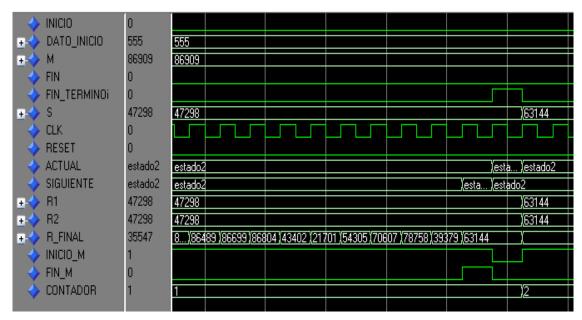

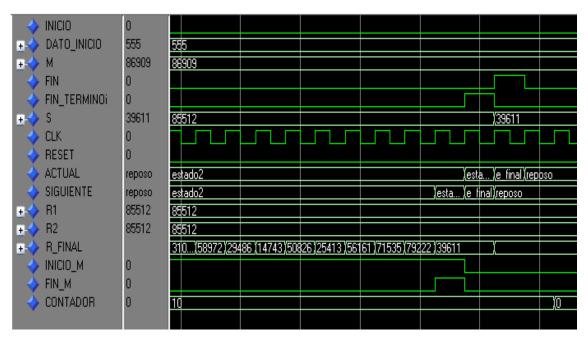

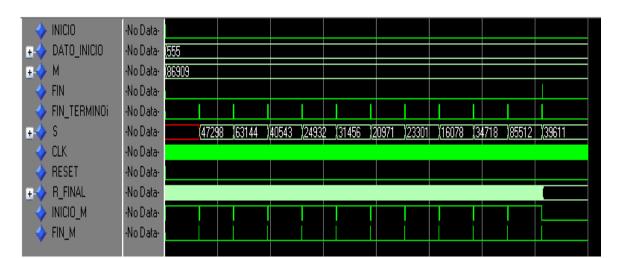

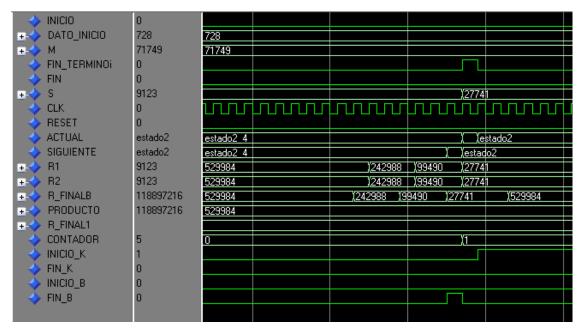

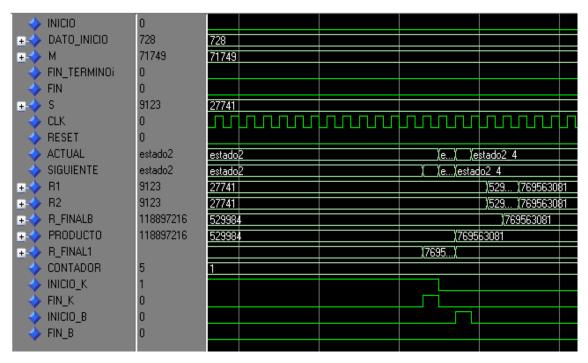

| 4.2.3 <u>SIMULACION</u>                           | 156 |

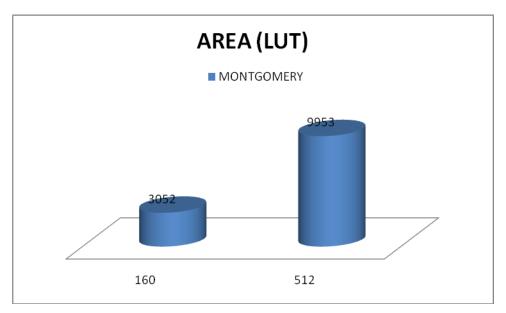

| 4.2.4 <u>SINTESIS</u>                             | 159 |

| 4.2.5 <u>RESULTADOS</u>                           | 160 |

| 4.3 BLUM BLUM AND SHUB (KARATSUBA)                | 163 |

| 4.3.2 <u>IMPLEMENTACIÓN EN VHDL</u>               | 163 |

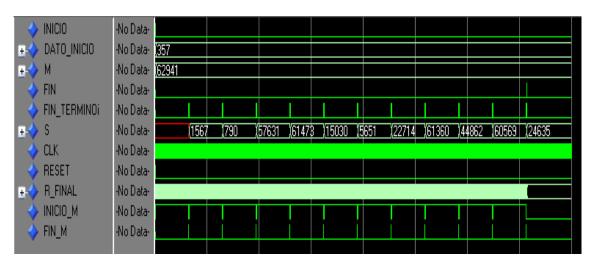

| 4.3.3 <u>SIMULACIÓN</u>                           | 167 |

| 4.3.4 <u>SÍNTESIS</u>                             | 170 |

| 4.3.5 <u>RESULTADOS</u>                           | 171 |

| 4.4 BLUM BLUM AND SHUB (Clasico)                  | 174 |

| 4.4.2 <u>IMPLEMENTACIÓN EN VHDL</u>               | 174 |

| 4.4.3 <u>SIMULACIÓN</u>                           | 178 |

| 4.4.4 <u>SINTESIS</u>                             | 181 |

| 4.4.5 <u>RESULTADOS</u>                           | 182 |

| 4.5 CONCLUSIÓN BLUM BLUM & SHUB                   | 185 |

|                                                   |     |

| CAPÍTULO 5: EXPONENCIACIÓN MODULAR                |     |

| 5. IMPLEMENTACIÓN EXPONENCIACIÓN MODULAR          | 189 |

| 5.2 <u>IMPLEMENTACIÓN EN VHDL</u>                 |     |

| 5.3 <u>SIMULACIÓN</u>                             | 193 |

| 5.4 <u>SINTESIS</u>                               | 195 |

| 5 5 DESULADOS                                     | 107 |

| CA | APÍTULO 6: CONCLUSIÓN DEL PROYECTO |     |

|----|------------------------------------|-----|

| 6. | CONCLUSIÓN DEL PROYECTO            | 200 |

| CA | APÍTULO 7: PROPUESTAS FUTURAS      |     |

| 7. | PROPUESTAS FUTURAS                 | 202 |

| CA | APÍTULO 8: BIBLIOGRAFIA            |     |

| 8. | BIBLIOGRAFÍA                       | 203 |

| CA | APÍTULO 9: ANEXO                   |     |

| 8. | ANEXO                              | 205 |

#### **INDICE DE FIGURAS**

| Figura 1 – TECNOLOGIA RFID                 | 16 |

|--------------------------------------------|----|

| Figura 2 – TECNOLOGIA RFID 2               | 17 |

| Figura 3 – TECNOLOGIA RFID 3               | 17 |

| Figura 4 – TECNOLOGIA RFID 4               | 19 |

| Figura 5 – TECNOLOGIA RFID 5               | 20 |

| Figura 6 – ANCHO DE FRECUENCIA RFID        | 21 |

| Figura 7 – CARACTERISTICAS FRECUENCIA RFID | 22 |

| Figura 8 – REGIONES RFID                   | 23 |

| Figura 9 – APLICACIÓN RFID                 | 24 |

| Figura 10 - SLAP                           | 25 |

| Figura 11 – SLAP 2                         | 26 |

| Figura 12 – SLAP 3                         | 27 |

| Figura 13 – SLAP 4                         | 28 |

| Figura 14 - MODULAR MULTIPLICATION         | 31 |

| Figura 15 - MODULAR MULTIPLICATION 2       | 33 |

| Figura 16 - MODULAR MULTIPLICATION 3       | 33 |

| Figura 17 - MODULAR MULTIPLICATION 4       | 34 |

| Figura 18 - MODULAR MULTIPLICATION 5       | 34 |

| Figura 19 - MODULAR MULTIPLICATION 6       | 35 |

| Figura 20 - MODULAR MULTIPLICATION 7       | 35 |

| Figura 21 - MODULAR MULTIPLICATION 8       | 36 |

| Figura 22 - MODULAR MULTIPLICATION 9       | 37 |

| Figura 23 – RETRASO KARAT_BOOTH            | 38 |

| Figura 24 – AREA KARAT_BOOTH               | 39 |

| Figura 25 – AREA X TIEMPO KARAT_BOOTH      | 39 |

| Figura 26 – RESTO BARRET                   | 41 |

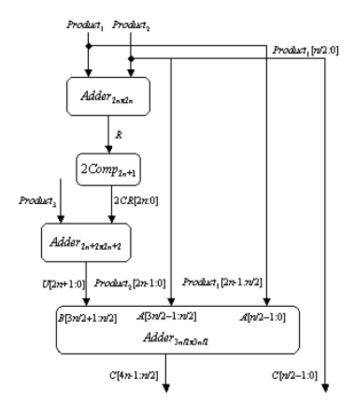

| Figura 27 - ARQUITECTURA M.MODULAR         | 42 |

| Figura 28 - ARQUITECTURA MONTG 1           | 44 |

| Figura 29 - CONTROLADOR MONTGOMERY         | 44 |

| Figura 30 - ARQUITECTURA MONTG 2           | 46 |

| Figura 31 - ESTADOS MONTGOMERY             | 46 |

| Figura 32 - CONTROLADOR MONTG 2            | 48 |

| Figura 33 - SIMULACION MONTG 1             | 48 |

| Figura 34 - SIMULACION MONTG 2             | 49 |

| Figura 35 - ARQUITECTURA SISTOLIC          |    |

| Figura 36 - CELDA PE                       | 51 |

|                                            |    |

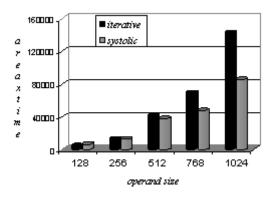

| Figura 37 - GRAFICA 4                | 52  |

|--------------------------------------|-----|

| Figura 38 - D.ESTADOS PROYECTO       | 56  |

| Figura 39 - D.ESTADOS COMBINACIONAL  | 64  |

| Figura 40 - SIMULACION COMB 1        | 64  |

| Figura 41 - SIMULACION COMB 2        | 65  |

| Figura 42 - AREA COMBINACIONAL       | 68  |

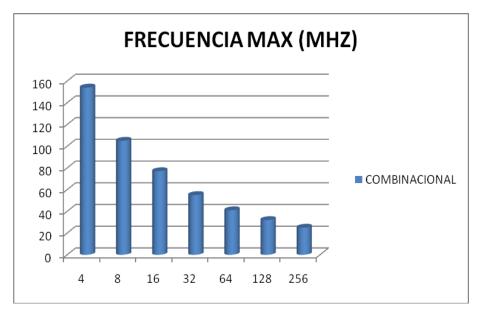

| Figura 43 - FRECUENCIA COMBINACIONAL | 68  |

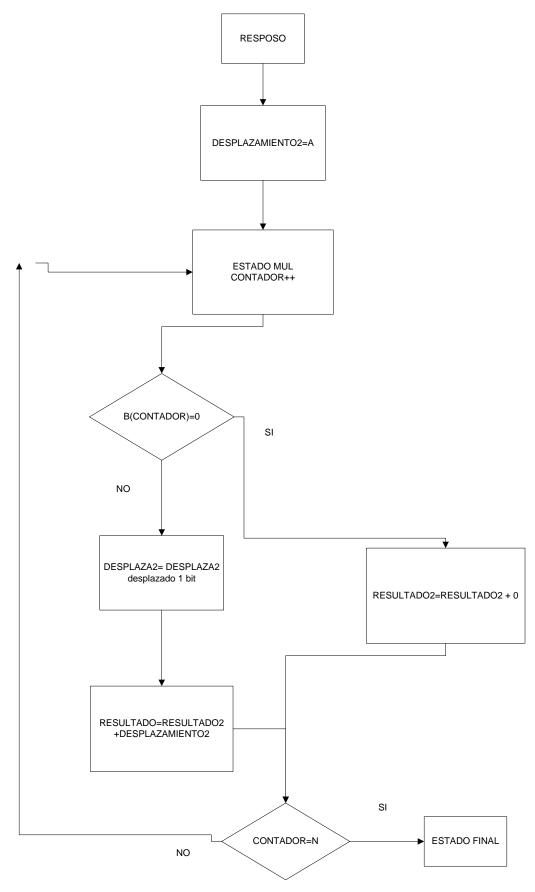

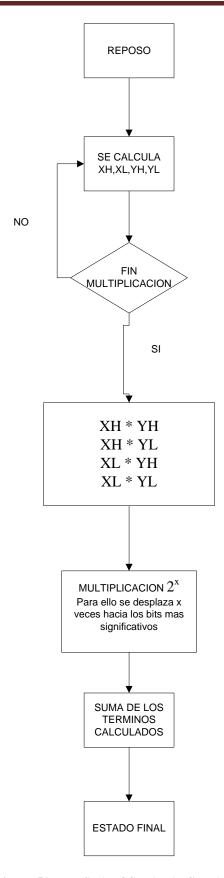

| Figura 44 - ALGORITMO CLASICO        | 70  |

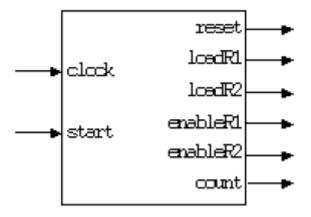

| Figura 45 - ENTIDAD CLASICO          | 72  |

| Figura 46 - D.ESTADOS CLASICO        | 74  |

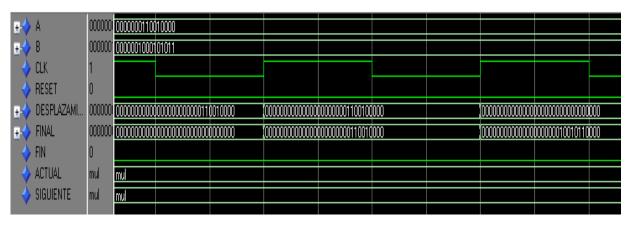

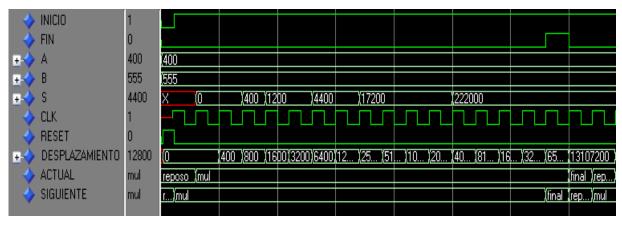

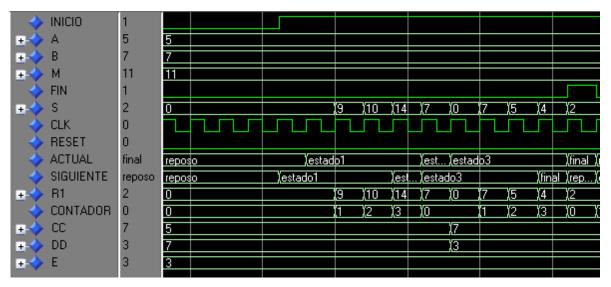

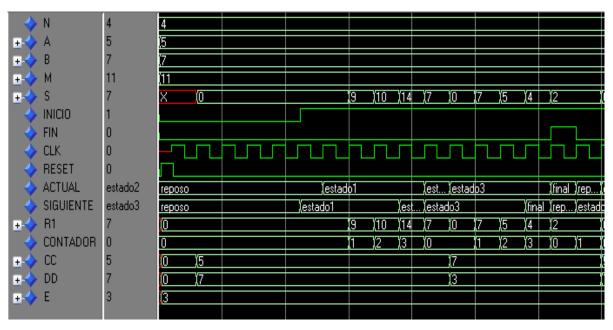

| Figura 47 - SIMULACION CLASICO 1     | 75  |

| Figura 48 - SIMULACION CLASICO 2     | 75  |

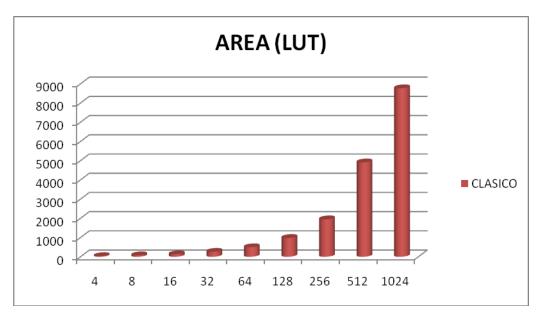

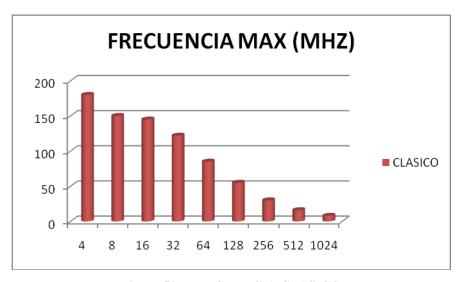

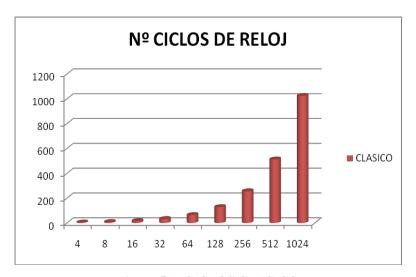

| Figura 49 - AREA CLASICO             | 79  |

| Figura 50 - FRECUENCIA CLASICO       | 80  |

| Figura 51 - CICLOS CLASICO           |     |

| Figura 52 - D.ESTADOS KARATSUBA      | 87  |

| Figura 53 - SIMULACION KARATSUBA 1   | 88  |

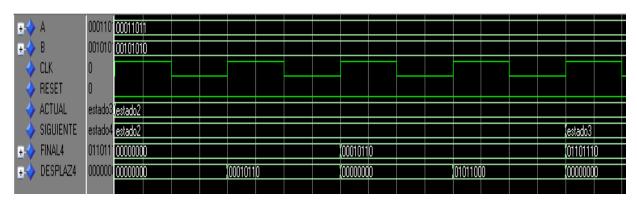

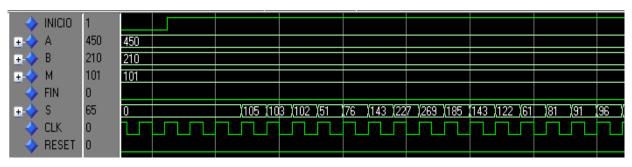

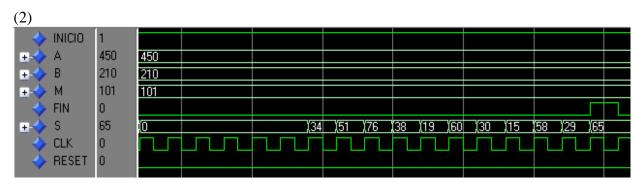

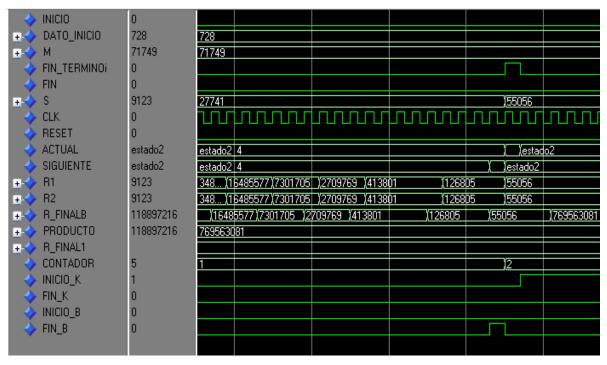

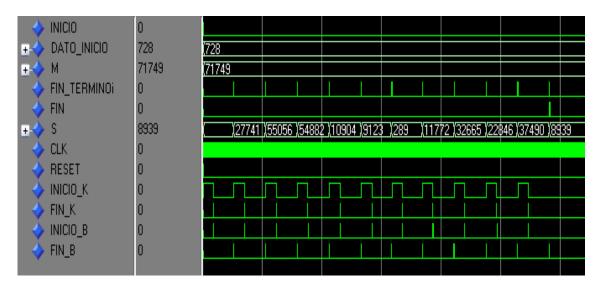

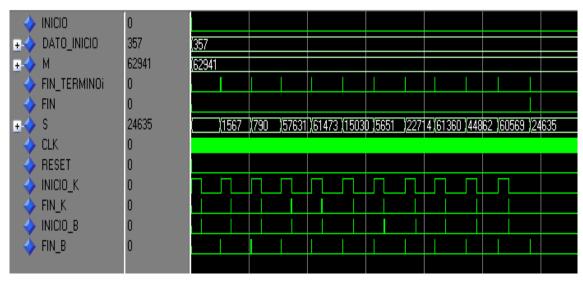

| Figura 54 - SIMULACION KARATSUBA 2   | 89  |

| Figura 55 - SIMULACION KARATSUBA 3   | 89  |

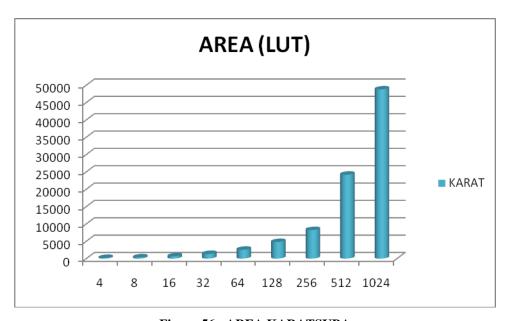

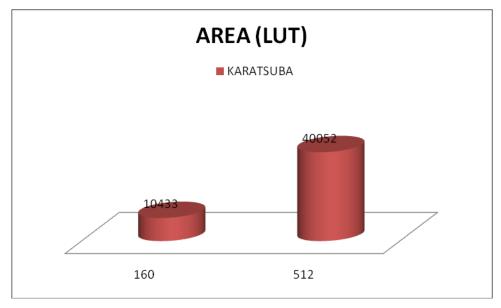

| Figura 56 - AREA KARATSUBA           | 92  |

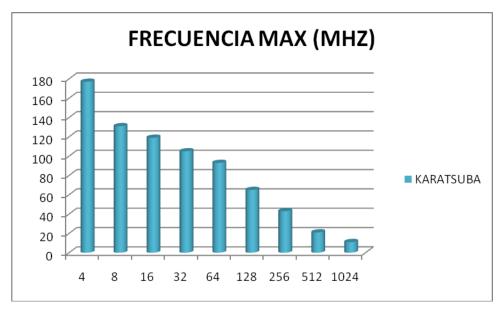

| Figura 57 - FRECUENCIA KARATSUBA     | 93  |

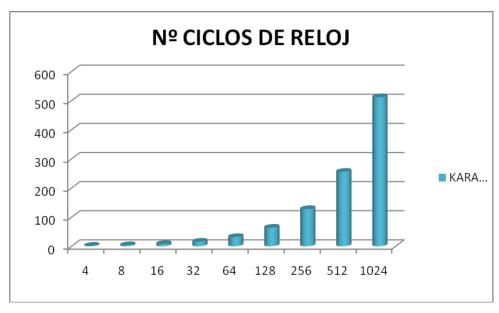

| Figura 58 - CICLOS KARATSUBA         | 93  |

| Figura 59 - D. ESTADOS BARRET1       | 98  |

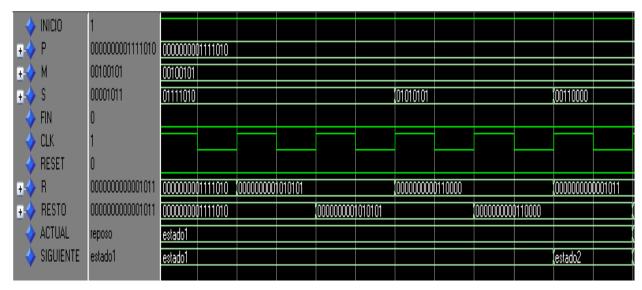

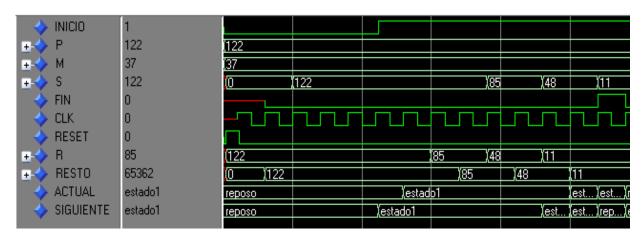

| Figura 60 - SIMULACION BARRET1 1     | 99  |

| Figura 61 - SIMULACION BARRET1 2     | 99  |

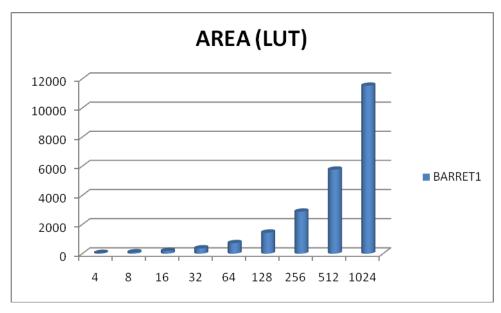

| Figura 62 - AREA BARRET1             | 103 |

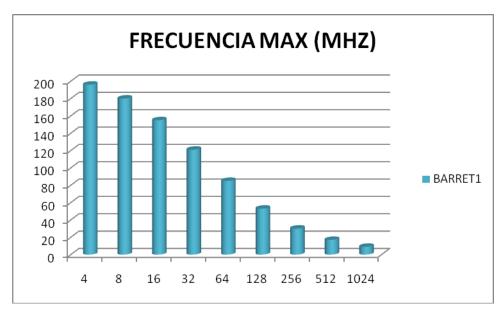

| Figura 63 - FRECUENCIA BARRET1       | 103 |

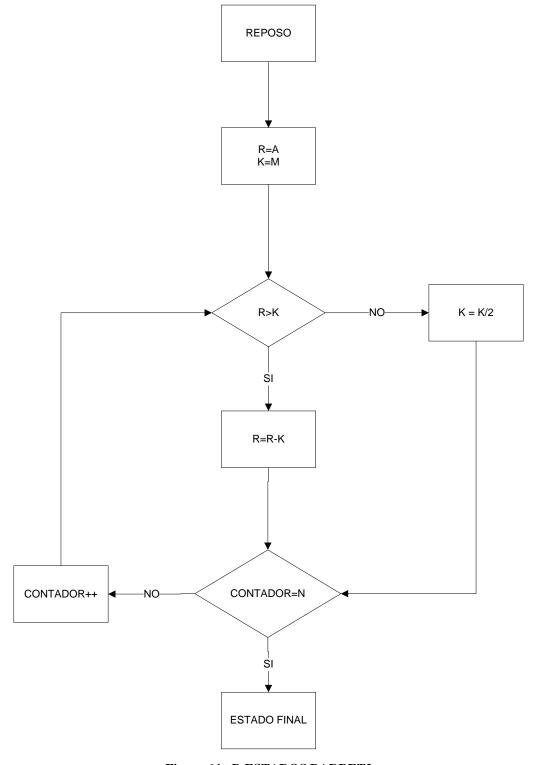

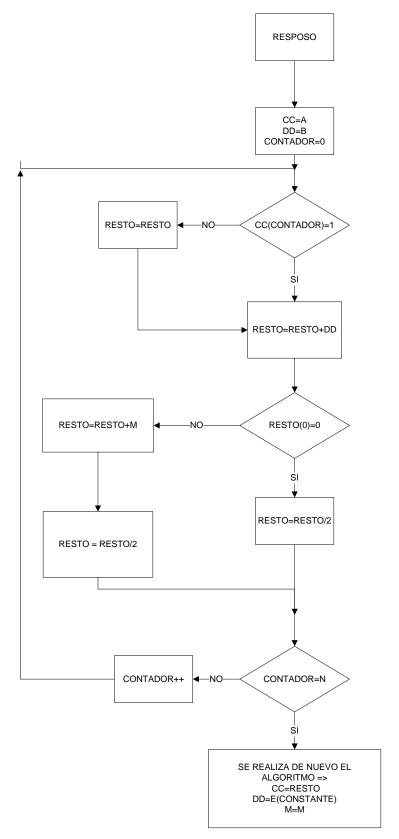

| Figura 64 - D.ESTADOS BARRET2        | 105 |

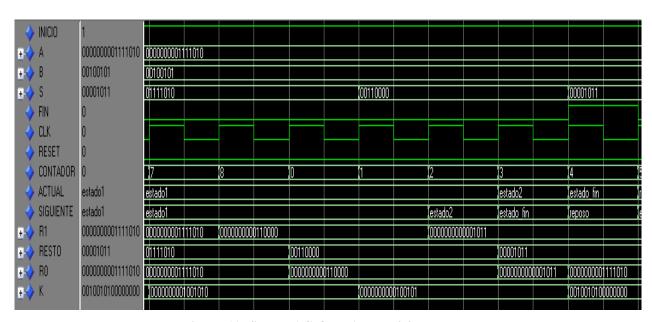

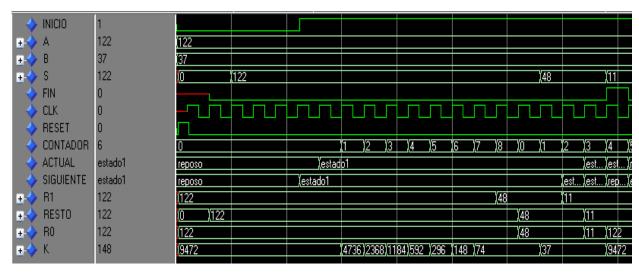

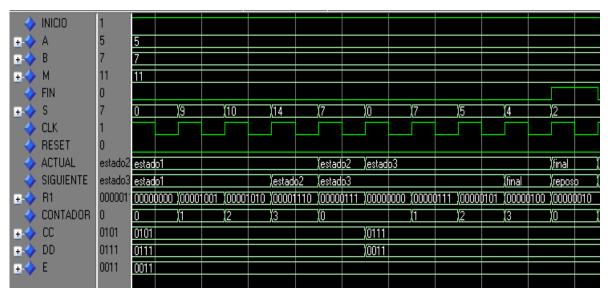

| Figura 65 - SIMULACION BARRET2 1     | 106 |

| Figura 66 - SIMULACION BARRET2 2     | 106 |

| Figura 67 - SIMULACION BARRET2 3     | 107 |

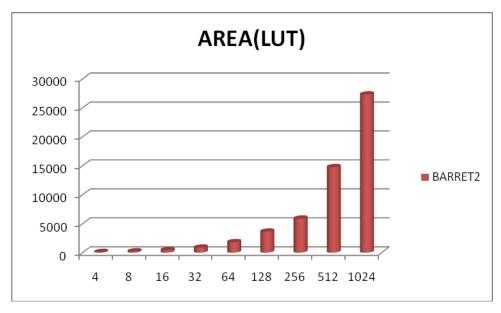

| Figura 68 - AREA BARRET2             | 111 |

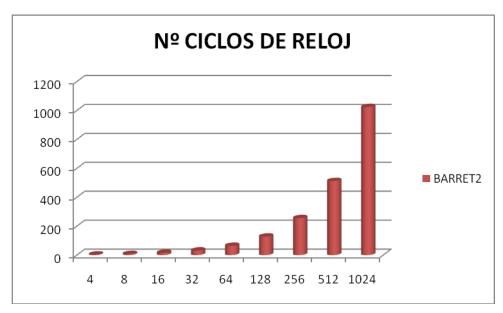

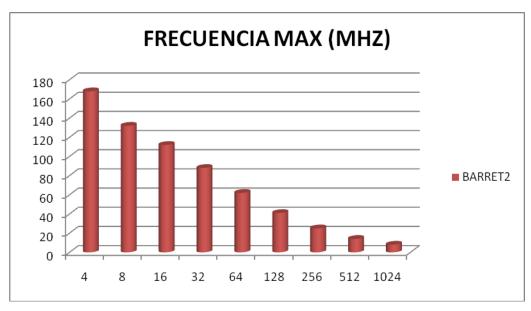

| Figura 69 - CICLO BARRET2            | 111 |

| Figura 70 - FRECUENCIA BARRET2       | 112 |

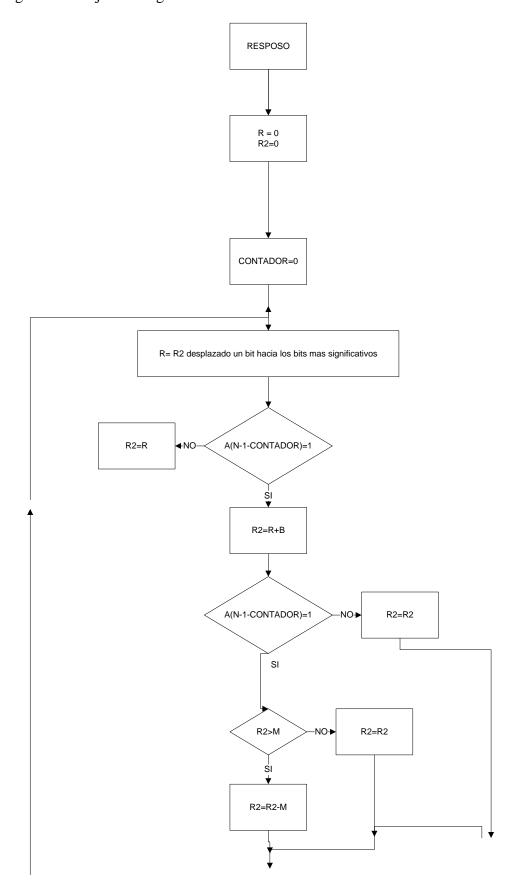

| Figura 71 - D.ESTADOS MONTGOMERY     | 116 |

| Figura 72 - SIMLACION MONTGOMERY 1   | 117 |

| Figura 73 - SIMLACION MONTGOMERY 2   |     |

| Figura 74 - SIMULACION MONTGOMERY 3  | 118 |

| Figura 75 - SIMULACION MONTGOMERY 4              | 119 |

|--------------------------------------------------|-----|

| Figura 76 - SIMULACION MONTGOMERY 5              | 119 |

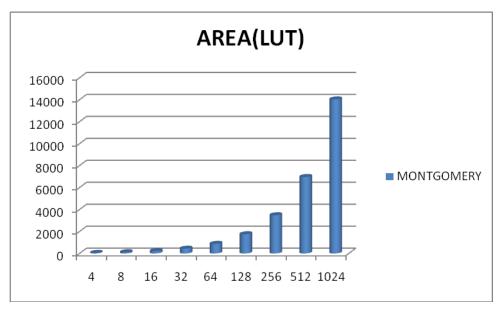

| Figura 77 - AREA MONTGOMERY                      |     |

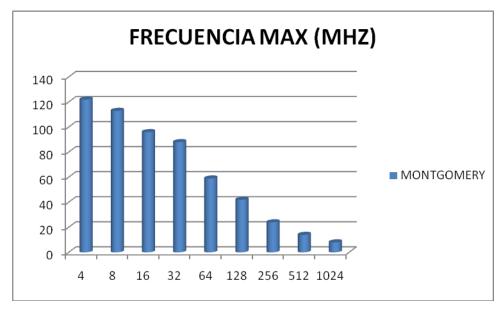

| Figura 78 - FRECUENCIA MONTGOMERY                | 123 |

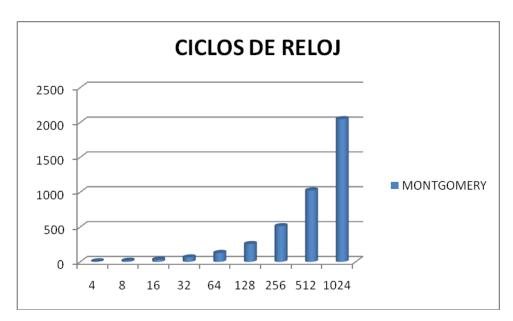

| Figura 79 - CICLOS MONTGOMERY                    | 123 |

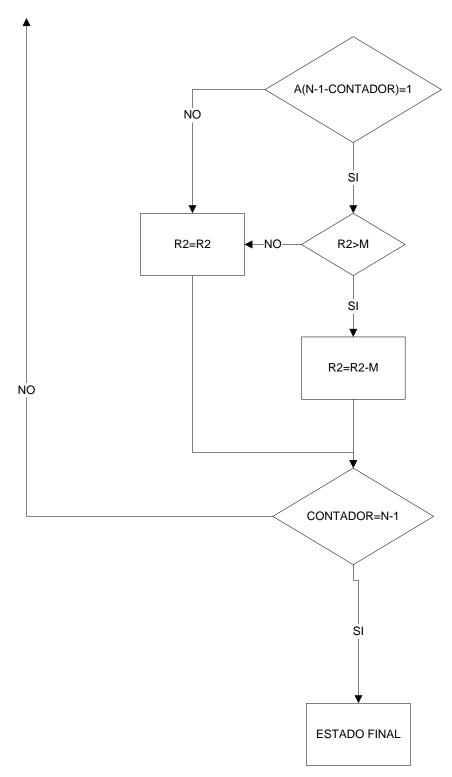

| Figura 80 - D.ESTADOS BUCLEY                     | 127 |

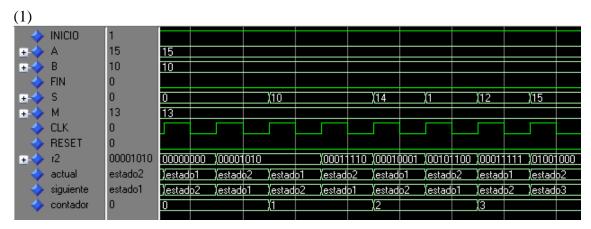

| Figura 81 - SIMULACION BUCKLEY 1                 | 129 |

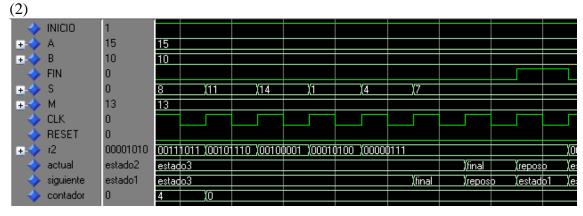

| Figura 82 - SIMULACION BUCKLEY 2                 | 129 |

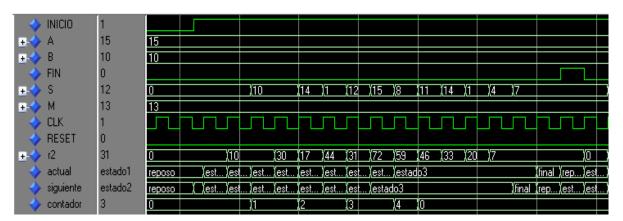

| Figura 83 - SIMULACION BUCKLEY 3                 | 130 |

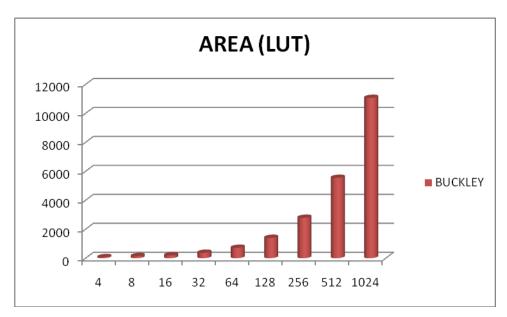

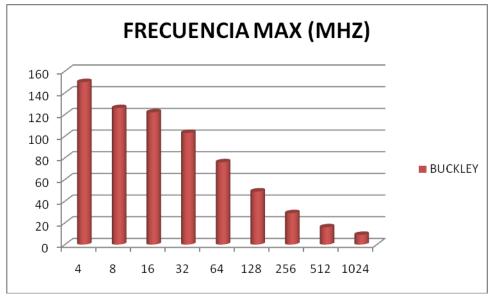

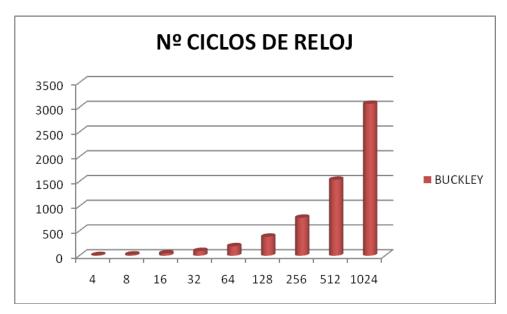

| Figura 84 - AREA BUCKLEY                         | 133 |

| Figura 85 - FRECUENCIA BUCKLEY                   | 133 |

| Figura 86 - CICLOS BUCKLEY                       | 134 |

| Figura 87 - CICLOS COMB_CLASICO_KARAT            | 136 |

| Figura 88 - FRECUENCIA COMB_CLA_KARAT            | 137 |

| Figura 89 - AREA BARRET1_BARRET2                 | 139 |

| Figura 90 - FRECUENCIA BARRET1_BARRET2           | 139 |

| Figura 91 - CICLOS BARRET1_BARRET2               |     |

| Figura 92 - AREA MONTGOMERY_BUCKLEY              | 141 |

| Figura 93 - FRECUENCIA MONTGOMERY-BUCKLEY        | 141 |

| Figura 94 - CICLOS MONTGOMERY_BUCKLEY            | 142 |

| Figura 95 - AREA X CICLOS MONT_BUCKLEY           |     |

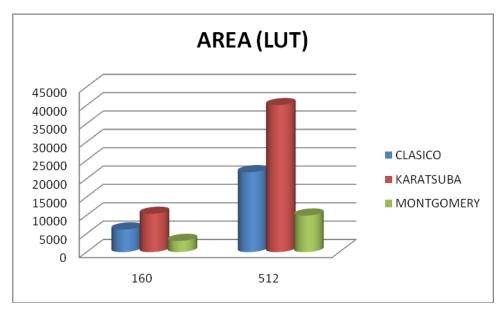

| Figura 96 - COMPARACIÓN AREA TODOS               | 144 |

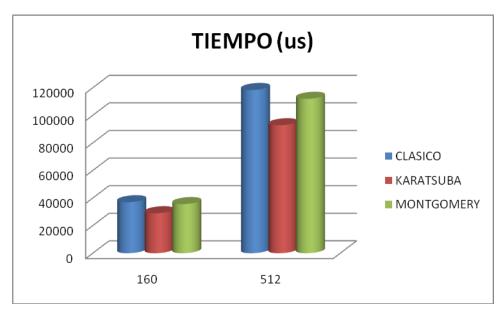

| Figura 97 - COMPARACION TIEMPO TODOS             | 145 |

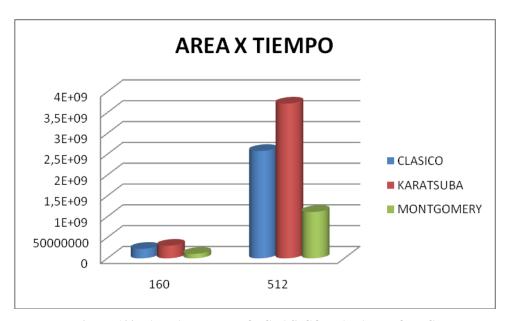

| Figura 98 - TIEMPO CLASICO_KARAT_MONTGOMERY      | 146 |

| Figura 99 - AREA X CICLOS CLASICO_KARAT_MONTG    | 147 |

| Figura 100 - ENTIDAD BLUM BLUM & SHUB MONTGOMERY | 153 |

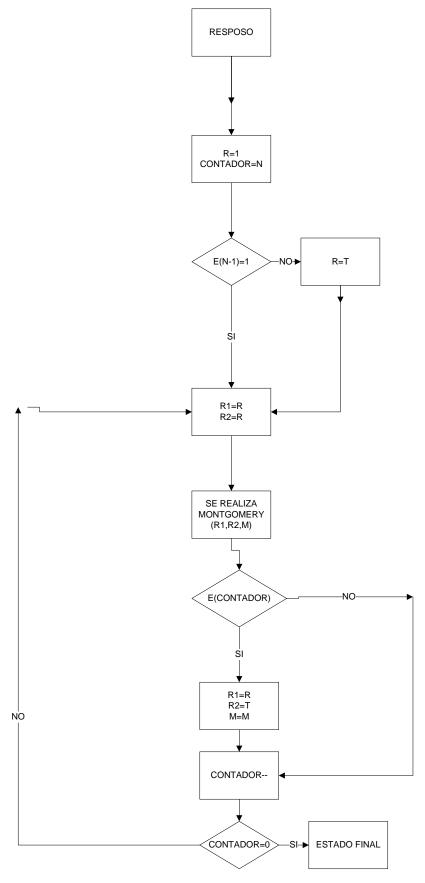

| Figura 101 - D.ESTADOS BB&SHUB MONTGOMERY        | 155 |

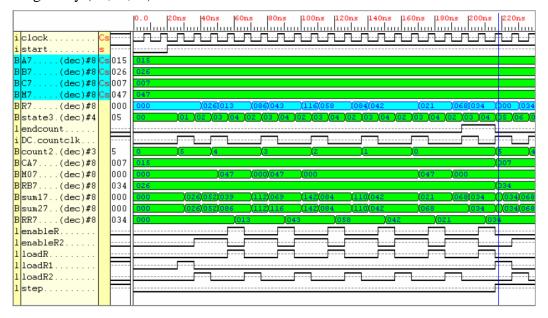

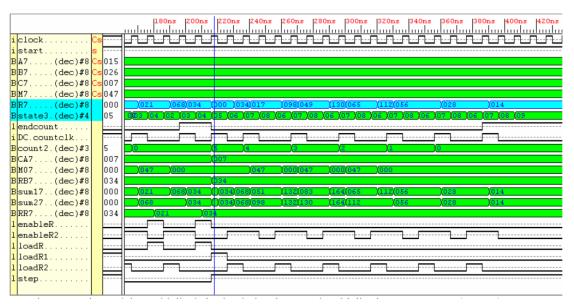

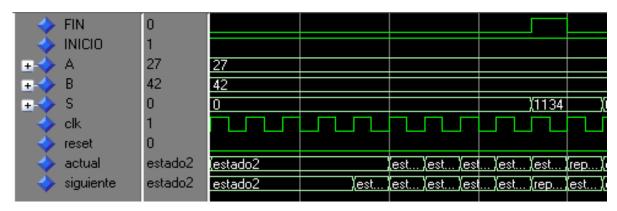

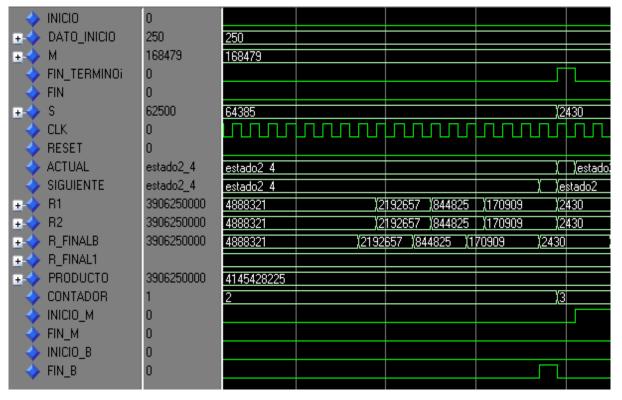

| Figura 102 - SIMULACION BBS MONTGOMERY 1         | 156 |

| Figura 103 - SIMULACION BB&S MONTGOMERY 2        | 157 |

| Figura 104 - SIMULACION BB&S MONTGOMERY 3        | 157 |

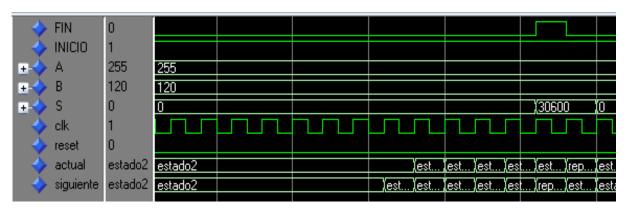

| Figura 105 - SIMULACION BB&S MONTGOMERY 4        | 158 |

| Figura 106 - SIMULACION BB&S MONTGOMERY 5        | 159 |

| Figura 107 - AREA BB&S MONTGOMERY                | 160 |

| Figura 108 - TIEMPO BB&S MONTGOMERY              | 161 |

| Figura 109 - ENTIDAD BB&S KARATSUBA              | 163 |

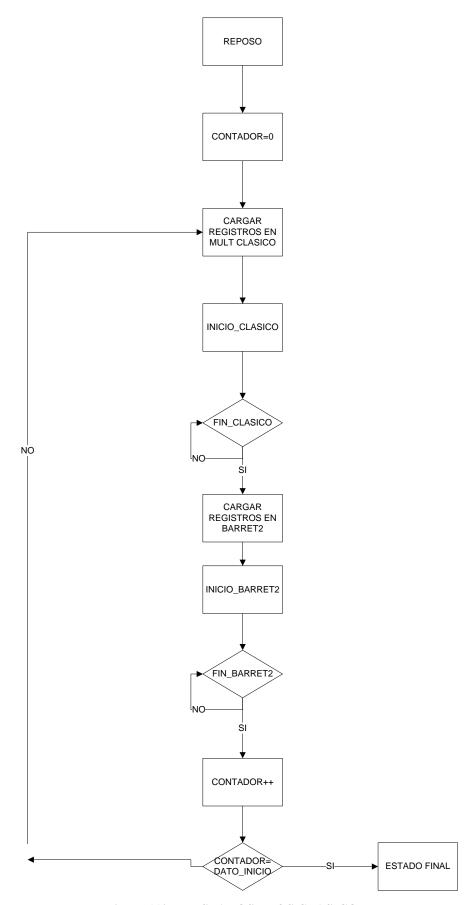

| Figura 110 - D.ESTADOS BB&S KARATSUBA            | 166 |

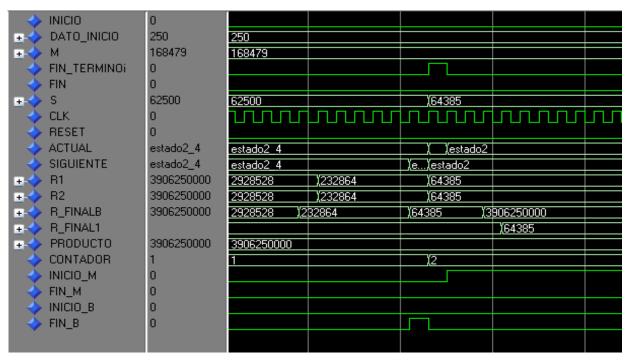

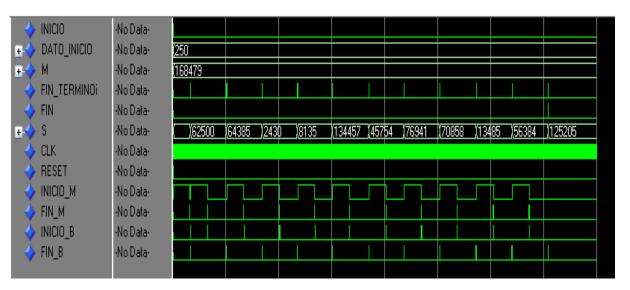

| Figura 111 - SIMULACION BB&S KARATSUBA 1         | 167 |

| Figura 112 - SIMULACION BB&S KARATSUBA 2         | 168 |

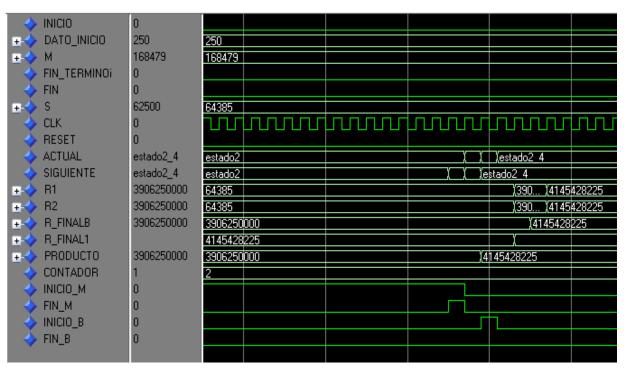

| Figura 113 - SIMULACION BB&S KARATSUBA 3       | 168 |

|------------------------------------------------|-----|

| Figura 114 - SIMULACION BB&S KARATSUBA 4       | 169 |

| Figura 115 SIMULACION BB&S KARATSUBA 5         | 170 |

| Figura 116 - AREA BB&S KARATSUBA               | 172 |

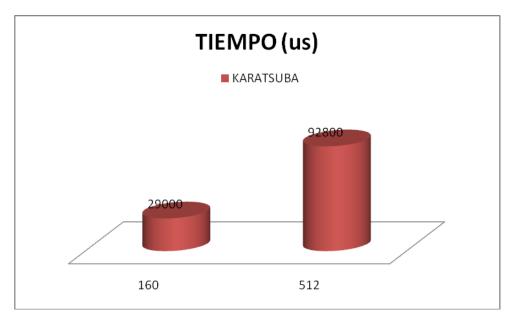

| Figura 117 - TIEMPO BB&S KARATSUBA             | 172 |

| Figura 118 - ENTIDAD BB&S CLASICO              | 174 |

| Figura 119 - D.ESTADOS BB&S CLASICO            | 177 |

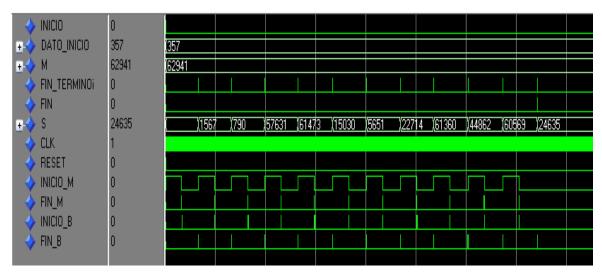

| Figura 120 - SIMULACION BB&S CLASICO 1         | 178 |

| Figura 121 - SIMULACION BB&S CLASICO 2         | 179 |

| Figura 122 - SIMULACION BB&S CLASICO 3         | 179 |

| Figura 123 - SIMULACION BB&S CLASICO 3         | 180 |

| Figura 124 - SIMULACION BB&S CLASICO 4         | 181 |

| Figura 125 - AREA BB&S CLASICO                 | 183 |

| Figura 126 - TIEMPO BB&S CLASICO               | 183 |

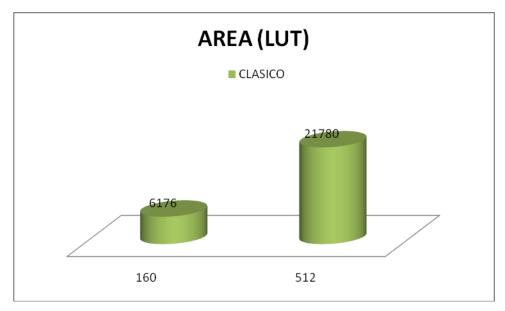

| Figura 127 - AREA BB&S CLASICO_KARAT_MONTG     | 185 |

| Figura 128 - TIEMPO CLASICO_KARAT_MONTG        | 186 |

| Figura 129 - AREA X TIEMPO CLASICO_KARAT_MONTG | 186 |

| Figura 130 - D.ESTADOS EXPONENTIATION          | 192 |

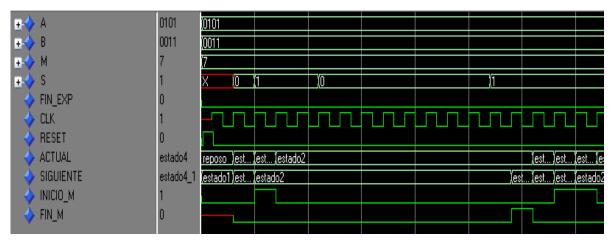

| Figura 131 - SIMULACION EXP 1                  | 193 |

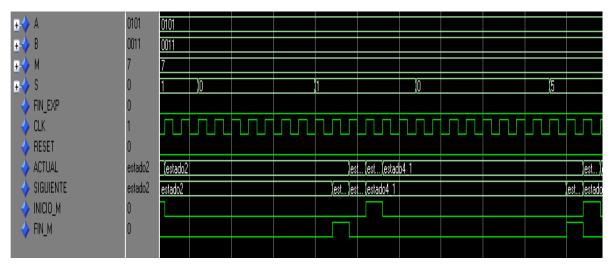

| Figura 132 - SIMULACION EXP 2                  | 193 |

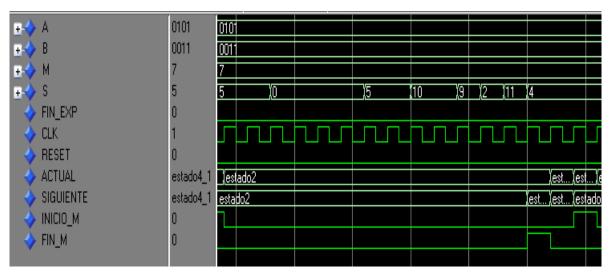

| Figura 133 - SIMULACION EXP 3                  | 194 |

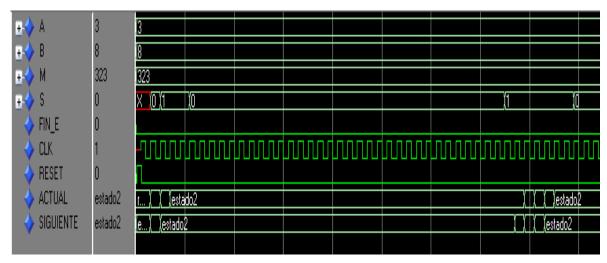

| Figura 134 - SIMULACION EXP 4                  | 194 |

| Figura 135 - SIMULACION EXP 5                  | 195 |

| Figura 136 - SIMULACION EXP 6                  | 195 |

| Figura 137 - AREA EXPONENTIATION               | 198 |

| Figura 138 - FRECUENCIA EXP                    | 198 |

| Figura 139 - TIEMPO EXP                        | 199 |

# INTRODUCCIÓN DEL PROYECTO

#### 1. OBJETIVO DEL PROYECTO

Actualmente los Sistemas de Identificación Automáticos se están convirtiendo en algo muy popular, de aquí el nacimiento de una nueva tecnología para la transmisión de datos, entre un transmisor (Transponder) y un lector, sin contacto físico. Estos son los llamados sistemas RFID. Esta tecnología consiste en la transmisión de datos por radio frecuencia, y va a ser en uno de los aspectos de esta tecnología en lo que se va a fundamentar nuestro proyecto.

En este proyecto queremos realizar un sistema para la encriptación de los datos enviados a través de la tecnología RFID, de modo que los datos que sean enviados estén encriptados y no sea posible su manipulación. La aplicación para la que se quiere realizar la encriptación es para las tarjetas tags. Estas tarjetas envían información a un receptor u otras tarjetas a través de señales de radio frecuencia., esa información enviada es la que se quiere proteger encriptando estos datos. El sistema de encriptado el cual se quiere implementar consta de 3 partes:

- a) Protocolo de encriptado el cual el receptor y el emisor establecen una comunicación de autentificación para que los datos que envíen estén protegidos.

En este proyecto este protocolo no se ha implementado pero se realizará un ejemplo de protocolo de encriptación llamado SLAP.

- b) Para el protocolo de encriptación como es el caso del SLAP necesita de una serie de algoritmos, una parte importante de estos algoritmos es lo que se conoce como generador de números aleatorios, en este proyecto se implementará un generador de números aleatorios de modo que se pueda utilizar en el protocolo de comunicación.

- c) A su vez el generador de números aleatorios que queremos implementar necesita de un algoritmo el cual realice la multiplicación modular. En este proyecto se ha implementado diferentes algoritmos que realizan la multiplicación modular de modo que se ha podido comparar entre ello cual es el mejor para nuestra aplicación.

Por tanto la mayor parte del proyecto constará en buscar diferentes algoritmos de implementación modular y comparar todos estos en área que ocupa y el tiempo que tarda. Considerando que en nuestro circuito que queremos implementar estos algoritmos no se trata de un microprocesador ni de una fpga sino que se trata de un

circuito hecho a medida, las características que se buscará en los algoritmos será que ocupe un área limitada y que el tiempo de computo no sea excesivamente alto.

Una vez implementado los diferentes algoritmos de multiplicación modular y hechas las comparaciones, aplicaremos los algoritmos que consideremos más eficientes en un generador de números aleatorios, de modo que en esta aplicación podremos ver cuáles de los algoritmos que previamente se han seleccionado se adaptan mejor en nuestra aplicación. Por último se va a realizar también una implementación del algoritmo de exponenciación modular el cual también se puede aplicar en el generador de números aleatorios.

El proyecto quedará organizado de la siguiente manera:

- a) En primer lugar se hablará de los conceptos básicos sobre la tecnología RFID, en este apartado se realizará una introducción sobre esta tecnología y sus aplicaciones.

- b) A continuación se estudiará un ejemplo de un protocolo de encriptación, se desarrollará el protocolo SLAP.

- c) Posteriormente se hablará de los conceptos básicos sobre el lenguaje utilizado en la programación, en este proyecto se programará en VHDL.

- d) Se realizará la implementación de los diferentes algoritmos de multiplicación modular que se han considerados para este proyecto. Para cada algoritmo se implementará en vhdl, se realizará la simulación, seguidamente se realizará la síntesis para finalmente obtener los resultados en cuanto a área y tiempo. Por último una vez obtenido los resultados de los algoritmos se realizará la comparación de todos ellos, de la comparación descartaremos aquellos de los cuales no son válidos para nuestro sistema.

- e) De los algoritmos que hemos considerado que se pueden aplicar al sistema de RFID los probaremos en un generador de números aleatorios. El generador de números aleatorios que se implementará será el de Blum Blum & Shub. En este caso se realizará la implementación en vhdl como en el caso de los multiplicadores modulares, después se realizará las simulaciones y posteriormente se realizará la síntesis para finalmente obtener los resultados en cuanto a área ocupada y tiempo que tarda en realizar el cálculo.

- f) Por último para finalizar el proyecto se implementará un algoritmo de exponenciación modular en el cual se necesitará los algoritmos de multiplicación modular.

A continuación se muestra los algoritmos que se van a implementar.

- a) Algoritmo basado en un circuito combinacional.

- b) Algoritmo basado en un circuito secuencial, al que denominaremos algoritmo clásico.

- c) Algoritmo Karatsuba Offman.

- d) Algoritmos de Barret.

- e) Algoritmo de Montgomery.

- f) Algoritmo de Buckley.

De todos estos algoritmos se va a elegir el que sea más favorable para nuestra aplicación.

# TECNOLOGÍA RFID

# [RADIO FREQUENCY IDENTIFICATION]

RFID - PROTOCOLO SLAP - MULTIPLICACIÓN MODULAR

#### 2. TECNOLOGÍA RFID

RFID (siglas de Radio Frequency IDentification, en español Identificación por radiofrecuencia) es un sistema de almacenamiento y recuperación de datos remoto que usa dispositivos denominados etiquetas, transpondedores o tags RFID. El propósito fundamental de la tecnología RFID es transmitir la identidad de un objeto (similar a un número de serie único) mediante ondas de radio. Las tecnologías RFID se agrupan dentro de las denominadas Auto ID (Automatic Identification, o Identificación Automática).

La tecnología RFID <sup>1</sup> está orientada a almacenamiento de datos y su transmisión, en el mercado existen varias tecnologías para introducir fácilmente la información de un producto en un sistema informático. La más popular es sin duda el código de barras, el cual es muy barato y fácil de implantar. No obstante presenta numerosos inconvenientes:

- a) Puede almacenar poca información. Por ejemplo los códigos de barras usados en los productos alimentarios contienen sólo 12 dígitos.

- b) Son relativamente difíciles de leer: es necesario orientar perfectamente el lector con el código para obtener una lectura correcta.

- c) No pueden ser modificados una vez impresos.

- d) Se deterioran fácilmente

Debido a esto, desde hace años se está popularizando una tecnología de identificación por radiofrecuencia (RFID) que presenta numerosas ventajas frente a los códigos impresos:

- a) Es difícil destruir

- b) Es fácil de leer, incluso es capaz de leer varios productos a la vez.

- c) Contiene mayor cantidad de información

- d) No necesita contacto directo, debido a que la lectura se realiza por radiofrecuencia.

- e) Permite la lectura del objeto en movimiento.

<sup>1</sup> [1] [2] y [3] bi<u>bliografía</u>

Una de las pocas desventajas que encontramos en la tecnología RFID frente al código de barras es su coste, debido a que el código de barras es un sistema que se puede realizar por impresión mientras que la tecnología RFID necesita de un circuito integrado.

#### 2.1 FUNCIONAMIENTO RFID

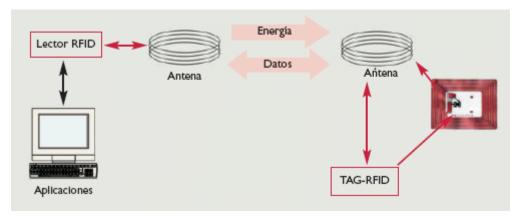

El modo de uso de la tecnología RFID es similar al tradicional código de barras. Al producto que se desea identificar se le añade una etiqueta y se utiliza un lector conectado a un ordenador para obtener la información de identificación automáticamente. No obstante, las similitudes terminan ahí: tanto la etiqueta como el lector son totalmente diferentes. El principio de funcionamiento es el siguiente: el lector emite una señal electromagnética que al ser recibida por la etiqueta hace que ésta responda mediante otra señal en la que se envía codificada la información contenida en la etiqueta.

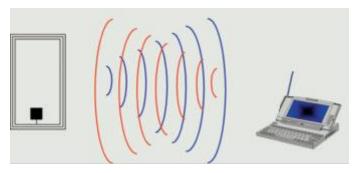

Figura 1 - TECNOLOGIA RFID

El funcionamiento de la tecnología RFID se resumen a continuación:

- a) El lector manda una señal de interrogación a la etiqueta.

- b) La etiqueta utiliza usa la energía de esta señal para funcionar, y su frecuencia como reloj.

- c) La etiqueta lee los datos del lector, en caso de que existan.

- d) El RFID contesta con su propia información.

- e) Un protocolo de autentificación permite gestionar la respuesta simultánea de múltiples etiquetas.

- f) Un protocolo de seguridad permite dar seguridad a la información que se transmite entre el lector y la tarjeta.

- g) La información recibida se integra con el resto de sistemas de información.

2.TECNOLOGÍAS RFID UNIVERSIDAD CARLOS III

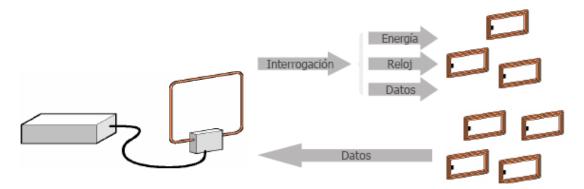

Figura 2 - TECNOLOGIA RFID 2

#### 2.1.2 LA ETIQUETA RFID

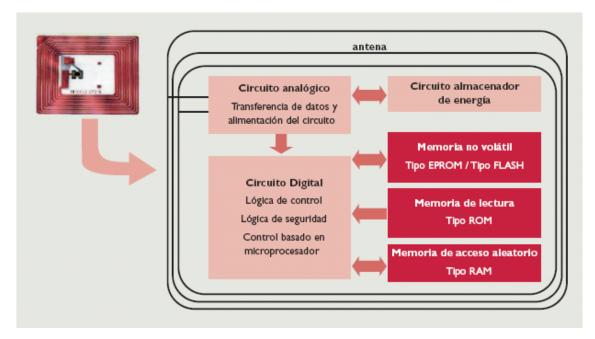

En una etiqueta RFID podemos distinguir tres elementos: la antena, el circuito integrado y el elemento almacenador de energía.

Figura 3 – TECNOLOGIA RFID 3

La antena permite realizar la comunicación entre la etiqueta y el lector. Su tamaño limita la distancia máxima a la que puede realizarse la lectura.

El circuito integrado es un circuito mixto analógico- digital. La parte analógica se encarga de controlar la alimentación y la comunicación por radiofrecuencia. Por otro lado, la parte digital gestiona la información almacenada en la etiqueta.

Por último, es necesario incluir un elemento para alimentar al circuito. En función del elemento usado existen dos tipos de etiquetas: las activas y las pasivas.

En las etiquetas pasivas, el elemento almacenador de energía es un condensador, el cual se carga con la energía emitida por el lector y luego utiliza dicha energía para responder. Por ello, la potencia de emisión está limitada, por lo que la distancia entre el lector y la etiqueta no puede ser muy elevada. La ventaja obvia de este tipo de etiquetas es el ahorro de espacio, la duración prácticamente ilimitada de la etiqueta y su menor coste. Debido a esto, éstas son las etiquetas más usadas, aplicándose en campos tan diversos como la identificación de animales, llaves de contacto de automóviles, identificación de productos en cadenas de montaje, control de accesos, cronometraje de carreras, etc. Obviamente, los componentes mencionados han de protegerse del ambiente exterior, por lo que en función de la aplicación habrá de elegirse el encapsulado adecuado. El más sencillo es el que se ha mostrado en la Figura 2 consistente en una lámina de plástico. No obstante los fabricantes ofrecen innumerables encapsulados, incluso a medida del cliente. Por ejemplo existen etiquetas en formato tarjeta de crédito para control de accesos, encapsuladas en una ampolla de vidrio para identificar animales, etiquetas en forma de clavo para palets, encapsulados resistentes a altas temperaturas para etiquetar equipos que tengan que soportar condiciones adversas, etc.

A diferencia de los tags pasivos, los activos poseen su propia fuente autónoma de energía, que utilizan para dar corriente a sus circuitos integrados y propagar su señal al lector. Estos tags son mucho más fiables (tienen menos errores) que los pasivos debido a su capacidad de establecer sesiones con el reader. Gracias a su fuente de energía son capaces de transmitir señales más potentes que las de los tags pasivos, lo que les lleva a ser más eficientes en entornos dificultosos para la radiofrecuencia como el agua (incluyendo humanos y ganado, formados en su mayoría por agua), metal (contenedores, vehículos). También son efectivos a distancias mayores pudiendo generar respuestas claras a partir de recepciones débiles (lo contrario que los tags pasivos). Por el contrario, suelen ser mayores y más caros, y su vida útil es en general mucho más corta.

Muchos tags activos tienen rangos efectivos de cientos de metros y una vida útil de sus baterías de hasta 10 años. Algunos de ellos integran sensores de registro de temperatura y otras variables que pueden usarse para monitorizar entornos de alimentación o productos farmacéuticos. Otros sensores asociados con ARFID incluyen humedad, vibración, luz, radiación, temperatura y componentes atmosféricos como el etileno. Los tags, además de mucho más rango (500 m), tiene capacidades de almacenamiento mayores y la habilidad de guardar información adicional enviada por el transceptor.

Actualmente, las etiquetas activas más pequeñas tienen un tamaño aproximado de una moneda. Muchas etiquetas activas tienen rangos prácticos de diez metros, y una duración de batería de hasta varios años.

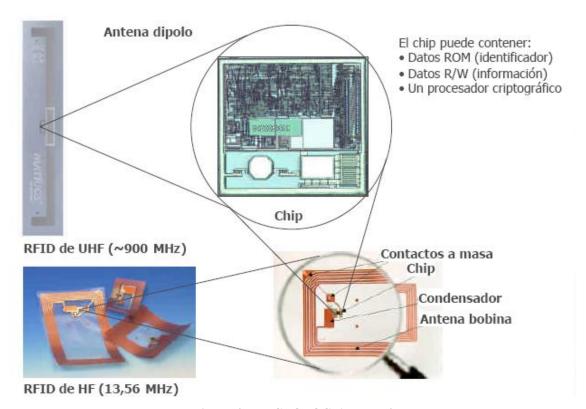

En la siguiente figura se muestra el interior de las etiquetas utilizadas para la tecnología RFID.

Figura 4 - TECNOLOGIA RFID 4

#### 2.1.3 EL LECTOR RFID

La estructura del equipo de lectura es similar a la de las etiquetas: es necesaria una antena para comunicarse con la etiqueta y un circuito para gestionar la comunicación. Este circuito dispone de un interfaz estándar, como por ejemplo RS-232 o CompactFlash, para conectarse a un ordenador o a una PDA. Además existen en el mercado equipos lectores con la antena integrada y equipos que admiten antenas externas, que pueden seleccionarse en función de la aplicación. En este último caso, existen dos tipos de antenas, las antenas tipo "cuadro", similares a las usadas en los grandes almacenes para evitar robos y las antenas con núcleo de ferrita. Las primeras, al tener un mayor tamaño pueden alcanzar distancias de lectura del orden de un metro, aunque con poca direccionabilidad. Las segundas en cambio tienen un tamaño más reducido por lo que su rango se reduce a unos pocos centímetros. Sin embargo su menor tamaño permite su uso en equipos portátiles. Además son más direccionales, por lo que se pueden leer etiquetas que estén próximas entre sí.

#### El software

El último componente en un sistema de identificación por RFID es el sistema de proceso de datos. Las etiquetas sólo de lectura devuelven un código único grabado "a fuego" al fabricar el chip (un tamaño típico es 64 bits.) Las etiquetas de lectura/escritura, que son más caras que las anteriores, permiten leer y/o escribir una longitud mayor de información (valores típicos son 32, 256 o 2048 bits). Por tanto será necesario usar algún sistema de bases de datos que realice la correlación entre la información devuelta por la etiqueta y el resto de información del producto. A modo de conclusión, en la siguiente figura se resume en forma gráfica el sistema completo RFID.

Figura 5 – TECNOLOGIA RFID 5

#### 2.1.4 COLISIONES

Las etiquetas más sencillas necesitan ser leídas de una en una, ya que si se sitúa más de una dentro del rango de alcance de la antena del lector, ambas interferirán entre sí y no podrá realizarse la lectura. Obviamente este tipo de etiquetas son más baratas y para muchas aplicaciones son más que suficientes. Sin embargo, existen aplicaciones en las que puede ser necesario leer varias etiquetas a la vez. Ejemplos de este tipo de aplicaciones son los sistemas de cronometraje, en los que varios corredores pasan simultáneamente por la antena lectora; el etiquetado de equipajes, etc. Para este tipo de aplicaciones se han desarrollado etiquetas anticolisión que permiten la lectura de varias etiquetas situadas en el rango de alcance de la antena. Además la lectura es bastante rápida

#### 2.1.5 FRECUENCIAS EN RFID

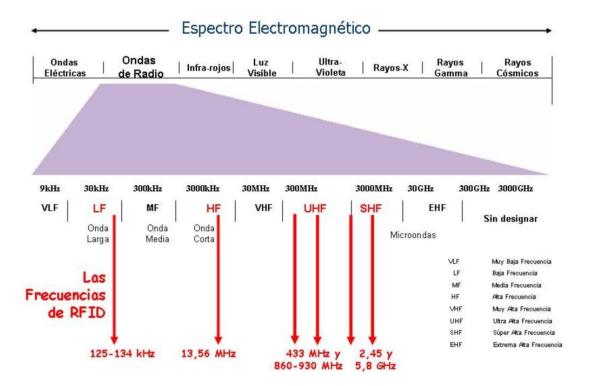

Las frecuencias utilizadas para esta tecnología RFID es la mostrada en la figura siguiente:

Figura 6 – ANCHO DE FRECUENCIA RFID

Los sistemas de comunicaciones están estandarizados por organismos internacionales (UIT, FCC, CCITT, etc.) que regulan su uso y operatividad. Además, estos organismos son también los encargados de repartir el espectro de frecuencia entre todas las aplicaciones que lo necesitan. Para las aplicaciones de RFID, se han asignado tres bandas principales de frecuencias, que se resumen en la Tabla 1, donde se indican además las características típicas de los sistemas que usan dicha banda, así como sus aplicaciones típicas.

| Banda de frecuencia                | Características                                                                                                  | Aplicaciones típicas                                                                                        |

|------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Baja<br>100-500 KHz                | Lectura para corta y media distancia<br>Sistemas con tags económicos<br>Velocidad de lectura baja                | Control de acceso<br>Identificación de animales<br>Control de existencias<br>Inmovilizadores de automóviles |

| Intermedia<br>10-15 MHz            | Lectura para corta y media distancia<br>Potencialmente barato<br>Velocidad de lectura media                      | Control de acceso<br>Tarjetas inteligentes                                                                  |

| Alta<br>850-950 MHz<br>2.4-5,8 GHz | Lectura para corta y media distancia<br>Velocidad de lectura alta<br>Línea de vista requerida<br>Tecnología cara | Supervisión en sistemas ferroviario<br>y automotriz.Acceso y control de<br>peaje                            |

Figura 7 - CARACTERISTICAS FRECUENCIA RFID

En la tabla anterior se han mostrado unos márgenes de frecuencia muy amplios en los que se encuadran los rangos asignados para RFID en cada uno de los países. Así, en función de la zona en la que estemos situados tendremos que usar un rango de frecuencia u otro, lo que implica usar etiquetas distintas. En la Figura 4 se muestran las tres regiones en las que se divide el planeta en función de las regulaciones de radiofrecuencia: Europa y África (Región 1), América (Región 2) y lejano oriente con Australasia (Región 3). Afortunadamente los fabricantes disponen de versiones de cada una de sus etiquetas para las distintas regiones. Por ejemplo las etiquetas Ucode HSL de Philips están disponibles para una banda de 869 MHz (región 1) y para una banda de 900 MHz (región 2)

2.TECNOLOGÍAS RFID

Figura 8 - REGIONES RFID

Otro parámetro importante que varía entre regiones es la máxima potencia de emisión, la cual está directamente relacionada con la distancia máxima de lectura de las etiquetas. Siguiendo el ejemplo anterior, en la región 1, donde para la banda de 869 MHz se admite una potencia máxima de emisión de 0,5 W, la distancia máxima para un tamaño típico de antenas es de 4m. En cambio las mismas etiquetas en la región 2, en donde la potencia máxima permitida es de 4 W, pueden leerse desde 8,4 m.

#### 2.1.6 ÁREAS DE APLICACIÓN PARA RFID

El uso potencial de RFID es prácticamente ilimitado en cada sector de la industria, comercio y servicios donde existen datos que deben ser leídos o comprobados. Las áreas principales de aplicación de RFID son:

- a) Transporte y logística.

- b) Fabricación y procesamiento.

- c) Seguridad de personas.

- d) Identificación y trazabilidad alimentaria animal.

- e) Rastreo postal.

- f) Verificación y control de equipaje.

- g) Control de peaje y medios de pago electrónico.

- h) Sustitución o uso simultáneo y compartido con códigos de barras.

- i) Vigilancia electrónica.

- j) Control de accesos y un largo etc.

2.TECNOLOGÍAS RFID UNIVERSIDAD CARLOS III

Figura 9 – APLICACIÓN RFID

#### 2.1.7 CONCLUSIONES

Hasta ahora se ha realizado una introducción a la tecnología RFID, la cual presenta numerosas ventajas frente a los métodos tradicionales de identificación como el código de barras. Se ha mostrado que su característica fundamental consiste en la utilización de etiquetas "inteligentes" capaces de almacenar mayor cantidad de información de forma segura y perdurable. No obstante, aunque esta tecnología se vislumbra como el futuro en las aplicaciones de identificación, aún necesita superar algunas barreras para que se popularice aún más. Aparte de los problemas de estandarización que se resolverán con el tiempo, el principal escollo es el precio de las etiquetas, que es claramente desfavorable frente al coste cero del código de barras. No obstante, la mayor facilidad de uso hace que el coste total de la aplicación pueda ser menor. Por ejemplo, una aplicación que impactaría en nuestra vida diaria sería el uso de etiquetas RFID para identificar los productos de un supermercado. Con este sistema bastaría con pasar por la antena lectora para que se registrasen todos los productos del carro. El día en que el precio de las etiquetas sea menor que el coste del tiempo empleado en pasar el producto por el lector de código de barras, veremos este tipo de etiquetas cada vez que hagamos la compra.

### 2.2 PROTOCOLO SLAP

Para poder utilizar la tecnología RFID hay que solucionar uno de los problemas que tiene esta tecnología que es la de los ataques de intrusos. Para ello se puede utilizar un protocolo de autentificación que nos sirva para proteger la información que se envía. Uno de los protocolos que podríamos utilizar sería el protocolo SLAP <sup>2</sup>, es un protocolo de autentificación para RFID basado en modular exponentiation (ME).

#### 2.2.2 TABLA DE NOTACION

| Simbolo   | Significado                                            |

|-----------|--------------------------------------------------------|

| Sid       | El ID number de la etiqueta                            |

|           | Numero ID entre la etiqueta y el                       |

| Pid       | lector                                                 |

|           | Numero de exponenciación secreto del lector en cada    |

| Er        | sesion                                                 |

|           | Numero de exponenciación secreto de la tarjeta en cada |

| Et        | sesión                                                 |

| N         | Cambio de valor usado en la etiqueta de anonimato      |

| Kt        | secure ME creado por la etiqueta                       |

| Kr*       | secure ME guardado en el lector                        |

| Kr(i)     | secure ME creado por el lector                         |

| Tt        | Tag-side secure ME                                     |

| Kj        | Llave de seguridad usada en la etiqueta                |

|           | Numero aleatorio de 64 bits creados por el             |

| R         | lector                                                 |

| J         | Contador de 8 bits usados en la etiqueta               |

| I         | Numero de éxito de la sesión                           |

|           | Toda la informacion sobre la                           |

| DATA      | etiqueta                                               |

|           | Numero primo usado en la actualizacion de la           |

| Z         | llave                                                  |

| X         | (sid) XOR ® XOR (Kj)                                   |

| Tr        | Reader-side secure ME                                  |

| r (8 bit) | registro                                               |

Figura 10 - SLAP

<sup>&</sup>lt;sup>2</sup> [8] bibliografía

#### 2.2.3 DISEÑO DEL PROTOCOLO

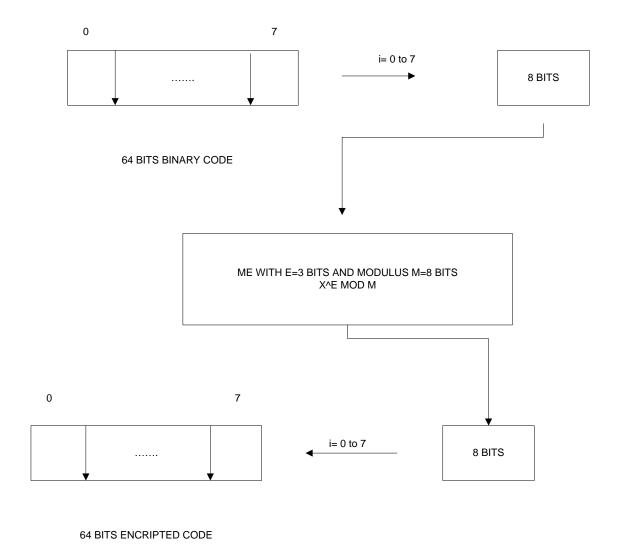

Lo primero que se realizará será la encriptación y desencriptación a través de ME, se recoge el proceso en la siguiente figura:

Figura 11 - SLAP 2

Después M y E deben actualizarse con un numero R aleatorio, además el modulo M debe ser numero primo de ahí que el valor encriptado del ith nunca debe ser igual a 0. El protocolo se puede dividir en 3 partes: identificación de la etiqueta, autentificación mutua y actualización de las llaves de seguridad

#### 1. FASE DE INICIO

Para cada tag, el servidor almacena inicialmente seis valores en la etiqueta: sid, pid, et, Kj,Kt, se obtiene el Tt , después de esta fase se puede pasar a la fase de autentificación mutua.

#### 2. FASE DE AUTENTIFICACIÓN

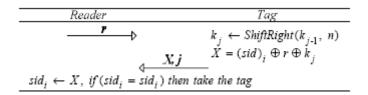

Antes de empezar con la fase de autentificación el lector debe identificar a la etiqueta. El proceso es el siguiente:

- a) El lector envía un numero aleatorio r a la etiqueta

- b) La tarjeta calcula el valor de X usando el valor de r,sid, y Kj, y envía X y j al lector.

- c) El lector recibe X y j, y consigue sid a través de X usando j. El lector compara el sid obtenido con el enviado por la tarjeta y si es igual la tarjeta ha sido identificada.

Figura 12 - SLAP 3

En la fase de autentificación se dan las siguientes fases:

- a) El lector recibe el ME, Kr del DB, y lo envía a la etiqueta.

- b) La tarjeta verifica que el Kr es igual al Kt de la tarjeta, si es igual la tarjeta autoriza al lector.

- c) Entonces la etiqueta genera el Tt, y se lo envía al lector. Además la etiqueta debe ejecutar la llave de actualización del proceso, ya que si no el lector no estará autentificado y la tarjeta permanecerá en silencio.

- d) El lector comparará el Kr con el Kr\*, si son iguales el lector autentificará a la etiqueta consiguiendo el numero de identificación de la etiqueta, TagID, del DB. El lector además debe ejecutar la llave de actualización del proceso, ya que si no se realiza esto la etiqueta permanecerá en silencio.

$$\begin{array}{c|c} Reader & Tag \\ \hline & K_R \\ \hline & & if (K_R^* = K_T^i) \ then \ R \ authenticated \ to \ T \\ \hline K_R^i \leftarrow (T_T^i)^{e_R^i} \ mod \ (pid)_i \leftarrow T_T^i \\ \hline if (K_R^* = K_R^i) \ then \ Authenticated \ T \ to \ R \\ \hline get \ TagID \ from \ DB \\ \hline (sid)_{i+1} \leftarrow (sid)_i \oplus r \oplus T_T^i \\ \hline \epsilon_T^{i+1} \leftarrow \epsilon_T^i \oplus (r_T r_T) \\ \hline \epsilon_T^{i+1} \leftarrow \epsilon_T^i \oplus (r_T r_T) \\ \hline get \ Z \ prime \ number \ then : \\ Z=Z \oplus (r_Sbit) \\ \hline K_R^i \leftarrow (sid)_{i+1}^{e_R^i} \mod (pid)_{i+1} \\ \hline K_R^i \leftarrow (sid)_{i+1}^{e_R^i} \mod (pid)_{i+1} \\ \hline K_R^i \leftarrow (sid)_{i+1}^{e_R^i} \mod (pid)_{i+1} \\ \hline then \ store \ K_R^i \ for \ next \ session \\ \hline \end{array}$$

Figura 13 - SLAP 4

#### 3. ACTUALIZAR LLAVE

La tercera fase que ser realiza en este protocolo sería la de la actualización de la llave. Las fases en las cuales se realiza la actualización son las siguientes:

a) Después de que el lector sea autentificado, la etiqueta debe actualizar dos valores: sid, y et de la siguiente manera:

$$(sid)_{i+1} \leftarrow (sid)_i \oplus r \oplus T_T^i$$

$$e_T^{i+1} \leftarrow e_T^i \oplus (r_{0+i}r_{63-i}r_{31+i})$$

b) Después de que la etiqueta sea autentificado el lector debe actualizar los valores de sid,pis,et,er,n,Kr\* estos valores serán utilizados en la siguiente sesión. Para actualizar el pid el lector selecciona el numero primo Z, que será calculado a través de Z y el XOR del registro r. El lector envía pid, Z, Tr a la etiqueta.

$$\begin{split} Z &\leftarrow Z \oplus (\underset{i \ 7-i \ 15+i}{rr} \underset{23-i \ 31+i}{r} \underset{39-i \ 47+i \ 55-i \ 63-i}{rr}) \\ T_R^{i+1} &\leftarrow (sid)_{i+1}^{e_R^{i+1}} \bmod (pid)_{i+1} \\ K_R^* &\leftarrow (sid_R^{i+1})^{(e_R^{i+1})*(e_T^{i+1})} \bmod (pid)_{i+1} \end{split}$$

- c) El Kr\* es el valor encriptado del lector y este lo reemplaza con valor antiguo de la sesión i, en el database. Este valor será usado como llave de autentificación en la próxima sesión.

- d) Después de recibir Z,pid y Tr, la etiqueta chequea el pid para determinar si los valores recibidos son correctos. Z es un numero primo que ha sido calculado al

hacer la XOR de Z con los 8 bits del numero r, por tanto para obtener Z habría que hacer la misma XOR con los 8 bit del numero r para obtener Z. Después de obtener Tr del lector, la etiqueta realiza la ecuación =>

e) El valor de Kt(i) será reemplazado en la EEPROM, el valor Kt(i+1) es el valor encriptado de la etiqueta que usará para autentificar al lector en la siguiente sesión.

#### 2.2.4 ANALISIS DE SEGURIDAD.

El protocolo debe ser seguro, y debe asegurar la seguridad del anonimato de la etiqueta como la prevención de la escucha.

- a) <u>Seguridad del ME</u>: En esta propuesta se encripta el código con una llave privada et,er y modulo pid usando byte a byte, por tanto este protocolo se puede considerar seguro.

- b) Ataques a la etiqueta de identificación: El sid es una llave compartida usada como llave de identificación de la etiqueta. Un intruso podría escuchar la comunicación entre la etiqueta y el lector. Pero X es un valor aleatorio y j no tendría sentido para el intruso, por tanto el intruso no podría identificar la etiqueta. El Kj y sid son llaves compartidas y X es un valor que se calcula a través de estos dos, el intruso no podría distinguir entre sid y X. Ademas después de cada sesión tanto el sid, Kj como el valor de n son actualizados. De este modo el intruso no podría rastrear la etiqueta en este momento.

- c) <u>Ataques a la mutua autentificación</u>: Kr\* será usado para autentificar el lector a la etiqueta y del mismo modo Tt será usado al revés. A través de la SE ME encriptará estos valores a través de sus llaves privadas er, et y pid. Esos dos valores serian como un numero aleatorio para el intruso, ya que no podría distinguir pid, del las llaves privadas er y et. Después de cada autentificación et, er y pid deben ser actualizados, para que Kr\* t Tr sean numero aleatorios y sin sentidos para el intruso.

- d) <u>Ataques a la actualización de llaves</u>: Z es un numero aleatorio, Tr(i+1) es una llave de seguridad del lector. El lector calcula el Tr(i+1) después de actulizar er y pid, por ello el intruso no puede identificar a la etiqueta. Además el intruso podría intentar atacar a la actualización de la información secreta de la tarjeta. Sin embargo, las llaves de seguridad serán actulizadas después de que el lector autentifique a la tarjeta y el intruso no puede saber el valor del pid, porque no

conoce el bit elegido para el proceso del pid. A pesar de que el intruso no conoce el pid este valor no sería útil en la siguiente sesión. Por tanto el intruso no puede realizar el ataque con éxito.

#### 2.2.5 CONCLUSION

Este protocolo se podría usar para la encriptación de la tecnología RFID, utiliza la exponenciación modular.. Como se observara en este método se utiliza la multiplicación modular para poder realizar las distintas operaciones, existe multitud de algoritmos para poder realizar la multiplicación modular los cuales estudiaremos y compararemos algunos de ellos a continuación. Además se observa como en este protocolo necesita de un generador de números aleatorios de ahí que en este proyecto también implementemos un generador de números aleatorios para poder utilizarlo en el protocolo.

#### 2.3 MULTIPLICACIÓN MODULAR

#### 2.3.2 INTRODUCCIÓN MULTIPLICACIÓN MODULAR

Los esquemas criptográficos modernos se valen de operaciones aritméticas de complejidad apreciable. Tradicionalmente estas operaciones se han implementado en software. Sin embargo, dado el crecimiento continuo de las capacidades de los sistemas de cómputo en los últimos años, ha sido necesario reajustar gradualmente la complejidad de las operaciones para cumplir con los requerimientos de seguridad específicos de cada aplicación. Normalmente estos ajustes hechos en las operaciones criptográficas implican el manejo de operandos de mayor longitud, lo que obviamente desmejora los tiempos de ejecución. Como consecuencia de esto, existe el interés de implementar estos operadores en hardware, de modo que los ajustes a los operadores se puedan hacer cumpliendo simultáneamente con tiempos de ejecución razonables.

La Multiplicación Modular <sup>3</sup> tiene tres operandos de entrada: A, B y M. Cada uno de estos operandos corresponde a un entero sin signo representado como un número binario de una longitud dada.

Para tres números enteros A, B y M, se define la multiplicación modular como:  $P \equiv A \cdot B \mod M$ , tal que:  $A \cdot B = M \cdot k + P$ , siendo k cualquier número entero.

Figura 14 - MODULAR MULTIPLICATION

Para la multiplicación modular pueden existir varios métodos. Entre los más importantes se encuentra los métodos Karatsuba-ofman y Booth como algoritmos de multiplicación, para obtener el modulo con estos métodos habrá que realizar un segundo método a ambos como puede ser el de Barret, y los métodos de Montgomery y Brickell como métodos en los que se utiliza la multiplicación y la reducción en el mismo método. Estos métodos se explican a continuación.

<sup>&</sup>lt;sup>3</sup> [4] bibliografía

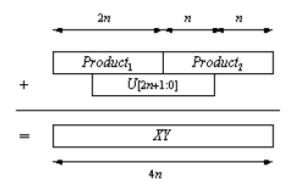

#### 2.2.3 METODO DE KARATSUBA-OFMAN

El algoritmo de Karatsuba-Ofman <sup>4</sup> está considerado como uno de los algoritmos más rápidos a la hora de multiplicar enteros de gran tamaño. En este algoritmo se realizará: una multiplicación de 2-n dígitos que se reducirá en 2 multiplicaciones de n dígitos, una multiplicación de (n+1) dígitos, 2 restas de n-dígitos, 2 operaciones de desplazamiento a izquierda, 2 sumas de n-dígitos y 2 sumas de 2n-digitos.

En cuanto al desarrollo del algoritmo es el siguiente:

$$X = XH 2n + XL$$

$$Y = YH 2n + YL$$

P=X\*Y se calcula de la siguiente manera:

$$P = XY = (X_H 2^n + X_L)(Y_H 2^n + Y_L) = 2^{2n}(X_H Y_H) + 2^n(X_H Y_L + X_L Y_H) + X_L Y_L$$

Usando esta ecuación se necesitan 4 multiplicaciones de N bits para calcular el producto P.

Desarrollando la ecuación anterior el cálculo de P se puede mejorar de la siguiente manera:

$$X_H Y_L + X_L Y_H = (X_H + X_L)(Y_H + Y_L) - X_H Y_H - X_L Y_L$$

En el algoritmo de Karatsuba-Ofman's observando la ecuación de arriba la multiplicación de 2-n bits se pueden reducir en 3 multiplicaciones de n-bits,  $X_H Y_H$ ,  $X_L Y_L$  and  $(X_H + X_L)(Y_H + Y_L)$ . The Karatsuba-Ofman's puede ser expresado como en el siguiente algoritmo, donde la function Size (x) devuelve el numero de bits de X, la function High(X) devuelve la parte alta de X y Low(X) devuelve la parte baja de X.

<sup>&</sup>lt;sup>4</sup> [9] [10] bibliografía

Además la función RightShift(X) devuelve  $X2^n$  y *OneBitMultiplication* (X, Y) devuelve XY donde X e Y serán calculados por un bit.

Figura 15 - MODULAR MULTIPLICATION 2

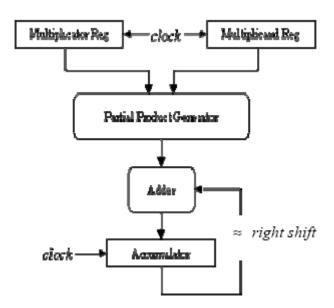

#### 2.3.4 MULTIPLICACIÓN DE BOOTH

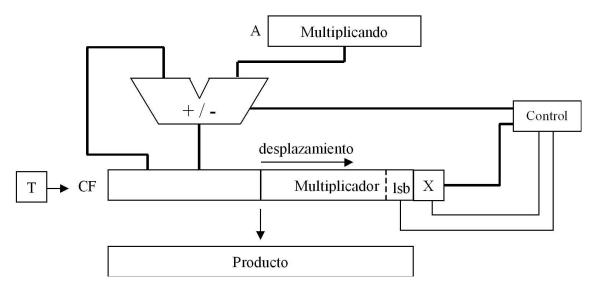

En este algoritmo <sup>5</sup> la multiplicación normalmente se genera en 2 pasos: el primero genera un producto parcial y el segundo que en el cual se va acumulando los productos parciales. Lo más básico en el algoritmo de multiplicación se basa en el método de addand-shift: la operación de desplazamiento genera el producto parcial mientras que el sumador los suma todos ellos.

Figura 16 - MODULAR MULTIPLICATION 3

I.T.I ELECTRONICA Página 33

\_

<sup>&</sup>lt;sup>5</sup> [4] [9] <u>bibliografía</u>

Figura 17 - MODULAR MULTIPLICATION 4

La manera de implementar un multiplicador es la basada en un método iterativo del adder-accumulator para generar los productos parciales mostrados en la siguiente figura. Sin embargo esta solución es bastante lenta ya que el resultado final solo se daría cuando pasasen n ciclos de reloj( siendo n el tamaño de los elementos)

Figura 18 - MODULAR MULTIPLICATION 5

Para una versión más rápida del multiplicador iterativo se tendría que añadir varios productos parciales al mismo tiempo. Esto se podría hacer con un circuito

combinacional el cual consista en varios productos parciales con sumadores que operan en paralelo.

Figura 19 - MODULAR MULTIPLICATION 6

El diagrama de bloques de este algoritmo sería el siguiente:

Figura 20 - MODULAR MULTIPLICATION 7

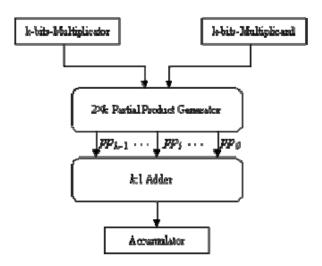

El algoritmo de Booth será el siguiente:

Tomamos X e Y como números enteros, y tomamos n y m como el tamaño de los operandos respectivamente.

Siguiendo el método add-and-shift se genera el cada producto: Xi\*Y, 0 <= i < n. Cada producto parcial es desplazado a la izquierda o derecha dependiendo de si el bit por el que empieza es el mas o menos significativo.

El numero de productos parciales dependerá de tamaño de los operandos, en criptografía los tamaños de los operandos suele ser bastante grande.

```

Algorithm Booth (x_{2\times i-1}, x_{2\times i}, x_{2\times i+1}, Y)

Int product := 0;

Int pp[\lceil (n+1)/2 \rceil -1 \rceil;

pp[0] := (\widetilde{x}_0 \times Y + 4 \times 2^{n+1}) \times 2^{2\times i};

For i = 0 To \lceil (n+1)/2 \rceil -1 Do

pp[i] := (\widetilde{x}_i \times Y + 3 \times 2^{n+1}) \times 2^{2\times i};

product := product + pp[i];

Return product mod 2^{n+\lceil (n+1)\rceil -1};

End Booth

```

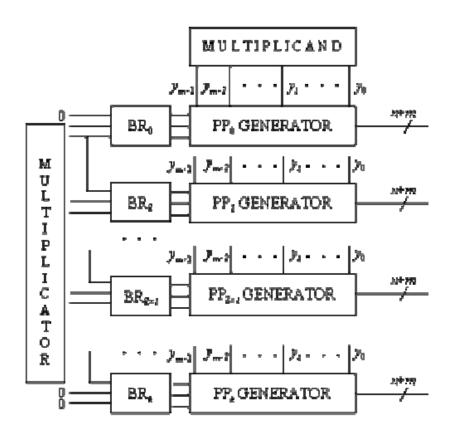

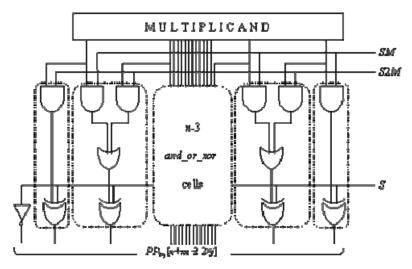

La arquitectura del generador de los productos parciales y su implementación es la siguiente:

Figura 21 - MODULAR MULTIPLICATION 8

Arquitectura de los generadores de productos parciales

Figura 22 - MODULAR MULTIPLICATION 9

Implementación de los generadores de los productos parciales

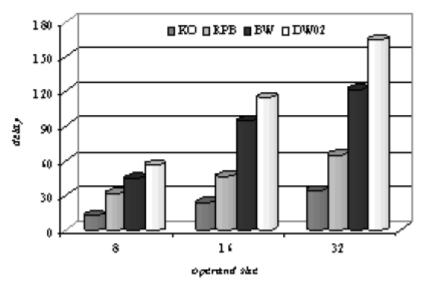

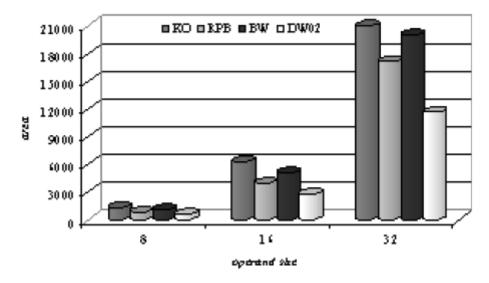

# 2.3.5 COMPARACIÓN BOOTH - KARATSUBA

A continuación se muestra una tabla y gráficos con resultados en cuanto al retraso del tiempo y área que necesita cada multiplicador. La K0 es del algoritmo de Karatsuba-ofman, las demás pertenecen al algoritmo de Booth con diferentes implementaciones de hardware.

Figura 23 – RETRASO KARAT\_BOOTH

# TIEMPO REQUERIDO

| size | КО    |       | BW    |       |

|------|-------|-------|-------|-------|

|      | delay | area  | delay | area  |

| 8    | 12.6  | 1297  | 44.6  | 1092  |

| 16   | 22.8  | 6300  | 93.9  | 5093  |

| 32   | 29.1  | 31740 | 121.5 | 20097 |

**RETRASOS Y AREAS**

El retraso se mide en nanosegundos, mientras que el área se mide en CLBs.

Figura 24 – AREA KARAT\_BOOTH

Figura 25 – AREA X TIEMPO KARAT\_BOOTH

En resumen se puede considerar observando los resultados que para grandes operandos es mas adecuado el algoritmo de Karatsuba-Ofman, mientras que para operandos pequeños que no excedan de 256 bits sería más convenientes utilizar el método de Booth

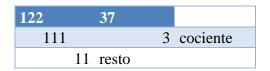

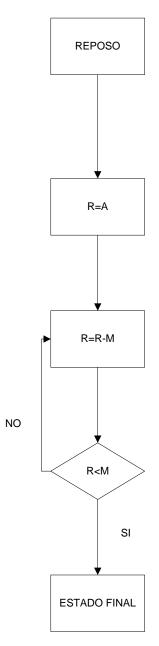

# 2.3.6 METODOS DE REDUCCIÓN DE BARRET

Una vez que se obtiene la multiplicación para la multiplicación modular se necesita una reducción, esto es lo que realiza el método de Barret. Una reducción es simplemente el cálculo del resto de una división.

$$X \bmod M = X - \left\lfloor \frac{X}{M} \right\rfloor \times M$$

Sin embargo una división es mucho más complicada que una multiplicación. Un algoritmo para división es el de NaiveReduction, el cual se muestra a continuación.

```

Algorithm NaiveReduction(P, M)

Int R := P;

Do R := R - M;

While R > 0;

If R ≠ 0 Then R := R + M;

Return R;

End NaiveReduction

```

Este algoritmo es muy ineficiente ya que requiere 2n-1 restas, 2n comparaciones y una suma extra.

Otra alternativa a este algoritmo puede ser el siguiente:

```

Algorithm RestoringReduction(P, M)

Int R<sub>0</sub> := P;

Int N := LeftShift(M, n);

For i = 1 To n Do

R<sub>i</sub> := R<sub>i-1</sub> - N;

If R < 0 Then R<sub>i</sub> := R<sub>i-1</sub>;

N := RightShift(N);

Return R<sub>i</sub>;

End RestoringReduction

```

Trata de restar el valor más grande de 2 múltiplos de M al resto actual. Cada vez que el resultado de esta operación da negativo se restaura el resto anterior y se repite el cálculo con todos los posibles valores de 2 múltiplos de M: 2nM, 2n-1M, ..., 2M, M. Para este algoritmo se requiere n restas, r comparaciones y algunas 2n desplazamientos así como algunas operaciones de restablecimiento. Esto es mucho más eficiente que el algoritmo de Naive

Una alternativa al RestoringReduction es NonRestoringReduction :

```

Algorithm NonRestoringReduction(P, M)

Int R<sub>0</sub> := P;

Int N := LeftShift(M, n);

For i = 1 To n Do

If R > 0 Then R<sub>i</sub> := R<sub>i-1</sub> - N;

Else R<sub>i</sub> := R<sub>i-1</sub> + N;

N := RightShift(N);

If R<sub>i</sub> < 0 Then R<sub>i</sub> := R<sub>i-1</sub> + N;

Return R<sub>i</sub>;

End RestoringReduction

```

Este algoritmo permite el resto negativo. Cuando el resto es no negativo se suma a la potencias de dos múltiplos de M. De lo contrario el múltiplo de M los resta. Mantiene hacerlo en repetidas ocasiones para todos los posibles potencias de 2 múltiplos de M: 2nM, 2n-1M, ..., 2M, M.

Usando el método de Barret's <sup>6</sup> podemos calcular el resto usando 2 simples multiplicaciones. El cálculo aproximado seria:

$$\left\lfloor \frac{X}{M} \right\rfloor = \left\lfloor \frac{\left\lfloor \frac{X}{2^{n-1}} \right\rfloor \times \left\lfloor \frac{2^{n-1} \times 2^{n+1}}{M} \right\rfloor}{2^{n+1}} \right\rfloor = \left\lfloor \frac{\left\lfloor \frac{X}{2^{n-1}} \right\rfloor \times \left\lfloor \frac{2^{2\times n}}{M} \right\rfloor}{2^{n+1}} \right\rfloor$$

Figura 26 – RESTO BARRET

Con Esta ecuación se puede calcular de forma muy eficiente para divisiones de potencia de 2, para este último método en el caso en el que las divisiones no sean exactas el resultado final sería una aproximación. Para solucionar esto se podría representar los números a través de representaciones en las cuales se pueda obtener decimales como es el caso de coma flotante o punto fijo.

<sup>&</sup>lt;sup>6</sup> [4] bibliografía

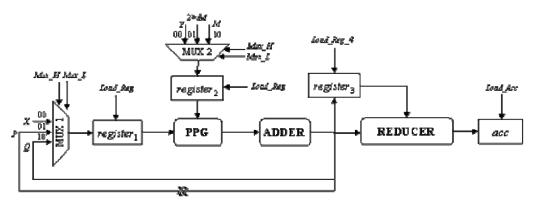

## 2.3.7 MÉTODO BOOTH - BARRET

Se calcula la multiplicación modular en 3 pasos: X\*Y mod M

- a) Calcular el producto P=X\*Y

- b) Calculo de la estimación del cociente: Q=P/M $Q=P/2^{n-1}x[2^{2xn}/M]$

- c) Calcular el resultado final

Durante el primer paso, primero se carga en el registro 1 y registro 2 los valores de X e Y. Después espera para que PPG obtenga los productos parciales y finalmente espera que el sumador sume todos los productos. Durante el paso 2, se carga en los registros1,2 y 3 con los valores obtenidos del producto P, el pre-calculado constante  $2^{2xn}$  /M y P respectivamente., entonces espera a que PPG calcule los productos parciales y finalmente los suma todos ellos. Durante el tercer paso, primero se carga en los registro 1 y 2, con los valores Q y modulo M respectivamente, entonces espera a que el PPG genere los productos parciales y finalmente espera a que el sumador sume todos ellos. Y finalmente espera para que el reductor calcule el resultado final del resultado P-QxM, el cual es cargado en el acumulador acc.

Figure 22: The modular multiplier architecture

Figura 27 - ARQUITECTURA M.MODULAR

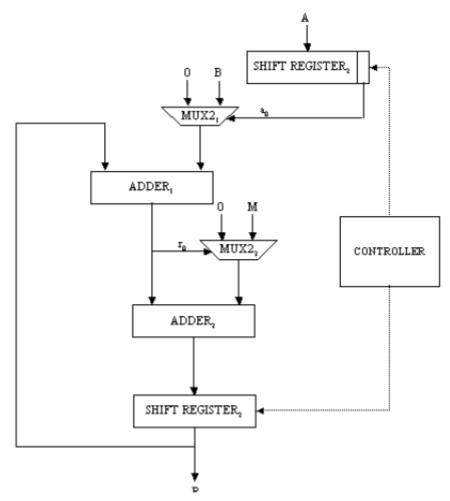

### 2.3.8 ALGORITMO DE MONTGOMERY

Este algoritmo de multiplicación modular se basa principalmente en 2 pasos: el primero en el que se calcula el producto P=AxB y el segundo el cual se realiza la reducción de P mod M.

Para este algoritmo se toma A,B como dos enteros cualquiera y M que será el modulo, siendo n el numero de bits de los operandos. Se define A,B y M de la siguiente manera:

$$A = \sum_{i=0}^{n-1} a_i \times 2^i$$

,  $B = \sum_{i=0}^{n-1} b_i \times 2^i$  and  $M = \sum_{i=0}^{n-1} m_i \times 2^i$

Las condiciones del método de Montgomery <sup>7</sup> son las siguientes:

- a) M necesita ser número primo.

- b) El multiplicando y el multiplicador necesitan ser más pequeños que M.

- c) Como se usa la representación binaria en los operandos, el modulo M necesita ser impar para satisfacer la primera condición.

El algoritmo utilizado para la multiplicación será el siguiente:

```

algorithm Montgomery(A, B, M)

int R = 0;

1: for i= 0 to n-1

2:   R = R + a<sub>1</sub>×B;

3:   if r<sub>0</sub> = 0 then

4:   R = R div 2

5:   else

6:   R = (R + M) div 2;

return R;

end Montgomery.

```

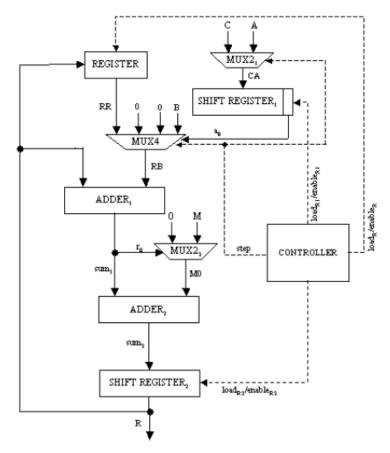

En la arquitectura utilizada se usan 2 multiplexores, 2 sumadores, 2 registros de desplazamiento, 3 registros y un controlador, en la siguiente figura se muestra esta arquitectura:

<sup>&</sup>lt;sup>7</sup> [5] [6] [11] bibliografía

Figura 28 - ARQUITECTURA MONTG 1

La función del controlador consiste en la sincronización de los desplazamientos y cargar las operaciones en los registros de desplazamiento 1 y 2. El controlador usa simplemente un contador descendente. El controlador estará compuesto de la siguiente manera:

Figura 29 - CONTROLADOR MONTGOMERY

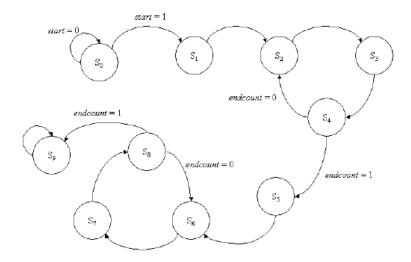

Este controlador es una máquina de estados, los cuales son 6 y son:

a) S0: inicializa la máquina de estados.Go to S1

b) S1: Carga el multiplicando y modulo en sus registros

Carga el multiplicador en el registro de desplazamiento 1

Go to S2

c) Espera al sumador1

Espera al sumador2

Carga el multiplicador dentro del registro de desplazamiento2

Incrementa el contador

Go to S3

d) Enable al registro de desplazamiento2

Enable al registro de desplazamiento1

Go to S4

e) Verifica el contador Si es 0 va al S5 sino al S2

f) Detener

Viendo el algoritmo de Montgomery se observa que se necesita una multiplicación modular extra de Montgomery para calcular  $2^n$  mod M, pero debido a que el objetivo de este algoritmo es el cálculo de la exponenciación, es preferible multiplicar antes los operandos de Montgomery por  $2^{2n}$  y después del algoritmo multiplicar el resultado por  $2^{-n}$ . Se necesita una multiplicación extra de Montgomery para obtener la constante  $r^{2n}$  mod M. El algoritmo utilizado es el siguiente:

```

algorithm ModularMult(A, B, M, n)

const C := 2<sup>n</sup> mod M;

int R := 0;

R := Montgomery(A, B, M);

return Montgomery(R, C, M);

end ModularMult.

```

# La arquitectura es:

Figura 30 - ARQUITECTURA MONTG 2

La máquina de estados se compone de 10 estados:

Figura 31 - ESTADOS MONTGOMERY

a) S0: Inicializa la máquina de estados

Go to S1

b) S1: Carga el multiplicando y modulo, carga el multiplicador dentro del registro1

Go to S2

c) S2: Espera al sumador1; espera al sumador2

Carga el resultado parcial en el registro 2

Incrementa el contador

Go to S4

d) S3: Enable al registro de desplazamiento2

Enable al registro de desplazamiento1

Go to S4

e) S4: Carga el resultado parcial del paso 0 en el registro

Actualiza el contador

Si es 0 go to S3 sino al S2

f) S5: Carga constante en el registro1

Resetea el registro

Set step to 1, Go to S6

g) S6: Espera al sumador1; espera al sumador2

Carga el resultado parcial en el registro2

Incrementa el contador, Go to S7

h) S7: Enable registro de desplazamiento2

Enable al registro de desplazamiento 1; go to S8

i) S8: Actualiza el contador

Si es 0 go to S9, sino vuelve al S6

j) Detener

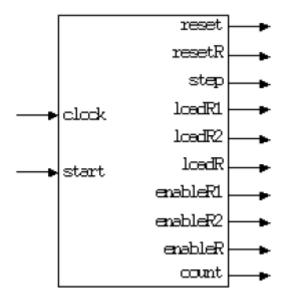

El interface del controlador sería el siguiente:

Figura 32 - CONTROLADOR MONTG 2

A continuación se muestra las simulaciones realizadas en la FPGA para los algoritmos 1 y 2.

# Montgomery (15,26,47)=34

Figura 33 - SIMULACION MONTG 1

Montgomery (7,34,47)=14

Figura 34 - SIMULACION MONTG 2

### 2.3.9 ALGORITMO SISTOLIC-MONTGOMERY

Existe una modificación en el algoritmo de Montgomery que sería una alternativa al método iterativo, el cual sería la systolic Montgomery. El algoritmo es el siguiente:

```

algorithm ModifiedMontgomery(A, B, M)

int R := 0;

1: for i := 0 to n-1

2: q_1 := (r_0 + a_1 \times b_0) \mod 2;

3: R := (R + a_1 \times B + q_1 \times M) \text{ div } 2;

return R;

end ModifiedMontgomery.

```

A través de este algoritmo se puede generar el algoritmo systolic de Montgomery :

```

algorithm SystolicMontgomery(A,B,M,MB)

int R := 0;

bit carry := 0, x;

0: for i:=0 to n

q_i := r_0^{(1)} \oplus a_i.b_o;

1:

for j := 0 to n

2:

3:

switch ai, qi

4:

1,1: x := mb_1;

1,0: x := b_i;

5:

0,1: x := m_i;

6:

0,0: x := 0;

7:

r_{j}^{(\text{i+1})} \ := \ r_{j+1}^{(\text{i})} \ \oplus \ x_{i} \ \oplus \ \text{carry};

\texttt{carry:=}\,r_{j+1}^{(1)}\,\,.\,x_{i}\!+\!\,r_{j+1}^{(1)}\,\,.\,\texttt{carry+}x_{i}\,.\,\texttt{carry};

return R;

end SystolicMontgomery.

```

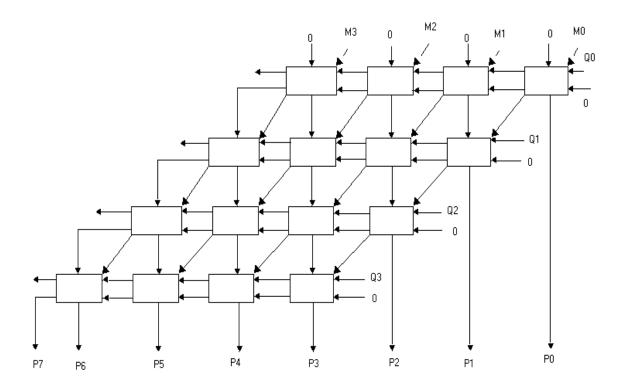

La arquitectura que da lugar a este algoritmo es el siguiente:

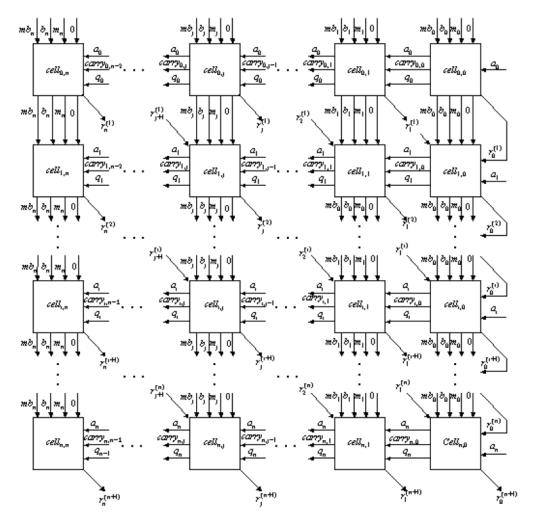

Figura 35 - ARQUITECTURA SISTOLIC

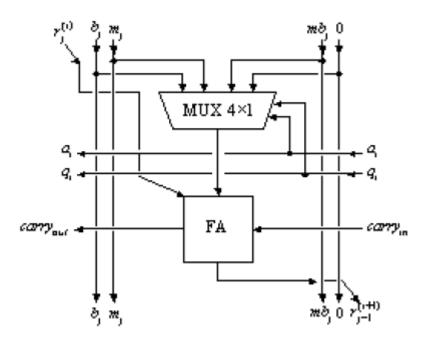

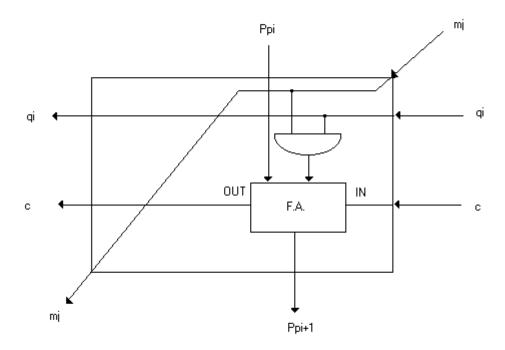

Cada celda se denomina como PE (procesing element) en los cuales se ejecuta la línea 8 del algoritmo.

Cada celda está compuesta como se muestra en la siguiente figura, que es la arquitectura básica de cada PE

Figura 36 - CELDA PE

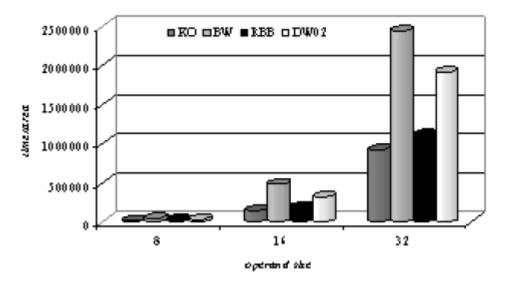

# 2.3.10 COMPARACIÓN SISTOLIC - ITERATIVO

En cuanto tiempo necesario y área requerida para cada método a continuación se muestra una tabla con los resultados obtenidos en una FPGA, en función del número de bits. IM (método iterativo), SM (systolic método)

| operand |     | rea<br>LBs) | clock<br>time |     | area×  | time  |

|---------|-----|-------------|---------------|-----|--------|-------|

| size    | IM  | SM          | IM            | SM  | IM     | SM    |

| 128     | 89  | 259         | 46            | 23  | 4094   | 5957  |

| 256     | 124 | 304         | 102           | 42  | 12648  | 12767 |

| 512     | 209 | 492         | 199           | 76  | 41591  | 37392 |

| 768     | 335 | 578         | 207           | 82  | 69345  | 47396 |

| 1024    | 441 | 639         | 324           | 134 | 142884 | 85626 |

Figura 37 - GRAFICA 4

Como se puede observar en el gráfico a medida que el tamaño de los operandos es mayor sería mejor utilizar el método systolic que el iterativo. Por tanto y apoyándonos en los resultados en el caso de tener un tamaño de los operandos hasta 512 bits sería mejor utilizar el método iterativo que el factor tiempos x area sería más ventajoso, por el contrario si tuviéramos un tamaño de los operandos de mas de 1024 bits el mejor método a utilizar sería el de systolic. Teniendo en cuenta en los procesos criptográficos el tamaño de los operandos es bastante grande (mayor de 512 bits) en esta ocasión para poder sacar el mayor rendimiento al circuito se implementaría el método de systolic.

#### **2.3.11 RESUMEN**

En este apartado se han explicado varios métodos para el cálculo de multiplicación modular.

En un primer caso se ha desarrollado los métodos en los cuales se hace una multiplicación primero (Karatsuba-offman y el de Booth) y luego se ha hecho el modulo de esa multiplicación a través del método de Barret. En contraste con este método se ha descrito un algoritmo en el cual se hacía tanto la multiplicación como el módulo dentro del mismo método como es el algoritmo de Monrgomery. Este método en comparación con los del primer caso es más utilizado y además se puede observar en las simulaciones que para operandos de gran tamaño el factor tiempo x área es mejor que en los anteriores métodos. Estos algoritmos y resultados han sido obtenidos de varios documentos en los que la síntesis y la simulación se ha realizado sobre una fpga concreta, en los siguientes apartados lo que se va a realizar la implementación de estos algoritmos y además de estos otros algoritmos de modo que todos los podamos comparar en una misma fpga y de esta forma los resultados que obtengamos se pueda realizar una conclusión de cuál es la implementación más favorable.

# IMPLEMENTACIÓN VHDL

# [LENGUAJE VHDL]

INTRODUCCIÓN - IMPLEMENTACIÓN - PROGRAMAS UTILIZADOS - TEST BENCHZ

### 2.4 LENGUAJE VHDL

### 2.4.2 INTRODUCCIÓN VHDL

Durante el proyecto para la realización de las diferentes implementaciones se ha realizado a través del lenguaje vhdl.

A mediados de los años setenta se produce una fuerte evolución en los procesos de fabricación de los circuitos integrados, y junto a las tecnologías bipolares, surge la MOS (metal oxide semiconductor), principalmente la NMOS, promoviendo el desarrollo de circuitos digitales hasta la primera mitad de los años ochenta. En aquellas épocas, el esfuerzo de diseño se concentraba en los niveles eléctricos para establecer características e interconexiones entre los componentes básicos a nivel de transistor. El proceso de diseño era altamente manual y tan solo se empleaban herramientas como el PSPICE para simular esquemas eléctricos con modelos previamente personalizados a las distintas tecnologías. A medida que pasaban los años, los procesos tecnológicos se hacían más y más complejos. Los problemas de integración iban en aumento y los diseños eran cada vez más difíciles de depurar y de dar mantenimiento. Inicialmente los circuitos MSI (Medium Scale Integration ) y LSI (Low Scale Integration ) se diseñaron mediante la realización de prototipos basados en módulos más sencillos. Cada uno de estos módulos estaba formado por puertas ya probadas, este método poco a poco, iba quedándose obsoleto. En ese momento (finales de los años setenta) se constata el enorme desfase que existe entre tecnología y diseño. La considerable complejidad de los chips que se pueden fabricar, implica unos riesgos y costes de diseño desmesurados e imposibles de asumir por las empresas. Es entonces, cuando diversos grupos de investigadores empiezan a crear y desarrollar los llamados "lenguajes de descripción de hardware" cada uno con sus peculiaridades. Empresas tales como IBM con su IDL, el TI - HDL de Texas Instruments, ZEUS de General Electric, etc., así como los primeros prototipos empleados en las universidades, empezaron a desarrollarse buscando una solución a los problemas que presentaba el diseño de los sistemas complejos. Sin embargo, estos lenguajes nunca alcanzaron el nivel de difusión y consolidación necesarias por motivos distintos. Unos, los industriales, por ser propiedad de la empresa permanecieron encerrados en ellas y no estuvieron disponibles para su estandarización y mayor difusión, los otros, los universitarios, perecieron por no disponer de soporte ni mantenimiento adecuado. Alrededor de 1981 el Departamento de Defensa de los Estados Unidos desarrolla un proyecto llamado VHSIC (Very High Speed Integrated

Circuit ) su objetivo era rentabilizar las inversiones en hardware haciendo más sencillo su mantenimiento. Se pretendía con ello resolver el problema de modificar el hardware diseñado en un proyecto para utilizarlo en otro, lo que no era posible hasta entonces porque no existía una herramienta adecuada que armonizase y normalizase dicha tarea, era el momento de los HDL's

En 1983, IBM, Intermetrics y Texas Instruments empezaron a trabajar en el desarrollo de un lenguaje de diseño que permitiera la estandarización, facilitando con ello, el mantenimiento de los diseños y la depuración de los algoritmos, para ello el IEEE propuso su estándar en 1984. Tras varias versiones llevadas a cabo con la colaboración de la industria y de las universidades, que constituyeron a posteriori etapas intermedias en el desarrollo del lenguaje, el IEEE publicó en diciembre de 1987 el estándar IEEE std 1076-1987 que constituyó el punto firme de partida de lo que después de cinco años sería ratificado como VHDL. Esta doble influencia, tanto de la empresa como de la universidad, hizo que el estándar asumido fuera un compromiso intermedio entre los lenguajes que ya habían desarrollado previamente los fabricantes, de manera que éste quedó como ensamblado y por consiguiente un tanto limitado en su facilidad de utilización haciendo dificultosa su total comprensión. Este hecho se ha visto incluso ahondado en su revisión de 1993. Pero esta deficiencia se ve altamente recompensada por la disponibilidad pública, y la seguridad que le otorga el verse revisada y sometida a mantenimiento por el IEEE. La independencia en la metodología de diseño, su capacidad descriptiva en múltiples dominios y niveles de abstracción, su versatilidad para la descripción de sistemas complejos, su posibilidad de reutilización y en definitiva la independencia de que goza con respecto de los fabricantes, han hecho que VHDL se convierta con el paso del tiempo en el lenguaje de descripción de hardware por excelencia.

### 2.4.3 PROGRAMAS UTILIZADOS

Los programas los cuales se ha usado en el proyecto para la realización del mismo son: ModelSim e ISE. El primero nos ha servido para la implementación del código vhdl y su posterior simulación. El segundo lo hemos utilizado para realizar la síntesis de los diferentes circuitos implementados y de esa manera poder comparar los diferentes algoritmos tanto en tiempo requerido como en área utilizada. Se ha elegido una FPGA para la síntesis del circuito SPARTAN 3 (XC3S50), se ha elegido esta FPGA debido a que es una de las cuales no son grandes pero tiene el suficiente tamaño para comparar de una manera clara los diferentes circuitos. Para la síntesis se ha eliminado la opción de bloque multiplicador el cual incorpora la FPGA, de este modo podremos comparar las diferentes implementaciones en puertas lógicas las cuales denominaremos LUT.

Una vez hecha la síntesis y la comprobación de que carece de errores se ha procedido a la post-síntesis, la cual nos va a permitir simular el circuito a través del ModelSim una vez sintetizado para comprobar que el circuito se comporta correctamente.

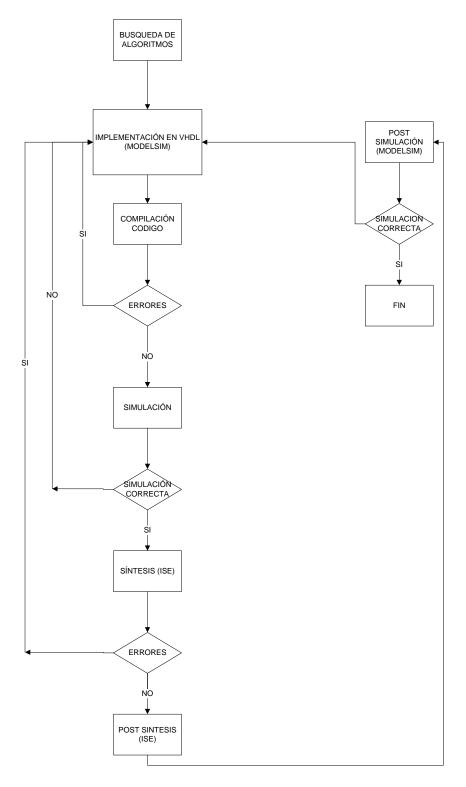

La realización del trabajo en el proyecto es el siguiente:

Figura 38 - D.ESTADOS PROYECTO

### **2.4.4 TEST-BENCH**

Para la realización de la simulación de los diferentes códigos se he realizado un código estándar para todos en el cual se estimulan las señales de entrada con ciertos valores. Las señales las cuales se estimulan a través del test-bench son las señales de reloj, reset, inicio, y de las entradas A,B y M (este último en caso de que tenga esta entrada). El código se muestra a continuación, para probar diferentes implementaciones lo único que se ha hecho es cambiar el componente a instanciar.

### Codigo=>

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity test_CARD IS

end test_CARD;

architecture test_CARD_a of test_CARD IS

COMPONENT mont_CARD

GENERIC(N:INTEGER:=4);

PORT(

A,B: IN STD_LOGIC_VECTOR(N-1 DOWNTO 0);

M: IN STD_LOGIC_VECTOR(N-1 DOWNTO 0);

S: OUT STD_LOGIC_VECTOR(N-1 DOWNTO 0);

INICIO: IN STD_LOGIC;

FIN: OUT STD_LOGIC;

CLK,RESET: IN STD_LOGIC

);

END COMPONENT;

```

```

SIGNAL INICIO: STD_LOGIC;

SIGNAL A,B: STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL FIN:STD_LOGIC;

SIGNAL S: STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL M: STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL CLK, RESET: STD_LOGIC;

begin

mi_test_CARD: MONT_CARD PORT MAP

(INICIO=>INICIO,A=>A,B=>B,S=>S,FIN=>FIN,M=>M,CLK=>CLK,RESET=>RESET);

--SIMULACION DEL RESET

PROCESS

BEGIN

reset <= '0';

INICIO<='0';

WAIT FOR 150 ns;

reset <= '1';

WAIT FOR 1000 ns;

reset <= '0';

WAIT FOR 10 us;

INICIO<='1';

WAIT;

END PROCESS;

-- SIMULACION CLK

PROCESS

BEGIN

wait for 1 us;

clk<='1';

wait for 1 us;

clk<='0';

end process;

```

```

PROCESS

BEGIN

A<=CONV_STD_LOGIC_VECTOR(5,4);

B<=CONV_STD_LOGIC_VECTOR(7,4);

M<=CONV_STD_LOGIC_VECTOR(11,4);

WAIT;

END PROCESS;

END TEST_CARD_A;

```

# IMPLEMENTACIÓN DE ALGORITMOS

# [MULTIPLICADOR COMBINACIONAL]

ALGORITMO - IMPLEMENTACIÓN VHDL - SIMULACIÓN - SÍNTESIS - RESULTADOS

# 3. IMPLEMENTACIÓN DE ALGORITMOS

# 3.1 <u>MULTIPLICACION COMBINACIONAL</u>

### **3.1.2 <u>ALGORITMO</u>**

En esta multiplicación se realizará la operación de forma directa a través de un circuito totalmente combinacional. El método de multiplicación por sumas y desplazamientos tiene una implementación combinacional prácticamente directa.

En la figura se muestra un multiplicador para números binarios sin signo de 4 bits. La propia disposición de las celdas ya recuerda el proceso de la multiplicación, es decir, generación de productos parciales desplazados hacia la izquierda. Para poder llegar a comprender el funcionamiento de este circuito es necesario en primer lugar analizar el funcionamiento de cada celda básica.

La figura muestra la estructura interna de esa celda básica. Consta de un sumador completo (FA) y una puerta AND lógica. La puerta AND realiza el producto de cada bit

del multiplicador qi con el bit correspondiente del multiplicando mj generándose así un operando para el Sumador Completo. Los otros operandos son el bit correspondiente del producto parcial anterior y el acarreo generado en la etapa previa.

Si se observa el multiplicador de la figura, la primera fila de celdas elementales realiza la generación del primer producto parcial mediante la función lógica AND de q0, con los bits m0, m1, m2 y m3 del multiplicando. En la segunda fila se genera el segundo producto parcial de manera similar, ahora realizando la función lógica AND de q1, con cada uno de los bits de M; este segundo producto parcial (desplazado un lugar a la izquierda) se suma con el generado en la fila anterior. La tarea realizada en las filas tres y cuatro es similar al de las dos anteriores, en ellas se generan, respectivamente, los productos parciales relativos a multiplicar M por q2 y q3.

### 3.1.3 <u>IMPLEMENTACION EN VHDL</u>

Para la implementación de este circuito se realizará a través del sintetizador ISE, crearemos un programa vhdl en el cual lo único que se programará será la multiplicación a través de una línea de código en la cual aparecerá S<=A\*B, una vez creado y compilado el código se realizará la síntesis la cual nos dará el circuito combinacional que queremos. En el sintetizador eliminamos la opción que nos da la fpga de utilizar su bloque multiplicador, de esa manera podemos ver el área que ocupa en número de LUT y poder compararlos con los demás algoritmos.

### Código=>

```

PROCESS(CLK,RESET)

BEGIN

IF RESET='1' THEN

S<=CONV_STD_LOGIC_VECTOR(0,2*N);

FIN<='0';

ELSIF CLK' EVENT AND CLK='1' THEN

FIN<='1';

S<= A*B;

END IF;

END PROCESS;

```

El diagrama de flujo se muestra a continuación:

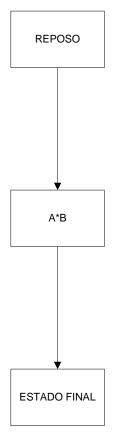

Figura 39 - D.ESTADOS COMBINACIONAL

# 3.1.4 SIMULACIÓN

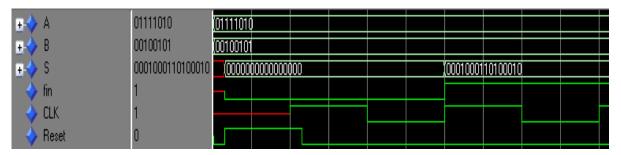

En las siguientes simulaciones se muestra tanto en código binario como en decimal el cálculo del producto a través de esta implementación.

Figura 40 - SIMULACION COMB 1

Figura 41 - SIMULACION COMB 2

Como se observa en las simulaciones para esta implementación el cálculo tarda 1 ciclo de reloj debido a que se basa en un circuito totalmente combinacional. Por tanto se puede concluir que para N bits esta implementación tarda 1 ciclo de reloj.

## **3.1.5 SINTESIS**

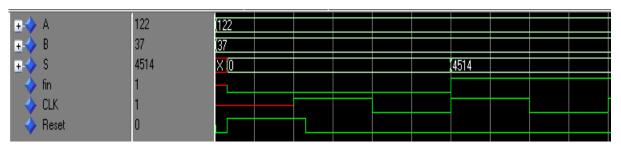

Para la implementación se ha elegido un FPGA Spartan 3, la síntesis se ha realizado para 4,8,16,32,64,128,256,512 y 1024 bits. Los resultados para los distintos bits se compararán más adelante con los otros algoritmos implementados. El área se medirá en número de LUT de 4 variables, también se calculará la frecuencia máxima a la que puede ir cada implementación.

N=4

Frecuencia Máxima= 154 MHZ

| Device Utilization Summary (estimated values) |      |           |             |  |  |

|-----------------------------------------------|------|-----------|-------------|--|--|

| Logic Utilization                             | Used | Available | Utilization |  |  |

| Number of Slices                              | 9    | 768       | 1%          |  |  |

| Number of 4 input LUTs                        | 15   | 1536      | 0%          |  |  |

| Number of bonded IOBs                         | 19   | 124       | 15%         |  |  |

| Number of GCLKs                               | 1    | 8         | 12%         |  |  |

N=8

Frecuencia Máxima = 105 MHZ

| Device Utilization Summary (estimated values) |      |           |             |  |  |

|-----------------------------------------------|------|-----------|-------------|--|--|

| Logic Utilization                             | Used | Available | Utilization |  |  |

| Number of Slices                              | 37   | 768       | 4%          |  |  |

| Number of 4 input LUTs                        | 70   | 1536      | 4%          |  |  |