**Ph.D. Dissertation**

# Design of Field-Programmable Mixed-Signal IC with Time-Domain Configurable Analog Block

가변기능형 아날로그 블록 기반의 현장 프로그램이 가능한 혼성 신호 집적회로의 설계

by

Yunju Choi

August, 2017

Department of Electrical Engineering and Computer Science College of Engineering Seoul National University

# Design of Field-Programmable Mixed-Signal IC with Time-Domain Configurable Analog Block

지도 교수 김재하

이 논문을 공학박사 학위논문으로 제출함 2017 년 7월

> 서울대학교 대학원 전기·컴퓨터공학부 최 윤 주

최윤주의 박사 학위논문을 인준함 2017 년 7월

# Design of Field-Programmable Mixed-Signal IC with Time-Domain Configurable Analog Block

by

Yunju Choi

A Dissertation Submitted to the Department of Electrical Engineering and Computer Science in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

at

#### SEOUL NATIONAL UNIVERSITY

August, 2017

Committee in Charge:

| Chairman      | Hyuk-Jae Lee   |

|---------------|----------------|

| Vice-Chairman | Jaeha Kim      |

| Member        | Chulwoo Kim    |

| Member        | Yongsam Moon   |

| Member        | Jung-Hoon Chun |

### Abstract

Fast-emerging electronic device applications demand a variety of new mixedsignal ICs to be developed in fast cycle and with low cost. While fieldprogrammable gate arrays (FPGAs) are established solutions for timely and low-cost prototyping of digital systems, their counterpart for mixed-signal circuits is still an active area for research. This thesis presents a design of a field-programmable IC for analog/mixed-signal circuits, which solves many challenges with the previous works by performing analog functions in time domain.

In order to realize the field-programmable analog functionality, time-domain configurable analog block (TCAB) is proposed. A single TCAB can be programmed to various analog circuits, including a time-to-digital converter, digitally-controlled oscillator, digitally-controlled delay cell, digital pulse-width modulator, and phase interpolator. In addition, the TCABs convey and process analog information using the frequency, pulse width, delay, or phase of digital pulses or pulse sequences, rather than using analog voltage or current signals for less susceptibility to attenuation and noise. This analog information expressed in the digital pulses makes it easy to implement scalable programmable interconnects among the TCABs. The architecture of field-programmable IC capable of emulating today's diverse mixed-signal systems is also introduced. In addition to the TCABs, the proposed IC also includes arrays of configurable logic blocks (CLBs) and programmable arithmetic logic units (ALUs) for programmable digital functions. By programming the functionality of the TCAB, CLB, and ALU arrays and configuring the interconnects,

the chip can implement various mixed-signal systems.

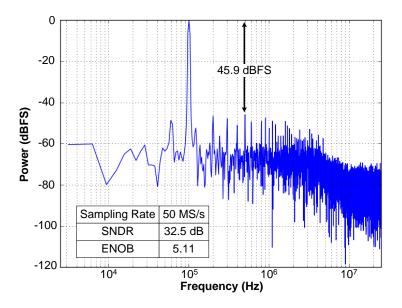

A prototype IC fabricated with 65-nm CMOS technology demonstrates the versatile programmability of the proposed TCAB and the IC by being successfully operated as a 1-GHz phase-locked loop with a 12.3-ps<sub>rms</sub> integrated jitter, as a 50-MS/s analog-to-digital converter with a 32.5-dB SNDR, and as a 1.2-to-0.7V DC–DC converter with 95.5 % efficiency.

Keywords : field-programmable mixed-signal IC, field-programmable analog array, reconfigurable architecture, reconfigurable analog array, mixed-signal IC. Student Number : 2013-30264

## Contents

| ABSTRACT    |                                       | Ι   |

|-------------|---------------------------------------|-----|

| CONTENTS    |                                       | III |

| LIST OF FIG | GURES                                 | VI  |

| LIST OF TA  | BLES                                  | XI  |

| CHAPTER 1   | INTRODUCTION                          | 1   |

| 1.1 Mo      | TIVATIONS                             | 1   |

| 1.2 THE     | SIS CONTRIBUTION AND ORGANIZATION     | 5   |

| CHAPTER 2   | TIME-DOMAIN CONFIGURABLE ANALOG BLOCK | 7   |

| 2.1 OVE     | RVIEW OF THE TCAB                     | 9   |

| 2.1.1.      | RECONFIGURABLE FUNCTIONALITY          | 9   |

| 2.1.2.      | TIME-DOMAIN SIGNAL PROCESSING         | 14  |

| 2.2 Circ    | CUIT IMPLEMENTATION OF THE TCAB       | 17  |

| 2.3 VER     | SATILE PROGRAMMABILITY OF TCAB        | 24  |

| 2.3.1.      | RELAXATION OSCILLATOR                 | 24  |

| 2.3.2.      | DIGITALLY-CONTROLLED OSCILLATOR       | 28  |

| 2.3.3.      | DIGITAL PULSE-WIDTH MODULATOR         | 32  |

| 2.3.4.      | GATED OSCILLATOR                      | 34  |

| 2.3.5.      | DIGITALLY-CONTROLLED DELAY CELL       | 35  |

| 2.3.6.      | PHASE INTERPOLATOR                    | 37  |

|       | 2.3.7. | MULTIPHASE DCO                          | 39 |

|-------|--------|-----------------------------------------|----|

|       | 2.3.8. | NON-OVERLAPPING PULSE GENERATOR         | 41 |

| 2.4   | TCA    | B ARRAY WITH PROGRAMMABLE INTERCONNECTS | 43 |

|       | 2.4.1. | TCAB ARRAY COMPOSITION                  | 43 |

|       | 2.4.2. | PROGRAMMABLE INTERCONNECTS              | 44 |

| CHAP' | TER 3  | PROPOSED ARCHITECTURE FOR FIELD-        |    |

| PROG  | RAMM   | IABLE MIXED-SIGNAL IC                   | 49 |

| СНАР  | TER 4  | CIRCUIT IMPLEMENTATION                  | 54 |

| 4.1   | CONF   | FIGURABLE LOGIC BLOCK ARRAY             | 55 |

| 2     | 4.1.1. | CONFIGURABLE LOGIC BLOCK                | 55 |

| 2     | 4.1.2. | CLB ARRAY                               | 56 |

| 4.2   | Ariti  | HMETIC LOGIC UNIT ARRAY                 | 58 |

| 2     | 4.2.1. | ARITHMETIC LOGIC UNIT                   | 58 |

| 2     | 4.2.2. | ALU ARRAY                               | 61 |

| 4.3   | INTER  | RFACING BLOCKS                          | 63 |

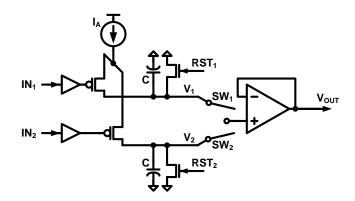

| 2     | 4.3.1. | VOLTAGE-TO-TIME CONVERTER               | 64 |

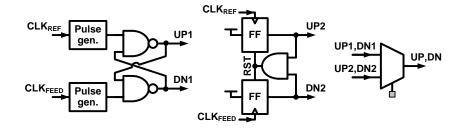

| 2     | 4.3.2. | PHASE-FREQUENCY DETECTOR                | 65 |

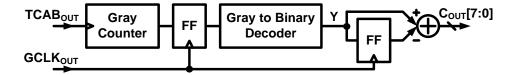

| 2     | 4.3.3. | COUNTER BLOCK                           | 66 |

| 2     | 4.3.4. | TIME-TO-VOLTAGE CONVERTER               | 68 |

| 4.4   | Prog   | RAM METHOD                              | 70 |

| СНАР  | TER 5  | MIXED-SIGNAL EXAMPLES AND EXPERIMENTAL  |    |

#### RESULTS

73

| 5.1   | MEA    | SUREMENT RESULTS OF TCAB        | 76  |

|-------|--------|---------------------------------|-----|

|       | 5.1.1. | DIGITAL PULSE-WIDTH MODULATOR   | 76  |

| -     | 5.1.2. | DIGITALLY-CONTROLLED OSCILLATOR | 79  |

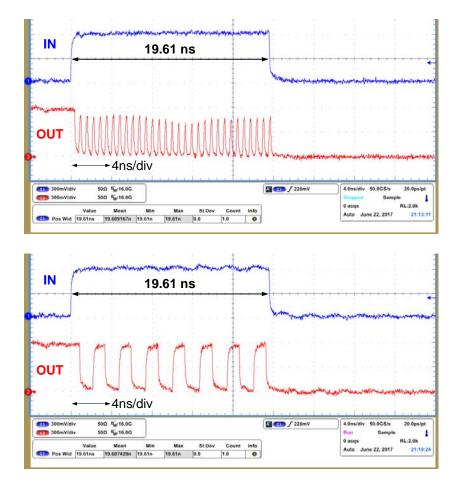

| -     | 5.1.3. | GATED OSCILLATOR                | 81  |

| 5.2   | DIGI   | TAL PHASE-LOCKED LOOP           | 83  |

| 5.3   | Anai   | LOG-TO-DIGITAL CONVERTER        | 89  |

| 5.4   | DC-l   | DC CONVERTER                    | 94  |

| СНАР  | TER 6  | CONCLUSION                      | 99  |

| BIBLI | OGRA   | РНҮ                             | 101 |

| 초 록   |        |                                 | 108 |

## **List of Figures**

| FIG. 1.1 PROCEDURES OF IC PRODUCTION                                                   |

|----------------------------------------------------------------------------------------|

| FIG. 1.2 PROCEDURES OF PROTOTYPING DIGITAL SYSTEMS WITH FPGAS                          |

| Fig. 2.1 TCAB that can change its functionality via field-programming10 $\!\!\!\!\!$   |

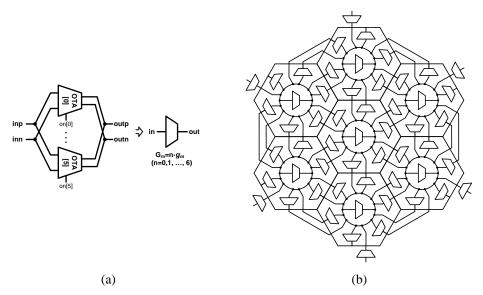

| Fig. 2.2 (a) The unit analog block (tunable $G_{M}$ cell) and (b) array composition of |

| THE UNIT BLOCK IN THE FIELD-PROGRAMMABLE ANALOG ARRAY [6]11                            |

| FIG. 2.3 (A) SCHEMATIC OF SIXTH BANDPASS FILTER AND (B) EXEMPLARY PLACEMENT-AND-       |

| ROUTING OF THE FILTER ON FPAA IN [6]11                                                 |

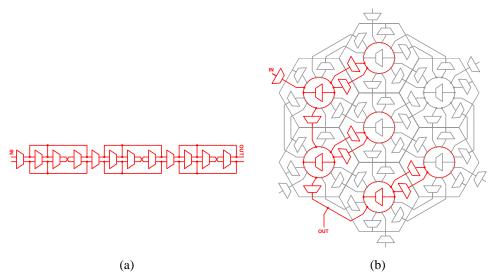

| Fig. 2.4 (a) Implementation of the programmable analog in $[10]$ , (b) schematics of   |

| LOGARITHMIC AMPLIFIER, (C) EXEMPLARY PLACEMENT-AND-ROUTING OF THE                      |

| AMPLIFIER ON THE PROGRAMMABLE IC IN [10]                                               |

| FIG. 2.5 (A) UNIT BLOCK OF PROGRAMMABLE NMOSS AND (B) ITS ARRAY COMPOSITION [12].      |

|                                                                                        |

| FIG. 2.6 THE COMPARISON AMONG THE SIGNAL REPRESENTATION WAY OF (A) CONVENTIONAL        |

| ANALOG BLOCKS WITH CONTINUOUS VOLTAGE FORMS, (B) TCAB WITH MODULATED                   |

| PULSE FREQUENCY, AND (C) TCAB WITH MODULATED PULSE-WIDTH14                             |

| FIG. 2.7 CIRCUIT IMPLEMENTATION OF TCAB CORE                                           |

| FIG. 2.8 CIRCUIT IMPLEMENTATION OF THE CROSSING DETECTOR IN THE TCAB                   |

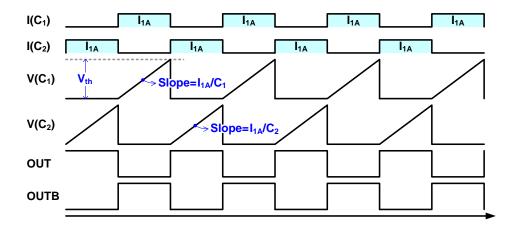

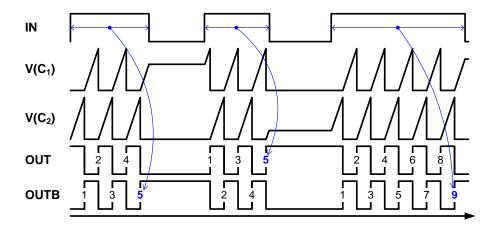

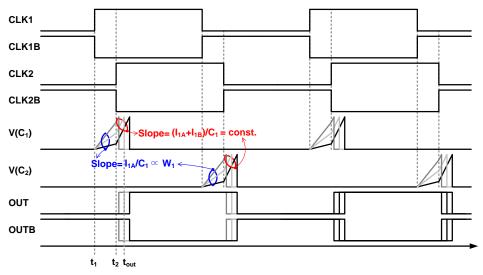

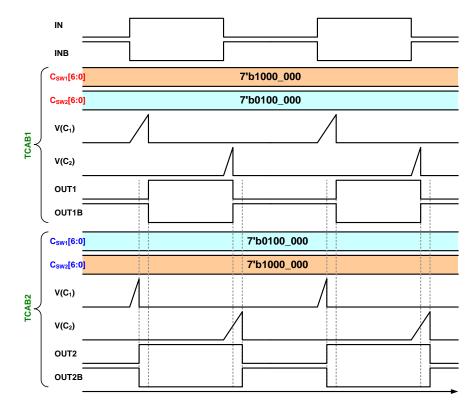

| FIG. 2.9 TIMING DIAGRAM FOR THE BASIC OPERATION OF THE TCAB                            |

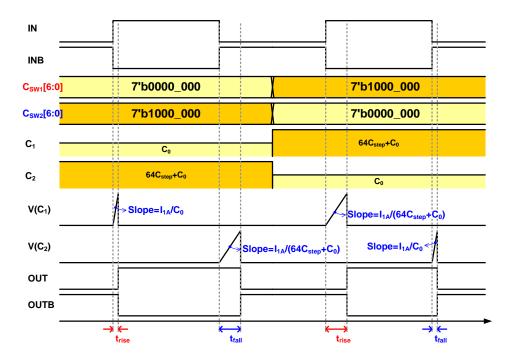

| FIG. $2.10$ TIMING DIAGRAM FOR TCAB OPERATION WHEN THE SWITCH CONFIGURATION            |

| CHANGES                                                                                |

| FIG. 2.11 CIRCUIT IMPLEMENTATION OF NMOS LADDER BASED CURRENT STEERING DAC IN          |

| THE TCAB                                                                           |

|------------------------------------------------------------------------------------|

| FIG. 2.12 CIRCUIT IMPLEMENTATION OF DIGITALLY-CONTROLLED CAPACITOR INCLUDED IN     |

| THE TCAB                                                                           |

| FIG. 2.13 TCAB IMPLEMENTATION INCLUDING THE INPUT MULTIPLEXERS AND                 |

| CONFIGURATION BLOCKS                                                               |

| Fig. 2.14 The TCAB configuration as a fixed-frequency relaxation oscillator 25 $$  |

| FIG. 2.15 TIMING DIAGRAM OF THE TCAB WHEN CONFIGURED AS A FIXED-FREQUENCY          |

| RELAXATION OSCILLATOR                                                              |

| FIG. 2.16 THE TCAB CONFIGURATIONS AS DIFFERENT RELAXATION OSCILLATORS              |

| FIG. 2.17 THE TCAB CONFIGURATION AS A DCO                                          |

| FIG. 2.18 TIMING DIAGRAM OF THE TCAB WHEN CONFIGURED AS A DCO                      |

| FIG. 2.19 THE TCAB CONFIGURATIONS AS DIFFERENT DCOS                                |

| FIG. 2.20 THE TCAB CONFIGURATION AS A DPWM                                         |

| FIG. 2.21 TIMING DIAGRAM OF THE TCAB WHEN CONFIGURED AS A DPWM                     |

| FIG. 2.22 THE TCAB CONFIGURATION AS A GATED OSCILLATOR                             |

| Fig. 2.23 Timing diagram of the TCAB when configured as a gated-oscillator 34 $$   |

| FIG. 2.24 THE TCAB CONFIGURATION AS A DIGITALLY-CONTROLLED DELAY CELL              |

| FIG. 2.25 TIMING DIAGRAM OF THE TCAB WHEN CONFIGURED AS A DIGITALLY-CONTROLLED     |

| DELAY CELL                                                                         |

| FIG. 2.26 THE TCAB CONFIGURATION AS A PHASE INTERPOLATOR                           |

| Fig. 2.27 Timing diagram of the TCAB when configured as a phase interpolator 38 $$ |

| FIG. 2.28 THE TCABS CONFIGURATION AS A MULTIPHASE (4-PHASE) DCO                    |

| FIG. 2.29 TIMING DIAGRAM FOR THE OPERATION OF THE TCABS AS A MULTIPHASE DCO 40     |

| FIG. 2.30 THE TCABS CONFIGURATION AS A NON-OVERLAPPING PULSE GENERATOR             |

| FIG. 2.31 TIMING DIAGRAM FOR THE OPERATION OF THE TCABS AS A NON-OVERLAPPING      |

|-----------------------------------------------------------------------------------|

| PULSE GENERATOR                                                                   |

| FIG. 2.32 COMPOSITION OF THE TCAB ARRAY                                           |

| FIG. 2.33 IMPLEMENTATION OF THE PROGRAMMABLE INTERCONNECTS IN THE TCAB ARRAY.     |

|                                                                                   |

| FIG. 2.34 EXAMPLE OF PROGRAMMABLE SIGNAL PATH IN THE TCAB ARRAY TO CONFIGURE A    |

| SINGLE TCAB AS THE RELAXATION OSCILLATOR                                          |

| FIG. 2.35 EXAMPLE OF PROGRAMMABLE SIGNAL PATH IN THE TCAB ARRAY TO CONFIGURE      |

| TWO TCABS AS THE FOUR PHASE DCO                                                   |

| FIG. 3.1. ARCHITECTURE AND FLOORPLAN OF THE PROPOSED FIELD-PROGRAMMABLE MIXED-    |

| SIGNAL IC                                                                         |

| FIG. 3.2 THREE TYPES OF PROGRAMMING OF THE MIXED-SIGNAL FEEDBACK SYSTEMS ON THE   |

| PROPOSED IC                                                                       |

| FIG. 3.3 PROGRAMMING OF THE DIGITALLY-ASSISTED ANALOG SYSTEMS ON THE PROPOSED IC. |

|                                                                                   |

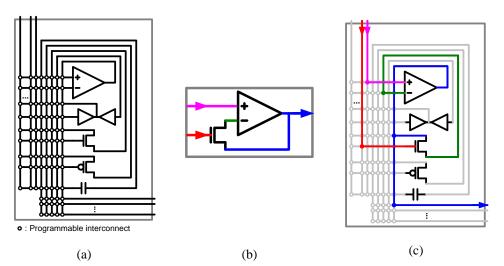

| FIG. 4.1 CIRCUIT IMPLEMENTATION OF THE CLB                                        |

| FIG. 4.2 CLB ARRAY COMPOSITION WITH PROGRAMMABLE INTERCONNECTS                    |

| FIG. 4.3 EXEMPLARY VTR RESULTS OF VERILOG MODULE INCLUDING 4-BIT GRAY DECODER     |

| (INPUT: LOW SIDE PORTS, OUTPUT: RIGHT SIDE PORTS)                                 |

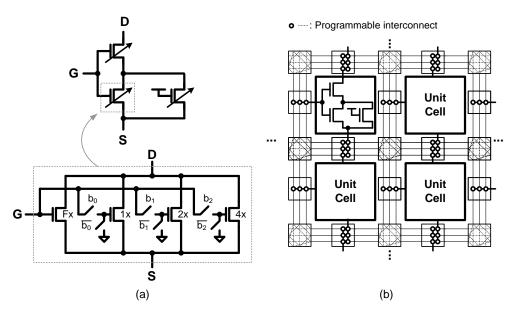

| FIG. 4.4 CIRCUIT IMPLEMENTATION OF THE ALU                                        |

| FIG. 4.5 ALU CONFIGURATION AS AN ACCUMULATOR                                      |

|                                                                                   |

| FIG. 4.6 ALU CONFIGURATION AS AN ARITHMETIC SHIFTER                               |

| FIG. 4.6 ALU CONFIGURATION AS AN ARITHMETIC SHIFTER                               |

| FIG. 4.9 CIRCUIT IMPLEMENTATION OF THE VTC                                        |

|-----------------------------------------------------------------------------------|

| FIG. 4.10 CIRCUIT IMPLEMENTATION OF THE PFD                                       |

| FIG. 4.11 CIRCUIT IMPLEMENTATION OF THE COUNTER BLOCK                             |

| FIG. 4.12 CIRCUIT IMPLEMENTATION OF THE TVC                                       |

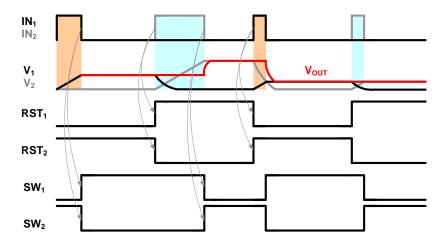

| FIG. 4.13 TIMING DIAGRAM OF THE TVC                                               |

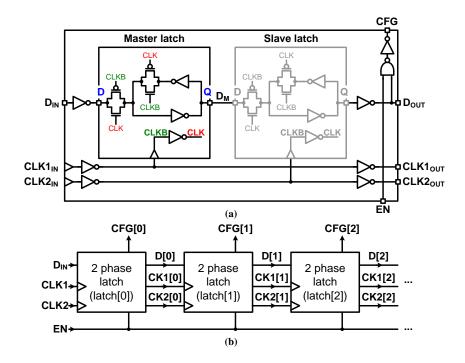

| FIG. 4.14. (A) IMPLEMENTATION OF 2 PHASE LATCH INCLUDING BUFFERS AND LOGIC FOR    |

| ENABLE OPTION AND (B) SCAN CHAIN BASED ON THE 2 PHASE LATCHES70                   |

| FIG. 4.15. (A) AN EXAMPLE SCAN CHAIN WITH TWO LATCHES AND (B) TIMING DIAGRAM FOR  |

| ITS OPERATION71                                                                   |

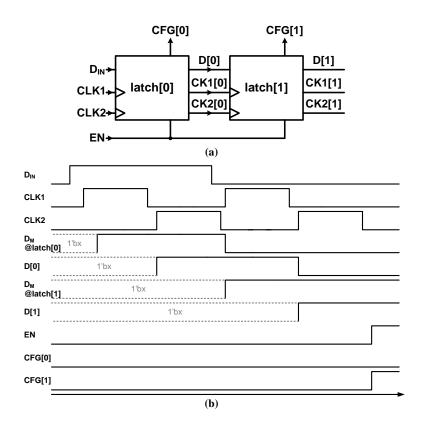

| FIG. 5.1 CHIP MICROGRAPH (ACTIVE LAYERS ONLY)                                     |

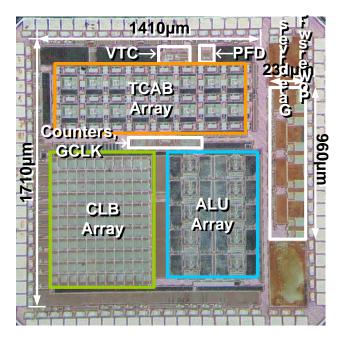

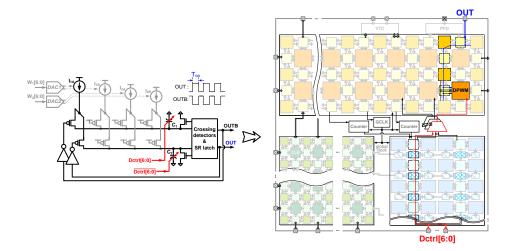

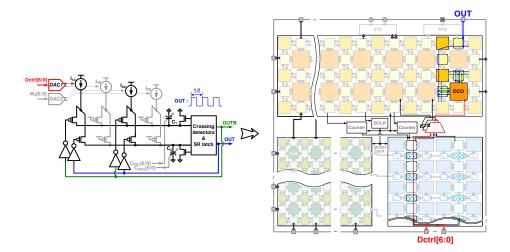

| FIG. 5.2 PLACEMENT AND ROUTING IN THE PROTOTYPE IC TO TEST A TCAB AS DPWM 76      |

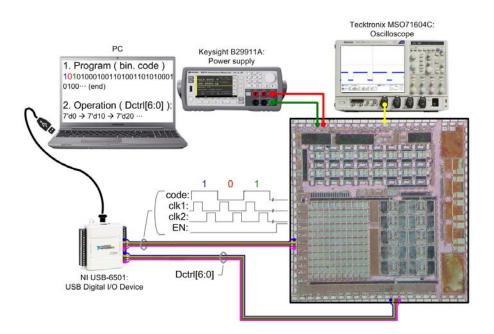

| FIG. 5.3 EXPERIMENT SETUP TO PROGRAM AND TEST THE IC77                            |

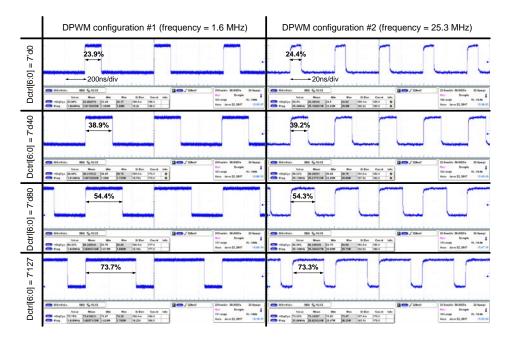

| Fig. 5.4 Measured waveforms when the IC operates as DPWM producing 1.6 MHz        |

| AND 25.3 MHz OUTPUT                                                               |

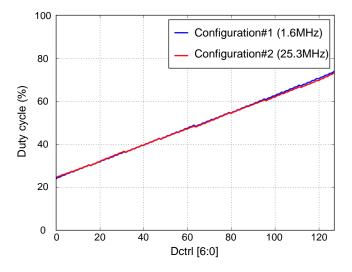

| FIG. 5.5 MEASURED TRANSFER FUNCTION OF DIGITAL INPUT CODE TO DUTY CYCLE OF OUTPUT |

| PULSE                                                                             |

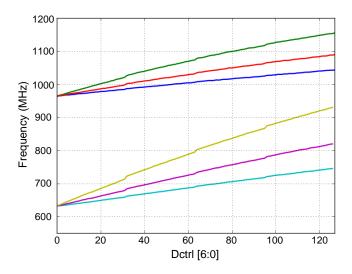

| FIG. 5.6 PLACEMENT AND ROUTING IN THE PROTOTYPE IC TO TEST A TCAB AS DCO          |

| FIG. 5.7 MEASURED TRANSFER FUNCTION OF DIGITAL INPUT COD E TO FREQUENCY OF OUTPUT |

| PULSE                                                                             |

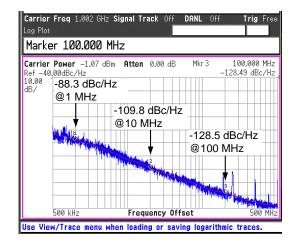

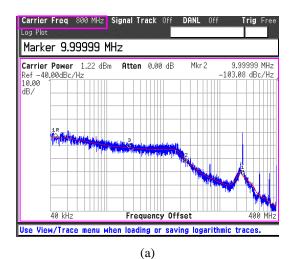

| FIG. 5.8 Measured phase noise of the programmed DCO when its output frequency     |

| IS 1.002 GHz                                                                      |

| Fig. 5.9 Placement and routing in the prototype IC to test a TCAB as gated        |

| OSCILLATOR                                                                        |

| OSCILLATOR                                                                        |

| GATED OSCILLATOR                                                                  |

|-----------------------------------------------------------------------------------|

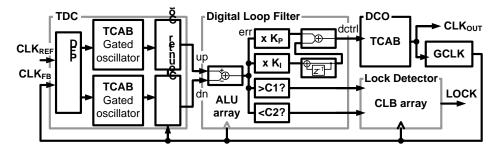

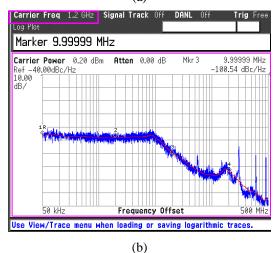

| FIG. 5.11 THE CHIP CONFIGURATION AS A 1-GHZ DIGITAL PLL                           |

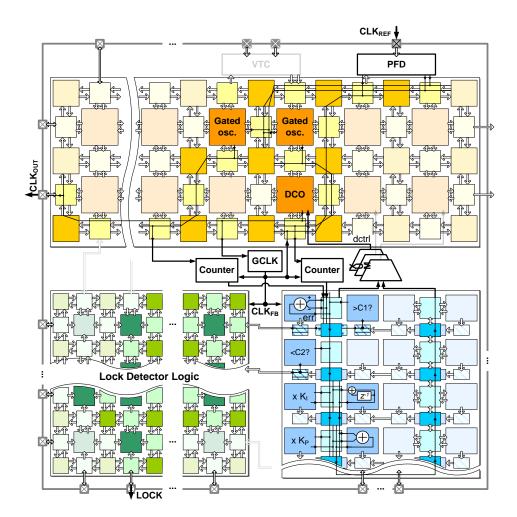

| FIG. 5.12 EXEMPLARY PLACEMENT AND ROUTING OF THE DIGITAL PLL                      |

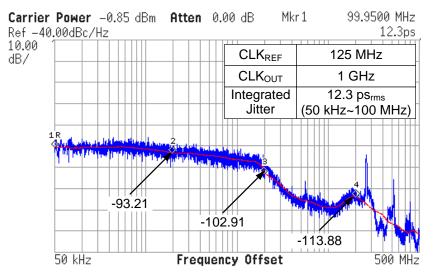

| FIG. 5.13 THE MEASURED PHASE NOISE OF THE PROGRAMMED DIGITAL PLL                  |

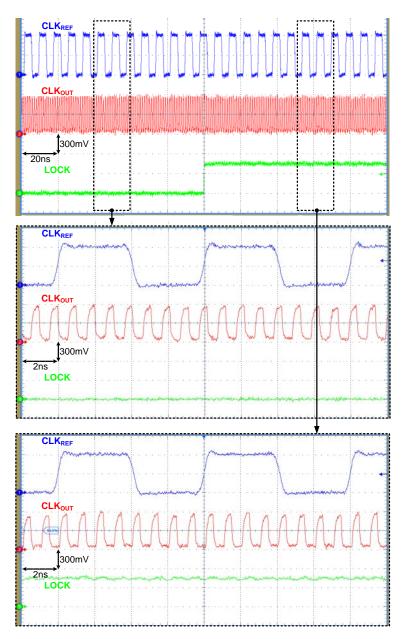

| Fig. 5.14 The measured voltage waveforms during initial locking transient of the  |

| PROGRAMMED DIGITAL PLL                                                            |

| Fig. 5.15 The measured phase noise of the programmed digital PLL when the         |

| INCLUDED DCO IS PROGRAMMED TO COVER OPERATING FREQUENCY OF (A) $800 \text{ MHz}$  |

| (B) 1.2 GHz                                                                       |

| FIG. 5.16 THE CHIP CONFIGURATION AS A 50 MS/S ADC                                 |

| FIG. 5.17 EXEMPLARY PLACEMENT AND ROUTING OF THE ADC                              |

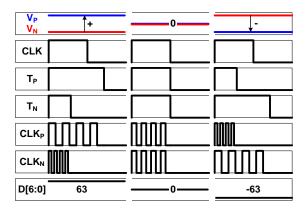

| FIG. 5.18 OPERATING PRINCIPLE OF THE PROGRAMMED ADC                               |

| FIG. 5.19 MEASURED DYNAMIC PERFORMANCE OF THE PROGRAMMED ADC                      |

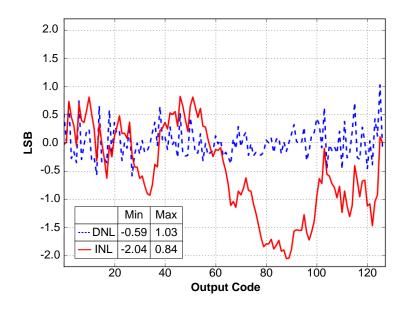

| FIG. 5.20 MEASURED STATIC PERFORMANCE OF THE PROGRAMMED ADC                       |

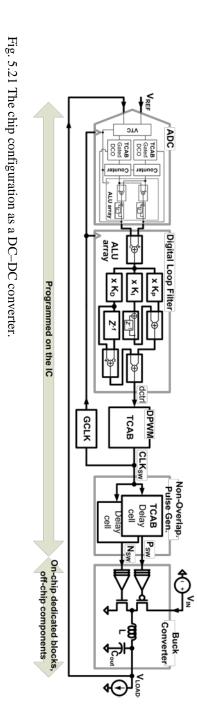

| FIG. 5.21 THE CHIP CONFIGURATION AS A DC–DC CONVERTER                             |

| FIG. 5.22 EXEMPLARY PLACEMENT AND ROUTING OF THE DC–DC CONVERTER96                |

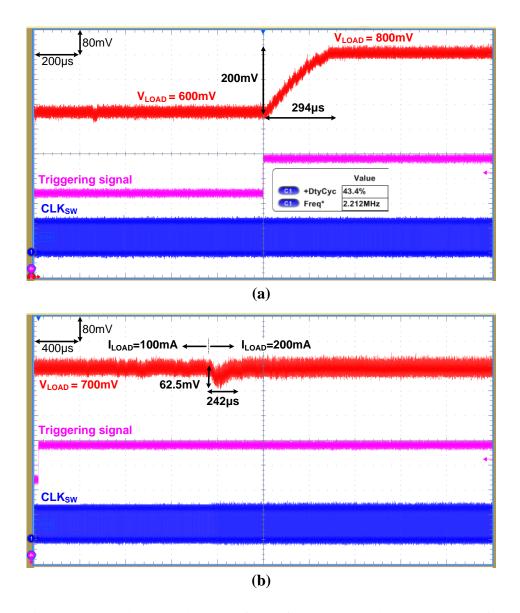

| Fig. 5.23 Measured output voltage waveforms of the programmed $DC-DC$             |

| CONVERTER IN (A) REFERENCE TRACKING (600-TO-800 MV STEP TRANSITION WITH A         |

| 150 MA LOAD CURRENT) AND (B) LOAD TRANSIENT (100-TO-200 MA STEP TRANSITION        |

| WITH A 700 MV OUTPUT VOLTAGE)                                                     |

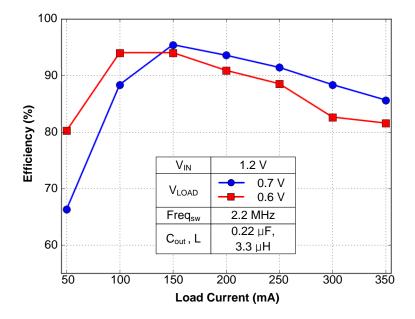

| FIG. 5.24 CONVERSION EFFICIENCIES FOR DIFFERENT LOAD CONDITIONS OF THE PROGRAMMED |

| DC–DC CONVERTER                                                                   |

## **List of Tables**

| TABLE. 5.1. CHARACTERISTIC SUMMARY OF THE PROTOTYPE IC                      | 74 |

|-----------------------------------------------------------------------------|----|

|                                                                             |    |

| TABLE. 5.2. COMPARISON OF PRIOR FIELD-PROGRAMMABLE ANALOG/MIXED- SIGNAL ICS |    |

|                                                                             |    |

| ARCHITECTURES                                                               | 75 |

## Chapter 1

## Introduction

### **1.1 Motivations**

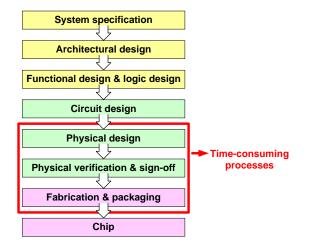

Today's fast-emerging electronic device applications require a variety of new analog/mixed-signal ICs and the ability to develop them with the least time, cost and effort. However, in general, the whole procedure from system specification to chipout for application-specific ICs (ASICs) takes lengthy period of time, as shown in Fig. 1.1. Particularly, the procedures of physical design, verification, and fabrication are very time-consuming. The fabrication step not only takes several months but also costs tens of thousands of dollars even if multi-project wafer (MPW) services are available for prototyping purpose. Such design and manufacture processes become more complicated and more expensive with modern deep sub-micron technologies.

Fig. 1.1 Procedures of IC production.

Fig. 1.2 Procedures of prototyping digital systems with FPGAs.

In this circumstance, field-programmable devices can help reduce the cost and time. In case of digital systems, for instance, field-programmable gate arrays (FPGAs) have been well developed and extensively used for those purposes, holding large market since the first commercial FPGA of mid 1980's [1]-[5]. As shown in Fig. 1.2, by synthesizing and programming the designs instead of fabricating them, the time and cost required for prototyping are significantly saved.

On the other hand, the corresponding field-programmable devices for analog/mixed-signal ICs are still under development [6]-[17]. Particularly, a proper design of the configurable analog block (CAB), which is an analog-equivalent to the configurable logic block (CLB) in FPGAs, remains unsettled.

One of the challenges in design of the CAB is to implement various programmable analog functionality. Contrary to the FPGAs including the CLBs whose input-to-output functionalities are reconfigurable by users via field-programming, most previous approaches of field-programmable mixed-signal ICs include fixed function blocks. For example, the works in [6], [7] provide a fixed function block with tunable performance characteristics to program analog filters only. Also, the field programmable ICs in [9], [10] contain several kinds of fixed function blocks and passive components. Then, those ICs are programmable to intended systems by choosing and connecting blocks among the limited blocks. Although there have been field-programmable analog ICs including programmable analog cells for emulation of single transistor behavior [12]-[14], they are too fine-grained to program today's complicated mixed-signal systems consisting of innumerable transistors.

In addition, it is common for the previously reported ICs [6]-[17] to process and propagate analog information with voltage or current amplitude, which limits degree of freedom for interconnection between blocks. Such signal processing with voltage or current form not only faces difficulties in analog circuit design coming along with technology scaling but also has fundamental weak-point in terms of programmable connection between blocks in the field-programmable devices. It is not easy to propagate analog signals through arbitrary direction or arbitrary long path which is reconfigured each time by users' programming. Therefore, it is required to insert power-hungry analog buffers on the signal path. However, the noise/distortionsensitive and band-limited nature of the analog buffers eventually limit programmability of signal path and even overall performance.

### **1.2 Thesis Contribution and Organization**

As described in Chapter 1.1, a proper design of the configurable analog block (CAB) both realizing various analog functions and enabling versatile interconnection remains unsettled. This thesis presents a field-programmable mixed-signal IC for the rapid and low-cost prototyping, which solves those challenges with the previous works by performing analog functions in time domain. As an approach to implement the CAB with the various programmable analog functions and ability of versatile interconnection, the time-domain CAB (TCAB) is proposed. It is demonstrated that the proposed TCAB can emulate the functionalities of various mixed-signal circuits used in timing generation, data conversion, and power management ICs. Moreover, since the input and output signals of the proposed TCABs are digital pulses with modulated pulse-width, delay, or frequency, the signals can be easily routed to other TCABs or other part of the IC via digital programmable interconnects. Additionally, this thesis also introduces field-programmable IC architecture to emulate various mixed-signal feedback systems.

This thesis is organized as follows. In Chapter 2, a design of time-domain configurable analog block (TCAB) for the programmable analog functionality is presented. The basic concept and strategy of implementing the TCAB are described. Then, its circuit implementation is presented. In order to show how the input-to-output function of the TCAB can change, diverse examples of the TCABs being programmed to different time-domain analog circuits are presented. An array

composition of multiple TCABs is also described.

In Chapter 3, an IC architecture for the field-programmable mixed-signal IC is introduced. It is explained that how the mixed-signal feedback systems or digitally assisted analog systems can be programmed on the proposed IC.

In Chapter 4, building blocks to implement the proposed field-programmable IC are introduced. In addition to the array of the TCABs for programmable analog functionality, the IC also includes the other two arrays of configurable logic blocks (CLBs) and arithmetic logic units (ALUs) for programmable digital function and interfacing blocks at the boundary of each array of the programmable blocks. Their role and circuit implementation are presented. A method to program the whole chip based on scan chain is also briefly described.

In Chapter 5, measurement results with a prototype IC fabricated in a 65-nm LP CMOS technology are provided. The programmability of the TCAB is first demonstrated by configuring the IC as a digital pulse-width modulator, digitally-controlled oscillator, and gated oscillator and measuring their characteristics. Then, the versatile programmability of the IC is demonstrated by configuring the IC as three representative mixed-signal systems, a PLL, ADC, and DC-to-DC converter, and measuring their characteristics.

Lastly, in Chapter 6, the proposed work is summarized with conclusion.

### Chapter 2

# Time-Domain Configurable Analog Block

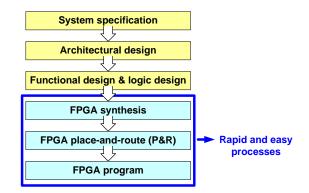

When implementing today's mixed-signal systems including timing generation ICs, data converters, and power management ICs, diverse analog blocks such as a time-to-digital converter (TDC), digitally-controlled oscillator (DCO), digitally-controlled delay cell, digital pulse-width modulator (DPWM), and phase interpolator are required. In common, the listed analog blocks are basically time-domain analog circuits. That is, inputs or outputs of the blocks are binary digital pulses of which time-domain quantity such as pulse-width, frequency, delay or phase encodes analog block (TCAB) that can change its input-to-output functionality to that of the time-domain analog blocks composing the mixed-signal feedback systems like digital PLL, ADC, or DC-DC converter is proposed [18].

That is, as an analogous to the configurable logic blocks (CLBs) used in digital

FPGAs, this work presents the field-programmable analog block of which input-tooutput function can be changed via programming. It is contrast to the prior works on field-programmable analog arrays (FPAAs) where the unit blocks have fixed inputto-output functions and only the interconnect blocks among them are programmable. For example, the work in [6] uses an array of transconductance ( $G_m$ ) cells of which only the parametric characteristics such as gain and bandwidth are programmable. Also, the field programmable ICs in [9], [10] contain more diverse active circuits (e.g., OTAs, current mirrors, and Gilbert multiplier) and passive components, but each block has fixed and unchangeable functionality.

Further, most previously reported ICs [6]-[17] suffer from the loss in signal quality while the signals propagate through the programmable interconnects in voltage or current forms. For instance, the analog voltages propagating via long interconnects and switches are susceptible to attenuation due to the resistance and capacitance of the circuit networks. Also, their signal-to-noise ratio (SNR) can be easily degraded due to noise and interference coupled to the network. Whereas inserting analog buffers (e.g., unity-gain amplifiers) can mitigate these issues to some degrees, analog buffers are typically power-hungry.

In order to achieve both programmable input-to-output functionality of unit analog blocks and solves the scalability of programmable interconnects among them, this work establishes a strategy of conveying and processing analog information in time domain. For instance, the proposed TCABs can be programmed to various time-domain analog circuits including TDC, DCO, DPWM, digitally-controlled delay cell, or phase interpolator. The TCABs receive and produce analog information in the form of digital pulses of which frequency, delay, phase or pulsewidth changes with the signal to be conveyed. Hence, the analog information expressed in digital pulses can reliably propagate through more scalable digital programmable interconnects (e.g., with tri-state buffers and digital buffers) with less susceptibility to attenuation and noise.

The rest of this chapter is organized as follows. The detailed description on features of the TCAB is presented in comparison with the prior works. Then, following subchapters cover the circuit implementation of the TCABs, and explain how their input-to-output functions can be changed via field-programming by listing configuration examples. Lastly, the TCAB array composition including the implementation of programmable interconnects is also described.

#### 2.1 Overview of the TCAB

#### **2.1.1. Reconfigurable functionality**

One of the most noteworthy difference of this work compared to the previouslyreported works is that programmable analog function is achieved solely by the TCAB. As illustrated in Fig. 2.1, a single TCAB can be programmed to time-domain analog blocks such as DCO, DPWM, gated oscillator, digitally-controlled delay cell or phase interpolator. It is in contrast to the works in [6], [7], [9], [10] that include limited kinds of analog blocks, each of which input-to-output function is fixed and unchangeable. When programming intended mixed-signal systems on those ICs, the only thing allowed to users is to choose the connections among the limitedly

Fig. 2.1 TCAB that can change its functionality via field-programming.

included blocks. Therefore, the availability of the ICs is eventually limited by how many kinds of analog blocks are included in the IC.

For example, Fig. 2.2 shows the field-programmable analog array (FPAA) in [6] which includes 55 tunable  $G_m$  cells. As a unit block, the tunable  $G_m$  cell includes six OTAs whose on/off is just controlled by digital program code in order to adjust the overall  $G_m$ , as shown in Fig. 2.2 (a). That is, the functionality of the unit block is fixed and only the parametric characteristics (i.e.,  $G_m$ ) are programmable. Therefore, when this FPAA is programmed to different analog systems, the things allowed to users are to decide whether to turn on or off each cell and  $G_m$ . Fig. 2.3 (a) shows an example analog system of sixth order bandpass filter and its placement-and-routing on the FPAA.

Fig. 2.2 (a) The unit analog block (tunable  $G_m$  cell) and (b) array composition of the unit block in the field-programmable analog array [6].

Fig. 2.3 (a) Schematic of sixth bandpass filter and (b) exemplary placement-and-routing of the filter on FPAA in [6].

Fig. 2.4 (a) shows how the field programmable IC in [10] provides the programmable analog. That is, it contains more diverse analog blocks like OTAs, floating gates to construct trans-linear circuits, a voltage buffer, capacitors, a transmission gate to configure switched-capacitor, nMOSs and pMOSs with two common terminals for easily constructing source-follower or current-mirror, and Gilbert multipliers. Each block still has fixed input-to-output functionality. Then, users choose the connection among the included diverse analog blocks by reconfiguring the programmable interconnects. For example, a logarithmic amplifier in Fig. 2.4 (b) can be programmed as shown in Fig. 2.4 (c) by programing the interconnects to connect the required blocks (i.e. an OTA and an nMOS).

Similarly, [9] contains OTAs, capacitors, switched capacitor, pMOSs or nMOSs, floating gate pMOSs with multiple control gates.

Fig. 2.4 (a) Implementation of the programmable analog in [10], (b) schematics of logarithmic amplifier, (c) exemplary placement-and-routing of the amplifier on the programmable IC in [10].

The way of programmable analog in this thesis (i.e., each TCAB maps the functionality of the analog circuits rather than their detailed structural topologies.) is also distinguished from the works in [12]-[14] that provide transistor level programmability to emulate behavior and critical analog properties (e.g.,  $I_d$ ,  $g_m$ , and  $r_{out}$ ) of each transistor in an intended system. Fig. 2.5 shows a unit block to emulate single transistor (nMOS case) and its array composition. Every single transistor in a target system are mapped to a unit cell in the array and the digital control code words ( $b_0$ ,  $b_1$ ,  $b_2$ ) in MOSs of the unit cells are programmed in order to match  $I_d$ ,  $g_m$ , and  $r_{out}$  to those of corresponding transistor in the system. However, due to the too fine-grained implementation, its availability is limited only to small-scale analog circuits (e.g., OTAs or analog filters) and difficult to be extended to today's mixed-signal systems consisting of innumerable transistor.

Fig. 2.5 (a) Unit block of programmable nMOSs and (b) its array composition [12].

#### 2.1.2. Time-Domain Signal Processing

Another important point is that the TCAB processes signals in time domain, receiving and producing digital pulses of which frequency, delay, phase or pulsewidth presents the analog information. The time-domain signal processing way of the TCAB is illustrated in Fig. 2.6 with the comparison to the voltage-domain signal

Fig. 2.6 The comparison among the signal representation way of (a) conventional analog blocks with continuous voltage forms, (b) TCAB with modulated pulse frequency, and (c) TCAB with modulated pulse-width.

processing way of the conventional analog blocks. Instead of processing analog information and exposing it with magnitude of voltage or current, the TCAB encodes the information to frequency, pulse-width, delay, or phase of digital pulses and the pulse sequences. Interestingly, this time-domain signal processing is a similar technique which time-based ADCs have adopted in order to overcome the various challenges in design of ADC (e.g., low supply voltage) as technology scales [19]-[22].

Since the inputs and outputs of the TCABs are digital pulses which are less susceptible to noise or distortion than signals in voltage or current forms, this work can achieve high programmability on signal propagation path. Actually, it is another major challenge to provide programmable connectivity for propagation of signals in field-programmable analog/mixed-signal IC because it is difficult to propagate analog signals over arbitrary path or long distance. Due to such difficulties, the work in [6] provides permanent connection between adjacent blocks and effectively disconnects them by programming the gain of the adjacent blocks to zero. Another implementation in [11] employs programmable switches which are placed only between the two adjacent blocks and lets users decide only whether to connect them. The work in [10] limitedly inserts analog buffers (e.g., OTA based unity-gain buffers) to convey analog signals farther, whereas most other interconnects are floating gate based switches that have limited availability due to their finite parasitic capacitance and resistance.

On the other hand, this work facilitates programmable connectivity comparable to that of digital FPGAs since both input and output of the TCAB are digital binary pulses. As can be seen in Chapter 2.4, the switch/connection blocks connecting among the TCABs are simply implemented with digital tri-state inverters and digital buffers in a similar way of digital FPGAs. As a result, the time-domain representation of analog information makes it easy to implement large-size of TCAB array, propagating signals to everywhere in the array.

The following subchapters present circuit implementation of the TCAB and how the TCAB can change its input-to-output functions in time-domain. Also, the TCAB array composition is described with the implementation of programmable interconnects included in the array in Chapter 2.4.

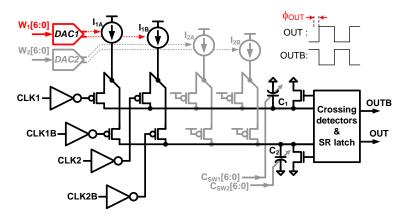

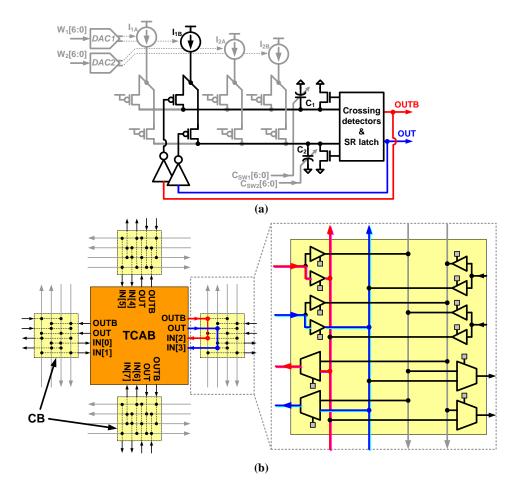

### 2.2 Circuit Implementation of the TCAB

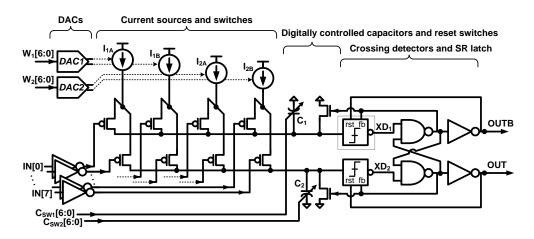

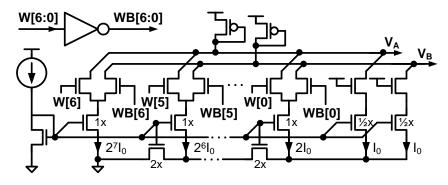

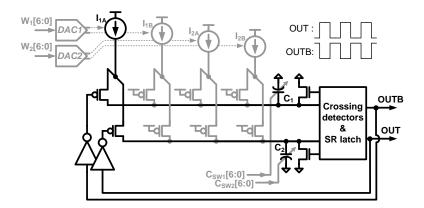

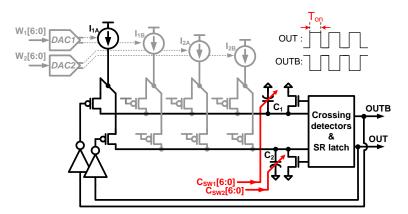

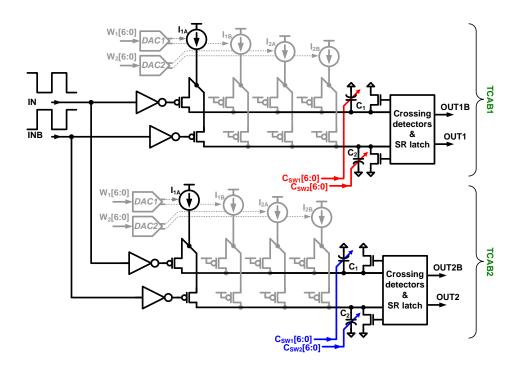

Fig. 2.7 shows the circuit implementation of the proposed TCAB. It consists of four sets of switched current source whose output current level is controlled by the preceded DAC, two digitally-controlled capacitors with reset switches, crossing detectors and an SR-latch.

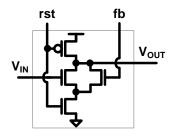

The current sources,  $I_{1A}/I_{1B}$  and  $I_{2A}/I_{2B}$ , selectively charge the digitally-controlled capacitors,  $C_1$  and  $C_2$ , depending on how the switches under each current source are configured by the 8 input signals, IN[7:0]. Once non-zero current flows to capacitor  $C_1$  and the voltage across  $C_1$  exceeds a certain threshold voltage, the following crossing detector makes falling transition at its output  $(XD_1)$ . For this operation, the crossing detector is implemented as shown in Fig. 2.8. The SR-latch then makes the two output pulses, *OUT* and *OUTB*, logic 1 and logic 0, respectively. Simultaneously,

Fig. 2.7 Circuit implementation of TCAB core.

Fig. 2.8 Circuit implementation of the crossing detector in the TCAB.

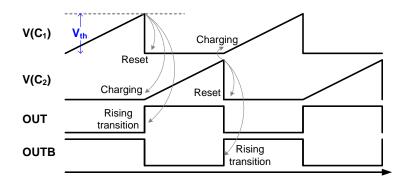

$C_1$  is discharged and the voltage across  $C_1$  is reset to zero by the reset switch. Then, the other capacitor  $C_2$  takes turn being charged, whereas  $C_1$  is maintained not to be charged. In this time, if the voltage across  $C_2$  exceeds the threshold, the output pulses, *OUT* and *OUTB*, are toggled to logic 0 and logic 1, respectively. That is, only one of the two capacitors gets charged at a time in an alternating fashion, while generating output pulses. This basic operation is illustrated in Fig. 2.9 with timing diagram.

The time-domain quantity of the TCAB output pulse that represents analog information is decided by how each capacitor is charged. The voltage across each

Fig. 2.9 Timing diagram for the basic operation of the TCAB.

capacitor after time t since time 0 when the corresponding capacitor starts being charged is given by

$$V_{C1}(t) = \int_0^t \frac{I_{C1}(\tau)}{C_1} d\tau, \ V_{C2}(t) = \int_0^t \frac{I_{C2}(\tau)}{C_2} d\tau,$$

(2.2.1)

where  $I_{C1}(\tau)$  or  $I_{C2}(\tau)$  denotes net current flowing to  $C_1$  or  $C_2$  at time  $\tau$ . By adjusting the current,  $I_{C1}(\tau)$  or  $I_{C2}(\tau)$ , or the capacitance of  $C_1$  or  $C_2$ , the time required for each capacitor to reach the threshold voltage changes and the time when output pulse is asserted changes.

There are three ways to control the charging behavior, and therefore, the pulse modulation of the TCAB output, which carries analog information. Those are to adjust *IN*[7:0] for the switch configuration,  $W_1$ [6:0] and  $W_2$ [6:0] for the DACs, and  $C_{SW1}$ [6:0] and  $C_{SW2}$ [6:0] for the digitally-controlled capacitors.

First, the charging behavior can change depending on the configuration of the 8 switches which are turned on/off by input pulses, IN[7:0]. When the switches are configured so that constant currents,  $I_{C1}$  and  $I_{C2}$ , always flow to  $C_1$  and  $C_2$ , the time which it takes for each output pulse to be asserted since the corresponding capacitor starts being charged is given by

$$t_{OUT} = \frac{V_{th}C_1}{I_{C1}} + t_{xing} + t_{logic}, \ t_{OUTB} = \frac{V_{th}C_2}{I_{C2}} + t_{xing} + t_{logic},$$

(2.2.2)

where  $V_{th}$  is the threshold voltage of crossing detector,  $t_{xing}$  denotes delay of crossing detector, and  $t_{logic}$  is logic gates delay from the SR-latch inputs to *OUT/OUTB*. In this case, output pulses oscillate and the oscillation period of the TCAB is given by

Fig. 2.10 Timing diagram for TCAB operation when the switch configuration changes.

$$T_{period} = \frac{V_{th}C_1}{I_{c1}} + \frac{V_{th}C_2}{I_{c2}} + 2(t_{xing} + t_{logic} + t_{reset}), \qquad (2.2.3)$$

where  $t_{reset}$  denotes the time that it takes for one of capacitor reset switches to be released since the other reaches the threshold voltage of the crossing detector.

If the switch configuration changes in the middle of charging and no current flows to  $C_1$  or  $C_2$  for a second, the voltage across each capacitor remains fixed during that time. Then, the switch configuration changes again and  $I_{C1}$  and  $I_{C2}$  flow to  $C_1$  and  $C_2$ , respectively, the output pulse is eventually asserted. When all the switches are open so that both  $I_{C1}$  and  $I_{C2}$  are always zero, then output pulses are not asserted at all. The described behaviors are illustrated in Fig. 2.10 with timing diagram when two switches are controlled by external signals and the others are maintained off.

Another way to control the charging behavior of the two capacitors is to change the current levels through the DACs. Each pair of current sources in the TCAB,

Fig. 2.11 Circuit implementation of nMOS ladder based current steering DAC in the TCAB.

$I_{1A}/I_{1B}$  or  $I_{2A}/I_{2B}$ , is adjusted by the preceded DAC so that their output currents in a pair are biased to be complementary each other. That is,  $I_{1A}+I_{1B}$  (or  $I_{2A}+I_{2B}$ ) remains constant regardless of  $W_1$  (or  $W_2$ ), while  $I_{1A}$  (or  $I_{2A}$ ) increases and  $I_{1B}$  (or  $I_{2B}$ ) decreases if  $W_1$  (or  $W_2$ ) increases and vice versa. To bias the paired current sources in this way, the preceded nMOS ladder based current steering DAC generates two voltages,  $V_A$  and  $V_B$ , as in Fig. 2.11. The ladder has similar architecture of R-2R ladder, therefore, the current through each pMOS is given by Eq. (2.2.4).

$$I_{A} = I_{0} + 2^{1}W[0] \times I_{0} + 2^{2}W[1] \times I_{0} + \dots + 2^{7}W[6] \times I_{0},$$

$$I_{B} = I_{0} + 2^{1}WB[0] \times I_{0} + 2^{2}WB[1] \times I_{0} + \dots + 2^{7}WB[6] \times I_{0},$$

(2.2.4)

where  $I_0$  is unit current step. Since WB[6:0] is inverse of W[6:0], the sum of  $I_A$  and  $I_B$  maintains same. Owing to its low-power consumption and compact size [23], the adopted DAC is suitable to compose the TCAB, considering that multiple TCABs are included in the proposed IC.

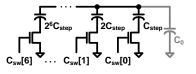

Lastly, it is also possible to adjust the charging rate by changing capacitances of  $C_1$  and  $C_2$ . Each of  $C_1$  and  $C_2$  is basically an array of binary weighted capacitors with switches which are turned on/off by input digital codes  $C_{SW1}[6:0]$  and  $C_{SW2}[6:0]$ , as shown in Fig. 2.12. Its equivalent output capacitance is given by

$$C_{1} = C_{0} + 2^{0}C_{sw1}[0] \times C_{step} + 2^{1}C_{sw1}[1] \times C_{step} + \dots + 2^{6}C_{sw1}[6] \times C_{step},$$

$$C_{2} = C_{0} + 2^{0}C_{sw2}[0] \times C_{step} + 2^{1}C_{sw2}[1] \times C_{step} + \dots + 2^{6}C_{sw2}[6] \times C_{step},$$

(2.2.5)

where  $C_{step}$  is the unit capacitance and  $C_0$  includes all the parasitic capacitance on that node and input capacitance of the following crossing detector. By changing the input digital codes  $C_{SW1}[6:0]$  and  $C_{SW2}[6:0]$ , the capacitances of  $C_1$  and  $C_2$  are adjusted.

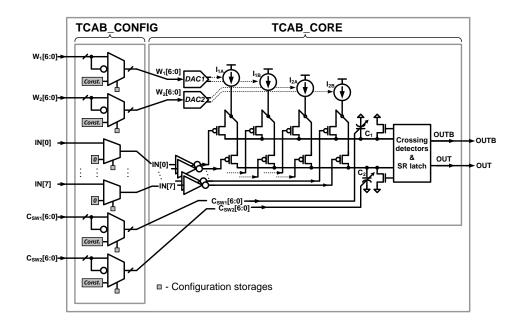

In addition to the described TCAB core in Fig. 2.7, the overall TCAB implement includes multiplexers for input signals ( $W_1$ [6:0],  $W_2$ [6:0], IN[7:0],  $C_{SW1}$ [6:0], and  $C_{SW2}$ [6:0]) and configuration blocks for selection signals of the multiplexers and storing of constants, as illustrated in Fig. 2.13. That is, instead of connecting input signals directly to the received signals, it is implemented for the signals to select among the received ones or programmed constants. For example,  $W_1$ [6:0],  $W_2$ [6:0],  $C_{SW1}$ [6:0], and  $C_{SW2}$ [6:0] of the core can be connected to one of the signals among

Fig. 2.12 Circuit implementation of digitally-controlled capacitor included in the TCAB.

received digital codes, their inverted codes, or programmed constants. Also, *IN*[7:0] can be connected to one of the signals among received digital pulse or zero. If they connected to zero, the corresponding switches after inverters are turned off. Configuration storages in Fig. 2.13 is where binary program codes are stored, which will be described in Chapter 4.4, Program Method. For the sake of simplicity, the rest figures to illustrate TCAB in this thesis can be presented, excluding the TCAB\_CONFIG part in Fig. 2.13.

Fig. 2.13 TCAB implementation including the input multiplexers and configuration blocks.

# 2.3 Versatile Programmability of TCAB

In order to explain how the input-to-output function of the TCAB changes, this subchapter presents configuration examples of the TCAB when it operates as six different time-domain analog blocks which are required when composing timing generation (e.g., PLLs), data conversion (e.g., ADCs), or power management ICs (e.g, DC-DC converters). Note that its input-to-output function totally changes depending on how the three kinds of inputs (i.e., IN[7:0] for the switch configuration,  $W_1$ [6:0] and  $W_2$ [6:0] for DACs, and ,  $C_{SW1}$ [6:0] and  $C_{SW2}$ [6:0] for digitally-controlled capacitors) are controlled.

Further, additional two examples, multiphase DCO and non-overlapping pulse generator, are also presented to show that multiple TCABs are combined together and operate as a time-domain analog block.

#### 2.3.1. Relaxation Oscillator

First, a TCAB can operate as a relaxation oscillator [24] with a fixed frequency as shown in Fig. 2.14. The TCAB is configured so that the two output pulses, *OUT* and *OUTB*, are connected back to two inputs, *IN*[1] and *IN*[0], respectively. Due to the complementarity of the output pulses which consequently turn on/off the two switches below a current source, the output current  $I_{1A}$  is always fully steered to one of the two capacitors. Then,  $C_1$  and  $C_2$  are charged alternately and output pulses are toggled. The timing diagram of this operation is presented in Fig. 2.15. If  $C_{SW1}$ [6:0]

Fig. 2.14 The TCAB configuration as a fixed-frequency relaxation oscillator.

Fig. 2.15 Timing diagram of the TCAB when configured as a fixed-frequency relaxation oscillator.

and  $C_{SW2}[6:0]$  are programmed same so that  $C_1$  and  $C_2$  have same capacitances, the configured TCAB operates as relaxation oscillator of which output pulse period,  $T_{period}$ , follows (2.3.1).

$$T_{period} = \frac{V_{th}C_1}{I_{1A}} + \frac{V_{th}C_2}{I_{1A}} + 2t_{xing} + 2t_{logic} + 2t_{reset}$$

=  $2\left(\frac{V_{th}C_1}{I_{1A}} + t_{xing} + t_{logic} + t_{reset}\right).$  (2.3.1)

By changing the current level of  $I_{1A}$  via  $W_1[6:0]$  or two capacitances via  $C_{SW1}[6:0]$ and  $C_{SW2}[6:0]$  via programming, the TCAB is reconfigured to different relaxation oscillator with different period.

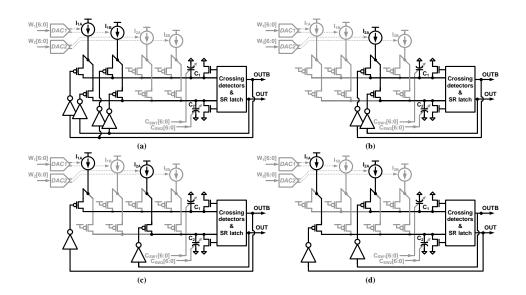

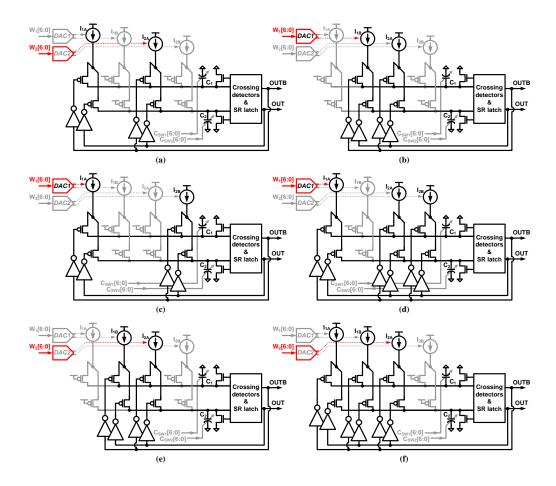

Fig. 2.16 also shows other four ways to configure relaxation oscillator with the TCAB. The relaxation oscillators in Fig. 2.16 (a)-(d) have the same behavior of that in Fig. 2.14, but with different expressions for  $T_{period}$ . Assuming  $C_1$  and  $C_2$  have same capacitances for Fig. 2.16 (a)-(d) and  $W_1$ [6:0] and  $W_2$ [6:0] are same so that  $I_{1A}$  and  $I_{2A}$  have same output currents for Fig. 2.16 (c)-(d),  $T_{period}$  for each is given by Eq.

Fig. 2.16 The TCAB configurations as different relaxation oscillators.

(2.3.2) - Eq. (2.3.5), respectively.

$$T_{period} = \frac{V_{th}C_1}{I_{1A} + I_{1B}} + \frac{V_{th}C_2}{I_{1A} + I_{1B}} + 2t_{xing} + 2t_{logic} + 2t_{reset}$$

$$= 2\left(\frac{V_{th}C_1}{I_{1A} + I_{1B}} + t_{xing} + t_{logic} + t_{reset}\right).$$

(2.3.2)

$$T_{period} = \frac{V_{th}C_1}{I_{2A}} + \frac{V_{th}C_2}{I_{2A}} + 2t_{xing} + 2t_{logic} + 2t_{reset}$$

=  $2\left(\frac{V_{th}C_1}{I_{2A}} + t_{xing} + t_{logic} + t_{reset}\right).$  (2.3.3)

$$T_{period} = \frac{V_{th}C_1}{I_{1A}} + \frac{V_{th}C_2}{I_{2A}} + 2t_{xing} + 2t_{logic} + 2t_{reset}$$

=  $2\left(\frac{V_{th}C_1}{I_{1A}} + t_{xing} + t_{logic} + t_{reset}\right).$  (2.3.4)

$$T_{period} = \frac{V_{th}C_1}{I_{2A}} + \frac{V_{th}C_2}{I_{1A}} + 2t_{xing} + 2t_{logic} + 2t_{reset}$$

=  $2\left(\frac{V_{th}C_1}{I_{1A}} + t_{xing} + t_{logic} + t_{reset}\right).$  (2.3.5)

In addition to relaxation oscillators in Fig. 2.14 and Fig. 2.16, there are 64 different ways to configure oscillators with the TCAB.

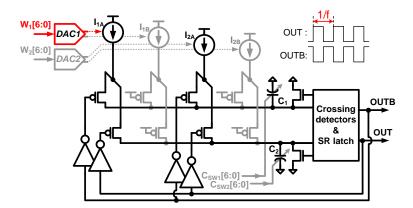

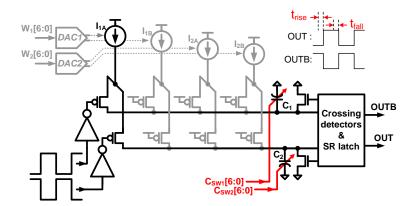

# 2.3.2. Digitally-Controlled Oscillator

Second, a TCAB can operate as a DCO when it is configured as shown in Fig. 2.17. The TCAB is configured so that the one of two output pulses, OUT, is fed to two inputs, IN[1] and IN[5], and the other, OUTB, is connected to other two inputs

Fig. 2.17 The TCAB configuration as a DCO.

Fig. 2.18 Timing diagram of the TCAB when configured as a DCO.

*IN*[0] and *IN*[4], in order to conduct both  $I_{1A}$  and  $I_{2A}$ . Similar to the configuration of the TCAB as a relaxation oscillator, the current  $I_{1A}$  and  $I_{2A}$  are always fully steered to one of the two capacitors and alternately charge  $C_1$  and  $C_2$ . The timing diagram of this operation is presented in Fig. 2.18, where the relative magnitude of current and oscillation frequency difference are shown. When  $W_1$ [6:0] increases,  $I_{1A}$  increases via the DAC1. Then, each capacitor gets charged faster, increasing output pulse frequency. Assuming  $t_{xing}$ ,  $t_{logic}$ , and  $t_{reset}$  are relatively small amount compared with charging time of the capacitors and the capacitances of  $C_1$  and  $C_2$  have same value, then output frequency of the TCAB,  $f_{osc}$ , is given by Eq. (2.3.6), as a linear function of input digital code  $W_1$ [6:0].

$$f_{osc} = \frac{1}{\frac{V_{th}C_{1}}{I_{1A} + I_{2A}} + \frac{V_{th}C_{2}}{I_{1A} + I_{2A}} + 2(t_{xing} + t_{logic} + t_{reset})}$$

$$\approx \frac{I_{1A} + I_{2A}}{2V_{th}C_{1}} = \frac{k \times W_{1} + I_{2A}}{2V_{th}C_{1}},$$

(2.3.6)

where k is gain from DAC input to  $I_{1A}$  (i.e., current change per unit change in the input code,  $\Delta I_{1A}/\Delta W_1$ ). The minimum frequency of this DCO is mainly determined as  $I_{2A}/2V_{th}C_1$  and its gain (i.e., frequency change per unit change in the input code,  $\Delta f_{osc}/\Delta W_1$ ) is  $k/2V_{th}C_1$ .

It is also possible to program different DCOs with different configurations of the TCAB. Fig. 2.19 shows additional six examples that the TCAB operates as DCO. The described basic operation is maintained same, the only difference is the equations that present  $f_{osc}$ . For example, the configured DCO in Fig. 2.19 (a) has the same connection when output pulses are fed back to switch control signals. However,

Fig. 2.19 The TCAB configurations as different DCOs.

its frequency is controlled via  $W_2[6:0]$ , not  $W_1[6:0]$ . Therefore,  $f_{osc}$  of the DCO in Fig. 2.19 (a) is determined as Eq. (2.3.7), a function of  $W_2[6:0]$ .

$$f_{osc} \cong \frac{I_{1A} + I_{2A}}{2V_{th}C_1} = \frac{k \times W_2 + I_{1A}}{2V_{th}C_1}.$$

(2.3.7)

In Fig. 2.19 (b), *OUT* and *OUTB* are connected back to IN[3],[5] and IN[2],[4], respectively. Then,  $f_{osc}$  is determined by Eq. (2.3.8).

$$f_{osc} \cong \frac{I_{1B} + I_{2A}}{2V_{th}C_1} = \frac{k \times (127 - W_1) + I_{2A}}{2V_{th}C_1}.$$

(2.3.8)

That is,  $f_{osc}$  increases when  $W_1[6:0]$  decreases and the opposite happens when  $W_1[6:0]$  increases. The DCOs in Fig. 2.19 (c) and (d) have the very similar that of Fig. 2.17 with the only difference in the minimum frequency.  $f_{osc}$  of the DCOs in Fig. 2.19 (c) and (d) is given by Eq. (2.3.9) and Eq. (2.3.10), respectively.

$$f_{osc} \approx \frac{I_{1A} + I_{2B}}{2V_{th}C_1} = \frac{k \times W_1 + I_{2B}}{2V_{th}C_1},$$

(2.3.9)

$$f_{osc} \cong \frac{I_{1A} + I_{2A} + I_{2B}}{2V_{th}C_1} = \frac{k \times W_1 + I_{2A} + I_{2B}}{2V_{th}C_1}.$$

(2.3.10)

Also,  $f_{osc}$  of the DCOs in Fig. 2.19 (e) and (f) is given by Eq. (2.3.11) and Eq. (2.3.12), respectively, each as a function of  $W_2[6:0]$ .

$$f_{osc} \cong \frac{I_{1B} + I_{2A}}{2V_{th}C_1} = \frac{k \times W_2 + I_{1B}}{2V_{th}C_1},$$

(2.3.11)

$$f_{osc} \cong \frac{I_{1A} + I_{1B} + I_{2A}}{2V_{th}C_1} = \frac{k \times W_2 + I_{1A} + I_{1B}}{2V_{th}C_1}.$$

(2.3.12)

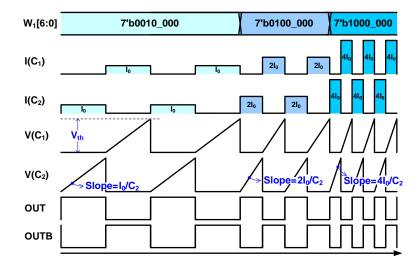

# 2.3.3. Digital Pulse-Width Modulator

Third, a TCAB configured similar to relaxation oscillator in Fig. 2.14 can also operate as a DPWM [24] as shown in Fig. 2.20. The only difference is that the

Fig. 2.20 The TCAB configuration as a DPWM.

Fig. 2.21 Timing diagram of the TCAB when configured as a DPWM.

capacitances of  $C_1$  and  $C_2$  are adjusted in a complementary fashion through  $C_{SW1}$ [6:0] and  $C_{SW2}$ [6:0] instead of adjusting charging current, respectively, maintaining the sum of those two digital input code as 127. Then, the TCAB exhibits same behavior as that of relaxation oscillator, as shown in timing diagram of Fig. 2.21, where the relative capacitance and time difference are shown. Its oscillation period given by Eq. (2.2.3) and duty-cycle of output pulse, *OUT*, follows Eq. (2.3.13).

$$D = \frac{T_{on}}{T_{period}}$$

$$= \frac{\frac{V_{th}C_{2}}{I_{1A}} + t_{xing} + t_{logic} + t_{reset}}{\frac{V_{th}C_{1}}{I_{1A}} + \frac{V_{th}C_{2}}{I_{1A}} + 2(t_{xing} + t_{logic} + t_{reset})}$$

$$= \frac{\frac{V_{th}(C_{0} + C_{sw2} \times C_{step})}{I_{1A}} + t_{xing} + t_{logic} + t_{reset}}{I_{la}}$$

$$= \frac{\frac{V_{th}(2 \times C_{0} + 127 \times C_{step})}{I_{1A}} + 2(t_{xing} + t_{logic} + t_{reset})}{I_{1A}}$$

$$\approx \frac{C_{0} + C_{sw2} \times C_{step}}{2 \times C_{0} + 127 \times C_{step}}.$$

(2.3.13)

That is, its duty-cycle is adjusted as a linear function of  $C_{SW2}[6:0]$ . If it is carefully designed so that  $C_0$  and the three kinds of delay,  $t_{xing}$ ,  $t_{logic}$ , and  $t_{reset}$ , are relatively small compared to  $127C_{step}$  and charging time of the capacitors, respectively, the configured DPWM covers wide range of duty-cycle.

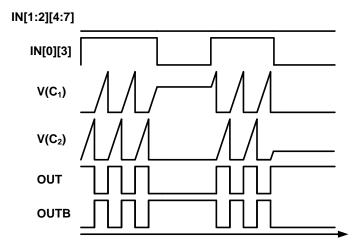

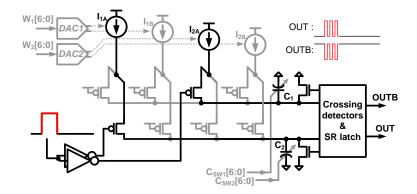

# 2.3.4. Gated Oscillator

Fourth, the TCAB is a gated oscillator as in Fig. 2.22. In this case, an external input is connected to the input switches so that the circuit oscillates only when the input is high. This operation is illustrated with timing diagram in Fig. 2.23. The number of edge transitions in the output pulses is proportional to the pulse width of

Fig. 2.22 The TCAB configuration as a gated oscillator.

Fig. 2.23 Timing diagram of the TCAB when configured as a gated-oscillator.

the input. Therefore, one can comprise a TDC [25], [26] with this TCAB followed by a counter. The counter records the number of edge transitions in the output pulse of gated oscillator, which directly relates to the on-time of the input pulse. That is, the output of counter, which is digital in nature, provides a quantized estimate of input pulse-width. The gated oscillator configured with the proposed TCAB can also hold its intermediate state similar to the case of [25]. As a result, the TDC achieves first order noise shaping.

# 2.3.5. Digitally-Controlled Delay Cell

Next, the TCAB can serve as a digitally-controlled delay cell as in Fig. 2.24. A pair of complementary input signals are connected to IN[1:0] and steers the current  $I_{1A}$  between  $C_1$  and  $C_2$ . In this configuration, only  $C_1$  gets charged if IN[0] is high and the other,  $C_2$ , gets charged if IN[1] is high, as shown in Fig. 2.25. Therefore, the outputs do not oscillate but toggle only once whenever the two inputs toggle with

Fig. 2.24 The TCAB configuration as a digitally-controlled delay cell.

Fig. 2.25 Timing diagram of the TCAB when configured as a digitally-controlled delay cell.

rising or falling delay given by

$$t_{rise} = \frac{V_{th}C_1}{I_{1A}} + t_{xing} + t_{logic}, \ t_{fall} = \frac{V_{th}C_2}{I_{1A}} + t_{xing} + t_{logic}.$$

(2.3.14)

By adjusting  $C_{SW1}[6:0]$  and  $C_{SW2}[6:0]$ , delay can be controlled linearly as a function of the two digital input codes.

### 2.3.6. Phase Interpolator

Lastly, the TCAB operates as a phase interpolator (PI) when two pairs of complementary input signals steer the current  $I_{1A}$  and  $I_{1B}$ , respectively, as shown in Fig. 2.26.

Its operating timing diagram is given in Fig. 2.27. If the rising edge of *CLK*1 arrives earlier than that of *CLK*2, the capacitor  $C_1$  is charged by the current source  $I_{1A}$  for the time period when only *CLK*1 is high. Then, voltage across  $C_1$  at  $t_2$  when the rising edge of *CLK*2 arrives is given by

$$V_{C1}(t_2) = \frac{I_{1A}}{C_1}(t_2 - t_1) = \frac{I_{1A}}{C_1}(\phi_{CLK2} - \phi_{CLK1}) \times \frac{1}{2\pi f},$$

(2.3.15)

where  $\phi_{CLK1}$  and  $\phi_{CLK2}$  denotes phase of *CLK*1 and *CLK*2, respectively, and *f* is frequency of *CLK*1 and *CLK*2. Once *CLK*2 rises, *C*<sub>1</sub> is charged with the current amount of  $I_{1A}+I_{1B}$ . Then, the time it takes for *C*<sub>1</sub> to reach the threshold voltage of the ensuing crossing detector, *V*<sub>th</sub>, since *t*<sub>2</sub> is given by

$$t_{out} - t_2 = \left( V_{th} - \frac{I_{1A}}{C_1} (\phi_{CLK2} - \phi_{CLK1}) \times \frac{1}{2\pi f} \right) \times \frac{C_1}{I_{1A} + I_{1B}}.$$

(2.3.16)

That is, if the phase of *CLK*1 is earlier than that of *CLK*2 so that  $\phi_{CLK1}$  is smaller than  $\phi_{CLK2}$ , the output phase,  $\phi_{OUT}$ , is given by

$$\phi_{OUT} = \phi_{CLK2} + (t_{out} - t_2) \times 2\pi f$$

=  $\phi_{CLK2} + 2\pi f \frac{CV_{th}}{I_{1A} + I_{2B}} - (\phi_{CLK2} - \phi_{CLK1}) \frac{I_{1A}}{I_{1A} + I_{1B}}.$  (2.3.17)

As  $W_1[6:0]$  increases,  $\phi_{OUT}$  gets earlier since  $I_{1A}$  increases, whereas  $I_{1A}+I_{1B}$  maintains

same. For the falling transition out *OUT*, the same behavior occurs when rising edge of *CLK1B* and *CLK2B* arrive, charging  $C_2$ . As a result, the circuit generates a delay which is a weighted sum of the delays from the two input pairs with different arrival time [27], [28].

Fig. 2.26 The TCAB configuration as a phase interpolator.

Fig. 2.27 Timing diagram of the TCAB when configured as a phase interpolator.

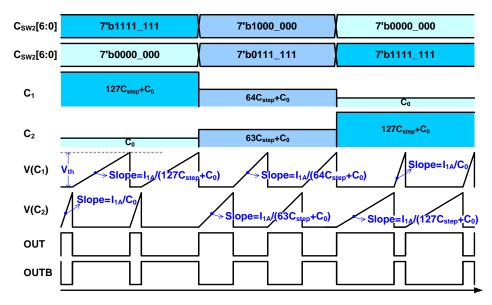

## 2.3.7. Multiphase DCO

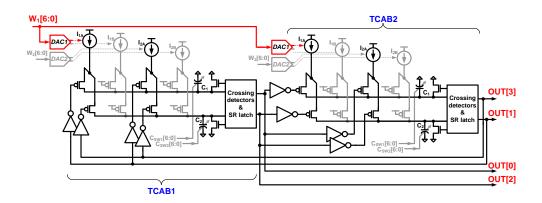

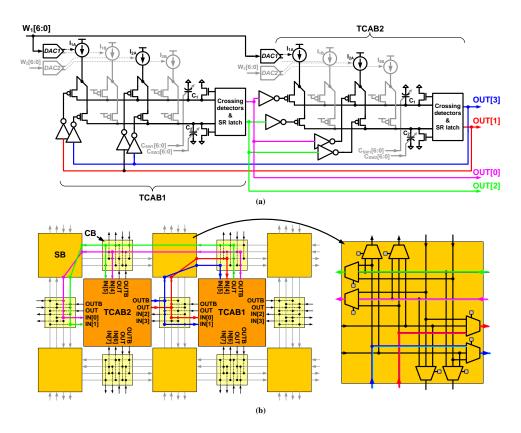

As an example to show that more than two TCABs are configured to operate as a time-domain analog block, Fig. 2.28 presents an example that the two TCABs are combined together in order to operate as a four phase DCO whose four output pulses have 90 degree space. *OUT* and *OUTB* of TCAB1 are connected to IN[1][5] and IN[0][4] of TCAB2, respectively. Likewise, *OUT* and *OUTB* of TCAB2 are connected to IN[1][5] and IN[0][4] of TCAB2, respectively. Likewise, *OUT* and *OUTB* of TCAB2 are connected to IN[1][5] and IN[0][4] of TCAB1, respectively. Those two TCABs have common input digital code word  $W_1[6:0]$ . Once  $C_1$  in TCAB1 is charged and reaches  $V_{th}$  of the ensuing crossing detector, OUT[2] (i.e., OUT of TCAB1) is asserted and OUT[0] (i.e., OUTB of TCAB1) toggles to zero. Then,  $C_2$  in TCAB2 takes turn being charged and OUT[3] is asserted and OUT[1] toggles to zero. In this way, a total of the four capacitors in the two TCABs are alternately charged in sequence of  $C_1$  in TCAB1,  $C_2$  in TCAB2,  $C_2$  in TCAB1,  $C_1$  in TCAB2,  $C_1$  in TCAB1, ..., and then 4 output pulses are generated. This sequence is illustrated with timing diagram

Fig. 2.28 The TCABs configuration as a multiphase (4-phase) DCO.

Fig. 2.29 Timing diagram for the operation of the TCABs as a multiphase DCO.

in Fig. 2.29.

Its oscillating frequency can be controlled by adjusting charging current  $I_{1A}$  both in TCAB1 and TCAB2 via  $W_1$ [6:0]. That is, if capacitors in the two TCABs are programmed to have equal capacitances and both  $I_{2A}$  are configured to flow same amount of current, its oscillating frequency  $f_{osc}$  is given by

$$f_{osc} = \frac{1}{\frac{4V_{ih}C_{1}}{I_{1A} + I_{2A}}} + 4\left(t_{xing} + t_{logic} + t_{reset}\right) \cong \frac{I_{1A} + I_{2A}}{4V_{ih}C_{1}} = \frac{k \times W_{1} + I_{2A}}{4V_{ih}C_{1}}, \quad (2.3.18)$$

In general, 2*N* phase DCO can be programmed by configuring *N* TCABs in a similar way of Fig. 2.28

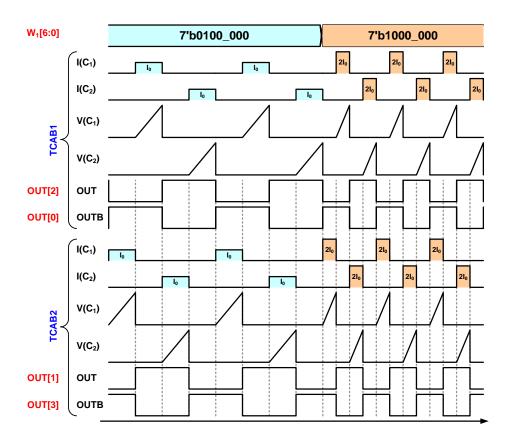

#### 2.3.8. Non-overlapping Pulse Generator

Another example in Fig. 2.30 shows that the two TCABs are combined together in order to generate non-overlapping pulses. Each TCAB receives the common pulse input and operates as a digitally-controlled delay cell described earlier in Fig. 2.24. In this time,  $C_{SW1}$ [6:0] and  $C_{SW2}$ [6:0] of each TCAB are programmed with constants so that  $C_{SW1}$ [6:0] of TCAB1 is larger than that of TCAB2 and  $C_{SW2}$ [6:0] of TCAB2 is

Fig. 2.30 The TCABs configuration as a non-overlapping pulse generator.

Fig. 2.31 Timing diagram for the operation of the TCABs as a non-overlapping pulse generator.

smaller than that of TCAB2. Then, OUT2 is always asserted earlier than OUT1 and OUT1B is always asserted earlier than OUT1B as shown in timing diagram (Fig. 2.31). Their timing difference is expressed as:

$$t_{rise1-rise2} = t_{fall2-fall1} = \frac{V_{th}C_{1,1}}{I_{1A}} - \frac{V_{th}C_{2,1}}{I_{1A}}.$$

(2.3.19)

As a result, among the four output signals, *OUT*1 and *OUT*2*B* become the final output pulses that have no time period of being turned on simultaneously.

# 2.4 TCAB Array

# with Programmable Interconnects

This subchapter describes how multiple TCABs are assembled in an array together with programmable interconnects. The implementation of the programmable interconnects (i.e., connection block and switch block) in the array is also presented.

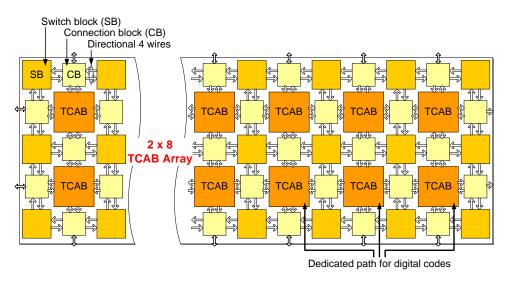

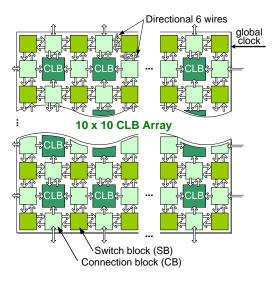

# 2.4.1. TCAB Array Composition

The TCAB array composition follows a traditional 2-D island-style FPGA architecture which is commonly adopted among commercial FPGAs [42], as illustrated in Fig. 2.32. The TCABs are regularly placed on 2-D grid and each TCAB is surrounded by wire tracks and programmable interconnect blocks of switch blocks (SB) and connection blocks (CB). The directional 4 wires are placed in both horizontal and vertical way around each TCAB. Input and output signals of each TCAB are connected the surrounding wire tracks via connection blocks. The adjacent wire tracks are interconnected via switch blocks that are placed at the intersection of horizontal and vertical tracks.

Fig. 2.32 Composition of the TCAB array.

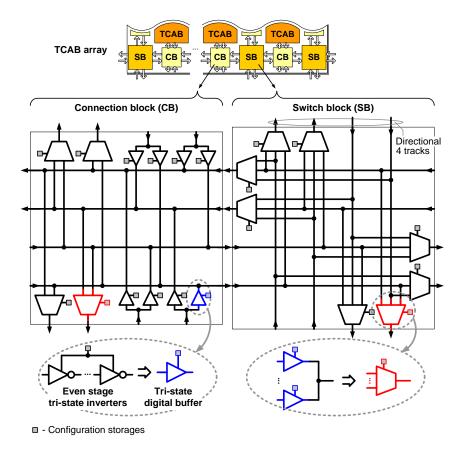

# 2.4.2. Programmable interconnects

As the TCABs receive and produce digital pulses, both switch block and connection block in the TCAB array are simply implemented based on digital tristate inverters, as shown in Fig. 2.33. Therefore, highly programmable connectivity comparable to that of digital FPGAs is achieved.

Depending on which tri-state inverters are turned on, the connection block decides which routing wires to be connected to the input and output signals of the TCABs, Likewise, the tri-state inverters in switch blocks decide the received signals to go forward, left or right. The architecture of switch blocks follows that of [43] in order to provide higher flexibility in interconnect than other architectures. This programmable routing architecture with connection blocks and switch blocks

Fig. 2.33 Implementation of the programmable interconnects in the TCAB array.

follows that of commercial FPGAs [42] so that the TCAB array facilitates high programmability on signal path.

Among input and output signals of TCAB, only input pulses (i.e., *IN*[7:0]) and output pulses (i.e., *OUT* and *OUTB*) are conveyed through the described programmable interconnects. In specific, a single TCAB receives 8 input pulses from four-sided adjacent connection blocks. Two output pulses, *OUT* and *OUTB*, of each TCAB can be connected to its all the four adjacent connection blocks.

The other input signals (i.e., digital codes -  $W_1$ [6:0],  $W_2$ [6:0],  $C_{SW1}$ [6:0], and  $C_{SW2}$ [6:0]) are either programmed with fixed constants or directly connected to output of ALU array. The former case is when the TCAB is programmed to a fixed-frequency oscillator, fixed-frequency gated oscillator, or fixed-delay cell whose frequency or delay does not have to change during run time. On the other hand, the latter case is when the TCAB is programmed to a DCO, DPWM, digitally-controlled delay cell, or phase interpolator whose output frequency, duty, delay or phase is controlled by input digital codes in real time. In most cases of mixed-signal systems, the input digital codes of an analog block are either results of digital filters or digital codes, three TCABs in the lower left corner of the TCAB array have dedicated signal path as shown earlier in Fig. 2.32. As described in Chapter 3, the digital code words are from the adjacent array of arithmetic logic units (ALUs).

To illustrate how the signals are propagated via the programmable interconnects within the TCAB array, Fig. 2.34 (b) shows a single TCAB and its adjacent connection box are utilized to configure the relaxation oscillator in Fig. 2.34 (a). First, *OUT* and *OUTB* of the TCAB are connected to the right connection box. Then, IN[2] and IN[3] can be connected to *OUTB* and *OUT*, respectively, via the right connection box. The other input pulse signals IN[1:0], [7:4], and  $W_1[6:0]$  are not connected to any connection box, being tied to ground by the multiplexers (not shown in the figure, refer Fig. 2.13). Likewise,  $W_2[6:0]$ ,  $C_{SW1}[6:0]$ , and  $C_{SW2}[6:0]$  are connected to the proper constants, which is programmed by users, for the intended operating frequency.

Fig. 2.34 Example of programmable signal path in the TCAB array to configure a single TCAB as the relaxation oscillator.

Fig. 2.35 also illustrates the case when two TCABs and their adjacent connection boxes and switch boxes are utilized to configure a four phase DCO. First *OUT* and *OUTB* of TCAB1 are connected to its upper wire tracks via connection box. Then, the left switch box passes the signals to its left connection box which connects the carried signals to *IN*[4:5] of TCAB2. The leftmost switch box passes *OUT* and

Fig. 2.35 Example of programmable signal path in the TCAB array to configure two TCABs as the four phase DCO.

*OUTB* of TCAB1 to lower connection box, which is left to TCAB2. Finally, *IN*[0:1] of TCAB2 are also connected. In this manner, *OUT* and *OUTB* of TCAB2 are also connected to *IN*[1][5] and *IN*[0][4] of TCAB1, respectively.

# Chapter 3

# Proposed Architecture for Field-Programmable Mixed-Signal IC

Before introducing the proposed architecture, the architectural features of various mixed-signal systems are briefly reviewed. Today's integrated systems consist of tightly coupled analog circuits and digital logic blocks. In most cases, the digital blocks are included to perform a variety of adaptation or calibration and closely interact with analog blocks [29]-[31]. Also, as technology scales, digitally-assisted analog design techniques [32]-[35] have been widely used to overcome the difficulties in design of analog circuits (e.g., matching, non-linearity, gate leakage or low supply voltage) by replacing a few analog circuits with digital ones or relaxing non-ideality effect of analog circuits with digital calibration engine. Specifically, it is usual in feedback systems to adopt the topology consisting of analog sensor, digital controller, and analog actuator. For example, digital PLLs are composed of TDC, digital loop filter, and DCO [27], [36]-[38]. This mixed-signal feedback

structure is also utilized when implementing DC-DC converters with ADC, digital loop filter, and DPWM [24], [39]-[41].

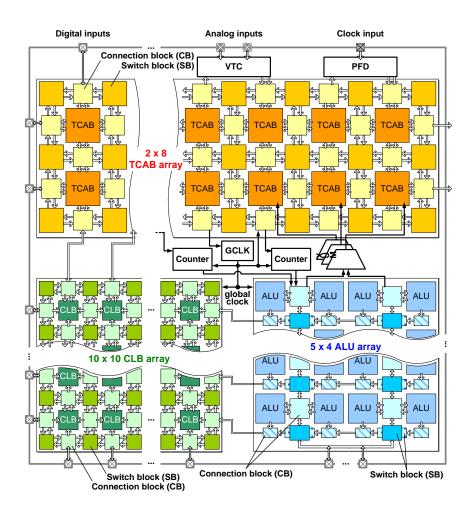

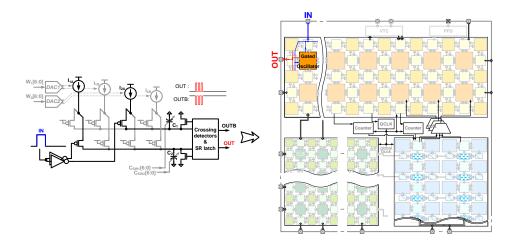

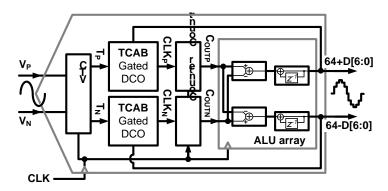

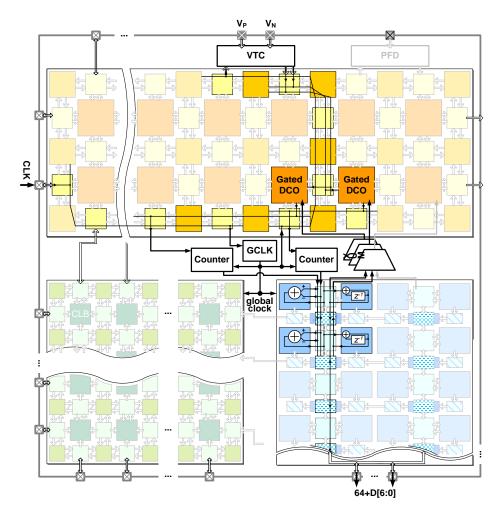

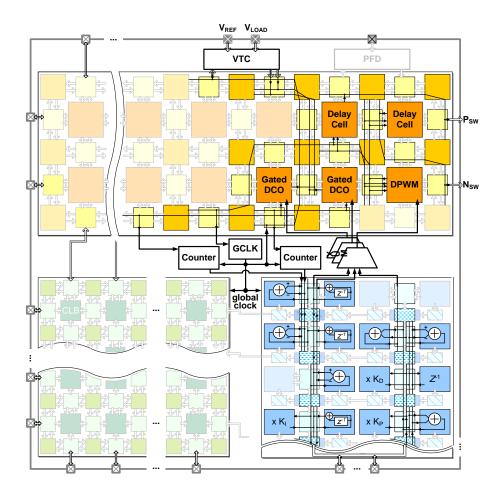

In order to program such mixed-signal feedback systems or digitally-assisted analog systems, the proposed IC has the architecture as illustrated in Fig. 3.1 [18].

Fig. 3.1. Architecture and floorplan of the proposed field-programmable mixed-signal IC.

The IC largely consists of three arrays of TCABs, configurable logic blocks (CLBs), and programmable arithmetic logic units (ALUs). In each array, the TCABs, CLBs, or ALUs are placed regularly and surrounded by tracks of wires and programmable interconnects (i.e., connection blocks and switch blocks). It also includes gluing blocks such as a voltage-to-time converter block (VTC), phase-frequency detector block (PFD), and counter block to interface among the three arrays or between an array and I/O.

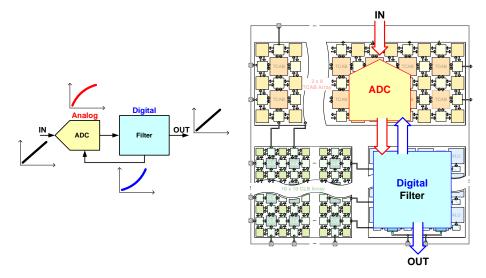

Various analog/mixed-signal feedback systems can be programmed on the proposed IC by mapping their analog sensors and actuators to TCABs and digital controllers to ALUs or CLBs, as shown in Fig. 3.2. That is, users change input-to-output function of each TCAB to perform the function of analog blocks required in the intended system. Then, Boolean logic required in the system is programmed on the array of the CLBs, each of which is basically a programmable look-up table (LUT). Lastly, digital arithmetic logic is programmed on the IC by programming each ALU to perform one of arithmetic operation among addition, subtraction, accumulation, and arithmetic shift. For instance, one can program a digital PLL on the IC by configuring TCABs to operate as TDC and DCO and programming digital loop filter to ALUs. Then, CLBs are programmed to lock detection logic which detects whether the PLL is locked, observing the loop condition. Similarly, it is also possible to configure DC-DC converter on the IC by programming ADC and DPWM on TCABs and mapping digital filter on ALUs.

Likewise, Fig. 3.3 illustrates how the digitally-assisted analog systems can be programmed on the proposed IC, configuring analog function on the TCABs and programming digital calibration engine on the ALUs or CLBs.

Fig. 3.3 Programming of the digitally-assisted analog systems on the proposed IC.

# **Chapter 4**

# **Circuit Implementation**

In addition to the array of the TCABs for programmable analog function, the proposed field-programmable IC also includes the other two arrays of configurable logic blocks (CLBs) and arithmetic logic units (ALUs) for programmable digital function and interfacing blocks at the boundary of each array of the programmable blocks as described in Chapter 3. Their role and circuit implementation are presented in following subchapters. Lastly, the method to program the whole chip based on scan chain is also presented.

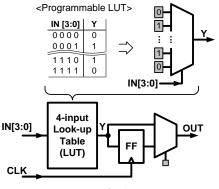

# 4.1 Configurable Logic Block Array

#### 4.1.1. Configurable Logic Block

In order to program arbitrary digital logics required in the intended mixed-signal systems, the IC contains configurable logic blocks (CLBs) based on look-up table (LUT). Each CLB consists of a programmable LUT whose output is connected to D flip-flop followed by a multiplexer to select the final output of CLB between output of LUT and output of D flip-flop, as shown in Fig. 4.1. The size of the included LUT is determined as 4 inputs and 16 rows, considering the trade-off between area and delay when multiple CLBs compose the array [44]. Therefore, a single CLB is capable of implementing any Boolean logic with 4 inputs depending on how the LUT is programmed. Then, the programmed logic becomes either combinational or sequential according to selection of the multiplexer. For the sequential logic, the

Configuration storages

Fig. 4.1 Circuit implementation of the CLB.

CLBs also receive a common triggering clock of D flip-flop which transmitted from GCLK block. The more complex logic with more than 4 inputs is implemented by combining multiple CLBs.

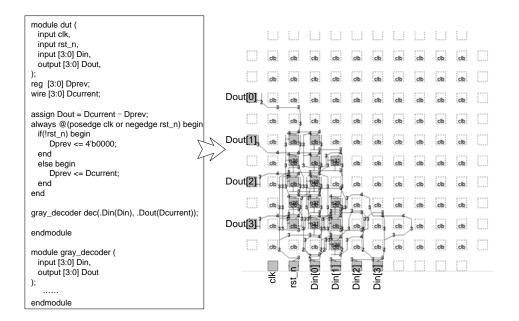

## 4.1.2. CLB Array

The multiple CLBs  $(10 \times 10)$  are grouped in the array together with connection blocks and switch blocks, following 2-D island-style like the TCAB array. The overall array composition is illustrated in Fig. 4.2. The only difference between the ALU array and TCAB array is the number of wires in a wire track. That is, the CLB array has 6 wires for each wire track, whereas the TCAB array has 4 for each track. The connection blocks and switch blocks in the CLB array are implemented with digital tri-state inverters like those in the TCAB array. Each CLB receives each digit

Fig. 4.2 CLB array composition with programmable interconnects.

of 4-bit input from 4-sided adjacent connection blocks and transmits output only to the upper side connection block.

The arbitrary digital logic written in hardware description language (e.g., Verilog) is synthesized and P&R (Place-and-route) onto the CLB array is performed, utilizing an open-source academic software suite, VTR [45]-[47]. Fig. 4.3 shows the visualized results of VTR after it synthesizes and performs P&R of a logic block including 4-bit Gray decoder which is written in Verilog.

Fig. 4.3 Exemplary VTR results of Verilog module including 4-bit Gray decoder (input: low side ports, output: right side ports).

# 4.2 Arithmetic Logic Unit Array

In addition to CLBs for programming Boolean logic, the proposed IC also contains programmable arithmetic logic units (ALUs) as additional programmable digital resource. Although the CLB array alone can afford to be programmed to any combinational or sequential logic including arithmetic logic, ALU array is additionally employed to reduce the overhead in area, performance degradation or wasting of CLBs that can occur when performing digital arithmetic operation only with LUT based CLB array. This is a similar strategy of many modern FPGAs that contain specific purpose blocks such as memory, adders, multipliers or DSP blocks [3], [4], [48]. In case of this work, ALU array is in charge of arithmetic such as addition, subtraction, or arithmetic shift. Therefore, digital filters in mixed-signal feedback systems can be programmed onto the ALU array with higher logic density and shorter critical path delay.

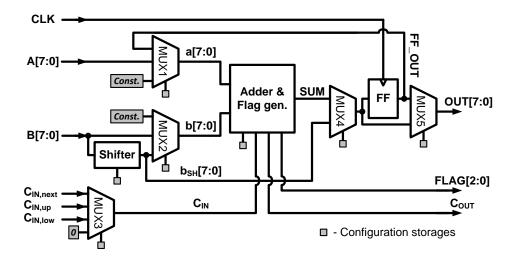

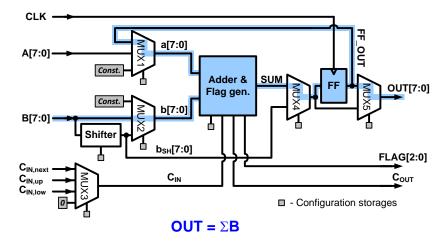

### 4.2.1. Arithmetic Logic Unit

As illustrated in Fig. 4.4, each ALU includes an adder capable both of addition and subtraction, shifter, flip-flop, and five multiplexers, receiving up to two 8-bit operands and producing an 8-bit operation result and flag signals. Arithmetic flags are produced as subsidiary results in every ALU. For instance, the flag bits indicate which one is larger between two operands of the adder or whether those two are same.

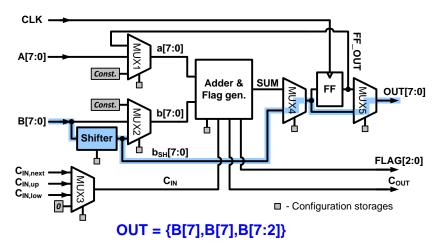

Fig. 4.4 Circuit implementation of the ALU.

It performs arithmetic operations such as addition, subtraction, accumulation, or arithmetic shift depending on how it is programmed. For example, an ALU is configured as an accumulator that accumulates input B[7:0] if the included adder is programmed to perform addition and MUX1 through MUX5 are programmed to select *FF\_OUT*, *B*[7:0], 0, *SUM*, and the output of MUX4, respectively, as shown in Fig. 4.5. Fig. 4.6 also shows that the ALU is programmed as a arithmetic shifter that shifts *B*[7:0] to the right in amount of 2 bits, extending sign bit. For this configuration, the shifter in the ALU is programmed to perform right-shift and MUX4 and MUX5 are programmed to select *b*<sub>SH</sub>[7:0] and the output of MUX4, respectively.

Fig. 4.5 ALU configuration as an accumulator.

Fig. 4.6 ALU configuration as an arithmetic shifter.

The ALUs are also capable of supporting wider bit-width operands. Adjacent two or three ALUs are extended to 16-bit or 24-bit ALU, exchanging carries each other. In order to facilitate bit-expanded configuration, a single ALU receives carry bits from its upper, lower, or next ALU.

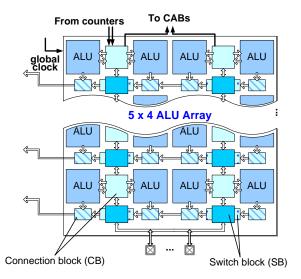

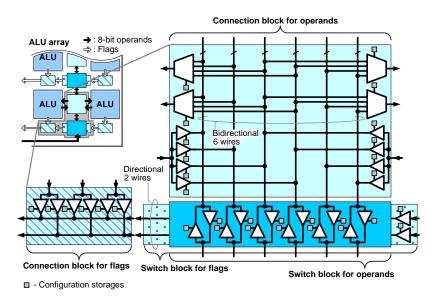

# 4.2.2. ALU Array

The ALU array is composed of 20 (5  $\times$  4) programmable ALUs and two different sets of programmable interconnects, as illustrated in Fig. 4.7. Whereas the 8-bit operands or results are conveyed through vertical wire tracks, the resulting flags are conveyed through horizontal wire tracks and eventually transferred to CLB array, as shown in Fig. 4.8. Like those in TCAB array or CLB array, connection blocks and switch blocks in the ALU array are implemented with tri-state inverters. Especially, each wire track for operands is bidirectional so that the wire tracks can convey the signals either up or down. The ALU array can receive 8-bit input operands from counter blocks or external and feed its final results into the TCAB array or transmit them to the external.

Fig. 4.7 ALU array composition.

Fig. 4.8 ALU array composition with programmable interconnects.

# 4.3 Interfacing Blocks

The described three arrays of programmable function blocks (i.e., TCAB array, CLB array, and ALU array) interact with external I/O or with each other at the array boundary through not only direct connections but also gluing blocks, as illustrated earlier in Fig. 3.1. Due to the fact that not only the digital programmable blocks, CLBs and ALUs, but also the analog programmable blocks, TCABs, receive and produce binary digital signals, it is possible to implement IC only with direct connection among the three arrays. However, if the IC only includes the three arrays of configurable units, input signal type of the IC is limited to digital pulse or binary digits which TCABs, CLBs, and ALUs can take as input signal. By employing interfacing blocks that convert external signals to pulse-width modulated signals, the IC can take various external analog signals as input. For example, voltage-to-time converter (VTC) converts voltage magnitude to time-domain pulse-widths and phase frequency detector (PFD) converts clock phase or frequency difference between two inputs to pulse-widths. Similarly, counter block converts time-domain pulse into 8bit binary digits when signals are transferred from TCAB array to ALU array. Lastly, global clock unit (GCLK) distributes clock with optional frequency division. The remainder of this subchapter describes circuit implementation of VTC, PFD, and counter block. In addition, description of time-to-voltage converter (TVC) is also introduced as an inverse of VTC.

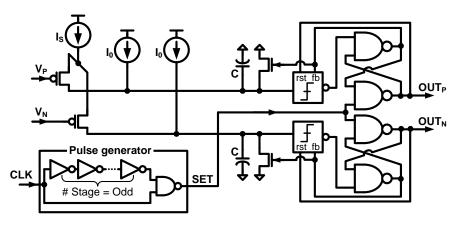

### 4.3.1. Voltage-to-Time Converter

The VTC which is adopted to take an external voltage as input of the IC is implemented and behaves in similar way of TCAB, as shown in Fig. 4.9. The VTC is composed of a current source,  $I_S$ , whose output current is steered by a pair of pMOS, the other two current sources that directly charge following capacitor, reset switches for the capacitors, two pairs of crossing detector and SR latch, and a pulse generator that sets the SR latches. Once *CLK* is asserted, the pulse generator makes short pulse, *SET*, to make both two SR-latch outputs, *OUT<sub>P</sub>* and *OUT<sub>N</sub>*, high and release reset switches beside capacitors. Then, the current sources start charging the capacitors. Particularly,  $I_S$  is steered by the difference between the input voltages,  $V_P$ and  $V_N$ . Therefore, the time which it takes for each output to make falling transition (i.e., pulse-width of output) since the corresponding capacitor starts being charged is given by

Fig. 4.9 Circuit implementation of the VTC.

$$T_{on,P} = \frac{CV_{th}}{I_0 + I_S + g_m (V_P - V_N)} + t_{xing} + t_{logic},$$

$$T_{on,N} = \frac{CV_{th}}{I_0 + I_S - g_m (V_P - V_N)} + t_{xing} + t_{logic},$$

(4.3.1)