### 저작자표시-비영리-변경금지 2.0 대한민국

## 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

## 공학박사 학위논문

# Direct Cu Deposition on Ru and Co/Ni Alloy Barrier Layer for the Next-generation Cu Damascene Process

차세대 구리 상감 공정을 위한 루테늄 및 코발트/ 니켈 합금 확산 방지막 상 직접 구리 도금

2016년 2월

서울대학교 대학원 화학생물공학부 김 광 환

## Direct Cu Deposition on Ru and Co/Ni Alloy Barrier Layer for the Next-generation Cu Damascene Process

차세대 구리 상감 공정을 위한 루테늄 및 코발트/ 니켈 합금 확산 방지막 상 직접 구리 도금

지도교수 김 재 정

이 논문을 공학박사 학위논문으로 제출함 2015년 11월

서울대학교 대학원 화학생물공학부 김 광 환

김광환의 공학박사 학위논문을 인준함 2015년 12월

| 위  | 원 장   | (인) |

|----|-------|-----|

| 부유 | 위 원 장 | (인) |

| 위  | 원     | (인) |

| 위  | 원     | (인) |

| 위  | 원     | (인) |

## **ABSTRACT**

In semiconductor manufacturing history, the transition of conducting material from Al to Cu was considered one of the most significant changes. Such replacement is accompanied with the introduction of damascene process, which proceeds first by deposition and patterning of the dielectric layer. Then the patterned dielectric is covered with diffusion barrier layer and Cu seed layer. Subsequently, Cu is filled by superfilling techniques, resulting in void-free and seamless filling of trenches and vias with high aspect ratios. Among these steps, the diffusion barrier and Cu seed layer are formed by physical vapor deposition. However, the problem induced by the poor step coverage of the diffusion barrier/Cu seed layer has become serious as trenches are being reduced. Therefore, different deposition methods such as chemical vapor deposition, atomic layer deposition, electroless deposition, and direct electrodeposition are considered as alternatives to physical vapor deposition for the formation of the barrier/seed layer. Specifically, electroless deposition and direct electrodeposition have received much interest due to their various advantages.

In this study, the entire metallization processes were modified for the next-generation interconnect fabrication. On Ta barrier layer, direct Cu electrodeposition was developed using Pd nanoparticles as a Cu nucleation promoter. Pd nanoparticles were synthesized

by a polyol method and loaded onto a pretreated Ta substrate. Through a two-step potentiostatic electrodeposition process in a pyrophosphate-based electrolyte, a continuous Cu seed layer was deposited on the Ta substrate, although the surface showed irregular morphology. The addition of allyl alcohol improved the surface regularity of the Cu seed layer, allowing the conformal Cu seed layer to be formed successfully on the 55 nm patterned Ta substrate. Cu gap-filling was achieved by galvanostatic ED in a sulfate-based electrolyte on the preformed seed layer.

On SiO<sub>2</sub> substrate, electroless deposition of various barrier layers was investigated for all-wet Cu interconnect fabrication. In this study, the entire fabrication process including substrate activation, barrier layer electroless deposition, and direct Cu electrodeposition was modified. The SiO<sub>2</sub> substrate was activated via Pd nanoparticles that were immobilized on the substrate by using a preformed self-assembled monolayer composed of 3-aminopropyl-triethoxysilane. Reduction of barrier layer resistivity was achieved by applying ultrasound during the substrate activation process and by adjusting the composition of the electroless deposition bath. The Cu electrodeposition was performed directly on the electroless barrier layers after performing coulometric oxide reduction, thus improving the adhesion and nucleation density of Cu on the barrier layer. The electrodeposition process was conducted in two steps: Cu nucleation and Cu thin film formation at a high overpotential followed by additional Cu film growth at a low overpotential. As a result, a uniform, smooth Cu film covered the barrier layer. In

addition, bottom-up Cu filling was accomplished on a 120 nm wide, patterned substrate

with a 2.5 aspect ratio. Barrier layer performance was evaluated by using a stacked

specimen formed by applying the proposed procedure.

On Ru substrate which is considered as next-generation barrier material, Cu growth

phenomena were investigated during electroless deposition. Different to the

formaldehyde based bath, the use of hydrazine based bath facilitated the observation of

Cu growth phenomena during the electroless deposition. The whole surface-catalyzed

electroless deposition occurred on Ru, and electrochemical quartz crystal microbalance

as well as linear sweep voltammetry studies revealed that Cu covered Ru surface within a

few seconds of deposition. Measurement of sheet resistance change confirmed that Cu

nucleation on Ru was continuous with forming a film. During the period, Cu film growth

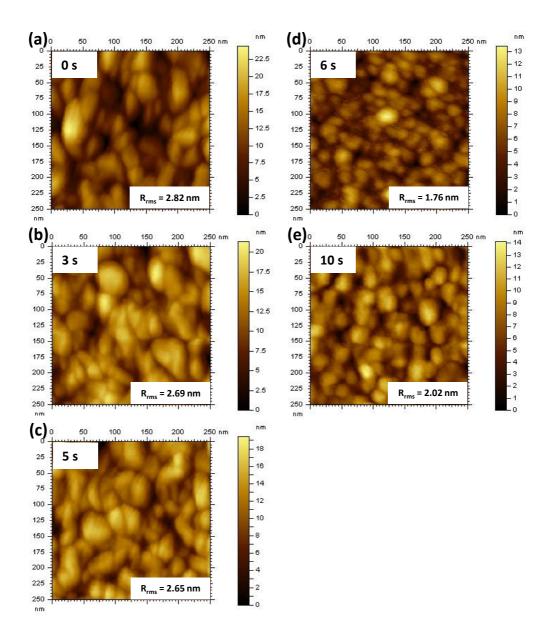

was monitored by an atomic force microscope imaging, indicating that Cu was deposited

on Ru preferentially, rather than on the deposited Cu at the initial stage of the deposition.

The whole surface-catalyzed electroless deposition achieved the 55 nm gap-filling, and

this showed the possibility of the practical adoption of electroless deposition as a method

for metallization in ultralarge-scale integration.

keywords: Cu, direct electrodeposition, electroless deposition, next-generation barrier

layer, all-wet metallization

**Student Number**: 2010-20981

iii

# TABLE OF CONTENTS

| ABSTRACT                                                     | i    |

|--------------------------------------------------------------|------|

| TABLE OF CONTENTS                                            | iv   |

| LIST OF TABLES                                               | vii  |

| LIST OF FIGURES                                              | viii |

| CHAPTER I. Introduction and overview                         | 1    |

| 1.1. The interconnection technology for ULSI                 | 1    |

| 1.1.1. The present and issues of interconnection technology  | 1    |

| 1.1.2. The next-generation interconnection technology        | 4    |

| 1.2. Direct Cu deposition                                    | 12   |

| 1.2.1. Direct Cu ED                                          | 12   |

| 1.2.2. Cu ELD                                                | 13   |

| 1.2.3. Direct Cu ELD                                         | 15   |

| 1.3. All-wet metallization                                   | 19   |

| 1.3.1. Electroless Co/Ni alloy as a barrier/capping material | 19   |

| 1.3.2. All-wet metallization                                 | 23   |

| 1.4. Concepts of the study                                   | 29   |

| CHAPTER II. Experimental                                     | 31   |

| 2.1. Direct ED of Cu on Ta                                   | 31   |

| 2.1.1. Preparation of Pd NPs                                                 | 31 |

|------------------------------------------------------------------------------|----|

| 2.1.2. Direct ED of Cu on Ta                                                 | 32 |

| 2.2. Direct ED of Cu on Co/Ni alloy                                          | 35 |

| 2.2.1. Pretreatment of substrate and SAM-Pd activation                       | 35 |

| 2.2.2. ELD of Co/Ni alloy films and direct Cu ED                             | 36 |

| 2.3. Direct ELD of Cu on Ru                                                  | 38 |

| 2.3.1. Pretreatment of Ru and direct Cu ELD                                  | 38 |

| 2.3.2. Preparation of Ru electrode and EQCM monitoring                       | 39 |

| 2.4. Instrumentation                                                         | 41 |

| CHAPTER III. Direct ED of Cu on Ta                                           | 44 |

| 3.1. Seed layer formation by direct Cu ED on blanket Ta substrate            | 44 |

| 3.1.1. Pd NPs loading on blanket Ta substrate                                | 44 |

| 3.1.2. Cu seed layer formation by direct Cu ED on Pd NPs-loaded Ta substrate | 45 |

| 3.2. Trench filling by direct Cu ED on patterned Ta substrate                | 56 |

| CHAPTER IV. Direct ED of Cu on Co/Ni alloy                                   | 62 |

| 4.1. ELD of Co/Ni alloy barrier layer                                        | 62 |

| 4.1.1. Optimization of substrate activation process                          | 62 |

| 4.1.2. Optimization of barrier layer ELD                                     | 64 |

| 4.2. Direct Cu ED on ELD-barrier layer                                       | 76 |

| 4.3. Barrier layer performance and trench filling                            | 88 |

| 4.3.1. Barrier layer performance investigation                 | 88  |

|----------------------------------------------------------------|-----|

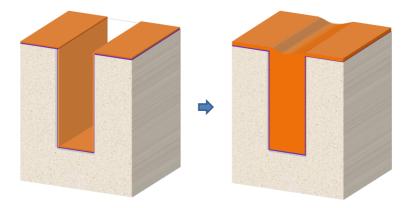

| 4.3.2. Trench filling by all-wet metallization process         | 89  |

| CHAPTER V. Direct ELD of Cu on Ru                              | 97  |

| 5.1. Cu growth phenomena on Ru during ELD                      | 97  |

| 5.1.1. Preparation of Ru electrode for EQCM monitoring         | 97  |

| 5.1.2. Observation of Cu growth phenomena on Ru during ELD     | 98  |

| 5.1.3. Determination of Cu growth phenomena on Ru during ELD   | 103 |

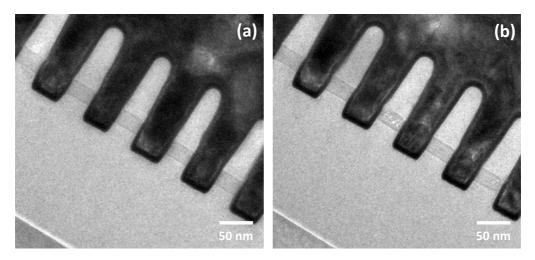

| 5.2. Trench filling by direct Cu ELD on patterned Ru substrate | 117 |

| CHAPTER VI. Conclusions                                        | 120 |

| REFERENCES                                                     | 122 |

| 국무초록                                                           | 133 |

# LIST OF TABLES

| Table 2.1. Composition of ELD Bath for the Deposition of NiWP / CoWP / NiCoP | . 37 |

|------------------------------------------------------------------------------|------|

| Table 4.1. Composition and Properties of Each Barrier Layer                  | . 67 |

| Table 5.1. Calculated Thickness of Deposited Cu on Ru                        | 106  |

# LIST OF FIGURES

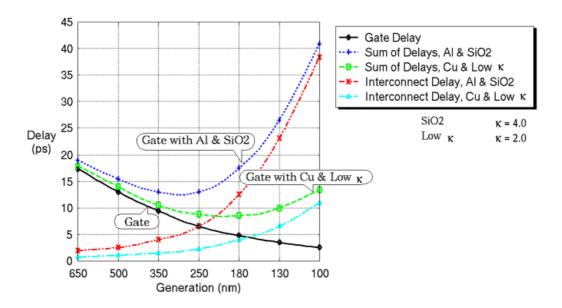

| Figure 1.1. Gate and interconnect delay versus technology generation (edited from ref.  |

|-----------------------------------------------------------------------------------------|

| [3])7                                                                                   |

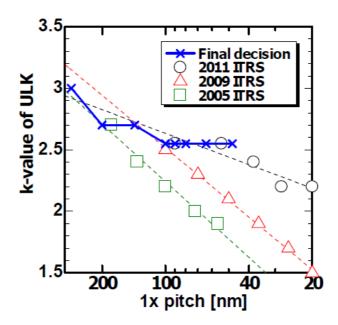

| Figure 1.2. Predictions of ULK roadmap in the ITRS'2005, 2009, and 2011, and the final  |

| decisions of ITRS'2013 (edited from ref. [9])                                           |

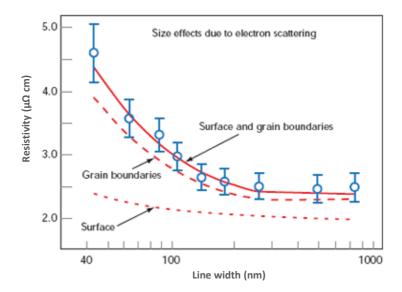

| Figure 1.3. Measured narrow Cu line resistivity (blue circles) versus line width.       |

| Comparisons are depicted with suggested models considering electron                     |

| scattering due to surface and grain boundaries (edited from ref. [16])9                 |

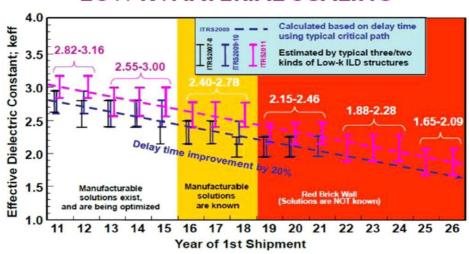

| Figure 1.4. Prediction of low-k materials scaling according to the 2013 edition of ITRS |

| Roadmap                                                                                 |

| Figure 1.5. Schematic diagram of the damascene process of Cu in ULSI11                  |

| Figure 1.6. Seam formation after conformal ELD in narrow trench                         |

| Figure 1.7. Void-free filling of narrow trench by ELD with organic additives            |

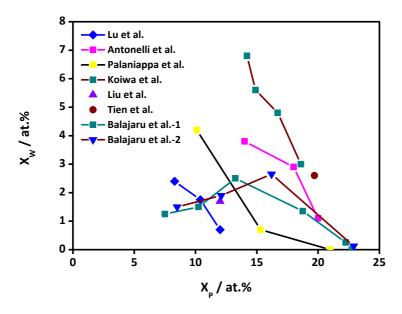

| Figure 1.8. W versus P atomic content for ELD-CoWP (edited from ref. [62,63]) 25        |

| Figure 1.9. W versus P atomic content for ELD-NiWP (edited from ref. [64-71]) 26        |

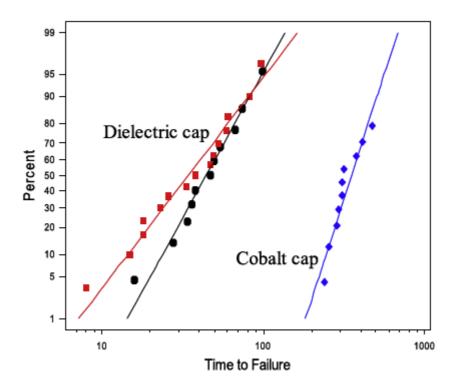

| Figure 1.10. Damascene Cu interconnect EM data comparing undoped Cu with Co alloy       |

| capping layer to Si(C)N dielectric capping layer (edited from ref. [59]) 27             |

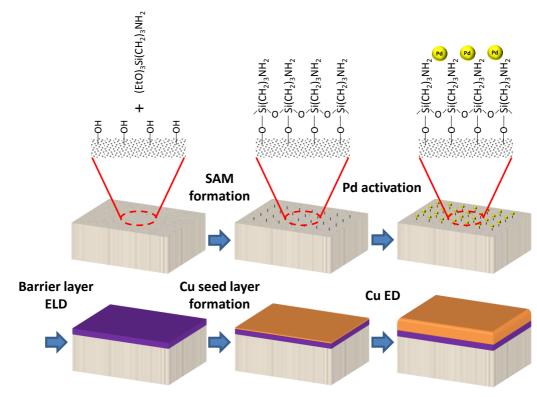

| Figure 1.11. Schematic diagram of the "all-wet" metallization process                   |

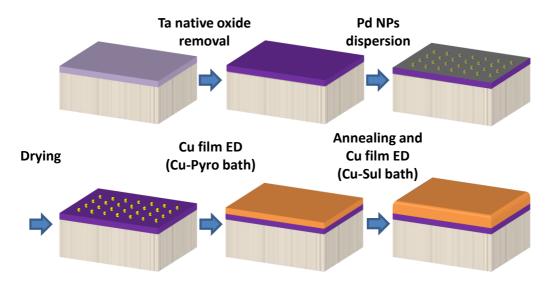

| Figure 2.1. Schematic diagram of the direct Cu ED process on Ta assisted by the Pd NPs. |

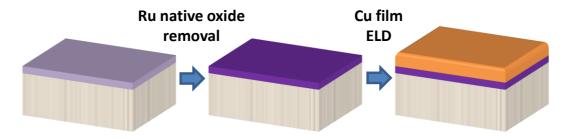

| Figure 2.2. Schematic illustration of direct Cu ELD process on Ru substrate 40          |

|-----------------------------------------------------------------------------------------|

| Figure 2.3. Schematic illustration of method for film adhesion test referring to ASTM   |

| D3359. <sup>111</sup> 43                                                                |

| Figure 3.1. (a) TEM image of synthesized Pd NPs on TEM grid and (b) number              |

| probability of Pd NPs according to the particle size                                    |

| Figure 3.2. (a) The mass change during the Pd NPs coating process on QCM electrode      |

| and (b) XPS analysis of the Ta substrate after Pd NPs loading 50                        |

| Figure 3.3. The AFM surface morphology of Ta substrate (a) before and (b) after the Pd  |

| NPs loading                                                                             |

| Figure 3.4. FESEM images of Cu deposited on (a, c) blanket Ta and (b, d) Pd NPs-loaded  |

| Ta substrates. Inset in (d): AFM image of the specimen                                  |

| Figure 3.5. (a) LSV on Pd NPs-loaded Ta substrate with the addition of allyl alcohol to |

| the Cu-Pyro bath (scan rate = $10 \text{ mV s}^{-1}$ ). (b, c) FESEM images of Cu film  |

| deposited on Pd NPs-loaded Ta substrate with 0.035 M allyl alcohol. Insets in           |

| (c): AFM image of the specimen                                                          |

| Figure 3.6. LSV on Cu deposited on (a) the blanket Ta, (b) the Pd NPs-loaded Ta without |

| allyl alcohol, and (c) the Pd NPs-loaded Ta with 0.035M allyl alcohol. LSV              |

| experiments were conducted in Cu-Sul bath (scan rate = $10 \text{ mV s}^{-1}$ ) 54      |

| Figure 3.7. LSV on a Cu seed layer prepared on the Pd NPs-loaded Ta by direct ED in     |

| Cu-Pyro bath containing 0.035 M allyl alcohol. LSV experiment was                       |

|-----------------------------------------------------------------------------------------|

| conducted in Cu-Sul bath (scan rate = $10 \text{ mV s}^{-1}$ ) and the concentration of |

| each additive is specified in the Chapter 2.1.2                                         |

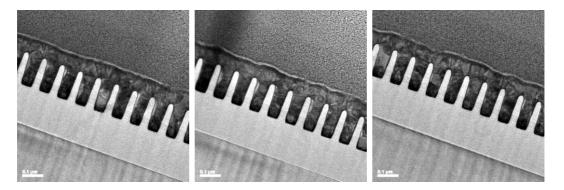

| Figure 3.8. FESEM images of 55 nm patterned Ta substrate (a, d) before seed layer       |

| deposition and after seed layer formation (b, e) without Pd NPs and (c, f)              |

| with Pd NPs58                                                                           |

| Figure 3.9. FESEM images of Cu seed layer deposited on 55 nm patterned Ta with Pd       |

| NPs, according to the allyl alcohol concentration. Allyl alcohol content in             |

| Cu-pyro bath was (a, e) 0.0175 M, (b, f) 0.035 M, (c, g) 0.0525 M, and (d, h)           |

| 0.07 M                                                                                  |

| Figure 3.10. (a) Trench opening width after Cu seed layer formation with varying the    |

| allyl alcohol concentration in Cu-Pyro bath and (b) TEM image for the Cu                |

| seed layer deposited with 0.07 M allyl alcohol (Pt was sputtered before the             |

| TEM specimen preparation by FIB)                                                        |

| Figure 3.11. TEM analyses of 55 nm patterned trench covered with the Cu seed layer      |

| after filling in Cu-Sul bath. The Cu seed layer was prepared by direct ED on            |

| the Pd NPs-loaded Ta with 0.07 M allyl alcohol in Cu-Pyro bath                          |

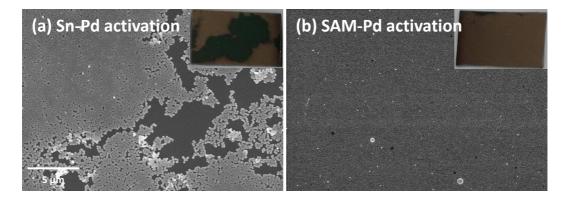

| Figure 4.1. FESEM surface analyses of ELD-NiWP layer deposited on (a) Sn-Pd             |

| activated and (b) SAM-Pd activated SiO <sub>2</sub> blanket substrate. Picture of the   |

| specimen was also taken after ELD (insets)                                              |

|                                                                                         |

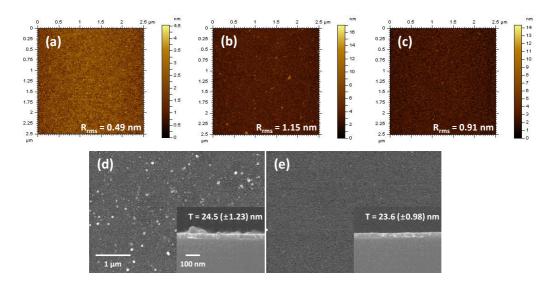

| Figure 4.2. The AFM morphology analyses of (a) pristine SiO <sub>2</sub> substrate and the SiO <sub>2</sub>       |

|-------------------------------------------------------------------------------------------------------------------|

| substrate after SAM-Pd activation (b) without and (c) with sonication during                                      |

| the Pd NPs adsorption step. (d) and (e) show FESEM surface and cross-                                             |

| sectional (insets) analyses for a 25 nm thick NiWP film deposited on (b) and                                      |

| (c), respectively                                                                                                 |

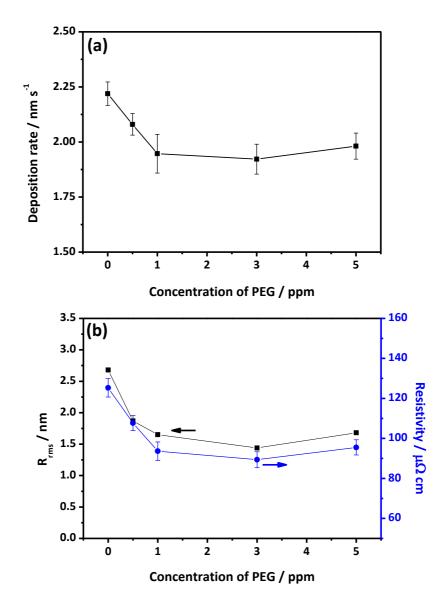

| Figure 4.3. The effect of PEG concentrations on (a) the rate of NiWP ELD and (b)                                  |

| resistivity and surface roughness of a 25 nm thick NiWP film                                                      |

| Figure 4.4. Surface and cross-sectional FESEM analyses of CoWP layer deposited with                               |

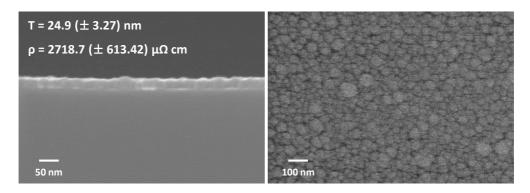

| 0.4 M citrate and 0.2 M NaH <sub>2</sub> PO <sub>2</sub> 71                                                       |

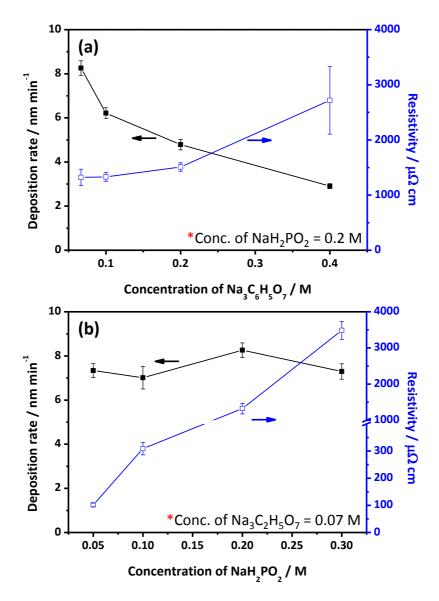

| Figure 4.5. Effect of citrate and NaH <sub>2</sub> PO <sub>2</sub> concentration on the deposition rate of CoWP   |

| ELD and resistivity of 25 nm thick CoWP film                                                                      |

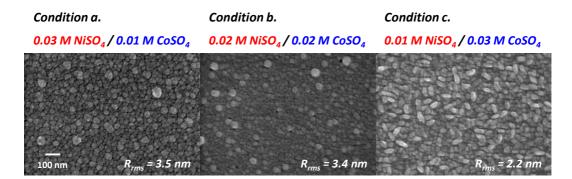

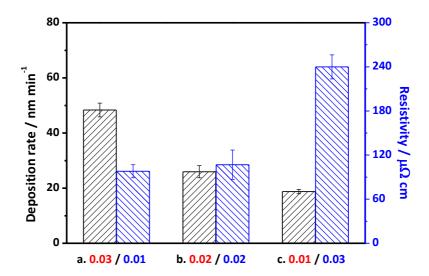

| Figure 4.6. FESEM surface analyses of $Ni_xCo_{(0.04-x)}P$ film prepared with each deposition                     |

| condition                                                                                                         |

| Figure 4.7. The deposition rate and resistivity of 25 nm thick Ni <sub>x</sub> Co <sub>y</sub> P film prepared in |

| each deposition condition                                                                                         |

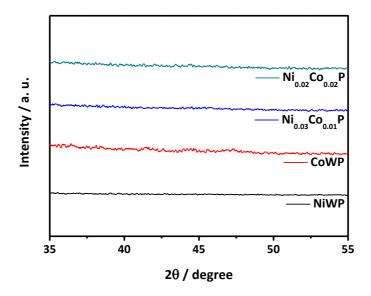

| Figure 4.8. XRD analyses of each barrier layer having 25 nm of thickness                                          |

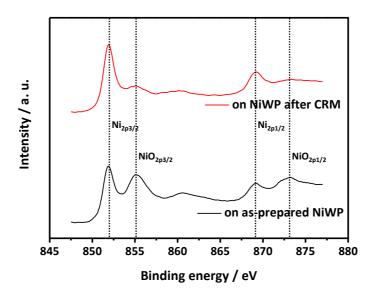

| Figure 4.9. Results of XPS analyses of NiWP film before (black line) and after (red line)                         |

| undergoing the coulometric reduction process (slight oxidation occurs during                                      |

| sample transfer)                                                                                                  |

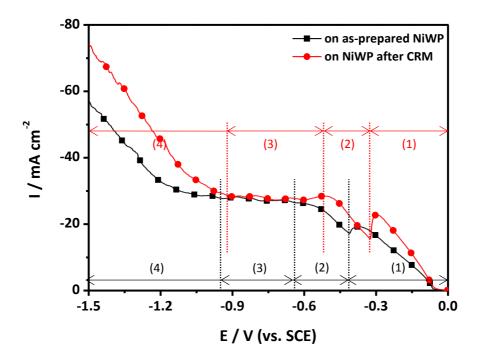

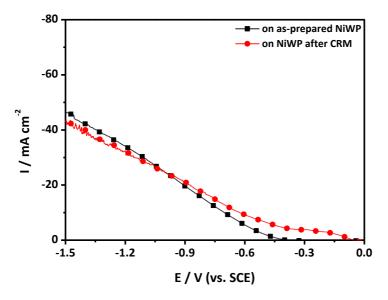

| Figure 4.10. Results of LSV on the NiWP layer before (black line) and after (red line)                            |

| coulometric reduction (scan rate = $20 \text{ mV s}^{-1}$ )                                   |

|-----------------------------------------------------------------------------------------------|

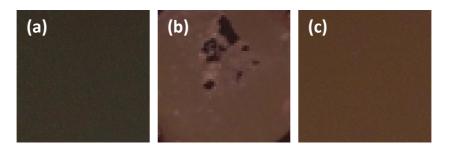

| Figure 4.11. Pictures of (a) as-prepared NiWP film and (b, c) Cu film electrodeposited (b)    |

| without coulometric reduction process or (c) after coulometric process on                     |

| NiWP film. 82                                                                                 |

| Figure 4.12. The LSV results on the NiWP layer before (black line) and after (red line)       |

| coulometric reduction process. The LSV studies were conducted in 1 M                          |

| $H_2SO_4$ electrolyte (Cu ED bath without Cu ion and additives, scan rate = 20                |

| $mV s^{-1}$ )                                                                                 |

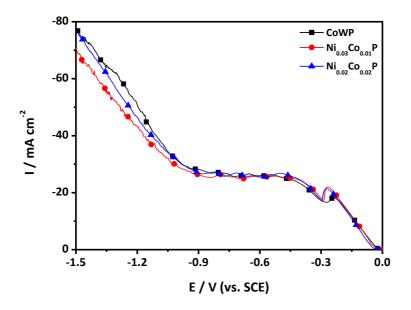

| Figure 4.13. Results of LSV on each barrier layer after coulometric reduction (scan rate =    |

| 20 mV s <sup>-1</sup> )                                                                       |

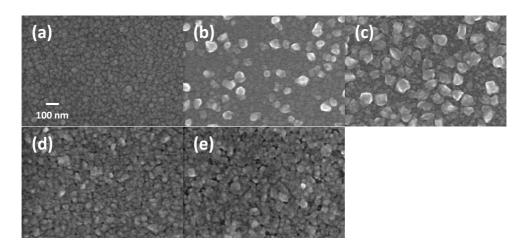

| Figure 4.14. FESEM surface analyses of 25 nm thick NiWP layers (a) after coulometric          |

| reduction, and (b-e) after Cu ED at (b) $-0.75$ V, (c) $-1.0$ V, (d) $-1.25$ V, and           |

| (e) $-1.5$ V vs. SCE. In all cases, the deposition charge density was $10$ mC                 |

| cm <sup>-2</sup> 85                                                                           |

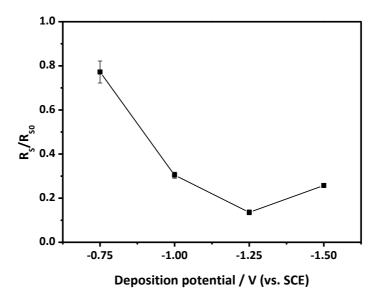

| Figure 4.15. The effect of deposition potential on the ratio of the sheet resistance after Cu |

| ED $(R_S)$ to the resistance before Cu ED $(R_{S0})$ . The deposition charge density          |

| was 10 mC cm $^{-2}$ and the average $R_{S0}$ for the 25 nm thick NiWP layer was 35           |

| $\Omega \text{ square}^{-1}$ 86                                                               |

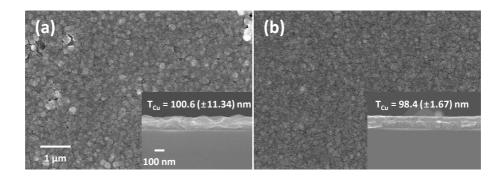

| Figure 4.16. FESEM surface analyses of a Cu film deposited on a NiWP layer (a) at             |

| -1.25 V (vs. SCE) for 200 mC cm <sup>-2</sup> and (b) at -1.25 V (vs. SCE) for 10 mC          |

| cm <sup>-2</sup> followed by -0.45 V (vs. SCE) for 190 mC cm <sup>-2</sup> . The insets present a |

|---------------------------------------------------------------------------------------------------|

| cross-sectional FESEM images of a 100 nm thick Cu film on a 25 nm thick                           |

| NiWP layer. 87                                                                                    |

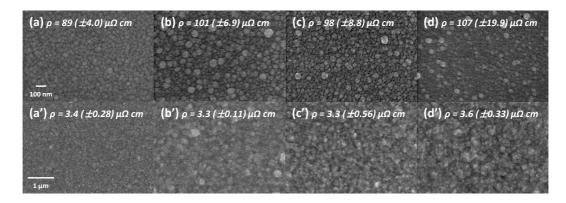

| Figure 4.17. FESEM surface analyses of 25 nm thick (a) NiWP, (b) CoWP, (c)                        |

| $Ni_{0.03}Co_{0.01}P$ , and (d) $Ni_{0.02}Co_{0.02}P$ formed by ELD on SAM-Pd activated $SiO_2$   |

| substrate. (a'~d') FESEM surface analyses of 100 nm thick Cu film directly                        |

| deposited by ED on corresponding (a~d) ELD-barrier layer                                          |

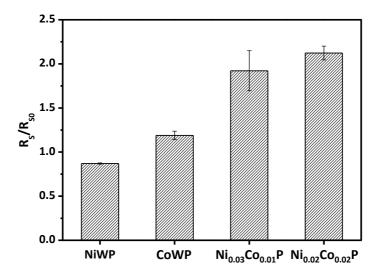

| Figure 4.18. Change in sheet resistance after thermal treatment (500°C, 30 min in a $N_2$         |

| atmosphere) of each specimen having different barrier layer. The thickness of                     |

| each barrier layer was 25 nm and that of the overlaying Cu was 100 nm 92                          |

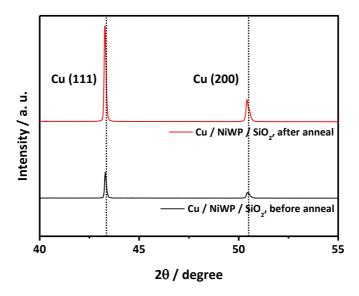

| Figure 4.19. XRD analyses of a Cu (100 nm) / NiWP (25 nm) / SiO <sub>2</sub> stacked specimen     |

| before (black line) and after (red line) thermal treatment at 500°C for 30 min                    |

| in a N <sub>2</sub> atmosphere                                                                    |

| Figure 4.20. LSV on the NiWP substrate after 1 <sup>st</sup> step Cu ED with varying the additive |

| combination in Cu ED electrolyte. Inset: LSV on the 30 nm thick Cu film                           |

| after CRM. The scan rate was 20 mV s <sup>-1</sup>                                                |

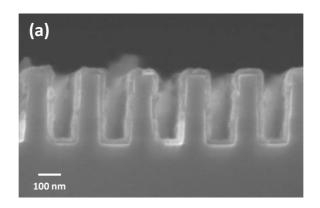

| Figure 4.21. (a) FESEM image of 120 nm width trench after NiWP barrier layer                      |

| formation and (b) the evaluation of conformality                                                  |

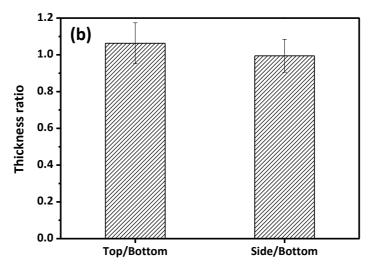

| Figure 4.22. FESEM images of 120 nm width trench (a) after NiWP ELD and after direct              |

| Cu FD on (a) with total charge amount of (b) 150 mC cm <sup>-2</sup> (c) 200 mC cm <sup>-2</sup>  |

|             | and (d) 300 mC cm <sup>-2</sup>                                                            |

|-------------|--------------------------------------------------------------------------------------------|

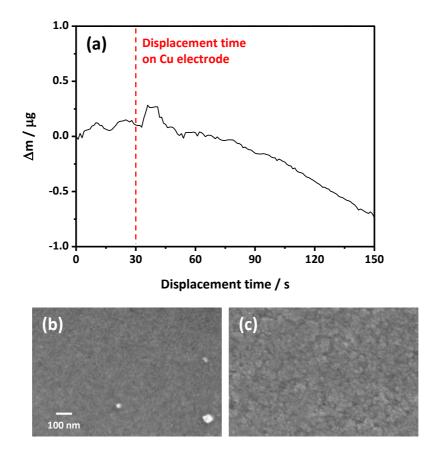

| Figure 5.1. | (a) QCM analysis during the displacement reaction between Cu and Ru ion                    |

|             | on Cu electrode. (b, c) FESEM analyses of (b) before and (c) after Ru                      |

|             | displacement reaction on Cu electrode                                                      |

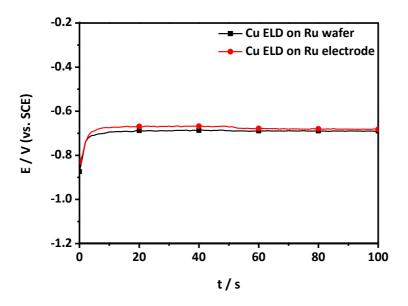

| Figure 5.2. | E transient as a function of the ELD time both on Ru wafer and electrode.                  |

|             | ELD was conducted in a hydrazine based Cu ELD bath                                         |

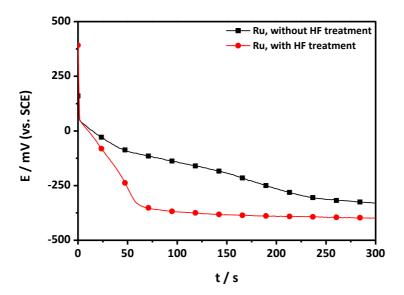

| Figure 5.3. | The effect of HF treatment on the potential transient during coulometric                   |

|             | reduction of Ru surface                                                                    |

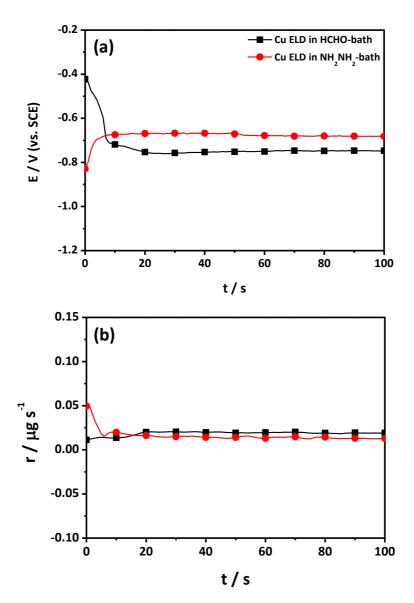

| Figure 5.4. | The EQCM monitoring on Ru electrode in formaldehyde or hydrazine based                     |

|             | Cu ELD bath. Changes in (a) potential and (b) mass change rate were                        |

|             | simultaneously recorded as a function of time                                              |

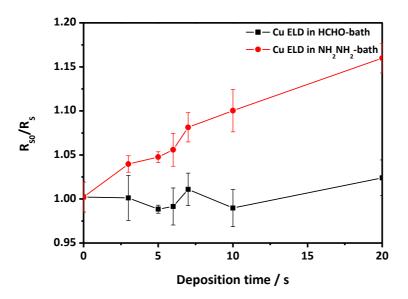

| Figure 5.5. | The sheet resistance ratio $(R_{S0}/R_S)$ change of Ru substrate with respect to the       |

|             | deposition time in formaldehyde or hydrazine based Cu ELD bath111                          |

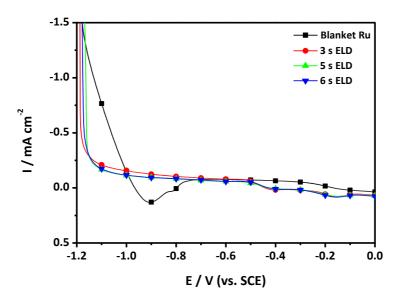

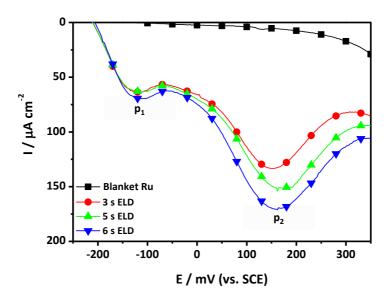

| Figure 5.6. | LSV on Ru and on Cu deposited Ru substrate (scan rate = 20 mV s <sup>-1</sup> )112         |

| Figure 5.7. | AFM morphology analyses of electroless deposited Ru according to the                       |

|             | deposition time                                                                            |

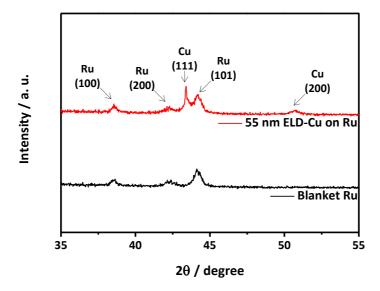

| Figure 5.8. | XRD analyses of blanket Ru and 55 nm Cu prepared by ELD on Ru in                           |

|             | hydrazine based Cu ELD bath                                                                |

| Figure 5.9. | Electrochemical stripping of ELD-Cu on Ru substrate (scan rate = $20 \text{ mV s}^{-1}$ ). |

|             | 115                                                                                        |

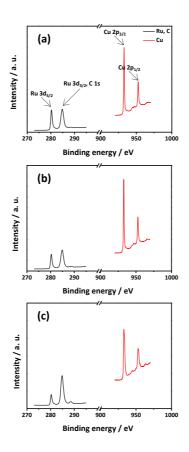

| Figure 5.10. XPS spectra of (a) 3 s, (b) 5 s, and (c) 6 s deposited Ru substrate   | 116    |

|------------------------------------------------------------------------------------|--------|

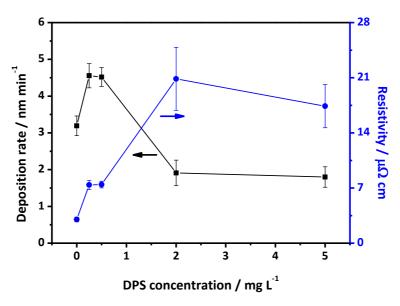

| Figure 5.11. Dependence of deposition rate of Cu ELD and the resistivity of result | ant Cu |

| film on the concentration of DPS in the bath.                                      | 118    |

## **CHAPTER I. Introduction and overview**

## 1.1. The interconnection technology for ULSI

#### 1.1.1. The present and issues of interconnection technology

An integrated circuit (IC) is a set of electronic circuits on one small plate of semiconductor material. Modern ICs can be made very compact, incorporating up to several billions transistors and other electronic components in an area of about 1 cm<sup>2</sup> in consequence of ultra-large scale integration (ULSI).<sup>1</sup> All transistors and other IC components have to be electrically interconnected to provide the proper functionality. The width of the conducting lines that connect different transistors in a circuit is becoming smaller as the technology advances; it dropped below 100 nm in 2008 and in 2015, the width of the half-pitch for metal 1 of memory and logic ICs reached 24 nm and 32 nm, respectively.<sup>2</sup>

In parallel, the interconnect delay is becoming an increasing limitation of the overall signal propagation delay. The total resistance (R) of the interconnect structure is now a significant factor affecting the chip performance. At the same time, the capacitance (C) between wires is increasing due to the decreasing spacing between the wires. Both

factors significantly increase the RC delay of IC circuits. In the early 1990s, the semiconductor industry found that the concept to improve IC performance by enhancing the speed of individual transistors through scaling should be complemented by an improvement of the interconnect delay. This was possible by making changes to the materials used for both the wires and the insulator (Fig. 1.1).<sup>3</sup> The need to decrease the RC delay, the dynamic power consumption, and the cross-talk noise was the main driving force behind the introduction of new materials to the back-end-of-line (BEOL, the part of the IC manufacturing process where interconnects are made) integration.<sup>4</sup>

Metallic conductivity and resistance to electromigration of bulk copper (Cu) were known to be better than those for aluminum (Al), which was the interconnect material until Cu interconnect was introduced in the late 1990s.<sup>5</sup> Application of an interconnect material with lower resistivity such as Cu decreases the interconnect RC delay, which, in turn, increases the IC speed.<sup>6</sup> The transition to Cu as the conductor was one of the most significant changes in semiconductor manufacturing history. The first working microprocessor using Cu was made by IBM in 1997 and the process was introduced into high volume manufacturing in IBM's facilities in 1998.<sup>5</sup>

Replacement of Al by Cu has an enormous obstacle for the semiconductor industry, because Al is deposited over the entire wafer surface and then patterned by reactive ion etching (RIE).<sup>7</sup> Cu cannot be patterned by traditional RIE because of the very low vapor pressure of the reaction products, and a new process had to be developed. As a result, the

damascene process has emerged as the industry standard.<sup>8</sup> The dielectric layer is deposited and patterned first before the metal deposition. Then the patterned dielectric is filled by superfilling techniques, in which higher deposition rates are achieved at the bottom of the trenches with respect to the sidewalls, resulting in void-free and seamless filling of trenches and vias with high aspect ratios. These processes have played a pivotal role in the success of this technology.

However, the introduction of Cu was not sufficient for the necessary reduction of RC delays. The most straightforward way to reduce the C value is to lower the dielectric constant (k) of dielectric layer. Fig. 1.2 shows the trends in k number, referred to the ITRS roadmaps of three different editions. Despite the ITRS roadmap kept pushing lower-k forward to more advanced node, the real situation had been much more challenging and complicated. According to 2013 edition of the ITRS, ultra-low-k (ULK) materials with dielectric constants still as high as k = 2.5 were integrated in 2012 (Fig. 1.2). The general issue of (porous) low-k materials is that they are generally soft, mechanically weak, and do not adhere well to silicon or metal wires. Furthermore, porous low-k materials do not withstand conventional interconnect processing (e.g. they degrade during the plasma and chemical processing). Several different types of low-k materials have been considered. Initially, organosilicate-based (OSG) ULK materials were rapidly developed, such as XLK, LKD, NCS, etc.; however, they quickly met huge challenges during their integration. Low-k dielectrics based on organic polymers have

low polarizability and, therefore, are able to provide the lowest k values (2.8–3.0) without requiring the introduction of porosity. However, efforts to integrate organic materials into ICs have also not been successful. In addition to poor mechanical and thermal properties, the key problems were related to the relatively high coefficient of thermal expansion (CTE) with respect to other components of ICs.<sup>11</sup>

Additional challenges during the introduction of Cu and low-k dielectrics are related to the high diffusivity of Cu ions.<sup>2</sup> To avoid Cu diffusion into the dielectric, significant efforts were made to develop Cu diffusion barriers. These include conductive barriers isolating the Cu wire and the low-k dielectric in a metallization level and dielectric barriers deposited after chemical mechanical planarization (CMP) and before starting the next metallization level. The major requirements for these barrier layers are their density and amorphous nature and a lack of any chemical groups that can oxidize Cu so that no Cu ions can be formed.<sup>12-15</sup> Therefore, the barriers must be hydrophobic and good barriers against moisture diffusion because penetrated water can oxidize Cu and form Cu ions.

#### 1.1.2. The next-generation interconnection technology

The efforts during the last two decades have made the Cu/low-k technology matured.

While Cu was successfully introduced to decrease the interconnect delay, the

development and the selection of both low-k dielectrics and more suitable conductor materials other than Cu are becoming subjects of intensive research, owing to the aggressive scaling of Cu line width and height. Indeed, the Cu resistivity drastically increases below line widths of 20 nm due to pronounced size effects (Fig. 1.3). Nevertheless, Cu remains uncontested conductor in view of conductivity and resistance to electromigration. While the search for new interconnect materials such as carbon nanotubes and graphene is ongoing, there are still no clear alternative materials at this point. Due to the long transition time from research to production, there is a great risk that no novel material will be ready to replace Cu/low-k interconnects at 11nm or even smaller technology nodes.

According to the ITRS, material innovation in combination with traditional scaling will no longer satisfy the performance requirements in the long-term and radically new interconnect paradigms are needed. For example, the integration beyond the 7 nm technology node is currently much less clear and a "red brick wall" (Fig. 1.4) appears in the 2013 edition of the ITRS Roadmap.<sup>2</sup> Therefore, processing as well as architectural solutions, instead of materials solutions, are being suggested.

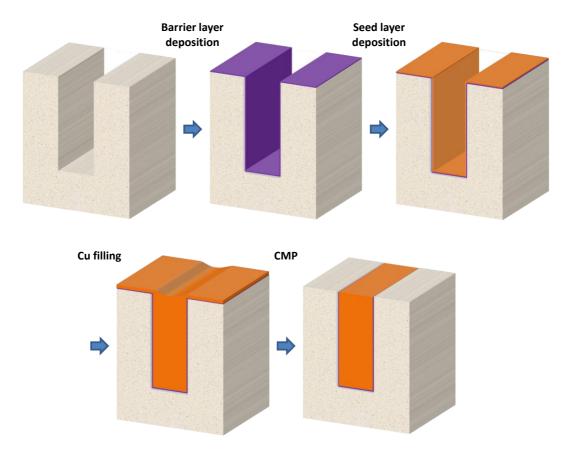

As already be mentioned in Chapter 1.1, the damascene process is composed of the patterning of a low-k dielectric layer, the deposition of a diffusion barrier/Cu seed layer, Cu gap-filling, and CMP (Fig. 1.5). Among these steps, the diffusion barrier and Cu seed layer are formed by physical vapor deposition (PVD). Generally, metals deposited

by the PVD method show good adhesion with the substrate and superior film properties, such as low resistivity and low surface roughness.<sup>20,21</sup>

However, the problem induced by the poor step coverage of the diffusion barrier/Cu seed layer has become serious as trenches are being reduced. Various papers have reported the difficulties in Cu gap-filling by electrodeposition (ED) due to overhang and defects at the sidewalls of the PVD diffusion barrier/Cu seed layer on narrow trenches.<sup>22-</sup> Therefore, other deposition methods such as chemical vapor deposition (CVD), atomic layer deposition (ALD), electroless deposition (ELD), and direct ED are considered as alternatives to PVD for the formation of the barrier/seed layer. Specifically, ELD and direct ED have received much interest due to their various advantages, such as their low process cost, short process time, and excellent control of the thickness of the deposited metal.<sup>26</sup>

Figure 1.1. Gate and interconnect delay versus technology generation (edited from ref. [3]).

Figure 1.2. Predictions of ULK roadmap in the ITRS'2005, 2009, and 2011, and the final decisions of ITRS'2013 (edited from ref. [9]).

Figure 1.3. Measured narrow Cu line resistivity (blue circles) versus line width. Comparisons are depicted with suggested models considering electron scattering due to surface and grain boundaries (edited from ref. [16]).

## LOW-K: MATERIAL SCALING

Figure 1.4. Prediction of low-k materials scaling according to the 2013 edition of ITRS Roadmap.

Figure 1.5. Schematic diagram of the damascene process of Cu in ULSI.

## 1.2. Direct Cu deposition

#### 1.2.1. Direct Cu ED

Direct Cu ED is defined as the ED of Cu without a Cu seed layer on a heterogeneous substrate such as tantalum (Ta), titanium (Ti), iridium (Ir), or ruthenium (Ru). Some papers reported Cu superfilling of sub-micron features as well as seed layer deposition performed by direct ED.<sup>22,27-31</sup> Our previous paper described the direct Cu ED on a TiN/Ti diffusion barrier with the aid of a palladium (Pd) particle which was formed via a displacement reaction.<sup>22</sup> The displaced Pd particle assisted in the formation of a uniform Cu film layer by reducing the charge transfer resistance during the ED process. Thus, defectless superfilling was realized on a 400 nm feature. In addition, studies of direct Cu ED on a Ta-based barrier layer were also published by Kim *et al.* and Starosvetsky *et al.* Kim *et al.* focused on the observation of the growth of Cu films on a TaN substrate after the anodic removal of Ta oxides in a saturated KOH solution.<sup>30</sup> Starosvetsky *et al.* succeeded in the seedless gap-filling of a 300 nm trench which consisted of a TaN/Ta barrier layer after a cathodic pretreatment in a pyrophosphate-based electrolyte.<sup>31</sup>

Although various approaches have been reported by various research groups, it is still challenging by means of direct ED to fill sub-100 nm trenches covered with highly resistive barriers owing to their low conductivity and large charge transfer resistance. The

aforementioned studies applied various strategies, such as native oxide removal or the use of Pd activation: however, the remaining oxides or large Pd particles especially with a wide distribution prohibited the formation of an ultrathin layer and the sub-100 nm feature filling.

#### 1.2.2. Cu ELD

ELD is a well-known method for preparing thin films of metals and their alloys. <sup>32</sup> It is a highly selective method allowing additional patterning of isolated and embedded structures on insulating substrates, e.g. glass, plastic or ceramic. ELD is a relatively low temperature (less than the boiling point of the electrolyte) and low cost process compared to other deposition methods such as PVD or CVD. <sup>33-35</sup> ELD features uniform and normally conformal deposition with low defect density and some unique material properties. In the last few decades, ELD of metals (e.g. copper, gold, nickel, cobalt, palladium, iron, silver, etc.) and their alloys was demonstrated for micro system applications: microelectronics, micro electro mechanics, micro electro optics and microfluidics, micro fuel cells, micro batteries etc. ELD was also demonstrated on nano structures, both artificial and natural. <sup>32,36</sup> The progress in ELD followed the need and the trend for better metallization technologies for complex structures with critical dimensions that had been shrinking continuously in the last few decades. <sup>37,39</sup>

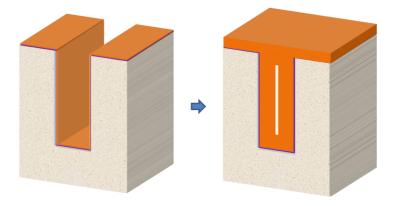

Electroless Cu for ULSI metallization was proven to be competitive to ED. The resistivity of ELD-Cu could be in the range of 2.0- $\mu\Omega$  cm and it was capable of forming deep submicron features. 40 Cu ELD was highly conformal, leading to seam formation at the center of interconnect lines (Fig. 1.6). Void-free filling of high aspect ratio via-holes was reported with the proper choice of additives such as bis-(3-sulfopropyl)-disulfide (SPS) and mercapto alkyl carboxylic acids as accelerators, and poly(ethylene glycol)poly(propylene glycol) triblock copolymers as inhibitors. 41-43 Void-free electroless Cu deposition in sub-micrometer trenches was obtained in the presence of poly(ethylene glycol) (PEG) as inhibitor as well as accelerating species such as SPS and its derivatives, 3-N,N-dimethylamino-dithiocarbamoyl-1-propanesulfonic acid (DPS) and 2-mercapto-5benzimidazole-sulfonic acid (MBIS) (Fig. 1.7). 44-48 Nevertheless, ELD of Cu still needs further improvements to combine the highest conductivity and the best seamless trench filling compatible with most inter-level dielectric schemes and the process requirements. For example, the use of formaldehyde as a reducing agent is regulated and might be restricted in a few countries. Therefore, alternative scheme using glyoxylic acid was devised.<sup>49</sup> Typical Cu plating bath operates at high pH (>12.5) and deposition temperature near 70°C which may be a problem to some polymer based low dielectric insulators. Thus, other solutions working at lower pH and lower temperatures are also possible, although, they usually yield Cu with higher specific resistivity.

#### 1.2.3. Direct Cu ELD

Direct Cu ELD is also defined as the deposition of Cu without a Cu seed layer on a heterogeneous substrate such as Ta, Ti, Ir, or Ru by means of ELD. Recently, Ru has received attention as an alternative seed and barrier layer instead of conventional Cu seed and Ta barrier layer, because of its low resistivity and excellent adhesion, as well as its negligible solubility with Cu.<sup>50-52</sup> As the CVD and ALD of Ru are well-developed, the application of Ru seemed promising in the past few years.<sup>53-55</sup> Unfortunately, however, Ru itself was determined not to be suitable as a barrier layer, since Cu could diffuse through columnar Ru grains.<sup>51,56</sup> Therefore, research on the improvement in the barrier layer property of Ru-alloy (e.g. Ru-Al<sub>2</sub>O<sub>3</sub>, RuCr) or Ru/barrier layer stack (e.g. Ru/Ta, Ru/TiN) are widely conducted nowadays. In addition, study on the feasibility of direct Cu ED on those layers also takes huge interest.<sup>50,55-57</sup>

On the other hand, the deposition of a Cu film on Ru by ELD has not yet received much attention, although ELD is currently one of the promising technologies for metallization. Despite numerous advantages of ELD as mentioned in Chapter 1.2.2, the necessity of the catalyzing process on conventional barrier layers such as Ta or TiN has limited the practical application of ELD in ULSI. 19,58 The catalyzing process signifies the formation of catalytic particles on the substrate, which act as initial nucleation sites for Cu ELD. 33 The catalytic particle generally causes low-density Cu nucleation, disturbing thin film

formation as well as sub-100 nm feature filling.<sup>19,58</sup> However, the catalyzing process is not required in the case of Ru, because the whole Ru surface is catalytic to ELD, and this facilitates the relatively high-density Cu nucleation.<sup>53</sup> Therefore, the thin film formation and sub-100 nm feature filling by ELD are expected to be feasible on Ru surface. Recently, F. Inoue *et al.* reported the Cu seed layer deposition by ELD directly on ALD-Ru for the TSV filling.<sup>53</sup> However, the detailed understanding over the growth phenomena and feature filling by Cu ELD on Ru is still insufficient.

Figure 1.6. Seam formation after conformal ELD in narrow trench.

Figure 1.7. Void-free filling of narrow trench by ELD with organic additives.

# 1.3. All-wet metallization

#### 1.3.1. Electroless Co/Ni alloy as a barrier/capping material

Electroless cobalt (Co) and nickel (Ni) alloys can be excellent barrier and capping materials for Cu and silver (Ag) metallization. Electroless Co and Ni alloys are highly selective, uniform and serve their function even for ultrathin layers (10–20 nm). To deposit electroless Co or Ni films, hypophosphite or di-methyl-amino-borane (DMAB) was used as reducing agents, and as a result of reducing agent oxidation, phosphorous (P) or boron (B) could be incorporated into the deposit. Furthermore, to improve the thermal stability and diffusion properties, refractory metals such as tungsten (W), molybdenum (Mo), or rhenium (Re) can be co-deposited with electroless Co or Ni when water-soluble compounds of refractory metals were introduced into the deposition solutions. For example, W was incorporated into electroless Co film up to 12 at% when tungsten-phosphoric acid was used as a W source in the deposition bath. The incorporation reaction pathways for each constituent are described elsewhere, and for example, the

Acidic electrolyte with hypophosphite reducing agent

$${\rm H_2PO_2^- + H_2O \to HPO_3^{2-} + H^+ + 2H_{ad}}$$

[1.1]

Ni<sup>2+</sup> or Co<sup>2+</sup> + 2H<sub>ad</sub>

$$\rightarrow$$

Ni or Co + 2H<sup>+</sup> (Ni or Co dep.) [1.2]

$H_2PO_2^- + H_{ad} \rightarrow P + H_2O + OH^-$  (P incorp.) [1.3]

$2H_{ad} \rightarrow H_2$  (H<sub>2</sub> evol.) [1.4]

Basic electrolyte with hypophosphite reducing agent

$$H_2PO_2^- + OH^- \rightarrow H_2PO_3^- + H_{ad} + e^-$$

[1.5]

$Ni^{2+}$  or  $Co^{2+} + 2e^- \rightarrow Ni$  or  $Co$  (Ni or  $Co$  dep.) [1.6]

$H_2PO_2^- + e^- \rightarrow P + 2OH^-$  (P incorp.) [1.7]

$H_{ad} + H_{ad}^+ + e^- \rightarrow H_2$  (H<sub>2</sub> evol.) [1.8]

W co-deposition

$$WO_2^{2+} + 6H_2PO_2^- + 4H_2O \rightarrow W + 6H_2PO_3^- + 3H_2 + 2H^+$$

[1.9]

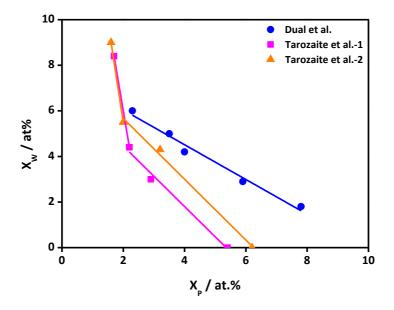

Various studies have reported the effect of the concentration of ELD bath constituents on the P and W incorporation amount in CoWP or NiWP films. The results of investigation using several CoWP or NiWP baths are depicted in Fig. 1.8 and 1.9. 62-71 It could be seen from the figures that co-deposition of W clearly influenced on the P content of the deposits: in general, the incorporation of P into the film was impeded by the co-deposition of W, probably due to a competitive consumption of hypophosphite for the incorporation of P and W (reaction [1.3] and [1.7] vs. [1.9]).

Electroless barriers for on-chip metallization are characterized by the following microstructure effects: (a) the so-called "solute effect", P (or B) and W (or Mo, Re) impurities create a "stuffed" boundary, blocking possible Cu diffusion through the grain boundaries; (b) \(\varepsilon\)-cobalt grains embedded in an amorphous matrix, thus avoiding the high diffusivity paths of the grain boundaries in regular polycrystalline materials.<sup>59</sup> For instance, selectively deposited electroless Ni-P and Co-P, Ni-Co-P films were investigated as the barrier/cladding materials for Cu metallization. 72,73 The former electroless barriers for Cu were effective up to a temperature of 400°C. The introduction of a third alloying element, especially refractory metal, e.g. W, Mo, or Re, improves barrier efficiency. NiB, NiReP and NiWP show ability to serve as a barrier and cladding layers without significant diffusion of Cu into the barrier and no Cu line resistance increases at temperatures up to 400-500°C. Electroless CoWP thin films showed an ability to function as effective barriers/cladding layers for Cu metallization at temperatures up to 550°C.74 Electroless barrier layers can be formed on PVD or CVD deposited Co (or Ni) seed layers as well as directly on dielectric layers (such as SiO<sub>2</sub>). Self-assembled monolayer (SAM) of silane-based compounds followed by treatment in a Pd containing activator was utilized as the adhesion promoter/catalytic layer.

SiN or SiC layer is typically used as the etch stop and passivation layer for Cu. SiN/Cu or SiC/Cu interface is a major electromigration-voiding site. Selective metal capping with electroless metals was proposed as one of the ultimate solutions to this problem.<sup>72-76</sup>

Electroless metal capping/barrier layers such as CoWBP, CoWP, NiMoP also provide barrier properties against Cu and oxygen diffusion so that lower effective interconnect capacitance can be obtained with thinner or even without SiN (SiC) layers which have high-k.<sup>77-79</sup> It was also demonstrated that both the contact resistance and the leakage that could be lower for a stand-alone electroless metal cap compared to a stand-alone SiN cap, presumably due to the damage associated with the SiN deposition. The electromigration median-time-to-failure (EM MTTF) of damascene Cu interconnects with Co capping layer is about ten-times better than that of Cu metallization with Si(C)N dielectric capping layer. The distribution of the EM failures is also tighter on Co capping wafers (Fig. 1.10).<sup>59</sup> The increase of the EM resistance with an electroless capping layer can be explained by the complete passivation of the top interface as fastest diffusion path resulting in increased adhesion and interfacial bonding strength (i.e. metal/metal > metal/Si > metal/oxygen bonding).

Selective electroless Ni process was demonstrated to fill the contact holes to Si while providing low contact resistance and planar surface.<sup>80,81</sup> Selective electroless Co and Ni deposition into through silicon vias (TSV) for 3D interconnects has been also achieved through the mechanical removal of catalysts from the front surface of the wafers or the use of photosensitive TiO<sub>2</sub>/catalyst process.<sup>59</sup> It enables selective TSV filling that eliminates the needs for PVD barrier/seed layer and CMP that significantly reduces the 3D packaging cost.

#### 1.3.2. All-wet metallization

As referred in Chapter 1.1, owing to some critical failures of Cu metallization, especially designed barrier and capping layers are used to overcome those difficulties. Since Cu may diffuse via those layers or even react with them causing another kind of failure, the most popular barriers are TaN, TiN, or Ta/TaN bilayer. <sup>82</sup> Alternative barriers are ternary compounds of transition metal films that provide a good Cu diffusion barrier due to its nano-crystalline or amorphous structure, such as Ti–Al–N, Ta–Al–N which have been developed using a reactive PVD or CVD. <sup>83</sup> It is reported that CVD is preferable for fabricating barrier layer, because disadvantageous characteristics of PVD such as poor step coverage have set critical limits on silicon device applications by increasing the aspect ratio of the trenches.

Following those reports, it is evident that the application of ELD has superior advantage due to its simplicity and by having a better step coverage on complex shape substrate. The electroless NiB, CoB, NiW-X or CoW-X (X = P, B), CoSnB films have outstanding thermal stability as a capping layer or barrier layer. Moreover, the insertion of a SAM, which had been investigated as diffusion barrier, to the formation of these layers is effective to produce conformal and thin film.

An interesting approach was integrating all the various wet processes together onto a unified process; a so-called "all-wet" process as described in Fig. 1.11. The proposed

all-wet metallization process includes barrier layer ELD, seed layer formation, and Cu ED. To form a barrier layer by ELD on a dielectric substrate such as SiO<sub>2</sub>, most studies have created a SAM prior to ELD in order to immobilize the catalytic particles. <sup>90,94,95</sup> Generally, the use of a SAM improves catalytic nanoparticle coverage as well as adhesion between the electroless deposited film and the substrate, because the alkoxy group in the silane radical makes a strong bond with the SiO<sub>2</sub> surface and the amino or thiol group of the reverse position traps the catalysts. Electroless Co or Ni alloy films are uniformly deposited on the SiO<sub>2</sub> substrate by using 3-aminopropyltriethoxysilane (APTES) as the organosilane molecule. <sup>90,94,95</sup>

A Cu seed layer formation step is essential before undertaking Cu ED on electroless barrier layers, because the conductivity of electroless deposited Co or Ni alloy layers are low. Usually, Cu seed layer formation on an electroless deposited barrier layer is conducted by using Cu ELD and/or by means of a displacement reaction between Cu ions and the barrier material. Subsequently, Cu ED is performed on the seed layer, thus realizing an all-wet metallization process. 90,96 However, Cu seed layer formation through a displacement reaction can lower device reliability by inducing surface damage and pitting on the barrier layer. Therefore, the development of a method for direct Cu ED is highly pursued on electroless deposited Co or Ni alloy barrier layers. It is as well expected that the elimination of the seed layer formation step would enhance the productivity of the device.

Figure 1.8. W versus P atomic content for ELD-CoWP (edited from ref. [62,63]).

Figure 1.9. W versus P atomic content for ELD-NiWP (edited from ref. [64-71]).

Figure 1.10. Damascene Cu interconnect EM data comparing undoped Cu with Co alloy capping layer to Si(C)N dielectric capping layer (edited from ref. [59]).

Figure 1.11. Schematic diagram of the "all-wet" metallization process.

# 1.4. Concepts of the study

In this study, the entire metallization processes were modified for the next-generation interconnect fabrication. On Ta barrier layer, a feasible direct Cu ED was investigated, in an effort to realize sub-100 nm gap-filling by direct Cu ED. Well-defined Pd nanoparticles (NPs) were introduced on a Ta substrate to promote the nucleation of Cu on a highly resistive substrate. Pd NPs ~3 nm in size and the addition of allyl alcohol in the ED bath facilitated the preparation of a uniform Cu seed layer on a blanket Ta substrate. The seed layer formation method was also successfully applied to a 55 nm patterned Ta substrate. After the deposition of the seed layer, gap-filling of the trenches was accomplished.

A method for direct Cu ED on an electroless deposited Co or Ni alloy barrier layer was investigated for all-wet Cu interconnect fabrication. To achieve practicable direct Cu ED, we modified the entire all-wet metallization process. A reduction in electroless deposited Co or Ni alloy films' resistivity was achieved by controlling the activation process and the composition of the ELD bath. To obtain a uniform, smooth Cu film, barrier layer oxide was removed through a coulometric reduction method (CRM) followed by a two-step potentiostatic Cu ED process, leading to a successful bottom-up Cu filling.

On Ru substrate, which is considered as next-generation barrier/seed material, Cu growth phenomena were investigated during direct Cu ELD. Major obstacle that

interferes with the understanding of growth phenomena during ELD is the existence of induction period, which is occasionally reported in ELD when it is conducted in a formaldehyde or a glyoxylic acid based solutions. <sup>34,53,97</sup> Generally, induction period in ELD is originated from the poor catalytic activity of substrate to ELD or from the complex surface reaction such as adsorption of reagents, substrate oxide formation as well as removal. <sup>53,97</sup> Therefore, Cu ELD bath that did not exhibit the induction period on Ru substrate was introduced in this study. By using the solution, the Cu nucleation and film growth on Ru was investigated at the early stage of the ELD. In addition, the feasibility of Cu ELD on Ru, as a practical metallization process, was examined by a gap-filling experiment.

# **CHAPTER II. Experimental**

# 2.1. Direct ED of Cu on Ta

#### 2.1.1. Preparation of Pd NPs

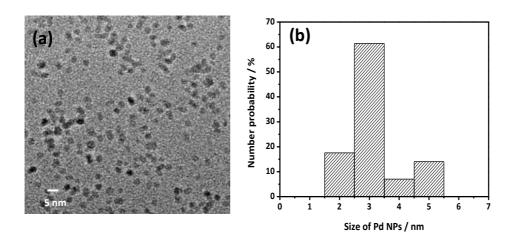

Pd NPs were synthesized using a microwave-assisted polyol method. A solution containing  $0.003 \text{ M K}_2\text{PdCl}_6$ , 0.01 M polyvinylpyrrolidone (PVP, Mw =  $40,000 \text{ g mol}^{-1}$ ), 0.001 M cetyltrimethylammonium bromide (CTAB), and 10 M ethylene glycol (EG) was prepared for the Pd NPs synthesis. The solution was heated in a microwave for 80 s to induce the reduction of Pd ions. After heating, the solution was dispersed in acetone and the centrifugation was conducted at 10000 rpm for 20 min to separate the Pd NPs from the solution. The separated Pd NPs were washed by n-hexane and ethyl alcohol to remove the residual PVP and EG, and then dispersed in ethyl alcohol to make the 0.18 wt% Pd NPs dispersion. The zeta-potential of the synthesized Pd NPs was measured to  $-53 \text{ (}\pm 1.9) \text{ mV}$ , and this attributed to the excellent dispersing property of the Pd NPs in ethyl alcohol.

#### 2.1.2. Direct ED of Cu on Ta

Fig. 2.1 illustrates a schematic diagram of the direct Cu ED process assisted by the Pd NPs. A blanket or 55 nm patterned SiO<sub>2</sub>/Si substrate covered with a Ta barrier layer (7 nm, PVD) was used as the substrate. The substrate was cut to 1.5 × 1.5 cm<sup>2</sup>, and the native Ta oxide was removed by immersing the specimen in a solution containing 0.6 M HF and 0.3 M HNO<sub>3</sub> for 10 min (blanket) or 3 min (pattern, the adjustment in the immersion time was inevitable because of a vulnerable Ta barrier layer at the sidewall of the pattern). The process not only removes the native oxide but also improves the hydrophilicity of the Ta surface. After the Ta oxide removal process and a subsequent rinsing step, the Pd NPs were loaded onto substrate by coating 0.1 mL of the dispersion, and dried on hot plate for 15 min at 80°C to evaporate the ethyl alcohol.

The electrolyte for the deposition of the Cu seed layer consisted of 0.3 M  $Cu_2P_2O_7$  and 1.0 M  $K_4P_2O_7$  (Cu-Pyro bath). The Cu seed layer was formed onto the Pd NPs-loaded Ta substrate by direct Cu ED via two steps: a nucleation step and a film formation step. The deposition potential and charge amount in each case were fixed to -1.5 V (vs. saturated calomel electrode; SCE) and 6 mC cm<sup>-2</sup>. After the deposition of the seed layer, annealing was conducted at  $100^{\circ}$ C for 30 min in a  $N_2$  atmosphere to improve the adhesion of the seed layer.

The electrolyte for additional Cu deposition was comprised of 0.25 M CuSO<sub>4</sub> and 1 M

$H_2SO_4$  (Cu-Sul bath). 88  $\mu$ M PEG (Mw = 3400 g mol<sup>-1</sup>), 1 mM NaCl, and 50  $\mu$ M SPS were added as additives for the trench filling. Prior to the gap-filling, the Cu native oxide on the Cu seed layer was removed by dipping the specimen into a solution containing 0.02 M citric acid and 0.03 M KOH for 30 s.  $^{107}$

Figure 2.1. Schematic diagram of the direct Cu ED process on Ta assisted by the Pd NPs.

# 2.2. Direct ED of Cu on Co/Ni alloy

The experimental scheme of direct Cu ED on Co/Ni alloy layer prepared by ELD on SiO<sub>2</sub> dielectric is similar with that depicted in Fig. 1.11 of all-wet metallization. However, the Cu seed layer formation step was omitted by the modification of the entire all-wet metallization process.

#### 2.2.1. Pretreatment of substrate and SAM-Pd activation

Blanket or patterned,  $1.5 \times 1.5 \text{ cm}^2 \text{ SiO}_2/\text{Si}$  substrate samples were etched with 0.6 M HF solution for 5 s to remove air-born oxide and contaminants. After rinsing the etched samples with deionized water, an APTES-SAM was formed on the substrate by immersion in a toluene solution containing 1 wt% APTES for 10 min at  $60\,^{\circ}\text{C}$ . The SAM-bearing substrate was then dipped in a Pd NPs dispersion for 3 min to induce the adsorption of Pd NPs. The dispersion contained 3 nm average diameter Pd NPs which were synthesized by a polyol method as described in Chapter 2.1.1. Dispersion concentration was adjusted to 0.01 wt% by dilution with ethyl alcohol.

#### 2.2.2. ELD of Co/Ni alloy films and direct Cu ED

After SAM-Pd activation of the samples, ELD of Co or Ni alloy films was performed on the samples. The composition of each ELD bath is presented in Table 2.1. Whereas the pH of Ni alloy ELD bath was set as 5, that of Co alloy ELD bath was adjusted to 10 due to low deposition kinetic of Co ELD in acidic environment.

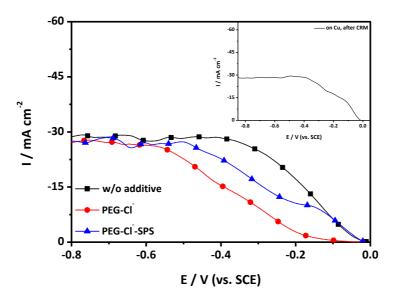

Before direct Cu ED on electroless Co or Ni alloy layers, the native oxide of the alloy layer was removed by a coulometric reduction process in a 0.01 M  $H_2SO_4$  solution along with 100  $\mu$ A cm<sup>-2</sup> of cathodic current for 100 s. The electrolyte for Cu ED contained 0.25 M CuSO<sub>4</sub> and 1.00 M  $H_2SO_4$ . Conventional additives for bottom-up filling [88  $\mu$ M PEG (Mw = 3400 g mol<sup>-1</sup>), 1 mM NaCl, and 50  $\mu$ M SPS] were added to the electrolyte during trench filling. <sup>103-106</sup>

Table 2.1. Composition of ELD Bath for the Deposition of NiWP / CoWP / NiCoP

|                                  | NiWP          | CoWP         | NiCoP         |

|----------------------------------|---------------|--------------|---------------|

| citrate                          | 0.08 M        | 0.07 – 0.4 M | 0.07 M        |

| CH <sub>3</sub> COO              | 0.06 M        | -            | -             |

| $H_3BO_3$                        | -             | 1 M          | 1 M           |

| NiSO <sub>4</sub>                | 0.075 M       | -            | 0.03 – 0.01 M |

| CoSO <sub>4</sub>                | -             | 0.04 M       | 0.01 – 0.03 M |

| Na <sub>2</sub> WO <sub>4</sub>  | 0.02 M        | 0.03 M       | -             |

| additive                         | 0 - 5 ppm PEG | 1.15 mM ATRA | 1.15 mM ATRA  |

| NaH <sub>2</sub> PO <sub>2</sub> | 0.25 M        | 0.05 – 0.3 M | 0.05 M        |

| рН                               | 5             | 10           | 10            |

| temp.                            | 90°C          | 90°C         | 90°C          |

# 2.3. Direct ELD of Cu on Ru

### 2.3.1. Pretreatment of Ru and direct Cu ELD

The experimental scheme of direct Cu ELD on Ru covered specimen is illustrated in Fig. 2.2. Cu ELD was performed on a  $1.5 \times 1.5$  cm<sup>2</sup> coupon Si wafer covered with ALD-Ru (30 nm on blanket and 7 nm on patterned substrate). Prior to ELD, all substrates were immersed in 0.6 M HF solution for 3 min to remove the native oxide layer on the surface. Subsequent to pretreatment, each substrate was dipped into the Cu ELD solution consisting of 4 mM CuSO<sub>4</sub>, 8 mM ethylenediaminetetraacetic acid (EDTA), and 12 mM p-HCHO (para-formaldehyde) or NH<sub>2</sub>NH<sub>2</sub>. The solution pH was adjusted by KOH to 12.8, and the temperature was maintained at 70°C using a thermostat.

The effect of HF application on Ru substrate was examined by coulometric reduction method (CRM). The CRM was conducted in  $0.01~M~H_2SO_4$  electrolyte with the cathodic current density of  $100~\mu A~cm^{-2}.^{110}$  In addition, the formation and the deposition amount of Cu films were determined by linear sweep voltammetry (LSV) which was conducted in a 0.05~M tetramethylammonium hydroxide (TMAH) containing solution.

#### 2.3.2. Preparation of Ru electrode and EQCM monitoring

To investigate the surface state and mass change during Cu ELD, electrochemical quartz crystal microbalance (EQCM) monitoring was introduced. A Ru electrode was prepared by Ru displacement reaction on the Cu-coated AT-cut crystal QCM electrode (QA-A9M-Cu(M), mirror finish, Seiko EG&G model, A = 0.196 cm<sup>2</sup>). The displacement of Cu to Ru was performed in a solution consisting of 0.5 mM RuCl<sub>3</sub> and 0.1 M HClO<sub>4</sub>, for 30 s at 70°C. Before the displacement, native Cu oxide was removed by cathodic polarization in 0.1 M H<sub>2</sub>SO<sub>4</sub> solution at 5 mA cm<sup>-2</sup> for 5 min.<sup>97</sup> The prepared Ru electrode was dipped into the Cu ELD solution after the oxide removal.

Figure 2.2. Schematic illustration of direct Cu ELD process on Ru substrate.

# 2.4. Instrumentation

Solutions were agitated during mixing and temperature adjustment. However, solutions were quiescent during the pretreatment, activation, and deposition steps. In all electrochemical experiments, including LSV, CRM, and ED, specimen was loaded onto a laboratory-made electrochemical cell that exposed 1 cm<sup>2</sup> of the sample surface. SCE and platinum (Pt) wire were used as reference and counter electrodes, respectively. A potentiostat (PAR 2273, EG&G) was used for the ED process and the electrochemical analysis. On the other hand, the potential and mass change during the EQCM observation were simultaneously recorded by potentiostat (263A, EG&G) and QCM (QCA917, EG&G).

A field emission scanning electron microscope (FESEM; S-4800, Hitachi), a transmission electron microscope (TEM; JEM-2100F, JEOL), and an atomic force microscope (AFM; 5100 AFM, Agilent Technologies) were utilized for the microscopic observations. A focused ion beam (FIB; Quanta 3D FEG, FEI) was used to prepare the specimen for the TEM analysis. In addition, an X-ray photoelectron spectroscope (XPS; AXIS-His, Kratos) and an Auger electron spectroscopy (AES; PHI 670, Perkin-Elmer) were used for the spectroscopic analyses.

Sheet resistance (R<sub>S</sub>) of the specimen was measured by using a 4-point probe (CMT-SP 2000N, Advanced Instrument Technology). Film resistivity was calculated based on the

film thickness and  $R_S$ , assuming that major path for current flow is along the film surface. An X-ray diffractometer (XRD; D8-Advance, Bruker Miller) was used to characterize film crystallinity.

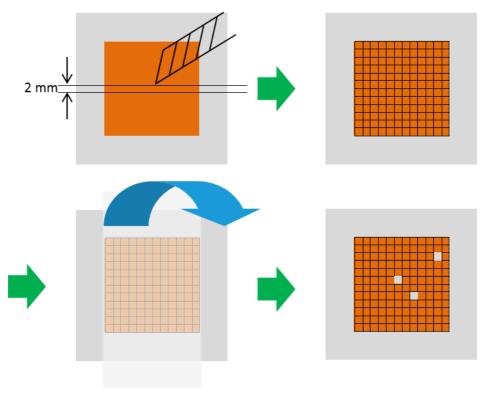

Film adhesion of the specimen was assessed by the tape test method proposed in ASTM D3359. The testing per ASTM D3359, the specimen surface was divided into  $2 \times 2$  mm<sup>2</sup> squares by using sharp cutting tool. The area of the film that detached after tape removal was used to calculate the percentage of area removed (PAR) value (Fig. 2.3).

Figure 2.3. Schematic illustration of method for film adhesion test referring to ASTM D3359.<sup>111</sup>

# CHAPTER III. Direct ED of Cu on Ta

# 3.1. Seed layer formation by direct Cu ED on blanket Ta substrate

#### 3.1.1. Pd NPs loading on blanket Ta substrate

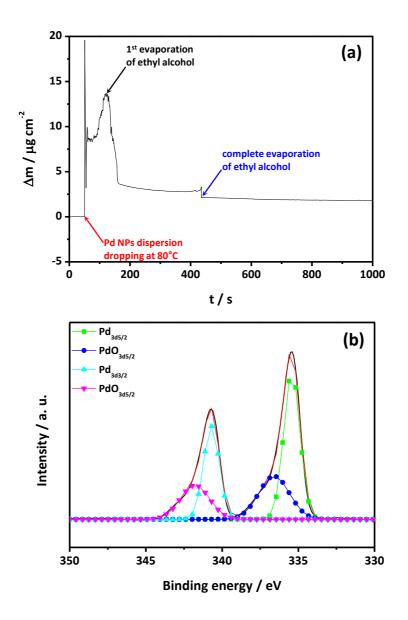

by TEM. The TEM observation was conducted after sampling and drying the Pd NPs dispersion on TEM grid (Formvar Grid 100mesh, Cu). As shown in Fig. 3.1a and b, the synthesized Pd NPs had a uniform size distribution with average size of 3.0 (±0.4) nm. The amount of Pd NPs loaded on the substrate following the method described in Chapter 2.1.2 was measured by QCM by coating the QCM electrode with Pd NPs dispersion. The frequency change according to the drying time was measured, and the mass change was calculated based on it. As depicted in Fig. 3.2a, initial fluctuation of the mass occurred after the Pd NPs loading (50 s) and abrupt decrease of the mass occurred after the complete evaporation of ethyl alcohol (430 s). By the calculation, the fixing amount of Pd NPs was determined to 1.8 μg cm<sup>-2</sup>. Moreover, distinct Pd-related peaks were identified by XPS analysis after the Pd NPs loading onto Ta substrate. As can be seen in Fig. 3.2b, there existed peaks related to Pd and PdO (The PdO seemed

The synthesized Pd NPs that would act as a promoter for Cu nucleation were analyzed

to be formed during the drying process by the oxidation of Pd).

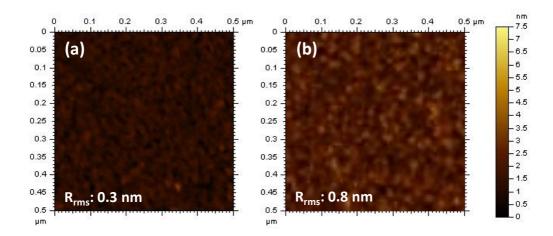

The distribution of Pd NPs on Ta substrate after loading was evaluated by comparing the surface morphology measured by AFM. As depicted in Fig. 3.3a and b, the surface morphology was rarely changed except the slight increase in the surface roughness, indicating that no severe aggregation of Pd NPs occurred on the surface. Therefore, it could be expected that the Pd NPs were quite uniformly distributed over the Ta substrate after loading. The improved hydrophilicity of Ta surface after pretreatment seemed to facilitate the uniform wetting of the Pd NPs dispersion during the coating process.

#### 3.1.2. Cu seed layer formation by direct Cu ED on Pd NPs-loaded Ta substrate

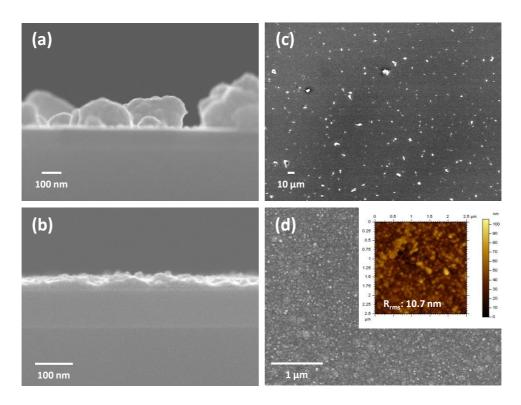

After removing the ethyl alcohol by drying, the deposition of the Cu seed layer on the highly resistive Ta barrier was performed using a basic Cu-Pryo bath. Generally, the use of basic electrolyte gives higher nucleation density on highly resistive substrate during the ED, which facilitates the formation of the continuous Cu seed layer. As already be mentioned in Chapter 2.1.2, The Cu seed layer formation step was composed of two potentiostatic ED steps; a nucleation step and a film formation step. After performing the ED process, Cu film was exclusively formed on Pd NPs-loaded Ta as shown in Fig. 3.4. It was presumed that, during the nucleation step, the Cu nuclei were primarily developed on the loaded Pd NPs because the Pd NPs promoted the electron transfer. During the film

formation step, Cu film formation was completed via the coalescence between the Cu nuclei. Consequently, 18 ( $\pm 4.8$ ) nm of Cu film was deposited on the Ta substrate, as depicted in Fig. 3.4b.

However, the seed layer showed an irregular thickness with a root mean square roughness ( $R_{rms}$ ) value of 10.7 nm, as shown in Fig. 3.4d. The non-uniform thickness distribution should be originated from the preferential growth of the deposited Cu during the film formation step. Cu nuclei which developed on Pd NPs during the nucleation step would prompt the Cu ion reduction even more than Ta or Pd NPs. Cu film deposition with a rough surface morphology would not be avoidable in the event of non-uniform growth.

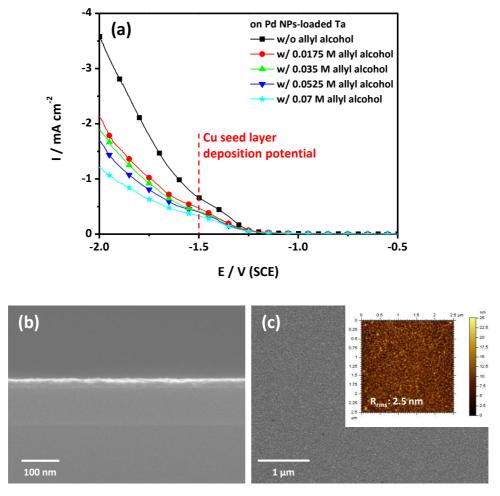

In order to solve the surface roughness problem, allyl alcohol, which has been applied as a leveler during the deposition of a Cu-Zn alloy in a pyrophosphate-based electrolyte, was adopted. Despite the lack of information, it was reported by Senna *et al.* that allyl alcohol suppressed the Cu deposition by forming a stable complex with Cu ion, and improved the surface uniformity during the Cu-Zn alloy deposition process. Similarly in this study, the addition of allyl alcohol clearly suppressed the kinetics of Cu deposition as depicted in Fig. 3.5a. Consequently, the uniformity of the Cu seed layer was significantly improved by the addition of 0.035 M allyl alcohol into the Cu-Pyro bath (Fig. 3.5b and c). Owing to the brightening effect of the allyl alcohol, the thickness of the Cu seed layer decreased to 12 (±1.2) nm and the R<sub>rms</sub> value was reduced to 2.5 nm.

The adhesion of the Cu seed layer was tested via the tape test method. The adhesion of the Cu seed layer was markedly affected by the thermal treatment at  $100\,^{\circ}$ C for 30 min in a  $N_2$  atmosphere, decreasing PAR value from 19.4% to 6.7%. The improvement also had a positive influence on the subsequent Cu ED. Without the thermal treatment, peeling-off of Cu deposit was observed when a 100 nm thick Cu film was electrodeposited on the seed layer. On the other hand, the film remained intact on the thermally-treated Cu seed layer showing the PAR value of 12.5%. Therefore, the thermal treatment was performed after the seed layer formation in all cases.

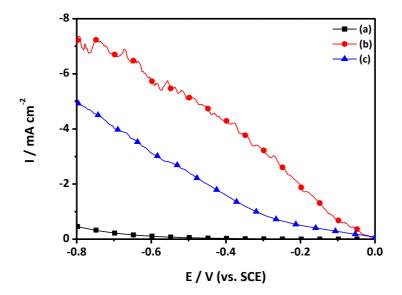

Subsequent to the seed layer formation, LSV in a Cu-Sul bath was conducted on the seed layer. As depicted in Fig. 3.6, the Cu deposit formed on the blanket Ta gave the lowest current density, and the on-set potential for the Cu reduction ( $\eta_{red, Cu}$ ) was -0.5 V (vs. SCE). This occurred because the Cu film was not completely formed on the bare Ta substrate. In contrast,  $\eta_{red, Cu}$  was positively shifted to 0.0 V (vs. SCE) on the Cu seed layers deposited on the Pd NPs-loaded Ta substrates. At the same time, the current density was high on the Cu seed layers in all of the potential ranges investigated. Despite the similar  $\eta_{red, Cu}$  value, a higher current density was observed on the Cu seed layer deposited without allyl alcohol compared to that deposited with 0.035 M allyl alcohol, as expected given that ally alcohol reduced the surface roughness.

In addition, the effect of the additives, an accelerator and a suppressor, all of which are essential for trench filling in a Cu-Sul bath, was tested on a Cu seed layer by LSV. A seed

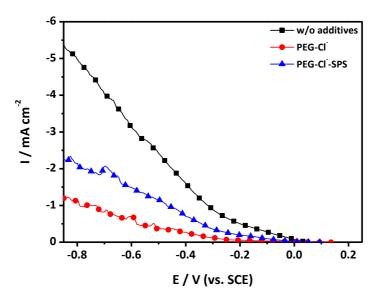

layer deposited on the Pd NPs-loaded Ta with 0.035 M allyl alcohol was used to test the additive effect. In Fig. 3.7, the additives worked well on the seed layer, as on a conventional Cu electrode. That is, a combination of PEG and Cl suppressed the reduction of the Cu ions, and the addition of the SPS accelerated the Cu ion reduction on the seed layer, as usual.

Figure 3.1. (a) TEM image of synthesized Pd NPs on TEM grid and (b) number probability of Pd NPs according to the particle size.

Figure 3.2. (a) The mass change during the Pd NPs coating process on QCM electrode and (b) XPS analysis of the Ta substrate after Pd NPs loading.

Figure 3.3. The AFM surface morphology of Ta substrate (a) before and (b) after the Pd NPs loading.

Figure 3.4. FESEM images of Cu deposited on (a, c) blanket Ta and (b, d) Pd NPs-loaded Ta substrates. Inset in (d): AFM image of the specimen.

Figure 3.5. (a) LSV on Pd NPs-loaded Ta substrate with the addition of allyl alcohol to the Cu-Pyro bath (scan rate =  $10 \text{ mV s}^{-1}$ ). (b, c) FESEM images of Cu film deposited on Pd NPs-loaded Ta substrate with 0.035 M allyl alcohol. Insets in (c): AFM image of the specimen.

Figure 3.6. LSV on Cu deposited on (a) the blanket Ta, (b) the Pd NPs-loaded Ta without allyl alcohol, and (c) the Pd NPs-loaded Ta with 0.035M allyl alcohol. LSV experiments were conducted in Cu-Sul bath (scan rate =  $10 \text{ mV s}^{-1}$ ).

Figure 3.7. LSV on a Cu seed layer prepared on the Pd NPs-loaded Ta by direct ED in Cu-Pyro bath containing 0.035 M allyl alcohol. LSV experiment was conducted in Cu-Sul bath (scan rate =  $10~\text{mV s}^{-1}$ ) and the concentration of each additive is specified in the Chapter 2.1.2.

# 3.2. Trench filling by direct Cu ED on patterned Ta substrate

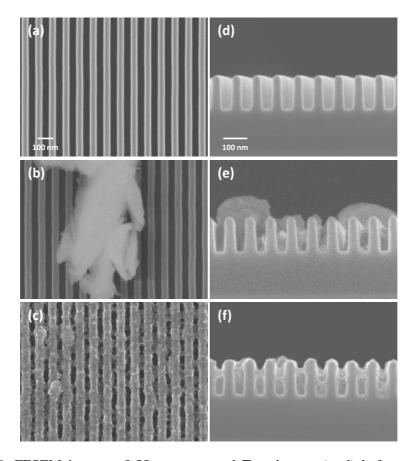

Direct Cu ED was also applied to a 55 nm patterned Ta substrate to form a seed layer and to fill the trench. Fig. 3.8a and d present the 55 nm patterned substrate covered with 7 nm of a Ta barrier layer. As was expected, only irregular Cu islands were observed on the rib of the trench after the seed layer formation steps when Pd NPs were not loaded (Fig. 3.8b and e). In contrast, a Cu seed layer was deposited on the bottom, side, and top of the trench of the Pd NPs-loaded Ta substrate, as depicted in Fig. 3.8c and f, although the uniformity of the seed layer was poor. Therefore, allyl alcohol was used again during the seed layer formation process on the trench.

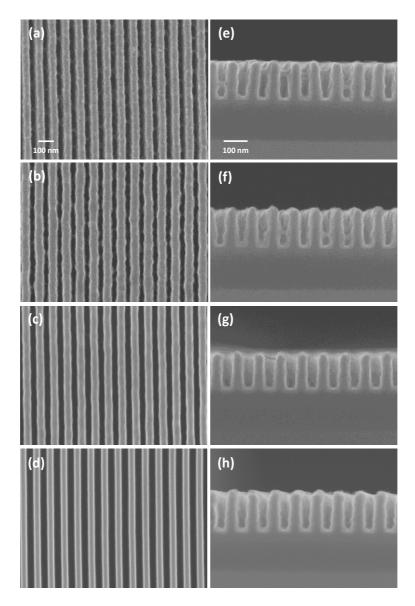

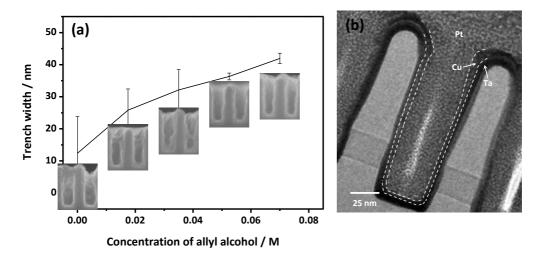

The effect of the allyl alcohol content on the uniformity of the seed layer was investigated by FESEM images, as depicted in Fig. 3.9. These images show that the uniformity of the seed layer was gradually improved with increase in the concentration of allyl alcohol. To compare the seed layer uniformity quantitatively, the trench opening after the formation of the seed layer was measured, as shown in Fig. 3.10a. Finally, when 0.07 M of allyl alcohol was added, the width of the trench opening approached to that of a Ta substrate, which was sufficient to be applied for the trench filling step. Based on the TEM image in Fig. 3.10b, the thickness of the seed layer was measured as  $5.1 \pm 0.3$ , bottom) nm,  $4.3 \pm 0.3$ , side) nm, and  $5.5 \pm 0.6$ , top) nm, indicating the formation of a conformal seed layer.

The brightening effect was not observed on the patterned substrate with 0.035 M allyl alcohol, which was sufficient concentration on the blanket substrate. It indicated that the surface concentration of allyl alcohol would change with the surface area of the substrate at the same bulk concentration. Therefore, the increased allyl alcohol concentration (0.07 M) was required for obtaining the smooth deposit on the patterned substrate, due to the large surface area of the patterned substrate compared to that of the blanket substrate.

Galvanostatic ED was carried out to fill the trench covered with the seed layer. A Cu-Sul bath was used in combination with PEG-CI<sup>-</sup>-SPS as additives for the filling. The applied cathodic current was set to 5 mA cm<sup>-2</sup> and the deposition process was stopped when the accumulated charge amount exceeded 300 mC cm<sup>-2</sup>. TEM observation result after cutting by a FIB is illustrated in Fig. 3.11. Without any defects or voids, a 55 nm patterned substrate was successfully filled.

Figure 3.8. FESEM images of 55 nm patterned Ta substrate (a, d) before seed layer deposition and after seed layer formation (b, e) without Pd NPs and (c, f) with Pd NPs.

Figure 3.9. FESEM images of Cu seed layer deposited on 55 nm patterned Ta with Pd NPs, according to the allyl alcohol concentration. Allyl alcohol content in Cu-pyro bath was (a, e) 0.0175 M, (b, f) 0.035 M, (c, g) 0.0525 M, and (d, h) 0.07 M.

Figure 3.10. (a) Trench opening width after Cu seed layer formation with varying the allyl alcohol concentration in Cu-Pyro bath and (b) TEM image for the Cu seed layer deposited with 0.07 M allyl alcohol (Pt was sputtered before the TEM specimen preparation by FIB).

Figure 3.11. TEM analyses of 55 nm patterned trench covered with the Cu seed layer after filling in Cu-Sul bath. The Cu seed layer was prepared by direct ED on the Pd NPs-loaded Ta with 0.07 M allyl alcohol in Cu-Pyro bath.

# CHAPTER IV. Direct ED of Cu on Co/Ni alloy

# 4.1. ELD of Co/Ni alloy barrier layer

### 4.1.1. Optimization of substrate activation process

The effectiveness of a SAM-Pd activation process on the subsequent ELD procedure was examined by comparing with ELD of NiWP on a SiO<sub>2</sub> substrate activated via conventional Sn-Pd activation process. Conventional Sn-Pd activation process is sequentially carried out by adsorption of colloidal Sn particles on the substrate, followed by covering metallic Pd through displacement reaction between Sn and Pd ions. Then the substrate is "activated" for a subsequent ELD process as Pd can catalyze the ELD. The merit of introducing colloidal Sn particles is that they adsorb well on various substrates and activate substrates including non-conductive material. Nevertheless, ELD of NiWP on Sn-Pd activated SiO<sub>2</sub> substrate induced non-uniform deposit formation as shown in Fig. 4.1a. Thus it was inevitable to introduce SAM on SiO<sub>2</sub> substrate for the activation because the result should be originated from poor adsorption strength of Sn-Pd particles on SiO<sub>2</sub>. Consequently by using SAM-Pd activated SiO<sub>2</sub> substrate, we could obtain uniform NiWP film by ELD as shown in Fig. 4.1b.