# The Characteristics and Reliability of In-Ga-Zn-O Thin-Film Transistors on Glass and Flexible Polyimide Substrate under Temperature and Illumination Stress

유리와 플라스틱 기판에 제작한 인듐갈륨징크 산화물 박막 트랜지스터의 온도와 빛의 특성 및 신뢰성에 관한 연구

2013년 2월

서울대학교 대학원

전기·컴퓨터 공학부

### 국 승 희

### Abstract

## The Characteristics and Reliability of In-Ga-Zn-O Thin-Film Transistors on Glass and Flexible Polyimide Substrate under Temperature and Illumination Stress

Seung-Hee Kuk

School of Electrical Engineering and Computer Science College of Engineering Seoul National University

Recently, flexible displays have attracted considerable attention in the emerging electronic device market. Flexible plastic substrates have the advantages such as flexibility, ruggedness and light-weight and its low cost, compared to glass substrate. Indium-Gallium-Zinc-Oxide thin-film transistors (IGZO TFTs) are promising candidates for next generation display backplane due to high mobility, good uniformity, and low process temperature, which suitable for flexible display.

In this thesis, the characteristics and reliability of flexible IGZO TFTs were presented and discussed.

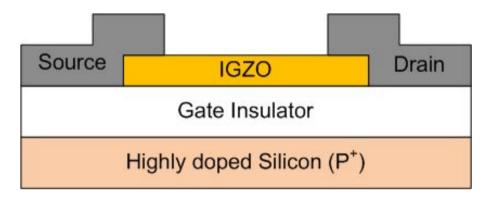

Firstly, the electrical characteristics and reliability of IGZO TFTs on glass substrate are discussed. The IGZO TFTs were fabricated on a glass substrate with an inverted staggered structure. The initial electrical characteristics and gate bias induced instability was investigated. And drain bias induced instability is investigated. Unique degradation phenomenon was observed under the high drain bias stress. After the high drain bias stress, the drain current, measured at the low drain bias, was significantly decreased. Based on the experimental results, I proposed a degradation model for the high drain bias induced degradation. And light-induced hysteresis of IGZO TFTs is investigated. Hysteresis was observed under the 450-nm illumination, and was increased with temperature. And hysteresis was increased with wavelength decrease. Lightinduced hysteresis occurs due to increased sub-band gap states at the interface between the gate insulator layer and the active layer. Also, bias illumination stress induced instability is investigated. The transfer curve did not change after positive bias illumination stress. However, the transfer curve shifted to a negative direction after negative bias illumination stress. The transfer curve could be shifted to the negative direction after negative bias illumination stress due to the increase of V<sub>0</sub><sup>2+</sup> states.

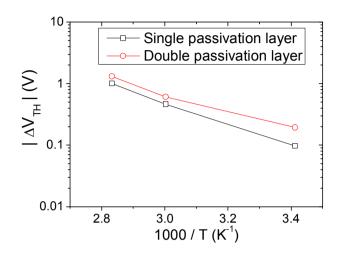

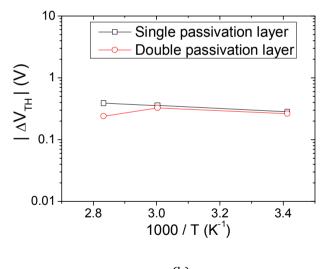

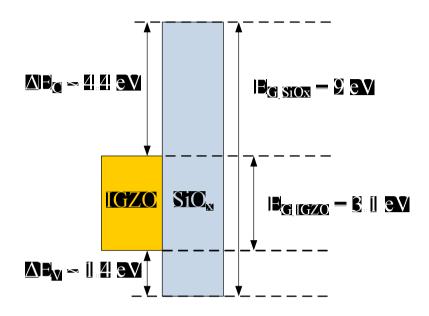

Secondly, the electrical characteristics and reliability of IGZO TFTs on flexible substrate are discussed. The IGZO TFTs were fabricated on a polyimide (PI) substrate with an inverted staggered structure. An inorganic buffer layer, composed of SiO<sub>2</sub> and SiN<sub>x</sub> multi-layer, was employed, in order to prevent the environmental stress, such as water or oxygen molecules. The effects of PI and inorganic buffer layer on the characteristics and reliability of IGZO TFTs were investigated. And the effects of passivation layer on the electrical stability of IGZO TFTs with single passivation layer and double passivation layer fabricated on PI substrate were investigated. The positive bias stress and negative bias stress were applied to the IGZO TFTs at various temperatures from 20 °C to 80 °C. The threshold voltage shift of double passivation device was slightly less than that of single passivation device under PBTS. The threshold voltage shift of NBTS is considerably increased than that of PBTS at high temperature due to

the difference between conduction band offset and valence band offset. Lastly, the effects of mechanical bending on the electrical stability of flexible IGZO TFTs were investigated.

Keywords: thin-film transistor, Indium-Gallium-Zinc-Oxide (IGZO), flexible display, reliability Student Number: 2009-30178

### Contents

| Abstracti                                                   |

|-------------------------------------------------------------|

| Contentsiv                                                  |

| List of Tablesvii                                           |

| List of Figures viii                                        |

| Chapter 1 Introduction1                                     |

| 1.1 Evolution of display technology2                        |

| 1.2 Outline of this thesis10                                |

| Chapter 2 Review of IGZO TFTs and flexible display          |

| technology11                                                |

| 2.1 Recent issues of IGZO TFTs12                            |

| 2.1.1 Reliability under bias temperature stress             |

| 2.1.2 Reliability under negative bias illumination stress   |

| 2.1.3 Reliability under various environments24              |

| 2.2 Various backplane materials for flexible display        |

| Chapter 3 The electrical characteristics and reliability of |

| IGZO TFTs on glass substrate33                              |

| 3.1 Overview                                                |

| 3.2 Fabrication process of IGZO TFTs on glass substrate     |

| 3.3 Electrical characteristics of IGZO TFTs                 |

| flexible IGZO TFTs109                                             |

|-------------------------------------------------------------------|

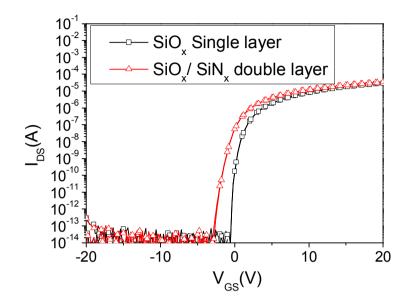

| 4.5 Effects of passivation layer on the electrical stability of   |

| flexible IGZO TFTs115                                             |

| 4.5.1 Introduction115                                             |

| 4.5.2 Experimental methods 117                                    |

| 4.5.3 Experimental results and discussions                        |

| 4.5.4 Conclusion                                                  |

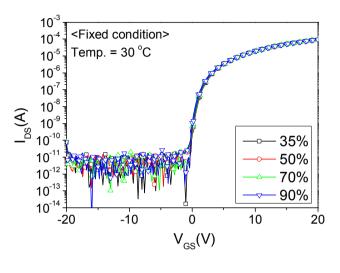

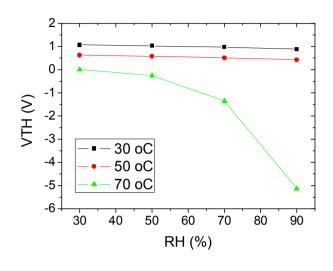

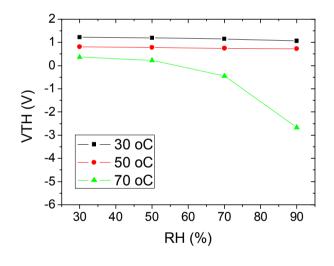

| 4.6 Effects of humidity on the electrical characteristics of IGZO |

| TFTs128                                                           |

| 4.7 Effects of mechanical bending on the electrical stability of  |

| flexible IGZO TFTs139                                             |

| Chapter 5 Summary154                                              |

| Bibliography156                                                   |

| 초 록175                                                            |

### List of Tables

| Table 2-1 The continuous use temperature and characteristics of the plastic    |

|--------------------------------------------------------------------------------|

| substrates. [93, 94]32                                                         |

| Table 3-1 The layers information of the fabricated oxide TFTs.    38           |

| Table 3-2 The extracted parameter of the fabricated IGZO TFTs                  |

| Table 4-1 The layers information of the fabricated flexible oxide TFTs 104     |

| Table 4-2 The extracted parameters of the fabricated IGZO TFTs employing oxide |

| interface and nitride interface114                                             |

| Table 4-3 Fabricated device parameters measured at 20 °C 126                   |

### **List of Figures**

| Figure 1-1 The evolution of display technology                                                                             |

|----------------------------------------------------------------------------------------------------------------------------|

| Figure 1-2 Four-inch QVGA bottom-emission AMOLED display driven by oxide TFTs without any pixel compensation circuit. [27] |

|                                                                                                                            |

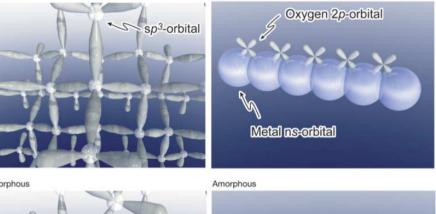

| Figure 2-1 Schematic orbital drawings for the carrier transport paths in                                                   |

| crystalline and amorphous semiconductors. (a) Covalent semiconductor,                                                      |

| for example, silicon (b) oxide semiconductor. [22]13                                                                       |

| Figure 2-2 Comparison of the effect of a positive and a negative gate bias stress                                          |

| on the transfer characteristics. [31]16                                                                                    |

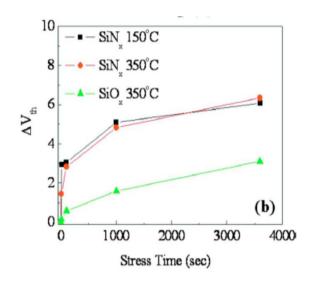

| Figure 2-3 (a) The variations in the $V_{\text{TH}}$ shift for IGZO TFTs with various gate                                 |

| dielectrics (SiN <sub>x</sub> 150 °C, SiN <sub>x</sub> 350 °C, and SiO <sub>x</sub> 350 °C) as a function of               |

| stress time. [32] (b) The variations in the Von and mobility shift for IGZO                                                |

| TFTs with plasma treatment as a function of stress time. [35]17                                                            |

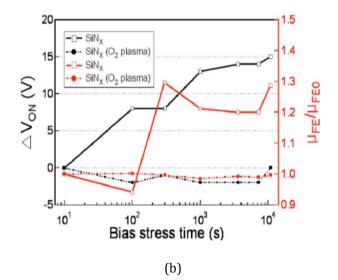

| Figure 2-4 The evolution of transfer curves as a function of the applied -20 V NBS                                         |

| time (a) in the dark and (b) under green light exposure. [57]20                                                            |

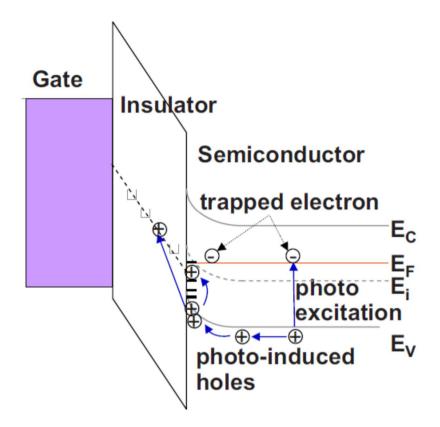

| Figure 2-5 Schematic energy band diagram to explain photo-induced hole                                                     |

| trapping. [51]21                                                                                                           |

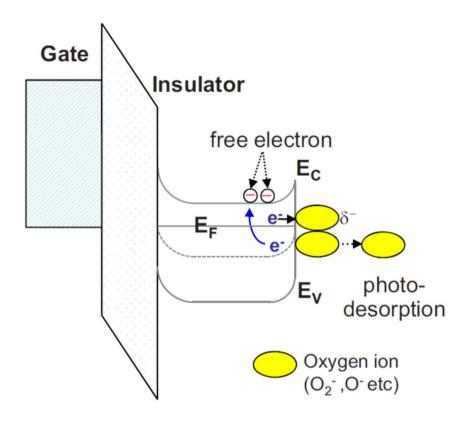

| Figure 2-6 Schematic energy band diagram showing the photo-desorption of                                                   |

| oxygen molecules into the ambient atmosphere for the un-passivated                                                         |

| device under the application of NBS. [60]22                                                                                |

| Figure 2-7 Schematic energy band diagram showing the sub-band gap states                                                   |

| related to oxygen vacancy. [57]23                                                                                          |

|                                                                                                                            |

| Figure 2-8 Shifts of transfer curves at different oxygen partial pressures. [70]26                                         |

- Figure 3-2 Transfer curves of fabricated IGZO TFTs by repeated measurement..40

- Figure 3-4 Transfer curves before and after (a) 30 V and (b) 50 V gate bias stress. A detailed stress condition is shown in the figures......44

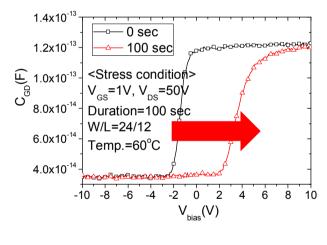

- Figure 3-8 (a) Gate-source capacitance (C<sub>GS</sub>) and (b) gate-drain capacitance (C<sub>GD</sub>) versus gate bias curves (C-V curves) before and after 40 V drain bias stress. C<sub>GD</sub> versus gate bias curves before and after (c) 30 V drain bias stress and (d) 50 V drain bias stress.

- Figure 3-10 Comparison of output curves before and after high drain bias stress between (a) simulation and (b) experimental data. Comparison of transfer curves before and after high drain bias stress between (a) simulation and (b) experimental data.

- Figure 3-12 Transfer characteristics of IGZO TFTs under various sweep ranges with 450 nm illumination (a) [ $V_{GS} = -10 \sim 10V$ ,  $-20 \sim 20V$ ,  $-30 \sim 30V$ ], (b) [ $V_{GS} = -30 \sim 30V$ ,  $-30 \sim 10V$ ,  $-10 \sim 30V$ ]......71

Figure 3-13 (a) The energy level of sub-band states of neutral oxygen vacancy

| (V_0), singly ionized oxygen vacancy (V_0^+) and doubly ionized oxygen  | en |

|-------------------------------------------------------------------------|----|

| vacancy ( $V_0^{2*}$ ). (b) Formation energies vs Fermi level for oxyge | en |

| vacancies in ZnO in the 0, 1+, and 2+charge states, under Zn-ri-        | ch |

| conditions. [117]                                                       | /2 |

- Figure 3-15 Band diagram of IGZO TFTs with light illumination under (a) negative gate bias and (b) positive gate bias......74

- Figure 3-18 C-V characteristics under dark and light-illumination measured at (a) 60°C (W/L = 1000/6) and (b) 90°C (W/L = 2000/6)......85

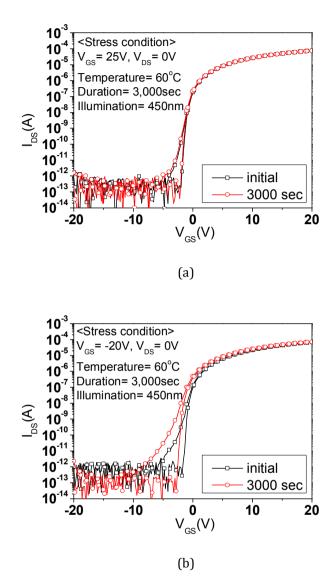

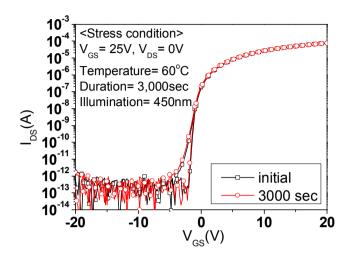

- Figure 3-21 Transfer curves before and after (a) positive bias illumination temperature stress and (b) negative bias temperature illumination stress. A detailed stress condition is shown in the figures......92

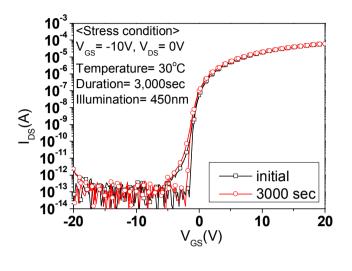

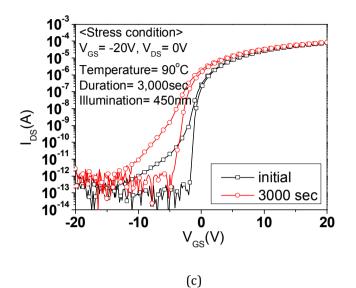

Figure 3-22 Transfer curves before and after (a) -10 V, (b) -20 V, and (c) -30

| negative bias temperature illumination stress. A detailed stress condition |

|----------------------------------------------------------------------------|

| is shown in the figures94                                                  |

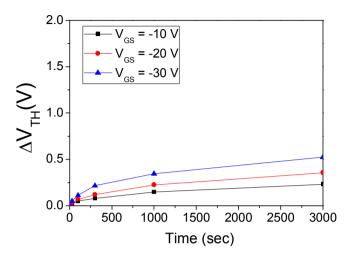

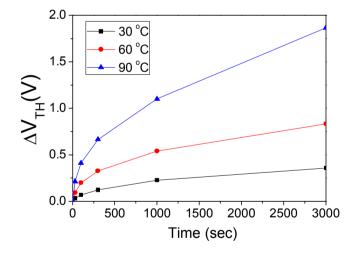

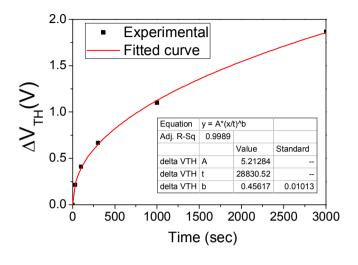

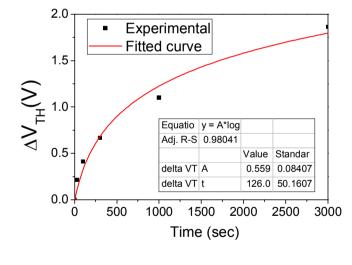

| Figure 3-25 Time dependence of threshold voltage shift ( $\Delta V_{\text{TH}}$ ) due to negative |

|---------------------------------------------------------------------------------------------------|

| bias illumination stress under 90 °C. Fitting to (a) power law and (c)                            |

| logarithmic law are shown as solid lines                                                          |

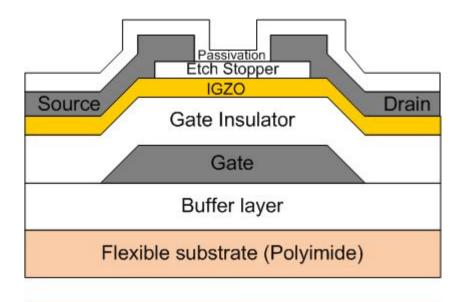

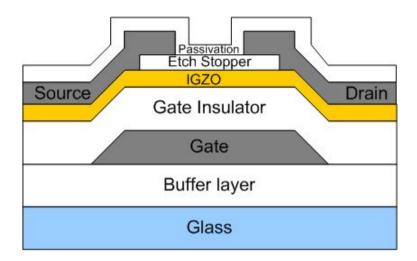

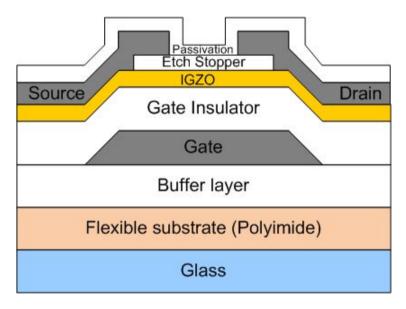

| Figure | 4-2  | The   | cross-sectional  | view   | of  | fabricated | IGZO | TFTs | on | (a) | glass |

|--------|------|-------|------------------|--------|-----|------------|------|------|----|-----|-------|

|        | subs | trate | and (b) polyimid | e subs | tra | te         |      |      |    |     | 106   |

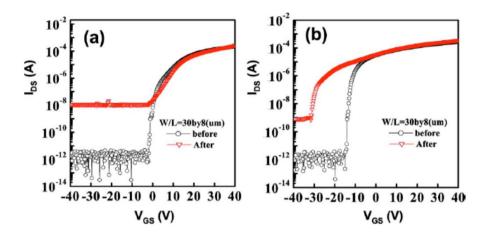

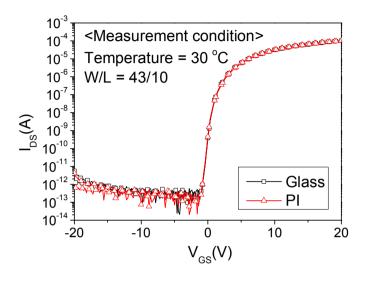

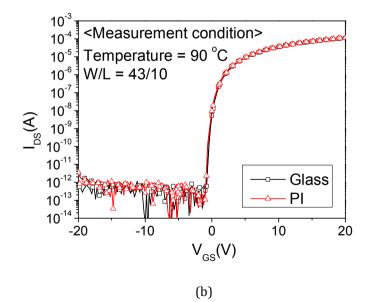

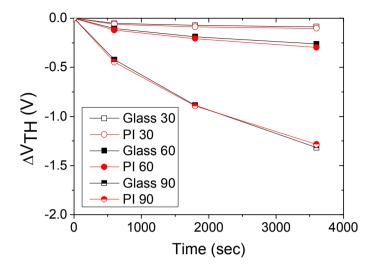

Figure 4-3 Comparison of transfer curves between glass substrate and PI substrate under (a) 30 °C (b) 90 °C...... 107

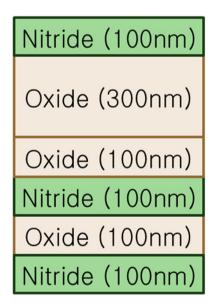

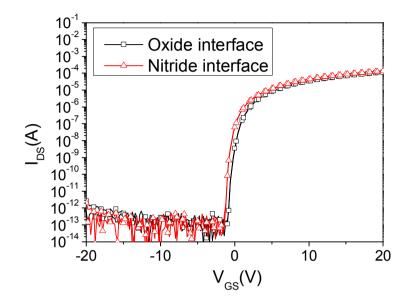

Figure 4-5 Schematic of inorganic multi-buffer layer with an (a) oxide interface and (b) nitride interface. Detailed layer information is shown in figures.

Figure 4-6 Transfer curves of fabricated IGZO TFTs employing oxide interface and

| nitride interface |

|-------------------|

|-------------------|

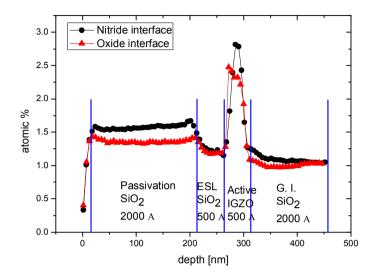

Figure 4-7 Hydrogen atomic ratio versus depth profile of oxide interface and nitride interface measured by secondary ion mass spectroscopy (SIMS).

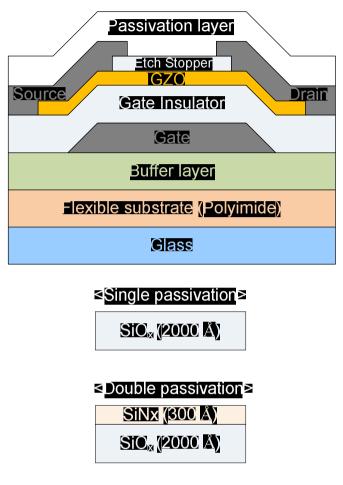

| Figure 4-8 Cross sectional view of fabricated IGZO TFT on glass/ PI substrate. |

|--------------------------------------------------------------------------------|

| SiO_x (2000 Å) single passivation layer and SiO_x/ SiN_x (2000 Å/ 300 Å)       |

| double passivation layer are fabricated respectively118                        |

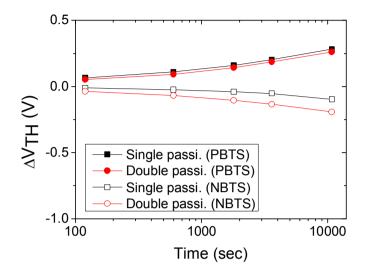

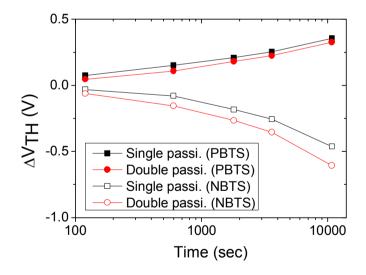

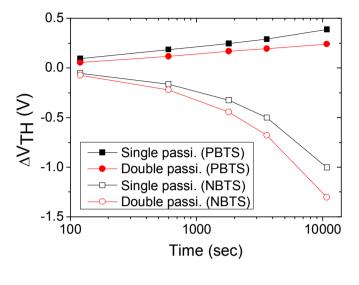

Figure 4-10 Threshold voltage shift vs stress time for stress applied at various temperature: (a) 20 °C, (b) 60 °C, and (c) 80 °C. For PBTS (NBTS) test, V<sub>GS</sub> was applied to 30 V (-30 V) and V<sub>DS</sub> was applied to 0.1V for 3 hours..... 123

Figure 4-13 The cross-sectional view of the fabricated un-passivated oxide TFTs.

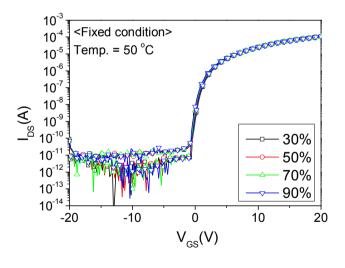

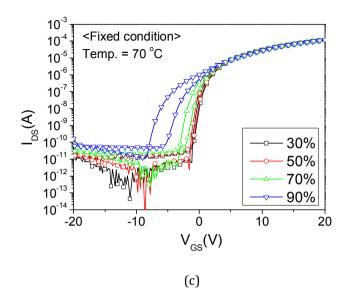

Figure 4-14 The transfer curves of the fabricated un-passivated IGZO TFTs under

(a) 30 °C (b) 50 °C (c) 70 °C as a function of relative humidity...... 133

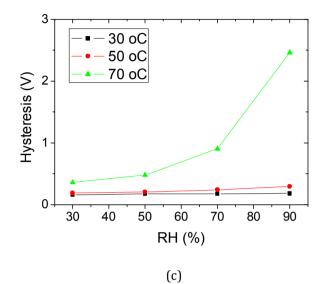

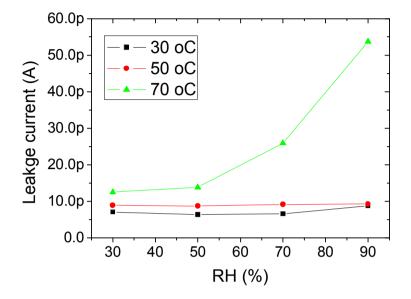

| Figure 4-16 Leakage current as a function of relative humidity under 30 °C, 50 °C,              |

|-------------------------------------------------------------------------------------------------|

| and 70 °C136                                                                                    |

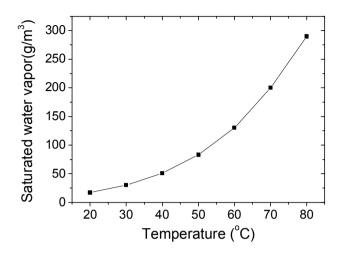

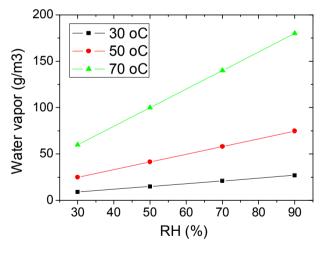

| Figure 4-17 (a) Saturated water vapor as a function of temperature. (b) Current                 |

| amount of water vapor as a function of relative humidity under 30 $^{\circ}\mathrm{C},$         |

| 50 °C, and 70 °C                                                                                |

| Figure 4-18 Schematic showing the adsorption of the water molecules under (a)                   |

| high water vapor and (b) low water vapor138                                                     |

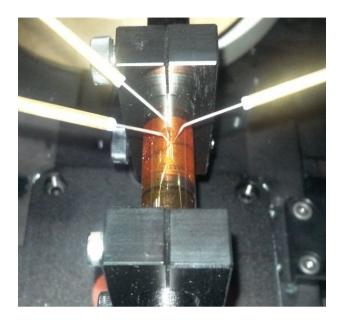

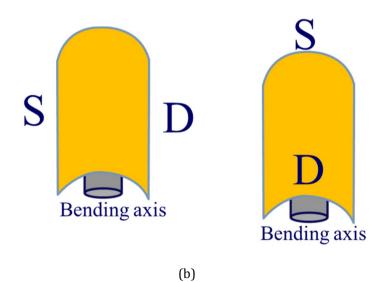

| Figure 4-19 (a) A photograph of bending measurement system. (b) Schematic                       |

| showing bending direction perpendicular to channel (left) and parallel to                       |

| channel (right)142                                                                              |

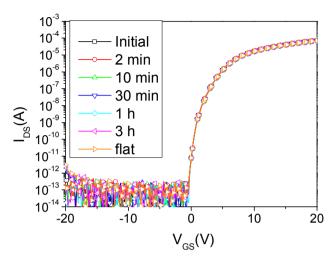

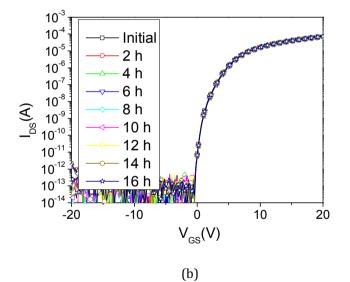

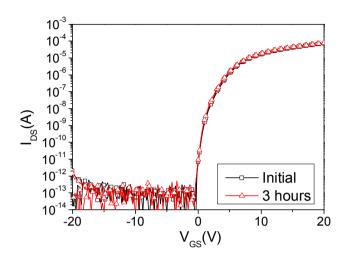

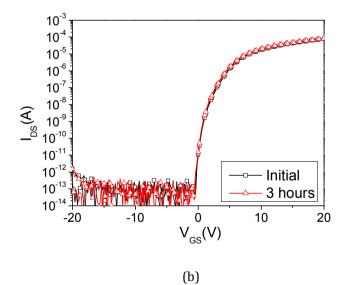

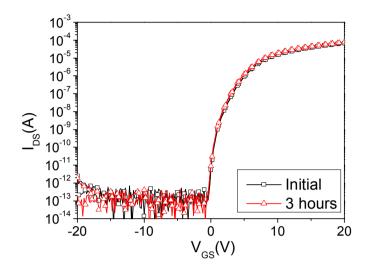

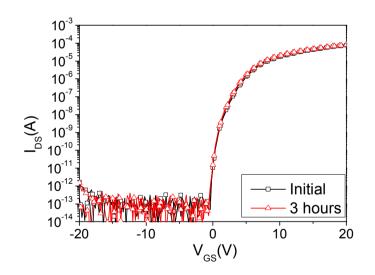

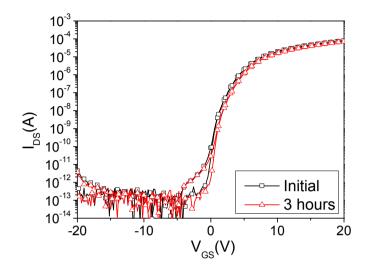

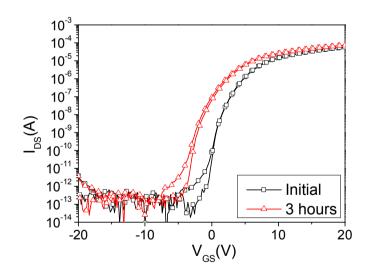

| Figure 4-20 (a) A change of transfer curves on standing state for 3 hours under 5               |

| mm bending radius. (b) A change of transfer curves on standing state for                        |

| additional 16 hours under 5 mm bending radius143                                                |

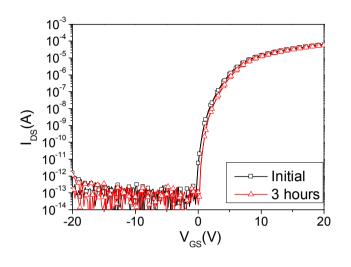

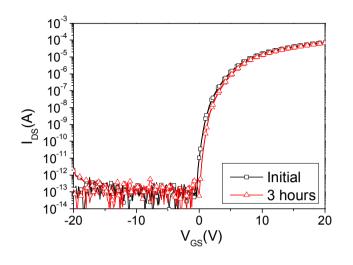

| Figure 4-21 Shifts of transfer curves under PBTS ( $V_{GS}$ = 30 V, $V_{DS}$ = 0.1 V) under 5   |

| mm bending radius. (a) Bending direction is perpendicular to channel and                        |

| (b) bending direction is parallel to channel                                                    |

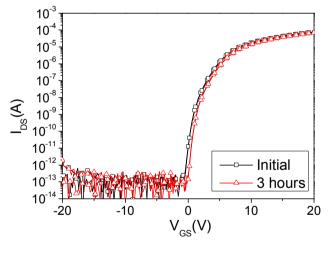

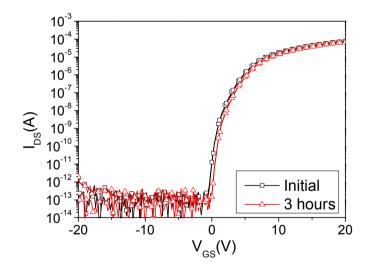

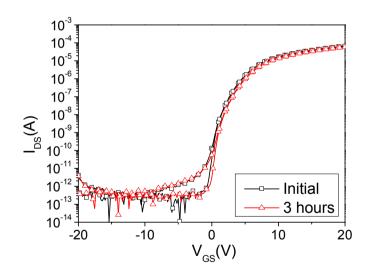

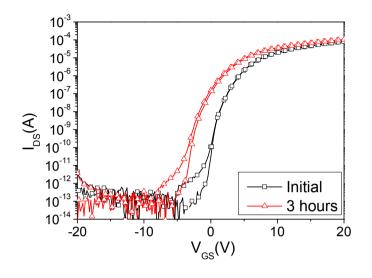

| Figure 4-22 Shifts of transfer curves under NBTS ( $V_{GS}$ = -30 V, $V_{DS}$ = 0.1 V) under    |

| 5 mm bending radius. (a) Bending direction is perpendicular to channel                          |

| and (b) bending direction is parallel to channel145                                             |

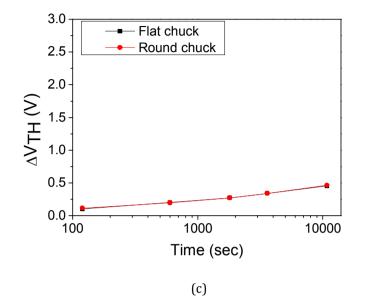

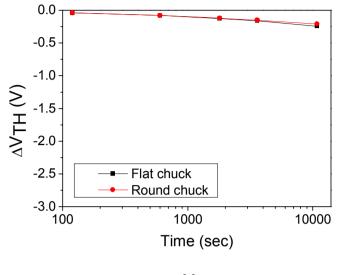

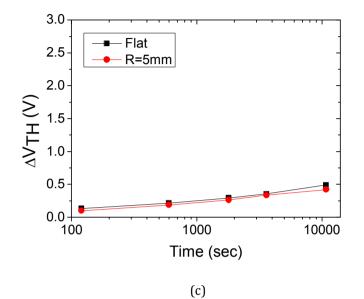

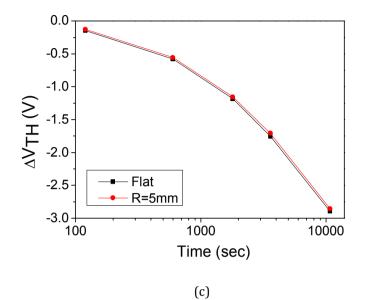

| Figure 4-23 Shifts of transfer curves under PBTS ( $V_{GS}$ = 30 V, $V_{DS}$ = 0.1 V) under (a) |

| flat condition and (b) 5 mm bending radius. (c) Threshold voltage shift                         |

| under PBTS as a function of time of flat condition and bending condition.                       |

|                                                                                                 |

| Figure 4-24 Shifts of transfer curves under NBTS ( $V_{GS}$ = -30 V, $V_{DS}$ = 0.1 V) under    |

(a) flat condition and (b) 5 mm bending radius. (c) Threshold voltage shift

under NBTS as a function of time of flat condition and bending condition.

### **Chapter 1 Introduction**

Recently, flexible displays have attracted considerable attention in the emerging electronic device market. Flexible plastic substrates have the advantages such as flexibility, ruggedness and light-weight and its low cost, compared to glass substrate. Indium-Gallium-Zinc-Oxide thin-film transistors (IGZO TFTs) are promising candidates for next generation display backplane due to high mobility, good uniformity, and low process temperature, which suitable for flexible display. There have been a lot of attempts to apply the IGZO TFTs for flexible display, but still need more verification. Therefore, it is very critical to investigate the characteristics and reliability of flexible IGZO TFTs.

### 1.1 Evolution of display technology

Flat panel displays (FPDs) were considered a very attractive alternative to the cathode ray tube (CRT) as illustrated in Figure 1-1. There are various FPDs such as a liquid crystal display (LCD), a plasma display panel (PDP), an organic light emitting diode (OLED) display, and a field emission display (FED), which can be defined by the types of materials and the display method they use [1-4]. They have the merits providing large area, the slim and light-weight and high-resolution images, which are not achieved easily with CRTs and projection display.

Among all the FPDs, the most successful display technology to emerge so far is the LCDs. LCDs are thin, light-weight, bright and cost-effective due to the lowtemperature process on glass substrates. Therefore, they have enabled successful applications to laptop computers or desktop monitors, which occupy the large portion of FPD market. Also, the low voltage drive for portable applications is possible, so that the target market is not limited by an increasing diverse set of systems.

The development of active matrix liquid crystal displays (AMLCDs) for high resolution and full-color display has been achieved by the thin-film transistors (TFTs). The active matrix display employing the TFT as a pixel switch has enhanced the capability of high quality image processing, so that the importance of LCDs in commercial fields increases. Hydrogenated amorphous silicon thin film transistors (a-Si:H TFTs) have been widely used for AMLCDs due to their high productivity on large area glass substrates by low temperature process below 400 °C. The a-Si TFT can represent the gray scale by switching the voltage data and charging the capacitors of each pixel element. However, the poor current driving characteristics of a-Si:H TFT due to the low field effect mobility

(< 0.5  $\text{cm}^2/\text{V}\cdot\text{sec}$ ) are the limitation in realization of the high resolution display [5, 6].

The problem of low carrier mobility of a-Si:H TFTs can be solved by employing the polycrystalline silicon (Poly-Si) film as an active layer in the TFT. Generally, Poly-Si film is fabricated by recrystallization of the a-Si:H film deposited at low temperature below 400 °C. Poly-Si TFTs have attracted considerable attentions due to its high electron mobility (30 ~ 500 cm<sup>2</sup>/V·sec) and current driving capability [7, 8]. Compared with an a-Si:H TFT, the superior electrical characteristics of the poly-Si TFT allow a fast switching, required for the high resolution image. In addition, poly-Si TFTs enable implementing the complementary metal oxide semiconductor (CMOS) technology and integrating the peripheral driver circuits and pixel switching devices simultaneously on a glass substrate.

ELA technologies have been extensively studied to fabricated high qualty poly-Si thin film on a large area glass substrate [8-10]. It employs the pulsed laser induced rapid heating of the a-Si film, and more than 90% of the excimer laser energy is absorbed within shallow depth (~20 nm) from the surface of a-Si film during the tens of nano-seconds of laser pulse duration. It is noted that the low temperature (< 400 °C) crystallization of a-Si film on a glass can be obtained by ELA without any thermal damage to the glass. Therefore, it is possible to integrate the digital and analog drivers such as inverter, level-shifter, shift register, digital-to-analog converter (DAC), and amplifier by employing low temperature poly-Si (LTPS) TFTs on the glass panel.

However, although the ELA LTPS TFT technology is attractive and researched widely due to its high performances, the electrical properties of the ELA LTPS TFTs are still insufficient to realize the high quality displays and need to be improved yet in terms of the non-uniformity of grain-boundaries induced by the fluctuation of ELA energy. Additionally, the LTPS technology has a cost issue to fabricate TFTs compared with a-Si technology. The crystallization of a-Si film is critical to proceed to the stable process. The troublesome vacuum break process such as the crystallization and the doping process lead to low throughput and high sensitivity of electrical properties variation. Therefore, the conventional LTPS TFT process requires more process steps than a-Si TFT, decreasing the process yield.

In 1987, *C. W. Tang* and *S. A. VanSlyke* reported luminescence from an organic material [11]. They deposit small molecules to form a layered structure in a vacuum. The layered structure is sandwiched between an anode and cathode. The thin (< 1  $\mu$ m) of organic material permits a high electric field at low voltage. Thus, a light from thin film organic materials is usually produced at low voltage. OLED displays exhibit superb electro-optical properties such as a fast response (~ several  $\mu$ sec) to the image addressing and a wide viewing angle due to selfemissive characteristics. Many research groups have been investigating new organic materials and new configurations of devices to improve efficiency and stability of OLED displays [12-15]. Therefore, AMOLED displays employing the TFT backplane have the potential for new technology comparable to the AMLCDs.

The electro-optical performance of AMOLED is very sensitive to the characteristics of TFT. A small variation of the OLED current in the each pixel may cause a critical non-uniform image problem because the OLED luminance is controlled by the current driving. Thus, each TFT pixel in AMOLED panel requires a constant current source that maintains a desired image data during the whole emission time.

For a reliable current driving with a low voltage in a limited pixel area, such as a

high density display, LTPS TFTs may be attracted as the pixel element rather than a-Si TFTs because they can supply sufficient OLED current by a small circuit area due to their high current driving capability. Although some LTPS TFT based AMOLED display have been shown, they need to be improved due to the current non-uniformity [14, 16]. The random creation of grain boundaries during the crystallization varies the output current in pixel to pixel due to the non-uniform field effect mobility and threshold voltage of the poly-Si TFT [8-10]. Therefore, the I<sub>OLED</sub> compensation pixel circuits, which can compensate the non-uniform characteristics of poly-Si TFTs, are required for the uniform luminance in the display panel. There are two approaches to compensate the current variation: the voltage programming and the current programming, and each method have merits and drawbacks in itself [17, 18].

The a-Si technology widely used in AMLCDs is considered for large area AMOLED displays due to its low fabrication cost and excellent uniformity. However, the critical problem of the long-term device degradation would be a huge barrier to meet the needs for high quality. Therefore, the degradation of the a-Si:H TFT should be compensated by the pixel circuit and the new driving scheme to suppress the degradation of a-Si TFTs itself should be developed. This would require a rather complicated compensation circuit compared with the poly-Si TFT based pixel design. However, it is not easy to fabricate the compensation circuit in every pixel of limited dimension due to large size a-Si:H TFT components and the space required for the layout of additional signals and capacitors of the circuit.

Nowadays, TFT technology is challenging the realization of flexible displays on transparent plastic substrate and metal foil [19, 20]. Flexible plastic substrates have some merits such as flexibility, ruggedness and light-weight and its low cost, ultimately, compared with glass substrate. These merits make plastic substrate

attractive for portable systems such as a smart phone, and a tablet PC. However, the TFT technology on plastic substrate must overcome the limitation of process temperature. Plastic substrate has a much lower thermal budget, so that the process temperature of the TFT fabrication should be sufficiently low [21]. The most of commercially developed plastic substrates can stand low temperature below 200 °C, and the critical temperature of plastic substrates is determined by the inherent characteristics of plastics [21]. Limited process temperature affects the deposition of films and the physical properties of the films tend to be deteriorated with the decrease of the process temperature. Due to the lack of thermal treatment, characteristics of the TFTs on plastic may be degraded much compared with those of the TFTs on glass.

Oxide semiconductor materials are promising candidates for next generation display materials due to a relative high mobility, which is large enough to fabricate a high-speed transistor for driving the AMLCDs [22-24]. In addition, oxide semiconductor materials have an amorphous phase, which shows uniform electrical properties even with a large-size display [22, 25, 26]. High resolution, such as ultra-high defition (UD :  $3840 \times 2160$ ), a high frame rate (> 240 Hz), and large size display (more than 70 inches) require the higher electrical performance than that of the a-Si TFTs. At least 3 cm<sup>2</sup>/V·s of field-effect mobility is required to satisfy such demands, which is not so easy to achieve by the conventional amorphous silicon material [27].

Furthermore, the oxide semiconductor TFTs has advantageous to the AMOLED. In general, LTPS TFTs employed to drive AMOLEDs because they exhibit high mobility and good electrical stability than a-Si:H TFTs. However, the LTPS TFT has a problem with the uniformity which is originated from the non-uniform grain sizes in the poly-Si film. Consequently, the LTPS TFT is not suitable for the AMOLED TV. Even for a small size AMOLED panel, a compensation circuit is required in order to maintain uniform image quality for the LTPS TFT. Therefore, many demonstrations of AMOLEDs driven by the oxide semiconductor TFTs have been shown [27, 28]. Figure 1-2 shows four-inch QVGA bottom-emission AMOLED display driven by oxide TFTs without any pixel compensation circuit [27].

Another advantage of the oxide semiconductor based TFTs over the siliconbased TFTs is that the oxide semiconductors are transparent in the visible light region. Zinc oxide based semiconductor, such as indium-gallium-zinc-oxide, exhibits large optical band gap (> 2.8 eV) compared to silicon-based semiconductor [29, 30]. Due to large band gap characteristics, the oxide semiconductor exhibits low leakage current.

Figure 1-1 The evolution of display technology.

Figure 1-2 Four-inch QVGA bottom-emission AMOLED display driven by oxide TFTs without any pixel compensation circuit. [27]

#### **1.2 Outline of this thesis**

This study focuses on the characteristics and reliability of flexible IGZO TFTs under various environments. Recent technical trend in flat panel display industry is the high resolution display and flexible display. In order to meet the two trends, IGZO TFTs are promising candidates. In this thesis, IGZO TFTs were fabricated on glass and flexible substrate, and investigated the characteristics and reliability under various environments.

Chapter 2 gives a brief introduction to the IGZO semiconductor. Recent issues of IGZO TFTs, such as reliability under negative bias illumination stress and reliability under various environments, are reviewed. Also, various backplane materials for flexible display are reviewed.

Chapter 3 focuses on the electrical characteristics and reliability of IGZO TFTs on glass substrate. Fabrication process and initial electrical characteristics of IGZO TFTs are introduced. Instability of IGZO TFTs under gate bias and drain bias without illumination is investigated. In addition, light-induced hysteresis phenomenon under various temperatures and wavelengths is investigated. Reliability of IGZO TFTs under illumination is also investigated.

Chapter 4 concentrates on the electrical characteristics and reliability of IGZO TFTs on flexible substrate. Comparison between IGZO TFTs on glass substrate and flexible substrate is investigated. The effects of buffer layer, passivation layer, and mechanical bending on the electrical characteristics and reliability of flexible IGZO TFTs are also investigated.

Lastly, I summarize the results of the characteristics and reliability of IGZO TFTs under various environments in Chapter 5.

# Chapter 2 Review of IGZO TFTs and flexible display technology

The flexible IGZO TFTs is now considered as a next generation display technology in active matrix displays. In this chapter, the recent issues of IGZO TFTs, such as reliability under bias temperature stress, negative bias illumination stress, and various environments, are reviewed. Also, various backplane materials for flexible display are reviewed.

#### 2.1 Recent issues of IGZO TFTs

In 2004, Nomura et al. reported an amorphous oxide semiconductors based on IGZO deposited at room temperature, and exhibited high mobility compared to amorphous silicon TFTs ( $\mu_{sat} \approx 7 \text{ cm}^2/\text{V} \cdot \text{s}$ ) [22]. Despite the amorphous state, the origin of the high mobility was attributed to the electronic orbital structure of the material. Figure 2-1 shows schematic orbital drawings for the carrier transport paths in crystalline and amorphous semiconductors. Covalent semiconductors have carrier transport paths composed of strongly directive sp<sup>3</sup> orbitals, so structural randomness greatly degrades the magnitude of bond overlap, that is, carrier mobility [22]. However, amorphous oxide semiconductors composed of post-transition-metal cations. Spheres denote metal s orbitals. The contribution of oxygen 2p orbitals is small. Direct overlap between neighbouring metal s orbitals is rather large, and is not significantly affected even in an amorphous structure [22]. Therefore, amorphous oxide semiconductor could exhibits high mobility even in an amorphous phase.

#### а

Covalent semiconductors, for example, silicon Crystalline

Post-transition-metal oxide semiconductors

Crystalline

Amorphous

Figure 2-1 Schematic orbital drawings for the carrier transport paths in crystalline and amorphous semiconductors. (a) Covalent semiconductor, for example, silicon (b) oxide semiconductor. [22]

#### 2.1.1 Reliability under bias temperature stress

For the stable operation, the device instability under the bias temperature stress should be investigated. During the operation of the display, TFTs have been applied positive or negative bias continuously. It is reported that threshold voltage is positively shifted under positive bias stress, while threshold voltage is scarcely shifted under negative bias stress. Figure 2-2 shows the comparison of the effect of a positive and a negative gate bias stress on the transfer characteristics. [31] The field effect mobility or the sub-threshold slope was not altered. When positive gate bias is applied to the IGZO TFTs, the electrons are accumulated at the channel, and electrons could be trapped at the interface between the IGZO and gate insulator layer. On the other hand, when negative gate bias is applied to the IGZO TFTs, the electrons are depleted at the channel, and electrons could not be trapped. Holes could not accumulate under negative bias, because IGZO is inherently n-type semiconductor.

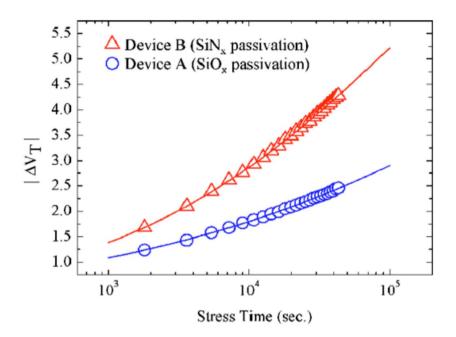

Threshold voltage shift and hysteresis could be improved by high quality gate insulator or plasma treatment at the gate insulator [32-35]. Figure 2-3 (a) shows the variations in the V<sub>TH</sub> shift for IGZO TFTs with various gate dielectrics (SiN<sub>x</sub> 150 °C, SiN<sub>x</sub> 350 °C, and SiO<sub>x</sub> 350 °C) as a function of stress time [32]. The positive Vth shift in the a-IGZO TFTs with the SiN<sub>x</sub> gate dielectric deteriorated significantly during constant bias stress due to the higher hydrogen content in the SiN<sub>x</sub> films providing more charge trap sites, which would produce a high shallow hydrogen-related states. Figure 2-3 (b) shows the variations in the Von and mobility shift for IGZO TFTs with plasma treatment as a function of stress time [35]. The interface treatment by O<sub>2</sub> plasma significantly improves the stability of the a-IGZO TFT. This suggests that the V<sub>TH</sub> shift is determined by the properties of the gate dielectrics, such as the density of charge traps. The degradation mechanism is classified into the charge trapping and the defect state creation. The degradation mechanisms are originated from a-Si:H TFTs [36-39]. The charge trapping process shows the logarithmic time dependence and has very small temperature dependence. On the other hand, the defect state creation process shows the power law time dependence and is thermally activated [37, 39]. The stretched exponential time dependence could be fitted to the charge trapping process [36]. The fabrication process and structure of the IGZO TFTs are not same each other, so the experimental results are. Therefore, the degradation mechanism of IGZO TFTs under bias temperature stress is still debated [31-33, 40-47].

Figure 2-2 Comparison of the effect of a positive and a negative gate bias stress on the transfer characteristics. [31]

(a)

Figure 2-3 (a) The variations in the  $V_{TH}$  shift for IGZO TFTs with various gate dielectrics (SiN<sub>x</sub> 150 °C, SiN<sub>x</sub> 350 °C, and SiO<sub>x</sub> 350 °C) as a function of stress time. [32] (b) The variations in the Von and mobility shift for IGZO TFTs with plasma treatment as a function of stress time. [35]

#### 2.1.2 Reliability under negative bias illumination stress

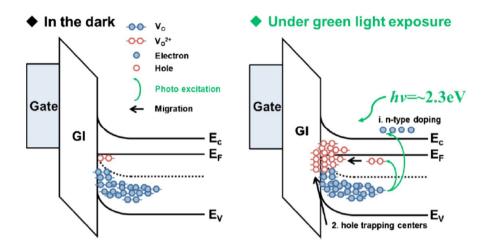

For the stable operation, the device instability under the bias, thermal, illumination, and environmental stress have been intensively studied [31-35, 41, 43, 46, 48-78]. As a result, significant advances in reliability have been made. Nevertheless, reliability under negative bias illumination stress is still remained issue [51-68]. Since switching TFTs of active-matrix liquid crystal displays or organic light emitting diodes are almost always negatively biased and exposed to light during their operation, instability caused by the negative bias illumination stress is a crucial problem to be resolved [57]. Figure 2-4 shows transfer curves as a function of the applied -20 V negative bias stress (NBS) time (a) in the dark and (b) under green light exposure. The device did not suffer from any V<sub>on</sub> shift by NBS in the dark. Meanwhile, V<sub>on</sub> shift of -5.2 V with insignificant change in SS was observed under illumination.

In the case of amorphous silicon, prolonged light illumination reduces the conductivity of the a-Si film, which can be attributed to the formation of a metastable deep-level defect (so called Staebler–Wronski effect) [79, 80]. Therefore, a-Si TFTs under light illumination conditions would be affected adversely by stretching-out of the sub-threshold drain current [56].

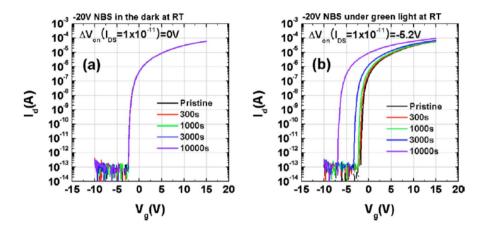

In case of oxide TFTs, however, prolonged negative bias stress with light illumination results in a huge negative shift of the threshold voltage. A couple of degradation models have been proposed to account for this observation. First degradation model is the trapping of photo-generated hole carriers [51, 52]. Figure 2-5 shows the schematic energy band diagram to explain photo-induced hole trapping [51]. Second degradation model is photo-desorption of the oxygen-related molecules [60]. Figure 2-6 shows the schematic energy band diagram showing the photo-desorption of oxygen molecules into the ambient atmosphere

for the un-passivated device under the application of NBS [60]. Third degradation model is the creation of sub band gap states [57, 59]. Figure 2-7 shows the schematic energy band diagram showing the sub-band gap states related to oxygen vacancy [57]. However, the degradation mechanism to explain overall phenomenon is unclear at this stage.

Figure 2-4 The evolution of transfer curves as a function of the applied -20 V NBS time (a) in the dark and (b) under green light exposure. [57]

Figure 2-5 Schematic energy band diagram to explain photo-induced hole trapping. [51]

Figure 2-6 Schematic energy band diagram showing the photo-desorption of oxygen molecules into the ambient atmosphere for the un-passivated device under the application of NBS. [60]

Figure 2-7 Schematic energy band diagram showing the sub-band gap states related to oxygen vacancy. [57]

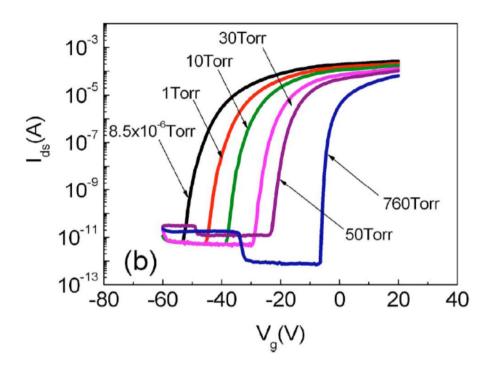

#### 2.1.3 Reliability under various environments

The oxide semiconductor TFTs are sensitive to environmental air, such as oxygen, hydrogen, or water molecules [51, 54, 70-78]. Figure 2-8 shows the shifts of transfer curves at different oxygen partial pressures. [70] As oxygen partial pressure increases, transfer curve is positively shifted. The adsorbed oxygen forms depletion layer below the surface, resulting in positive shift of threshold voltage. Figure 2-9 shows the comparison of the transfer curves before and after the water exposure [73]. Leakage current and sub-threshold slope was increased, after water exposure of the IGZO TFTs.

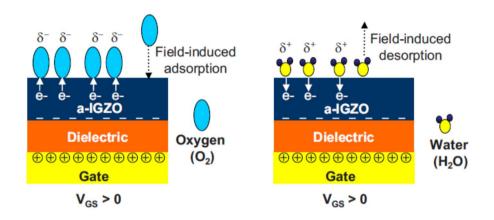

Left of Figure 2-10 shows the schematic showing the electric-field-induced adsorption of oxygen molecules from the ambient atmosphere under the application of positive bias stress. Right of Figure 2-10 shows schematic showing the electric-field-induced desorption of water molecules into the ambient atmosphere under positive bias stress [71].

$O_2(gas) + e^- = 2O^-(solid) - \dots (1)$

The interaction between the backchannel of active layer and ambient plays a critical role in the threshold voltage shifts. The adsorbed oxygen can capture an electron from the conduction band and that the resulting oxygen species can exist in various forms such as  $O^{2-}$ ,  $O^-$ , or  $O_{2^-}$ , as described by the equation (1). As a result, a depletion layer is formed beneath the oxide semiconductor surface, leading to an increase in the threshold voltage.

In order to prevent the effects of the environmental air, the passivation layer is employed. The effects of passivation layer on the stability of IGZO TFTs have been intensively studied [71, 81-87]. Figure 2-11 shows the variations in the  $V_{TH}$  shift for IGZO TFTs with different passivation layer (SiN<sub>x</sub> and SiO<sub>x</sub>) as a function

of stress time [86]. The IGZO TFTs employing SiO<sub>x</sub> passivation layer shows better reliability. The hydrogen incorporation during the nitride growth has generated bulk defects within the semiconductor and/or at the interface between the semiconductor and gate insulator layer. In order to reduce the damage during the deposition of the passivation layer, organic passivation layer and inorganic multi-layer passivation was reported [82, 84].

Figure 2-8 Shifts of transfer curves at different oxygen partial pressures. [70]

Figure 2-9 The comparison of the transfer curves before and after the water exposure for the device with (a) 35-nm-thick and (b) 150-nm-thick channels, respectively. [73]

Figure 2-10 Schematic showing the electric-field-induced adsorption of oxygen molecules from the ambient atmosphere under the application of positive bias stress (left). Schematic showing the electric-field-induced desorption of water molecules into the ambient atmosphere under positive bias stress (right). [71]

Figure 2-11 The variations in the  $V_{TH}$  shift for IGZO TFTs with different passivation layer (SiN<sub>x</sub> and SiO<sub>x</sub>) as a function of stress time. [86]

## 2.2 Various backplane materials for flexible display

Recently, flexible displays have attracted considerable attention in the emerging electronic device market. Flexible plastic substrates have the advantages such as flexibility, ruggedness and light-weight and its low cost, compared to glass substrate. These merits make plastic substrate attractive for portable systems such as a smart phone, and a tablet PC.

However, the TFT technology on plastic substrate must overcome the limitation of process temperature. Plastic substrate has a much lower thermal budget, so that the process temperature of the TFT fabrication should be sufficiently low [21]. The most of commercially developed plastic substrates can stand low temperature below 250 °C, and the critical temperature of plastic substrates is determined by the inherent characteristics of plastics [21]. Limited process temperature affects the deposition of films and the physical properties of the films tend to be deteriorated with the decrease of the process temperature. Due to the lack of thermal treatment, characteristics of the TFTs on plastic may be degraded much compared with those of the TFTs on glass.

Polyethylene naphthalate (PEN), polyethylene terephthalate (PET), polyether sulfone (PES), polycarbonate (PC), polyimide (PI), stainless steel, and thin glass were used as flexible substrate materials [20, 88-94].

PI exhibits 275 °C of the continuous use temperature, orange color, high CTE, good chemical resistance, expensive cost, and high moisture absorption. PES exhibits 230 °C of the continuous use temperature, clear, good dimensional stability, poor solvent resistance, expensive cost, and moderate moisture absorption. PC exhibits 155 °C of the continuous use temperature, clear, poor CTE, inexpensive cost, moderate moisture absorption. PEN exhibits 150 °C of the

continuous use temperature, clear, moderate CTE, good chemical resistance, inexpensive cost, moderate moisture absorption. PET exhibits 120 °C of the continuous use temperature, clear, moderate CTE, good chemical resistance, inexpensive cost, moderate moisture absorption. Table 2-1 summarizes the continuous use temperature and characteristics of the plastic substrates [93, 94].

Various active materials, such as amorphous silicon, low temperature poly silicon, single crystalline silicon, and oxide semiconductor, were considered as flexible display backplane [90, 95-97]. Flexible displays are demonstrated with the combination of various active materials and substrate materials [19, 20, 22, 88-92, 95-106]. Among the various active materials, oxide semiconductor has an advantage of low process temperature. Most of plastic substrates can stand low temperature below 250 °C. Therefore, oxide semiconductor could be fabricated on various plastic substrates.

In this thesis, the PI, coated on glass as rigid carrier, was used, overcoming difficulties in handling flexible freestanding plastic substrates, eliminating the problem of plastic shrinkage with high temperature processing and allowing the use of standard semiconductor fabrication equipment. Until now, deposition of gate insulator and post thermal annealing process are high temperature process (> 300 °C). Therefore, the PI is the most suitable for flexible substrate of oxide TFTs.

Table 2-1 The continuous use temperature and characteristics of the plastic substrates. [93, 94]

| Continuous use<br>temperature | Material                               | Characteristics                                                                                           |

|-------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 275 °C                        | Polyimide (PI)                         | Orange color, high CTE, good<br>chemical resistance, expensive,<br>high moisture absorption               |

| 230 °C                        | Polyether<br>Sulfone (PES)             | Clear, good dimensional stability,<br>poor solvent resistance, expensive,<br>moderate moisture absorption |

| 155 °C                        | Polycarbonate<br>(PC)                  | Clear, poor CTE, inexpensive,<br>moderate moisture absorption                                             |

| 150 °C                        | Polyethylene<br>naphthalate<br>(PEN)   | Clear, moderate CTE, good<br>chemical resistance, inexpensive,<br>moderate moisture absorption            |

| 120 °C                        | Polyethylene<br>terephthalate<br>(PET) | Clear, moderate CTE, good<br>chemical resistance, inexpensive,<br>moderate moisture absorption            |

# Chapter 3 The electrical characteristics and reliability of IGZO TFTs on glass substrate

### 3.1 Overview

Indium-Gallium-Zinc-Oxide thin-film transistors (IGZO TFTs) have gained considerable attention for active matrix displays due to the high field effect mobility and good uniformity [26, 107]. In order to adopt the IGZO TFTs for actual display backplane, the stable characteristics under various stress conditions, such as bias, temperature, and illumination, are required.

In this chapter, the electrical characteristics and reliability of IGZO TFTs on glass substrate are discussed. Firstly, the fabrication process is introduced. The IGZO TFTs were fabricated on a glass substrate with an inverted staggered structure. The etch stopper layer were employed, in order to improve the reliability of IGZO TFTs. After the introduction of device fabrication, the initial electrical characteristics, such as threshold voltage, mobility, sub-threshold slope, on-off ratio, and leakage current level, are introduced. Following the introduction of the initial characteristics, gate bias induced instability without illumination is investigated.

And, drain bias induced instability without illumination is investigated. Unique degradation phenomenon was observed under the high drain bias stress. After the high drain bias stress, the drain current, measured at the low drain bias, was significantly decreased. Based on the experimental results, I proposed a degradation model for the high drain bias induced degradation.

Following the drain bias induced instability, light-induced hysteresis of IGZO TFTs is investigated. Hysteresis was observed under the 450-nm illumination, and was increased with temperature. And hysteresis was increased with wavelength decrease. Light-induced hysteresis occurs due to increased sub-band gap states at the interface between the gate insulator layer and the active layer.

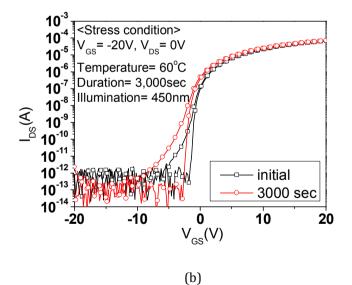

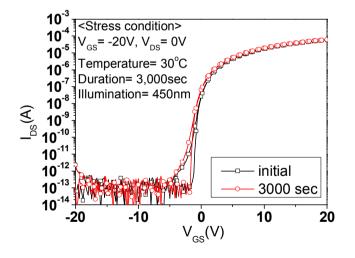

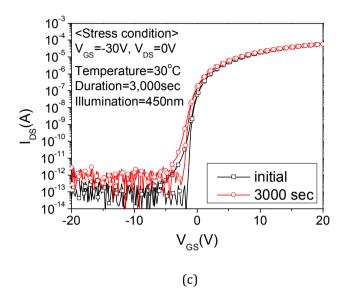

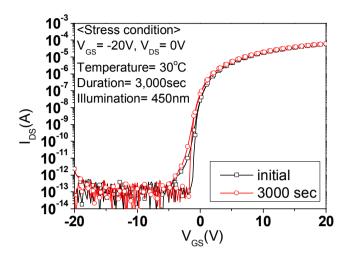

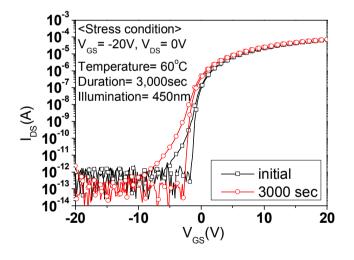

Lastly, bias illumination stress induced instability is investigated. The transfer curve did not change after positive bias illumination stress. However, the transfer curve shifted to a negative direction after negative bias illumination stress. The transfer curve could be shifted to the negative direction after negative bias illumination stress due to the increase of  $V_0^{2+}$  states.

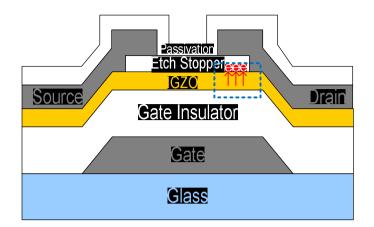

# 3.2 Fabrication process of IGZO TFTs on glass substrate

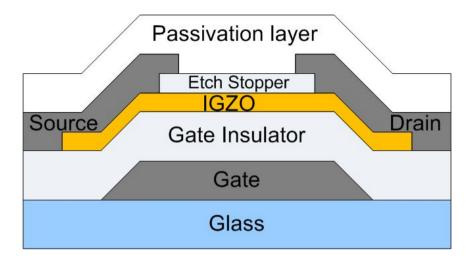

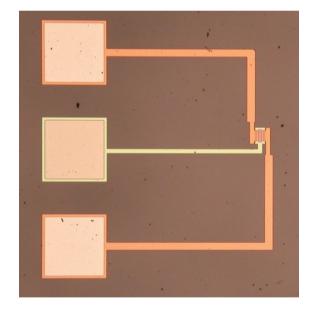

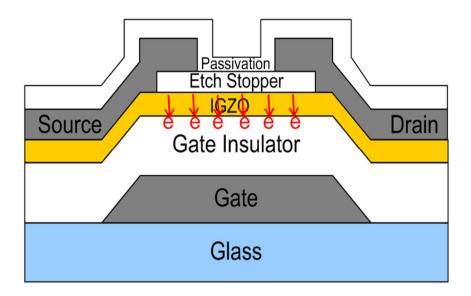

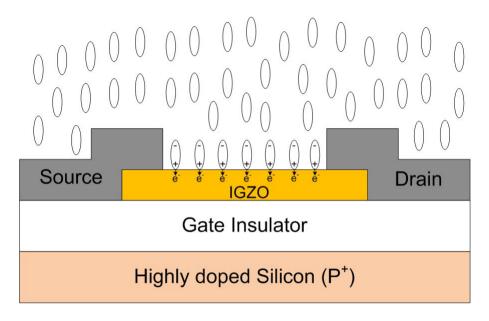

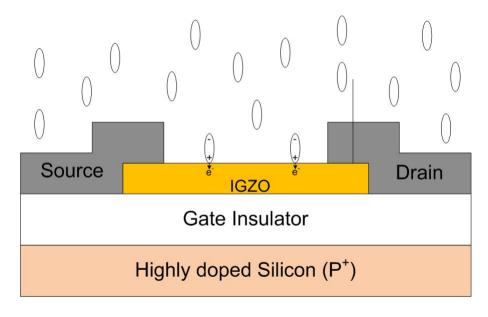

The a-IGZO TFTs were fabricated on a glass substrate with an inverted staggered structure. Figure 3-1 (a) shows the cross sectional view of the fabricated IGZO TFTs. First, Mo/AlNd were deposited and patterned as the gate electrode. SiO<sub>2</sub> of 2,000 Å thickness was then deposited by plasma-enhanced chemical vapor deposition (PECVD) and served as the gate dielectric layer. The IGZO (In:Ga:Zn = 1:1:1) layer with a thickness of 500 Å was deposited by sputtering. The SiO<sub>2</sub> etch stop layer was deposited by PECVD. The source and drain were formed by depositing a layer of Mo and were patterned by dry etching. The SiO<sub>2</sub> layer was used as a passivation layer. Annealing of the device was performed as the final process at 300 °C in ambient air. Table 3-1 summaries the layers information of the fabricated oxide TFTs. Figure 3-1 (b) shows the microscope image of the fabricated oxide TFTs.

The channel width was 24  $\mu$ m and the length was 12  $\mu$ m. The transfer characteristics of the TFTs were evaluated using an Agilent B1500A semiconductor parameter analyzer. For the light illumination test, the device was irradiated by a xenon lamp using narrow band pass filters.

(a)

(b)

Figure 3-1 (a) The cross-sectional view and (b) the microscope image of the fabricated oxide TFTs

| Layer          | Material    | Equipment  |

|----------------|-------------|------------|

| Gate           | Mo/AlNd     | DC sputter |

| Gate Insulator | SiO2 200 nm | PECVD      |

| Active         | IGZO 50nm   | DC sputter |

| Etch stopper   | SiO2 50 nm  | PECVD      |

| Source/Drain   | Мо          | DC sputter |

| Passivation    | SiO2 200 nm | PECVD      |

Table 3-1 The layers information of the fabricated oxide TFTs.

### 3.3 Electrical characteristics of IGZO TFTs

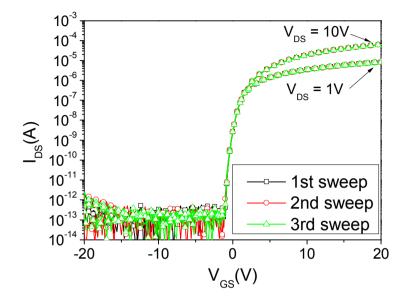

Figure 3-2 shows the transfer curves of fabricated IGZO TFTs by repeated measurement. The transfer curve maintains its origin state under repeated measurement. The threshold voltage ( $V_{TH}$ ) is -0.2 V, and the field effect mobility is 12 cm<sup>2</sup>/V·s. The sub-threshold slope is 200 mV/dec, and the on-off ratio is greater than 10<sup>8</sup>. The leakage current level is less than 10<sup>-12</sup> A. Table 3-2 summaries the extracted parameter of the fabricated IGZO TFTs.

Despite the amorphous state, the origin of the high mobility was attributed to the electronic orbital structure of the material [22]. Zinc oxide based semiconductor, such as IGZO, exhibits large optical band gap (>2.8 eV) compared to silicon-based semiconductor [29, 30]. Due to large band gap characteristics, the oxide semiconductor exhibits low leakage current. Large on-off ratio is attributed to the high mobility and low leakage current. Zinc oxide based semiconductor, such as IGZO, exhibits low sub-band gap states compared to amorphous silicon [108-110]. Small sub-threshold slope of IGZO TFTs is originated from low sub-band gap states characteristics.

Figure 3-2 Transfer curves of fabricated IGZO TFTs by repeated measurement.

| Parameter           | Value               | Unit    |

|---------------------|---------------------|---------|

| V <sub>TH</sub>     | -0.2                | V       |

| Mobility            | 12                  | cm²/V·s |

| Sub-threshold slope | 200                 | mV/dec  |

| On-off ratio        | > 10 <sup>8</sup>   | -       |

| Leakage current     | < 10 <sup>-12</sup> | А       |

Table 3-2 The extracted parameter of the fabricated IGZO TFTs.

### 3.4 Gate bias induced instability without illumination

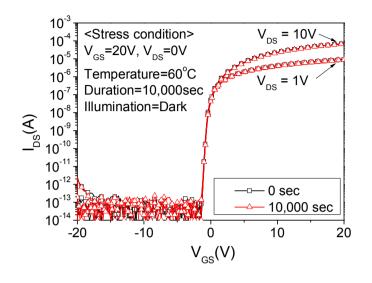

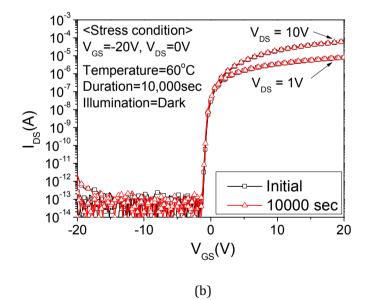

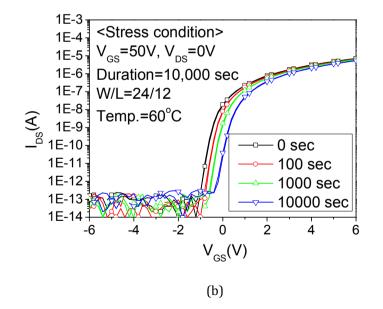

Figure 3-3 shows the transfer curves before and after (a) positive bias temperature stress and (b) negative bias stress conditions. For positive bias stress, gate-source voltage (V<sub>GS</sub>) was applied to 20 V, and drain-source voltage (V<sub>DS</sub>) was applied to 0 V under no illumination for 10,000 seconds. The temperature was set to 60 °C, in order to accelerate degradation. For negative bias stress, V<sub>GS</sub> was applied to -20 V, and the other stress condition was same to positive bias stress. Transfer curve was scarcely changed after positive bias tress (20 V) and negative bias stress (-20 V).

In order to investigate gate bias induced degradation, we applied 30 V and 50 V to the gate bias stress. The other stress condition was same to the above condition. Figure 3-4 shows the transfer curves before and after 30 V and 50 V gate bias stress. In case of 30 V gate bias stress, transfer curve was scarcely changed. The fabricated devices show superior reliability compared to the literatures [31, 41, 46]. In case of 50 V gate bias stress, threshold voltage was positively shifted by the amount of 1.5 V. The other parameters, such as mobility or sub-threshold slope, were scarcely changed.

The dominant degradation mechanism is electron trapping at the interface between gate insulator and IGZO. Figure 3-5 shows the schematic drawing of trapped electrons at the interface between the gate insulator layer and IGZO layer due to high gate bias induced degradation.

(a)

Figure 3-3 Transfer curves before and after (a) positive bias temperature stress and (b) negative bias stress conditions. A detailed stress condition is shown in the figures.

(a)

Figure 3-4 Transfer curves before and after (a) 30 V and (b) 50 V gate bias stress. A detailed stress condition is shown in the figures.

Figure 3-5 Schematic drawing of trapped electrons at the interface between the gate insulator layer and IGZO layer due to high gate bias induced degradation.

# 3.5 Drain bias induced instability without illumination

#### 3.5.1 Introduction

Amorphous Indium-Gallium-Zinc-Oxide (IGZO) thin-film transistors (TFTs) have gained considerable attention for active matrix displays due to the high field effect mobility and good uniformity [26, 107]. The electrical stability of IGZO TFTs under the bias, temperature, and illumination has been intensively studied [45, 46, 62].

The effects of gate bias stress on IGZO TFTs have been widely researched [31, 41, 43]. However, there are a few reports on the drain bias induced degradation in IGZO TFTs [41, 111]. It is reported that the effect of the drain bias on the stability of IGZO TFTs is not significant compared to the gate bias induced stress [41]. In the previous works, the high gate bias was applied simultaneously with the drain bias stress, which is different from our experimental condition [41, 111]. In our experimental results, however, a-IGZO TFTs with the etch stopper structure was degraded under the high drain bias stress. Our experimental results show that a linear region of an output curve was severely decreased after the high drain bias stress. Furthermore, in the transfer curve, the drain current measured at the low drain bias ( $V_{DS} = 1 V$ ) was significantly decreased after the high drain bias stress. High drain bias to the driving transistor of the OLED TV is enhanced as the size of the panel increases.

The purpose of our work is to investigate the high drain induced degradation in IGZO TFTs with the etch stopper structure. I propose a degradation model for the

high drain bias induced degradation. Computer aided device simulations and capacitance-voltage (C-V) measurements were employed to support my degradation model.

### **3.5.2 Experimental methods**

The IGZO TFTs were fabricated on a glass substrate with the bottom gate structure. The bottom gate structure is widely used for a-IGZO TFTs, to adapt a conventional mass production process and design [23, 61, 113]. Most of the bottom gate structures have employed the etch stopper layer, to improve the reliability of a-IGZO TFTs [23, 61, 113]. The detailed fabrication process is reported elsewhere [114]. The SiO<sub>2</sub> etch stopper layer was employed to reduce the damage of the IGZO layer during the source-drain dry etching process.

#### 3.5.3 Experimental results and discussions

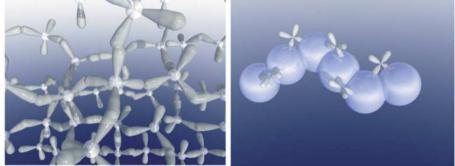

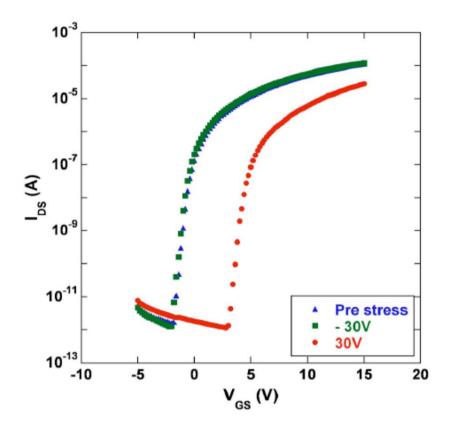

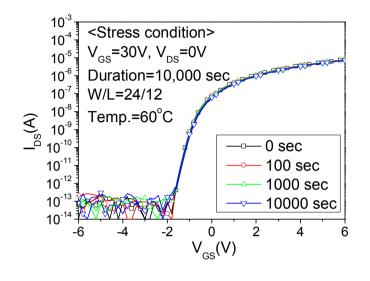

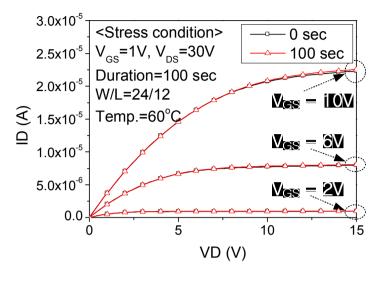

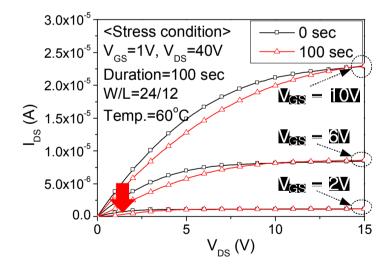

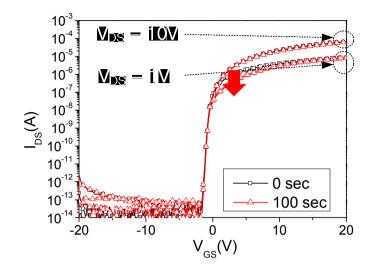

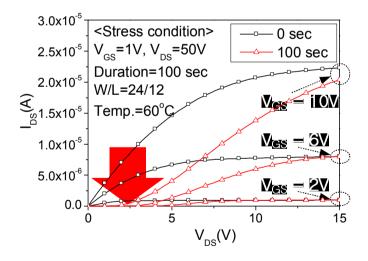

In order to investigate the drain bias induced degradation, we applied the various drain bias (10 V ~ 50 V) to the IGZO TFTs under 30 and 60 °C for 100 seconds. For the purpose of minimizing the effect of gate bias, we fixed the gate bias to 1 V. The degradation was not observed under 30 V drain bias stress as shown in Figure 3-6 (a). Over 40 V drain bias stress, however, the drain current at low drain bias regime was decreased. Figure 3-6 (b) shows the output curve before and after 40 V drain bias stress. The output curve was measured at 2 V, 6 V, and 10 V gate bias. Regardless of the measuring gate bias, the linear region of the output curve was slightly decreased after 40 V drain bias stress. Figure 3-6 (c) shows the transfer curve before and after 40 V drain bias stress. The transfer curve was measured at 1 V and 10 V drain bias. The drain current measured at 1 V drain bias was slightly decreased, while the drain current measured at 10 V drain bias was scarcely decreased. In case of 50 V drain bias stress, the drain current at low drain bias regime was decreased significantly. Figure 3-6 (d) and (e) show the output curve and transfer curve before and after 50 V drain bias stress. Linear region of output curve was severely distorted after 50 V drain bias stress. In terms of the transfer curve, the drain current measured at 1 V drain bias was significantly decreased, while the drain current measured at 10 V drain bias was slightly decreased. The degradation was occurred in a short time compared to the high gate bias induced stress. However, the degradation did not proceed additionally, as the stress time increased.

When high gate bias stress is applied, threshold voltage is shifted according to the polarity of the applied gate bias [31, 41, 43]. On-current level of the output curve could be changed according to the shift of threshold voltage, while linear region of output curve is hardly changed. The high gate bias induced degradation mechanism is the charge trapping at the interface between the gate insulator layer and active layer. Our experimental result is a unique degradation phenomenon compared to the previous reports.

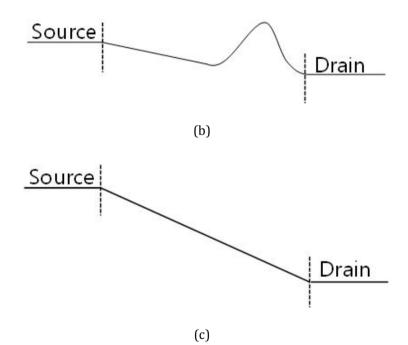

To explain the unique degradation phenomenon, we assumed that the electrons could be trapped at the etch stopper layer due to the high drain bias. In this case, the drain bias has an effect on the electrons vertically, not laterally. In the gate-drain overlapped region, the electrons could have a vertical electric field. Figure 3-7 (a) shows the schematic drawing of trapped electrons at the etch stopper layer due to high drain bias induced degradation. The electrons are trapped at the etch stopper layer near the drain electrode due to high vertical field. Figure 3-7 (b) shows the band diagram of the low drain bias measurement condition ( $V_{DS} = 1 V$ ) after the high drain bias induced degradation. When the electrons are trapped at the etch stopper layer, the energy barrier is formed near the drain electrode due to the trapped electrons. In case of the low drain bias measurement condition ( $V_{DS} = 1 V$ ), the energy barrier blocks the carriers and the drain current could be decreased significantly. In case of the high drain bias measurement condition ( $V_{DS} = 10 V$ ), however, the energy barrier is lowered due to the applied drain bias and the drain current could be decreased slightly.

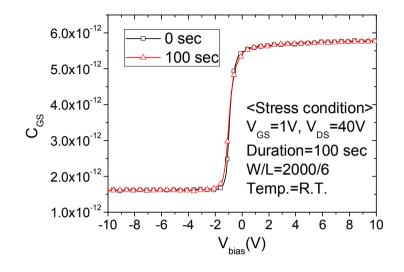

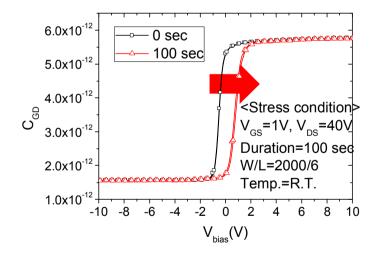

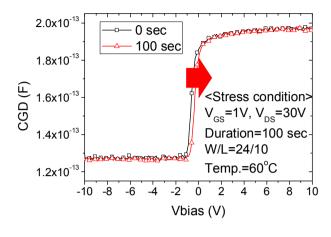

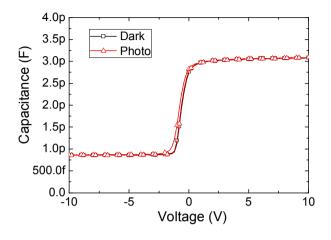

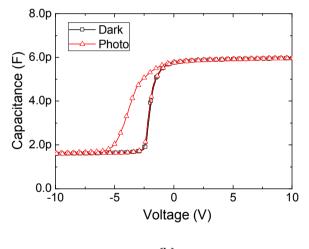

The Capacitance-Voltage (C-V) characteristics were investigated, in order to verify the degradation model. Figure 3-8 (a) and (b) show gate-source capacitance ( $C_{GS}$ ) and gate-drain capacitance ( $C_{GD}$ ) before and after the 40 V drain bias stress. The  $C_{GS}$  was measured with a floating drain, while the  $C_{GD}$  was measured with a floating source. The C-V curve of  $C_{GS}$  was not altered after stress, while the C-V curve  $C_{GD}$  was positively shifted by amount of 1.23 V after 40 V drain bias stress. Figure 3-8 (c) and (d) show the C-V curve of  $C_{GD}$  before and after the 30 V and 50 V drain bias stress. The C-V curve of  $C_{GD}$  was positively shifted by amount of 0.28 V (4.96 V) after 30 V (50 V) drain bias stress. As the

applied drain bias increased, the amount of shift of C-V curve was increased.

When the electrons are trapped at the insulator in MIS structure, C-V curve could be positively shifted. Density of interface trapped electrons ( $\Delta Q_n$ ) could be calculated using the following equation ( $\Delta Q_n = C \cdot \Delta V_{shift}$ ). The calculated  $Q_n$  is about to 2E11 cm<sup>-2</sup> (30 V drain bias stress), 8E11 cm<sup>-2</sup> (40 V drain bias stress), and 3E12 cm<sup>-2</sup> (50 V drain bias stress). The C-V characteristics suggest that the electron is trapped at the etch stopper layer near the drain region and support my degradation model.

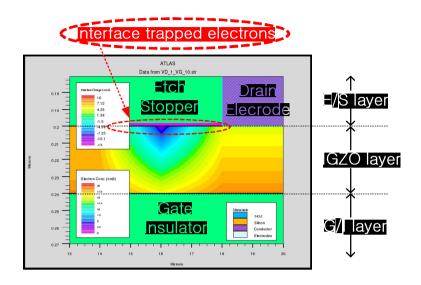

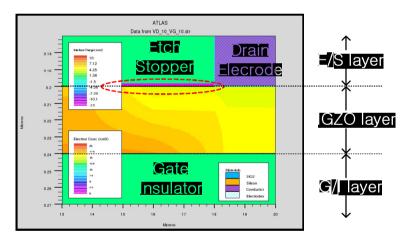

In order to support our degradation model, we employed the computer aided device simulation. We used ATLAS device simulator made by Silvaco. The interface trapped electrons were introduced at the etch stopper layer near the drain electrode in consideration of high drain bias induced degradation. Density of interface trapped electron is applied to the extracted data from our experimental results. Figure 3-9 (a) and (b) show the simulated output curves and transfer curves, and they are well matched to our experimental results. Figure 3-9 (c) and (d) show the free electron concentration in IGZO layer calculated by the computer aided device simulation (assuming  $Q_n = 3E12 \text{ cm}^{-2}$ ). Blue-dashed-squared region in Figure 3-7 (a) represents the simulation region. Figure 3-9 (c) shows the electron concentration in the IGZO layer under 1 V drain bias measurement condition. The free electrons in IGZO layer are depleted under the etch stopper layer due to the electric field induced by the interface trapped electrons at the etch stopper layer. Figure 3-9 (d) shows the electron concentration in IGZO layer under the 10 V drain bias measurement condition. The electrons are not depleted anymore at 10 V drain bias measurement condition because 10 V drain bias lowers the energy barrier made by the interface trapped electrons. The simulation results support my degradation model.

Figure 3-10 shows the comparison of output curves and transfer curves before and after high drain bias stress between (a, c) simulation and (b, d) experimental data. The simulated output curve and transfer curve are well matched that of the experimental results. These curves are support my degradation model.

(a)

(b)

(c)

(d)

(e)

Figure 3-6 (a) Output curve before and after 30 V drain bias stress. (b) Output curve and (c) transfer curve before and after 40 V drain bias stress. (d) Output curve and (e) transfer curve before and after 50 V drain bias stress. Detailed stress condition is shown in figures.

Figure 3-7 (a) Schematic drawing of trapped electrons at the etch stopper layer due to high drain bias induced degradation. (b) Band diagram of low drain bias measurement condition ( $V_{DS} = 1V$ ) and (c) high drain bias measurement condition ( $V_{DS} = 10V$ ) after degradation.

(b)

(c)

(d)

Figure 3-8 (a) Gate-source capacitance ( $C_{GS}$ ) and (b) gate-drain capacitance ( $C_{GD}$ ) versus gate bias curves (C-V curves) before and after 40 V drain bias stress.  $C_{GD}$  versus gate bias curves before and after (c) 30 V drain bias stress and (d) 50 V drain bias stress.

(b)

Figure 3-9 Simulated (a) output curves and (b) transfer curves by assuming the interface trapped electrons ( $Q_n = 0$ , 2E11, 8E11, 3E12 cm<sup>-2</sup>). And electron concentration in IGZO layer calculated by computer aided device simulation (SILVACO) under (c) 1 V drain bias measurement condition and (d) 10 V drain bias measurement condition.

(b)

(d)

Figure 3-10 Comparison of output curves before and after high drain bias stress between (a) simulation and (b) experimental data. Comparison of transfer curves before and after high drain bias stress between (a) simulation and (b) experimental data.

### **3.5.4 Conclusion**

I have investigated the high drain bias induced degradation in IGZO TFTs with the etch stopper structure. The drain current, measured at the low drain bias, was significantly decreased after the high drain bias stress. The electrons were trapped at the etch stopper layer due to the high drain bias. The drain bias has an effect on the electrons vertically, not laterally. The computer aided simulation and C-V measurements support our degradation mechanism. Highly reliable etch-stopper-free-structure should be developed, to solve the high drain bias induced degradation and establish simple fabrication process.

# 3.6 Light-Induced Hysteresis of IGZO TFTs with Various Wavelengths

### 3.6.1 Introduction

Indium-Gallium-Zinc Oxide thin-film transistors (IGZO TFTs) are promising candidate for next generation display backplane, due to its large mobility and good uniformity. Threshold voltage ( $V_{TH}$ ) of IGZO TFTs was not shifted under positive gate bias stress (PBS) or negative gate bias stress (NBS) without illumination. However,  $V_{TH}$  of IGZO TFT was negatively shifted significantly under NBS with light illumination. In order to investigate this unique degradation phenomenon, stability of IGZO TFT under negative bias illumination stress (NBIS) has been intensively studied [57, 59, 68].

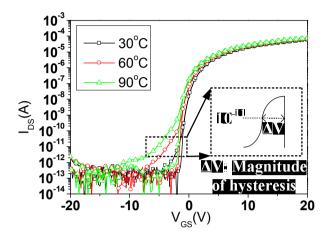

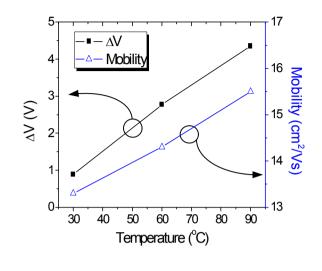

However, light-induced changes in device characteristics, such as hysteresis, are scarcely reported. Recently, I reported light-induced hysteresis and its mechanism of IGZO TFTs under various temperatures [114]. My experimental results showed that sub-threshold slope (S.S.) under 450-nm illumination increased compared to dark state during the forward sweep. However, S.S. under 450-nm illumination did not change compared to dark state during the reverse sweep. This phenomenon could be called light-induced hysteresis.

In this paper, I report the effects of wavelength and negative bias on lightinduced hysteresis of IGZO TFTs. Hysteresis was increased, as wavelength decreased. And hysteresis was increased, as applied negative bias increased.

## 3.6.2 Experimental methods

The IGZO TFTs were fabricated on a glass substrate with an inverted staggered structure. First, Mo/AlNd were deposited and patterned as the gate electrode. SiO<sub>2</sub> of 2000 Å thickness was then deposited by plasma enhanced chemical vapor deposition (PECVD) and served as the gate dielectric layer. The IGZO (In:Ga:Zn = 1:1:1) layer with a thickness of 500 Å was deposited by sputtering. The SiO<sub>2</sub> etch stop layer was deposited by PECVD. The source and drain were formed by depositing a layer of Mo and patterned by dry etching. The SiO<sub>2</sub> layer was used as a passivation layer. Annealing of the device was performed as the final process at 300°C in an ambient air. For the light illumination test, the device was irradiated by a Xenon lamp with narrow band pass filters.

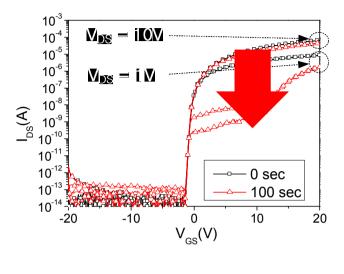

### 3.6.3 Experimental results and discussions

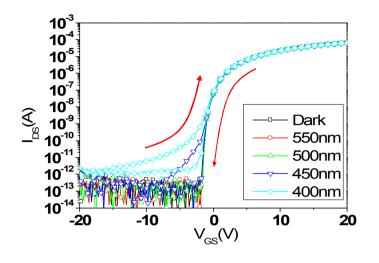

Figure 3-11 (a) shows the transfer curves under dark and illumination conditions at 60°C. The center wavelengths of band pass filters were 550nm, 500nm, 450nm, and 400nm and light intensity was adjusted to 1 mW/cm<sup>2</sup>. The transfer curves were measured by the double sweep method from –20V to 20V and the drain bias was fixed to 10 V. The transfer curves measured under dark condition and illumination conditions of 550 nm and 500 nm did not show any hysteresis. On the other hand, the transfer curves measured under 450 nm and 400 nm illumination conditions showed hysteresis. The magnitude of hysteresis increased as the wavelength decreased. Figure 3-11 (b) shows the magnitude of hysteresis ( $\Delta V$ ) and mobility extracted from Figure 3-11 (a). Mobility was not altered regardless of wavelength. Moreover, mobility was not changed under dark condition.

The mobility of the IGZO TFT strongly depends on carrier concentration [22]. Electron concentration could be increased by light and thermal energy. To increase the mobility of IGZO TFTs under the illumination conditions, the light-induced free carrier concentration ( $\Delta n_L$ ) should be increased as much as the intrinsic carrier concentration. The intrinsic carrier concentration of IGZO is known to be  $10^{16-20}$  cm<sup>-3</sup> [22, 115]. According to Lambert-Beer's law, the approximated quantum efficiency ( $\eta$ ) could be estimated using the following equation ( $\eta = 1 - \exp[-\alpha_{sub} \cdot d]$ , where  $\alpha_{sub}$  is the sub-band gap absorption coefficient and d is the thickness of the IGZO film) [116]. When  $\alpha_{sub}$  is assumed to be  $10^4$  cm<sup>-1</sup> [110],  $\eta$  is calculated to be 4.9%. If light of a 400-nm wavelength and 1 mW/cm<sup>2</sup> intensity is illuminated to IGZO TFTs,  $\Delta n_L$  could be estimated using following equation ( $\Delta n_L = \tau \cdot \eta \cdot I \cdot \lambda / [Ih \cdot c \cdot d]$ ).  $\tau$  is the electron life-time (assumed to  $10^{-6}$  sec), I and  $\lambda$  are the intensity and wavelength of the illuminated light, h is

Planck's constant, and c is the speed of light.  $\Delta n_L$  is calculated to be approximately  $10^{13}$  cm<sup>-3</sup>, which is far less than the intrinsic carrier concentration. Under the illumination condition of wavelength longer than 400nm,  $\Delta n_L$  should be decreased, due to the decrease of  $\alpha_{sub}$ . It is suggested that light induced channel defect concentration is not large enough to change the mobility of IGZO TFTs.

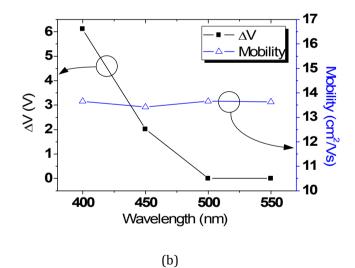

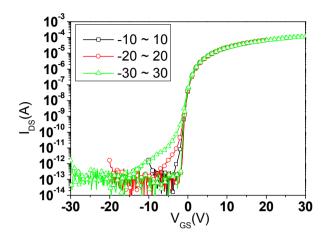

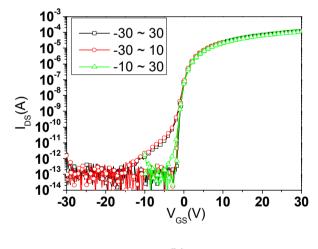

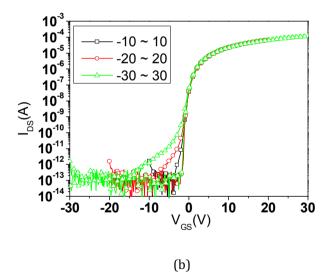

Figure 3-12 (a) shows the transfer characteristics of IGZO TFTs under various sweep ranges (V<sub>GS</sub> = -10 ~ 10V, -20 ~ 20V, -30 ~ 30V) with 450 nm illumination at 60 °C. The magnitude of hysteresis increased as sweep range increased. In order to investigate hysteresis mechanism in detail, we measured IGZO TFTs asymmetrically. Figure 3-12 (b) shows the transfer characteristics of IGZO TFTs under various sweep ranges (V<sub>GS</sub> = -30 ~ 30V, -30 ~ 10V, -10 ~ 30V) with 450 nm illumination at 60 °C. The magnitude of hysteresis was similar between (V<sub>GS</sub> = -30 ~ 30V) and (V<sub>GS</sub> = -30 ~ 10V). The magnitude of hysteresis was decreased when sweep range is (V<sub>GS</sub> = -10 ~ 30V). We have found that the magnitude of hysteresis was independent on the magnitude of applied negative gate bias. And we have found that the magnitude of hysteresis was independent on the magnitude of applied positive gate bias.

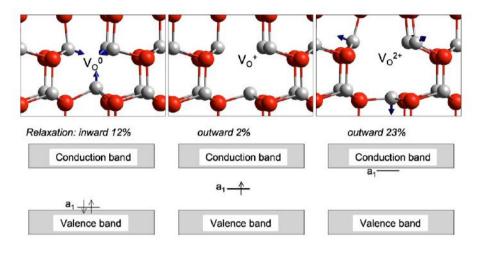

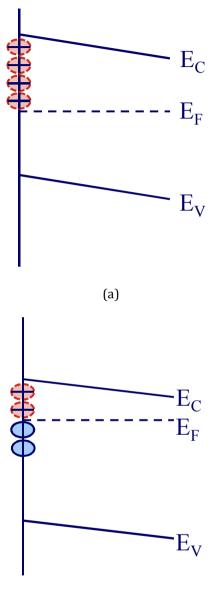

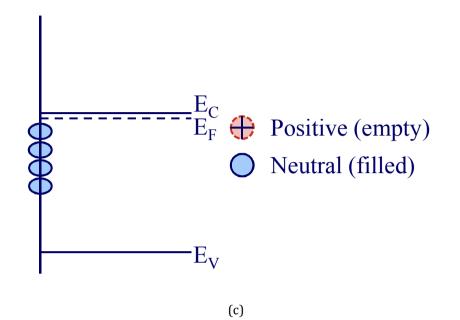

When a ZnO based semiconductor is deposited, the deposited film has the native point defect, such as the oxygen vacancy. The oxygen vacancy has 3 possible charge states ( $V_0$ ,  $V_0^+$ , and  $V_0^{2+}$ ). Neutral oxygen vacancy ( $V_0$ ) is located near valence band maximum (VBM), and doubly ionized oxygen vacancy ( $V_0^{2+}$ ) is located near conduction band minimum (CBM). Figure 3-13 (a) shows the energy level of sub-band states of neutral oxygen vacancy ( $V_0^{2+}$ ). The energy level of sub-band states of neutral oxygen vacancy ( $V_0^{2+}$ ). The energy level of sub-band states could be calculated using the first-principle calculations. Figure 3-13 (b) shows the formation energies vs Fermi level for oxygen vacancies in ZnO in

the 0, 1+, and 2+charge states, under Zn-rich conditions. [117]

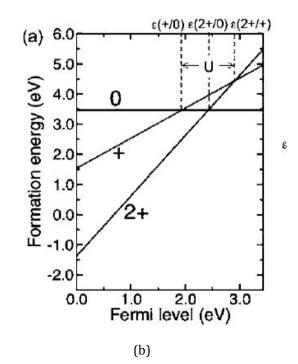

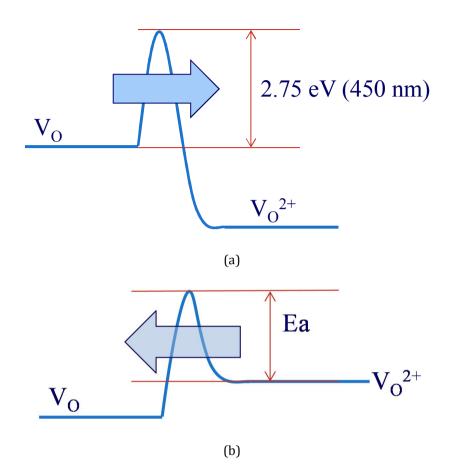

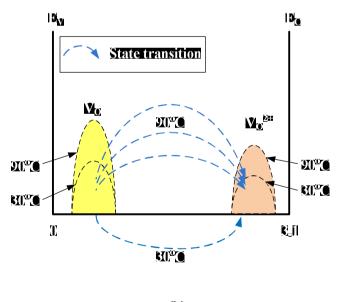

Figure 3-14 shows the schematic configuration coordinate diagrams for (a) negative gate bias and (b) positive gate bias. When the negative V<sub>GS</sub> is applied, the Fermi level moves toward the valence band. The formation energy of  $V_0^{2+}$  states could be smaller than that of V<sub>0</sub> states. It is suggested that  $V_0^{2+}$  states are more stable than V<sub>0</sub> states under negative gate bias. The formation energy of  $V_0^{2+}$  states is reduced further, as the Fermi level decreases. When the energy over the energy barrier is applied, V<sub>0</sub> states could be turned to V<sub>0</sub><sup>2+</sup> states. The energy barrier from V<sub>0</sub> states to V<sub>0</sub><sup>2+</sup> states is considered to about 2.75 eV, because light-induced hysteresis could not be observed under the illumination of longer than 450 nm. Therefore, V<sub>0</sub><sup>2+</sup> states could be observed during the forward sweep.

When the positive  $V_{GS}$  is applied, the Fermi level moves toward the conduction band. The formation energy of  $V_0^{2+}$  states is increased, and the formation energy of  $V_0$  states could be smaller than that of  $V_0^{2+}$  states. It is suggested that  $V_0$  states are more stable than  $V_0^{2+}$  states under positive gate bias. The energy barrier from  $V_0^{2+}$  states to  $V_0$  states could be smaller than 2.75 eV. Therefore,  $V_0^{2+}$  states could not be observed during the reverse sweep.

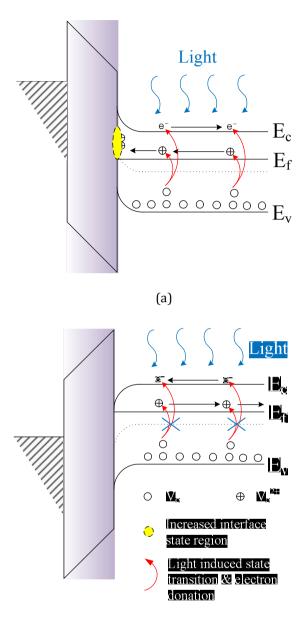

Figure 3-15 shows band diagram of IGZO TFTs with light illumination under negative gate bias (a) and positive gate bias (b). Photon irradiation and negative gate bias causes the transition of neutral oxygen vacancy (V<sub>0</sub>) to the doubly ionized oxygen vacancy (V<sub>0</sub><sup>2+</sup>) and the donation of two electrons to the conduction band. The V<sub>0</sub><sup>2+</sup> states are created at the interface, and the generated V<sub>0</sub><sup>2+</sup> states from the bulk could be migrated to the interface due to the applied negative gate bias. Interface states could be increased during this time, resulting in increase of sub-threshold slope. When the gate bias is changed from negative bias to positive bias, V<sub>0</sub><sup>2+</sup> states at the interface are neutralized to V<sub>0</sub> states by capturing two electrons. Therefore, transfer curves under dark and illumination are almost identical at the positive gate bias regime.

In contrast to forward sweep, transfer curves under dark and illumination are almost identical during a whole reverse sweep. At the beginning of the reverse sweep, positive gate bias is applied so that  $V_0^{2+}$  states could not be generated at the interface. When the gate bias is changed from positive bias to negative bias during reverse sweep, transfer curves turn to off state. Therefore, transfer curves under dark and illumination could be identical during the whole reverse sweep.

As wavelength decreased, absorption coefficient of IGZO film increased. It is obvious that more V<sub>0</sub> states could be excited to the V<sub>0</sub><sup>2+</sup> states, as the wavelength decreased. Therefore, the magnitude of hysteresis is enhanced, as the wavelength is shifted to deep blue. Our experimental results suggested that V<sub>0</sub> states ranged from 2.75 eV (wavelength ~ 450nm) below the conduction band minimum.

When sweep range is changed from (-10V  $\sim$  10V) to (-30V  $\sim$  30V), the magnitude of initial negative bias and time to be applied negative bias are increased, resulting in increase of interface state and sub-threshold slope. Therefore, hysteresis could be increased with the magnitude of applied initial negative gate bias.

Figure 3-11 (a) Transfer characteristics of IGZO TFTs under dark and various wavelengths at 60 °C (Wavelength = 550 nm, 500 nm, 450 nm, and 400 nm, Intensity =  $1 \text{ mW/cm}^2$ ) (b) Magnitude of hysteresis and mobility as a function of wavelength.

(b)

Figure 3-12 Transfer characteristics of IGZO TFTs under various sweep ranges with 450 nm illumination (a)  $[V_{GS} = -10 \sim 10V, -20 \sim 20V, -30 \sim 30V]$ , (b)  $[V_{GS} = -30 \sim 30V, -30 \sim 10V, -10 \sim 30V]$

Figure 3-13 (a) The energy level of sub-band states of neutral oxygen vacancy  $(V_0)$ , singly ionized oxygen vacancy  $(V_0^+)$  and doubly ionized oxygen vacancy  $(V_0^{2+})$ . (b) Formation energies vs Fermi level for oxygen vacancies in ZnO in the 0, 1+, and 2+charge states, under Zn-rich conditions. [117]

Figure 3-14 Schematic configuration coordinate diagrams for (a) negative gate bias and (b) positive gate bias.

(b)

Figure 3-15 Band diagram of IGZO TFTs with light illumination under (a) negative gate bias and (b) positive gate bias.

## **3.6.4 Conclusion**

I have observed light-induced hysteresis under various wavelengths and sweep ranges, and have investigated its mechanism. Light-induced hysteresis is caused by the increase of  $V_0^{2+}$  states at the interface due to initial negative gate bias and light. Increased sub band gap states at the interface cause increase of sub-threshold slope during forward sweep. The magnitude of light-induced hysteresis increased, as the wavelength decreased. And the magnitude of light-induced bias increased.

# 3.7 Light-Induced Hysteresis of IGZO TFTs with Various Temperatures

### **3.7.1 Introduction**

Recently, amorphous Indium-Gallium-Zinc Oxide thin-film transistors (a-IGZO TFTs) have attracted considerable attention due to their high mobility and good uniformity [22, 27]. Device characteristics under light illumination and various temperatures are critical issues because display backplanes suffer from light illumination and thermal energy simultaneously.

The reliability of a-IGZO TFTs under bias, temperature, environment, and illumination has been intensively studied [57, 59, 65, 68, 118]. However, light-induced changes in device characteristics, such as hysteresis, are scarcely reported. It has been reported that the sub-threshold slope (S.S.) and off current increases as wavelength decreases from 700 nm to 450 nm [119]. Our experimental results show that S.S. increased compared to dark state during the forward sweep under 450-nm illumination condition. However, S.S. did not change compared to dark state during the reverse sweep. This could be called light-induced hysteresis. Our experimental results show that this light-induced hysteresis increases as temperature increases. The mobility of IGZO TFTs also increased, as temperature increased.