#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

#### Ph.D. Dissertation

# A Design of Calibration-Free Phase-Locked Loops (PLLs)

캘리브레이션이 필요 없는 위상고정루프의 설계

by

Hwanseok Yeo

February, 2017

School of Electrical Engineering and Computer Science

College of Engineering

Seoul National University

# A Design of Calibration-Free Phase-Locked Loops (PLLs)

지도 교수 김 재 하

이 논문을 공학박사 학위논문으로 제출함 2017 년 2 월

> 서울대학교 대학원 전기·컴퓨터공학부 여 환 석

여환석의 박사 학위논문을 인준함 2017 년 2 월

| 위원     | 원 장 | 정 덕 균 | (인) |

|--------|-----|-------|-----|

| 부위     | 원장  | 김 재 하 | (인) |

| 위      | 원   | 남 상 욱 | (인) |

| 위<br>위 | 원   | 박 병 하 | (인) |

| 위      | 원   | 김 태 익 | (인) |

ABSTRACT

# **Abstract**

A PVT-insensitive-bandwidth PLL and a chirp frequency synthesizer PLL are proposed using a constant-relative-gain digitally-controlled oscillator (DCO), a constant-gain time-to-digital converter (TDC), and a simple digital loop filter (DLF) without an explicit calibration or additional circuit components.

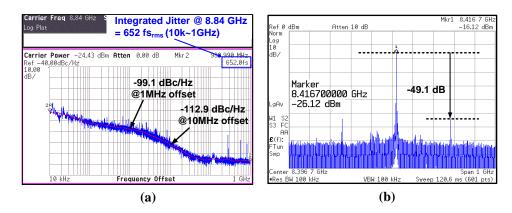

A digital LC-PLL that realizes a PVT-insensitive loop bandwidth (BW) by using the constant-relative-gain LC-DCO and constant-gain TDC is proposed. In other words, based on ratiometric circuit designs, the LC-DCO can make a fixed percent change to its frequency for a unit change in its digital input and the TDC can maintain a fixed range and resolution measured in reference unit intervals (UIs) across PVT variations. With such LC-DCO and TDC, the proposed PLL can realize a bandwidth which is a constant fraction of the reference frequency even with a simple proportional-integral digital loop filter without any explicit calibration loops. The prototype digital LC-PLL fabricated in a 28-nm CMOS demonstrates a frequency range of 8.38~9.34 GHz and 652-fs<sub>rms</sub> integrated jitter from 10-kHz to 1-GHz at 8.84-GHz while dissipating 15.2-mW and occupying 0.24-mm². Also, the PLL across three different die samples and supply voltage ranging from 1.0 to 1.2V demonstrates a nearly constant BW at 822-kHz with the variation of ±4.25-% only.

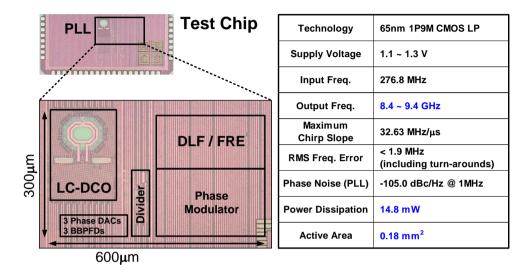

A chirp frequency synthesizer PLL (FS-PLL) that is capable of precise triangular frequency modulation using type-III digital LC-PLL architecture for X-band FMCW imaging radar is proposed. By employing a phase-modulating two-point modulation (TPM), constant-gain TDC, and a simple second-order DLF with polarity-

**ABSTRACT** II

alternating frequency ramp estimator, the PLL achieves a gain self-tracking TPM

realizing a frequency chirp with fast chirp slope (=chirp BW/chirp period) without

increasing frequency errors around the turn-around points, degrading the effective

resolution achievable. A prototype chirp FS-PLL fabricated in a 65nm CMOS

demonstrates that the PLL can generate a precise triangular chirp profile centered at

8.9-GHz with 940-MHz bandwidth and 28.8-us period with only 1.9-MHz<sub>rms</sub> fre-

quency error including the turn-around points and 14.8-mW power dissipation. The

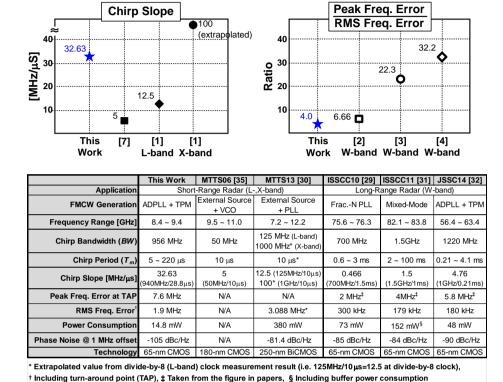

achieved 32.63-MHz/µs chirp slope is higher than that of FMCW FS-PLLs previ-

ously reported by  $2.6\times$ .

**Keywords**: digital phase-locked loop (DPLL), digitally-controlled oscillator (DCO),

time-to-digital converter (TDC), bang-bang phase-frequency detector (BB-PFD),

frequency synthesizer phase-locked loop (FS-PLL), calibration, adaptive-bandwidth,

bandwidth tracking, frequency modulated continuous wave (FMCW), Radar, fre-

quency chirp.

**Student Number : 2012-30217**

CONTENTS

# **Contents**

| ABSTRACT                                  | Ι   |

|-------------------------------------------|-----|

| CONTENTS                                  | III |

| LIST OF FIGURES                           | VI  |

| LIST OF TABLES                            | XI  |

| CHAPTER 1 INTRODUCTION                    | 1   |

| 1.1 MOTIVATION                            | 1   |

| 1.2 Thesis Organization                   | 5   |

| CHAPTER 2 CONVENTIONAL PHASE-LOCKED LOOP  | 7   |

| 2.1 CHARGE-PUMP PLL.                      | 7   |

| 2.1.1 OPERATING PRINCIPLE                 | 7   |

| 2.1.2 LOOP DYNAMICS                       | 9   |

| 2.2 DIGITAL PLL                           | 10  |

| 2.2.1 OPERATING PRINCIPLE                 | 11  |

| 2.2.2 LOOP DYNAMICS                       | 12  |

| CHAPTER 3 VARIATIONS ON PHASE-LOCKED LOOP | 14  |

| 3.1 OSCILLATOR GAIN VARIATION             | 14  |

| 3.1.1 RING VOLTAGE-CONTROLLED OSCILLATOR  | 15  |

| 3.1.2 LC VOLTAGE-CONTROLLED OSCILLATOR    | 17  |

| 3.1.3 LC DIGITALLY-CONTROLLED OSCILLATOR       | 19         |

|------------------------------------------------|------------|

| 3.2 Phase Detector Gain Variation              | 20         |

| 3.2.1 LINEAR PHASE DETECTOR                    | 20         |

| 3.2.2 LINEAR TIME-TO-DIGITAL CONVERTER         | 21         |

| CHAPTER 4 PROPOSED DCO AND TDC FOR CALIBRATION | N-FREE PLL |

|                                                | 23         |

| 4.1 DIGTALLY-CONTROLLED OSCILLATOR (DCO)       | 25         |

| 4.1.1 Overview                                 | 24         |

| 4.1.2 CONSTANT-RELATIVE-GAIN DCO               | 26         |

| 4.2 TIME-TO-DIGITAL CONVERTER (TDC)            | 28         |

| 4.2.1 OVERVIEW                                 | 28         |

| 4.2.2 CONSTANT-GAIN TDC                        | 30         |

| CHAPTER 5 PVT-INSENSITIVE-BANDWIDTH PLL        | 35         |

| 5.1 Overview                                   | 36         |

| 5.2 Prior Works                                | 37         |

| 5.3 Proposed PVT-Insensitive-Bandwidth PLL     | 39         |

| 5.4 CIRCUIT IMPLEMENTATION                     | 41         |

| 5.4.1 CAPACITOR-TUNED LC-DCO                   | 41         |

| 5.4.2 Transformer-Tuned LC-DCO                 | 45         |

| 5.4.3 OVERSAMPLING-BASED CONSTANT-GAIN TDC     | 49         |

| 5.4.4 Phase Digital-to-Analog Converter        | 52         |

| 5.4.5 DIGITAL LOOP FILTER                      | 54         |

| 5.4.6 Frequency Divider                        | 55         |

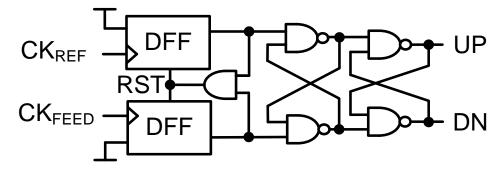

| 5.4.7 Bang-Bang Phase-Frequency Detector     | 56  |

|----------------------------------------------|-----|

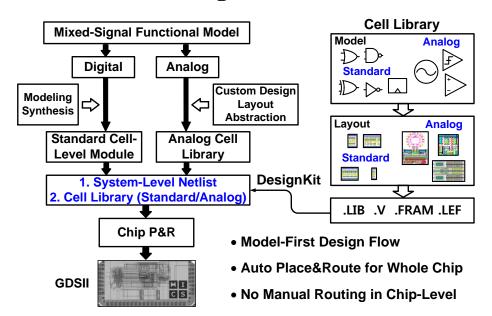

| 5.5 CELL-BASED DESIGN FLOW                   | 57  |

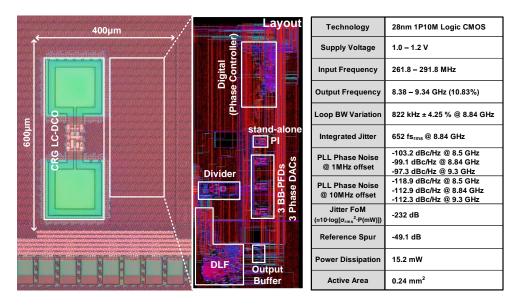

| 5.6 MEASUREMENT RESULTS                      | 58  |

| CHAPTER 6 CHIRP FREQUENCY SYNTHESIZER PLL    | 66  |

| 6.1 Overview                                 | 67  |

| 6.2 Prior Works                              | 71  |

| 6.3 PROPOSED CHIRP FREQUENCY SYNTHESIZER PLL | 75  |

| 6.4 CIRCUIT IMPLEMENTATION                   | 83  |

| 6.4.1 SECOND-ORDER DIGITAL LOOP FILTER       | 83  |

| 6.4.2 Phase Modulator                        | 84  |

| 6.4.3 CONSTANT-GAIN TDC                      | 85  |

| 6.4.4 VRACTOR-BASED LC-DCO                   | 87  |

| 6.4.5 OVERALL CLOCK CHAIN                    | 90  |

| 6.5 MEASUREMENT RESULTS                      | 91  |

| 6.6 SIGNAL-TO-NOISE RATIO OF RADAR           | 98  |

| CHAPTER 7 CONCLUSION                         | 100 |

| BIBLIOGRAPHY                                 | 102 |

| 초 록                                          | 109 |

| 감사의 글                                        | 110 |

LIST OF FIGURES VI

# **List of Figures**

| FIG. 1.1 DETECTION AND ADJUSTMENT OF LOOP PARAMETERS BY PVT CALIBRATOR AGAINST                  |

|-------------------------------------------------------------------------------------------------|

| PVT VARIATIONS IN PREVIOUSLY-REPORTED PLLS                                                      |

| FIG. 2.1 CONVENTIONAL CHARGE-PUMP PLL.                                                          |

| Fig. 2.2 The s-domain model of a second-order charge-pump PLL9                                  |

| FIG. 2.3 A DIGITAL PLL EQUIVALENT TO THE CONVENTIONAL CHARGE-PUMP PLL11                         |

| Fig. 2.4 The z-domain model of a second-order digital PLL                                       |

| Fig. 3.1 A ring oscillator composed of M stage inverters                                        |

| Fig. 3.2 Simulated delay variation of the inverter versus fan-out                               |

| FIG. 3.3 (A) CONVENTIONAL LC-VCO WITH VARACTOR TUNING. (B) VARACTOR TUNING                      |

| CURVE                                                                                           |

| FIG. 3.4 (A) LC-DCO WITH SWITCHED-CAPACITOR (SC) ARRAY. (B) SWITCHED-CAPACITOR                  |

| TUNING CURVE                                                                                    |

| FIG. 3.5 LINEAR PD AND CP CONVERT PHASE ERROR TO CURRENT PULSE                                  |

| FIG. 3.6 (A) VERNIER TDC. (B) BBPD AND ITS TRANSFER CURVE                                       |

| FIG. 4.1 TRANSFER CHARACTERISTICS OF (A) VCO AND (B) DCO                                        |

| FIG. 4.2 OSCILLATOR GAIN VARIATION OF (A) VCO AND (B) DCO                                       |

| Fig. 4.3 Constant relative-gain characteristics                                                 |

| Fig. 4.4 Comparison of $K_{DCO}$ according to $\Omega_{OUT}$ between the linear capacitor-tuned |

| LC-DCO AND CONSTANT RELATIVE-GAIN LC-DCO                                                        |

| FIG. 4.5 TRANSFER CHARACTERISTIC OF (A) LINEAR PD AND (B) TDC                                   |

| Fig. 4.6 (a) Linearization of the TDC characteristics with added random dither. (e              |

| IMPLEMENTATION OF CONSTANT-GAIN TDC.                                                | 30   |

|-------------------------------------------------------------------------------------|------|

| Fig. 4.7 (A) A PLL model for analyzing the noise contribution of the TI             | DC   |

| QUANTIZATION NOISE AND DITHER JITTER. (B) THE NORMALIZED TOTAL I                    | N-   |

| TEGRATED JITTER.                                                                    | 33   |

| FIG. 5.1 THE PLL LOOP BANDWIDTH VARIATION ACCORDING TO PVT CONDITIONS               | 36   |

| FIG. 5.2 THE PREVIOUSLY-REPORTED PVT-INSENSITIVE LOOP BW PLLS                       | 37   |

| FIG. 5.3 THE PROPOSED DIGITAL PLL WITH PVT-INSENSITIVE LOOP BANDWIDTH               | 39   |

| FIG. 5.4 THE PROPOSED CONSTANT RELATIVE-GAIN QUADRATURE LC-DCO IMPLEMENTE           | ED   |

| WITH THE CAPACITOR-COUPLED TWO IDENTICAL ESCBS.                                     | 41   |

| Fig. 5.5 Detailed schematic of the coarse and fine ESCBs.                           | 42   |

| FIG. 5.6 INDUCTANCE AND QUALITY FACTOR OF THE DESIGNED INDUCTOR                     | 44   |

| Fig. 5.7 Simulation results: (a) frequency tuning range and (b) relative gain A     | ΑT   |

| HAND-OVER BETWEEN THE COARSE AND FINE ESCB RANGES                                   | 44   |

| FIG. 5.8 SIMULATED PHASE NOISE                                                      | 45   |

| Fig. 5.9 Transformer-tuned (magnetically-tuned) LC-DCO.                             | 46   |

| FIG. 5.10 THE BLOCK DIAGRAM OF THE CONSTANT-GAIN TDC.                               | 49   |

| Fig. 5.11 Linearization of the TDC with the addition of random dither               | 50   |

| Fig. 5.12 Simulated effective TDC gain: (a) when $\Delta \phi$ =0.037 UI and (b) we | IEN  |

| ΔΦ=0.083 UI                                                                         | 51   |

| Fig. 5.13 (a) Circuit implementation of Phase-Domain DAC. (b) Operating waves       | FORM |

| OF PHASE INTERPOLATOR (PI)                                                          | 52   |

| Fig. 5.14 Simulated results: (a) transfer characteristic of the phase DAC and       | (B)  |

| DIFFERENTIAL NONLINEARITY (DNL)                                                     | 53   |

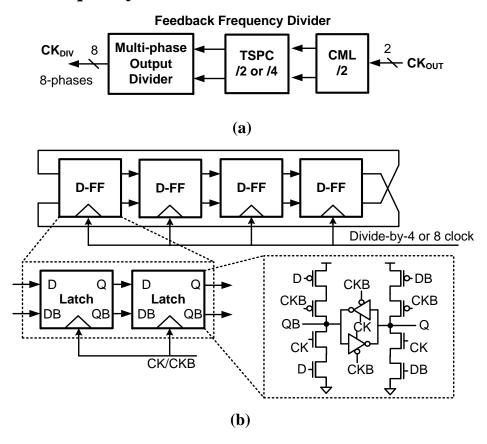

| FIG. 5.15 (A) FEEDBACK FREQUENCY DIVIDER WITH DIVISION RATIO OF 4 OR 8. (B) 8-PHAS  |      |

| OUTPUT DIVIDER55                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIG. 5.16 SCHEMATIC OF BB-PFD.                                                                                                                                                                                   |

| Fig. 5.17 Cell-based design flow.                                                                                                                                                                                |

| FIG. 5.18 CHIP MICROGRAPH AND PERFORMANCE SUMMARY                                                                                                                                                                |

| Fig. 5.19 Measured results of the PLL: (a) PLL phase noise and RMS integrated                                                                                                                                    |

| JITTER AND (B) POWER SPECTRUM59                                                                                                                                                                                  |

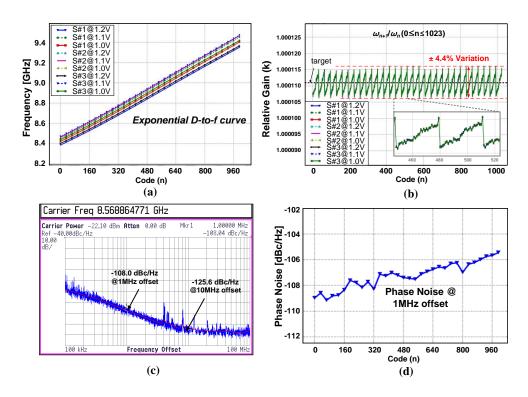

| Fig. 5.20 Measured results of the LC-DCO: (a) exponential digital-to-frequency                                                                                                                                   |

| (D-TO-F) CURVE, (B) RELATIVE GAIN VERSUS INPUT DIGITAL CODE WITH TARGET VAL-                                                                                                                                     |

| UE, (C) LC-DCO PHASE NOISE, AND (D) PHASE NOISE ACCORDING TO FREQUENCY60                                                                                                                                         |

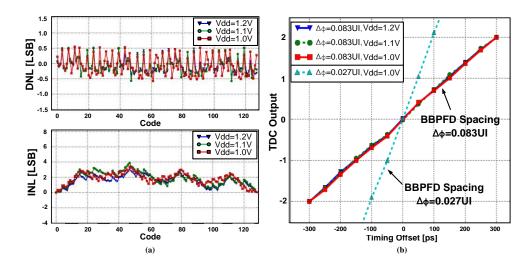

| Fig. 5.21 Measured results of the TDC: (a) DNL and INL of the phase interpolator                                                                                                                                 |

| (PI), (B) TDC TRANSFER ACROSS SUPPLY VOLTAGE AND PHASE SPACING6                                                                                                                                                  |

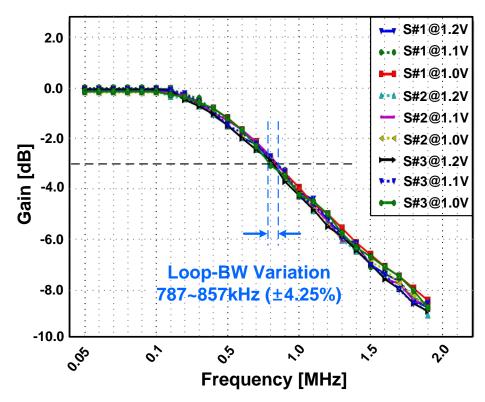

| Fig. 5.22 Measured loop transfer function on three samples and three different                                                                                                                                   |

| SUPPLY VOLTAGES                                                                                                                                                                                                  |

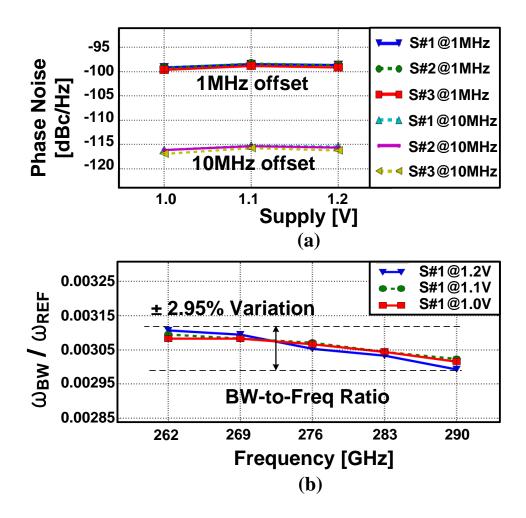

| Fig. 5.23 (a) Measured phase noise variations. (b) loop BW to reference frequency                                                                                                                                |

| RATIO                                                                                                                                                                                                            |

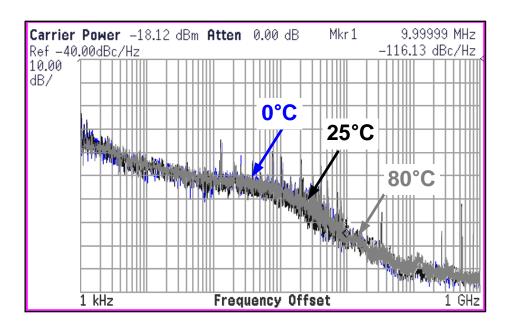

| Fig. 5.24 Measured phase noise for three different temperatures                                                                                                                                                  |

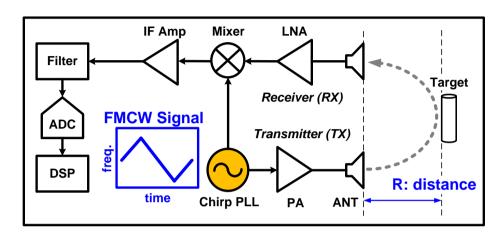

| Fig. 6.1 FMCW RADAR TRANSCEIVER67                                                                                                                                                                                |

|                                                                                                                                                                                                                  |

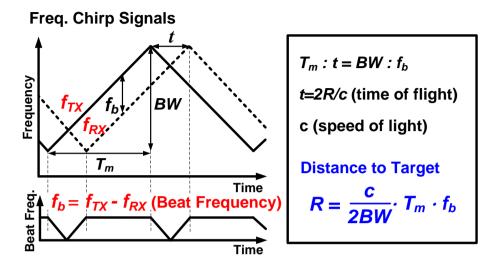

| Fig. 6.2 FMCW RADAR OPERATING PRINCIPLE. 68                                                                                                                                                                      |

|                                                                                                                                                                                                                  |

| Fig. 6.2 FMCW RADAR OPERATING PRINCIPLE. 68                                                                                                                                                                      |

| FIG. 6.2 FMCW RADAR OPERATING PRINCIPLE                                                                                                                                                                          |

| FIG. 6.2 FMCW RADAR OPERATING PRINCIPLE                                                                                                                                                                          |

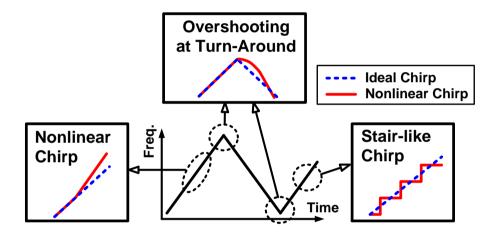

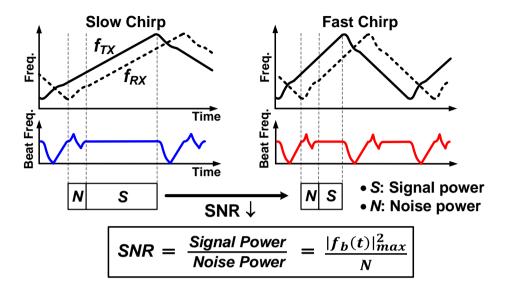

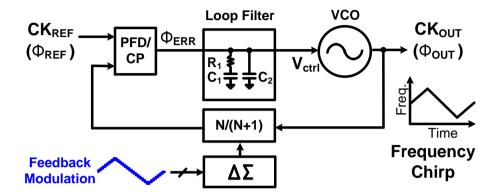

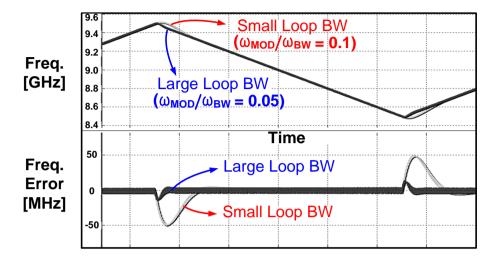

| FIG. 6.2 FMCW RADAR OPERATING PRINCIPLE. 68 FIG. 6.3 NONLINEARITY ON THE FREQUENCY CHIRP PROFILE. 69 FIG. 6.4 SNR DEGRADATION BY FREQUENCY OVERSHOOTING AT TURN-AROUND. 70 FIG. 6.5 ONE-POINT MODULATION PLL. 72 |

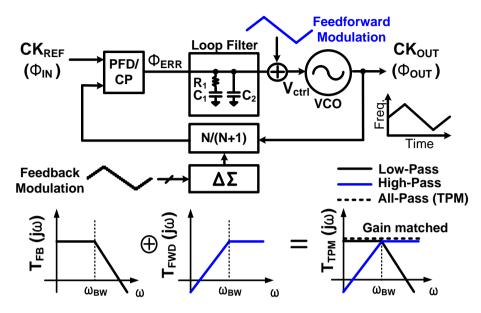

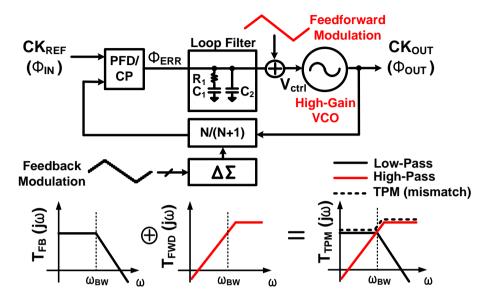

| FIG. 6.8 Two-point modulation PLL With high gain VCO.                             | 14 |

|-----------------------------------------------------------------------------------|----|

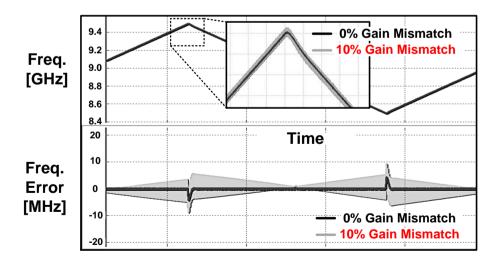

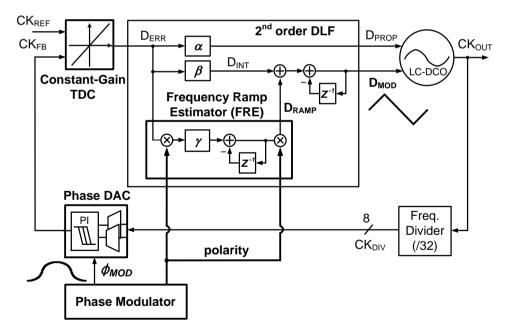

| Fig. 6.9 Simulated frequency chirp profiles and frequency errors in the           |    |

| TPM PLL ACCORDING TO GAIN MISMATCH7                                               | 74 |

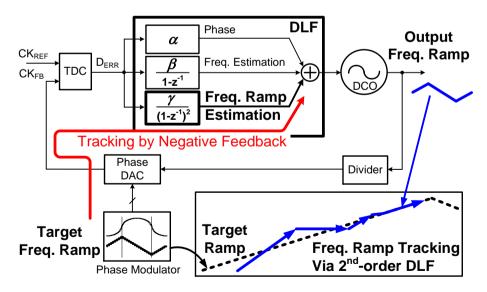

| Fig. 6.10 Proposed type-III third-order chirp frequency synthesizer PLL architec- | -  |

| TURE                                                                              | 15 |

| FIG. 6.11 COMPARISON OF THE TYPE-II AND TYPE-III PLLS                             | 17 |

| FIG. 6.12 STEADY STATE PHASE ERROR OF THE TYPE-II AND TYPE-III PLLS               | 17 |

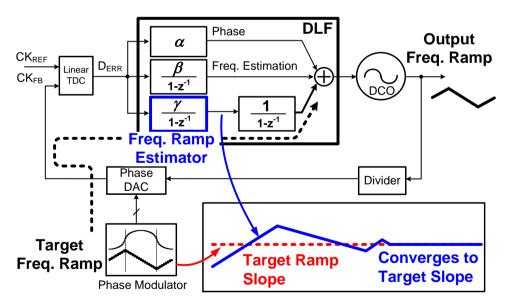

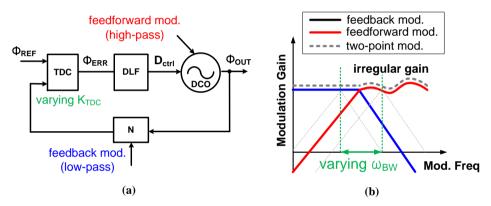

| Fig. 6.13 Gain self-tracking for feedforward modulation signal                    | 78 |

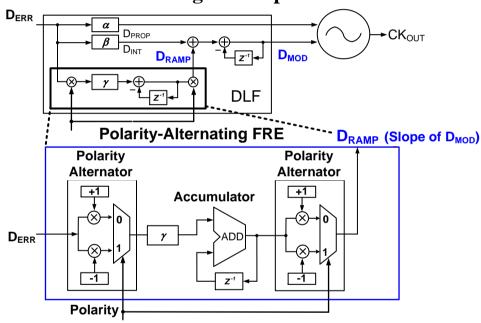

| FIG. 6.14 FRE OPERATION WHICH TRACKS TARGET RAMP SLOPE                            | 79 |

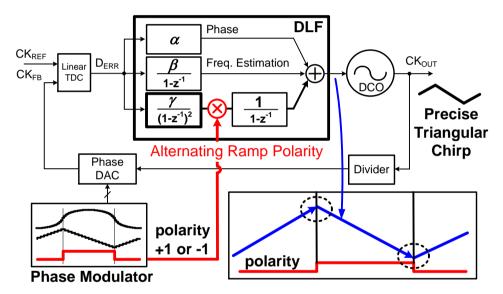

| Fig. 6.15 Polarity alternation of integration according to the sign of ramp slope | Ξ. |

| 8                                                                                 | 30 |

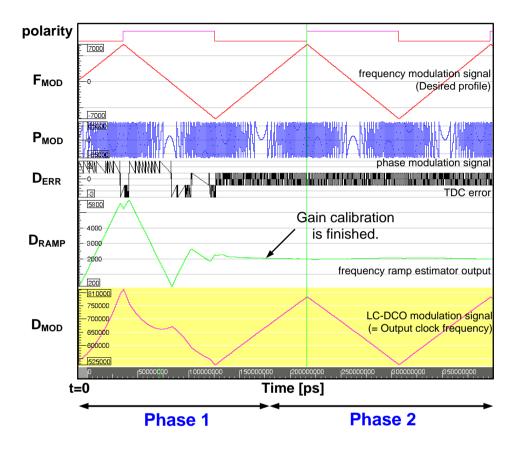

| Fig. 6.16 Behavioral simulation results for gain self-tracking.                   | 32 |

| FIG. 6.17 IMPLEMENTATION OF THE PROPOSED SECOND-ORDER DLF                         | 33 |

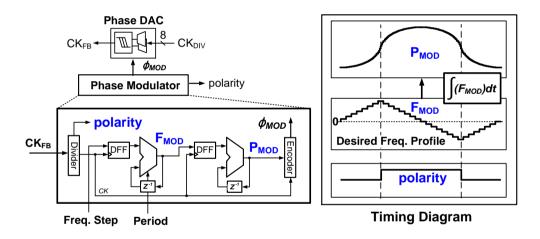

| Fig. 6.18 Implementation of the phase modulator and its operating waveform 8      | 34 |

| Fig. 6.19 (A) Two-point modulation. (B) Gain mismatch between two modulation      |    |

| PATHS DUE TO NONLINEAR DCO GAIN IN WIDE-BAND MODULATION                           | 36 |

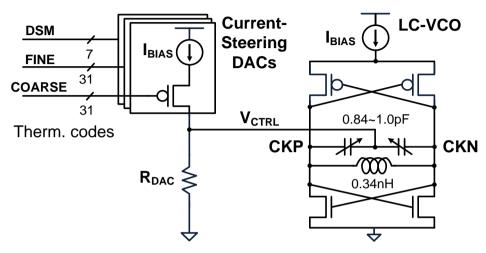

| Fig. 6.20 Implementation of the varactor-based LC-DCO, consisting of current-     |    |

| STEERING DACS AND LC-VCO                                                          | 37 |

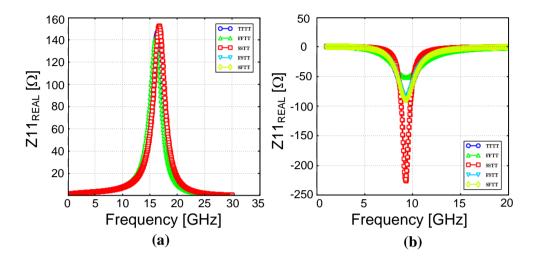

| Fig. 6.21 (a) Simulated ohmic loss of the LC tank. (b) Compensated effective re-  |    |

| SISTANCE $R_{EFF}$ BY NEGATIVE $G_{M}$                                            | 38 |

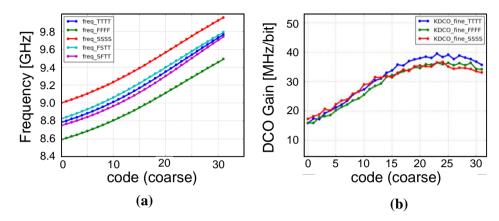

| Fig. 6.22 (a) Simulated LC-DCO frequency tuning range. (b) DCO gain               | 39 |

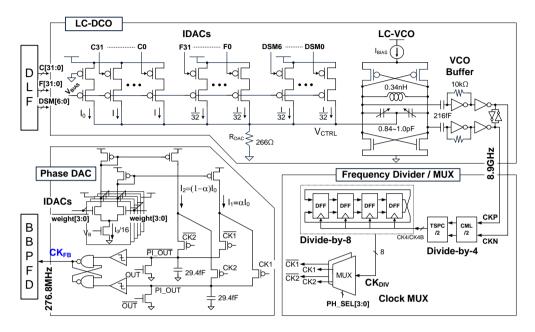

| Fig. 6.23 Overall clock chain denoting important design parameters                | 90 |

| FIG. 6.24 CHIP MICROGRAPH AND PERFORMANCE SUMMARY.                                | 1  |

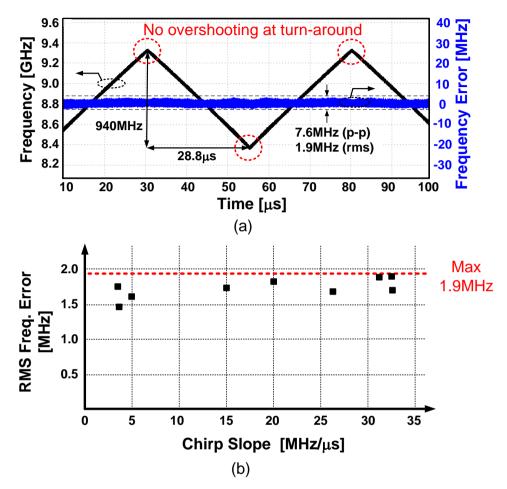

| Fig. 6.25 (a) The measured FMCW chirp profile. (b) RMS frequency error across     |    |

LIST OF FIGURES X

| THE ENTIRE OPERATING RANGE                                                                                   |

|--------------------------------------------------------------------------------------------------------------|

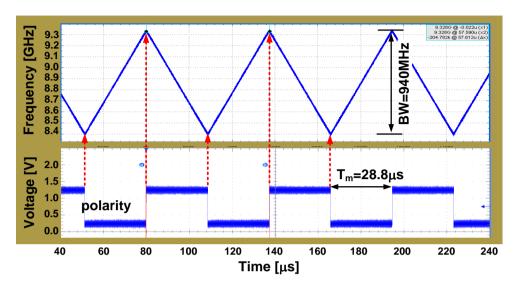

| Fig. 6.26 Instant switching of frequency chirp directed by polarity signal93                                 |

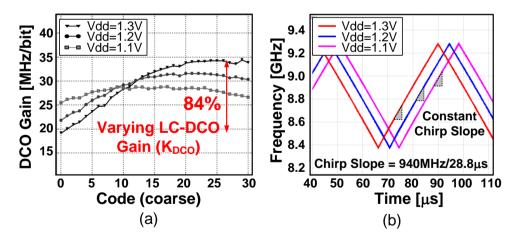

| Fig. 6.27 (a) Varactor-based LC-DCO gain variation. (b) Constant Chirp slope re-                             |

| GARDLESS OF LC-DCO GAIN VARIATION93                                                                          |

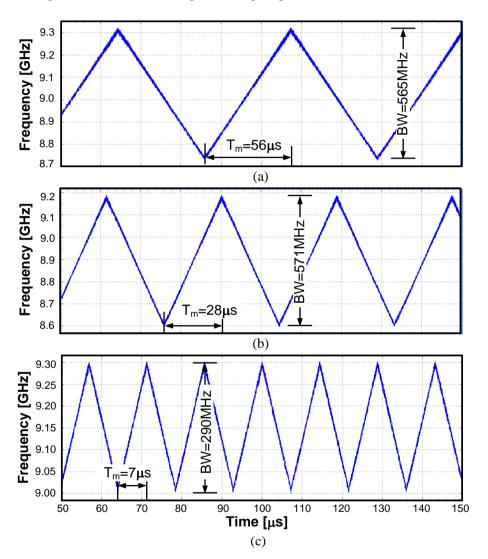

| Fig. 6.28 Various Chirp Profile: (a) $BW$ =565 MHz, $T_M$ =56 $\mu$ s, (b) $BW$ =571 MHz, $T_M$ =28 $\mu$ s, |

| AND (C) $BW=290$ MHz, $T_M=7\mu$ s94                                                                         |

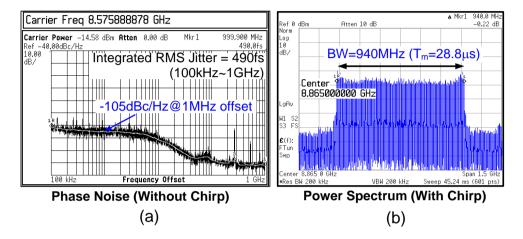

| Fig. 6.29 (a) Measured PLL phase noise without chirp. (b) Measured power spec-                               |

| TRUM WITH CHIRP95                                                                                            |

| Fig. 6.30 Measured power spectrum without chirp                                                              |

LIST OF TABLES XI

# **List of Tables**

| TABLE 5.1 PERFORMANCE COMPARISON. | 64 |

|-----------------------------------|----|

| Tari e 6.1 Performance comparison | 97 |

# Chapter 1

# Introduction

# 1.1 Motivation

The significant increase of the required calculating power and communication bandwidth imposes an increase of power consumption, area, and design complexity on recent system-on-chips (SoCs) for mobile application processor, graphic processing unit (GPU), and so on. Therefore, a scaling of CMOS technology is inevitable and in continuous concerns for satisfying these requirements. However, as the CMOS technology scales down continuously, variations of device characteristics according to process, voltage, and temperature (PVT) conditions are increased accordingly. These variations are originated from the small feature of transistors, resulting in non-uniform carrier mobility between devices and R/C variation on on-chip interconnects and via structures. In addition, near threshold operation of transistors by low supply voltage also increases the variation due to inaccurate device modeling in sub-threshold operations.

With the large PVT variations, a phase-locked loop (PLL) that maintains its performance such as jitter, lock time, and bandwidth is critical for the overall system performances. However, it is becoming more difficult to satisfy all these requirements in limited die area and power budget, because the large variation on device characteristics result in various trade-offs in PLL design [1]. To circumvent these trade-offs, this paper presents a design concept and its validation results for PVT-insensitive PLL, minimizing trade-offs.

In charge-pump PLLs, a loop characteristic varies due to PVT-sensitive circuit parameters such as the voltage-controlled oscillator (VCO) gain and charge-pump (CP) current [2]. Even in digital PLLs, the uncertainties of loop characteristics still remains due to the variation in the digitally-controlled oscillator (DCO) gain and time-to-digital converter (TDC) gain [3].

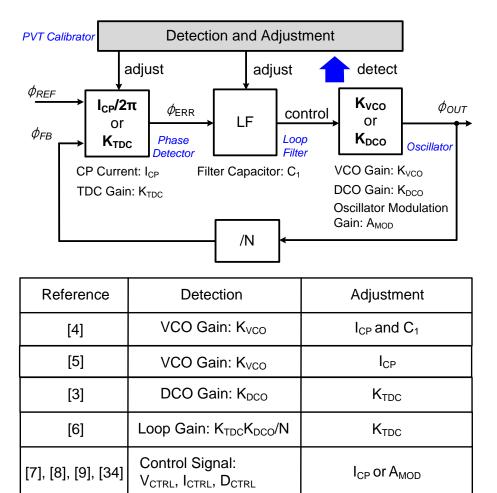

To cope with these uncertainties, prior works have adopted a calibration method for loop parameters [3]-[9]. Most of the calibrations are generally conducted by a detection of loop parameter variation and an adjustment of other loop parameters to compensate for the variations. As shown in Fig. 1.1, a dedicated PVT calibrator detects the variation of loop parameter such as the VCO gain  $K_{VCO}$ , the DCO gain  $K_{DCO}$ , or loop gain at first. Next, the PVT calibrator adjusts other loop parameters, i.e., the charge-pump current  $I_{CP}$ , a filter capacitor  $C_I$ , a TDC gain  $K_{TDC}$ , or a modulation gain for oscillator  $A_{MOD}$ .

Fig. 1.1. Detection and adjustment of loop parameters by PVT calibrator against PVT variations in previously-reported PLLs.

These calibration methods can be largely categorized as a foreground and a background operation. Since most of the calibrations are performed in foreground, they need a periodic recalibration if the environmental conditions (e.g., voltage and temperature) change [3]-[6]. Unlike the foreground calibration, the background calibration

tion can handle the real-time drift due to voltage and temperature [7]-[9]. However, most of the background calibrations monitor analog voltage/current or digital code to detect the voltage and temperature drifts. Therefore, these methods are susceptible to a linearity and noise performance of the detection blocks, so that it is hard to apply them for the deeply-scaled CMOS technologies with low voltage headroom  $(V_{DD}-V_{TH})$  and larger device noises. In addition, the background calibration needs additional blocks and feedback loops to detect and compensate the variation of control voltage/current or code.

To mitigate such drawbacks, this paper presents a digital PLL that desensitize the loop characteristics to PVT variations using functional blocks with PVT-insensitive transfer. The PVT-insensitive transfer characteristic can be realized by a ratiometric design that utilizes a ratio between currents, a fixed ratio between device size, or a fixed fraction of the reference clock period. Also, since we are intended to reduce the uncertainty in functional block-level such as DCO, TDC, and DLF, the proposed PLLs realize predictable characteristics in background without explicit calibration or additional circuits.

#### Consequently, two design concepts covering this thesis can be summarized as:

- 1. Without additional blocks, we build the calibration-free PLLs to keep the PVT-insensitive performances, focusing on the performance of basic PLL blocks.

- 2. Based on the ratiometric design, we make the transfer characteristic of these functional blocks to be only determined by a relative portion of specific variable, size of identical elements, or given clock period or unit interval.

# 1.2 Thesis Organization

This thesis is organized as follows.

In Chapter 2, the characteristics of basic charge-pump PLL and digital PLL are explained. Also, based on their loop dynamics, key design parameters to realize a calibration-free PLL without explicit calibration are introduced.

In Chapter 3, by reviewing the frequently-used oscillators and phase detectors, their variation which causes the uncertainties of loop characteristics is introduced.

In Chapter 4, in order to mitigate the variation of both oscillator and phase detector, the design concepts of covering this paper are explained and compared to previous one.

In chapter 5, a digital LC-PLL that has a PVT-insensitive loop bandwidth (BW) by using a constant-relative-gain DCO and a constant-gain TDC is explained. A motivation and the prior works implementing PVT-insensitive loop BW PLL are explained. To obtain the PVT insensitive loop BW which is a constant fraction of the reference frequency, the PLL architecture even with a simple proportional-integral digital loop filter without explicit calibration is explained. Then, the circuit implementation is explained and the measurement results are shown.

In chapter 6, an 8.9-GHz, digitally-controlled frequency synthesizer PLL capable of precise triangular frequency chirp designed with proposed design concepts is explained. A FMCW radar principle, required specification and the prior works implementing chirp frequency synthesizer PLL are explained. To obtain the precise triangular chirp profile, a proposed calibration-free two-point modulation via a type-

III PLL architecture and a polarity-alternation with given chirp slope information is explained and the simulation results are shown using behavioral model. Then, the circuit implementation is explained and the measurement results are shown.

Chapter 7 summarizes the proposed works and concludes this thesis.

# Chapter 2

# Conventional Phase-Locked Loop (PLL)

In this section, we'll overview the conventional PLL architectures to bring up the critical loop parameters, determining the key performance of the PLL such as jitter, phase noise, lock time, and modulation capability, etc.

# 2.1 Charge-Pump PLL

A charge-pump PLL is the most popular architecture in various fields such as wireless and wireline communications, and system on chips (SoCs) applications [2]. This is because the integral control via a charge-pump and filter capacitor helps suppress static phase offset because it ensures that the loop will not settle until  $\phi_{ERR}$  reaches zero. When  $\phi_{ERR}$  become zero, i.e., no input from the charge-pump, the control voltage maintains constant if a leakage current is not quite large.

## 2.1.1 Operating Principle

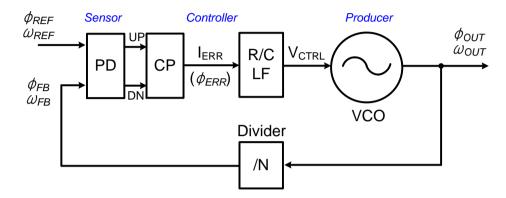

Fig. 2.1. Conventional charge-pump PLL.

Fig. 2.1 shows a block diagram of a conventional charge-pump PLL, consisting of a phase detector as a sensor, a charge-pump (CP) and R/C loop filter (LF) as a controller, and a voltage-controlled oscillator (VCO) as a producer. A PLL is a feedback system that tries to match the oscillator output phase  $\phi_{OUT}$  and frequency  $\omega_{OUT}$  to those of the reference clock,  $\phi_{OUT}$  and  $\omega_{OUT}$ , respectively. A PD measures the error between the two phases,  $\phi_{REF}$  and  $\phi_{FB}$ . Upon the detection of the phase error,  $\phi_{ERR}$ , the LF makes appropriate adjustments on the VCO frequency  $\omega_{OUT}$  to reduce this error. After the phase and frequency between input and output are same,  $\phi_{OUT}$  and  $\omega_{OUT}$  are equal to  $N\phi_{REF}$  and  $N\omega_{REF}$ , respectively.

## 2.1.2 Loop Dynamics

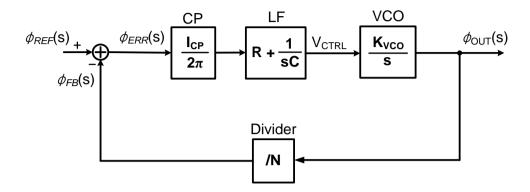

Fig. 2.2. The s-domain model of a second-order charge-pump PLL.

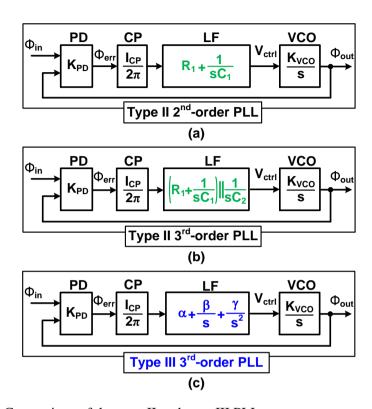

Fig. 2.2 shows the s-domain model of a second-order charge-pump PLL which can guide the role of the basic loop parameters for PLL dynamics. First, the open-loop transfer function the PLL G(s) can be expressed as:

$$G(s) = \frac{\phi_{OUT}}{\phi_{FRR}} = \frac{I_{CP}}{2\pi} \cdot Z(s) \cdot \frac{K_{VCO}}{s} \cdot \frac{1}{N} = \frac{I_{CP}}{2\pi} \cdot \left(R + \frac{1}{sC}\right) \cdot \frac{K_{VCO}}{s} \cdot \frac{1}{N} \quad (3.1)$$

where Z(s) is the transfer function of 1<sup>st</sup> order loop filter (LF),  $I_{CP}$  is the chargepump current,  $K_{VCO}$  is the gain of VCO, and N is the division ratio of the clock divider. And, R and C are the LF resistance and capacitance, respectively.

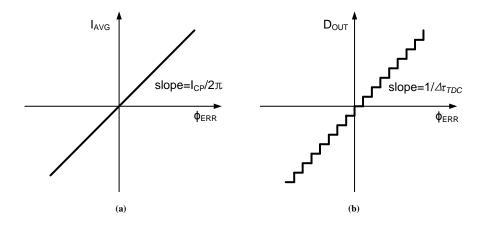

The unit of the gains of the PD and the CP, i.e.,  $I_{CP}/2\pi$  and the VCO, i.e.,  $K_{VCO}$  are A/rad and rad/s/V, respectively.

Using the G(s), the overall closed-loop transfer function of the PLL H(s) can be expressed as:

$$H(s) = \frac{\phi_{OUT}}{\phi_{REF}} = \frac{NG(s)}{1 + G(s)} = \frac{\frac{I_{CP}K_{VCO}}{2\pi C} \cdot (1 + sRC)}{s^2 + \frac{I_{CP}K_{VCO}R}{2\pi N} s + \frac{I_{CP}K_{VCO}}{2\pi NC}} = \frac{N\omega_n^2 \cdot (1 + sRC)}{s^2 + 2\zeta\omega_n s + \omega_n^2}$$

(3.2)

From the definition shown in the last line of (3.2), we can express  $\omega_n$  and  $\zeta$  as:

$$\zeta = \frac{R}{2} \cdot \sqrt{\frac{I_{CP} K_{VCO} C}{2\pi N}}$$

$$\omega_n = \sqrt{\frac{I_{CP} K_{VCO}}{2\pi N C}}$$

(3.3)

$$\omega_{BW} \approx 2\zeta \omega_n = \frac{I_{CP} K_{VCO} R}{2\pi N}$$

(3.4)

where  $\omega_{BW}$  is the loop bandwidth of the PLL.

(3.3) and (3.4) tells us that the loop bandwidth  $\omega_{BW}$  as well as the natural frequency  $\omega_n$  and damping factor  $\zeta$  of the charge-pump PLL are significantly dependent on the loop parameters such as  $I_{CP}$ ,  $K_{VCO}$ , R, and C, varying with process, voltage, and temperature (PVT) conditions.

# 2.2 Digital PLL

A digital phase-locked loop (PLL) that can be realized entirely in digital circuits has been an actively pursued goal in recent literature [3]. The motivation is to eliminate the analog circuits and control signals in conventional charge-pump PLLs so that their designs are insensitive to a leakage current on the capacitors and can be easily migrated to various process technologies. In addition, the digital PLL removes an area penalty imposed by the RC loop filter for narrow loop bandwidth, a dynamic range problem of the charge-pump in deeply-scaled technologies as the supply voltage approaches near the device threshold, and an up/down current mismatch incurring reference spur.

## 2.2.1 Operation Principle

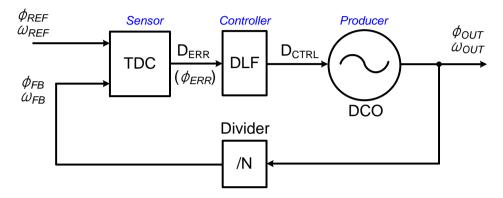

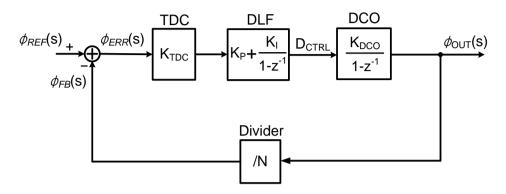

Fig. 2.3. A digital PLL equivalent to the conventional charge-pump PLL.

Fig. 2.3 shows a block diagram of a digital PLL equivalent to the charge-pump PLL in Fig. 2.1, which consists of a time-to-digital converter (TDC), a digital loop filter (DLF), a digitally-controlled oscillator (DCO), and a divide-by-N frequency divider. The TDC provides a digitized measure  $D_{ERR}$  of the phase error between the two phases,  $\phi_{REF}$  and  $\phi_{FB}$ . Upon this  $D_{ERR}$ , the DLF updates the DCO input code  $D_{CTRL}$  proportional to the phase error. According to the  $D_{CTRL}$ , the DCO controls its frequency. Finally, the divide-by-N divider generates feedback clock phase  $\phi_{FB}$  for the TDC.

#### 2.2.2 Loop Dynamics

Fig. 2.4. The z-domain model of a second-order digital PLL.

Fig. 2.4 shows the z-domain model of a second-order digital PLL. First, the open-loop transfer function the PLL G(s) can be expressed as:

$$G(z) = \frac{\phi_{OUT}}{\phi_{FRR}} = K_{TDC} \cdot \left( K_P + \frac{K_I}{1 - z^{-1}} \right) \cdot \frac{K_{DCO}}{1 - z^{-1}} \cdot T_S \cdot \frac{1}{N}$$

(3.5)

Where  $K_{TDC}$  and  $K_{DCO}$  is the TDC and DCO gains, in units of bits/radian and rad/s/bit, respectively and N is the division ratio of the clock divider.  $K_P$  and  $K_I$  are the fixed proportional and integral gains of the DLF, respectively and  $T_S$  is the sampling period of the DLF.

Here, G(z) can be converted into s-domain continuous-time model by approximating  $z^{-1}$  as  $\exp(-sT_S) \approx 1-sT_S$ , while this approximation is valid only for a frequency range well below the sampling frequency  $(1/T_S)$  [10].

Therefore, the s-domain open-loop transfer function can be derived as:

$$G(s) = \frac{\phi_{OUT}}{\phi_{FDP}} = \frac{K_{TDC}K_{DCO}}{NT_s} \cdot \frac{K_P T_S s + K_I}{s^2}$$

(3.6)

Using the G(s), the overall closed-loop transfer function of the PLL H(s) can be expressed as:

$$H(s) = \frac{\phi_{OUT}}{\phi_{REF}} = \frac{NG(s)}{1 + G(s)} = \frac{\frac{K_{TDC}K_{DCO}}{T_S} \cdot \left(K_p T_S s + K_I\right)}{s^2 + \frac{K_p K_{TDC}K_{DCO}}{N} s + \frac{K_I K_{TDC}K_{DCO}}{NT_S}} = \frac{N\omega_n^2 \cdot \left(1 + s \frac{K_p}{K_I} T_S\right)}{s^2 + 2\zeta \omega_n s + \omega_n^2}$$

$$\zeta = \frac{K_p}{2} \cdot \sqrt{\frac{K_{TDC}K_{DCO}T_S}{NK_I}}$$

$$\omega_n = \sqrt{\frac{K_I K_{TDC}K_{DCO}}{NT_S}}$$

$$\omega_{BW} \approx 2\zeta \omega_n = \frac{K_{TDC}K_{DCO}K_p}{N} \quad (3.9)$$

Equation (3.8) and (3.9) implies that the loop bandwidth  $\omega_{BW}$  as well as the natural frequency  $\omega_n$  and damping factor  $\zeta$  of the digital PLL are also dependent on the loop parameters such as  $K_{TDC}$  and  $K_{DCO}$ , varying with PVT conditions.

Therefore, even though the digital PLL has many advantages compared to the charge-pump PLL, these uncertainties on loop parameters are still problematic in the use of digital PLLs.

# **Chapter 3**

# Variations on Phase-Locked Loop (PLL)

In this section, we'll review the variation of oscillator and phase detector gains which are key parameters to determine the loop characteristics of the PLL.

## 3.1 Oscillator Gain Variation

As explained in Chapter 2, an oscillator generates a clock that has a frequency controlled by a control signal from the loop filter. There are two kinds of the most popular oscillators. At first, a ring oscillator is used in many consumer SoCs and energy-efficient transceivers due to its wide tuning range, low power, and multi-phase outputs. While the ring oscillator has many advantages, it typically has a poor jitter performance compared to an LC oscillator [11]. In contrast, the LC oscillator has the superior jitter and phase noise performance at high frequency, so that it is widely used for RF and wireline transceivers with high data rate. However, it typically op-

erates only over a narrow tuning range and dissipates large power. Unfortunately, the gain of both ring and LC oscillators are PVT-sensitive parameters. For instance, in 65nm CMOS technologies, the gain of the ring oscillator varies by a factor of 3~6 and the gain of the LC oscillator with varactor-based tuning varies by a factor of 1~2.

### 3.1.1 Ring Voltage-Controlled Oscillator

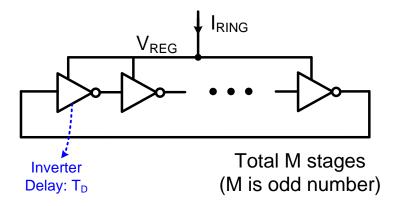

Fig. 3.1. A ring oscillator composed of M stage inverters.

Fig. 3.1 shows a ring oscillator, consisting of M stage CMOS inverters. A delay  $T_D$  of a single stage inverter and an oscillator frequency  $f_{osc}$  can be expressed as:

$$T_{D} = \frac{C \cdot V_{REG}}{I_{RING}}$$

$$f_{osc} = \frac{1}{2MT_{D}} = \frac{I_{RING}}{2MCV_{REG}}$$

(3.10)

Where C is the total load capacitance of each inverter stage, M is the number of stages,  $I_{RING}$  is the oscillator driving current, and  $V_{REG}$  is the supply voltage of the ring oscillator.

By differentiating the last line of (3.10) according to  $T_D$ , the gain of the ring oscillator can be derived as:

$$K_{RING} = \frac{\partial f_{osc}}{\partial T_D} = -\frac{1}{2M} \cdot \frac{1}{T_D^2} \quad (3.11)$$

Equation (3.11) implies that the gain of ring oscillator is inversely proportional to the square of the  $T_D$ . This result implies that the gain is nonlinear and sensitive to the PVT variations of the delay element.

For instance, the simulated FO4 delay of thin oxide NMOS in TSMC 65nm CMOS technology is shown in Fig. 3.2. By (3.11), delay variation by a factor of 2.4 results in the gain decrease by factor of 5.78.

Fig. 3.2. Simulated delay variation of the inverter versus fan-out.

## 3.1.2 LC Voltage-Controlled Oscillator

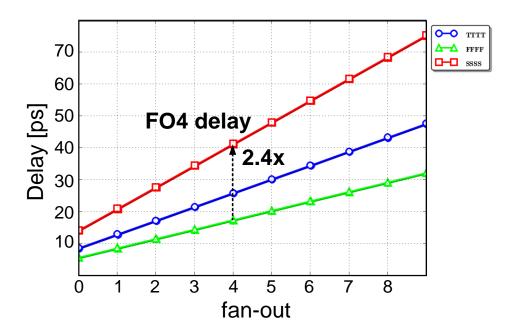

Fig. 3.3. (a) Conventional LC-VCO with varactor tuning. (b) Varactor tuning curve.

Fig.3.3 shows the schematic of conventional LC-VCO with varactor-based tuning. The VCO gain  $K_{VCO}$  can be written as:

$$K_{VCO} = \left| \frac{\partial \omega_{osc}}{\partial V_{CTRL}} \right| = \left| \frac{\partial \omega_{osc}}{\partial C_{VAR}} \right| \cdot \left| \frac{\partial C_{VAR}}{\partial V_{CTRL}} \right|$$

(3.12)

Where  $V_{CTRL}$  and  $C_{VAR}$  are the control voltage and the capacitance of varactor, respectively. The oscillation frequency  $\omega_{osc}$  is given by:

$$\omega_{osc} = \frac{1}{\sqrt{L \cdot (C_o + C_{VAR})}} \quad (3.13)$$

Where  $C_0$  is the tank capacitance excluding the  $C_{VAR}$ .

By differentiating (3.13) with respect to  $C_{VAR}$ , the frequency change over  $C_{VAR}$  can

be derived as:

$$\left| \frac{\partial \omega_{osc}}{\partial C_{VAR}} \right| = \frac{L}{2} \cdot \omega_{osc}^3 \quad (3.14)$$

Therefore, from (3.12), the VCO gain  $K_{VCO}$  can be derived as:

$$K_{VCO} = \frac{L}{2} \cdot \omega_{osc}^{3} \cdot \left| \frac{\partial C_{VAR}}{\partial V_{CTRL}} \right| \quad (3.15)$$

Equation (3.15) indicates that the gain of LC-VCO is proportional to  $|\partial C_{VAR}/\partial V_{CTRL}|$ . As shown in Fig. 3.3(b), the slope  $|\partial C_{VAR}/\partial V_{CTRL}|$  on varactor tuning curve is changed by the average voltage of oscillation node ( $V_C$ ) that is changed by PVT conditions [12]. In addition, the  $K_{VCO}$  are proportional to  $\omega^3_{OUT}$  even if linear capacitor tuning is possible, i.e., constant  $|\Delta C_{VAR}/\Delta V_{CTRL}|$ . Therefore, the gain of LC-VCO is nonlinear according to operating frequency and sensitive to PVT conditions.

### 3.1.3 LC Digitally-Controlled Oscillator (LC-DCO)

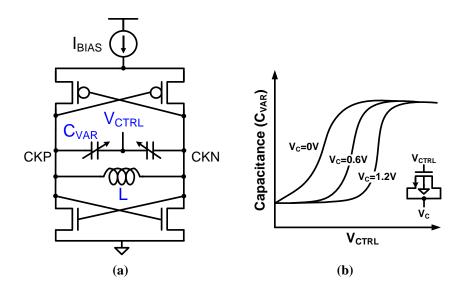

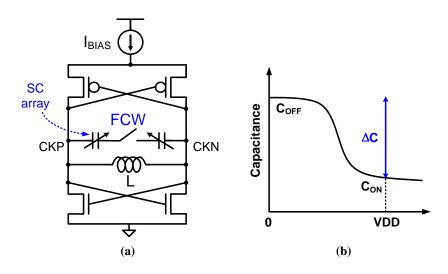

Fig. 3.4. (a) LC-DCO with switched-capacitor (SC) array. (b) Switched-capacitor tuning curve.

As shown in Fig. 3.4(a), an LC digitally-controlled oscillator (LC-DCO) is usually implemented by using switched-capacitor (SC) array [13]. Fig. 3.4(b) also shows the tuning curve of varactor used in SC array. When a frequency control word (FCW) is low and high, the capacitance is large ( $C_{OFF}$ ) and small ( $C_{ON}$ ). The input FCW controls the frequency of LC-DCO by changing the number of switched-capacitors operating in large or small capacitance region.

Similar to the LC-VCO, the DCO gain  $K_{DCO}$  can be expressed as:

$$K_{DCO} = \frac{L}{2} \cdot \omega_{osc}^{3} \cdot \left| \frac{\Delta C}{\Delta D_{CTRL}} \right|$$

(3.16)

Where  $D_{CTRL}$  is the FCW from a digital loop filter and  $\Delta C$  is the difference between  $C_{OFF}$  and  $C_{ON}$ , respectively.

According to (3.16), if the  $\Delta C$  is changed by PVT conditions, the DCO gain  $K_{DCO}$  also changes. In addition, since the  $K_{DCO}$  is also proportional to  $\omega^3_{osc}$ , the variation of  $\Delta C$  can greatly affect the  $K_{DCO}$  in the vicinity of high frequency.

# 3.2 Phase Detector Gain Variation

As explained in Chapter 2, a phase detector (PD) measures the phase error between the reference clock phase and the feedback clock phase. There are two kinds of widely used phase detectors.

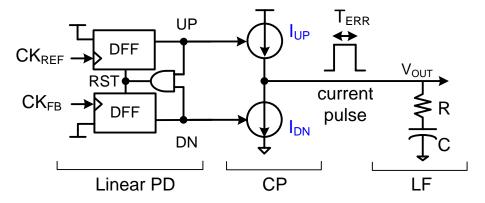

#### 3.2.1 Linear Phase Detector (PD)

Fig. 3.5. Linear PD and CP convert phase error to current pulse.

As shown in Fig. 3.5, a linear PD which is implemented by two edge-triggered DFFs with reset logic is widely used in most of charge-pump PLLs due to its linear transfer function regardless of PVT and frequency conditions. However, although

the transfer characteristic of linear PD is insensitive to PVT conditions, extent of current pulse produced by the charge pump (CP) followed by linear PD (i.e., linear PD + CP) varies with PVT conditions. This is because the CP current  $I_{UP}$  and  $I_{DN}$  change according to PVT conditions. It is well known that the gain of linear PD is determined as  $I_{CP}/2\pi$ . So, the gain of linear PD is also PVT-sensitive design parameter.

### 3.2.2 Linear Time-to-Digital Converter (TDC)

Fig. 3.6. (a) Vernier TDC based on delay chains. (b) BBPD and its transfer curve.

Fig. 3.6(a) shows the linear time-to-digital converter (TDC) based on delay chain. One problem with the delay chain TDC is that its gain and resolution may vary with the operating conditions. For instance, a Vernier TDC in [14] is composed of two delay chains, of which delay can change with the PVT conditions. Ring oscillator based TDCs also have a problem due to the delay variation, and need to be compensated [39],[40].

On the other hand, in Fig. 3.6(b), a bang-bang PD (BBPD) using a single D-type flip-flop can serve as a linear TDC in presence of the input jitter, but its effective gain depends strongly on the standard deviation of input jitter, i.e.,  $K_{BB} \propto 1/\sigma$  [15]. One way to alleviate this dependency is to add an intentional dither jitter that can overwhelm the other jitter components [16], [17]. However, the resulting TDC characteristic may still be subject to PVT variations, unless the dither jitter is generated in a PVT-independent way.

# **Chapter 4**

# Proposed DCO and TDC for Calibration-Free PLL

In previous sections, we have reviewed the PVT variations on PLLs. In this section, in order to mitigate these variations, we'll investigate the principle of key building blocks, reducing the variations on the PLL. Thanks to the proposed DCO and TDC, the PLL can realize PVT-insensitive loop characteristics without an explicit calibration or additional circuits.

## **4.1 Digitally-Controlled Oscillator (DCO)**

#### 4.1.1 Overview

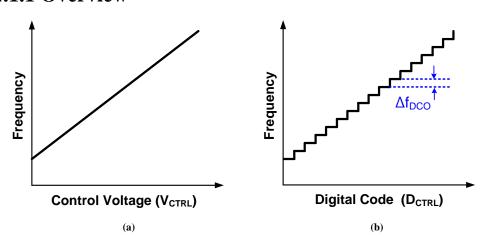

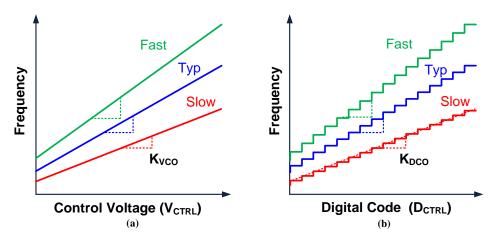

Fig. 4.1. Transfer characteristics of (a) VCO and (b) DCO.

A digitally-controlled oscillator (DCO) performs a digital-to-frequency conversion for digital PLL. Therefore, the DCO clock frequency is controlled by the input digital code contrary to the control voltage in the VCO. Fig. 4.1 shows the transfer characteristics of the VCO and DCO. As explained in Section 3.1, while the VCO gain indicates a frequency change with respect to the control voltage change, i.e.,  $|\partial f_{VCO}/\partial V_{CTRL}|$ , the DCO gain represents a frequency change with respect to the unit change of input digital code, i.e.,  $|\partial f_{DCO}/\partial D_{CTRL}|$ .

Generally, most of the VCO and DCO designs focus on the linear voltage-to-frequency (V-to-f) and code-to-frequency (D-to-f) characteristics, respectively. If the gain of VCO and DCO is ideally constant, these linear transfer characteristics are effective in entire frequency tuning range. The main reason of this linearization is that the minimized gain variation can improve noise sensitivity of the oscillator [8].

Likewise, a LC-VCO for low noise PLL tries to reduce the oscillator gain itself by utilizing multiple low gain V-to-f curves in the RF applications [7].

Unfortunately, the VCO and DCO with linear transfer have fundamental drawback. As shown in Fig. 4.2, the gain of the VCO and DCO still vary with PVT conditions.

Fig. 4.2. Oscillator gain variation vs. PVT conditions: (a) VCO and (b) DCO.

Even if the ring-VCO PLL operates at single frequency, the gain variation by PVT change results in large variation of loop characteristics such as natural frequency and damping factor [1]. Also, in the LC-VCO PLL with linear varactor tuning, the gain variation according to PVT and  $\omega_{OUT}$  changes results in the variation of loop transfer [7]. For instance, in wireless application such as Radar, the loop bandwidth variation deteriorates a modulation accuracy of chirp signal generator. Also, in wireline application such as SONET [18], the variation of jitter peaking bring about large jitter amplification when multiple PLLs are in cascade.

#### 4.1.2 Constant-Relative-Gain DCO

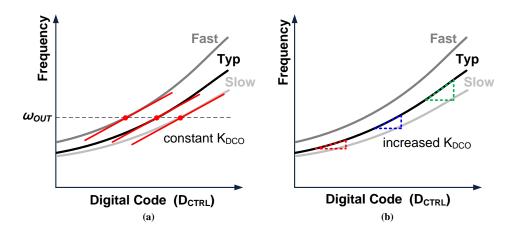

To address this problem, a VCO and DCO with constant relative-gain were presented in [19],[20]. The constant-relative-gain DCO changes its frequency by a constant fraction of the current operating frequency  $\omega_{OUT}$  in response to a unit step in its digital input:

$$\frac{\Delta \omega_{OUT}/\omega_{OUT}}{\Delta D_{IN}} = constant \quad (4.1)$$

That is, at a given operating frequency  $\omega_{OUT}$ , which is fixed by the reference frequency and multiplication ratio of the PLL, the DCO has a constant gain, or equivalently a gain that scales proportionally with  $\omega_{OUT}$  as shown in Fig. 4.3.

In a linear DCO with constant gain  $\Delta\omega_{OUT}/\Delta D_{IN}$ , as the  $\omega_{OUT}$  increases, the relative change according to unit code change  $\Delta\omega_{OUT}/(\Delta D_{IN} \cdot \omega_{OUT})$  decreases. On the other hand, in constant-relative-gain DCO follows (4.1), the relative change according to unit code change  $\Delta\omega_{OUT}/(\Delta D_{IN} \cdot \omega_{OUT})$  stays constant. In other words, the DCO gain  $K_{DCO} = \Delta\omega_{OUT}/\Delta D_{IN}$  is solely proportional to  $\omega_{OUT} = N \cdot \omega_{REF}$ , which is typically well-controlled. The constant-relative-gain DCO can be achieved by the ratiometric circuit design and this will be explained in circuit implementations.

Fig. 4.3. Constant relative-gain characteristics: (a) constant  $K_{DCO}$  at given operating frequency  $\omega_{OUT}$  and (b)  $K_{DCO}$  is proportional to  $\omega_{OUT}$ .

In addition, in case of the LC-DCO covering relatively wide frequency range with single tuning curve, the  $K_{DCO}$  are significantly nonlinear according to  $\omega_{OUT}$  [7]. In (3.16), the  $K_{DCO}$  are proportional to  $\omega_{OUT}^3$  even though linear capacitor tuning is adopted, i.e., constant  $|\Delta C/\Delta D_{CTRL}|$ . As a result, at high frequency, phase noise performance may worsen by large  $K_{DCO}$ . On the other hand, since the constant-relative-gain DCO has the  $K_{DCO}$  proportional to  $\omega_{OUT}$ , the  $K_{DCO}$  is much smaller than that of linear capacitor-tuned LC-DCO at high frequency. Fig. 4.4 shows the comparison of  $K_{DCO}$  according to  $\omega_{OUT}$  between linear switched-capacitor-based LC-DCO and constant relative-gain LC-DCO.

Fig. 4.4. Comparison of  $K_{DCO}$  according to  $\omega_{OUT}$  between the linear capacitor-tuned LC-DCO and constant relative-gain LC-DCO.

# **4.2 Time-to-Digital Converter (TDC)**

#### 4.2.1 Overview

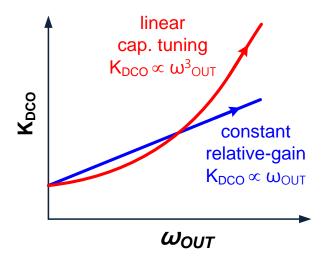

Fig. 4.5 Transfer characteristic of (a) linear PD and (b) TDC.

Fig. 4.5 shows the transfer characteristic of linear phase detector (PD) and linear time-to-digital converter (TDC). The linear PD converts the phase error  $\phi_{ERR}$  to voltage in a charge-pump PLL. In similar way, the TDC generates a digital code which is proportional to the  $\phi_{ERR}$  between the reference and feedback clock phases.

The TDC output  $D_{OUT}$  can be expressed by:

$$D_{OUT} = \frac{\Delta t}{\Delta \tau_{TDC}} = \left(\frac{\Delta \phi}{2\pi} \cdot T_{REF}\right) \cdot \frac{1}{\Delta \tau_{TDC}} = \frac{T_{REF}}{2\pi \cdot \Delta \tau_{TDC}} \cdot \Delta \phi \tag{4.3}$$

Where  $\Delta \tau_{TDC}$  is the unit delay of delay chain. And,  $\Delta t$  and  $\Delta \phi$  are the time and phase error, respectively [14].

Therefore, the TDC gain  $K_{TDC}$  in units of bit/rad can be written as:

$$K_{TDC} = \frac{\Delta D_{OUT}}{\Delta \phi} = \frac{T_{REF}}{2\pi \cdot \Delta \tau_{TDC}}$$

(4.4)

(4.4) indicates that the TDC gain is determined by the unit delay of delay chain and operating frequency. As explained in Chapter 3.1, delay variation by a factor of 2~4 in CMOS inverter results in significant change of the  $K_{TDC}$ , so that it is problematic for predictable PLL loop characteristics. In addition, the  $K_{TDC}$  is also changed by an operating frequency (=1/ $T_{REF}$ ). Therefore, the TDC gain calibration method has been actively studied [17].

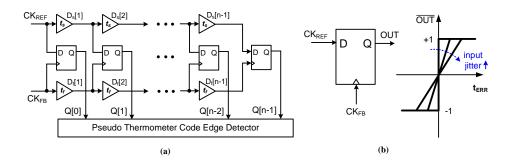

#### 4.2.2 Constant-Gain TDC

To mitigate the TDC gain variation, we presented the constant-gain TDC architecture regardless of PVT, input jitter, and operating frequency conditions [20]. The proposed constant-gain TDC provides a digitized measure of the phase error with a constant resolution measured in radians or UIs. The TDC gain  $K_{TDC}$  in units of bits/UI stays constant regardless of the PVT and frequency conditions.

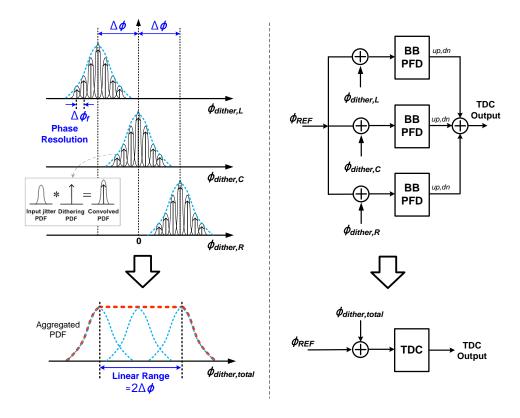

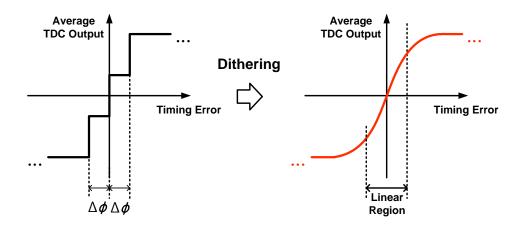

Fig. 4.6. (a) Linearization of the TDC characteristics with added random dither. (b) Implementation of constant-gain TDC.

Fig. 4.6 illustrates how the proposed TDC provides a linear measure on the phase error. A TDC gain which is independent of the PVT, input jitter, and frequency conditions can be achieved by using three oversampling BB-PFDs triggered by individually dithered clocks. These three dithered clocks with a unit phase step of  $\Delta\phi_f$  and a phase offset of  $\Delta\phi$ , 0, or  $\Delta\phi$  serve as sampling clocks for BB-PFDs. Both the dither jitter step  $\Delta\phi_f$  and phase offset  $\Delta\phi$  are digitally programmable in units of a phase interpolator (PI) resolution steps via an external I<sup>2</sup>C interface.

Basically, each BB-PFD recovers the linear measure in a statistical sense by comparing the phase error with a different threshold. Furthermore, the use of multiple BB-PFDs whose sampling phases dither at different offsets ( $\phi_{dither,L}$ ,  $\phi_{dither,C}$ , and  $\phi_{dither,R}$ ) enhances the accuracy of the phase error that can be recovered in a finite time period.

Fig. 4.6(a) illustrates the probability density functions (PDFs) of the individual feedback clock phases triggering the BB-PFDs and the aggregate PDF of all the clock phases combined ( $\phi_{dither,tot}$ ). When finite input jitter is present, the effective jitter PDF experienced by the BB-PFDs is the input jitter PDF convolved with the added dither jitter PDF. It can be shown that with a proper amount of dither jitter and phase offset between the unit PDFs, the aggregate PDF can take an approximately uniform distribution in the range of  $-\Delta\phi \sim +\Delta\phi$ . This uniform PDF results in a linear TDC characteristic within the range of  $2\Delta\phi$  when the TDC output is computed as a difference between the up and dn counts of the BB-PFDs, accumulated over a given period.

Consequently, as long as the phase offset  $(\Delta \phi)$  and dither jitter step  $(\Delta \phi_f)$  maintain constant magnitudes in units of UIs (i.e., in fixed numbers of phase steps), the effec-

tive TDC gain is determined mainly by  $\Delta\phi$ , which can remain constant despite the change in the PVT, input jitter conditions at given operating frequency. Even if the operating frequency changes, the TDC gain in units of bit/UI maintains by the operating principle using fixed number of phase steps.

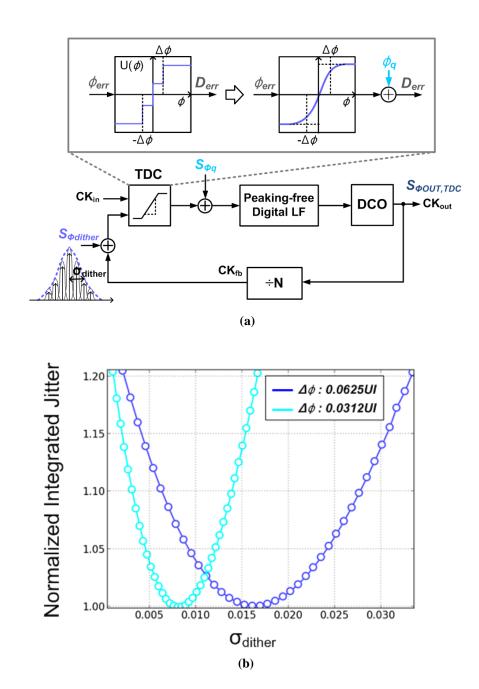

However, the dithering jitter and quantization noise of the oversampling TDC can degrade the overall phase noise performance of the PLL. Fig. 4.7(a) depicts the noise model to analyze these TDC-related noises. Using the pseudo-linear approach described in [41], the TDC is modeled as a linear gain element followed by an additive white noise source, where the effective linear gain  $K_{TDC,eff}$  and the noise variance  $\phi_q^2$  can be derived using the following equations:

$$K_{TDC,eff} = \frac{E[\phi_{err} \cdot U(\phi_{err})]}{E[\phi_{err}^{2}]} = \frac{\int_{-\infty}^{+\infty} U(\phi_{err}) \cdot \phi_{err} \cdot f(\phi_{err}) d\phi_{err}}{\int_{-\infty}^{+\infty} \phi_{err}^{2} \cdot f(\phi_{err}) d\phi_{err}}$$

$$\sigma_{q}^{2} = E[U(\phi_{err})^{2}] - K_{TDC,eff}^{2} \cdot E[\phi_{err}^{2}]$$

$$= \int_{-\infty}^{+\infty} U(\phi_{err})^{2} \cdot f(\phi_{err}) d\phi_{err} - K_{TDC,eff}^{2} \int_{-\infty}^{+\infty} \phi_{err}^{2} \cdot f(\phi_{err}) d\phi_{err}$$

$$(4.6)$$

$U(\cdot)$  denotes the raw transfer function of the TDC and  $f(\phi_{err})$  is the PDF of the phase error including the dither. Once this linearized TDC model is derived, the power spectral density (PSD) of the PLL output phase noise due to the TDC quantization noise  $(\phi_q)$  and dither jitter  $(\phi_{dither})$  can be obtained:

$$S_{\phi_{OUT},TDC}(f) = \left(S_{\phi dither}(f) + S_{\phi q}(f)/K_{TDC,eff}^{2}\right) |H(f)|^{2}$$

(4.7)

Fig. 4.7. (a) A PLL model for analyzing the noise contribution of the TDC quantization noise and dither jitter. (b) The normalized total integrated jitter.

Using Eq. (4.5)-(4.7), it can be shown that for a given BB-PFD phase spacing of  $\Delta\phi$ , there exists an optimal amount of dither jitter ( $\sigma_{dither}$ ) that minimizes the contribution of the TDC-related noises to the output phase noise,  $S_{\phi OUT,TDC}$ . Fig. 4.7(b) plots the normalized integrated jitter of  $S_{\phi OUT,TDC}$  as a function of  $\sigma_{dither}$  for the  $\Delta\phi$  values of 0.0625 and 0.0312-UI when the PLL has a bandwidth of 750-kHz and damping factor of 1. The optimal  $\sigma_{dither}$  values are found to be 0.016 and 0.008-UI, respectively. When the high-frequency dither jitter is sufficiently filtered by the PLL bandwidth, the contribution of the quantization noise ( $\phi_q$ ) dominates over that of the dither jitter ( $\phi_{dither}$ ).

# Chapter 5

## **PVT-Insensitive-Bandwidth PLL**

In this section, a PVT-insensitive loop bandwidth PLL with a constant-gain TDC and a constant relative-gain LC-DCO will be introduced as an example corresponding proposed design concepts. Based on ratiometric circuit designs, the LC-DCO makes a fixed 0.011% change to its current frequency for a unit change in its digital input and the TDC can maintain a fixed range of –0.13~0.13-UI and fixed resolution of 0.00781-UI across PVT variations. With such DCO and TDC, the prototype digital PLL fabricated in a 28-nm CMOS technology operates over an 8.38~9.34-GHz frequency range and realizes a bandwidth which is a constant fraction of 0.00305±2.95% of the reference frequency across the whole range. Also, at 8.84-GHz, the PLL dissipates 15.2-mW, achieves 652-fs<sub>rms</sub> integrated jitter from 10-kHz to 1-GHz, and has a nearly constant BW at 822-kHz with the worst-case deviation of only ±4.25% across three different die samples and the supply ranging from 1.0 to 1.2V.

#### **5.1 Overview**

Various standards for wireless and wireline communications require a phase-locked loop (PLL) that maintains a well-controlled loop bandwidth (BW) as well as low phase noise against process, voltage, and temperature (PVT) variations [1]. As explained in Section 3, PLL design parameters determining the loop characteristics are changed according to PVT and/or frequency conditions.

Fig. 5.1. The PLL loop bandwidth variation according to PVT conditions.

As shown in Fig. 5.1, in analog PLLs, the loop BW may vary due to PVT-sensitive circuit parameters such as the voltage-controlled oscillator (VCO) gain and charge pump (CP) current. Even in digital PLLs, the loop BW may deviate from its optimum value due to the variation in the digitally-controlled oscillator (DCO) gain and time-to-digital converter (TDC) gain. To suppress such undesired variation in the loop BW, this work presents a digital PLL that desensitizes the loop BW to PVT variations using a LC-DCO and TDC with constant gains at a given operating frequency.

### **5.2 Prior Works**

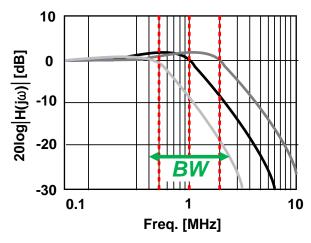

Prior works have demonstrated that the PLL BW can be kept constant by adapting the loop parameters and compensating the variations in the oscillator characteristics [4]-[8].

Fig. 5.2. The previously-reported PVT-insensitive loop BW PLLs: (a) BW tracking PLL via loop BW calibration [4], (b) constant loop BW PLL via loop BW calibration [5], [6], and BW tracking PLL via adaptive CP biasing [7], [8].

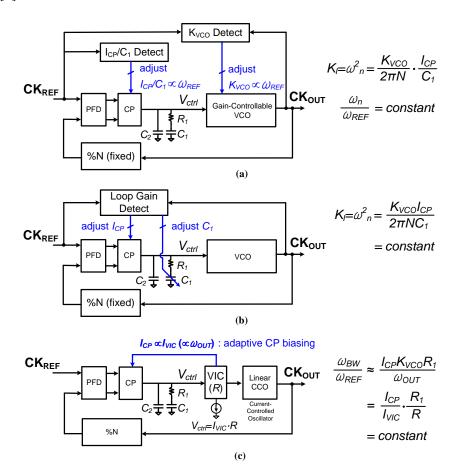

For instance, the PLLs presented in [4]-[6] employed a digital calibration scheme that measures the DCO or VCO gain and adjusts the TDC gain, CP current, or filter capacitor, accordingly. As shown in Fig. 5.2(a), a loop BW calibration is conducted for the constant natural frequency  $\omega_n$  by calibrating the VCO gain  $K_{VCO}$  and the charge pump current  $I_{CP}$  over a loop filter capacitor  $C_I$  (i.e.,  $I_{CP}/C_I$ ) in comparison with the reference frequency  $\omega_{REF}$  [4]. As a result, it realizes not only process-independent  $\omega_n$  at each operating frequency but also constant BW-to-frequency ratio i.e.,  $\omega_n/\omega_{REF}$ =constant. The loop BW calibration in Fig. 5.2(b) adjusts the  $I_{CP}$  and  $C_I$  to compensate for the loop gain variation. The constant natural frequency  $\omega_n$  can be achieved by calibrating the charge pump current  $I_{CP}$  and loop filter capacitor  $C_I$  by measuring the VCO gain or an integral path gain [5],[6]. However, one drawback of this approach is that the calibration is performed in foreground, requiring recalibration if the environmental conditions drift.

On the other hand, the PLLs in [7],[8] calibrate the BW in the background by maintaining a constant ratio between the currents of the charge pump and oscillator, as shown in Fig. 5.2(c). Since the ratio between the bandwidth  $\omega_{BW}$  and reference frequency  $\omega_{REF}$  is fixed by this current ratio, the BW can stay constant for a given operating frequency. However, it is becoming difficult to keep the current ratio constant over a wide operating range for deeply-scaled technologies as the supply voltage approaches near the device threshold.

To address these problems, this paper presents a digital PLL with a constant relative-gain LC-DCO and a constant-gain TDC, realizing a PVT-insensitive loop bandwidth without requiring any explicit calibration loop or additional components.

# 5.3 Proposed PVT-Insensitive-Bandwidth

#### **PLL**

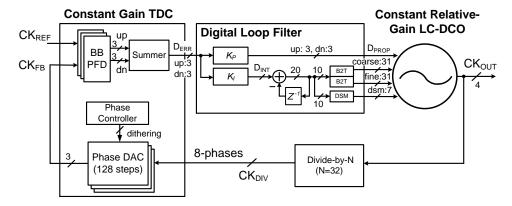

Fig. 5.3. The proposed digital PLL with PVT-insensitive loop bandwidth.

Fig. 5.3 illustrates the architecture of the proposed PLL, consisting of a TDC, a proportional-integral digital loop filter (DLF), an LC-DCO with quadrature phase outputs, and a divide-by-32 frequency divider. The key to achieving the PVT-insensitive loop BW without any calibration loop or adaptive CP biasing is the constant-gain TDC and the constant-relative-gain DCO. A constant-gain TDC provides a digitized measure of the phase error with a constant resolution measured in radians or UIs. In other words, the TDC gain in units of bits/UI stays constant over the PVT and frequency conditions. On the other hand, a constant-relative-gain DCO changes its frequency by a constant fraction of the current operating frequency  $\omega_{OUT}$  in response to a unit step in its digital input:

$$\frac{\Delta \omega_{OUT} / \omega_{OUT}}{\Delta D_{IN}} = constant$$

(5.1)

That is, at a given operating frequency  $\omega_{OUT}$ , which is fixed by the reference frequency and multiplication ratio of the PLL, the DCO has a constant gain, or equivalently a gain that scales proportionally with  $\omega_{OUT}$ . The constant-gain TDC and constant-relative-gain DCO are realized by ratiometric designs, i.e. using circuits that rely only on relative ratios between identical elements, as explained in Section 4. Therefore, the characteristics of the TDC and DCO are fixed at the design stage and not affected by the change in the absolute parameters such as PVT variations or model uncertainties.

With a constant-gain TDC and constant-relative-gain DCO, a digital PLL can realize a bandwidth which is a constant fraction of the reference frequency even with a simple proportional-integral digital loop filter without any explicit calibration loops. It is well known that the loop BW  $\omega_{BW}$  and damping factor  $\zeta$  of a digital PLL are expressed as [20]:

$$\omega_{BW} \approx 2\zeta \omega_n = \frac{K_P K_{TDC} K_{DCO}}{N} \propto K_P K_{TDC} \omega_{REF} \quad (5.2)$$

$$\zeta = \frac{K_P}{2} \cdot \sqrt{\frac{2\pi K_{TDC} K_{DCO}}{K_I N \omega_{REF}}} \propto \frac{K_P}{2} \cdot \sqrt{\frac{2\pi K_{TDC}}{K_I}} \quad (5.3)$$

where  $K_P$  and  $K_I$  are the fixed proportional and integral gains of the DLF, respectively and  $K_{TDC}$  and  $K_{DCO}$  are the TDC and DCO gains, in units of bits/rad and rad/s/bit, respectively. These expressions imply that when  $K_{TDC}$  is constant and  $K_{DCO}$  is proportional to  $\omega_{OUT} = N \cdot \omega_{REF}$ ,  $\omega_{BW}$  will be a constant fraction of  $\omega_{REF}$  and  $\zeta$  will be constant. Therefore, at a given reference frequency  $\omega_{REF}$ , which is typically well-

controlled, the digital PLL with a constant-gain TDC and a constant-relative-gain DCO will have a well-predicted loop BW insensitive to PVT variations.

## **5.4 Circuit Implementation**

#### **5.4.1 Capacitor-Tuned LC-DCO**

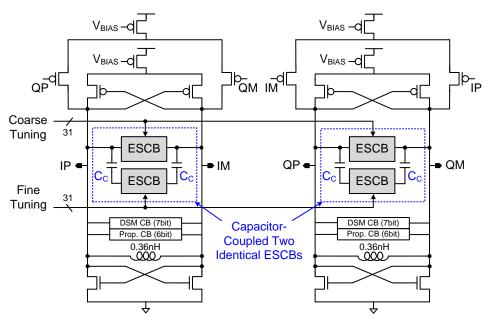

Fig. 5.4. The proposed constant relative-gain quadrature LC-DCO implemented with the capacitor-coupled two identical ESCBs.

Fig. 5.4 shows the overall schematic of the proposed constant relative-gain LC-DCO employing exponentially-sized capacitor banks (ESCBs) for frequency tuning [27]. The LC-DCO is composed of two coupled LC oscillator cores for quadrature phase generation and each core is composed of a 31-bit-thermometer-coded coarse

ESCB and a 31-bit-thermometer-coded fine ESCB for wide-range frequency tuning, a 6-bit-binary-coded capacitor bank (CB) for direct proportional control [21], and a 7-bit-binary-coded CB for a delta-sigma modulator (DSM) dithering. The fine ESCB is identical to the coarse ESCB except being coupled to the nodes IP(QP) and IM(QM) via series capacitors *Cc*. Adding this series capacitors *Cc* can improve the frequency resolution of the DCO without degrading the tuning range or phase noise [22].

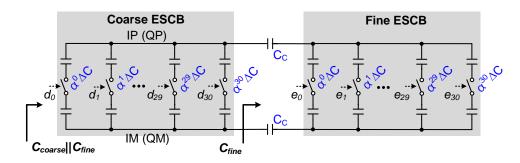

Fig. 5.5. Detailed schematic of the coarse and fine ESCBs.

As shown in Fig. 5.5, each ESCB consists of exponentially-sized switched-capacitors with a constant radix of  $\alpha$ , so that the DCO frequency can change by a constant fraction of the current frequency set by  $\alpha$ . Each CB is made of a set of parallel NMOS varactors and switches each of which shorts the internal node either to power or to ground. The switches are controlled by a 31-bit thermometer code  $d_0 \sim d_{30}$  (for coarse ESCB) or  $e_0 \sim e_{30}$  (for fine ESCB), which are generated from two binary-to-thermometer (B2T) encoders.

The coarse capacitance  $C_{coarse}$  and fine capacitance  $C_{fine}$  of the capacitor-coupled two identical ESCBs assuming  $C_0 \gg \Delta C$  can be calculated as:

$$C_{coarse} = C_0 + T_C \cdot \Delta C \quad (T_C = d_o + d_1 \cdot \alpha^1 + \dots + d_{30} \cdot \alpha^{30}) \quad (5.4)$$

$$C_{fine} = \frac{(C_0 + T_F \cdot \Delta C) \cdot \frac{C_C}{2}}{(C_0 + T_F \cdot \Delta C) + \frac{C_C}{2}} = \frac{(C_o + T_F \cdot \Delta C) \cdot \frac{C_C}{2C_0}}{1 + \frac{T_F \Delta C}{C_0} + \frac{C_C}{2C_0}} \approx \frac{C_C}{2} + T_F \cdot \Delta C \cdot \frac{C_C}{2C_0}$$

$$(T_F = e_o + e_1 \cdot \alpha^1 + \dots + e_{30} \cdot \alpha^{30}) \quad (5.5)$$

Where  $\Delta C$  is the unit capacitance and  $C_0$  is the total fixed capacitance on the nodes IP(QP) and IM(QM).

Using the total capacitance  $C_{total} = C_{coarse} + C_{fine}$ , the constant relative gain k can be expressed as:

$$k = \frac{\omega_{n+1}}{\omega_n} = \sqrt{\frac{\left(C_0 + \frac{1 - \alpha^{N_C}}{1 - \alpha} \cdot \Delta C\right) + \left(\frac{C_C}{2} + \frac{1 - \alpha^{N_F}}{1 - \alpha} \cdot \Delta C \cdot \frac{C_C}{2C_o}\right)}{\left(C_0 + \frac{1 - \alpha^{N_C}}{1 - \alpha} \cdot \Delta C\right) + \left(\frac{C_C}{2} + \frac{1 - \alpha^{N_F - 1}}{1 - \alpha} \cdot \Delta C \cdot \frac{C_C}{2C_o}\right)}} \approx 1 + \frac{\Delta C \cdot C_C}{2C_0^2}$$

(4)

where n is the 10-bit binary-coded index of the frequency control code  $(n=2^5N_C+N_F)$ . And,  $N_C$  (coarse) and  $N_F$  (fine) are upper and lower 5-bits, respectively. In the prototype design, the value of  $\alpha$  is set to be 0.9958, which realizes a constant relative gain k of 1.00011 (=0.011%/step). At 8.4-GHz, it corresponds to a frequency resolution of 924-kHz. The capacitance Cc is sized to  $C_0/16$  for seamless hand-over between the coarse and fine ESCB ranges. However, since this capacitance was implemented using metal-to-metal capacitors for their linearity instead of the MOS varactors used in the ESCBs, possible gain mismatch may exist due to their variations.

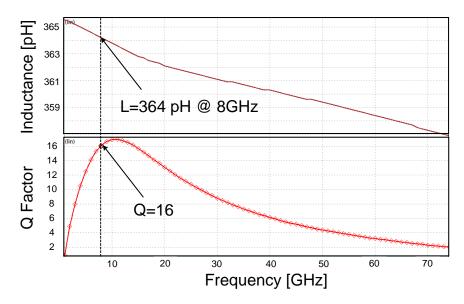

Each oscillator core uses a 364-pH symmetric-square planar inductor with a 25 $\mu$ m-wide, 2.225 $\mu$ m-thick top-metal layer, achieving a quality factor of 16 at 8-GHz with the total series resistance less than 1 $\Omega$  as shown in Fig. 5.6.

Fig. 5.6. Inductance and quality factor of the designed inductor.

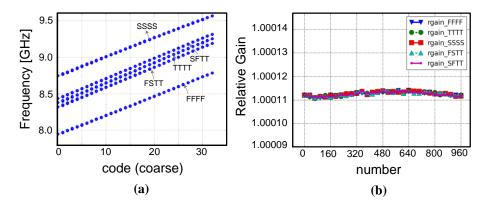

As shown in Fig. 5.7, the proposed capacitor-tuned LC-DCO was designed to have a 10-bit resolution with a constant relative gain of 1.00011 (=0.011%/step) over an 8.4~9.3-GHz range, while dissipating 9.1-mW at the frequency of 9.3-GHz.

Fig. 5.7. Simulation results: (a) frequency tuning range and (b) relative gain at hand-over between the coarse and fine ESCB ranges (32-points).

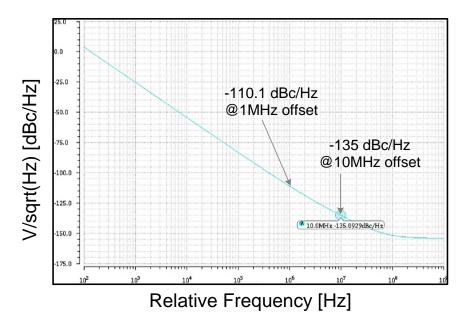

In addition, the simulated phase noise of the LC- DCO at 8.9 GHz was -110.1-dBc/Hz at 1-MHz offset and -135-dBc/Hz at 10-MHz offset as shown in Fig. 5.8.

Fig. 5.8. Simulated phase noise at 8.9GHz.

#### 5.4.2 Transformer-Tuned LC-DCO

As explained in Section 4, uncertainties in the DCO gain can make the precise control of the PLL's bandwidth and damping factor difficult. Sparing margins to accommodate these uncertainties may sacrifice the key performance metrics such as phase noise and power dissipation. To alleviate such a DCO gain variation, the LC-DCO that has constant relative-gain is proposed. The constant relative-gain is secured by the ratiometric circuit design, i.e., frequency is controlled by the ratio between two currents.

Fig. 5.9 Transformer-tuned (magnetically-tuned) LC-DCO.

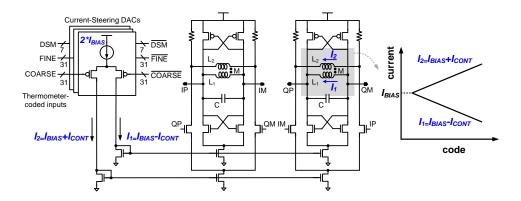

Fig. 5.9 shows the schematic of the proposed transformer-based LC-DCO that realizes a predictable gain without the aid of an explicit calibration. The principle of the transformer-based frequency tuning is explained in [26]. The effective inductance of the primary inductor  $L_1$  is tuned by adjusting the current flowing in the secondary inductor  $L_2$ . The two coupled LC oscillator cores enforce the necessary quadrature-phase relationship between the currents in the primary and secondary inductors,  $I_1$  and  $I_2$ , respectively. The oscillation frequency  $\omega_{OSC}$  can be expressed as:

$$\omega_{OSC} = \frac{\omega_0}{2Q} \cdot \frac{M}{L_1} \cdot \frac{I_2}{I_1} + \sqrt{\left(\frac{\omega_0}{2Q} \cdot \frac{M}{L_1} \cdot \frac{I_2}{I_1}\right)^2 + \omega_0^2} \quad (5.16)$$

where  $\omega_0$  is the LC tank's resonant frequency without the secondary inductor, Q is the quality factor, and M is the mutual-inductance of the transformer. Equation (16) shows that the oscillation frequency varies with the ratio  $I_2/I_1$ , which is controlled by a current-steering DAC.

The ratio  $I_2/I_1$  using n-bit binary control can be expressed by:

$$\left(\frac{I_2}{I_1}\right)_n = \frac{I_{BIAS} + I_{CONT}}{I_{BIAS} - I_{CONT}} = \frac{1 + \frac{n\Delta I}{I_{BIAS}}}{1 - \frac{n\Delta I}{I_{BIAS}}} \approx e^{\frac{2\Delta I}{I_{BIAS}} \cdot n}$$

$$x = \frac{I_{CONT}}{I_{BIAS}} = \frac{n\Delta I}{I_{BIAS}}$$

(0 < x < 1) (5.17)

Where  $I_{BIAS}$  and  $I_{CONT}$  are the fixed bias current and varying current by digital code, respectively.

The current-steering DAC adjusts the two currents  $I_1$  and  $I_2$  in a complementary fashion, realizing a pseudo-exponential D-to-f characteristic and a PVT-invariant relative gain of the DCO. When  $I_1$  varies as  $I_{BIAS}$ ·(1-x) and  $I_2$  varies as  $I_{BIAS}$ ·(1+x) where x is a tuning parameter, the ratio  $I_2/I_1$  varies exponentially with x since  $exp(2x) \cong (1+x)/(1-x)$  and so does the oscillation frequency according to Eq. (5.16). Therefore, for a unit change in the input code, the DCO frequency will change by a constant fraction of the current frequency, i.e., constant relative-gain of  $exp(2\Delta I/I_{BIAS})$ . The LC-DCO was designed to have a 10-bit resolution with a constant relative gain of 0.0064%/step over an 8.9~9.5-GHz range, while dissipating 51-mW at the frequency of 9.2-GHz. The simulated phase noise of the LC-DCO at 9.2 GHz was -91.2-dBc/Hz at 1-MHz offset and -120.9-dBc/Hz at 10-MHz offset.

However, the measured gain was 0.0047%/step due to the mis-estimation of the transformer's self- and mutual-inductances in presence of the routing wires.

Unfortunately, as discussed in Section 5, the designed DCO exhibits rather high phase noise and power dissipation compared to the state-of-the-art LC oscillators reported in literature and multiple reasons can be attributed to this. First, a half of the power dissipation is wasted on the second oscillator core generating the quadra-

ture-phase clocks required for the transformer-based tuning. While this was to generate precise quadrature clocks against PVT variation, it does incur more power than the alternative solution of using inverter-based 90-degree phase shifters [19]. Second, the frequency tuning was done by decreasing the main current  $I_1$  while increasing the auxiliary current  $I_2$ , degrading the phase noise as the ratio  $I_2/I_1$  increases. Furthermore, to ensure the proper start-up of the oscillator even with the lowest  $I_1$ , the overall current level had to be increased and energy-storing transistors had to be oversized, degrading both the power and phase noise. Lastly, the load resistors added in the outer loop to down-shift the voltage levels degraded the quality factor of the LC tank and added thermal noise while satisfying the voltage-rating requirement on the transistors.

In [20] with separate prototype, the transformer-tuning LC-DCO had a tuning range of 8.9~9.5-GHz and its phase noise was less than -120-dBc/Hz at a 10-MHz offset. The PLL with this LC-DCO consumed 63.9-mW in total and its majority, 51mW, was dissipated in the DCO. In addition, the PLL had -92.8-dBc/Hz phase noise at 1-MHz offset and -114-dBc/Hz phase noise at 10-MHz offset at 9.2-GHz.

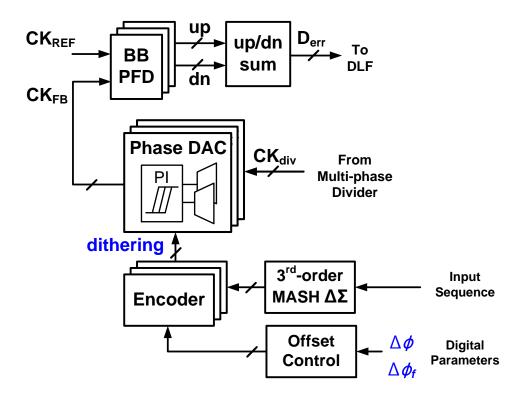

#### 5.4.3 Oversampling-Based Constant-Gain TDC

Fig. 5.10. The block diagram of the constant-gain TDC.

Fig. 5.10 shows the block diagram of the proposed TDC. A constant TDC gain which is independent of the PVT, input jitter, and frequency conditions is achieved by using three oversampling BB-PFDs triggered by individually dithered clocks using a set of phase digital-to-analog converters (DACs) and a 1-1-1 third-order multistage noise-shaping (MASH) DSM. The DSM generates a random dithering sequence whose noise power is shaped into a high frequency range by using the mini-

mum fractional value possible as the input [23]. Each phase DAC then converts the sequence into a dithering clock with a unit phase step size of  $\Delta\phi_f$  and a phase offset of  $\Delta\phi$ , 0, or  $\Delta\phi$ .

Fig. 5.11. Linearization of the TDC with the addition of random dither.

The TDC linearization principle is illustrated in Fig. 5.11. With a sufficiently large dither, the overall TDC characteristic becomes a straight line whose slope is determined largely by the phase spacing between the BB- PFDs. Since this phase spacing is set as a fixed fraction of the clock period by the use of phase-interpolating DACs, the slope, corresponding to the effective TDC gain, will remain unchanged despite the change in the PVT, input jitter, and frequency conditions.

Both the dither jitter step  $(\Delta \phi_f)$  and phase offset  $(\Delta \phi)$  are digitally programmable in units of PI resolution steps via an external I<sup>2</sup>C interface. When the up/down counter tallies the BB-PFD outputs (up and dn) over multiple input cycles, the difference in their counts indicates the digitized phase error  $(D_{err})$ .

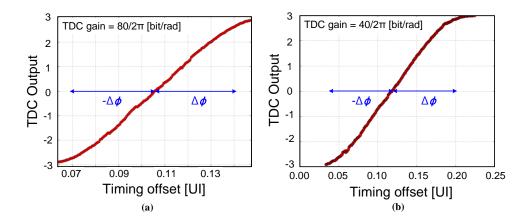

Fig. 5.12. Simulated effective TDC gain: (a) when  $\Delta\phi$ =0.037 UI and (b) when  $\Delta\phi$ =0.083 UI.

Fig. 5.12 plots the simulated TDC gain when the phase offset is set by  $\Delta\phi$ =0.037 UI and  $\Delta\phi$ =0.083 UI at 280 MHz frequency. The input clock has 1-ps<sub>rms</sub> jitter. Thus, simulated TDC gains are  $80/2\pi$ =12.7 [bit/rad] and  $40/2\pi$ =6.36 [bit/rad], respectively. From these, ), the effective TDC gain is determined mainly by  $\Delta\phi$ , which can stay constant regardless of the PVT and input jitter conditions. Even if the operating frequency changes, the TDC gain in units of bit/UI stays constant.

#### **5.4.4 Phase Digital-to-Analog Converter**

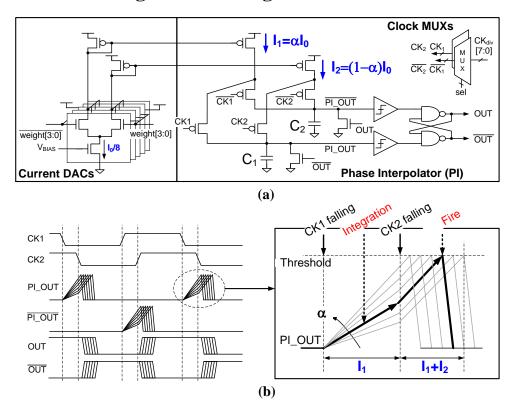

Fig. 5.13. (a) Circuit implementation of phase-domain DAC. (b) Operating waveform of phase interpolator (PI).

Fig. 5.13(a) shows the phase DAC circuit which is a set of two multiplexers followed by a digitally controlled phase interpolator (PI). Fig. 5.13(b) illustrates the operation of the PI, of which main advantage over the other published ones is that there is no contention between the two driving stages, saving power dissipation due to crowbar currents. The basic circuit topology is similar to the one in [25], except that two complementary stages work in an alternating fashion to interpolate both the

rising and falling edges of the input clocks. In each stage, two switched current sources each biased at  $I_1$  and  $I_2$  charge a shared capacitor when the respective input clocks (*CK1* and *CK2*) fall low. It then gives rise to a ramp signal on the node  $PI\_OUT$ , which toggles the output clock OUT when  $PI\_OUT$  crosses the threshold of a Schmitt-trigger type comparator. It can be shown that the interpolation weight  $\alpha$  between the two input phases can be adjusted by controlling  $I_1$  and  $I_2$  as  $\alpha \cdot I_0$  and (1- $\alpha$ )· $I_0$ , respectively, using a 4-bit binary-coded current-steering DAC. The implemented phase DAC dissipates only 102  $\mu$ W, whose output spans the entire 360° range with a resolution of 2.8125° (128-steps).

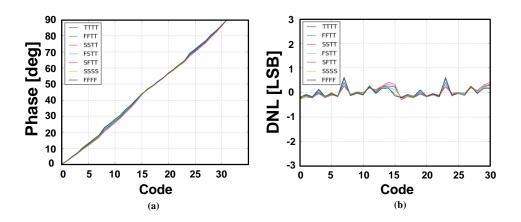

Fig. 5.14(a) shows the simulated transfer characteristic of the phase DAC with input code from 0 to 31. Fig. 5.14(b) shows that the phase DAC was designed to have a DNL less than 0.5 LSB.

Fig. 5.14. Simulated results: (a) transfer characteristic of the phase DAC and (b) differential nonlinearity (DNL).

#### **5.4.5 Digital Loop Filter**

Thanks to the constant-relative-gain DCO and constant-gain TDC, the digital loop filter (DLF) used in the proposed PVT-insensitive loop BW PLL is a simple one that has proportional and integral paths. The proportional path updates the DCO input code by a factor of  $K_P$ , so that corrects the phase error. The integral path corrects the frequency error by updating DCO input code with the amount of time integral of the phase error, multiplied by  $K_I$ .

In order to realize the loop BW determined and scaled solely by the  $\omega_{REF}$ , the constant-relative-gain DCO changes its frequency by a constant fraction of the current operating frequency  $\omega_{OUT}$  in response to a unit step in its digital input. That is,  $(\Delta \omega_{OUT}/\omega_{OUT})/\Delta D_{in}$  is always constant. Therefore, the DLF only need to update the DCO input code proportional to the phase error in entire frequency range without explicit calibration.

Unlike the constant-relative-gain DCO, conventional linear D-to-f DCO as explained Section 4.1 changes its frequency by a constant quantity in response to a unit step in its digital input, i.e., constant gain (= $\Delta\omega_{OUT}/\Delta D_{in}$ ). So, ( $\Delta\omega_{OUT}/\omega_{OUT}$ )/ $\Delta D_{in}$  is decreased with respect to the increase of  $\omega_{OUT}$ . To scale the loop BW proportional to the  $\omega_{REF}$  in whole tuning range, explicit calibration is inevitable in the digital loop filter [3].

#### **5.4.6 Frequency Divider**

Fig. 5.15. (a) Feedback frequency divider with division ratio of 4 or 8. (b) 8-phase output divider.