#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

### Ph.D. DISSERTATION

# A STUDY ON LOW-PHASE-NOISE 77-GHZ CMOS TRANSMITTER FOR FMCW RADAR

저 위상잡음 77 GHz CMOS FMCW 레이더 송신기에 관한 연구

FEBRUARY 2017

# GRADUATE SCHOOL OF ELECTRICAL AND COMPUTER ENGINEERING SEOUL NATIONAL UNIVERSITY

JAEHOON SONG

# 공학박사 학위논문

# A STUDY ON LOW-PHASE-NOISE 77-GHZ CMOS TRANSMITTER FOR FMCW RADAR

저 위상잡음 77 GHz CMOS FMCW 레이더 송신기에 관한 연구

2017 년 2 월

서울대학교 대학원 전기·정보 공학부 송 재 훈

# A STUDY ON LOW-PHASE-NOISE 77-GHZ CMOS TRANSMITTER FOR FMCW RADAR

지도 교수 남 상 욱

이 논문을 공학박사 학위논문으로 제출함 2017 년 2 월

서울대학교 대학원 전기·정보 공학부 송 재 훈

송재훈의 공학박사 학위논문을 인준함 2017 년 2 월

| 위원 | <sup>ᆁ</sup> 장 _ | <u>서 광 석</u> | (인) |

|----|------------------|--------------|-----|

| 부위 | 원장 _             | 남 상 욱        | (인) |

| 위  | 원 _              | 정 덕 균        | (인) |

| 위  | 원 _              | 김 병 성        | (인) |

| 위  | 원 _              | 이 문 규        | (인) |

# **Abstract**

This thesis presents design methodology and experimental verification of a low-phase-noise 77-GHz CMOS FMCW (Frequency Modulated Continuous Wave) radar transmitter. It is quite difficult to design a low-phase-noise signal generator at millimeter-wave frequencies in CMOS because gain of CMOS transistors is extremely low at those frequencies. When using a frequency multiplier, it is relatively advantageous to design a low-phase-noise signal source because a VCO can be designed at lower frequency band where gain of active devices is high. When using multiple stage frequency multipliers to achieve low-phase-noise performance, the operating frequency range can be reduced and DC power consumption can be increased. Therefore, in this thesis, two methods for realizing 77-GHz CMOS low-phase-noise signal source have been proposed.

One method is to combine a ×6 frequency multiplier and a 12.8-GHz FMCW signal generator. In this case, a VCO, an injection-locked VCO buffer, a ×3 frequency multiplier (tripler), and a ×2 frequency multiplier (doubler) constituting the 77-GHz signal generator are designed as a four-stage coupled injection-locked oscillator (ILO) chain which is oscillated and injected into the output signal of the preceding stage. The VCO used in the 12.8-GHz PLL (phase locked loop) was designed using linearized transconductance (LiT: Linearized Transconductance) technology

to have low phase noise characteristics and was designed to be simpler than the existing LiT VCO using a 3:2 transformer. Since the PLL is designed as the integer-N type, an external frequency modulated triangular reference signal must be injected into the phase frequency detector (PFD) of the PLL to generate the FMCW signal. The fabricated transmitter chip supports FMCW output signals in the 76.81-77.95 GHz band when supplied with the external reference triangular signal from 50.00 to 50.75 MHz. The RF output power is about 8.9 dBm and consumes 116.7 mW of DC power. The measured phase noise is -91.16 dBc/Hz at the 1-MHz offset of the 76.81-GHz carrier frequency, which is the lowest phase noise characteristic of the previously announced 77-GHz CMOS transmitter and transceiver. A transmitter module for 77-GHz radar performance measurement was fabricated by combining the transmitter chip with the on-chip feeder that can solve the millimeter-wave packaging problem.

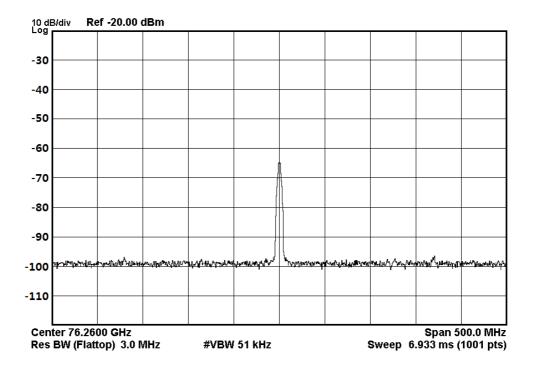

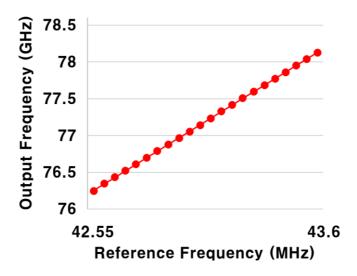

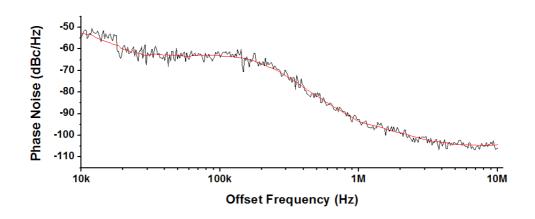

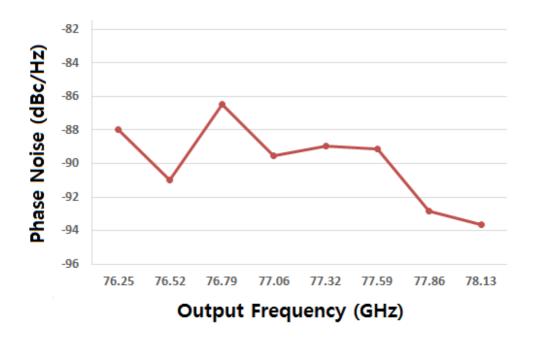

The other is a method of combining a ×28 frequency multiplier and a 2.75-GHz FMCW signal generator. As in the previous method, the VCO, a ×7 multiplier, and two ×2 multipliers constituting the 77-GHz signal generator are each designed as a 4-stage ILO chain. The VCO used in the 2.75-GHz PLL is designed as a class-C type that improves the startup problem to have low-phase-noise characteristics. As in the previous case, an integer-N type PLL is used. The fabricated transmitter chip supports FMCW output signals in the 76.26-78.23 GHz band when supplied with the

external reference triangular signal from 42.55 to 43.65 MHz. The

RF output power is about -18 dBm and consumes 195.4 mW of DC

power. The measured phase noise is -93.64 dBc/Hz at the 1-MHz

offset of the 78.13-GHz carrier frequency, which is even lower

phase noise characteristic than the ×6 frequency multiplier based

transmitter chip.

**Keyword**: 77-GHz, FMCW radar transmitter, frequency multiplier,

low-phase-noise VCO, PLL

**Student Number**: 2012-30212

iii

# Table of Contents

| Abstract                                               |

|--------------------------------------------------------|

| Table of Contentsiv                                    |

| List of Figuresvi                                      |

| List of Tablesx                                        |

|                                                        |

| Chapter 1. Introduction                                |

| 1.1 Types and Applications of Automotive Radars 2      |

| 1.1 Research Strategy                                  |

|                                                        |

| Chapter 2. Frequency and Architecture selection        |

| 2.1 LiT VCO                                            |

| 2.2 Class-C VCO                                        |

| 2.3 Injection-Locked Oscillator Chain                  |

| 2.4 Summary                                            |

|                                                        |

| Chapter 3. 77-GHz FMCW Radar Transmitter with 12.8-GHz |

| PLL and ×6 Frequency Multiplier30                      |

| 3.1 Proposed LiT VCO                                   |

| 3.2 ×6 Multiplier and Power Amplifier                  |

| 3.3 Measurement Results                                |

|--------------------------------------------------------|

| 3.3.1 LiT VCO Measurement Results                      |

| 3.3.2 77-GHz Transmitter (v1) Measurement Results 49   |

| 3.4 Summary                                            |

|                                                        |

| Chapter 4. 77-GHz FMCW Radar Transmitter with 2.75-GHz |

| PLL and ×28 Frequency Multiplier                       |

| 4.1 Proposed class-C VCO65                             |

| $4.2 \times 28$ Multiplier and Power Amplifier         |

| 4.3 Measurement Results                                |

| 4.3.1 Class-C VCO Measurement Results80                |

| 4.3.2 77-GHz Transmitter (v2) Measurement Results 83   |

| 4.4 Summary                                            |

|                                                        |

| Chapter 5. Conclusion                                  |

|                                                        |

| Bibliography94                                         |

| Abstract in Korean                                     |

# **List of Figures**

| Fig. 1. ADAS function                                          | 3     |

|----------------------------------------------------------------|-------|

| Fig. 2. General architecture of FMCW radar                     | 5     |

| Fig. 3. Time-frequency waveform of conventional FMCW radar.    | 5     |

| Fig. 4. Detecting target at a distance of R from the radar     | 8     |

| Fig. 5. Minimum SNR according to detection probability &       | false |

| alarm probability                                              | 8     |

| Fig. 6. A simplified Doppler shift radar system demonstrating  | ; the |

| effects of phase noise on the downconverted Doppler shift      | 9     |

| Fig. 7. Process technology trend.                              | .10   |

| Fig. 8. Gm versus voltage swing showing a typical oscillator c | urve  |

| and a preferred curve for improved phase noise                 | .14   |

| Fig. 9. Feedback concept for LiT using lower voltage swing or  | ı the |

| drain node                                                     | .15   |

| Fig. 10. LiT VCO: (a) full circuit and (b) half circuit        | .17   |

| Fig. 11. Schematic of the class-C LC-tank oscillator           | .19   |

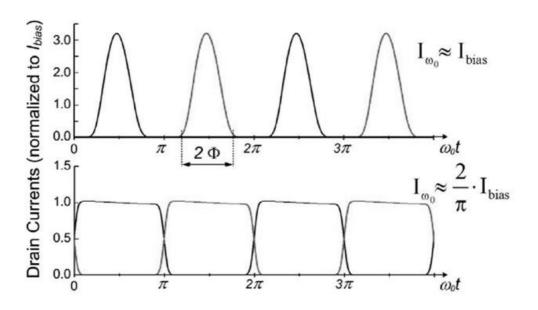

| Fig. 12. Drain current of the FETs for conventional LC-tank V  | ′COs  |

| and class-C VCOs.                                              | .20   |

| Fig. 13. MOS current waveforms and amplitude of the fundame    | ental |

| current harmonic in the class-C oscillator (top), differential | pair  |

| LC-tank oscillator (hottom)                                    | 21    |

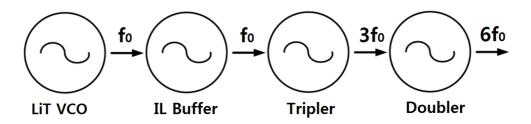

| Fig. 14. A four-stage injection locked oscillator chain structure of   |

|------------------------------------------------------------------------|

| the proposed 77-GHz signal generator with the ×6 frequency             |

| multiplier24                                                           |

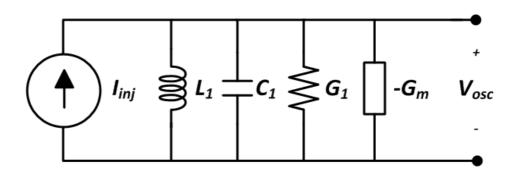

| Fig. 15. Simple equivalent circuit of injection-locked oscillator load |

|                                                                        |

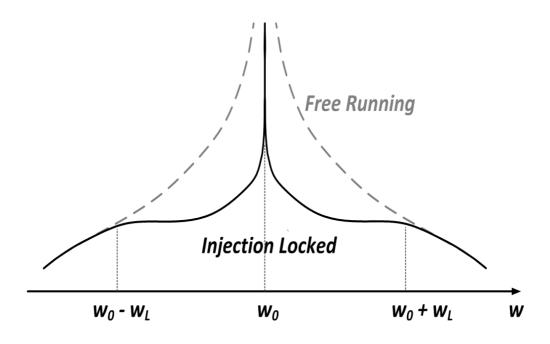

| Fig. 16. Phase noise reduction by injection-lock technique28           |

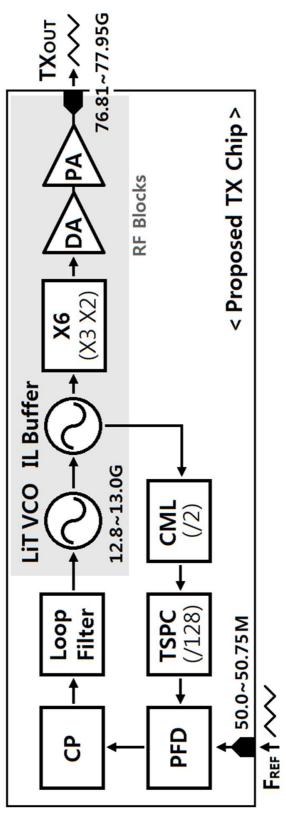

| Fig. 17. Block diagram of the proposed 77-GHz TX chip31                |

| Fig. 18. Schematic of the proposed improved LiT VCO33                  |

| Fig. 19. Designed 3:2 transformer for the proposed LiT VCO34           |

| Fig. 20. (a) Simulated waveforms of a 3:2 transformer based LiT        |

| VCO, (b) Those of a conventional LC VCO36                              |

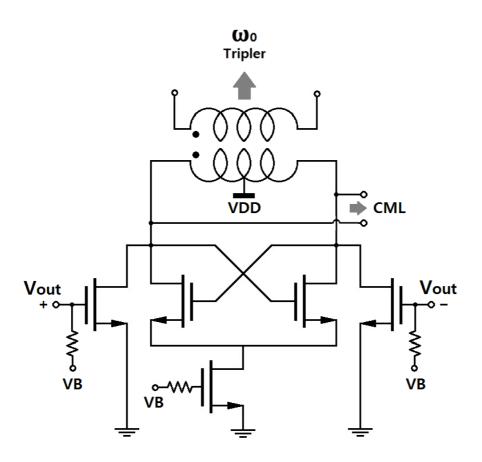

| Fig. 21. Schematic of the injection-locked buffer37                    |

| Fig. 22. Schematic of (a) the frequency tripler and (b) the            |

| frequency doubler                                                      |

| Fig. 23. Schematic of the power amplifier                              |

| Fig. 24. Total circuit schematic of RF blocks                          |

| Fig. 25. Chip micro-photograph of the proposed LiT VCO and IL          |

| buffer                                                                 |

| Fig. 26. Measured output frequency                                     |

| Fig. 27. Measured phase noise when carrier frequency is 13.2 GHz       |

| 47                                                                     |

| Fig. 28. A microphotograph of the transmitter chip50                   |

| Fig. 29. A PCB to measure fabricated transmitter chip51            |

|--------------------------------------------------------------------|

| Fig. 30. An experimental environment                               |

| Fig. 31. A measured frequency spectrum                             |

| Fig. 32. Measured phase-locked output frequency and power54        |

| Fig. 33. Measured phase-noise at 76.81-GHz carrier frequency55     |

| Fig. 34. Measured spread spectrum with 10-ms slow chirp            |

| reference signal                                                   |

| Fig. 35. FMCW profile and frequency error with 1-ms fast chirp     |

| reference signal                                                   |

| Fig. 36. Output spectrums of the harmonics in (a) 0-50 GHz, (b)    |

| 50–75 GHz57                                                        |

| Fig. 37. Block diagram of the proposed 77-GHz TX chip63            |

| Fig. 38. Schematic of (a) the proposed class-C VCO with an         |

| auxiliary class-B pair, (b) the adaptive bias circuit, and (c) the |

| output buffer66                                                    |

| Fig. 39. Adaptive bias voltage waveform of the proposed VCO67      |

| Fig. 40. Comparison of a class-C VCO startup by transient          |

| simulation69                                                       |

| Fig. 41. Comparison of simulated phase noise of each case71        |

| Fig. 42. Block diagram of the designed ×28 frequency multiplier.   |

|                                                                    |

|                                                                    |

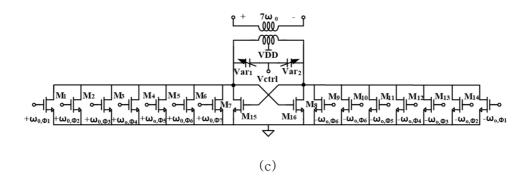

Fig. 43. (a) Block diagram of the 7-stage ring oscillator, (b)

| schematic of the ring cell, and (c) schematic of the adder and the |

|--------------------------------------------------------------------|

| oscillator (7f0)76                                                 |

| Fig. 44. Schematic of the two stage frequency doubler77            |

| Fig. 45. Schematic of the power amplifier                          |

| Fig. 46. Chip micro-photograph of the proposed class-C VCO80       |

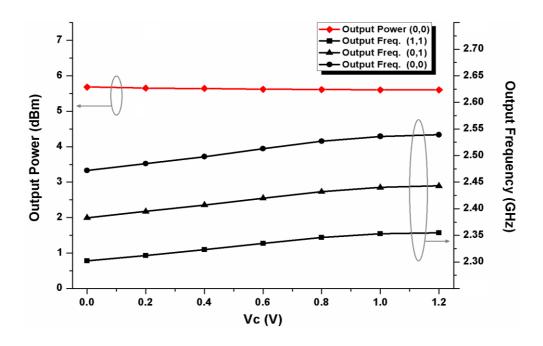

| Fig. 47. Measured output frequency and output power81              |

| Fig. 48. Measured output frequency and output power81              |

| Fig. 49. A microphotograph of the transmitter chip.aa84            |

| Fig. 50. Output frequency spectrum85                               |

| Fig. 51. Measured phase-locked output frequency86                  |

| Fig. 52. Measured phase noise                                      |

| Fig. 53. Phase noise vs. output frequency                          |

# **List of Tables**

| TABLE I. Radar classification according to detection distance3 |

|----------------------------------------------------------------|

| Table II. Performance of the proposed LiT VCO48                |

| TABLE. III. Comparison of RADAR Transmitters or Transceivers.  |

| 58                                                             |

| TABLE. IV. Comparison of Startup w/ & w/o the Self-Turn-Off    |

| Auxiliary Pair71                                               |

| TABLE. V. Comparison of published CMOS class-C VCO82           |

| TABLE. VI. Comparison of RADAR Transmitters or Transceivers.   |

| 89                                                             |

# **Chapter 1. Introduction**

In the past, radar systems, which were primarily used only for military, aircraft, and scientific navigation purposes, have recently begun to be installed in automobiles with the development of cheap and small radar systems. The automotive radar system is not only used for safety purposes such as collision avoidance and blind spot detection but also is becoming popular in terms of convenience such adaptive cruise control. Furthermore, it is becoming an indispensable element in the development of an "intelligent vehicle" capable of automatic driving in the future. Although laser radar for automobiles has been commercialized in the early 1980s, lasers are so sensitive to various weather conditions that millimeter-wave radars are now widely available. In chapter 1.1, types and applications of the automotive radar will be described briefly, and the concept of FMCW radar will be discussed in detail. And research strategies for developing low-phase-noise transmitter in CMOS have been discussed in chapter 1.2.

## 1.1. Types and Applications of Automotive Radars

RADAR is an abbreviation of RAdio Detection And Ranging. Its main function is detection of position or direction of object and measurement of distance or velocity. Among them, the distance and speed of the detected object are based on the measurement of the frequency shift due to the Doppler Effect, which includes the propagation speed of the radio wave, the propagation time, and the reflected or scattered radio wave respectively. The distance and velocity measurements of the radar using the above principle are based on (1) and (2).

$$R = \frac{c \cdot \Delta t}{2} \tag{1}$$

$$v = \frac{\lambda \cdot f_d}{\cos \theta} \tag{2}$$

In the above equation (1), c is the propagation speed in free space, and  $\Delta t$  is the time taken for the emitted radio wave to be reflected by the measured object and returned to the radar. In (2),  $f_d$  is the Doppler frequency shift,  $\lambda$  is the wavelength of the radiated wave, and  $\theta$  is the angle between the radar and the measured object, which is the angle between the measurement direction of the radar and the moving direction of the measured object.  $f_d$  becomes larger when a higher frequency is used than when a lower frequency is used for measuring the velocity of a subject moving at the same speed. This means that it is easier to extract the Doppler frequency

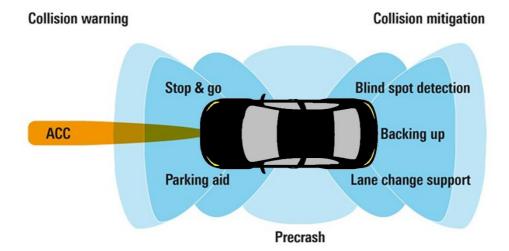

Fig. 1. ADAS function.

TABLE I. Radar classification according to detection distance

| Radars | Freq.<br>(GHz) | Modulation      | Angle<br>(Deg) | Distance<br>(m) | Resolution<br>(m) | Applications                                                       |

|--------|----------------|-----------------|----------------|-----------------|-------------------|--------------------------------------------------------------------|

| LRR    | 77             | FMCW            | 15             | 150~            | 0.5               | ACC                                                                |

| MRR    | 77 /<br>77-81  | FMCW /<br>Pulse | 40             | ~100            | 0.5               | Stop&go,<br>Cross traffic<br>alert,<br>Lane change                 |

| SRR    | 77-81          | Pulse           | 80             | ~30             | 0.1               | Collision<br>avoidance,<br>Blind spot<br>detection,<br>Parking aid |

shift by using a relatively high frequency in the measurement of the speed. Therefore, automotive radars are used at frequencies higher than those used by other conventional electronic products such as 24, 77, and 79 GHz. In Europe, which is leading the automobile parts industry, the 77-GHz is mainly used as a medium-and long-range detection radar for 100 ~ 250m and 79-GHz is used as a short-range collision prevention radar for 10 ~ 20m.

Fig. 1. Shows various ADAS (Advanced Driver Assistance Systems) functions. The functions of ADAS include ACC (Adaptive Cruise Control), Stop & Go, parking aid, blind spot detection, backing up, lane change detection, and collision warning. Vehicle radars can be classified as LRR (Long Range Radar), MRR (Medium Range Radar), or SRR (Short Range Radar) depending on the detection range [Table. I]. The LRR detects long distances of more than 150m in the 77–GHz band and is mainly used for ACC. The MRR detects distances of several tens of meters and uses 77–GHz FMCW radar or 77~81–GHz pulse radar, mainly used for stop & go, cross traffic alert, and lane change support. The SRR detects short distances of less than 30m in the 77~81–GHz band and is used for collision avoidance, blind spot detection, and parking aid.

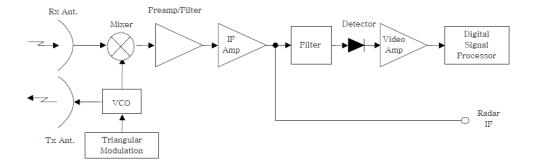

The 77-GHz FMCW radar used mainly for LRR or MRR is as follows. The basic radar configuration is shown in Fig. 2 [1]. An FMCW radar literally means a radar in which frequency-modulated signals are continuously transmitted. A typical signal waveform is shown in Fig. 3 [2]. The solid line indicates the transmission signal

Fig. 2. General architecture of FMCW radar.

Fig. 3. Time-frequency waveform of conventional FMCW radar.

of the radar, and the dotted line indicates the reception signal in which the transmission signal is reflected or scattered back to the object to be measured. Distance and velocity measurements can be obtained using the delay time ( $\Delta$ t) and the Doppler frequency shift ( $f_D$ ) of the received signal.

$$R = \frac{f_D \cdot c}{4f_m \Delta F} \tag{3}$$

$$v = \frac{\left(f_D - \delta f_u\right)c}{2f_0} \tag{4}$$

$\Delta F$  is the maximum frequency deviation,  $f_0$  is the center frequency, and  $f_m$  is the modulation frequency.

## 1.2. Research Strategy

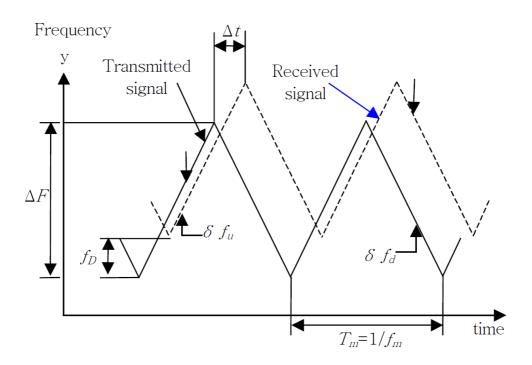

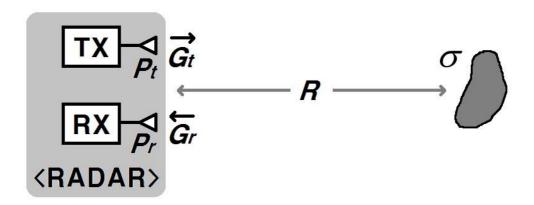

For the development of FMCW radar integrated circuit in CMOS for vehicles, it is necessary to establish the direction and strategy of this research. First, to determine the radar performance specification, the relationship between radar detection distance and radar SNR should be clarified. In the situation shown in Fig. 4, the radar equation is widely known as follows [3].

$$P_r = \frac{P_t G_t G_r \lambda^2 \sigma}{(4\pi)^3 R^4} \tag{5}$$

$P_t$  is transmit power (W),  $P_r$  is received power (W),  $G_t$  is transmit antenna gain,  $G_r$  is receive antenna gain,  $\sigma$  is radar cross section (RCS, m<sup>2</sup>), and R is distance to target. From (5), the relationship between the maximum detection distance (R<sub>max</sub>) and the minimum detectable SNR (S/N<sub>min</sub>) can be derived as follows.

$$R_{\text{max}}^{4} = \frac{P_{t}G_{t}G_{r}\lambda^{2}\sigma}{\left(4\pi\right)^{3}kT_{0}BF_{n}\left(S/N\right)_{\text{min}}}$$

(6)

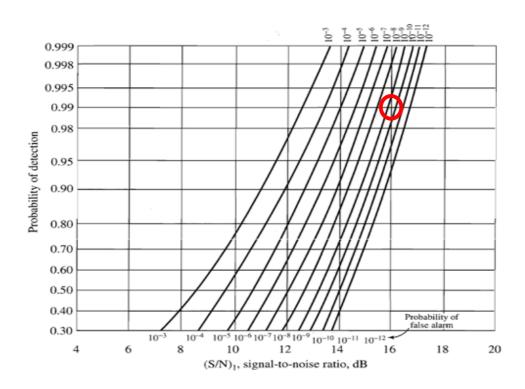

When the minimum SNR is known as shown in equation (6), the maximum detection distance can be calculated. The minimum SNR is determined from the false alarm probability and the detection probability [4]. The graph of Fig. 5 shows the false alarm probability when the x-axis is the SNR and the y-axis is the detection probability. Generally, the SNR at the detection probability 99% and the false alarm probability  $10^{-10}$  is determined as the minimum SNR, which is about 16 dB. Since the radar SNR

Fig. 4. Detecting target at a distance of R from the radar.

Fig. 5. Minimum SNR according to detection probability & false alarm probability.

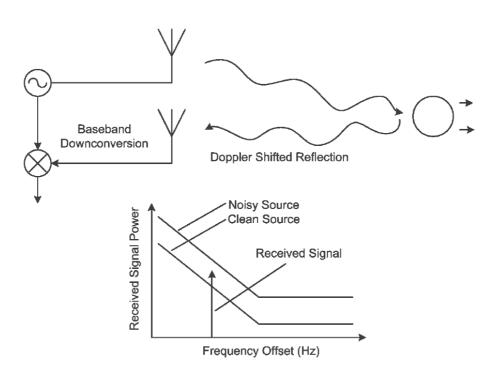

determines the maximum detection distance of the radar, it is a measure of the sensitivity of the radar. One of the factors that greatly affect the SNR is the phase noise of the signal source. The phase noise of signal source directly determines the radar sensitivity as shown in Fig. 6. The reflected signal will be extremely low power and can be overshadowed by an oscillator with too much noise [5]. Therefore, designing a low-phase-noise FMCW radar is one of the most important ways to increase the

Fig. 6. A simplified Doppler shift radar system demonstrating the effects of phase noise on the downconverted Doppler shift.

maximum detection distance of a radar.

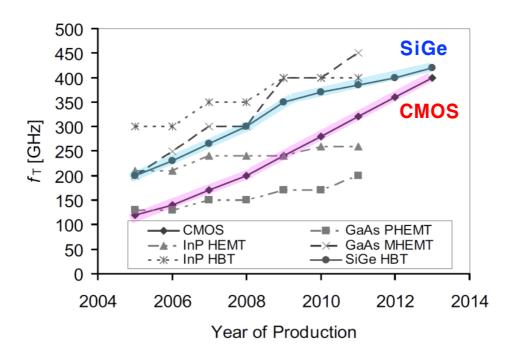

Fig. 7 shows process technology trend. In millimeter—wave frequencies, SiGe technologies have been widely used from the past due to high cut—off frequency and breakdown voltage [6], [7]. With the recent performance development of CMOS devices, CMOS can be applied to mm—wave radar systems [8]—[10]. Although CMOS radar systems have some advantages, such as low cost and high integration, the phase—noise performance should be improved further in order to compete with SiGe radar systems. Thus,

Fig. 7. Process technology trend.

achieving a low-phase-noise signal generator in CMOS has been a significant issue. Several approaches to designing a low-phasenoise 77-GHz FMCW signal generator are employed in this thesis. The first approach is to use a frequency multiplier. A VCO suffers from high phase noise due to poor transistor gain as well as the low quality factor of varactors at mm-wave frequencies. Therefore, despite consuming more DC power, combining a lower frequency VCO and a frequency multiplier can be a more appropriate solution than direct mm-wave oscillation for the mm-wave low-phasenoise performance [11]. Secondly, the proposed 77-GHz signal generator is designed with an injection-locked (IL) oscillator (ILO) chain, which is a powerful tool to realize low-phase-noise oscillators with good harmonic suppression at mm-wave frequencies [12]. Since the phase noise of the ILO chain is determined by the injected signal purity, the low frequency VCO should be designed to have low phase noise characteristics using the appropriate technique, which is the third approach. In this thesis, two versions of the 77-GHz signal source were presented, each of which was implemented using a  $\times 6$  frequency multiplier and a  $\times 28$ multiplier. Since it is important to design a VCO with low noise characteristics with the appropriate techniques at the frequency before being multiplied. A linearized transconductance (LiT) VCO at 12.8 GHz and a class-C VCO at 2.75 GHz were designed and improved with circuit ideas in this research.

# **Chapter 2. Frequency and Architecture Selection**

Before designing a 77-GHz FMCW radar transmitter chip with a frequency multiplier, the most important thing to consider is determining the architecture and the frequency of the transmitter. When the 77-GHz signal generator including the VCO, the buffer and the frequency multiplier is designed as an ILO chain as in the previous study, the final output phase noise characteristics is determined by the phase noise characteristics of the first stage oscillator of the ILO chain. Therefore, it is necessary to set the frequency of the first stage oscillator and the multiplication factor (N) of the frequency multiplier, which are advantageous for low phase noise characteristics. Considering the system implementation issues such as the frequency locking ranges and DC power consumption of cascaded frequency multipliers, the appropriate number of frequency multiplier stages should be determined. In this research, thus, a ×6 frequency multiplier, which is a combination of  $\times 3$  multipliers and  $\times 2$  multipliers, and a  $\times 28$  multiplier that combines ×7 multipliers and two-stage ×2 multipliers have been developed in our group. A low-phase-noise 77-GHz signal generator should be designed by combining these two multipliers with a low-phase noise VCO at each pre-multiplication frequency.

In the relatively high 12.8-GHz frequency band, it is difficult to apply the class-C technique, known as providing the lowest phase

noise performance, because of the parasitic components, so the LiT VCO, suitable for low phase noise characteristics in that band, will be explained in chapter 2.1. In chapter 2.2, the class—C VCO will be described in detail as a suitable scheme for low—phase—noise VCO design in the 2.75—GHz band. In chapter 2.3, we will briefly explain what the ILO chain is and then use it to show the benefits of phase—noise characteristics when designing a 77—GHz signal generator. Finally, a summary will be covered in Chapter 2.4.

### **2.1. LiT VCO**

It is widely known that phase noise in CMOS LC VCOs is fundamentally limited by the oscillation amplitude and the inherent device noise. A new approach based on transconductance linearization of the active devices, so called LiT (Linearized Transconductance) VCO, that increases the signal swing while reducing the active device noise contribution in LC VCOs in year

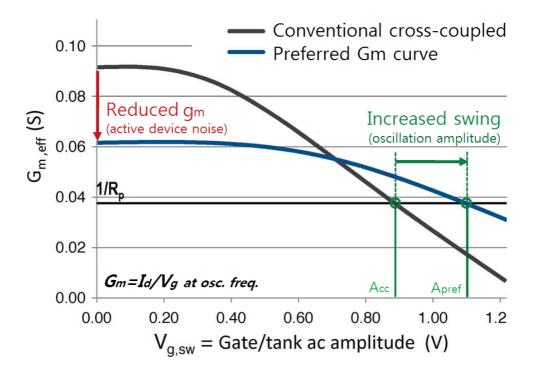

Fig. 8. G<sub>m</sub> versus voltage swing showing a typical oscillator curve and a preferred curve for improved phase noise.

2013 [13]. The oscillation amplitude is usually limited by the non–linearity of the large signal transconductance  $(G_m)$ . The effective transconductance  $(G_{m,eff})$  versus gate ac voltage swing showing a typical oscillator curve and a preferred curve for improved phase noise is presented in Fig. 8. From these curves, two important observations can be seen. The first one is about the oscillation

Fig. 9. Feedback concept for LiT using lower voltage swing on the drain node.

amplitude. As shown in the figure, the  $G_{m,eff}$  drops with increasing oscillation amplitude. The equilibrium amplitude  $A_{cc}$  is reached when  $G_m R_p = 1$ . The main source of nonlinearity is the transistor entering the triode region. The second one is the active device noise. Fig. 8 also shows the small-signal transconductance  $(g_m)$  corresponding to  $G_m$  for an infinitesimally small amplitude of oscillation. Note that this  $g_m$  determines the active device noise power at the oscillation zero crossings (when the oscillator's phase noise sensitivity is at its highest). As a result, with other factors remaining constant, the device  $g_m$  is a significant determinant of the VCO phase-noise performance. From these two observations, a more linear  $G_m$  curve (blue line in Fig. 8) realizes larger oscillation amplitude and lower active device noise, thereby improving SNR. Consequently, the phase noise characteristic of the VCO can be improved [13].

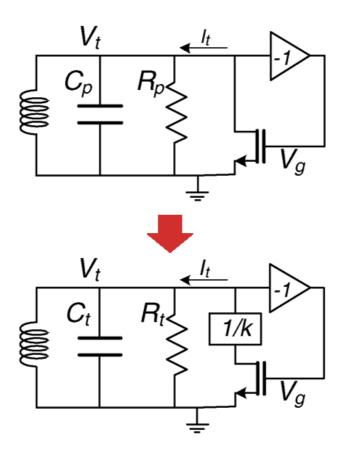

The conceptual feedback scheme in Fig. 9 can achieve the desired linearization because the drain node in the MOSFET is mainly responsible for large signal nonlinear device  $G_m$ . A portion of the tank/gate amplitude is fed to the drain, reducing swing at the drain. The result is a reduction in triode behavior that linearizes the  $G_m$  curve. This feedback scheme can be implemented using a capacitive divider as shown in Fig. 10 (a).

This LiT VCO solves two problems that worsen phase noise and shows improved phase noise performance. However, since the LC tank is connected to the gate node, a large-sized choke inductor is required at the drain node for VDD bias. Relatively complicated

Fig. 10. LiT VCO: (a) full circuit and (b) half circuit

layout are also required because the feedback is formed by a complex capacitor divider network. Thus, an improved LiT VCO for solving these problems of existing LiT VCO has been proposed in this paper, and details can be found in chapter 3.1.

# 2.2. Class-C VCO

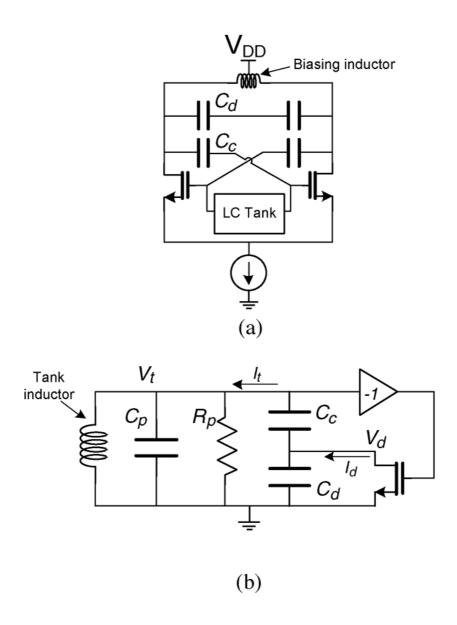

Since the publication of the first class—C VCO paper in 2008, numerous class—C VCO papers have been published because they have much better phase noise performance than conventional VCOs. Compared with an LC cross—coupled VCO, the class—C VCO provides better phase noise performance due to its low gate—bias

Fig. 11. Schematic of the class-C LC-tank oscillator.

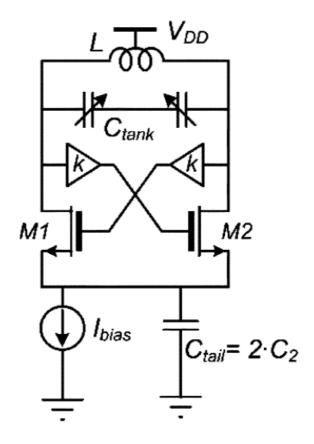

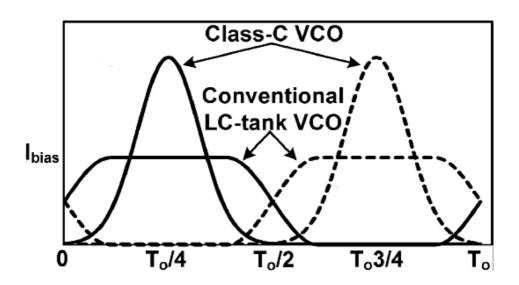

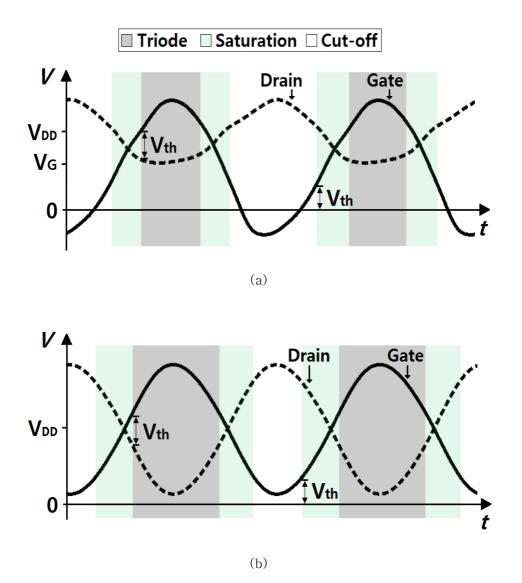

voltage, which can be explained by impulse sensitivity function [14]. A schematic of the class-C LC-tank oscillator is shown in Fig. 11 [15]. For a class-C VCO (Fig. 11), the drain current of the switching transistors (M1/M2) is a pulse wave instead of a near rectangular wave in a conventional LC-tank VCO, as in Fig. 12. The class-C operation generates impulse-like fundamental drain current with much higher efficiency, resulting in much higher oscillation voltage amplitudes versus a given current consumption. Fig. 13 shows MOS current waveforms and amplitude of the

Fig. 12. Drain current of the FETs for conventional LC-tank VCOs and class-C VCOs.

fundamental current harmonic in the class-C oscillator (top), differential pair LC-tank oscillator (bottom). In a typical LC VCO, the transistor has a conduction angle of half of the oscillation period, and the drain current at this time has a square-like waveform with 50% duty. In the case of a class-C VCO, however, the transistor has a much smaller conduction angle than half the oscillation period due to the low gate bias voltage. The drain current has an impulse-

Fig. 13. MOS current waveforms and amplitude of the fundamental current harmonic in the class-C oscillator (top), differential pair LC-tank oscillator (bottom).

like waveform because the transistor is turned on only for a short time. As demonstrated in [16], ideal Class-C operation results in a 36% lower bias current, compared to the conventionally used Class-B oscillator, for the same oscillation amplitude and phase noise. This is because the conversion of bias current into fundamental current harmonic is more efficient in Class-C (with an ideal conversion factor  $\alpha_{\rm C}$  equal to 2) than in Class-B (ideal conversion factor  $\alpha_{\rm B} = 4/\pi$ ). Therefore, the theoretical phase noise improvement for the same current consumption, compared to the standard differential-pair LC-tank oscillator, is 3.9 dB.

Although the class-C VCO has an advantage of providing a very good phase noise performance, it is not suitable for a relatively high frequency application because it is difficult to realize a sharp impulse-like drain current waveform due to the parasitic capacitance. Therefore, in order to generate a 77-GHz signal with the class-C VCO, there is no other way to connect multiple frequency multipliers in series.

Also, since a class—C VCO has inevitable startup problems due to its low gate—bias voltage, there have been several attempts to achieve robust startup such as hybrid VCOs [16], [17], a dual—conduction VCO [18], an adaptive bias scheme [19] and an automatic startup loop [15]. However, the hybrid and dual—conduction topologies, which are secure approaches for robust startup, are not sure solutions in that a free—running auxiliary pair distorts the class—C waveform and degrades the steady—state

phase noise performance. A class-C VCO with the automatic startup loop shows good performance, but it has reliability issues because of its switching operation. An adaptive bias scheme is generally known as a way to easily get a robust startup, but there is a need for an improved scheme that can guarantee startup more reliably.

A method with lower phase noise characteristics (similar to an adaptive bias scheme) than hybrid or dual-core VCO, with improved startup (similar to a hybrid or dual core VCO) over adaptive bias scheme, has been proposed in this paper. More details will be covered in chapter 4.1.

## 2.3. Injection-Locked Oscillator Chain

The injection-locked (IL) oscillator is characterized in that, when an external signal having a frequency similar to that of the free oscillation frequency is injected, the oscillator synchronizes with the injected signal and outputs the same frequency as the injected frequency [20]. It is one way to make an oscillator that is injected and synchronized at the same frequency and has low phase noise characteristics, such as a signal injected at the desired frequency. There is a problem that it is difficult to fix the phase noise characteristic and the phase when designing the oscillator in the high frequency band. Thus, by designing the low-phase-noise VCO in the low frequency band (f<sub>0</sub>) and synchronizing the high

Fig. 14. A four-stage injection locked oscillator chain structure of the proposed 77-GHz signal generator with the ×6 frequency multiplier.

frequency oscillator with the injection lock as the harmonic component  $(n^{th})$  of the VCO output signal, it is possible to design a high frequency  $(n \times f_0)$  signal generator with good phase noise characteristics.

Fig. 14 shows an example of a four-stage IL oscillator (ILO) chain structure of the proposed 77-GHz signal generator with the  $\times 6$  frequency multiplier. Initially at frequency  $f_0$ , the LiT VCO generates a low-phase-noise signal that is injected into a free-running oscillator (IL buffer). The  $3^{\rm rd}$  harmonic component of the output signal of the IL buffer is injected into the freely oscillating tripler near the  $3f_0$  and the tripler oscillation frequency is locked at exactly  $3f_0$ . Likewise, the  $2^{\rm nd}$  harmonic component of the tripler output signal (i.e.,  $6f_0$ ) is injected into the freely oscillating doubler

Fig. 15. Simple equivalent circuit of injection—locked oscillator load.

near the  $6f_0$  and the doubler oscillation frequency is locked at exactly  $6f_0$ .

In order to analyze the phase noise characteristics of the injection locked oscillator in detail, an injection locked oscillator is shown as an equivalent model as shown in Fig 15 [21]. Fig 15 shows a simple one—port modeling of the resonant load when an external signal is applied and G1 is the loss of the resonant load. The circuit in the figure can be expressed simply by the equation (7) as follows.

$$C_{1} \frac{d^{2} V_{osc}}{dt^{2}} - (G_{1} - G_{m}) \frac{d V_{osc}}{dt} + \frac{1}{L_{1}} V_{osc} = \frac{dI_{inj}}{dt}$$

(7)

$I_{inj}(t)$  and  $V_{osc}(t)$  can be expressed by the equations (8) and (9), respectively, and  $V_A(t)$  is the amplitude of the output signal.

$$I_{inj}(t) = I_{inj,p} \cos w_{inj} t = Re \{I_{inj,p} \exp(jw_{inj}t)\}$$

(8)

$$V_{osc}(t) = V_A(t)\cos(w_{inj}t + \theta) = Re\{V_A(t)\exp(jw_{inj}t + j\theta)\} \tag{9}$$

Equations (8) and (9) can be substituted into (7) and the real and imaginary parts can be represented by expressions (10) and (11), respectively.

$$C_{1} \frac{d^{2} V_{A}}{dt^{2}} - C_{1} \left( w_{inj} + \frac{d\theta}{dt} \right)^{2} V_{A} + (G_{1} - G_{m}) \frac{d V_{A}}{dt} + \frac{1}{L_{1}} V_{A}$$

$$= w_{inj} I_{imj,p} \sin \theta$$

(10)

$$\begin{split} &2C_{1}\!\!\left(w_{inj}\!+\!\frac{d\theta}{dt}\right)\!\frac{d\,V_{A}}{dt}\,+\,C_{1}\frac{d^{2}\theta}{dt^{2}}\,V_{A}\!+\!\left(G_{1}\!-\!G_{\!m}\right)\!\!\left(w_{inj}\!+\!\frac{d\theta}{dt}\right)V\\ &=w_{inj}I_{\!imj,p}\!\cos\!\theta \end{split} \tag{11}$$

Several assumptions were made to simplify this equation. The output signal moves slowly in very small amounts, the LC resonator load is  $R_p = G^{-1} = QL_1w_0$ ,  $w^2_{inj} - w^2_0 = 2w_0(w_0 - w_{inj})$ , and  $w_{inj} = w_0$ . Finally, assuming that the phase of the signal changes slowly, equations (8) and (9) can be simplified to equations (10) and (11).

$$\frac{d\theta}{dt} = w_0 - w_{inj} - \frac{w_0 I_{inj,p}}{2 Q I_{osc,p}} sin\theta \tag{12} \label{eq:12}$$

$$\frac{dV_A}{dt} + \frac{G_1 - G_m}{2C_1} V_{env} = \frac{I_{inj,p} \cos\theta}{2C_1}$$

(13)

If the applied signal and the free oscillation signal are synchronized, we can express it as an equation (14).

$$\left(\frac{w_0 - w_{inj}}{w_L}\right)^2 + \left(\frac{G_1 - G_m}{I_{inj,p}} V_{A,p}\right)^2 = 1, \ G_m = G_1 - \frac{V_{A,p}}{I_{inj,p}}$$

(14)

In this case, if the injection lock oscillator is successfully locked, the LC resonator loss is reduced by  $V_{A,p}/I_{inj,p}$  from the free oscillation state loss G1, so that the phase noise characteristic of

the injection lock oscillator is improved compared with that of a general oscillator. Intuitively, there is an effect of lowering the jitter accumulation in terms of time domain as the injection signal is synchronized with the oscillation signal at the zero crossing for every cycle.

It can be found out in Fig. 16 that when the external signal having low-phase-noise characteristic is injected into the oscillator having the high-phase-noise characteristic in the free oscillation state, it has a low-phase-noise characteristic of the injected external signal as shown in the figure when it is locked.

Fig. 16. Phase noise reduction by injection—lock technique.

## 2.4. Summary

In this thesis, in order to generate a 77-GHz low-phase-noise signal was significantly access in three ways. The first approach is to apply a frequency multiplier. At mm-wave frequencies, a VCO suffers from high phase noise due to poor transistor gain as well as the low quality factor of varactors. Therefore, despite consuming more DC power, combining a lower frequency VCO and a frequency multiplier can be a more appropriate solution than direct mm-wave oscillation for the mm-wave low-phase-noise performance. The second approach is to design a VCO with very low phase noise at low frequencies. In this paper, two versions of the 77-GHz signal generator were designed using a ×6 frequency multiplier and a ×28 multiplier, and in each case the problems of the existing LiT VCO and class-C VCO were improved. Finally, a third approach is to use the ILO chain. After designing an improved LiT, class-C VCO with very low phase noise characteristic at low frequencies, the harmonic component of this output signal was injected and locked to the corresponding high frequency oscillator. When constructing a multi-stage ILO chain, the frequency lock range is reduced and power consumption is increased. However, an automotive FMCW radar systems only require a narrow frequency band and battery capacity will be sufficient. Therefore, with the above three approaches, a low-phase-noise 77-GHz FMCW radar transmitter chip could be designed well.

# Chapter 3. 77-GHz FMCW Radar Transmitter with 12.8-GHz PLL and ×6 Frequency Multiplier

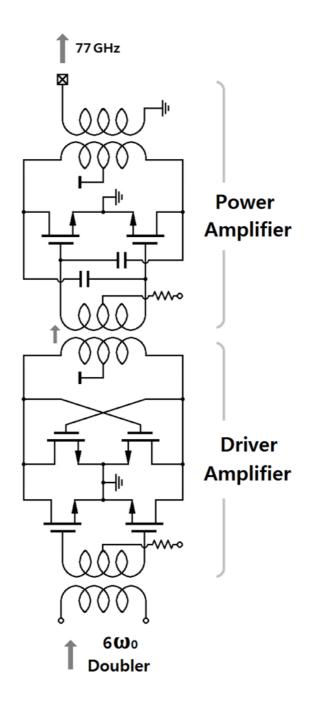

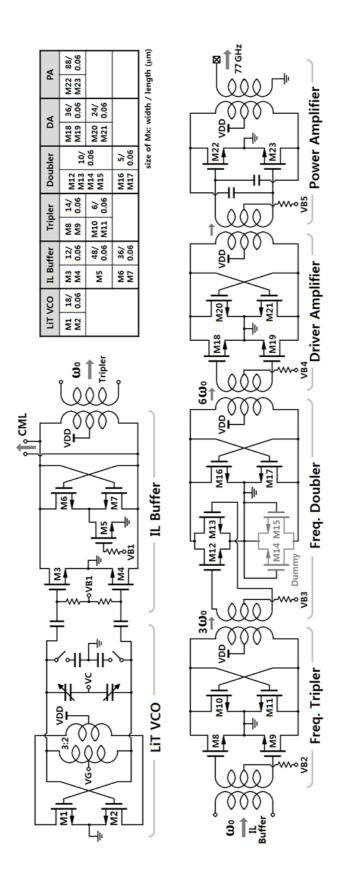

At the beginning of Chapter 2, it was mentioned that there were two approaches to select frequency and architecture. One method (version 1) of them is to combine a ×6 frequency multiplier and a 12.8-GHz PLL. The block diagram of the proposed 77-GHz radar TX is shown in Fig. 17. It consists of a 77-GHz signal generator, a driver amplifier, a power amplifier and PLL blocks. Because the signal generator is implemented with the ILO chain without requiring gain buffers after each ILO, the DC power consumption and chip area can be decreased. Moreover, harmonic suppression, which is one of the main concerns of the multiplier-based system, can be improved by the ILO chain because each oscillator acts as a narrow band-pass filter. A PLL is composed of a current-mode logic (CML) divider, seven stages of true-single-phase-clock (TSPC) divider, a phase frequency detector (PFD), a charge pump (CP), and a loop filter.

In chapter 3.1, an improved LiT VCO design and PLL (phase locked loop) will be discussed in detail. The VCO used in the 12.8-GHz PLL was designed using LiT technology to have low-phase-noise characteristics and was designed to be simpler than the existing LiT VCO using a 3: 2 transformer. The other RF blocks

Fig. 17. Block diagram of the proposed 77-GHz TX chip.

that make up the transmitter chip except VCO, VCO buffer, and PLL blocks will be covered in chapter 3.2. The measurement results are shown in chapter 3.3, and finally the summary will be placed in chapter 3.4.

# 3.1. Proposed LiT VCO and PLL

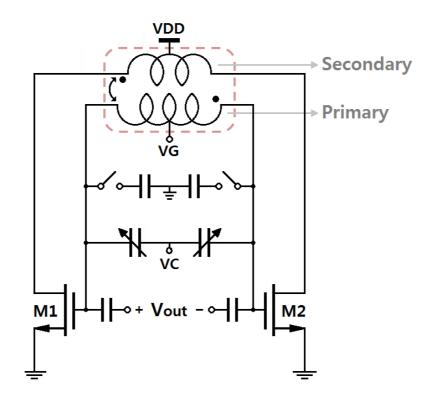

Fig.18 shows the proposed LiT VCO schematics. It is well known that the phase noise characteristic of a VCO is fundamentally due to the oscillation amplitude limit and the inherent noise of the transistor itself. Recently, LiT technology has been developed to solve the above problems and improve the phase noise

Fig. 18. Schematic of the proposed improved LiT VCO.

Fig. 19. Designed 3:2 transformer for the proposed LiT VCO.

.

characteristic of VCO [13]. As described in Chapter 2.1, the LiT technology reduces noise in small signals and increases amplitude in large signals, resulting in good phase noise characteristics. Unlike conventional cross—coupling schemes, a feedback scheme in which the amplitude of the voltage waveform at the drain node of the VCO core transistor is less than the amplitude of the voltage waveform at the gate node should be used. The existing LiT VCO uses complex capacitor divider circuits to obtain this waveform and connects the LC resonator to the gate node of the core. Since the LC resonator is connected to the gate, a very large choke inductor, which appears to be open in AC, must be connected to supply the VDD voltage to the drain node. A complex capacitor divider circuit and a very large choke inductor are added to the VCO, resulting in chip area increase and layout complexity.

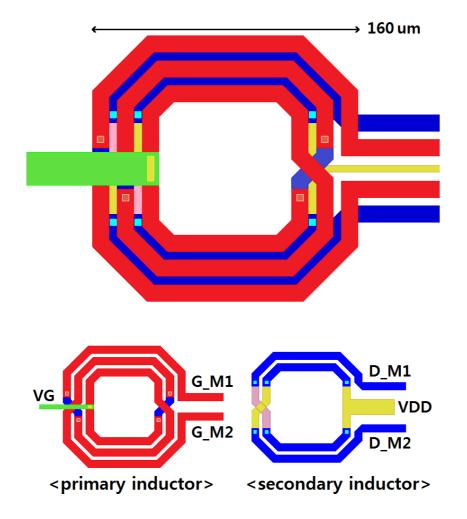

In order to solve the problems mentioned above, to replace the role of choke inductors of the LC resonator and the drain node connected to the capacitor divider circuit and the gate node with a simple and compact 3:2 transformer is proposed [31]. Fig. 18 shows a schematic of the proposed LiT VCO and Fig. 19 presents a designed 3:2 transformer for the proposed LiT VCO. The diameter of the outermost coil of the designed 3: 2 transformer primary inductor is 160 µm. The primary inductor with a turn number of three is connected to the gate node of the VCO core and the inductance measured by EM-simulation is 324 pH at 12.8-GHz. Secondary inductors with a turn number of 2 are connected to the

Fig. 20. (a) Simulated waveforms of a 3:2 transformer based LiT VCO, (b) Those of a conventional LC VCO.

drain node, and similarly the inductance is 147 pH at 12.8-GHz. Fig. 20 (a) shows a waveform that is suitable for LiT by connecting a primary turn-inductor with a turn number to the gate node and a secondary inductor with a small turn number to the drain node. Comparing Fig. 20 (a) and (b), it can be seen intuitively that the

Fig. 21. Schematic of the injection-locked buffer.

general VCO is longer than the LiT VCO in the triode region, which is one of the main causes of VCO nonlinearity. Therefore, it can be concluded that the proposed LiT VCO can obtain improved phase noise characteristics.

Since the output signal of the VCO must be transmitted to the CML frequency divider and the frequency multiplier of the PLL, respectively, a buffer that provides a large output power is needed. Therefore, a buffer is constructed using an injection-lock oscillator [22]. As shown in Fig. 21, the injection-lock buffer consists of small transistors acting as a buffer, a large cross-coupled transistors serving as a large output power, a current source, and a transformer which transfers the signal to the × 3 multiplier while being used as a load of an injection-locked oscillator. When the output signal of the VCO is injected into the buffer, the oscillation frequency of the buffer is locked by the oscillation frequency of the VCO when the buffer oscillates itself near 12.8-GHz.

In this paper, an integer N-type PLL is designed. The designed PLL consists of a CML divider, a TSPC divider, a PFD, a charge pump and a loop filter. The output signal of the VCO buffer enters the CML frequency divider. Because the CML frequency divider can operate at a relatively high speed without using the resonance structure requiring the inductor, the high frequency input signal of 12.8 GHz is divided into 6.4 GHz. The designed CML divider is commonly used and designed on the basis of a master-slave D flip-flop. The divided signal by CML divided into low-frequency

signals of about 50-MHz through the seven-stage TSPC divider. The PFD compares phase and frequency of the divided VCO output signal to those of a reference signal (F<sub>REF</sub>). The loop bandwidth can be adjusted from 100~kHz to 1~MHz by controlling the CP bias current.

# 3.2. ×6 Multiplier and Power Amplifier

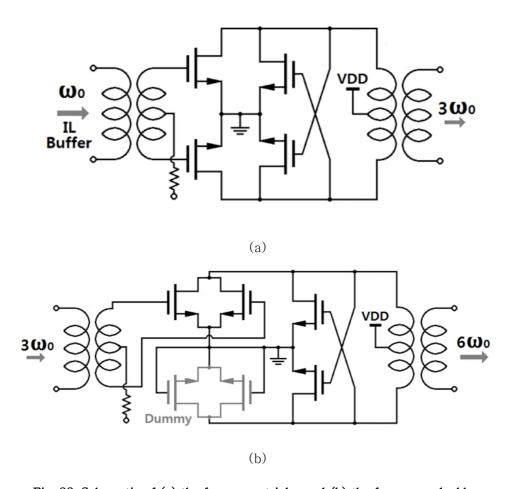

Fig. 22 is a schematic of a  $\times 6$  frequency multiplier. The proposed  $\times 6$  multiplier consists of a  $\times 3$  frequency multiplier (tripler) and a  $\times 2$  frequency multiplier (doubler) connected in series by using an injection-locked oscillator. In general, since the

Fig. 22. Schematic of (a) the frequency tripler and (b) the frequency doubler.

output power of the harmonic component exceeding the third order is small, the 2<sup>nd</sup> or 3<sup>rd</sup> harmonic component is often used for the frequency multiplier. In this design process, a multiplier using a 3<sup>rd</sup> harmonic component is used for the first stage, and next, a 2<sup>nd</sup> harmonic component is used for the second stage. Consequently, a frequency multiplier chain which is multiplied by 6 at a frequency of 12.8 GHz to 77 GHz is designed. The tripler is designed to inject the 3<sup>rd</sup> harmonic component generated from the VCO buffer into the self-oscillating tripler core near the triple frequency through the injection transistors [23]. The injection-locking range of the 3<sup>rd</sup> harmonic injection-lock oscillator can be expressed as an equation (15).

$$\begin{split} \left| 3 \, \bullet \, \omega_{inj} \! - \! \omega_0 \right| \; < \Delta \omega_{lock} \\ \Delta \omega_{lock} = \frac{\omega_0}{2 \, Q} \, \bullet \, \frac{A_{3w_0, \, inj}}{A} \end{split} \tag{15}$$

Q,  $\omega_0$ , and A in the equation represent the Q-factor, the resonance frequency of the LC resonator of the oscillator, and the output voltage amplitude of the self-oscillating tripler, respectively.  $A_{3wo,inj}$  represents the output voltage amplitude of the VCO buffer. It can be found out from equation (15) that if the Q-factor of the LC resonator of the tripler becomes large, the frequency lock range becomes narrow, so that the output frequency of the tripler cannot follow the frequency of the output oscillation signal of the VCO buffer. Also, the larger the frequency lock range, the greater the

frequency difference between the two signals for frequency synchronization, and thus the more stable circuit can be realized. Therefore, the tripler in this research was designed to ensure a proper frequency lock range. If the tripler is designed to resonate in a band similar to the three-times of output oscillation frequency of the VCO buffer and have an appropriate frequency lock range, then it is advantageous to obtain lower DC consumption voltage and higher RF output power than the amplifier type multiplier (not ILO chain) type do. In the case of a large-signal operation in which the oscillator oscillates in a frequency-synchronized state, the output voltage amplitude V<sub>out</sub> of the tripler can be expressed by an equation (16).

$$V_{out} = rac{2}{\pi} \cdot I_{bias} \cdot R_L$$

$I_{bias}$  in equation (16) denotes a bias current switched between the differential stages of the tripler, and  $R_L$  denotes a substantial load resistance. If the tripler operates as an oscillator, the output voltage amplitude is determined by the bias current and the actual load resistance. And the loss of the LC resonator is compensated by the negative resistance end due to the cross-coupling pair, thereby obtaining a large output voltage amplitude. Thus, two multipliers can be connected directly without using a gain buffer.

A 38.5-GHz signal with a large output power and three times multiplication is passed through the transformer to the doubler. The doubler uses a method of injecting a signal by adding a push-push

Fig. 23. Schematic of the power amplifier.

cell with a common source structure next to the cross-coupling pair structure. The push-push method is mainly used for a general frequency doubler because it can increase the 2<sup>nd</sup> harmonic component and remove unwanted odd order components. Since the push-push cell is connected to only one side of the doubler core, a dummy cell is added to the other side to make the resonance load conditions the same. The 2<sup>nd</sup> harmonic component generated from the push-push cell is injected into the doubler core oscillating freely at near 77-GHz. In order to set the frequency of the oscillator to 77-GHz accurately, both the passive element and the wiring layout of the active element were modeled through EM simulation.

Fig. 23 is a circuit schematic of a driver amplifier and a power amplifier designed to have a sufficiently large output power that the proposed transmitter is suitable for a 77-GHz automotive midrange and long-range radar. The driver amplifier is designed with a high gain structure using a cross-coupled pair to achieve a large voltage swing with low power consumption [24]. The power amplifier is designed with a neutralization technique to neutralize the C<sub>gd</sub> parasitic capacitors between the gate and drain nodes by adding capacitors between the drain and the gate in a differential manner in the cross-coupled structure [25]. The gain and stability of the power amplifier have been increased due to this technique. The total schematic of RF blocks is shown in Fig. 24.

Fig. 24. Total circuit schematic of RF blocks.

#### 3.3. Measurement Results

#### 3.3.1 LiT VCO Measurement Results

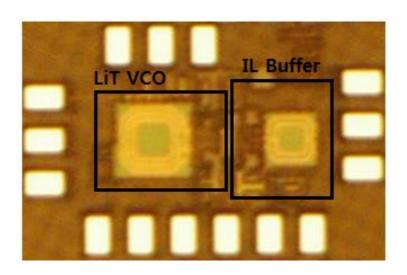

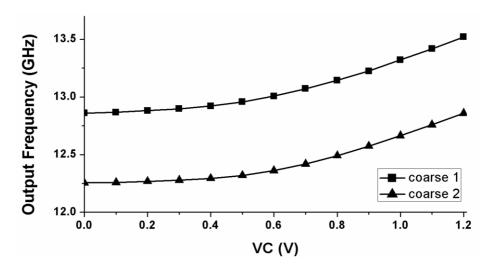

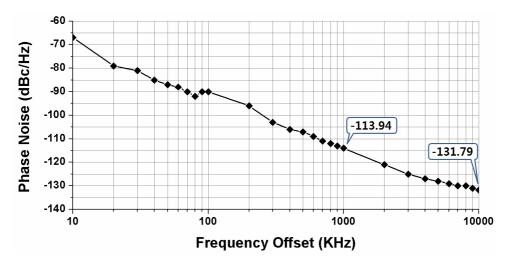

The proposed 13 GHz LiT VCO with the 3:2 transformer is fabricated in 65-nm RF CMOS process. Fig. 25 shows a chip micro-photograph of the proposed LiT VCO and IL buffer. The output frequency and phase noise are measured by an Agilent E4448A spectrum analyzer with RF and DC probing. The measured output frequency tuning ranges are 12.25 GHz ~ 12.86 GHz and 12.86 GHz ~ 13.52 GHz [Fig. 26]. The output power is approximately 7.2 dBm when the VCO core and the IL buffer consume 7.7 mW and 21.6 mW, respectively. The measured phase

Fig. 25. Chip micro-photograph of the proposed LiT VCO and IL buffer.

Fig. 26. Measured output frequency.

Fig. 27. Measured phase noise when carrier frequency is 13.2 GHz.

noise shows a good value of -113.94 dBc/Hz at 1 MHz offset frequency [Fig. 27]. Fig. 5 shows a micro-photograph of a chip. The chip size is  $830\times530~\mu\text{m}^2$ , including test pads. Table II highlights the details of the VCO performance. The FOM is determined as below.

$$FOM = -L(\Delta f) - 10\log\{(\Delta f / f_{osc})^2 \cdot P_{dc\_mW}\}$$

(14)

$L(\Delta f)$  is the phase noise,  $\Delta f$  is the offset frequency,  $f_{\rm osc}$  is the oscillation frequency and  $P_{dc\_mW}$  is the DC power consumption.

Table II. Performance of the proposed LiT VCO

| Technology      | 65 nm RF CMOS                                              |  |  |  |

|-----------------|------------------------------------------------------------|--|--|--|

| Tuning Range    | Coarse 1: 12.25 ~ 12.86 GHz<br>Coarse 2: 12.86 ~ 13.52 GHz |  |  |  |

| Phase Noise     | -113.94 dBc/Hz @ 1MHz offset                               |  |  |  |

| Core DC power   | 7.7 mW                                                     |  |  |  |

| Buffer DC power | 21.6 mW                                                    |  |  |  |

| Output power    | 7.2 dBm                                                    |  |  |  |

| Full-Chip Size  | $830 \times 530 \ \mu m^2$                                 |  |  |  |

| FOM             | 187.48                                                     |  |  |  |

### 3.3.2 77-GHz Transmitter (v1) Measurement Results

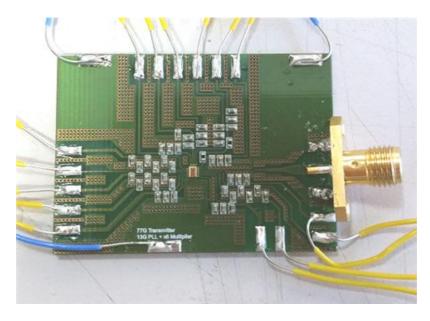

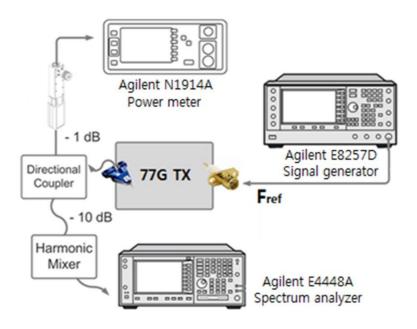

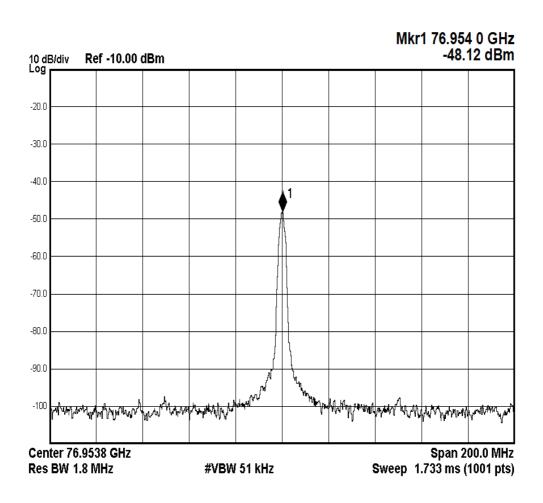

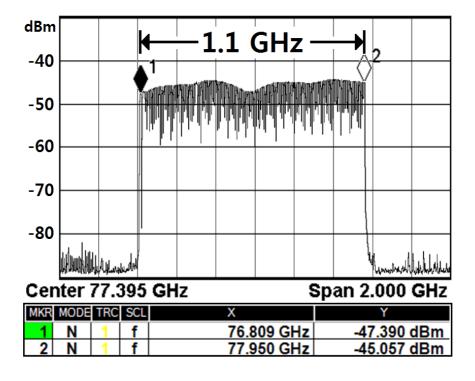

The proposed chip was fabricated using a 1-poly 8-metal, 65nm CMOS process with a top copper metal thickness of 3 µm. Fig. 28 is a microphotograph of the manufactured transmitter chip for a 77-GHz automotive radar. The size of the designed chip is  $1.38 \times$ 0.79 mm<sup>2</sup> including the pad. PCB was fabricated for measurement as shown in Fig. 29. DC bias was applied through PCB line and RF output was measured by on-wafer probing using an RF probe capable of measuring up to 110-GHz. The 50-MHz triangular reference signal was applied to the chip on the PCB board using the SMA connector. Fig. 30 presents the equipment settings for measuring the W-band signal output. Since the Agilent E4448A spectrum analyzer cannot measure up to 77-GHz by itself, the output frequency spectrum and phase noise performance are measured by connecting the external mixer. The RF output power was measured using an Agilent N1914A power detector and the output power and output frequency spectrum were simultaneously verified using a -10 dB directional coupler at the output stage. The reference chirp signal was applied to the Agilent E8257D signal generator. The output spectrum measured in the above-mentioned experimental environment is shown in Fig. 31. It is the output spectrum screen when the PLL is locked and the reference signal is 50.1 MHz and the carrier frequency is 76.54 GHz which is 1536 times the reference signal. Because the horizontal axis of the

Fig. 28. A microphotograph of the transmitter chip.

Fig. 29. A PCB to measure fabricated transmitter chip.

Fig. 30. An experimental environment.

Fig. 31. A measured frequency spectrum.

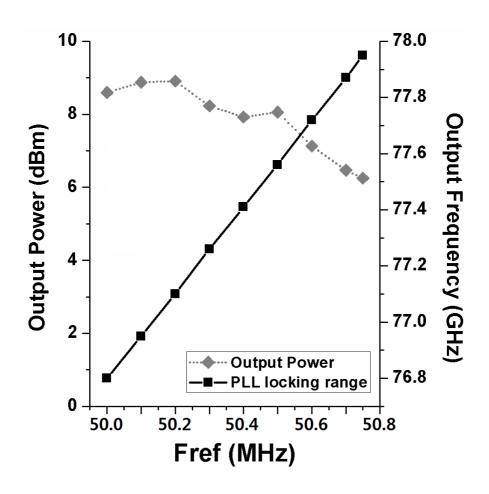

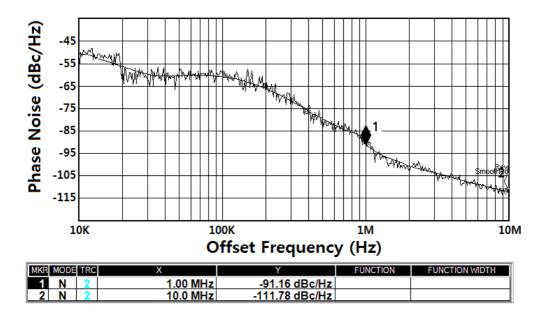

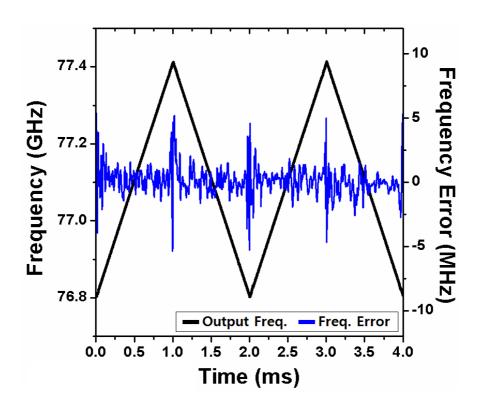

screen is 200-MHz in total, it is 20-MHz per space in the horizontal direction. Since the output signal must pass through the RF probe, cable, external mixer, and -10 dB coupler until it reaches the spectrum analyzer, the output power shown in the spectrum analyzer is low due to these losses. The actual output power measured by the power detector and compensated for various losses and the output frequency seen by the spectrum analyzer are shown in Fig. 32. The output frequency range measured with the PLL locked to the reference signal is 76.81 ~ 77.95-GHz when the reference signal is 50.0 ~ 50.75-MHz. Output power was measured at 6 to 8.9 dBm in the lock range. Fig. 33 represents the measured phase noise characteristics when the transmitter output carrier frequency is 76.91-GHz. The measured phase noise value is -91.16 dBc / Hz at the 1-MHz frequency offset and -111.78 dBc / Hz at the 10-MHz frequency offset with the markers placed on the spectrum analyzer screen. Fig. 34 shows the output spread spectrum of the transmitter chip when changing the reference signal from 50.00-MHz to 50.75-MHz slowly (10 ms). In the figure, the proposed transmitter chip can cover the output triangular wave bandwidth of 1.1-GHz when the triangular wave reference signal is applied, which is twice as large as the minimum triangular wave bandwidth 600 MHz required for the 77-GHz FMCW radar for vehicles. Because fast sweep time of an external triangular chirp signal is required for the automotive FMCW radar application, the measured FMCW chirp bandwidth is lowered to 601 MHz with a fast

Fig. 32. Measured phase-locked output frequency and power.

Fig. 33. Measured phase-noise at 76.81-GHz carrier frequency.

Fig. 34. Measured spread spectrum with 10-ms slow chirp reference signal.

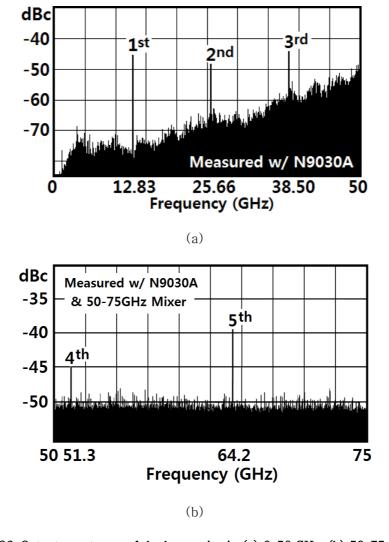

1-ms sweep time, as shown in Fig. 35. The measured root-mean-square (rms) frequency error is approximately 490 KHz.). The  $1^{\rm st}$ ,  $2^{\rm nd}$ , and  $3^{\rm rd}$  harmonic output spectrum is presented in Fig. 36 (a) and the  $4^{\rm th}$  and  $5^{\rm th}$  harmonic components are shown in Fig. 36 (b).

Fig. 35. FMCW profile and frequency error with 1-ms fast chirp reference signal.

Due to the ILOs, the undesired harmonic components are lowered below -39 dBc. Table III shows the performance comparison between the proposed paper and the recently published 77-GHz radar papers. Looking at the Table III in detail, the proposed radar transmitter chip is designed with the integer-N PLL, so it has a disadvantage that it needs a signal source that provides a triangular

Fig. 36. Output spectrums of the harmonics in (a) 0-50 GHz, (b) 50-75 GHz.

Table III. Comparison of RADAR Transmitters or Transceivers

|                          | [6]                        | [7]                | [8]              | [9]             | [10]            | This<br>work    |

|--------------------------|----------------------------|--------------------|------------------|-----------------|-----------------|-----------------|

| Tech.                    | SiGe<br>Bipolar            | SiGe<br>Bipolar    | 65nm<br>CMOS     | 90nm<br>CMOS    | 65nm<br>CMOS    | 65nm<br>CMOS    |

| Func./<br>PLL            | TRX /<br>Frac. N           | TRX /              | TRX /<br>Frac. N | TRX /<br>Int. N | TX /<br>Frac. N | TX /<br>Int. N  |

| Freq. (GHz)              | 68-93.6                    | 75-79              | 75.6<br>-76.3    | 78.1<br>-78.8   | 76-81           | 76.81<br>-77.95 |

| RMS Freq.<br>Error (KHz) | N/A                        | N/A                | < 300            | N/A             | 970             | 490             |

| ×N                       | ×1                         | ×18                | ×1               | ×1              | ×2              | ×6              |

| Pout (dBm)               | 7                          | 6.2                | 5.1              | -2.8            | 3               | 8.9             |

| Phase Noise<br>(dBc/Hz)  | -88<br>@10K,<br>-90<br>@1M | -105.3<br>*<br>@1M | -85.33<br>@1M    | -85<br>@1M      | -83.43<br>@1M   | -91.2<br>@1M    |

| TX+PLL<br>Pdiss (mW)     | 423                        | 1125               | 243<br>(TRX)     | 406             | 320             | 116.7           |

| Area (mm²)               | 1.9<br>×1.6                | 3<br>×1.8          | 1<br>×1.1        | 3.5<br>×2       | 1.5<br>×1.9     | 1.4<br>×0.8     |

$<sup>\</sup>ast$  4.25-GHz external signal source (Agilent E8257D) is used.

chirp reference signal, but it shows the quite good performances. The proposed chip provides the lowest phase noise among 77-GHz CMOS radar transmitter chips developed so far, suitable frequency range for FMCW radar, and low DC power consumption.

## 3.4. Summary

In this paper, a 77-GHz FMCW radar transmitter chip was fabricated by constructing a PLL using a 12.8-GHz high-performance VCO and integrating it with a ×6 frequency multiplier and a power amplifier. In the millimeter-wave band, it is well known that it is more advantageous to design the oscillator in the lower frequency band than direct oscillation at the mm-wave band.

Therefore, in this research, a 77-GHz radar transmitter chip was fabricated by designing an oscillator at 12.8 GHz and injecting a 12.8-GHz signal into a PLL and a × 6 multiplier. The 12.8-GHz high-performance VCO is designed to maximize the amplitude of VCO and reduce the inherent noise by applying LiT technology. Although the existing LiT technology has the effect of improving the phase noise characteristic but there is a problem that the structure is complicated and the required area becomes large. In the method using the proposed 3:2 transformer, the above problems are solved simply while maintaining the performance improvement.

Among the RF blocks of the proposed chip, the VCO, IL VCO buffer, ×3 multiplier, and ×2 multiplier, which correspond to the signal generator that produces the 77-GHz signal, are all designed as oscillators. Both of them were designed to follow the initial signal source VCO using frequency locking and phase noise performance using injection-locking techniques. That is, the signal generator including the × 6 multiplier was designed with only four connected

injection locked oscillators without additional buffers or gain stages. In this way, it is possible to improve the phase noise characteristics and to reduce the DC power consumption and area, but the frequency lock range becomes small. However, since the 77-GHz FMCW radar is a narrow-band system with a required frequency band of about 500-MHz, it may not be affected by the disadvantages of the multiple-stage oscillator coupled with the injection lock.

The designed chip is fabricated in 65nm CMOS process and the chip size is  $1.38 \times 0.79 \text{ mm}^2$  including pad. The RF output was measured through a probe through a wafer, and the DC bias was applied via a bonding wire on the PCB. The measurement equipment used was an Agilent E4448A spectrum analyzer, an Agilent N1914A power detector, and an Agilent E8257D signal generator. The measured chip supports a locked output frequency of 76.81 to 77.95-GHz, which is 1536 times the reference signal when the slow chirp (10 ms) reference signal is 50.0 to 50.75-MHz. The measured FMCW chirp bandwidth with a fast 1-ms sweep time is lowered to 601 MHz. The maximum output power is 8.9 dBm and the DC power consumption is 116.7 mW. Because the phase noise characteristic, which is the most important performance indicator in the radar transmitter, provides the best phase noise characteristic among the papers published at -91.16 dBc/Hz at 1-MHz offset. Therefore, it can be confirmed that the proposed chip is a highperformance 77-GHz vehicle radar transmitter.

# Chapter 4. 77-GHz FMCW Radar Transmitter with 2.75-GHz PLL and ×28 Frequency Multiplier

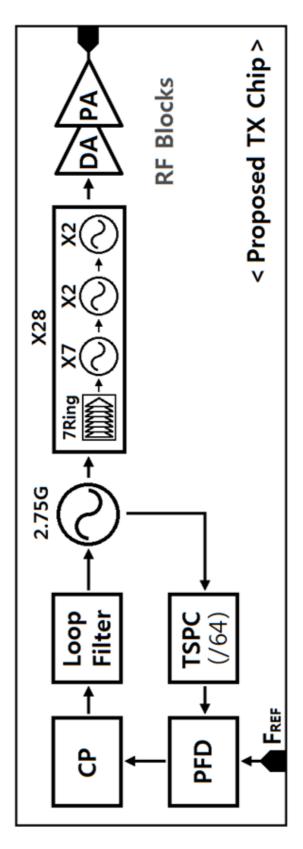

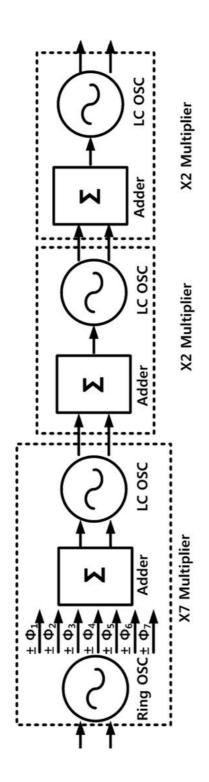

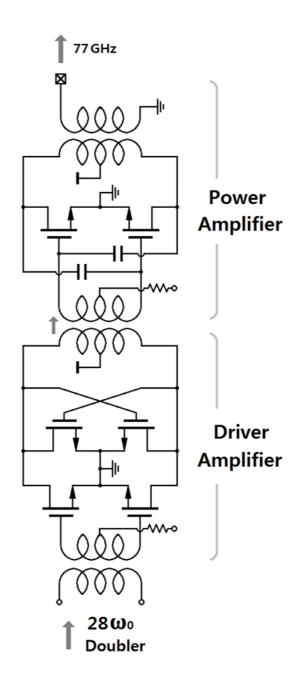

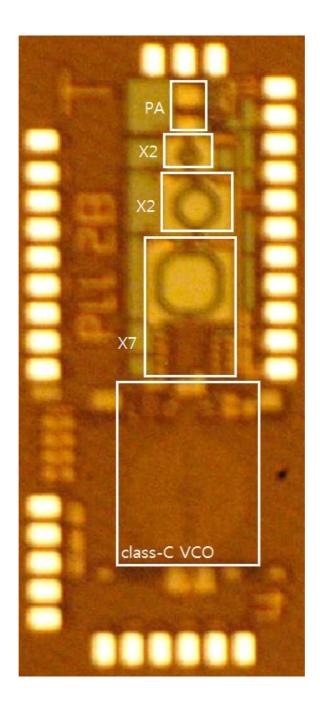

At the beginning of Chapter 2, it was mentioned that there were two approaches to select frequency and architecture. One method of them is to combine a ×6 frequency multiplier and a 12.8-GHz PLL, which is covered in chapter 3. The other method (version 2) is to combine a ×28 frequency multiplier and a 2.75-GHz PLL. The block diagram of the proposed 77-GHz radar TX is shown in Fig. 37. It consists of a 77-GHz signal generator (2.75-GHz VCO, ×7 multiplier, and two ×2 multipliers), a driver amplifier, a power amplifier and PLL blocks. The basic structure is similar to the transmitter discussed in chapter 3, but because the multiplication factor is increased to 28, the VCO could be designed at a lower frequency of 2.75 GHz. Thus, a class-C VCO, which is known to be the best in terms of phase noise, could be applied. In the case of the ×28 frequency multiplier, a ×7 multiplier and two doublers are cascaded. Similarly, the 77-GHz signal generator is configured in the form of an ILO chain.

In chapter 4.1, an improved class-C VCO design and PLL will be explained in detail. The class-C VCO used in the 2.75-GHz PLL was designed to have low-phase-noise characteristics and was designed to have faster and more robust startup than conventional

Fig. 37. Block diagram of the proposed 77-GHz TX chip.

class—C VCOs. The other RF blocks such as a frequency multiplier and a power amplifier will be covered in chapter 4.2. The measurement results are shown in chapter 4.3, and the summary will be followed in chapter 4.4.

#### 4.1. Proposed class-C VCO and PLL

Class-C VCOs have been proposed steadily in recent years.

Compared with an LC cross-coupled VCO, the class-C VCO provides better phase noise performance due to its low gate-bias voltage, which can be explained by impulse sensitivity function [14].

Given that a class-C VCO has inevitable startup problems due to its low gate-bias voltage, there have been several attempts to achieve robust startup such as hybrid VCOs [16], [17], a dualconduction VCO [18], an adaptive bias scheme [19] and an automatic startup loop [15]. However, the hybrid and dualconduction topologies, which are secure approaches for robust startup, are not sure solutions in that a free-running auxiliary pair distorts the class-C waveform and degrades the steady-state phase noise performance. A class-C VCO with the automatic startup loop shows good performance, but it has reliability issues because of its switching operation. An adaptive bias scheme is generally known as a way to easily get a robust startup, but there is a need for an improved scheme that can guarantee startup more reliably. To improve the startup beyond what an adaptive bias scheme can achieve a self-turn-off auxiliary Class-B pair that maintains low-phase-noise performance and mitigates the startup problem of class-C VCOs is proposed [32].

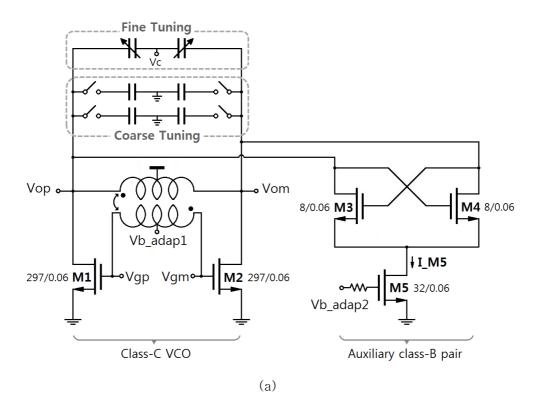

A schematic of the proposed class-C VCO with a self-turn-off auxiliary class-B pair is shown in Fig. 38(a). The gate bias voltage

Fig. 38. Schematic of (a) the proposed class-C VCO with an auxiliary class-B pair,

(b) the adaptive bias circuit, and (c) the output buffer.

of the main class-C pair (M1/M2) and that of the auxiliary class-B pair current source (M5) are generated by adaptive bias control circuits [Fig. 38(b)]. A bias network for class-C operation is simply realized by using the center-tapped secondary winding of a transformer, whose primary replaces the tank inductance [14]. The primary inductor has simulated inductance and quality factor (Q) at 2.5 GHz of 2.46 nH and 8.1, respectively, and the secondary

Fig. 39. Adaptive bias voltage waveform of the proposed VCO.

inductor has those of 1.66 nH and 6.4, respectively. The coupling coefficient of the transformer is 0.86 at 2.5 GHz.

In the adaptive bias control circuit, the gates of M7/M8 are, respectively, connected to those of M1/M2 to mirror the M1/M2 currents. These currents are summed at the Vb\_adap1 node and are compared with the M6 current. Then, the capacitor C1 converts the current difference to voltage. This voltage is fed back to the gate of M1/M2 through the center—tap of the transformer [19].

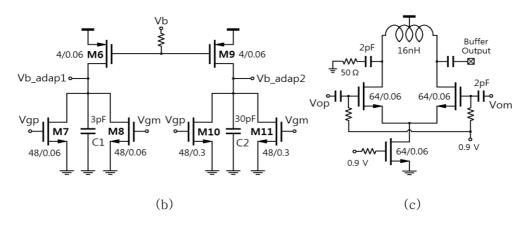

The transient waveforms of the class-C core and the adaptive bias circuit are shown in Fig. 39. The initial voltage and the slope of the Vb\_adap1/Vb\_adap2 graph are determined by the amount of current flowing in each bias circuit and by the sizes of C1 and C2. The initial voltage of Vb\_adap1 is set to 0.32 V when Vb is 0.4 V to guarantee oscillation. With the increase in the voltage amplitude of the oscillator core (Vgp), the currents of the class-C core and the bias circuit are increased. This increased current of the bias circuit is integrated into C1 at the Vb\_adap1 node and lowers the voltage of Vb\_adap1 to nearly 0 V for class—C operation (the solid black line). The dashed black line in the graph shows the adaptive bias for self-turn-off operation. The gate of the current source (M5) is biased by 0.8 V to turn on M5 in an initial state and almost 0 V to turn it off in a steady-state. The simulated current of the auxiliary pair (the solid red line) in the initial state and the steady-state is 2 mA and nearly 0 mA, respectively. Therefore, the auxiliary class-B pair can provide an additional negative trans-conductance for fast

Fig. 40. Comparison of a class-C VCO startup by transient simulation.

startup before entering the steady-state and then it turns itself off (no DC power consumption) in the steady-state.

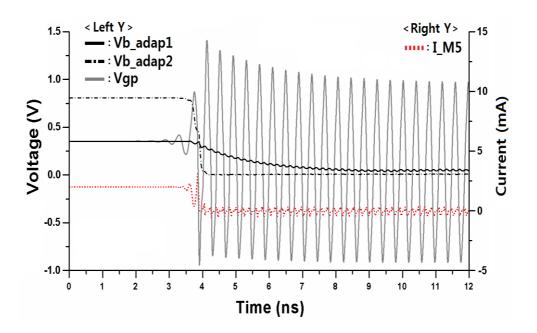

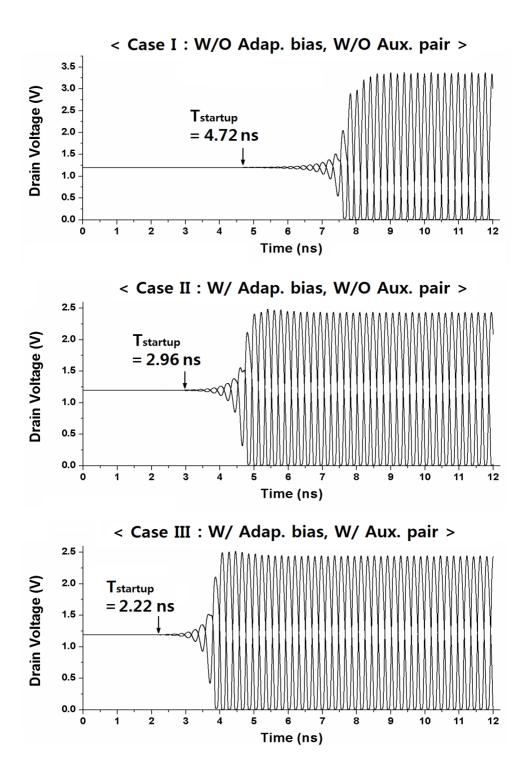

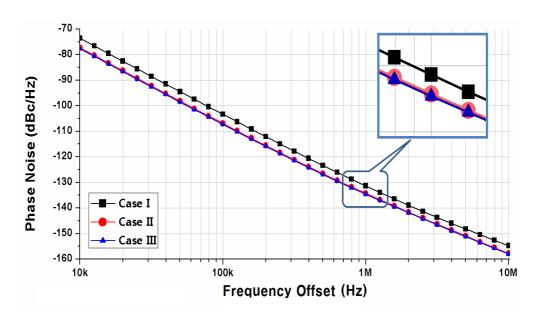

Transient simulation results that verify the fast startup are shown in Fig. 40. In this work,  $T_{\text{startup}}$  is defined according to the time when the difference between positive and negative voltage swings reaches 5 mV for the first time. The gate bias voltage of the VCO in case I is 0.32 V which is the same as the initial voltage of Vb\_adap1 for a fair comparison. The startup time of the adaptively biased class-C VCO with the auxiliary class-B pair (Case III) is 2.22 ns, which is faster than that of the adaptively biased class-C VCO without the auxiliary pair ( $T_{\text{startup}} = 2.96$  ns) as simulated in Case II and much faster than that of the general class-C VCO without a startup technique ( $T_{\text{startup}} = 4.72$  ns), as also simulated in Case I.

The simulated phase noise of each case is shown in Fig. 41. Because the gate bias of the class—C VCO core is decreased adaptively (Case II and III), the current waveform of the VCO is sharper than that of Case I which provides a longer conduction time [19]. Therefore, the phase noise of Case II and III is lower than that of Case I as much as approximately 3 dB in simulation. Unlike conventional hybrid or dual—conduction topologies, the phase noise performance in Case III is not degraded compared with Case II because the class—B auxiliary pair which distorts the impulse—like class—C current waveform turns itself off in steady—state automatically. To verify how much the proposed self—turn—off

Fig. 41. Comparison of simulated phase noise of each case.

TABLE IV.

Comparison of Startup w/ & w/o the Self-Turn-Off Auxiliary Pair

| w/o self-turn-off<br>auxiliary pair |                  | w/ self-turn-off<br>auxiliary pair |                  |  |

|-------------------------------------|------------------|------------------------------------|------------------|--|

| Core gate<br>bias (V)               | Tstartup<br>(ns) | Core gate<br>bias (V)              | Tstartup<br>(ns) |  |

| 0.32                                | 4.72             | 0.32                               | 2.92             |  |

| 0.30                                | 11.50            | 0.30                               | 4.56             |  |

| 0.28                                | -                | 0.28                               | 7.23             |  |

| :                                   | :                | :                                  | :                |  |

| 0.12                                | -                | 0.12                               | 44.64            |  |

| 0.10                                | -                | 0.10                               | -                |  |

auxiliary class—B pair contributes to the robustness of startup, the startup simulation results according to each fixed gate bias of the main VCO core are shown in Table III. The minimum oscillation gate bias voltage with and without the proposed auxiliary pair is 0.12 V and 0.3 V, respectively. Thus, the self—turn—off auxiliary pair can guarantee oscillation when the initial voltage of the adaptive bias circuit is reduced by process variation or a mismatch of transistor models.

Judging from Figs. 40 and 41 and Table IV, the proposed adaptively biased class—C VCO with the self—turn—off auxiliary class—B pair provides fast and robust startup without any performance degradation, such as phase noise increase or additional DC power consumption in the steady—state.

As with the version of the transmitter mentioned in chapter 3, an integer N-type PLL is designed. The designed PLL consists of a TSPC divider, a PFD, a charge pump and a loop filter. The VCO output signal is divided into low-frequency signals of about 41-MHz through the six-stage TSPC divider. The PFD compares phase and frequency of the divided VCO output signal to those of a reference signal ( $F_{REF}$ ). The loop bandwidth can be adjusted from 100 kHz to 1 MHz by controlling the CP bias current.

# 4.2. ×28 Multiplier and Power Amplifier

Harmonic amplification is commonly used for millimeter—wave frequency multipliers [26]. However, since amplification stages are required to enhance weak harmonic components, using a higher order harmonic component increases the burden on the system. As a result, unwanted frequency components require a filtering step. Therefore, in the transmitter chip of chapter 3, the frequency multiplier is designed using the ILO chain which does not need amplifier stages and can perform self—filtering. However, this is also not suitable for designing a frequency multiplier with high multiplication factor due to weak high—order harmonic power. If too many multiplier stages are connected in series, the frequency lock range will be reduced, power consumption and system complexity will increase, so a multiplier design with high multiplication factor is required.

Another way to multiply frequencies is to use multi-push technology [27]. Multi-push (N-push) technology eliminates unwanted harmonics by adding the desired harmonic components together in a structured manner, eliminating the need for additional amplifiers and filters. However, N-phase signal is required in the desired frequency and phase correction circuit [28].

Because N-push multipliers require N-phase signals with higher amplitudes at the desired harmonics to obtain sufficient output power, a ring oscillator composed of inverters can be a good

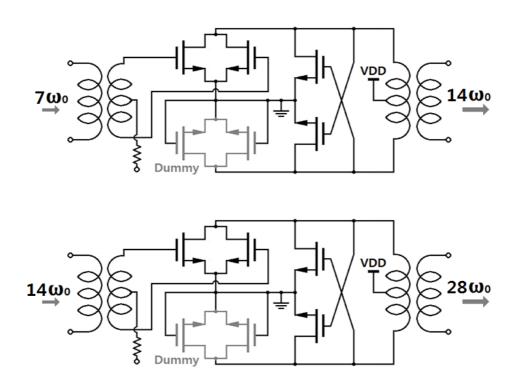

Fig. 42. Block diagram of the designed  $\times 28$  frequency multiplier.

candidate for generating phase signals with rich harmonic power. The ideal ring oscillator provides a square wave, so theoretically, all orders of the N-push multiplier can be implemented without degrading the amplitude. However, since the high-frequency harmonic signal is attenuated bу the low-pass characteristic, it is difficult to achieve sufficient harmonic power combination for a high order. Therefore in this thesis, a ×28 multiplier is implemented by putting two stages of doubler after 7push multiplier as shown in Fig. 42. This frequency multiplier was designed by referring to previous work which designed 10 multiplier [29], [30].

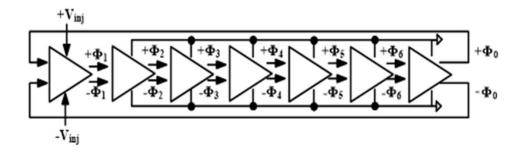

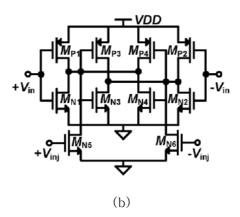

Fig. 43 is a circuit schematic of the designed 7-push frequency multiplier which consists of a 7-stage ring oscillator chain and adder. The 7-push multiplier requires the differential 7-stage ring oscillator with the rich 7-th harmonic component, but the large number of 7 results in more parasitic and bandwidth reduction which causes low harmonic power. The differential injection-locked ring oscillator with 7-stage inverters is used to generate 7-signals with 2pi/7 phase difference. The ring oscillator is locked by the low-phase-noise output signal of the proposed class-C VCO. Each output node of the ring cell is connected to the adder (class-AB CS amplifier). The class-AB transistors (M1-M14) and the cross-coupled transistors (M15, M16) share the output resonant load at  $7 w_0$ . The  $7^{th}$  harmonic is enhanced by the nonlinearity of the class-AB amplifiers and only the  $7^{th}$  harmonic is amplified by the  $7 w_0$  LC

(a)

Fig. 43. (a) Block diagram of the 7-stage ring oscillator, (b) schematic of the ring cell, and (c) schematic of the adder and the oscillator (7f<sub>0</sub>).

resonant load and cross-coupled pairs. In addition, unwanted harmonics that are not canceled due to phase and amplitude mismatches are filtered by the  $7 w_0$  LC resonant load.

The two-stage frequency doubler behind the 7-push multiplier is the same circuit mentioned in chapter 3 as shown in Fig. 44. The first stage doubler receives the 19.25-GHz signal, which is a 7-push multiplier output, and generates a second harmonic component,

Fig. 44. Schematic of the two stage frequency doubler.

Fig. 45. Schematic of the power amplifier.

38.5 GHz, through the common-node cell. This signal is injected and locked into the first doubler core oscillating near 38.5 GHz. The second stage doubler receivers the 38.5-GHz signal and also generates its second harmonic component, 77 GHz, through the common-node cell. This signal is injected and locked into the second doubler core oscillating near 77 GHz. Thus, the 2.75-GHz signal from the improved class-C VCO based PLL is multiplied by 28 times to a 77-GHz signal.

The power amplifier was designed with the same structure as mentioned in chapter 3 and the transistor size was modified to suit the load conditions as shown in Fig. 45.

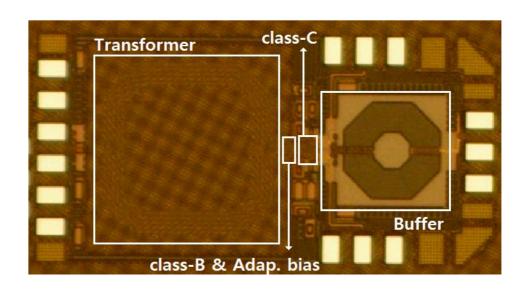

#### 4.3. 77-GHz Transmitter Measurement Results

#### **4.3.1 Class-C VCO Measurement Results**

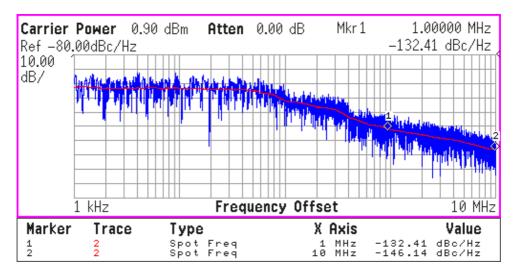

The proposed class-C VCO is fabricated via a standard 65-nm CMOS process. Fig. 46 shows a photograph of a chip. The total chip size is  $720 \times 1440~\mu\text{m}^2$ , including the test pads. The measured frequency tuning ranges are 2.30-2.36 GHz, 2.38 -2.44 GHz and 2.47-2.54 GHz and the measured output power is approximately 5.5 dBm when the output buffer consumes 16.8 mW at 1.2-V V<sub>DD</sub> [Fig. 47]. The measured phase noise shows a feasible value of -132.41 dBc/Hz at a 1-MHz frequency offset [Fig. 48]. The DC power

Fig. 46. Chip micro-photograph of the proposed class-C VCO.

Fig. 47. Measured output frequency and output power.

Fig. 48. Measured output frequency and output power.

consumption of the proposed VCO with the adaptive bias circuit is 6 mW at  $1.2-V\ V_{DD}$ . Table V highlights the details of a performance comparison with recently published class-C VCOs.

Table V. Comparison of published CMOS class-C VCO

| Ref.         | Topology /<br>Techniques for startup                      | Freq.<br>(GHz) | PN<br>(dBc/Hz)  | Core<br>Power<br>(mW) | FOM    | Proc. (nm) |

|--------------|-----------------------------------------------------------|----------------|-----------------|-----------------------|--------|------------|

| [14]         | Class-C /<br>None                                         | 4.9            | −130<br>@ 3M    | 1.3                   | 196    | 130        |

| [16]         | Class-B/C /<br>Aux. pair (free running)                   | 6.7            | −137<br>@ 2M    | 27                    | 188    | 55         |