#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

#### Ph.D. Dissertation

A Study on Energy-Efficient

Inductor Current Controls for

Maximum Energy Delivery in

Battery-free Buck Converter

무전원 벅 컨버터의 최대 에너지 전달을 위한 효율적인 인덕터 전류 제어에 관한 연구

by

Minbok Lee

February 2017

School of Electrical Engineering and Computer Science

College of Engineering

Seoul National University

# A Study on Energy-Efficient Inductor Current Controls for Maximum Energy Delivery in Battery-free Buck Converter

지도 교수 김 재 하

이 논문을 공학박사 학위논문으로 제출함 2017 년 2 월

> 서울대학교 대학원 전기·컴퓨터공학부 이 민 복

이민복의 박사 학위논문을 인준함 2017 년 2 월

| 위육 | <sup>원</sup> 장 | 정 덕 균 | (인) |

|----|----------------|-------|-----|

| 부위 | 원장             | 김 재 하 | (인) |

| 위  | 원              | 하 정 익 | (인) |

| 위  | 원              | 박 병 하 | (인) |

| 위  | 원              | 김 태 익 | (인) |

ABSTRACT I

#### **Abstract**

A discontinuous conduction mode (DCM) buck converter, which acts as a voltage regulator in battery-free applications, is proposed to maximize the energy delivery to the load system. In this work, we focus the energy loss problem during startup and steady-state operation of the buck converter, which severely limits the energy delivery. Especially, the energy loss problem arises from the fact that there is no constant power source such as a battery and the only a small amount of energy harvested from the ambient energy sources is available. To address such energy loss problem, this dissertation proposes optimal inductor current control techniques at each operation to greatly reduce the energy losses. First, a switching-based stepwise capacitor charging scheme is presented that can charge the output capacitor with constant inductor current during start-up operation. By switching the inductor with gradually incrementing duty-cycle ratios in a stepwise fashion, the buck converter can make the inductor current a constant current source, which can greatly reduce the start-up energy loss compared to that in the conventional capacitor charging scheme with a voltage source. Second, a variable on-time (VOT) pulse-frequencymodulation (PFM) scheme is presented that can keep the peak inductor current constant during steady-state operation. By adaptively varying the on-time according to the operating voltage conditions of the buck converter, it can suppress the voltage ripple and improve the power efficiency even with a small output capacitor. Third, an adaptive off-time positioning zero-crossing detector (AOP-ZCD) is presented that can adaptively position the turn-off timing of the low-side switch close to the zeroABSTRACT II

inductor-current timing by predicting the inductor current waveform without using a

power-hungry continuous-time ZCD. To demonstrate the proposed design concepts,

the prototype battery-free wireless remote switch including the piezoelectric energy

harvester and the proposed buck converter was fabricated in a 250 nm high-voltage

CMOS technology. It can harvest a total energy of 246 µJ from a single button press

action of a 300-mm<sup>2</sup> lead magnesium niobate-lead titanate (PMN-PT) piezoelectric

disc, and deliver more than 200 µJ to the load, which is sufficient to transmit a 4-

byte-long message via 2.4-GHz wireless USB channel over a 10-m distance. If such

battery-free application does not use the proposed buck converter, the energy losses

incurred at the buck converter would be larger than the energy harvested, and there-

fore it cannot operate with a single button-pressing action. Furthermore, thanks to

the proposed energy efficient buck converter, the battery-free wireless remote switch

can be realized by using a cheaper PZT piezoelectric source, which can achieve a

10× cost reduction.

**Keywords**: Buck converter, battery-free application, switching-based stepwise ca-

pacitor charging, variable on-time, adaptive off-time positioning zero-crossing de-

tector, piezoelectric, RF transmitter, battery-free wireless remote switch.

**Student Number : 2010-20852**

CONTENTS

# **Contents**

| ABSTRACT                                                   | I   |

|------------------------------------------------------------|-----|

| CONTENTS                                                   | Ш   |

| LIST OF FIGURES                                            | VII |

| LIST OF TABLES                                             | XI  |

| CHAPTER 1 INTRODUCTION                                     | 1   |

| 1.1 MOTIVATION                                             | 1   |

| 1.2 THESIS CONTRIBUTION AND ORGANIZATION                   | 6   |

| CHAPTER 2 OPERATION MODE AND OVERALL ARCHITECTURE          | 8   |

| 2.1 TOPOLOGY SELECTION                                     | 8   |

| 2.2 PRINCIPLE OF OPERATION                                 | 11  |

| 2.2.1 BASIC OPERATION IN CCM                               | 12  |

| 2.2.2 BASIC OPERATION IN DCM                               | 15  |

| 2.3 OPERATION MODE                                         | 17  |

| 2.4 OVERALL ARCHITECTURE                                   | 19  |

| CHAPTER 3 OPTIMAL INDUCTOR CURRENT CONTROLS FOR            |     |

| MAXIMUM ENERGY DELIVERY                                    | 23  |

| 3.1 CONSTANT INDUCTOR CURRENT CONTROL WITH SWITCHING-BASED |     |

| STEPWISE CAPACITOR CHARGING SCHEME                         | 24  |

| 3.1.1 CONVENTIONAL CHARGING SCHEME WITH A SWITCH           | 24         |

|------------------------------------------------------------|------------|

| 3.1.2 ADIABATIC STEPWISE CHARGING                          | 27         |

| 3.1.3 PROPOSED START-UP SCHEME                             | 29         |

| 3.2 CONSTANT INDUCTOR PEAK CURRENT CONTROL WITH VARIAB     | LE ON-TIME |

| PFM SCHEME                                                 | 35         |

| 3.2.1 BASIC OPERATION OF PFM BUCK CONVERTER                | 35         |

| 3.2.2 CONSTANT ON-TIME PFM SCHEME                          | 39         |

| 3.2.3 VARIABLE ON-TIME PFM SCHEME                          | 41         |

| 3.3 INDUCTOR CURRENT PREDICTION WITH ADAP-TIVE OFF-TIME P  | OSITIONING |

| ZCD (AOP-ZCD)                                              | 44         |

| 3.3.1 Previous Sampling-Based ZCD                          | 44         |

| 3.3.2 PROPOSED ADAPTIVE OFF-TIME POSITIONING ZCD           | 47         |

| CHAPTER 4 CIRCUIT IMPLEMENTATION                           | 49         |

| 4.1 CIRCUIT IMPLEMENTATION OF SWITCHING-BASED STEPWISE CA  | APACITOR   |

| Charger                                                    | 49         |

| 4.1.1 VOLTAGE DETECTOR (VD)                                | 50         |

| 4.1.2 DIGITAL PULSE WIDTH MODULATOR (DPWM)                 | 52         |

| 4.1.3 PROGRAMMABLE DUTY-CYCLE CONTROLLER (DCC)             | 55         |

| 4.1.4 SWITCHED CAPACITOR (SC) STEP-DOWN CONVERTER          | 57         |

| 4.2 CIRCUIT IMPLEMENTATION OF VARIABLE ON-TIME PULSE GEN   | ERATOR59   |

| 4.3 CIRCUIT IMPLEMENTATION OF ADAPTIVE OFF-TIME POSITIONIN | NG ZCD64   |

| 4.2.1 An appropriate Oper Thurs (A OT) Provide Course and  | 61         |

| 4.3.1 Adaptive Off-Time (AOT) Pulse Generator              | 04         |

*CONTENTS* V

| CHAPTER 5 MEASUREMENT RESULTS OF PROPOSED BUCK                 |            |

|----------------------------------------------------------------|------------|

| CONVERTER                                                      | 70         |

| 5.1 SWITCHING-BASED STEPWISE CAPACITOR CHARGER                 | 71         |

| 5.2 STEADY-STATE PERFORMANCE WITH VOT PULSE GENERATOR AND AOP  | <b>'</b> _ |

| ZCD                                                            | 61         |

| CHAPTER 6 REALIZATION OF BATTERY-FREE WIRELESS REMOT           | Έ          |

| SWITCH                                                         | 71         |

| 6.1 KEY BUILDING BLOCKS OF BATTERY-FREE WIRELESS REMOTE SWITCH | 74         |

| 6.2 PIEZOELECTRIC ENERGY HARVESTER WITH P-SSHI RECTIFIER       | 86         |

| 6.2.1 ANALYSIS ON SINGLE-PULSED ENERGY HARVESTING              | 88         |

| 6.2.2 Proposed Piezoelectric Energy Harvester                  | 91         |

| 6.2.3 CIRCUIT IMPLEMENTATION                                   | 93         |

| 6.3 MEASUREMENT RESULTS OF BATTERY-FREE WIRELESS SWITCH        | 96         |

| CHAPTER 7 CONCLUSION                                           | 101        |

| BIBLIOGRAPHY                                                   | 103        |

| 초록                                                             | 110        |

LIST OF FIGURES VI

# **List of Figures**

| FIG. 1.1 SIMPLE SCHEMATIC OF THE BATTERY-FREE APPLICATION.                       | 2         |

|----------------------------------------------------------------------------------|-----------|

| FIG. 1.2 SPECIFIC OPERATION OF THE VOLTAGE REGULATOR AND ITS DESIGN ISSUES IN B. | AT-       |

| TERY-FREE APPLICATIONS.                                                          | 3         |

| FIG. 1.3 SCHEMATIC OF SYNCHRONOUS DCM BUCK CONVERTER AND ITS KEY WAVE-FOR        | RMS       |

| WHEN M <sub>N</sub> TURNS OFF EARLY OR LATE.                                     | 4         |

| FIG. 2.1 TOPOLOGY COMPARISON; (A) BUCK-BOOST, (B) BUCK.                          | 9         |

| Fig. 2.2 Equivalent circuit diagrams of CCM buck converter at (a) ON state .     | AND       |

| (B) OFF STATE AND ITS KEY WAVEFORMS.                                             | 13        |

| FIG. 2.3 CAPACITOR CURRENT WAVEFORM IN STEADY-STATE OPERATION.                   | 14        |

| FIG. 2.4 EQUIVALENT CIRCUIT DIAGRAMS OF DCM BUCK CONVERTER AND ITS KEY WAV       | Е-        |

| FORMS                                                                            | 15        |

| FIG. 2.5 (A) SIMPLE BLOCK DIAGRAM OF THE BUCK CONVERTER AND ITS CONTROLLER, A    | AND (B)   |

| KEY OPERATING WAVEFORMS.                                                         | 18        |

| FIG. 2.6 OVERALL ARCHITECTURE OF THE PROPOSED BUCK CONVERTER WITH A SWITCHE      | NG-       |

| BASED STEPWISE COUT CHARGING SCHEME AND A PFM CONTROL SCHEME INCLU               | DING      |

| A VARIABLE ON-TIME (VOT) PULSE GENERATOR AND AN ADAPTIVE OFF-TIME                |           |

| POSITIONING ZERO-CROSSING DETECTOR (AOP-ZCD).                                    | 21        |

| FIG. 3.1 CONVENTIONAL START-UP SCHEME WITH A SIMPLE SWITCH MSTART-UP             | 25        |

| Fig. 3.2 Energy losses versus C <sub>out</sub> .                                 | 26        |

| FIG. 3.3 STEPWISE CHARGING THE CAPACITOR WITH N TANK CAPACITORS.                 | 28        |

| FIG. 3.4 DESIGN CONCEPT OF THE PROPOSED CAPACITOR CHARGING SCHEME WITH A CUR     | <b>≀-</b> |

| RENT SOURCE                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------|

| FIG. 3.5 SCHEMATIC OF THE SWITCHING-BASED STEPWISE CAPACITOR SCHEME AND ITS                                              |

| OPERATING WAVEFORMS                                                                                                      |

| Fig. 3.6 Schematic of the loss components in the buck converter: $R_s,R_L,$ and the                                      |

| PARASITIC CAPACITANCES IN THE SWITCHING NODES                                                                            |

| Fig. 3.7 Start-up energy loss ( $E_{\text{loss,st}} + E_{\text{loss,Cout}}$ ) in change with N and $F_{\text{sw}},$ when |

| CHARGING (A) 4.7-UF AND (B) 2.2-UF CAPACITORS                                                                            |

| Fig. 3.8 $E_{\text{loss,st}}$ comparison between the conventional and the proposed start-up                              |

| SCHEME. 34                                                                                                               |

| FIG. 3.9 SIMPLE SCHEMATIC OF THE BUCK CONVERTER WITH PFM CONTROL OPERATING IN                                            |

| DCM AND ITS KEY WAVEFORMS                                                                                                |

| Fig. 3.10 Inductor current waveforms under constant on-time PFM scheme; (a)                                              |

| SWITCHING FREQUENCY INCREASE AT LOW $V_{\mbox{\tiny IN}}$ , (B) SLOW SWITCHING FREQUENCY WITH                            |

| LARGER $T_{\text{on}}$ at low $V_{\text{in}}$ and (c) resulting large voltage ripple at high $V_{\text{in}},,40$         |

| FIG. 3.11 PROPOSED VARIABLE TON CURVE TO REDUCE COUT AND IMPROVE THE POWER                                               |

| EFFICIENCY. 4                                                                                                            |

| Fig. 3.12 Performance comparison between the variable $T_{\mbox{\tiny ON}}$ (VOT) and the                                |

| CONSTANT $T_{\text{on}}$ (COT); (a) $T_{\text{on}}$ value, (b) inductor peak current ( $I_{\text{L,peak}}$ ), (c)        |

| SWITCH-ING FREQUENCY ( $F_{SW}$ ) AND (D) VOLTAGE RIPPLE ( $V_{RIPPLE}$ )                                                |

| FIG. 3.13 BLOCK DIAGRAM OF (A) THE CONTINUOUS-TIME ZCD AND (B) THE SAMPLING-BASED                                        |

| ZCD                                                                                                                      |

| FIG. 3.14 BLOCK DIAGRAM OF THE PROPOSED AOT-ZCD. 48                                                                      |

| FIG. 4.1 (A) SCHEMATIC OF THE LEAKAGE-BASED VOLTAGE DETECTOR AND (B) THE SIMULA-                                         |

| TION RESULT OF THE DETECTION VOLTAGE                                                                                     |

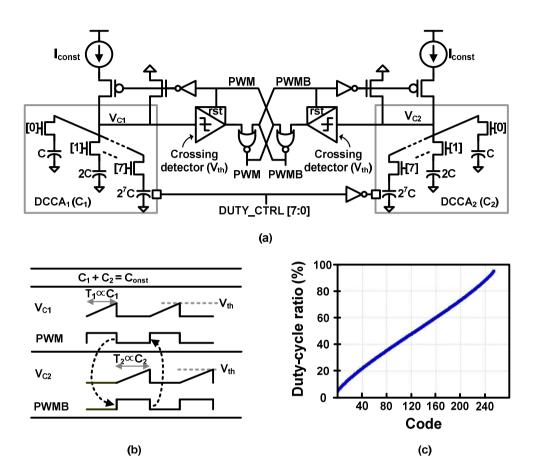

| FIG. 4.2 (A) CIRCUIT IMPLEMENTATION OF DPWM, (B) ITS KEY WAVEFORMS, AND (C)                                      |

|------------------------------------------------------------------------------------------------------------------|

| SIMULATION RESULT OF THE DUTY-CYCLE RATIO VERSUS DUTY_CTRL [7:0]53                                               |

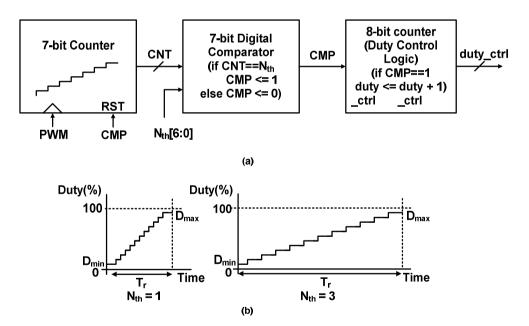

| FIG. 4.3 (A) BLOCK DIAGRAM OF THE PROGRAMMABLE DUTY-CYCLE CONTROLLER AND (B)                                     |

| THE EXAMPLE TRAJECTORY OF THE DUTY-CYCLE DURING THE CHARGING OPERATION                                           |

| WHEN $N_{TH} = 1$ AND $N_{TH} = 3$ .                                                                             |

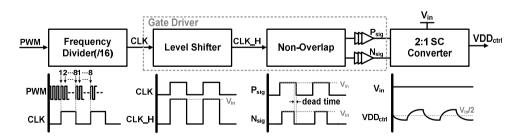

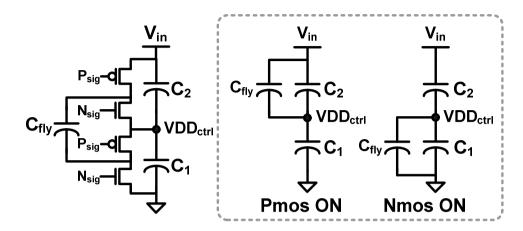

| Fig. 4.4 Block diagram of 2:1 switched-capacitor (SC) step-down converter in-                                    |

| CLUDING THE GATE DRIVER CIRCUIT AND ITS KEY WAVEFORMS                                                            |

| Fig. 4.5 Circuit implementation of the 2:1 switched-capacitor (SC) converter 58                                  |

| FIG. 4.6 SIMPLE BLOCK DIAGRAM OF THE VARIABLE ON-TIME (VOT) PULSE GENERATOR AND                                  |

| ITS KEY WAVEFORMS                                                                                                |

| FIG. 4.7 CIRCUIT IMPLEMENTATIONS OF (A) THE PREVIOUS VOT PULSE GENERATOR AND ITS                                 |

| KEY WAVEFORMS AND (B) THE PROPOSED ONES. 60                                                                      |

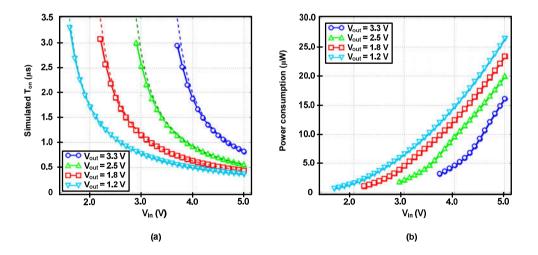

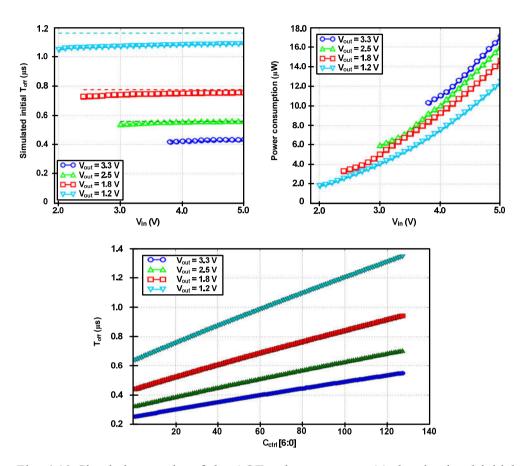

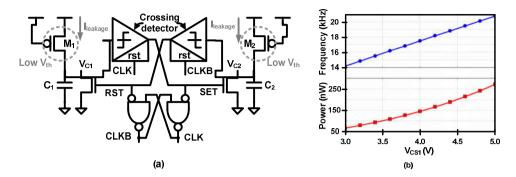

| FIG. 4.8 SIMULATION RESULTS OF THE VOT PULSE GENERATOR: (A) THE SIMULATED TON AND                                |

| (B) ITS POWER CONSUMPTION FOR VARIOUS $V_{\mbox{\tiny IN}}$ AND $V_{\mbox{\tiny OUT}}$ CONDITIONS                |

| FIG. 4.9 CIRCUIT IMPLEMENTATION OF THE PROPOSED AOT PULSE GENERATOR AND ITS KEY                                  |

| WAVEFORMS. 65                                                                                                    |

| FIG. 4.10 SIMULATION RESULTS OF THE AOT PULSE GENERATOR: (A) THE SIMULATED INITIAL                               |

| $T_{\text{OFF}},$ (B) its power consumption for various $V_{\text{in}}$ and $V_{\text{out}}$ conditions, and (c) |

| THE SIMULATED $T_{\text{OFF}}$ WITH A CHANGING DIGITAL CODE $C_{\text{CTRL}}$ [6:0]66                            |

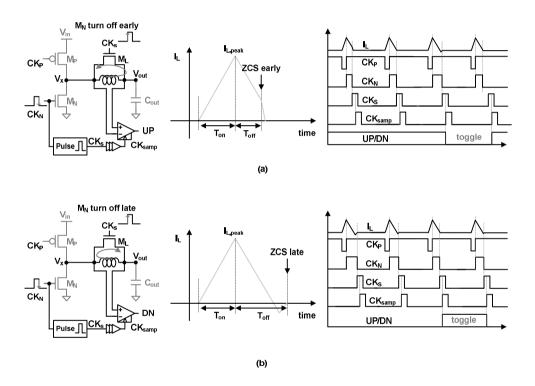

| Fig. 4.11 Timing error detector and the timing calibration waveforms when (a) $M_{\rm N}$                        |

| TURNS OFF EARLY (I.E., ZCS-EARLY CASE) AND (B) $M_{\text{N}}$ TURNS OFF LATE (I.E., ZCS-                         |

| LATE CASE)68                                                                                                     |

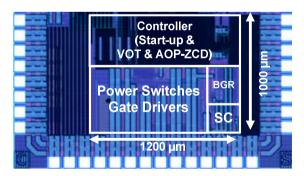

| FIG. 5.1 DIE PHOTOGRAPH. 70                                                                                      |

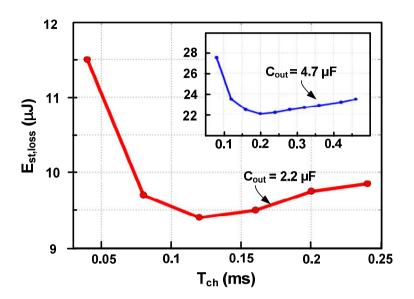

| Fig. 5.2 Measured start-up energy loss in change with $T_{\text{ch}}$ . When charging 2.2-uf                     |

| $C_{\text{out}}$ and 4.7-uf $C_{\text{out}}$                                                                                                         | 2 |

|------------------------------------------------------------------------------------------------------------------------------------------------------|---|

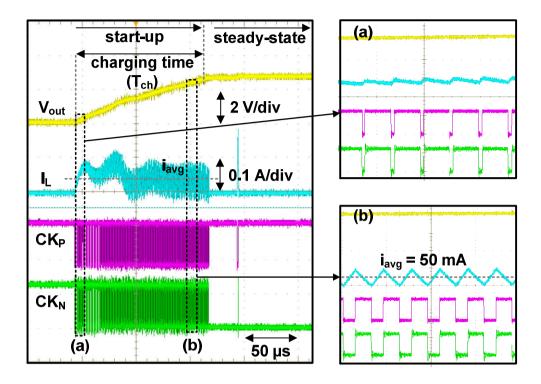

| FIG. 5.3 MEASURED KEY WAVEFORMS DURING START-UP OPERATION                                                                                            | 3 |

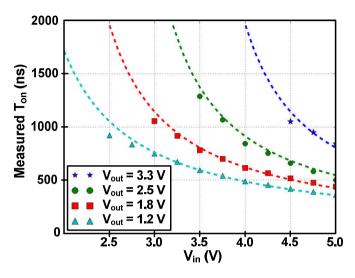

| Fig. 5.4 Measurement of the generated on-time ( $T_{\text{on}}$ ) from the variable on-time                                                          |   |

| PULSE GENERATOR                                                                                                                                      | 5 |

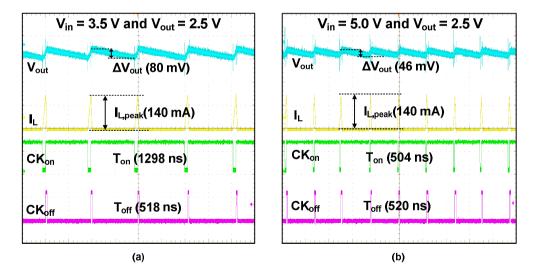

| Fig. 5.5 Measured waveforms at difference input voltages ( $V_{\text{in}}$ = 3.5V, 5V) and at                                                        |   |

| 2.5 V V <sub>OUT</sub>                                                                                                                               | 5 |

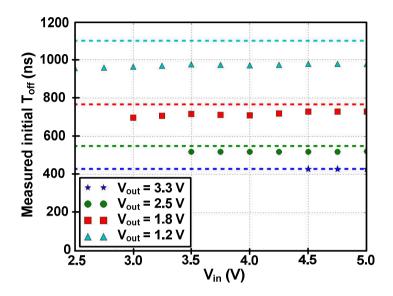

| Fig. 5.6 Measurement of the generated off-time $(T_{\text{off}})$ from the adaptive off-time                                                         |   |

| PULSE GENERATOR                                                                                                                                      | 6 |

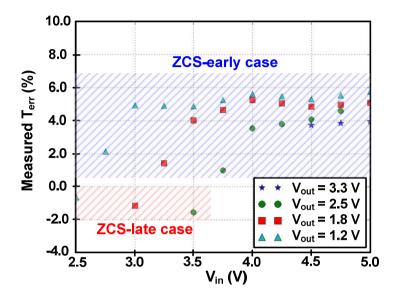

| Fig. 5.7 Measured timing error ( $T_{\text{err}}$ ) over wide ranges of input and output voltage                                                     | E |

| CONDITIONS                                                                                                                                           | 7 |

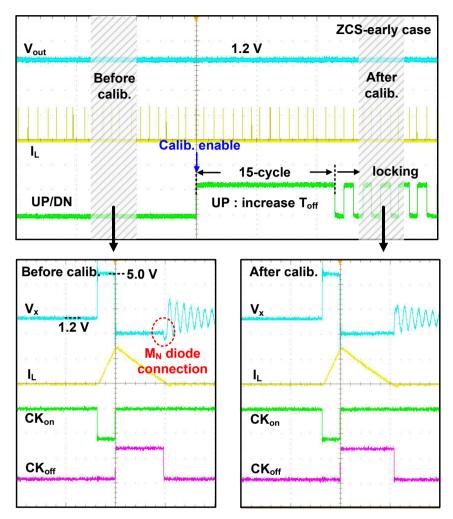

| Fig. 5.8 Measured transient waveforms of $T_{\text{err}}$ compensation for the worst ZCS-                                                            |   |

| EARLY CASE WHEN CONVERTING 5.0 V TO 1.2 V                                                                                                            | 8 |

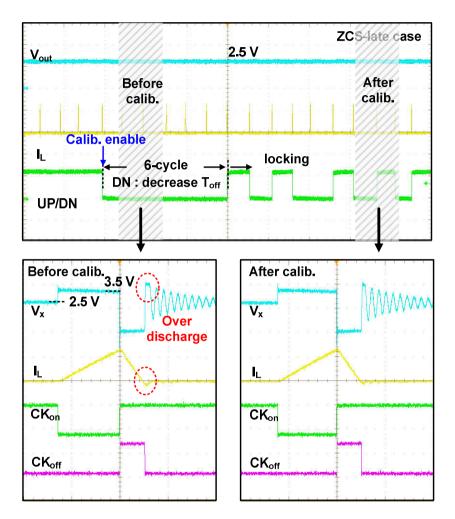

| Fig. 5.9 Measured transient waveforms of $T_{\text{err}}$ compensation for the worst ZCS-                                                            |   |

| LATE CASE WHEN CONVERTING 3.5 V TO 2.5 V                                                                                                             | 9 |

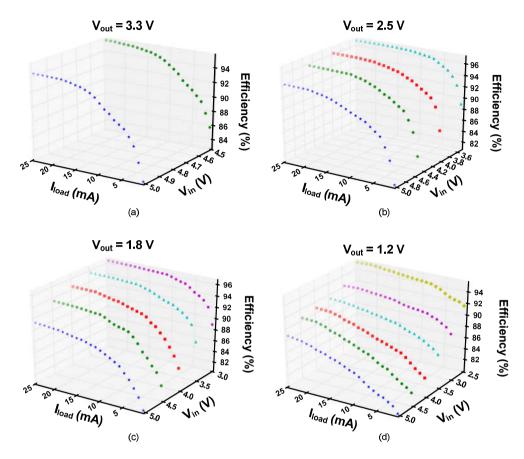

| FIG. 5.10 MEASURED POWER EFFICIENCY AT THE STEADY STATE FOR VARIOUS LOAD                                                                             |   |

| CURRENTS $I_{LOAD}$ , $V_{IN}$ , AND $V_{OUT}$ : (A) $V_{OUT} = 3.3 \text{ V}$ , (B) $V_{OUT} = 2.5 \text{ V}$ , (C) $V_{OUT} = 1.8 \text{ V}$ , (D) |   |

| $V_{OUT} = 1.2 \text{ V}.$ 80                                                                                                                        | 0 |

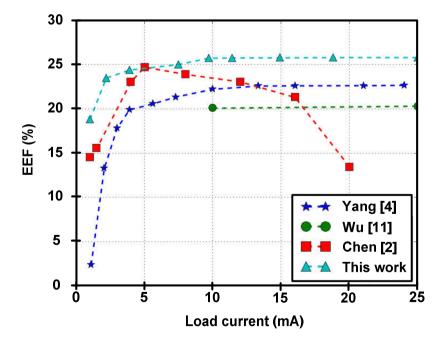

| FIG. 5.11 EFFICIENCY ENHANCEMENT FACTOR (EEF) COMPARISON                                                                                             | 2 |

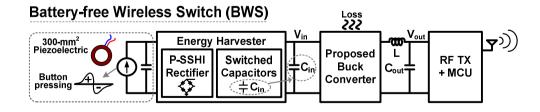

| Fig. 6.1 Key building blocks of the battery-free wireless remote switch (BWS) 85                                                                     | 5 |

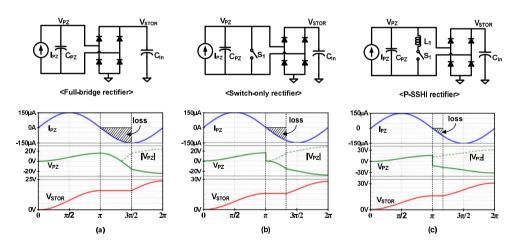

| FIG. 6.2 THREE EXAMPLES OF PIEZOELECTRIC ENERGY-HARVESTING CIRCUITS AND THEIR KEY                                                                    |   |

| WAVEFORMS: (A) FBR, (B) SWITCH-ONLY RECTIFIER (SOR), AND (C) P-SSHI RECTI-                                                                           |   |

| FIER                                                                                                                                                 | 6 |

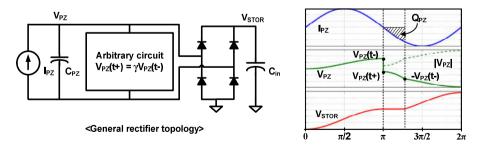

| Fig. 6.3 General rectifier topology with an arbitrary voltage changer                                                                                | 8 |

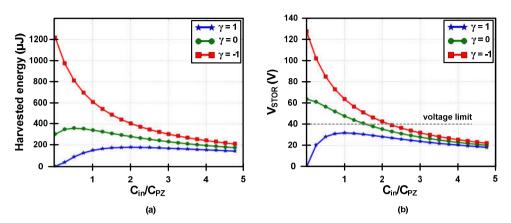

| Fig. 6.4 (a) Theoretical Harvesting energy, and (b) post-harvesting-voltage $V_{\text{STOR}}$                                                        |   |

LIST OF FIGURES X

| ACCORDING TO THE VALUE OF FLIPPING COEFFICIENT ( $\Gamma$ ) AND THE CAPACITOR RATIO                                      |

|--------------------------------------------------------------------------------------------------------------------------|

| $C_{\text{IN}}/C_{PZ}$ of example topologies of an FBR ( $\Gamma$ = 1), SOR ( $\Gamma$ = 0), P-SSHIR ( $\Gamma$ = -1).90 |

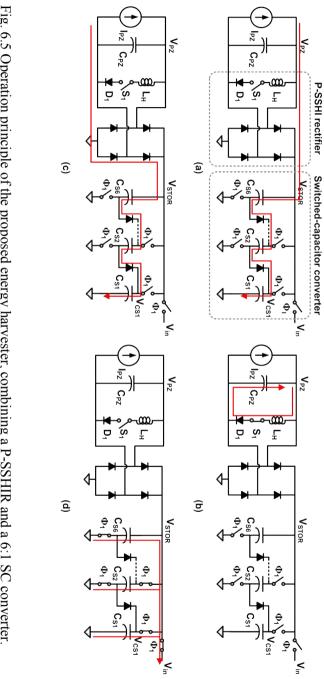

| Fig. 6.5 Operation principle of the proposed energy harvester, combining a P-                                            |

| SSHIR AND A 6:1 SC CONVERTER. 92                                                                                         |

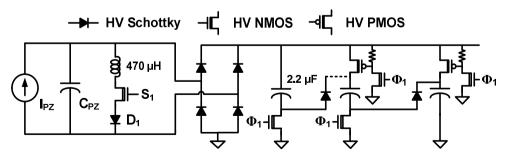

| Fig. $6.6$ Detailed circuit implementation of the proposed harvesting circuit93                                          |

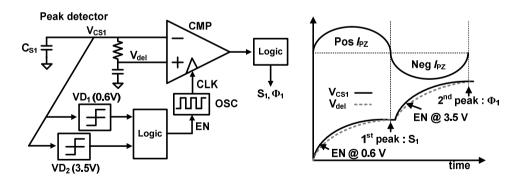

| Fig. 6.7 Timing control circuit including a clocked comparator, an oscillator,                                           |

| AND TWO VOLTAGE-LEVEL DETECTORS. 94                                                                                      |

| FIG. 6.8 (A) SCHEMATIC OF ULTRA-LOW-POWER RELAXATION OSCILLATOR AND (B) SIMULA-                                          |

| TION RESULT OF FREQUENCY AND POWER CONSUMPTION. 95                                                                       |

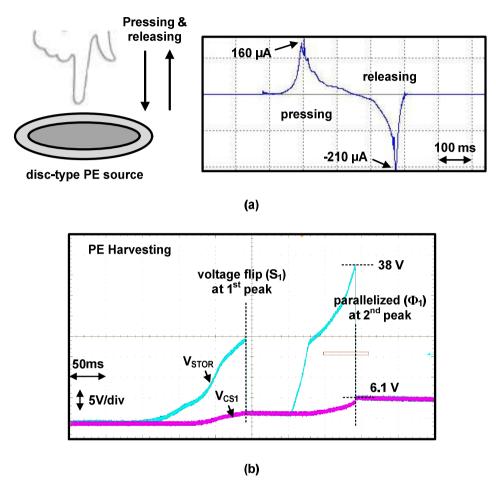

| Fig. 6.9 (a) Measured $I_{PZ}$ when a $300\text{-}\text{mm}^2$ PMN-PT piezoelectric disc button is                       |

| PRESSED AND RELEASED BY A USER, AND (B) MEASURED VOLTAGE WAVEFORMS 97                                                    |

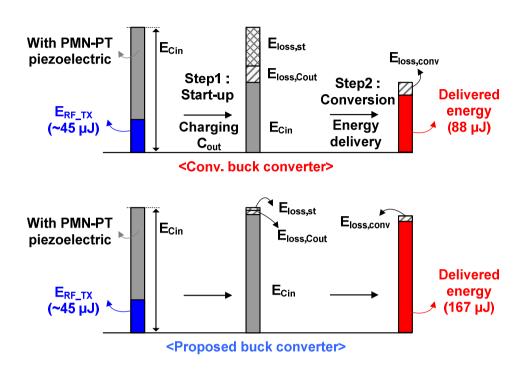

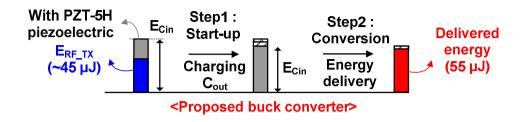

| Fig. 6.10 Energy flows and losses during start-up and conversion operation of                                            |

| THE (A) CONVENTIONAL AND (B) PROPOSED BUCK CONVERTER98                                                                   |

| FIG. 6.11 ENERGY FLOWS AND LOSSES DURING START-UP AND CONVERSION OPERATION OF                                            |

| THE PROPOSED BUCK CONVERTER WITH PZT-5H PIEZOELECTRIC DISC99                                                             |

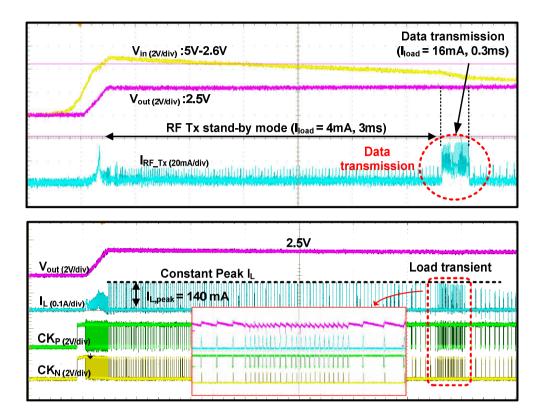

| Fig. 6.12 Measured waveforms for RF transmitter operating in active mode with                                            |

| PZT-5H                                                                                                                   |

LIST OF TABLES XI

# **List of Tables**

| T 5 1 D-     |                                        | 0.1 |

|--------------|----------------------------------------|-----|

| TARLE 5 L PI | ERFORMANCE COMPARISON WITH PRIOR WORKS | 81  |

# Chapter 1

#### Introduction

#### 1.1 Motivation

With active researches in energy harvesting system [1]–[4], there is a growing demand for battery-free applications [4], [26]–[28] such as wireless switches and sensors. While these applications utilize the energy existing in environment, for example kinetic motion [35], pressure [26]–[30], light [36] and differences in temperature [38], combining energy harvesters and ultra-low power wireless applications creates the battery-free solutions. Such battery-free applications can save maintenance and installation costs for use in buildings, smart home and industrial applications as well as for the Internet of Things (IoTs). However, the energy harvested from such ambient energy sources is limited and the large energy losses incurred during the system's operation make it difficult to supply enough energy to meet the

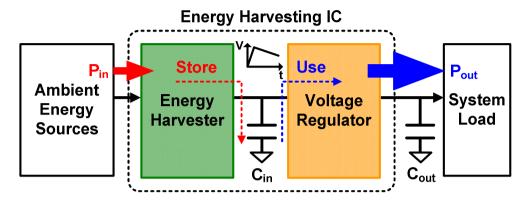

Fig. 1.1. Simple schematic of the battery-free application.

requirements for successful data transmission. This dissertation proposes an energyefficient voltage regulator circuit and its optimal inductor current control techniques to deliver the largest possible energy while a small amount of energy harvested is available.

A simple schematic of the battery-free system is illustrated in Fig. 1.1. It consists of an ambient energy source, energy harvester, storage capacitor ( $C_{in}$ ), voltage regulator and load system. When the ambient energy sources such as a solar cell, piezoe-lectric transducer and thermoelectric generator (TEG) generate the electric charge, the energy harvester collect this charge in  $C_{in}$ , instead of the battery. Since the generated power from the ambient energy sources (i.e,  $P_{in}$ ) is smaller than the required power of the load system (i.e.,  $P_{out}$ ) in most cases, the energy should be collected in  $C_{in}$  during the sufficient time before operating the voltage regulator. After the enough energy is charged in  $C_{in}$ , the voltage regulator begins charging its output capacitor ( $C_{out}$ ) to a desired output voltage using the energy stored in  $C_{in}$  (i.e., start-up operation), and then delivers this energy to the load (i.e., RF transmitter) at a

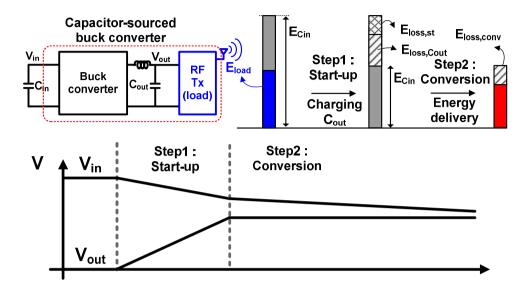

Fig. 1.2. Specific operation of the voltage regulator and its design issues in battery-free applications.

steady output voltage. In this study, we focus on the voltage regulator because its energy loss is dominant, thereby significantly limiting the energy delivery.

The challenges in designing such a voltage regulator arise from the energy losses incurred during the start-up operation with fully discharged output capacitor ( $C_{out}$ ) and during the steady-state operation with the large quiescent current in control circuits. Fig. 1.2 illustrates the specific operation of the voltage regulator and its design issues in battery-free applications. Note that the small input capacitor ( $C_{in}$ ) is required to collect the large energy with a high voltage in energy harvesting process [35], [40], which calls for the step-down buck converter topology as a voltage regulator to down-convert the voltage. First, the large energy is dissipated at start-up operation of the buck converter. Specifically, to charge  $C_{out}$  from zero to the desired

output

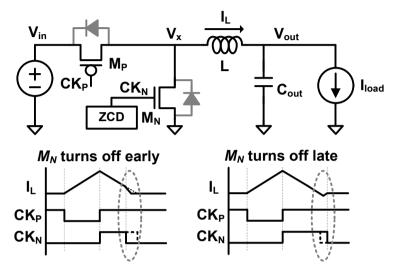

Fig. 1.3. Schematic of synchronous DCM buck converter and its key waveforms when  $M_N$  turns off early or late.

voltage ( $V_{\text{out}}$ ), the capacitor charging loss is incurred, which contains two losses; one is the energy dissipation at the resistive component ( $E_{\text{loss,st}}$ ) such as a switch, and the other is the stored energy in  $C_{\text{out}}$  (i.e.  $E_{\text{loss,Cout}} = 0.5C_{\text{out}}V_{\text{out}}^2$ ). Second, the large energy loss ( $E_{\text{loss,conv}}$ ) is also dissipated during steady-state operation. Specifically, to regulate  $V_{\text{out}}$  at a steady voltage, the large quiescent current of the buck converter's controller is incurred. Especially, the power efficiency of a discontinuous conduction mode (DCM) buck converter is mainly limited by the precision of its zero-crossing detector (ZCD), which controls and generates the timing signal to turn off the low-side switch  $M_N$  when the inductor current becomes zero. For instance, the timing error between the actual turn-off timing of  $M_N$  and the zero-inductor-current timing can incur a large power loss, either due to the body diode conduction when

$M_N$  turns off too early or due to the inverse inductor current when  $M_N$  turns off too late, as shown in Fig. 1.3. To circumvent these losses, the ZCDs require high precision in detecting this timing error. However, the high-precision ZCDs employing a continuous-time comparator [4], [8]–[11] incur a large static power consumption (e.g., ~250  $\mu$ W [4]) in operation.

#### 1.2 Thesis Contribution and Organization

To address the aforementioned challenges in both start-up and steady-state operation, this dissertation proposes optimal inductor current control techniques for each operation.

First, in order to reduce the resistive loss ( $E_{loss,st}$ ) at start-up operation, a switching-based stepwise charging technique [39] is proposed that can charge the capacitor with a current source; this can be realized by keeping the average inductor current constant and operating the buck converter in continuous conduction mode (CCM) with linearly incrementing duty-cycle ratios in a stepwise fashion.

Second, in order to minimize the required energy to charge the capacitor ( $E_{loss,Cout}$ ) at start-up operation, a variable on-time pulse-frequency modulation (PFM) control [4] is proposed that can make use of a small  $C_{out}$  without degrading the steady-state performance such as voltage ripple and power efficiency; this can be realized by adaptively varying the on-time of PFM pulse with inversely proportional to the voltage difference between input and output (i.e.,  $T_{on} \sim 1/(V_{in} - V_{out})$ ), which can keep the peak inductor current constant.

Lastly, in order to reduce the controller loss ( $E_{loss,conv}$ ) at steady-state operation, an adaptive off-time positioning ZCD (AOP-ZCD) is proposed, which is a sampling-based ZCD [1]–[3] with an adaptive off-time pulse generator that can achieve both high-precision in timing detection and low-power consumption in operation for wide ranges of input and output voltage conditions; this can be realized by the inductor current waveform prediction aided with the constant peak inductor current control.

This thesis is organized as follows. Chapter 2 describes the overall architecture of the proposed buck converter for battery-free applications. Specifically, the operation mode, overall architecture and building blocks of the proposed buck converter will be described. Chapter 3 provides the design concepts of the proposed optimal inductor current control techniques based on the detailed analysis. Specifically, energy savings from the switching-based start-up scheme [39], the variable on-time (VOT) PFM scheme [4] and the adaptive off-time positioning zero-crossing detector (AOP-ZCD) scheme will be described. Chapter 4 explains the detailed circuit implementation of the building blocks and shows their simulation results. Chapter 5 provides the measurement results of the proposed buck converter and Chapter 6 demonstrates the effectiveness of our approaches by applying the proposed buck converter to the battery-free wireless switch application.

# Chapter 2

# **Operation Mode and Overall Architecture**

After discussing the motivation and design issues of this work in Chapter 1, this chapter describes the operation mode and the overall architecture of the proposed buck converter for batter-free applications. The proposed buck converter employs both a continuous conduction mode (CCM) and discontinuous conduction mode (DCM) control schemes at each start-up and steady-state operation, respectively, to achieve maximum energy delivery. The principle of each control scheme will be discussed in detail in following sections.

# 2.1 Topology Selection

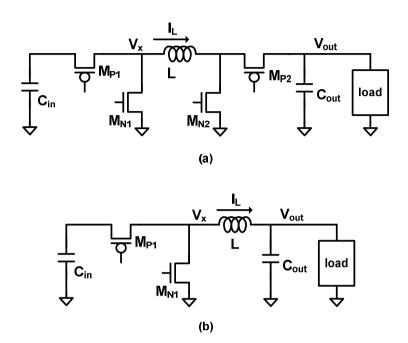

To down-convert the voltage, the step-down converter topology is required such as a buck converter or buck-boost converter as shown in Fig. 2.1. Considering that

Fig. 2.1. Topology Comparison; (a) buck-boost, (b) buck.

the aim of the voltage regulator is delivering the maximum energy stored in the input capacitor to the load, the buck-boost topology could be preferable because it can operate even though the input voltage is lower than the output voltage, delivering more energy. However, this topology requires additional power switches  $M_{P2}$  and  $M_{N2}$  as shown in Fig. 2.1 (a), which incurs the larger conduction loss and switching loss. To reduce the conduction loss, the large-sized power switches are required; however, they occupy large silicon area. On the other hands, the simple buck topology as shown in Fig. 2.1 (b) does not require the additional power switches and hence this topology can achieve high efficiency and small silicon area. However, the buck topology can deliver the energy only when the input voltage is higher than the output voltage. Therefore, the rest of energy in the input capacitor could be wasted.

The topology chosen is the buck converter. Because the battery-free applications are realized by combining an energy harvester and ultra-low-power wireless application as described in Chapter 1.1, low supply voltages of the load systems (e.g., 1.0 V, 1.2 V) are used in practice. This means that the advantage of energy delivery in buck-boost topology is lost when the output voltage is low enough. Although the buck topology can deliver slightly smaller amount of energy, this topology can be more superior in ultra-low-power battery-free application because it can achieve high efficiency and reduce area.

### 2.2 Principle of Operation

The basic operation of the buck converter is stepping down the DC voltage efficiently by switching an inductor. In synchronous buck converter, two switches are used to control the inductor current and their switching signals determine the performance of the buck converter. Specifically, according to the duty-cycle ratios and switching frequency of switching signals, the performance such as current/voltage ripples and power efficiency can be changed and hence the optimal current controls should be analyzed first before designing. In buck converter, there are two operation modes; continuous conduction mode (CCM) and discontinuous conduction mode (DCM). Continuous inductor current mode is characterized by current flowing continuously in the inductor during the entire switching cycle in steady-state operation. Discontinuous inductor current mode is characterized by the inductor current being zero for a portion of the switching cycle. The two different modes will be discussed in this subsection.

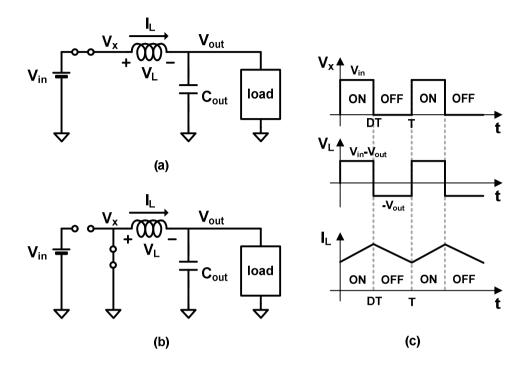

#### 2.2.1 Basic Operation in CCM

In continuous conduction mode, the buck power stage assumes two states per switching cycle. The ON state is when  $M_P$  turns on and  $M_N$  turns off. The OFF state is when  $M_P$  turns off and  $M_N$  turns on. The circuit diagram for each of the two states is shown in Fig 2.2. At ON state, the high-side switch turns on and the applied voltage across the inductor is the voltage difference between input and output (i.e.,  $V_L = V_{in} - V_{out}$ ) during DT, where D is a duty-cycle ratio of the switching signal (0 < D < 1) and T is a switching period. Because the voltage across the inductor  $V_L$  is a positive value, the inductor current increases with a slope of  $(V_{in} - V_{out})/L$ , where L is an inductance. At OFF state, the low-side switch turns on and the applied voltage across the inductor is the output voltage (i.e.,  $V_L = -V_{out}$ ) during  $(1-D) \cdot T$ . Because the voltage across the inductor  $V_L$  is a negative value, the inductor current decreases with a slope of  $-V_{out}/L$ . In steady-state operation, the amount of increase and decrease in inductor current should be same as expressed in (2.1). From this equation, we can find that the ratio between input and output voltage in CCM is proportional to the duty-cycle ratio.

$$\frac{V_{in} - V_{out}}{L}DT = \frac{V_{out}}{L}(1 - D)T \quad \Rightarrow \frac{V_{out}}{V_{in}} = D$$

(2.1)

In other words, since the pulsed voltage  $V_x$  is filtered by a low-pass L/C filter to generate a DC voltage  $V_{\text{out}}$ , the average value of  $V_x$  equals to  $V_{\text{out}}$ . Ideally, if an inductor (L) and a capacitor ( $C_{\text{out}}$ ) is large enough, a DC output voltage is generated and its voltage level varies with proportional to D.

However, because the inductance and capacitance values are finite, their non-

Fig. 2.2. Equivalent circuit diagrams of CCM buck converter at (a) ON state and (b) OFF state and its key waveforms.

idealities incur the current/voltage ripples. The maximum/minimum current  $I_{\text{max}}$  and  $I_{\text{min}}$  can be induced as (2.2), respectively, where  $I_{\text{avg}}$  is an average current (i.e.,  $I_{\text{avg}} = V_{\text{out}}/R_{\text{load}}$ ).

$$I_{max} = I_{avg} + \frac{V_{in}D(1-D)T}{2L}$$

$$I_{min} = I_{avg} - \frac{V_{in}D(1-D)T}{2L}$$

(2.2)

Therefore, the current ripple ( $\Delta I_L = (I_{\text{max}} - I_{\text{min}})/2$ ) can be calculated. Since the AC component of the inductor current flows through the output capacitor, the capacitor

Fig. 2.3. Capacitor current waveform in steady-state operation.

current ( $I_c$ ) can be plotted as shown in Fig. 2.3 and it generates the output voltage ripple ( $\Delta V_{\rm out}$ ), which can be induced as (2.3).

$$\Delta V_{out} = \frac{1}{C} \cdot \Delta I_L \cdot \frac{T}{2} = \frac{V_{in}(1 - D)D \cdot T^2}{8LC}$$

(2.3)

From (2.3), in order to minimize the voltage ripple, a fast switching frequency, a low input voltage, and large inductance and capacitance values are required.

#### 2.2.2 Basic Operation in DCM

In discontinuous conduction mode, the buck power stage assumes three states per switching cycle as described in Fig.2.4. While the principle of operation of DCM buck converter almost same with that of the CCM buck converter as shown in Fig. 2.4 (a) and (b), there is an additional states (i.e., zero-inductor-current state) as described in Fig. 2.4 (c). When the high-side switch turns on, the inductor current increases with a slope of  $(V_{in} - V_{out})/L$  and when the low-side switch turns on the inductor current decreases with a slope of  $-V_{out}/L$  until the inductor current becomes zero. After this time, the stored charge in the output capacitor is transferred

Fig. 2.4. Equivalent circuit diagrams of DCM buck converter and its key waveforms.

.

to the load. In steady-state, the amount of increase and decrease in inductor current should be same as expressed in (2.4).

$$\frac{V_{in} - V_{out}}{L}DT = \frac{V_{out}}{L}(D_A - D)T \quad \Rightarrow \frac{V_{out}}{V_{in}} = \frac{D}{D_A}$$

(2.4)

Actually, the low-side switch turn-on time (i.e.,  $D_AT - DT$ ) is determined by the inductor peak current value and discharging slope.

$$D_{A}T - DT = \frac{I_{L,peak} \cdot L}{V_{cut}}$$

(2.5)

From the fact that the charge transferred to the load in one switching cycle equals to the area of triangle of inductor current,  $D_A$  can be induced as (2.6).

$$D_A = \frac{2I_{load}}{I_{L,peak}} \tag{2.6}$$

From (2.5) and (2.6),  $D_A$  can be induced as function of switching period (T), inductance(L), duty-cycle ratio (D) and load current ( $I_{load}$ ) as (2.7).

$$D_A = D + \frac{2I_{load} \cdot L}{D \cdot V_{in} \cdot T} \tag{2.7}$$

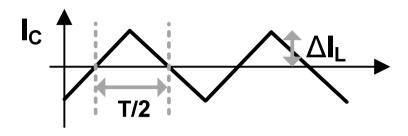

# 2.3 Operation Mode

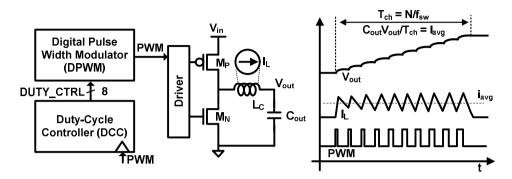

To maximize the energy delivery, the proposed buck converter operates in CCM and DCM at start-up and steady-state operation, respectively. A simple block diagram of the proposed buck converter and its CCM/DCM controllers are illustrated in Fig. 2.5.

In start-up operation, the controller employs a pulse-width modulation (PWM) scheme to keep the average inductor current constant. The key principle of the start-up controller is that the energy is transferred from the input capacitor ( $C_{in}$ ) to the output capacitor ( $C_{out}$ ) by toggling the power switches ( $M_P$  and  $M_N$ ) on and off multiple times, of which duty-cycle ratio linearly increments in a stepwise fashion. When the energy harvester collects the sufficient energy in  $C_{in}$ , the buck converter operates in the forward direction by turning on the high-side switch  $M_P$  and building up the positive inductor current that charges  $C_{out}$ . By linearly incrementing the duty-cycle ratio D from zero, the output voltage  $V_{out}$  increases linearly towards a desired voltage level,  $V_{out} = D \cdot V_{in}$ , which maintains the average inductor current constant.

After the charging  $C_{\rm out}$  completes, the buck converter changes its operation mode in pulse-frequency-modulation (PFM) mode. The converter employs a PFM control scheme to regulate the output voltage, and to enhance the light-load efficiency by dynamically adjusting the switching frequency according to the load current. The key principles of the PFM control are that the on-time  $(T_{\rm on})$  of the high-side switching signal  $CK_P$  is adaptively scaled with inversely proportional to  $V_{\rm in} - V_{\rm out}$  (i.e.,  $T_{\rm on} \sim 1/(V_{\rm in} - V_{\rm out})$ ) and the off-time  $(T_{\rm off})$  of the low-side switching signal  $CK_N$  is also

Fig. 2.5. (a) Simple block diagram of the buck converter and its controller, and (b) key operating waveforms.

adaptively scaled with inversely proportional to  $V_{\rm out}$  (i.e.,  $T_{\rm off} \sim 1/V_{\rm out}$ ). The generated  $T_{\rm on}$  can keep the inductor peak current constant regardless of  $V_{\rm in}$  and  $V_{\rm out}$  variation and the generated  $T_{\rm off}$  can turn off  $M_N$  with the right timing by predicting the zero-inductor-current timing. The detailed design concepts of the proposed inductor current control techniques will be described in Chapter 3.

#### 2.4 Overall Architecture

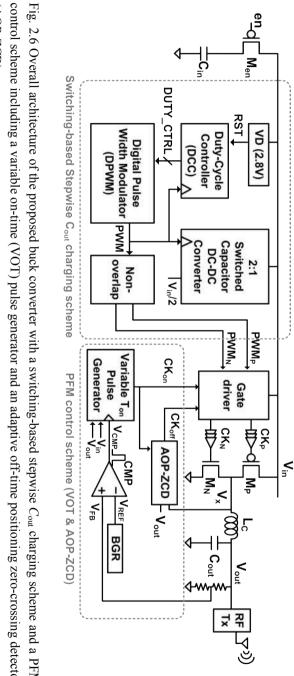

The overall architecture of the proposed buck converter is illustrated in Fig. 2.6. It is composed of a power stage of the buck converter, the switching-based stepwise charging scheme for start-up operation, the PFM control scheme including the variable on-time and adaptive off-time positioning ZCD, and the load system (i.e., 2.4-GHz WirelessUSB RF transceiver (CYRF8935)).

More specifically, during start-up, the switching-based stepwise charging scheme charges  $C_{\text{out}}$  with a constant inductor current, which is made by switching the buck converter with linearly incrementing the duty-cycle ratios. As shown in Fig. 2.6, it includes a voltage detector (VD), a duty-cycle controller (DCC), a digital pulse width modulator (DPWM), a non-overlap circuit and a 2:1 switched-capacitor (SC) converter. When the input capacitor  $(C_{in})$  is charged to a desired voltage (e.g., 5 V) by an energy harvester, an enable signal (en) turns on a switch  $M_{\rm en}$ . From this time, the input voltage  $V_{in}$  increases from zero to the capacitor voltage of  $C_{in}$  and then the proposed start-up controller begins to operate. When  $V_{\rm in}$  reaches a predetermined voltage level (i.e., 2.8 V), a voltage detector (VD) generates a reset signal for the DCC, which generates pre-programmed 8-bit digital code (DUTY CTRL). With this code, DPWM generates the pulse-width modulated signals (i.e.,  $PWM_P$  and  $PWM_N$ ) for both high-side and low-side switches (i.e.,  $M_P$  and  $M_N$ ). To prevent the significant power loss due to the crowbar current when both  $M_P$  and  $M_N$  turn on, the nonoverlap circuit generate the dead time, where both  $M_P$  and  $M_N$  turn off. By linearly incrementing DUTY CTRL from zero, the duty-cycle ratio (D) of the PWM clocks

also increase from zero; this can charge the output capacitor ( $C_{out}$ ) linearly and stepwise, and can maintain the average inductor current constant. Note that a 2:1 switched-capacitor (SC) DC-DC converter is utilized to supply a lower voltage to the control circuits; the lower supply can greatly reduce the dynamic power consumption in control circuits.

The proposed PFM controller employs the variable on-time (VOT) pulse generator to keep the inductor peak current ( $I_{L,peak}$ ) constant. When  $V_{out}$  reaches a desired output voltage that is determined by the output of a bandgap reference (BGR), an output sensing comparator (CMP) sets its output ( $V_{CMP}$ ) low to high. This event enables the PFM controller and simultaneously disables the start-up controller to reduce the unnecessary power consumption. The VOT pulse generator generates the high-side switching signal  $CK_P$ , for which the pulse width (i.e.,  $T_{on}$ ) is set inversely proportional to  $V_{in} - V_{out}$ . Because the inductor current is charged from zero to  $I_{L,peak}$  with a slope of ( $V_{in} - V_{out}$ )/L during  $T_{on}$ , the variable  $T_{on}$  can keep  $I_{L,peak}$  constant for various  $V_{in}$  and  $V_{out}$  (i.e.,  $I_{L,peak} = (V_{in} - V_{out})/L \cdot T_{on} = const$ ).

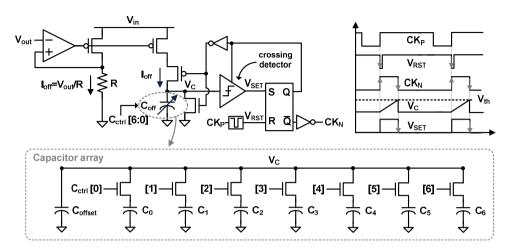

To position the turn-off timing of  $M_N$  near the zero-inductor-current timing by predicting the inductor current waveform, the adaptive off-time positioning zero-crossing detector (AOP-ZCD) is proposed. When  $T_{\rm on}$  ends, this event enables the AOP-ZCD, which is composed of an adaptive off-time (AOT) pulse generator and digital timing calibration loop. The AOT pulse generator generates the low-side switching signal  $CK_N$ , for which the pulse width (i.e.,  $T_{\rm off}$ ) is set inversely proportional to  $V_{\rm out}$  (i.e.,  $T_{\rm off} \sim 1/V_{\rm out}$ ). Because the inductor current is discharged from  $I_{L,\rm peak}$  to zero with a slope of  $-V_{\rm out}/L$  during  $T_{\rm off}$ , the generated  $T_{\rm off}$  can ideally turn off  $M_N$  when the inductor current reaches zero and the accurate zero-current switching

control scheme including a variable on-time (VOT) pulse generator and an adaptive off-time positioning zero-crossing detector Fig. 2.6 Overall architecture of the proposed buck converter with a switching-based stepwise  $C_{\text{out}}$  charging scheme and a PFM (AOP-ZCD).

(ZCS) timing of  $M_N$  can be predictable. However, the initially generated  $T_{\rm off}$  is not enough to guarantee the precise ZCS operation because the timing error can be incurred by various non-ideal effects, such as process–voltage–temperature (PVT) variations, device mismatches, or series resistance of the power switches and inductor. To compensate for the residual timing error, a digital timing calibration loop in the AOP-ZCD adjusts the  $T_{\rm off}$ .

### Chapter 3

# Optimal Inductor Current Controls for Maximum Energy Delivery

In Chapter 2, the operation mode and the overall architecture of the proposed buck converter were described. This chapter will discuss the optimal inductor current control techniques for maximum energy delivery in each start-up and steady-state operation in detail. Specifically, the previously-reported control schemes are described first, and then the proposed circuit techniques to reduce the energy losses introduced in Chapter 1 ( $E_{loss,st}$ ,  $E_{loss,Cout}$ ,  $E_{loss,conv}$ ) for achieving the best performance will be explained based on the detailed analysis.

# 3.1 Constant Inductor Current Control with Switching-Based Stepwise Capacitor Charging Scheme

In this section, we describe the proposed start-up control scheme and its advantage compared to those of the previous ones. Before discussing the effectiveness of our approach, the previously reported capacitor charging schemes will be described first

#### 3.1.1 Conventional Charging Scheme with a Switch

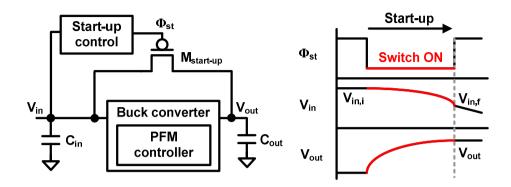

In previous energy harvesting applications, a simple start-up switch [3], [35] was used to charge  $C_{\text{out}}$  as shown in Fig. 3.1 because they focused on the steady-state operation with a continuous energy source such as vibration or RF input, in which the steady-state power efficiency matters than the start-up energy loss. However, this method is not proper to the target application because the steady-state condition does not last long, which makes the transient energy loss during the start-up phase of the buck converter dominant. In this sub-section, we derive the start-up energy loss (i.e.,  $E_{\text{loss,st}} + E_{\text{loss,Cout}}$ ) when charging the capacitor with a switch to show that this scheme incurs the large energy loss at the switch.

Fig. 3.1. Conventional start-up scheme with a simple switch  $M_{\text{start-up}}$ .

Its basic principle of charging  $C_{\text{out}}$  is the charge sharing between the input capacitor ( $C_{\text{in}}$ ) and the output capacitor ( $C_{\text{out}}$ ) by connecting them with a switch  $M_{\text{start-up}}$ . Since it charges  $C_{\text{out}}$  to  $V_{\text{out}}$  by directly connecting the voltage source ( $C_{\text{in}}$  can be considered as a voltage source), the large energy loss of  $C_{\text{out}}V_{\text{out}}^2/2$  is incurred at the switch even if its resistance is an extremely low value.

More specifically, the total energy loss when the  $C_{in}$  is connected to the  $C_{out}$  with the  $M_{start-up}$  can be derived as follows. Assuming that  $C_{out}$  is initially fully discharged and the initial voltage of the storage capacitor  $C_{in}$  is  $V_{in}$ , the final input voltage  $V_{in,f}$  after charge sharing can be expressed as:

$$V_{in,f} = V_{in} - \frac{V_{out}C_{out}}{C_{in}}$$

(3.1)

Therefore, the energy usage of  $C_{in}$  during start-up operation (i.e.  $E_{loss,St} + E_{loss,Cout}$ ) can be derived as (2):

$$E_{loss,st} + E_{loss,Cout} = \frac{1}{2} C_{in} (V_{in}^2 - V_{in,f}^2) = V_{in} V_{out} C_{out} - \frac{V_{out}^2 C_{out}^2}{2C_{in}}$$

(3.2)

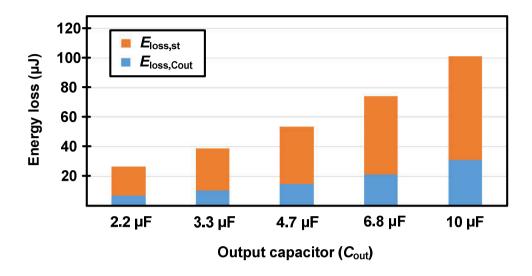

Fig. 3.2. Energy losses versus  $C_{\text{out}}$ .

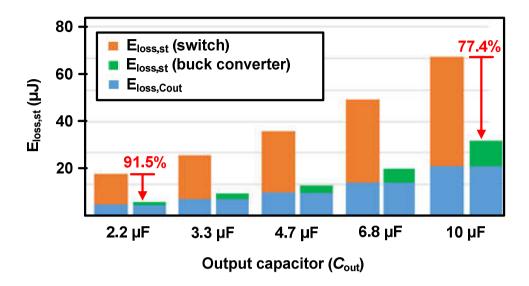

Fig. 3.2 plots the energy losses in change with  $C_{\rm out}$  from (3.2) with a 13.2- $\mu$ F  $C_{\rm in}$ , 5 V  $V_{\rm in}$  and 2.5 V  $V_{\rm out}$ . This figure shows that the large energy is lost at the switch and its loss increases as  $C_{\rm out}$  increases. For instance, to charge a 2.2- $\mu$ F  $C_{\rm out}$  to  $V_{\rm out}$ , 19.5- $\mu$ J energy is dissipated at the switch (i.e.,  $E_{\rm loss,st}$ ), while 6.9- $\mu$ J energy is stored in  $C_{\rm out}$  (i.e.,  $E_{\rm loss,Cout}$ ). However, to charge a 10- $\mu$ F  $C_{\rm out}$  to  $V_{\rm out}$ , 70.1- $\mu$ J energy is dissipated at the switch, while 31.3- $\mu$ J energy is stored in  $C_{\rm out}$ . Considering that the energy stored in 13.2- $\mu$ F  $C_{\rm in}$  was 165  $\mu$ J, this charging scheme cannot be used in this application due to the excessively large energy loss incurred during charging  $C_{\rm out}$ .

#### 3.1.2 Adiabatic Stepwise Charging

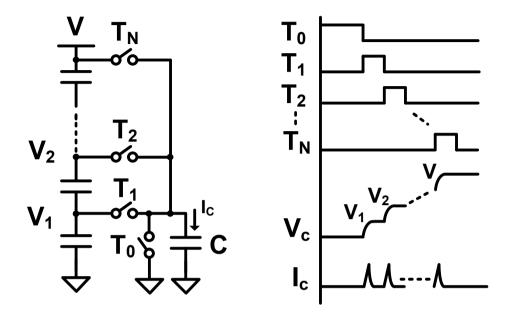

The energy loss problem incurred when charging capacitor already existed in related fields. To reduce the resistive loss incurred at the switch, an capacitor charging technique called adiabatic switching has previously been researched for their energy efficient integrated circuits such as logic [45]–[47], SRAM [48] and clock driver networks [49], [50]. Specifically, adiabatic circuits use a stepwise charging method [41]–[44] that ideally dissipates no energy when the charging level moves between infinitesimal voltage levels as shown in Fig. 3.3. To charge the capacitor to the supply voltage V using the N-stepwise method, the intermediate reference voltages of the tank capacitors ( $V_i = i \cdot V/N$ ) are connected to the load capacitor C in succession using the corresponding switches ( $T_1$ – $T_N$ ).

The effectiveness of adiabatic charging scheme is that charging the capacitor in N steps instead of a single step reduces the energy dissipation by a factor of N. To charge the capacitor C, each reference voltage level is connected to the capacitor in briefly in ascending order, until its voltage reaches the corresponding reference voltage level. While each reference voltage supply (i.e., voltage across tank capacitor) injects a charge to the capacitor, the energy loss at each switch ( $E_{TN}$ ) can be expressed as:

$$E_{TN} = \frac{C(V_i - V_{i-1})^2}{2} = \frac{CV^2}{2N^2}$$

(3.3)

Therefore, the total energy loss at the switches  $(T_1-T_N)$  can be derived as:

$$E_{TI-TN} = E_{TN} \cdot N = \frac{CV^2}{2N} \tag{3.4}$$

Fig. 3.3. Stepwise charging the capacitor with *N* tank capacitors.

Although this scheme can reduce the loss incurred at the switches, it is difficult to directly apply this technique to the battery-free applications because this method needs N additional tank capacitors to generate N step voltage levels, resulting in design complexity and increasing cost. Moreover, a large amount of energy is required to pre-charge N tank capacitors to their predetermined voltage levels.

#### 3.1.3 Proposed Start-up Scheme

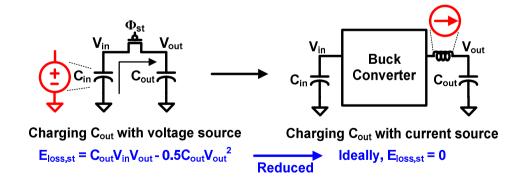

To efficiently charge  $C_{\text{out}}$  without incurring the loss at the start-up circuit (i.e.,  $E_{\text{loss,st}}$ ), the proposed start-up scheme [39] employs a current charging method as shown in Fig 3.4. Charging  $C_{\text{out}}$  with a current source can reduce  $E_{\text{loss,st}}$  to zero ideally, while the required energy is only  $E_{\text{loss,cout}}$  (i.e.,  $0.5C_{\text{out}}V_{\text{out}}^2$ ). Specifically, to realize the current source, the proposed start-up scheme directly uses the buck converter that can make the inductor current as a constant current source by switching the inductor. Note that  $E_{\text{loss,st}}$  in the proposed scheme is the required energy to make the constant inductor current during the buck converter's start-up operation.

To reduce the  $E_{loss,st}$ , the proposed buck converter realizes the stepwise charging by digitally incrementing duty-cycle ratios in a stepwise fashion. Specifically, since the buck converter can generate an output voltage that is proportional to the dutycycle ratio (D) (i.e.  $V_{out} = DV_{in}$ ), N voltage levels can be generated without using the

Fig. 3.4. Design concept of the proposed capacitor charging scheme with a current source.

Fig. 3.5. Schematic of the switching-based stepwise capacitor scheme and its operating waveforms.

N pre-charged tank capacitors. By increasing  $V_{\text{out}}$  stepwise, the average inductor current can be kept constant and the  $E_{\text{loss,st}}$  can be reduced by a factor of the number of stepwise voltage levels (N).

To control the duty-cycle ratio, the proposed start-up controller uses a digital pulse width modulator (DPWM) and duty-cycle controller (DCC), as shown in Fig. 3.5. The DPWM generates a pulse-width modulated (PWM) switching pulse to operate the buck converter in CCM and its duty-cycle ratio is digitally controlled by 8-bit  $DUTY\_CTRL$  [7:0] from DCC. By linearly incrementing  $DUTY\_CTRL$  [7:0], the buck converter can charge  $C_{out}$  to  $V_{out}$  in a stepwise fashion with the constant average inductor current.

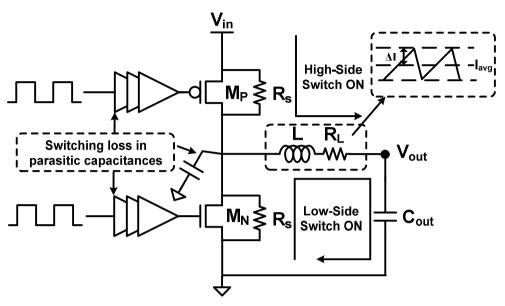

To verify the effectiveness of this approach, the buck converter losses are derived. Fig. 3.6 illustrates the main buck converter losses during the start-up operation including the conduction and switching energy losses. First, the conduction loss ( $E_{cond}$ ) is incurred at the resistive components such as the resistance of power switches ( $R_s$ ) and inductor ( $R_L$ ). During stepwise charging, the average inductor current ( $i_{avg}$ ) can

Fig. 3.6. Schematic of the loss components in the buck converter:  $R_s$ ,  $R_L$ , and the parasitic capacitances in the switching nodes.

be maintained roughly constant due to the linearly increasing duty-cycle ratio, and its ripple current ( $\Delta i[n]$ ) can be expressed as a function of the *n*-th duty-cycle ratio D[n]. Both  $i_{\text{avg}}$  and  $\Delta i[n]$  can be expressed as (3.5) and (3.6), respectively,

$$i_{avg} = C_{out} \frac{dV_{out}}{dt} = \frac{C_{out}V_{out}}{T_{ch}} = \frac{C_{out}V_{out}f_{sw}}{N}$$

(3.5)

$$\Delta i[n] = \frac{V_{in} \cdot D[n] \cdot (1 - D[n])}{L_C \cdot f_{sw}}$$

(3.6)

where  $T_{ch}$  is the charging time,  $f_{sw}$  is switching frequency of the *PWM* signal and  $L_C$  is the inductance. If the duty-cycle resolution is K, the n-th duty-cycle ratio D[n] can be given by:

$$D[n] = n/K \ (n = 1, 2, ..., N)$$

(3.7)

Note that the relationship between N and K is determined by the voltage conversion ratio, and hence the value of K can be expressed as:

$$K = \frac{NV_{in}}{V_{out}} \tag{3.8}$$

Assuming that transistors  $M_P$  and  $M_N$  have identical series on-resistances  $R_s$  and the inductor has a series resistance of  $R_L$ , and the total resistance in the current-delivering path is R (i.e.,  $R_s + R_L$ ), then the total conduction energy loss  $E_{cond}$  can be expressed as:

$$E_{cond} = \frac{R}{f_{sw}} \sum_{n=1}^{N} (i_{avg}^{2} + \frac{(\Delta i[n])^{2}}{12})$$

$$= \frac{RC_{out}^{2}V_{out}^{2}f_{sw}}{N} + \frac{RV_{in}^{2}}{12L_{C}^{2}f_{sw}^{3}} \sum_{n=1}^{N} (1 - \frac{n}{K})^{2} (\frac{n}{K})^{2}$$

(3.9)

Note that from (3.9), assuming that  $E_{cond}$  is the dominant loss and  $f_{sw}$  is high enough to ensure that  $\Delta i \cong 0$ , then charging the capacitor over N steps instead of a single step can reduce the energy dissipation by a factor of N. Second, the switching loss  $E_{swit}$  is incurred in the internal parasitic capacitors in the switching nodes in the driver and power switches. Assuming that the sum of the internal capacitors is  $C_{int}$ , the dynamic energy loss  $E_{swit}$  can be expressed as:

$$E_{swit} = C_{int} V_{in}^2 f_{sw}(N/f_{sw}) = C_{int} V_{in}^2 N$$

(3.10)

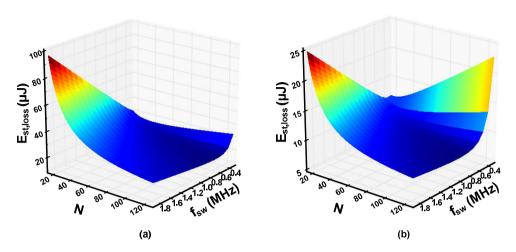

While  $E_{loss,st}$  is the sum of the energy losses derived in (3.9) and (3.10), we can find the optimal values of N and  $f_{sw}$  that can minimize the total energy loss for a given  $C_{out}$ . From the analysis, both  $E_{cond}$  and  $E_{swit}$  are highly dependent on the charging

Fig. 3.7. Start-up energy loss ( $E_{loss,st} + E_{loss,Cout}$ ) in change with N and  $f_{sw}$ , when charging (a) 4.7- $\mu$ F and (b) 2.2- $\mu$ F capacitors.

time (i.e.,  $T_{\rm ch} = N/f_{\rm sw}$ ). Since  $i_{\rm avg}$  is inversely proportional to  $T_{\rm ch}$ , as given by (3.5), a large  $T_{\rm ch}$  can reduce  $E_{\rm cond}$ . However, a large  $T_{\rm ch}$  incurs a large  $E_{\rm swit}$  from (3.10). Fig. 3.7 illustrates the sum of the total energy loss in the buck converter ( $E_{\rm loss,st}$ ) and the stored energy in  $C_{\rm out}$  ( $E_{\rm loss,Cout}$ ) with respect to changes in N and  $f_{\rm sw}$  when charging a 4.7  $\mu$ F and 2.2  $\mu$ F  $C_{\rm out}$ , respectively. To charge a 4.7- $\mu$ F capacitor to 2.5 V, the action of switching the buck converter at 0.9 MHz and ramping the duty-cycle from 0 to ~50% over a 0.14-ms  $T_{\rm ch}$  can maintain the start-up energy loss below 22  $\mu$ J, while the buck converter loss ( $E_{\rm loss,st}$ ) is only ~5.1  $\mu$ J (i.e., stored energy in 4.7- $\mu$ F  $C_{\rm out}$  ( $E_{\rm loss,Cout}$ ) is 14.7  $\mu$ J). From (3.5), we can find that the optimal inductor average current can be 84 mA in this case. In the same way, to charge a 2.2- $\mu$ F capacitor to 2.5 V, the action of switching the buck converter at 1.2 MHz and ramping the duty-cycle from 0 to ~50% over a 0.11-ms  $T_{\rm ch}$  can maintain the start-up energy loss below 10  $\mu$ J, while the buck converter loss ( $E_{\rm loss,st}$ ) is only ~1.7  $\mu$ J (i.e., stored energy in 2.2- $\mu$ F  $C_{\rm out}$  ( $E_{\rm loss,Cout}$ ) is 6.9  $\mu$ J). From (3.5), we can find that the optimal inductor

Fig. 3.8.  $E_{\rm loss,st}$  comparison between the conventional and the proposed start-up scheme.

average current can be 50 mA in this case. In both cases, the proposed start-up scheme can greatly reduce  $E_{loss,st}$  compared to the conventional charging scheme with a switch.

Fig. 3.8 plots the comparison of the energy loss incurred at the start-up circuit  $E_{\rm loss,st}$  between the conventional (i.e., switch) and proposed (i.e., buck converter) schemes versus  $C_{\rm out}$ , demonstrating the effectiveness of our approach. For instance, the proposed start-up scheme saves the energy by 91.5% at 2.2- $\mu$ F case and by 77.4% at 10- $\mu$ F case, respectively.

# 3.2 Constant Inductor Peak Current Control with Variable On-Time PFM Scheme

Although the proposed start-up scheme can reduce the  $E_{\rm loss,st}$ , the PFM buck converter still calls for a large  $C_{\rm out}$  to suppress the voltage ripples. Especially, because the input of the buck converter is a capacitor, its voltage decreases as the energy is delivered to the load, which demands for a larger  $C_{\rm out}$  to achieve the voltage ripple within an acceptable range needed by the application over wide range of input voltage conditions. In this sub-section, the design concept of the variable on-time PFM scheme will be explained that enables the use of a small  $C_{\rm out}$  to reduce  $E_{\rm loss,Cout}$ , while maintaining small voltage ripples and high efficiency over wide range of input voltage conditions.

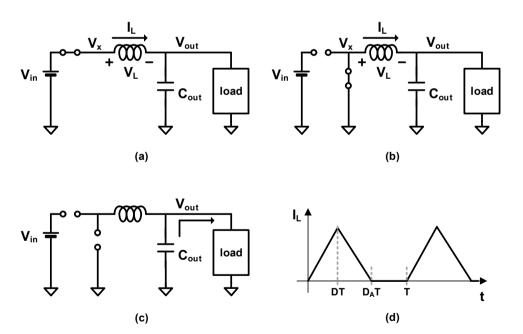

#### 3.2.1 Basic Operation of PFM Buck Converter

The DCM buck converters are widely used in many emerging low-power applications, including energy harvesting systems [1]–[4], wearable devices [5], medical sensors [3], [6], and the Internet of Things (IoT) [4] because they can achieve high efficiency at light loads and can extend the battery life. Especially, the buck converter employs a pulse-frequency modulation (PFM) control can save the energy in light load condition by adjusting the switching frequency according to the load current.

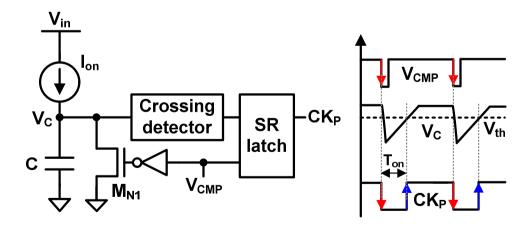

Fig. 3.9. Simple schematic of the buck converter with PFM control operating in DCM and its key waveforms.

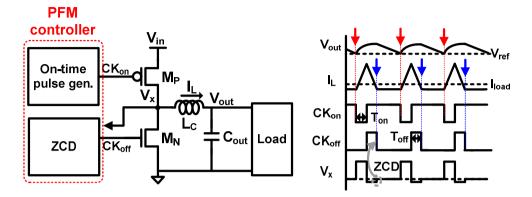

The simple schematic of the buck converter with PFM control operating in DCM and its key waveforms are illustrated in Fig. 3.9. When the output voltage  $V_{\text{out}}$  becomes smaller than the reference voltage  $V_{\text{ref}}$ , an on-time pulse generator generates the high-side switching signal  $CK_{on}$ , of which the pulse width is  $T_{\text{on}}$ . During the ontime  $(T_{\text{on}})$ , the high-side power transistor  $(M_P)$  turns on and the inductor current increases with a slope of  $(V_{\text{in}} - V_{\text{out}})/L$ . When  $M_P$  turns off, simultaneously the low-side switching signal  $CK_{off}$  is generated, of which the pulse width is  $T_{\text{off}}$ . During the off-time  $(T_{\text{off}})$ , the low-side power transistor  $(M_N)$  turns on and the inductor current decreases with a slope of  $-V_{\text{out}}/L$  until it reaches zero. At this time, the zero-current detector (ZCD) turns off  $M_N$  to prevent the reverse inductor current, which can incur the significant power loss. When both switches turn off, the stored charge in the output capacitor  $(C_{\text{out}})$  is delivered to the load until  $V_{\text{out}}$  becomes smaller than  $V_{\text{ref}}$  again.

In the PFM controller, the on-time ( $T_{on}$ ) determines the various key performance such as the inductor peak current ( $I_{L,peak}$ ), the switching frequency ( $f_{sw}$ ) and the volt-

age ripple ( $V_{ripple}$ ). From the amount of increase in the inductor current ( $I_L$ ) during the on-period ( $T_{on}$ ), the inductor peak current can be derived as:

$$\frac{(V_{in} - V_{out})T_{on}}{L} = \frac{V_{out}T_{off}}{L} = I_{L,peak}$$

(3.11)

This equation shows that the inductor peak current is determined by the voltage difference between input and output and the on-time period. Note that the amount of the increase and decrease in the inductor current should be same in the PFM control from the fundamental inductor current balancing equation and hence the off-time is determined by the inductor peak current and output voltage from (3.11). The total charge ( $Q_{\text{total}}$ ) stored in the inductor is the area under the inductor current waveform in one switching period, which can be express as:

$$Q_{total} = \frac{I_{L,peak} (T_{on} + T_{off})}{2}$$

(3.12)

Assuming that the power loss of the buck converter is zero (i.e., resistive components in current path assumed to zero) and it regulates the output voltage ideally (i.e., the zero-crossing timing of the inductor current is detected at the right timing), the charge transferred to the load can be expressed as (3.13), where  $T_{sw}$  is the switching period, which is determined by the load current ( $I_{load}$ ).

$$Q_{total} = I_{load} \cdot T_{sw} \tag{3.13}$$

Since the total charge stored in the inductor is equal to the charge transferred to the load in one switching period ( $T_{sw}$ ) from (3.13), the switching frequency ( $f_{sw}$ ) can be derived as:

$$f_{sw} = \frac{2I_{load}}{I_{L, peak}(T_{on} + T_{off})}$$

(3.14)

During  $T_{\rm on}$  and  $T_{\rm off}$ , the total charge ( $Q_{\rm total}$ ) stored in the inductor is decomposed into the charge transferred to the load and temporarily stored in the output capacitor (i.e.,  $Q_{\rm cap}$ ). Especially,  $Q_{\rm cap}$  causes the voltage ripple ( $V_{\rm ripple}$ ). In other words, the area of  $I_L$  –  $I_{load}$  (i.e.,  $Q_{\rm cap}$ ) determines  $V_{\rm ripple}$  and, it can be derived as:

$$V_{ripple} = \frac{(I_{L,peak} - I_{load})^2 (T_{on} + T_{off})}{2C_{out}I_{L,peak}}$$

(3.15)

Consequently, to ensure that the voltage ripple remains within an acceptable range needed by the application, the proper value of the on-time  $(T_{on})$  should be selected.

#### 3.2.2 Constant On-Time PFM Scheme

The constant  $T_{on}$  (COT) PFM scheme [14]–[17] have been widely used when the buck converter operates in the narrow ranges of input and output voltages. In other words, the optimal value of  $T_{on}$  can be a constant when the operating voltages are fixed. However, if the input supply varies under the COT control, both the inductor peak current value and the charge transferred to the load in each switching cycle can also vary, which results in producing a widely varying voltage ripple and an average value of the output voltage.

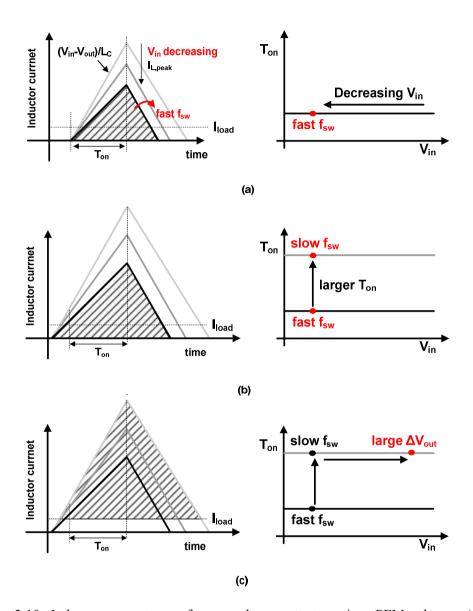

Especially, in the battery-free applications, the design challenges arise from the fact that the input supply voltage decreases as the charge in the input capacitor is delivered to the load. In other words, the decreasing input voltage incurs the widely varying inductor peak current because its slope during  $T_{\rm on}$  is proportional to  $V_{\rm in}$  –  $V_{\rm out}$  from (3.11). Fig. 3.10 (a) shows that the amount of charge transferred decreases as the input voltage decreases. This is due to the decrease of the inductor peak current from (3.12), which results in the fast switching frequency from (3.14) and defeats the power-saving advantage of the PFM control at a low  $V_{\rm in}$ . To alleviate this problem, a possible way is to increase the value of the on-time from the start (i.e., larger  $T_{\rm on}$ ). By increasing  $T_{\rm on}$ , a slow switching frequency at a low  $V_{\rm in}$  can be achieved as shown in Fig. 3.10 (b). However, this larger  $T_{\rm on}$  causes the high voltage ripple at a high  $V_{\rm in}$  as shown in Fig. 3.10 (c). Therefore, the COT PFM scheme must use the large output capacitor ( $C_{\rm out}$ ) to suppress the voltage ripple at a high  $V_{\rm in}$ , which is not proper to the battery-free application because the large  $C_{\rm out}$  can incur the start-up energy loss as illustrated in Fig. 3.8.

Fig. 3.10. Inductor current waveforms under constant on-time PFM scheme; (a) switching frequency increase at low  $V_{\rm in}$ , (b) slow switching frequency with larger  $T_{\rm on}$  at low  $V_{\rm in}$  and (c) resulting large voltage ripple at high  $V_{\rm in}$ .

#### 3.2.3 Variable On-Time PFM Scheme

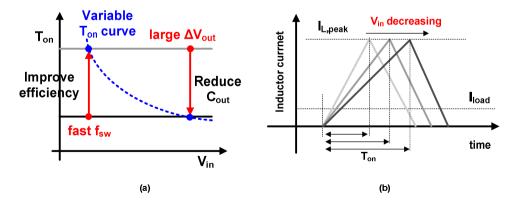

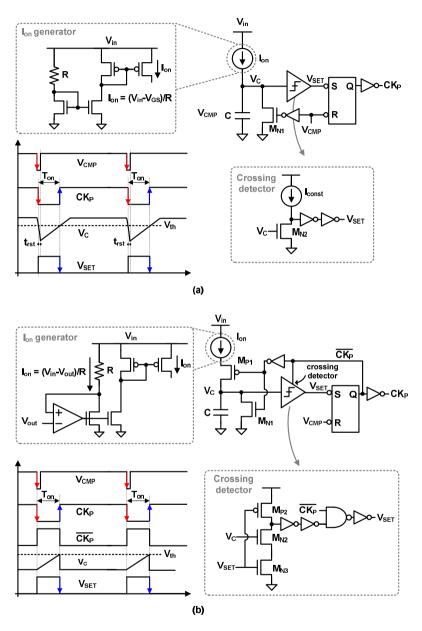

To address this problem, the variable on-time (VOT) PFM scheme is proposed that enables the use of a small  $C_{\rm out}$ , while maintaining the small voltage ripple and the low switching frequency over wide ranges of input voltage conditions. Specifically, the VOT pulse generator keeps the inductor peak current ( $I_{\rm L,peak}$ ) by varying  $T_{\rm on}$  inversely proportional to the  $V_{\rm in}-V_{\rm out}$  as shown in Fig. 3.11 (a). At a high  $V_{\rm in}$ , the VOT pulse generator generates a small  $T_{\rm on}$ , which enables the use of a small  $C_{\rm out}$  by reducing the worst case voltage ripple. In addition, the variable  $T_{\rm on}$  increases as the input voltage decreases, which can improve the power efficiency by reducing the switching frequency at a low  $V_{\rm in}$ . Consequently, under the VOT PFM control, the inductor peak current can be kept constant regardless of  $V_{\rm in}$  variation by adaptively varying  $T_{\rm on}$  as shown in Fig. 3.11 (b). Even for the various input and output voltages, by adaptively varying the on-time, the variation of the amount of charge transferred,

Fig. 3.11. Proposed variable  $T_{\rm on}$  curve to reduce  $C_{\rm out}$  and improve the power efficiency.

Fig. 3.12. Performance comparison between the variable  $T_{\rm on}$  (VOT) and the constant  $T_{\rm on}$  (COT); (a)  $T_{\rm on}$  value, (b) inductor peak current ( $I_{L,\rm peak}$ ), (c) switching frequency ( $f_{\rm sw}$ ) and (d) voltage ripple ( $V_{\rm ripple}$ ).

which is the area of  $I_L$ , can be reduced and be kept fairly constant.

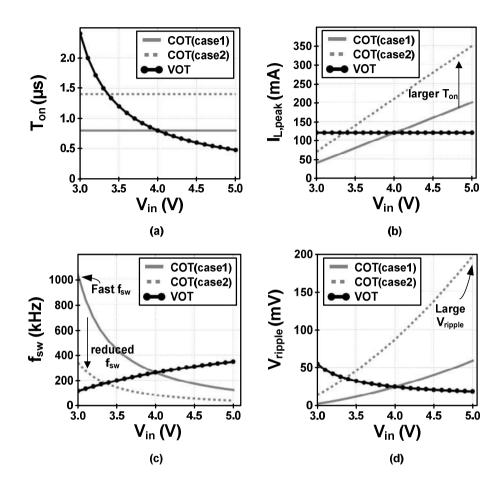

The performance comparison between the variable  $T_{\rm on}$  (VOT) and the constant  $T_{\rm on}$  (COT) controls are illustrated in Fig. 3.12. These figures are plotted based on the equations derived in Section 3.2.1 If  $T_{\rm on}$  is a constant value,  $I_{L,\rm peak}$  can widely vary

with  $V_{\rm in}$ ; this can incur widely varying  $V_{\rm ripple}$  and  $f_{\rm sw}$  across the range of  $V_{\rm in}$ . For instance, when  $T_{\rm on}$  has a constant value of 800 ns (i.e., Case 1) with a 10- $\mu$ H inductor,  $I_{L,\rm peak}$  is proportional to  $V_{\rm in}$  and varies between 50 mA and 200 mA as  $V_{\rm in}$  changes from 3 V to 5 V [see Fig. 3.12 (b)]. This means that it is difficult to operate the buck converter at a low  $V_{\rm in}$  because the amount of charge that is transferred to the load during one switching period is dramatically reduced as  $V_{\rm in}$  decreases. In addition,  $I_{L,\rm peak}$  at 3 V  $V_{\rm in}$  is too small, thereby incurring a very high  $f_{\rm sw}$  of 1 MHz, which degrades the light-load efficiency (see Fig. 3.12 (c)). Since both  $I_{L,\rm peak}$  and  $T_{\rm off}$  decrease as  $V_{\rm in}$  decreases,  $f_{\rm sw}$  is inversely proportional to the square of  $V_{\rm in}$  from (3.14). Therefore, a larger  $T_{\rm on}$  is required to reduce  $f_{\rm sw}$  (i.e., Case 2). For instance, the larger  $T_{\rm on}$  of 1.4  $\mu$ s can reduce  $f_{\rm sw}$  to 350 kHz, but this causes an unnecessarily large  $I_{L,\rm peak}$  of 350 mA at 5 V  $V_{\rm in}$ , thereby causing a large  $V_{\rm ripple}$  of 200 mV (see Fig. 3.12 (d)). An alternative way to suppress  $V_{\rm ripple}$  is to use a large  $C_{\rm out}$ , but this incurs the large startup loss as mentioned before.

On the other hands, the variable  $T_{\rm on}$  (VOT) can reduce the worst case  $V_{\rm ripple}$  and  $f_{\rm sw}$ . Specifically, the variable  $T_{\rm on}$  can maintain both  $I_{L,\rm peak}$  and  $T_{\rm off}$  constant from (3.9). Since these two design parameters are fixed, the variation of  $f_{\rm sw}$  and  $V_{\rm ripple}$  according to  $V_{\rm in}$  can be effectively reduced from (3.14) and (3.15) (see Fig. 3.12 (c) and (d)). As a result, the VOT PFM scheme can achieve a reduced worst-case  $V_{\rm ripple}$  of 50 mV that makes it possible to enable the use of a small  $C_{\rm out}$  (i.e., reducing  $E_{\rm loss,Cout}$ ), and a reduced worst-case  $f_{\rm sw}$  of 400 kHz that improves the power efficiency.

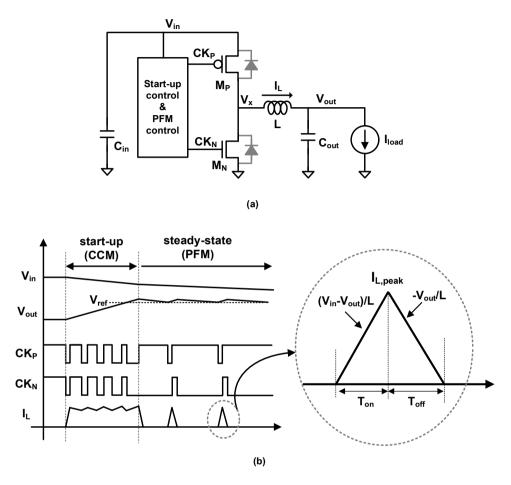

# 3.3 Inductor Current Prediction with Adaptive Off-time Positioning ZCD (AOP-ZCD)

While the VOT pulse generator can improve the power efficiency by reducing the worst case switching frequency as described in 3.2.3, the controller power loss is still large because the continuous-time ZCDs consume the large static power. To reduce  $E_{\rm loss,conv}$  by minimizing the static power consumption of the zero-crossing detector, the adaptive off-time positioning ZCD is proposed that can predict the zero-inductor-current timing without using the power-hungry continuous-time comparator. In addition, it can achieve high resolution and fast-tracking time in its timing detection for wide ranges of input and output voltages.

#### 3.3.1 Previous Sampling-Based ZCD

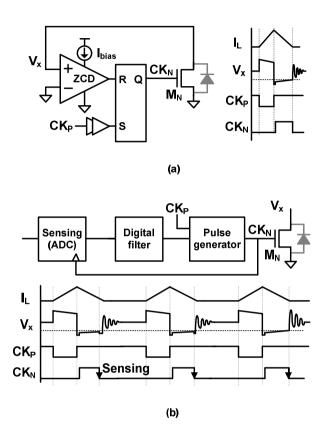

The energy loss problem due to the large quiescent current of the ZCD circuit in steady-state operation have previously been addressed by introducing sampling-based ZCDs [1]–[3]. Fig. 3.13 (a) and (b) compare the block diagrams of the continuous-time ZCD and the sampling-based ZCD. The continuous-time ZCD can accurately find the zero-inductor-current timing and generate the timing signal  $CK_N$  to turn off  $M_N$  for wide ranges of input and output voltages, but its comparator dissi-

Fig. 3.13. Block diagram of (a) the continuous-time ZCD and (b) the sampling-based ZCD.

pates large static current (e.g.,  $\sim$ 100  $\mu$ A [4]) to achieve high precision. On the other hands, the sampling-based ZCD detects the zero-inductor-current timing by using a timing error detector such as a clocked comparator [2] and a successive approximation register analog-to-digital converter (SAR-ADC) [3]. Specifically, because it detects whether  $M_N$  turns off too early or late by sampling the inductor current direction only once per switching cycle, the static power consumption can be reduced. Depending on the polarity of the sampled inductor current direction, the ZCD then increases or decreases the digital filter output accordingly and eventually, it con-

verges to an appropriate value. Controlled by the digital filter output, a pulse generator can generate an appropriate timing signal for the accurate ZCS operation of  $M_N$ .

While the sampling-based ZCD can lower the power consumption by eliminating the continuous-time comparator, it cannot be applied to the battery-free applications because it cannot operate over wide ranges of input and output voltage conditions without degrading either timing resolution or its time to converge to the optimal ZCS timing. To cover such a wide range of voltage conditions, the sampling-based ZCD must have a wide calibration range of timing because the zero-inductor-current timing can widely vary according to the voltage conditions. To extend the calibration range, a possible way is either to increase the unit step size or to increase the number of steps. However, the former sacrifices the precision (i.e. coarse resolution), while the latter convergence time. Due to these tradeoffs, the previous sampling-based ZCDs were used with narrow ranges of input/output voltage conditions.

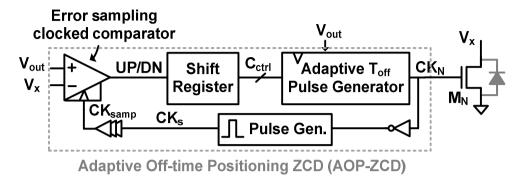

#### 3.3.2 Proposed Adaptive Off-time Positioning ZCD

To achieve both high resolution and short convergence time over wide range input and output voltage conditions, the adaptive off-time positioning ZCD (AOP-ZCD) is proposed, which is a sampling-based ZCD with an adaptive off-time (AOT) pulse generator. The block diagram of the proposed AOT-ZCD including the AOT pulse generator and the timing calibration loop is illustrated in Fig. 3.14. While the on-time  $T_{\rm on}$  was scaled with inversely proportional to the voltage difference between input and output (i.e.,  $T_{\rm on} \sim 1/(V_{\rm in} - V_{\rm out})$ ) as discussed earlier, now the AOT pulse generator generates the off-time  $T_{\rm off}$  scaled with inversely proportional to the output voltage (i.e.,  $T_{\rm off} \sim 1/V_{\rm out}$ ). Therefore, the AOT pulse generator can always position the initial turn-off timing of  $M_N$  close to the zero-inductor-current timing regardless of  $V_{\rm in}$  variation from the fundamental inductor current balancing equation in (3.11). Since the initial timing error between the initial turn-off timing of  $M_N$  and the zero-inductor-current timing can be always kept small, the ZCD can have a narrow calibration range enough to compensate the residual timing error. Therefore, the timing calibration loop can converge quickly with high resolution.

However, the initially generated  $T_{\rm off}$  by the AOT pulse generator is not enough to guarantee the precise ZCS operation because the timing error can be incurred by various non-ideal effects, such as process—voltage—temperature (PVT) variations, device mismatches, or series resistance of the power switches and inductor. To compensate for the residual timing error, the timing calibration loop adjusts the  $T_{\rm off}$  controlled by the digital filter output. Specifically, this digital calibration loop operates in a bang-bang control mode, sampling the inductor current direction at the falling

Fig. 3.14. Block diagram of the proposed AOT-ZCD.

edge of  $CK_N$  and incrementing or decrementing a 7-bit digital code  $C_{\text{ctrl}}$  based on the sample result UP/DN.

## **Chapter 4**

## **Circuit Implementation**

While the specific design concepts of the proposed inductor current controls were explained in Chapter 3, the detailed circuit implementation to realize the proposed control schemes will be described in this chapter.

## 4.1 Circuit Implementation of Switching-

#### **Based Stepwise Capacitor Charger**

As shown in Fig. 2.2, the proposed switching-based stepwise capacitor charging scheme includes the voltage detector (VD), the digital pulse width modulator (DPWM), the duty-cycle controller (DCC) and 2:1 switched-capacitor DC-DC converter. In this section, their circuit implementation will be explained.

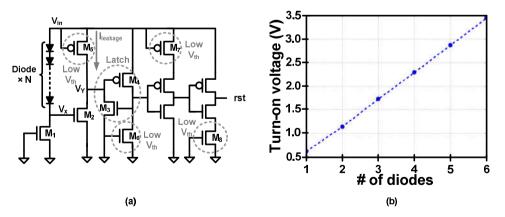

#### 4.1.1 Voltage Detector (VD)