#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

#### Ph.D. DISSERTATION

Vertical Tunnel Field-Effect Transistors with Tunnel-Direction Perpendicular to the Channel for Low Power Operation

저전력 동작을 위하여 채널에 직각인 터널방향과 수직형 구조를 가지는 터널 전계효과 트랜지스터

BY

JANG HYUN KIM

AUGUST 2016

DEPARTMENT OF ELECTRICAL ENGINEERING

AND COMPUTER SCIENCE

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

#### Ph.D. DISSERTATION

Vertical Tunnel Field-Effect Transistors with Tunnel-Direction Perpendicular to the Channel for Low Power Operation

저전력 동작을 위하여 채널에 직각인 터널방향과 수직형 구조를 가지는 터널 전계효과 트랜지스터

BY

JANG HYUN KIM

AUGUST 2016

DEPARTMENT OF ELECTRICAL ENGINEERING

AND COMPUTER SCIENCE

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

# Vertical Tunnel Field-Effect Transistors with Tunnel-Direction Perpendicular to the Channel for Low Power Operation

저전력 동작을 위하여 채널에 직각인 터널방향과 수직형 구조를 가지는 터널 전계효과 트랜지스터

지도교수 박병국 이 논문을 공학박사 학위논문으로 제출함 2016 년 08 월

> 서울대학교 대학원 전기 컴퓨터 공학부 김장현

김장현의 공학박사 학위논문을 인준함 2016 년 08 월

| 위 유         | 일 장 | 박 영 준     | (印) |

|-------------|-----|-----------|-----|

| 부위          | 원장  | 박 병 국     | (印) |

| 위           | 원   | 이종호       | (印) |

| 위<br>위<br>위 | 원   | 최 우 영     | (印) |

| 위           | 원   | <br>이 근 호 | (印) |

## Abstract

In this work, Tunnel Field-Effect Transistors (TFETs) with a novel structure will be proposed as a substituting devices which can implement steeper switching than the conventional MOSFETs do in low power operation. It is experimentally demonstrated that applying a vertical structure with a perpendicular tunnel to the channel can achieve an operation of high electrical performance and it can be integrated in a bulk Si substrate.

First of all, Si and SiGe TFETs with a planar structure are fabricated and measured to extract model parameters. From the measured results, the parameters of band-to-band tunnel (BTBT) model, which can be used to simulate TFETs accurate are calibrated. In this regard, Synopsys Sentaurus Device will be used for this purpose.

Then, based on the simulation of planar TFETs, the proposed devices will be presented as the vertical TFETs with the perpendicular tunnel junction based on the bulk Si substrate. The perpendicular tunnel junction and the large tunnel area are employed on the source side to achieve a steep subthreshold swing (SS) and high ON-current  $(I_{ON})$ , which can lead to TFET's outstanding performance. Moreover, the  $I_{ON}$  can be increased easily by adjusting a height of overlap region between a source and a gate. Although, the TFETs show good electrical performance, there is a hump phenomenon in transfer curve.

In order to suppress the hump phenomenon in the transfer curves, the hump

behavior in the proposed device should be investigated. After investigating it,

the hump behavior is found to be originated from the two different tunnel

regions. Moreover their threshold voltages originated from different tunnel show

different values. In order to improve the electrical performance, a capping layer

which can be made by gradual doping is inserted on the source. Then, the hump

behavior can be expected to decrease.

Finally, the proposed TFETs will be fabricated on the bulk Si substrate.

A thin intrinsic Si is epitaxially grown on the source region which forms the

perpendicular tunnel junction to the channel, resulting in abrupt band bending.

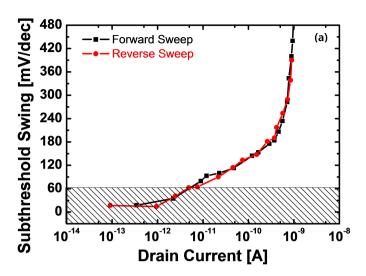

The fabricated the proposed TFETs show 17 mV/dec minimum subthreshold

swing (SS) and  $10^4$  ON/OFF current ratio  $(I_{ON}/I_{OFF})$  for sub-0.7 V gate

overdrive. In addition, SS is maintained less than 60 mV/dec while a drain

current increases from complete OFF-state  $(10^{-13})$  to more than two orders of

magnitude  $(10^{-11})$ .

In conclusion, the proposed device are fabricated successfully. From this

study, it is demonstrated that the proposed TFETs will be one of the most

promising candidate for a next-generation low-power device.

Keywords: band-to-band tunnel, tunnel field-effect transistor, vertical struc-

ture, TFET, low power device, perpendicular tunnel, subthreshold swing, Si

substrate

**Student Number**: 2009-30956

ii

# Contents

| Abstra | act                               | i  |

|--------|-----------------------------------|----|

| Chapte | er 1 Introduction                 | 1  |

| 1.1    | Power issues on CMOS technologies | 1  |

| 1.2    | Tunnel Field Effect Transistors   | 3  |

| 1.3    | Issue for TFETs                   | 6  |

| 1.4    | Propose of the Target Device      | 8  |

| 1.5    | Thesis outline                    | 10 |

| Chapte | er 2 Planar Si & SiGe TFET        | 12 |

| 2.1    | Device fabrication                | 12 |

| 2.2    | Measured Results                  | 14 |

| 2.3    | BTBT model calibrations           | 17 |

| 2.4    | Summary                           | 19 |

| 2.5    | Appendix: Process Flow            | 19 |

| Chapte | er 3 Simulation of the Proposed TFETs   | <b>2</b> 4 |

|--------|-----------------------------------------|------------|

| 3.1    | Introduction                            | 25         |

| 3.2    | Device structure and Fabrication Method | 25         |

| 3.3    | Simulation Results and Discussion       | 27         |

| 3.4    | Summary of Simulation                   | 34         |

| Chapte | er 4 Fabrication of the Proposed TFETs  | 36         |

| 4.1    | Introduction                            | 37         |

| 4.2    | Device Structure and Fabrication Method | 37         |

| 4.3    | Experimental results                    | 47         |

| 4.4    | Discussion                              | 52         |

|        | 4.4.1 High OFF leakage current          | 52         |

|        | 4.4.2 Short channel effect              | 54         |

|        | 4.4.3 Current Saturation by Drain       | 56         |

|        | 4.4.4 Process Optimization              | 59         |

| 4.5    | Summary                                 | 61         |

| 4.6    | Appendix: Process Flow                  | 61         |

| Chapte | er 5 Conclusion                         | 68         |

| 5.1    | Summary of Contributions                | 68         |

| 5.2    | Future works for TFETs Design           | 69         |

| Chapte | er 6 Appendix                           | 71         |

| 6.1    | Super-linear onset in TFETs             | 71         |

| 초로      |                         | 95 |

|---------|-------------------------|----|

| Bibliog | graphy                  | 88 |

| 6.7     | Conclusion              | 86 |

| 6.6     | Tunnel Resistance       | 80 |

| 6.5     | Drain Threshold Voltage | 79 |

| 6.4     | Simulation Results      | 73 |

| 6.3     | Device Structure        | 72 |

| 6.2     | Introduction            | 72 |

# List of Figures

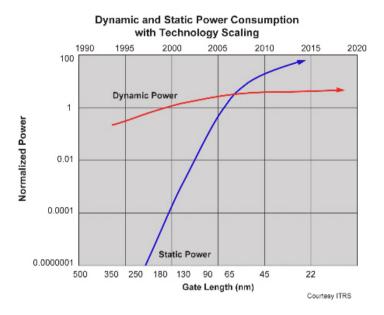

| Figure 1.1 | A power dissipation with the static power and the dy-       |    |

|------------|-------------------------------------------------------------|----|

|            | namic power (Courtesy: ITRS)                                | 2  |

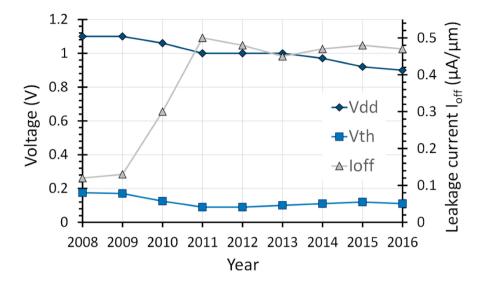

| Figure 1.2 | Trends for MOSFETs threshold voltage $(V_T)$ , operating    |    |

|            | voltage $(V_{DD})$ , and corresponding transistor OFF-state |    |

|            | leakage $(I_{OFF})$ [2]                                     | 4  |

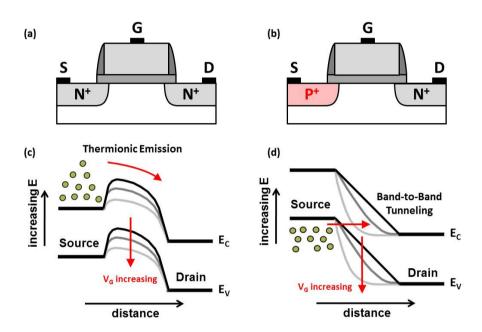

| Figure 1.3 | Schematic cross-sectional view of (a) MOSFETs and (b)       |    |

|            | TFETs. (c) The operation of a MOSFETs are based on          |    |

|            | the thermionic emission. (d) The operation of a TFETs       |    |

|            | are based on BTBT [3]                                       | 5  |

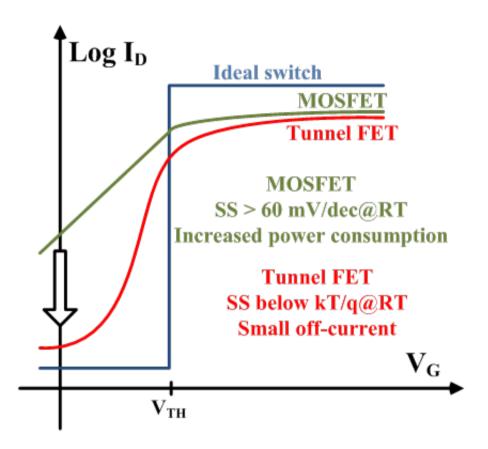

| Figure 1.4 | The switching properties of MOSFETs and TFETs               | 7  |

| Figure 1.5 | Cross sectional view of the MOSFETs and TFETs. Con-         |    |

|            | sidering co-integration within bulk substrate, the TFETs $$ |    |

|            | with vertical structure are highly efficient                | 10 |

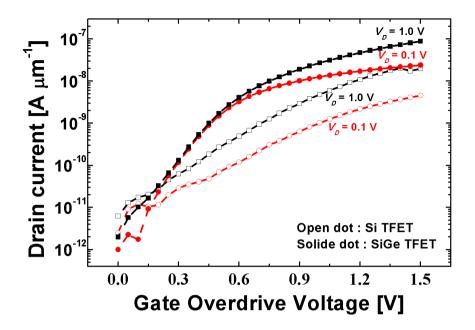

| Figure 2.1 | Schematic diagram and process flow for the Si and SiGe     |    |

|------------|------------------------------------------------------------|----|

|            | TFETs                                                      | 13 |

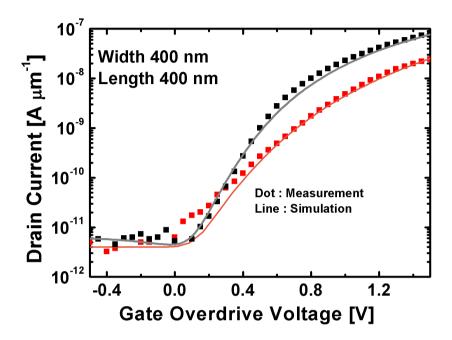

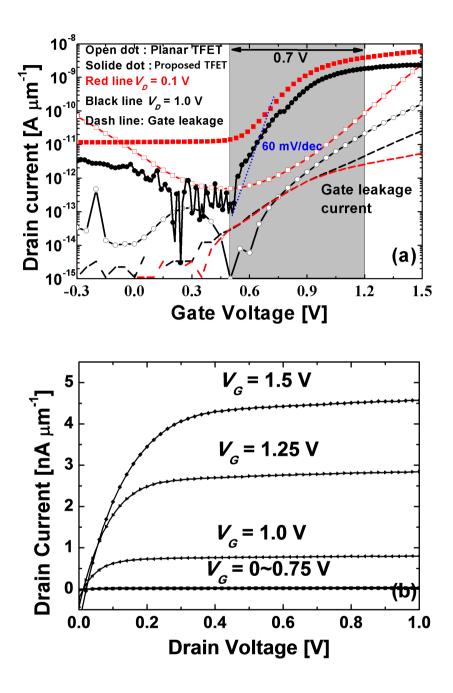

| Figure 2.2 | Measured $I_D$ – $V_G$ characteristics of planar-TFETs de- |    |

|            | vice with Si and SiGe substrate. The devices with SiGe     |    |

|            | TFETs show better current drivability than Si TFETs        | 14 |

| Figure 2.3 | Boron concentration profile from surface to bulk direc-    |    |

|            | tion using SIMS                                            | 16 |

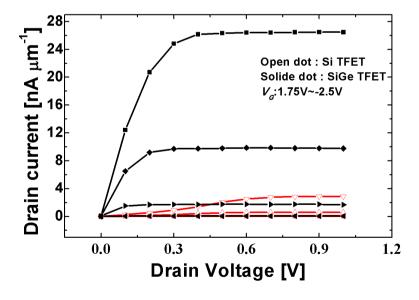

| Figure 2.4 | Measured output characteristics of n-type Si and SiGe      |    |

|            | TFETs                                                      | 16 |

| Figure 2.5 | Parameter calibration curves with simulation and mea-      |    |

|            | surement results of TFETs                                  | 18 |

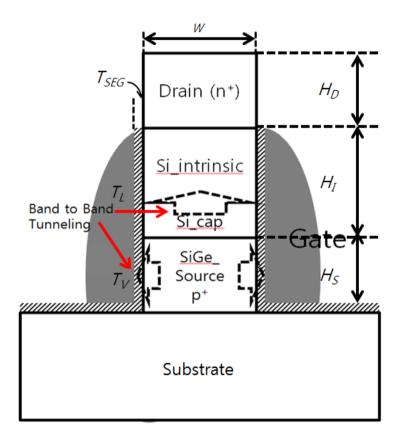

| Figure 3.1 | Schematic view of a vertical structure TFETs with per-     |    |

|            | pendicular tunnel junction to channel. The source ma-      |    |

|            | terial is SiGe. Due to the SEG layer, the tunnel junction  |    |

|            | is formed on source region                                 | 26 |

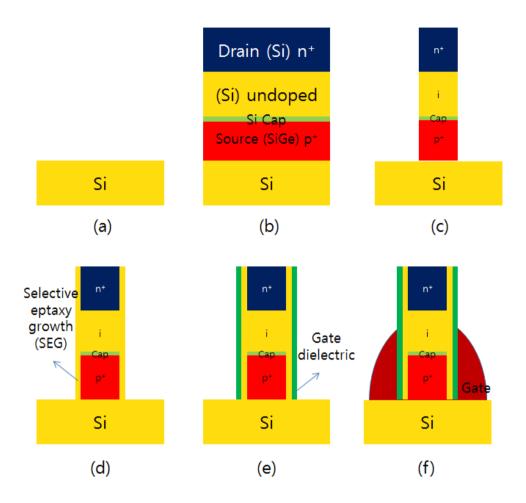

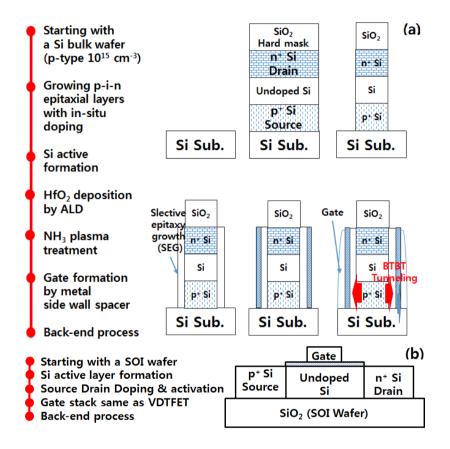

| Figure 3.2 | Key fabrication steps. (a) Starting with a Si bulk wafer.  |    |

|            | (b) Growing the p-i-n epitaxial layers with in-situ dop-   |    |

|            | ing. (c) Patterning and Etching the p-i-n layers (d) grow- |    |

|            | ing the channel layer with SEG (e) Depositing gate di-     |    |

|            | electric (f) Forming a metal gate side wall spacer         | 28 |

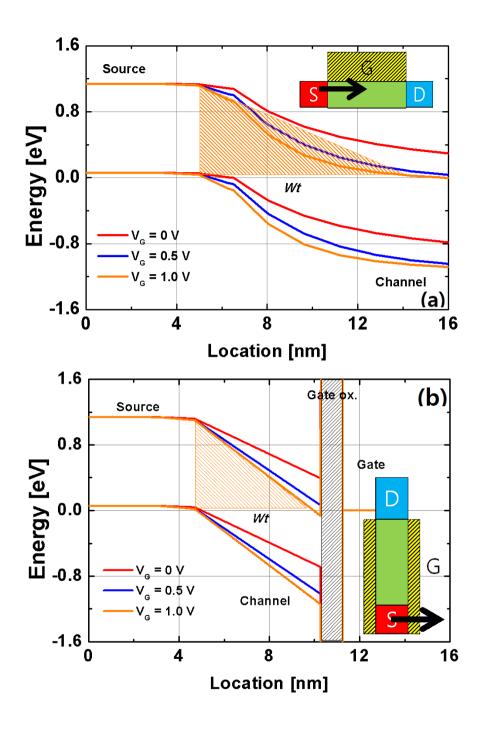

| Figure 3.3 | Simulated energy band diagram changes as a function of            |    |

|------------|-------------------------------------------------------------------|----|

|            | gate voltage in (a) Conventional planar TFETs and in              |    |

|            | (b) the proposed TFETs                                            | 31 |

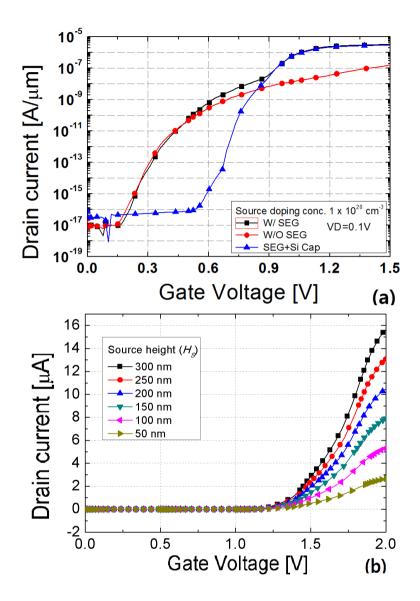

| Figure 3.4 | (a) $I_D$ – $V_D$ characteristic of a vertical structure TFETs    |    |

|            | devices with SEG layer and without SEG layer. The de-             |    |

|            | vice with SEG layer shows hump phenomena. (b) $I_D \!\!-\!\! V_D$ |    |

|            | characteristics of a vertical structure TFETs device de-          |    |

|            | pending on various heights of source                              | 32 |

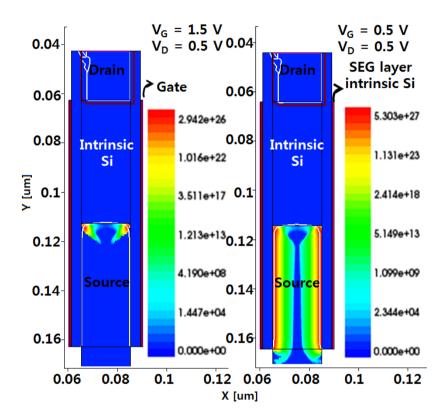

| Figure 3.5 | Band to band tunnel rate. The dominant tunnel region              |    |

|            | changed by applied gate voltage                                   | 33 |

| Figure 4.1 | (a) Schematic diagram and process flow for the proposed           |    |

|            | TFETs. Between the intrinsic Si layers and the source             |    |

|            | regions, the tunnel junctions are formed. (b) Schematic           |    |

|            | diagram and process flow for conventional TFETs. $$               | 38 |

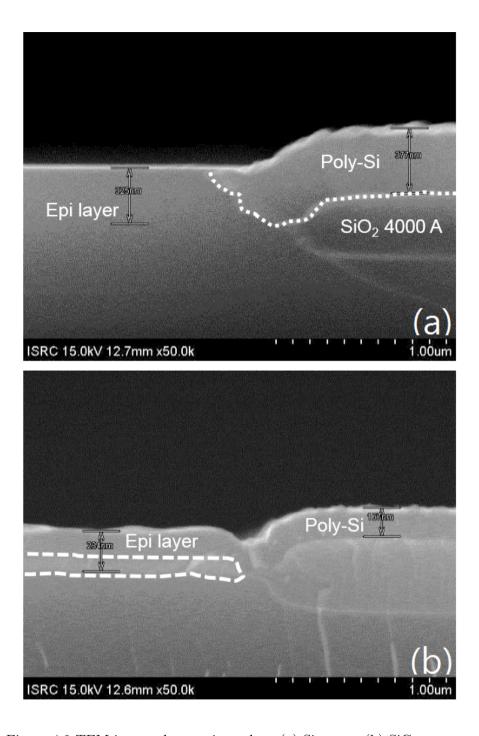

| Figure 4.2 | TEM image about epitaxy layer(a) Si source (b) SiGe               |    |

|            | source                                                            | 39 |

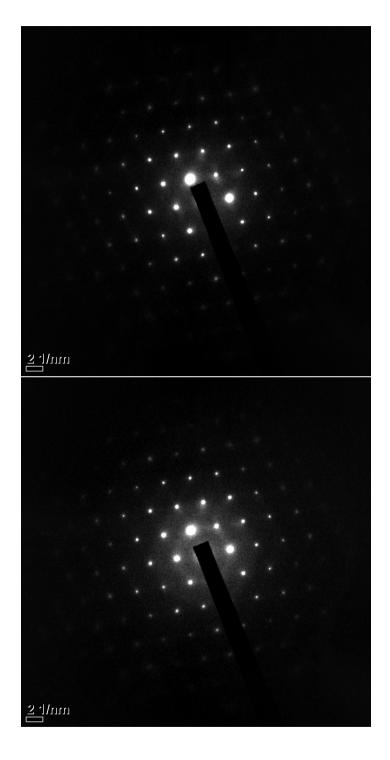

| Figure 4.3 | The selected-area electron diffraction analysis of(a) Si          |    |

|            | (b) SiGe                                                          | 40 |

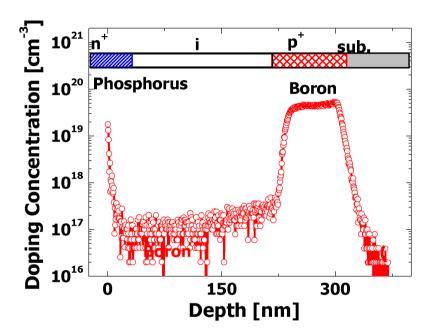

| Figure 4.4 | SIMS profile indicating phosphorus and boron concen-              |    |

|            | tration vs. depth. The dopants are doped by in-situ method        |    |

|            | when the Si layers are grown                                      | 41 |

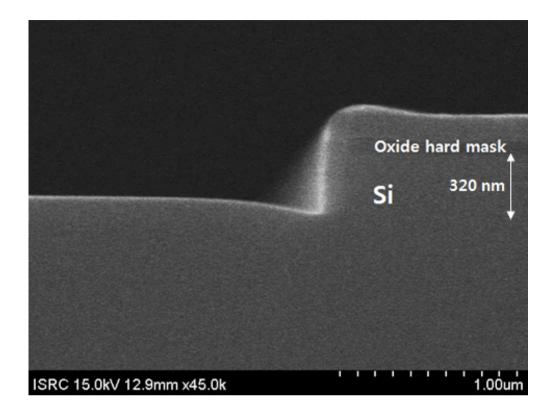

| Figure 4.5 | SEM image of active patterning with RIE process                   | 42 |

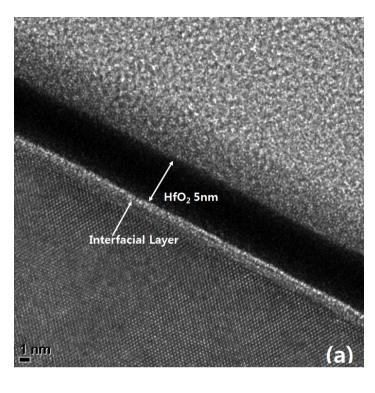

| Figure 4.6  | (a) Cross-sectional TEM image of a 5nm- $\mathrm{HfO}_2$ film   |    |

|-------------|-----------------------------------------------------------------|----|

|             | grown by ALD (b) AES depth profiles of $HfO_2$ films            |    |

|             | after NH <sub>3</sub> plasma treatment                          | 44 |

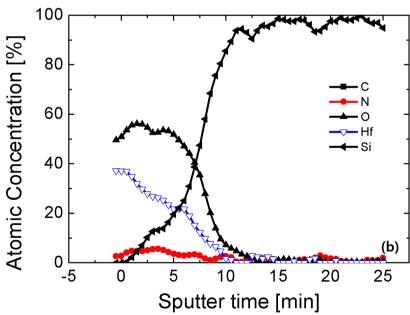

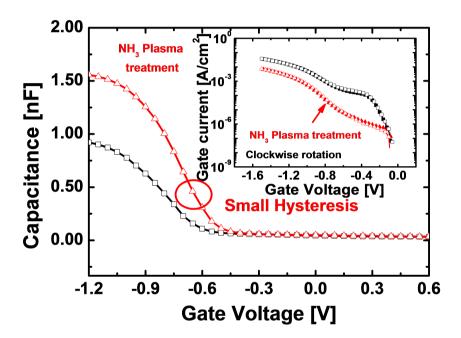

| Figure 4.7  | Measured hysteresis $C{-}V$ curves of MOS capacitors with       |    |

|             | high- $\kappa/$ metal gate stacks. The inset shows gate leakage |    |

|             | current                                                         | 45 |

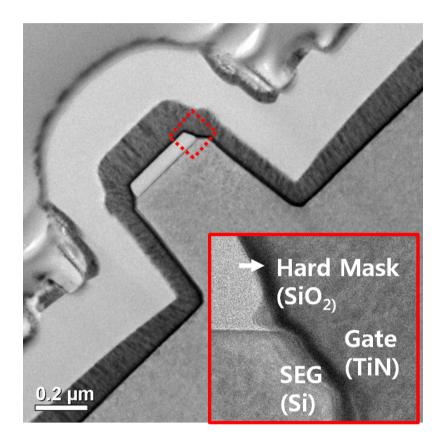

| Figure 4.8  | Cross-sectional HRTEM image which demonstrates fin              |    |

|             | structure. The thin epitaxially grown Si layer has 13 nm $$     |    |

|             | thickness.                                                      | 46 |

| Figure 4.9  | (a) Transfer characteristics of the proposed TFETs and          |    |

|             | conventional planar TFETs. (b) Output characteristics           |    |

|             | of proposed TFETs measured at various gate voltages             | 48 |

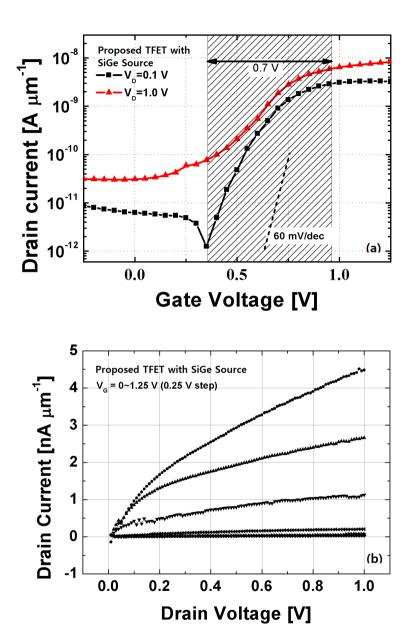

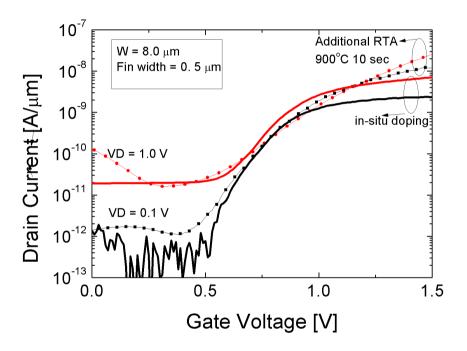

| Figure 4.10 | (a) Transfer characteristic of the proposed TFETs with          |    |

|             | SiGe source. (b) Output characteristic of the proposed          |    |

|             | TFETs measured at various gate voltages                         | 49 |

| Figure 4.11 | SS of the proposed TFETs with Si source as a func-              |    |

|             | tion of drain current measured by forward and reverse           |    |

|             | sweeps. The the proposed TFETs show steep SS below              |    |

|             | $20~\mathrm{mV/dec}$ in both forward and reverse sweeps         | 50 |

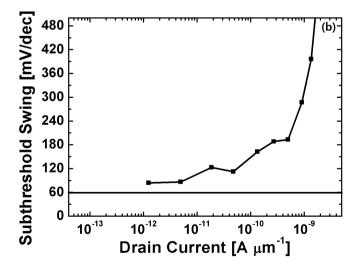

| Figure 4.12 | SS of the proposed TFETs with SiGe source as a func-            |    |

|             | tion of drain current.                                          | 50 |

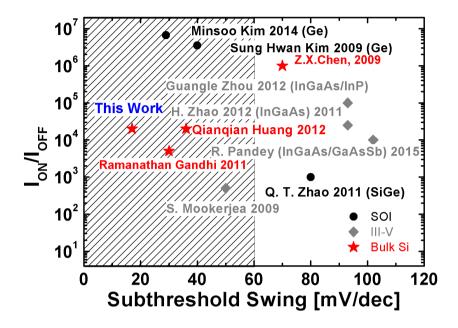

| Figure 4.13 | Performance comparison of TFETs. $I_{ON}/I_{OFF}$ of TFETs                    |    |

|-------------|-------------------------------------------------------------------------------|----|

|             | as a function of subthreshold swing                                           | 51 |

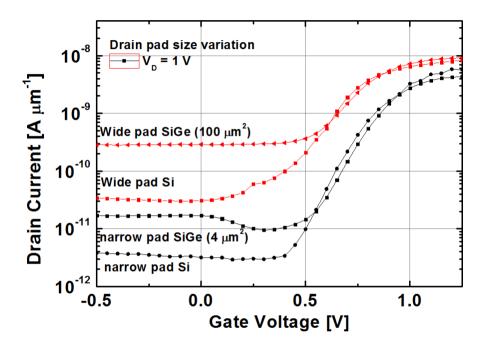

| Figure 4.14 | Transfer curves with various contact size. The $I_{OFF}$ is                   |    |

|             | depend on the pad size                                                        | 53 |

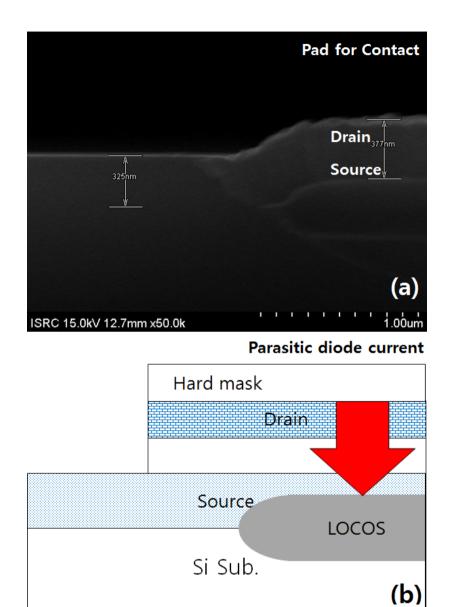

| Figure 4.15 | (a)Cross-sectional image of drain pad, (b)Illustration of                     |    |

|             | parasitic diode current in drain pad                                          | 55 |

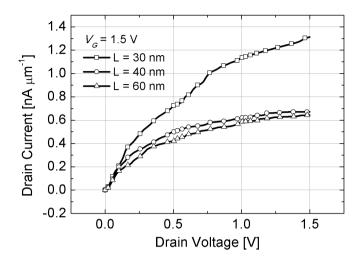

| Figure 4.16 | Output characteristic of the proposed TFETs simulated                         |    |

|             | with various channel length                                                   | 56 |

| Figure 4.17 | Transfer curves of the proposed TFETs. In the plot, the                       |    |

|             | ambipolar characteristics are confirmed at -2.5 V of $V_G$ .                  | 57 |

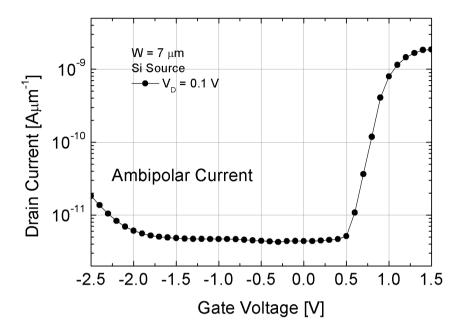

| Figure 4.18 | Transfer curve of the proposed TFETs with additional                          |    |

|             | RTA process                                                                   | 58 |

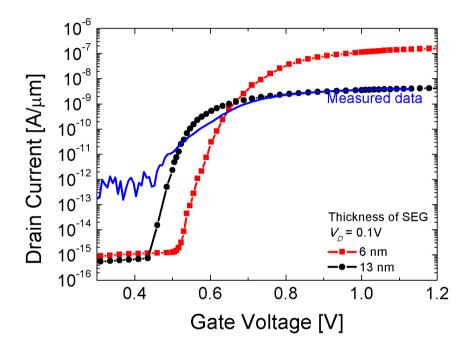

| Figure 4.19 | Transfer curves of the proposed TFETs and simulated                           |    |

|             | TFETs. In the plot, the simulation results show effects                       |    |

|             | of thickness of the SEG layer                                                 | 60 |

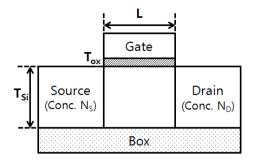

| Figure 6.1  | Schematic cross view of TFET devices. The parameter                           |    |

|             | which is used in the simulation are summarized in table.                      | 73 |

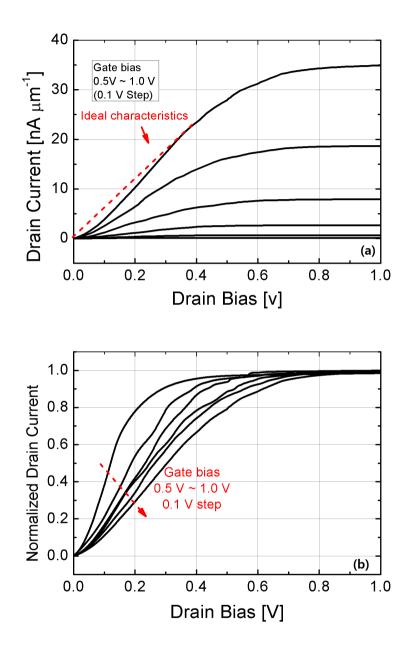

| Figure 6.2  | (a) Output characteristics in TFETs. The gate bias is                         |    |

|             | applied from $0.5~\mathrm{V}$ to $1.0~\mathrm{V}$ . The super-linear onset is |    |

|             | verified in the region of small drain bias. (b) Normalized                    |    |

|             | output characteristics in TFETs                                               | 75 |

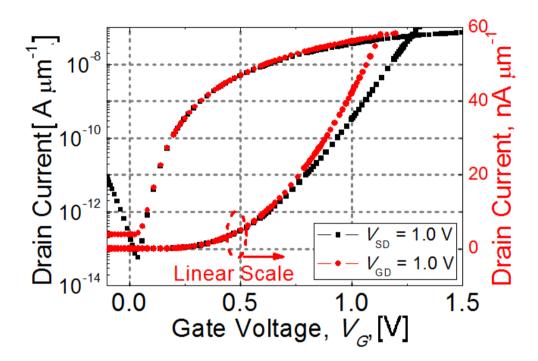

| Figure 6.3  | Transfer curves in TFETs. The tunnel current is satu-                                              |    |

|-------------|----------------------------------------------------------------------------------------------------|----|

|             | rated at $V_{SD}=1.0~\mathrm{V}$ due to the channel inversion                                      | 76 |

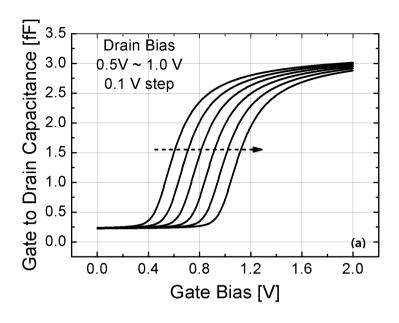

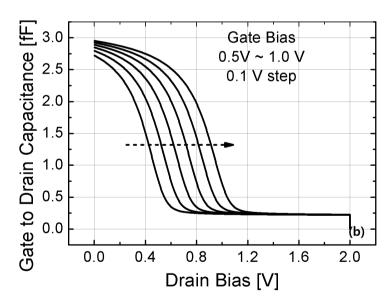

| Figure 6.4  | Capacitance–voltage characteristics showing gate-to-drain                                          |    |

|             | $(C_{GD})$ capacitances as a function of (a) $V_{GS}$ (b) $V_{DS}$ .                               | 77 |

| Figure 6.5  | Energy band diagram when applying high gate bias and                                               |    |

|             | low drain bias                                                                                     | 79 |

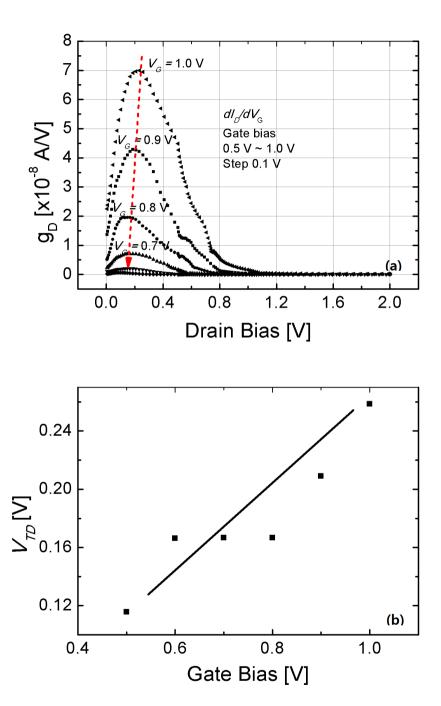

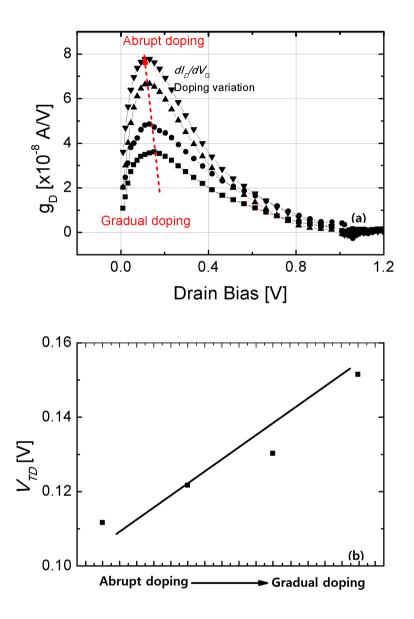

| Figure 6.6  | (a) $dI_D/dV_{DS}$ $(g_D)$ as a function of $V_D$ for various $V_G$ s.                             |    |

|             | (b) Threshold voltage in terms of $V_{DS}$                                                         | 81 |

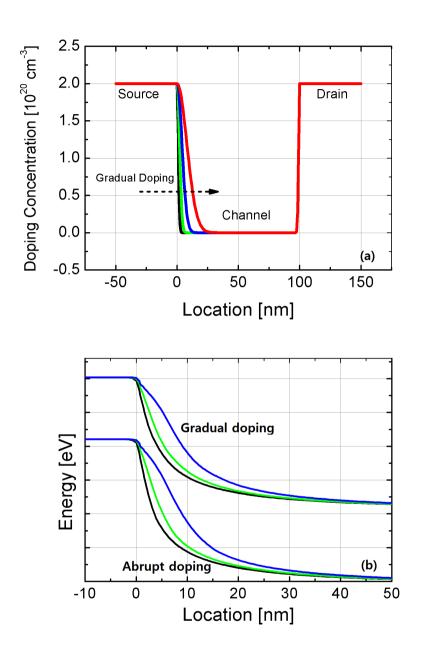

| Figure 6.7  | (a) Doping profile. only source region modulates the                                               |    |

|             | doping profile. (b) energy band diagram. A source with                                             |    |

|             | abrupt doping profile makes a small tunnel resistance. $% \left( 1,,1\right) =\left( 1,,1\right) $ | 82 |

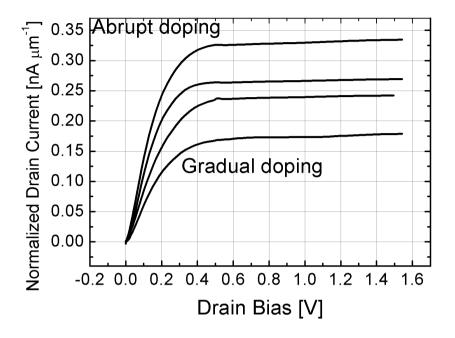

| Figure 6.8  | Output characteristics in TFET for different doping pro-                                           |    |

|             | file                                                                                               | 83 |

| Figure 6.9  | (a) $dI_D/dV_{DS}$ $(g_D)$ as a function of $V_D$ for various doping                               |    |

|             | profile. (b) Threshold voltage in terms of $V_{DS}$                                                | 84 |

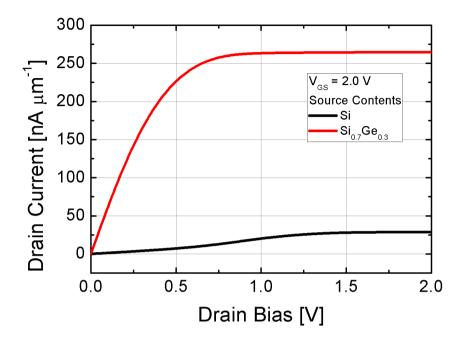

| Figure 6.10 | Output characteristics of TFETs with Si or SiGe source.                                            |    |

|             | The device with $Si_{0.7}Ge_{0.3}$ source do not show super-                                       |    |

|             | linear onset                                                                                       | 85 |

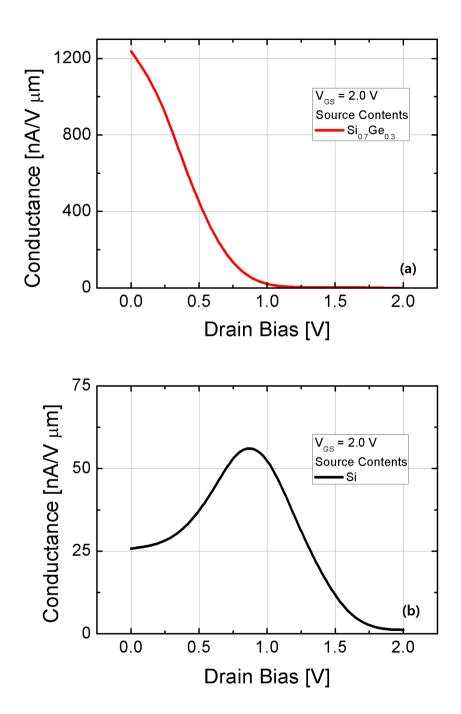

| Figure 6.11 | $dI_D/dV_{DS}\ (g_D)$ as a function of $V_D$ by Ge contents (a)                                    |    |

|             | $Si_{0.7}Ge_{0.3}$ source (b) Si source                                                            | 87 |

# List of Tables

| Table 1.1 | ITRS specs referred to year 2020 for multi-gate transistors. | Ĝ  |

|-----------|--------------------------------------------------------------|----|

| Table 2.1 | Simulated device parameters for the BTBT                     | 18 |

| Table 3.1 | Simulated device parameters for the proposed TFETs           | 29 |

# Chapter 1

## Introduction

#### 1.1 Power issues on CMOS technologies

During the last few decades, semiconductor devices and systems have been utilized and exploded. The miniaturization of semiconductor brings more features on chips and functionality at the lower cost. However a semiconductor industry is facing a serious obstacle. Although scale-down of the semiconductor has allowed a dramatic improvement, a power dissipation per unit area has been also equally increased [1]. In detail, a static power and a dynamic power have been considered as two principal sources of the power dissipation (Eq. 1.1). One of power dissipation is the static power. Whenever transistors are turned on or off, the static power is sustained from current that leaks through the transistors. The other is the dynamic power, which occurs from the repeated capacitance charge and discharge (Fig. 1.1). In the past, the dynamic power had been fo-

Figure 1.1 A power dissipation with the static power and the dynamic power (Courtesy: ITRS)

cused on a major source of the power consumption, and it has been controlled by scale-down of transistors and supply voltage. The dynamic power is proportional to the square of the supply voltage. Recently, however, the scale-downed transistors have aggravated the leakage current, so the static power begins to dominate the power consumption. The following equation defines overall power consumption as the sum of the dynamic and static power:

$$P = ACV^2 f + VI_{leak} (1.1)$$

where A is the fraction of gates actively switching and C is the total capacitance

load. The first term is the dynamic power lost from charging and discharging the load capacitors. The second term means the static power lost due to leakage current. In the Eq. 1.2, the leakage current ( $I_{leak}$ ) shows dependency on threshold voltage and supply voltage:

$$I_{leak} = KWe^{\frac{-V_T}{nV_0}} (1 - e^{\frac{-V_{DD}}{V_0}})$$

(1.2)

K and n are experimentally derived, W is the gate width, and  $V_0$  in the exponents is the thermal voltage. At room temperature,  $V_0$  is about 25 mV. Eq. 1.2 suggests two methods to reduce  $I_{leak}$ . The first solution is to shrink the supply voltage  $(V_{DD})$  or to turn off the device. Second, increasing the threshold voltage will be another solution for the negative term in the Eq. 1.2.

In the most recent decade, however, the gate overdrive voltage  $(V_{DD}-V_T)$  has not been reduced proportionately with the transistor size (Fig. 1.2). Therefore, as the number and density of transistors on a chip have increased, the peak power density has also increased dramatically.

#### 1.2 Tunnel Field Effect Transistors

In the previous section, the power dissipation has been mentioned. Many research groups have studied developing novel devices which can be operated in very low power [4]-[5]. Among these devices, the TFETs have been studied extensively due to outstanding subthreshold characteristics and capability for the

Figure 1.2 Trends for MOSFETs threshold voltage  $(V_T)$ , operating voltage  $(V_{DD})$ , and corresponding transistor OFF-state leakage  $(I_{OFF})$  [2].

low-power operation [6]-[10]. In the case of MOSFETs, which are conventionally used in almost every circuit (Fig 1.3(a)), there exists theoretical limit of 60 mV/dec subthreshold swing (SS) at room temperature (RT) because their carrier injection is based on thermionic emission (Eq.1.3) (Fig. 1.3(b)) [11]-[12].

$$SS = \left(\frac{dI_D}{dlogV_G}\right)^{-1} = \left(1 + \frac{C_{DEP}}{C_{OX}}\right) \left(\frac{kT}{q}ln10\right)$$

(1.3)

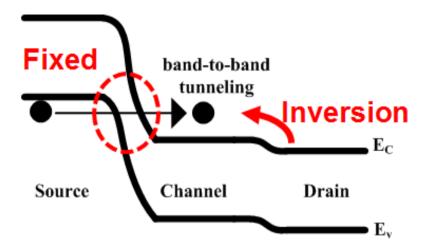

Considering operation of the TFETs which has opposite doping types with a source and a drain (Fig.1.3(b)), it has no theoretical limit by the thermionic carrier injection. Fig. 1.3(d) shows a energy band diagram to illustrate a tunnel process. When the TFETs are applied with  $V_G$ , electrons in the source transfer

Figure 1.3 Schematic cross-sectional view of (a) MOSFETs and (b) TFETs. (c) The operation of a MOSFETs are based on the thermionic emission. (d) The operation of a TFETs are based on BTBT [3].

to the channel due to band banding. The tunnel process has been proposed as a current conduction mechanism. This is because the TFETs have weak dependence on the Boltzmann distribution and the BTBT dominates the carrier injection that can be switched more abruptly than the thermionic injection [13]-[14]. Thus, a SS can be scaled down to sub-60 mV/dec at RT. The transistors using this mechanism is ideal in that abrupt switching behavior which, in principle, allows  $V_{DD}$ - $V_T$  to be scaled down aggressively while maintaining high  $I_{ON}$  (Fig. 1.4).

#### 1.3 Issue for TFETs

The TFETs have been studied extensively due to remarkable low SS and capability for the low-power operation. However, the experimental demonstrations of TFETs have considerable discrepancy compared with the theoretical studies to satisfy the required performance. An issue for the fabricated TFETs is on their poor electrical performances; low ON-current ( $I_{ON}$ ) and large SS, which are mainly attributed to the poor BTBT rate. In order to enhance the BTBT rate, the TFETs with double gate (DG) or gate-all-around structure are considered as a promising candidate due to the high controllability of gate on channel. And the abrupt junction between source and channel should be made. Then, the dopant profile has better abrupt junction. Moreover, it needs to employ hetero-junction technology such as silicon-germanium (SiGe), germanium (Ge), germanium-tin (GeSn), and III-V compound materials [15]-[16].

Figure 1.4 The switching properties of MOSFETs and TFETs.

The other issue is that the TFETs are the devices with a floating body. Since the source and drain in the TFETs have opposite doping types to make a p-i-n junction, the TFETs should be fabricated on a Silicon on insulator (SOI) substrate which is totally incompatible to CMOS process. Those devices, however, inevitably face self-heating effect and high fabrication cost. Moreover, in order to co-integrate with the MOSFETs with a bulk substrate, the TFETs should be fabricated without the SOI wafer.

#### 1.4 Propose of the Target Device

In the previous section, the low power operation has been emphasized. In the MOSFET devices which have been utilized as industrial standard devices, the SS had been fundamentally limited to 60 mV/dec due to carrier injection that obey the Boltzmann statistics. As a result, a novel switch with entirely different carrier injection mechanism needs to be investigated. In the previous section, the several disadvantages of the TFETs were addressed. In many papers, the ON-current for the TFETs has been demonstrated to be quite below ITRS requirements [2]. Several studies showed dramatically improved  $I_{ON}/I_{OFF}$  ratio and highly boosted ON-current utilizing novel structure for gate controllability and material for band-gap engineering. However, as the ITRS Roadmap, the ON-current and OFF-current are suggested with 0.6 mA and 10 pA in LSTP(Low Standby Power) category. Considering characteristics of TFETs, the proposed TFETs are aimed to achieve performances in terms of SS and  $I_{ON}/I_{OFF}$  ratio

Table 1.1 ITRS specs referred to year 2020 for multi-gate transistors.

| Device                               | Low Standby Power | Low Operation Power | High Power |

|--------------------------------------|-------------------|---------------------|------------|

| $V_{DD}$ [V]                         | 0.67              | 0.53                | 0.68       |

| $I_{ON} [\mathrm{nA}/\mu\mathrm{m}]$ | 0.01              | 5                   | 100        |

| $I_{OFF} [{\rm mA}/\mu{\rm m}]$      | 0.6               | 0.78                | 1.96       |

(sub 60 mV/dec SS and  $10^4 I_{OFF}/I_{OFF}$  for sub-0.7 V gate overdrive) (Table 1.1). In order to meet the requirement of the ITRS, the ON-current of the TFETs should be boosted. In order to satisfy the current requirement, several technologies have been suggested in this paper.

Firstly, the TFETs are adapted to a high- $\kappa$  gate dielectric. Then, the ON-current will be enhanced due to the high density of gate electric field. Moreover, the most important advantage TFETs has is the TFETs have low OFF-current. Therefore, employing the high- $\kappa$  dielectric which contribute to boost the ON-current is an essential technology for the TFETs.

Secondly, as many papers have reported, the ON-current in the TFETs is determined with a tunnel width between source and channel [10]. A design for BTBT perpendicular to the channel direction (vertical BTBT) has two effects on the TFETs. One of the effects is the channel thickness limits to tunnel width. It is expected to enhance ON-current by adopting the thin tunnel width formed by an epitaxy. The other effect is that a tunnel junction area is increased by adjusting the gate and source overlaps.

Figure 1.5 Cross sectional view of the MOSFETs and TFETs. Considering cointegration within bulk substrate, the TFETs with vertical structure are highly efficient.

Finally, a vertical structure is applied. The biggest merit of the vertical structure is that the channel can be isolated without silicon-on-insulator (SOI) substrate. Therefore, by using the vertical structure, the TFETs and MOSFETs can be integrated in the same bulk substrate. (Fig. 1.5).

#### 1.5 Thesis outline

This dissertation is to propose and implement a novel TFETs. Especially, it is important to present highly improved electrical performances including low SS and high  $I_{ON}$ . All of the performance and process have been predicted by Technology Computer-Aided Design (TCAD) simulation with reliable model

parameters. Then the proposed TFETs have been verified with measured results.

In Chapter 2, planar Si and SiGe TFETs are fabricated as a reference device. By using these device, basic characteristics of the TFETs are confirmed. Then, electrical characteristics are analyzed and calibrated with the BTBT model. The model parameter of BTBT based on Kane's formulation is fitted with measured data. The BTBT model parameters used by the device simulation in this dissertation (Sentaurus Device) are utilized to design novel devices and then used for a optimization study.

Chapter 3 presents novel TFETs design. The proposed TFETs have feature for vertical structure with BTBT perpendicular to the channel. The perpendicular BTBT is employed to achieve low SS and enhance the tunnel current. Additionally, the vertical structure TFETs have advantages for the integration with high density. Then, the electrical performance and side effect are confirmed before the proposed TFETs are fabricated.

Chapter 4 examines the proposed devices. A total process of the fabrication is explained with details. Then, electrical performance is measured and compared with that of other groups. Finally, the proposed TFETs are analyzed and discussed to increase electrical performance.

Chapter 5 has conclusions of this paper and suggestions for future works to enhance performance.

# Chapter 2

# Planar Si & SiGe TFET

In this chapter, Si and SiGe TFETs with planar structure are fabricated and measured to extract model parameters. Although TCAD simulation tool reflects real physics and has accurate material characteristics which are well-estimated, the TFETs, simulated with the BTBT model, needs to be calibrated. After the model calibration, from the extracted model parameter, performance of the proposed device will be estimated and predicted.

#### 2.1 Device fabrication

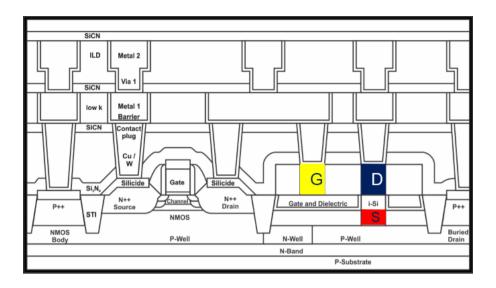

In order to prepare the planar TFETs as a reference, the TFETs had been fabricated on SOI wafer with CMOS compatibility. Fig. 2.1 illustrates a cross-sectional view of the fabricated TFETs and key processes. First, an active region was defined on 100 nm thickness. Then, gate dielectric was formed by dry

Figure 2.1 Schematic diagram and process flow for the Si and SiGe TFETs.

oxidation. The dry oxidation of 800 °C was performed during 30 sec. Then, a gate electrode was deposited with a poly-Si. The gate electrode was defined by photo-lithography and dry etch. Note that all of the pattens in this fabrication process were defined by i-line photo-lithography where the limit of the pattern size was 0.25  $\mu$ m. A source and a drain regions were doped with  $BF_2^+$  (8 x  $10^{14}$  cm<sup>-3</sup>, 10 keV, 7° tilt) and arsenic (8 x  $10^{14}$ cm<sup>-3</sup>, 10 keV, 7° tilt), respectively. In order to activate the dopant, rapid thermal annealing (RTA) process of 900 °C was performed during 5 sec. Finally, inter-layer dielectric (ILD) was formed with tetra-ethyl-ortho-silicate (TEOS) oxide by PECVD process and metal layers (Ti/TiN/Al/TiN stacks) were deposited by physical vapor deposition (PVD) process to make a contact. Then, current and capacitance were measured by using the HP 4156 C semiconductor parameter analyzer and HP 4284 A precision LCR meter, respectively. The detailed process and recipe were described in Appendix section 2.5.

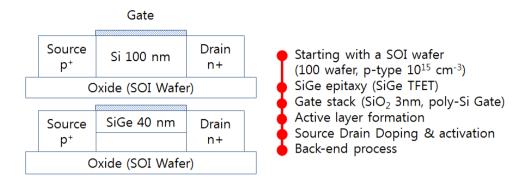

Figure 2.2 Measured  $I_D$ – $V_G$  characteristics of planar-TFETs device with Si and SiGe substrate. The devices with SiGe TFETs show better current drivability than Si TFETs.

#### 2.2 Measured Results

Fig. 2.2 shows the transfer characteristics of the fabricated Si TFETs and SiGe TFETs at 0.1 and 1.0 V drain voltages  $(V_D)$ . Measured TFETs have channel length and width of 400 nm and 400 nm respectively. The performance can be further improved by band-gap engineered TFETs with SiGe. In the Si and SiGe TFETs, the devices exhibit average slope of 415 and 165 mV/dec over one order of magnitude of  $I_D$  at  $V_D = 0.1$  V respectively. The  $I_{ON}/I_{OFF}$  ratio reaches  $10^4$  at  $V_D = 0.1$  V and  $V_G = 1.0$  V. Due to the small energy band of SiGe TFETs,

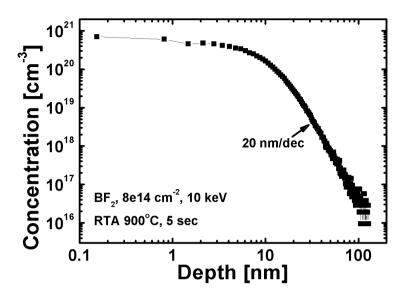

the subthreshold swing (SS) and  $I_{ON}$  are much better than that of Si TFETs. More specifically, the  $I_{ON}$  is about 10 times higher than that of Si TFETs. However, the SS is still above 60 mV/dec known as the limit of MOSFETs. The reason of degraded performance is the large tunnel resistance between source and channel. Note that, for the device using tunnel mechanism, broad doping gradient degrades gate modulation of the band-bending. Hence, to increase the tunnel current, the tunnel resistance should be reduced. Before proposing novel device, the dopant profile from the source to the channel should be identified to compare performances exactly as a reference. In order to confirm the source dopant profile, a secondary ion mass spectrometry (SIMS) is performed at the test sample which is fabricated with the same implantation and RTA processes. Fig 2.3. shows SIMS profile of boron and the dopant profile has 20 nm/dec slope.

Fig. 2.4 shows the output characteristics of Si and SiGe TFETs. The SiGe TFETs have larger current drivability than that of Si TFETs. Drive current of n-type SiGe TFETs is increased more 10 times more than that of Si TFET devices. Interestingly, the measured results show that a super-linear onset is definitely shown in the Si TFETs. When a large  $V_G$  and a very small  $V_D$  are applied, the phenomena is observed whereas the super-linear onset cannot be observed in any other bias condition. In the appendix chapter, the super-linear onset is investigated more detailedly.

Figure 2.3 Boron concentration profile from surface to bulk direction using SIMS.

Figure 2.4 Measured output characteristics of n-type Si and SiGe TFETs.

#### 2.3 BTBT model calibrations

In the previous section, the TFETs with planar structure were fabricated as a reference device for extracting tunnel parameters. In order to study and confirm the proposed device performance, the planar TFETs were used for calibrating band-to-band tunnel (BTBT) model. This calibration is validated as the reference for all the devices evaluated in the following chapters. Note that, gate leakage and contact resistance are not considered. Additionally the used models are followed: Fermi statistics, drift-diffusion carrier transport, band-gap narrowing and Shockley-Read-Hall (SRH) recombination models. The calibrated BTBT generation rates G per unit volume in this model are defined as

$$G = A\left(\frac{F}{F_0}\right)^P exp\left(-\frac{B}{F}\right) \tag{2.1}$$

where  $F_0 = 1$  V/m and P = 2.5. F is electric field. A is prefactor and B is exponential factor. The parameters of A and B are based on the Kane's model. For current fitting, simulation is performed based on experimental results of the fabricated TFETs. Fig. 2.5 shows the simulation results and measured results at  $V_D$  of 1.0 V with Si and SiGe TFETs. The simulation results for these parameters clearly show an excellent match with the experimental results (Table 2.1).

Figure 2.5 Parameter calibration curves with simulation and measurement results of TFETs.

Table 2.1 Simulated device parameters for the BTBT.

| parameter | Si                 | SiGe            | Unit            |

|-----------|--------------------|-----------------|-----------------|

| A         | $4 \times 10^{14}$ | $3 \ge 10^{16}$ | $cm^{-1}s^{-1}$ |

| В         | $9 \ge 10^6$       | $7 \ge 10^5$    | V/cm            |

## 2.4 Summary

In this chapter, the planar SiGe TFETs are fabricated and analyzed before implementing proposed TFETs. Based on the fabricated planar TFETs, the performance of the device has been evaluated and compared. Compared with Si TFETs, the SiGe TFETs show improved performance due to the small bandgap. As a reference device, the Si and SiGe TFETs are applied and calibrated to the tunnel models with a device simulation.

### 2.5 Appendix: Process Flow

## Recipe

#### 1. Wet station

| Process name | Temp      | Chemical               | Time | QDR  | Equipment   |

|--------------|-----------|------------------------|------|------|-------------|

| SC1 B Bath   | 80°C      | NH4OH:H2O2:D.I=1:1:5   | 600s | 360s |             |

| SC2 A Bath   | 80°C      | HCI : H2O2 : D.I=1:1:5 | 600s | 360s |             |

| HF C Bath    | Room Temp | HF: DI = 1:100         | 30s  | 360s | Wet station |

| SPM          | 120°C     | H2SO4 : H2O2 = 4 : 1   | 600s | 360s |             |

| PR Strip     | 120°C     | H2SO4 : H2O2 = 4 : 1   | 600s | 360s |             |

#### 2. Photolithgraphy

| Bottom material PR | Coating   |                | Exposure         | Equipment  |                 |

|--------------------|-----------|----------------|------------------|------------|-----------------|

|                    | RPM / sec | Rcp. / Coat No | msec / focus     | Equipment  |                 |

| Si, SiNx, SiO2     | SS03A9    | 4500 / 35      | 17 / 80(w/o EBR) | 320 / -1.5 | Nikon i-liner   |

| TiN                | SS03A9    | 4000 / 35      | 17 / 80(w/o EBR) | 320 / -1.5 | - Nikon I-liner |

#### 3. Epitaxy

| or apreasty   |      |                                                                               |            |     |             |

|---------------|------|-------------------------------------------------------------------------------|------------|-----|-------------|

| Process name  | Temp | Gas                                                                           | Epi rate   | ETC | Equipment   |

|               |      | pre-clean [180 sec, SF6 5ccm, H2 347 sccm]                                    | 2.68 Å/sec |     | Eureka 2000 |

| SiGe          | 600  | pre-clean [60 sec, Cl2 10 sccm, H2 70 sccm]                                   |            |     |             |

|               |      | [Si2H4 15 sccm, GeH4 45 sccm]                                                 |            |     |             |

| Si            | 750  | [Si2H6 50sccm]                                                                | 1.28 Å/sec |     |             |

| SiGe(Boron)   | 670  | H 20sccm 184sec, SiH4 20 sccm, GeH4 60<br>sccm 184 sec, B2H6 1.6 sccm, 30torr | 7.4 Å/sec  |     |             |

| Si(intrinsic) | 720  | 20H,50SiH4,30torr,356sec                                                      | 2.8 Å/sec  |     |             |

| Si(phospours) | 720  | 20H,50SiH4,127/127/7.3 PH3,30torr,183sec                                      | 1.38 Å/sec |     |             |

| Si(Boron)     | 640  | 20H,50SiH4,116.59/116.59/8.34B2H6                                             | 2.72 Å/sec |     |             |

#### 4. Etch

| Process name | Temp | Gas                                      | Etch rate  | ETC                  | Equipment |

|--------------|------|------------------------------------------|------------|----------------------|-----------|

| Si etch      | RT   | HBr 20 sccm, O2 1sccm, 2mT, He 9800 Torr | 33.2 Å/sec | Power (T/B) 900/80 W | STS       |

| SiO2 etch    | RT   | CHF3 25 sccm, CF4 5 sccm, Ar 70 sccm     | 50 Å/sec   |                      | P-5000    |

| SiNx etch    | RT   | CHF3 15 sccm, CF4 10 sccm, Ar 30 sccm    | 50 Å/sec   |                      | F-3000    |

#### 5. Deposition

| Process name | Temp | Gas                                | Deposition rate | ETC       | Equipment |

|--------------|------|------------------------------------|-----------------|-----------|-----------|

| SiNx         | 785  | DCS: 30sccm, NH3:100sccm, 200mTorr | 40 Å/min        |           | SHF-150L  |

| Poly-Si      | 630  | SiH4: 60sccm, 150mTorr             | 100 Å/min       |           |           |

| TEOS         | 380  | TEOS 700 sccm, 9mTorr, O2 700 sccm | 70 Å/sec        |           | P-5000    |

| TiN          | 200  | Ar 15 sccm, N2 85 sccm             | 11.62 Å/sec     | Power 5kW |           |

| Ti           | 200  | Ar 58 sccm                         | 18.29 Å/sec     | Power 2kW | Endura    |

| Al           | 200  | Ar 30 sccm                         | 125 Å/sec       | Power 6kW |           |

20

### Planar TFET

| LASER MARKER Marking wafer number in backside  W13A(WA-13,C1-6)SPM-CLEANING Initial cleaning W5A(WA-5,C1-6) SC-1,2 CLEANING RCA cleaning, HF dip  CMOS FURNACE II - WET OXIDATION Sol thinning process  Active layer pattern Active photo (Reticle : ACT)  CMOS IPPOLY ETCHER Trench etch 1000A +/-10%, E/R check a-step and SEM  CMOS PA SHER PR ashing  WET STATION WA-2 SPM PR STRIP PR strip  W5A(WA-5,C1-6) SC-1,2 CLEANING RCA cleaning, HF dip  CMOS POLY ETCHER Trench etch 1000A +/-10%, E/R check a-step and SEM  CMOS PR ASHER RCA cleaning, HF dip  W5A(WA-5,C1-6) SC-1,2 CLEANING RCA cleaning, HF dip  CMOS FURNACE II - DRY OXIDATION Gate p-Si depo 2000A +/-10%, THK at nanospec PR TRACK PR coating, develop  NIKON STEPPER Gate etch, 2000A 20% over, E/R check, pattern test  CMOS PR ASHER  RRACK PR cating Gate evelop  NIKON STEPPER Gate etch, 2000A 20% over, E/R check, pattern test  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP  GRE etch, 2000A 20% over, E/R check, pattern test  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP  PR strip  RRACK PR coating, develop  NIKON STEPPER Gate etch, 2000A 20% over, E/R check, pattern test  CMOS PR ASHER PR strip  PR Strip  PR STRIP  PR STRIP  PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP PR STRIP | Seq-No | Process Name                                              | Process Specification           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------------|---------------------------------|

| Marking wafer number in backside  ### W13A(WA-13,C1-6)SPM-CLEANING   Initial cleaning    ### W3A(WA-5,C1-6) SC-1,2 CLEANING    ### W15 W3A(WA-5,C1-6) SC-1,2 CLEANING    ### W15 W3A(WA-1,C1-6) W3A(WA-1,C10% Thickness checked by ellipsometer    ### W15 W3A(WA-1,C1-6) W4-7-10% Thickness checked by ellipsometer    ### W4 W4-110 W4-1 | 10     | LASER MARKER                                              | SOI wafer and bulk wafer (test) |

| Initial cleaning WSA(WA-5,C1-6) SC-1,2 CLEANING RCA cleaning, HF dip  CMOS FURNACE II - WET OXIDATION Sol thinning process Oxidation for thinning 1000A +/-10% Thickness checked by ellipsometer PR TRACK PR coating, develop  NIKON STEPPER Active layer pattern Active photo [Reticle : ACT] CMOS ICP POLY ETCHER CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP PR trunace cleaning for gate oxidation, HF dip  WSA(WA-5,C1-6) SC-1,2 CLEANING RCA cleaning, HF dip  CMOS FURNACE II - DRY OXIDATION OXIDATION TO THINNING SUN-47-3% THICKNESS CHECKED BY AUGUSTON OXIDATION Gate p-Si depo 2000A +/-10%, THK at nanospec PR TRACK PR coating, develop  NIKON STEPPER Gate etch, 2000A 20% over, E/R check, pattern test  CMOS PR ASHER PR sshing  WET STATION WA-2 SPM PR STRIP  PR STRIP  PR STRIP  100 GAGE p-Si depo 2000A 20% over, E/R check, pattern test  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP PR TRACK PR coating, develop NIKON STEPPER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10     | Marking wafer number in backside                          |                                 |

| Initial cleaning WSA(WA-5,C1-6) SC-1,2 CLEANING RCA cleaning, HF dip  Oxidation for thinning 1000A +/-10% Thickness checked by ellipsometer  PR TRACK PR coating, develop NIKON STEPPER Active photo [Reticle : ACT]  CMOS ICP POLY ETCHER Trench etch 1000A +/-10%, E/R check a-step and SEM  WET STATION WA-2 SPM PR STRIP PR strip  W13A(WA-13,C1-6)SPM-CLEANING Pre Furnace cleaning for gate oxidation, HF dip  W5A(WA-5,C1-6) SC-1,2 CLEANING RCA cleaning, HF dip  CMOS PR ASHER 100 RCA cleaning, HF dip  CMOS FURNACE II - DRY OXIDATION OXIGIATION TURNING SIDE OXIDATION Gate p-Si depo 2000A +/-10%, THK at nanospec  PR TRACK PR coating, develop  NIKON STEPPER Gate etch, 2000A 20% over, E/R check, pattern test  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP  100 RCA cleaning, HF dip  CMOS FURNACE II - DRY OXIDATION Gate dielectric oxidation Gate doposition  Gate doposition  Gate doposition  Gate doposition  Gate doposition  Gate p-Si depo 2000A +/-10%, THK at nanospec  PR TRACK PR coating, develop  NIKON STEPPER  Gate etch, 2000A 20% over, E/R check, pattern test  CMOS PR ASHER PR ashing  PR strip  PR strip  PR strip  PR Strip  PR TRACK PR coating, develop  NIKON STEPPER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20     | W13A(WA-13,C1-6)SPM-CLEANING                              |                                 |

| RCA cleaning, HF dip  CMOS FURNACE II - WET OXIDATION Sol thinning process Oxidation for thinning 1000A +/-10% Thickness checked by ellipsometer  PR TRACK PR coating, develop  NIKON STEPPER Active layer pattern Active photo [Reticle : ACT]  CMOS ICP POLY ETCHER Active etch Trench etch 1000A +/-10%, E/R check a-step and SEM  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP PR strip  W3A(WA-13,C1-6)SPM-CLEANING Pre Furnace cleaning for gate oxidation, HF dip  W5A(WA-5,C1-6) SC-1,2 CLEANING RCA cleaning, HF dip  CMOS FURNACE II - DRY OXIDATION Gate dielectric oxidation OXIDATION TO TIMINITING 300A +/-30% ITHICKNESS CHECKED BY allicementars LPCVD III CMOS Poly S(科함) Gate p-Si depo 2000A +/-10%, THK at nanospec PR TRACK PR coating, develop  NIKON STEPPER Gate photo [Reticle : PLY]  CMOS ICP POLY ETCHER Gate etch, 2000A 20% over, E/R check, pattern test  CMOS PR ASHER PR sshing  WET STATION WA-2 SPM PR STRIP PR strip  PR Strip  PR Strip  PR Strip  PR Strip  PR Strip  PR Strip  PR Strip  PR Strip  PR Strip  PR Strip  PR Strip  PR Strip  PR Strip  PR Strip  PR Strip  PR Strip  PR TRACK PR coating, develop  NIKON STEPPER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        | Initial cleaning                                          | •                               |

| RCA cleaning, HF dip  CMOS FURNACE II - WET OXIDATION Oxidation for thinning 1000A +/-10% Thickness checked by ellipsometer  PR TRACK PR coating, develop  NIKON STEPPER Active photo [Reticle : ACT]  CMOS ICP POLY ETCHER Trench etch 1000A +/-10%, E/R check a-step and SEM  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP PR strip  W3A(WA-13,C1-6)SPM-CLEANING Pre Furnace cleaning for gate oxidation, HF dip  W5A(WA-5,C1-6) SC-1,2 CLEANING RCA cleaning, HF dip  CMOS FURNACE II - DRY OXIDATION OXIDATION Gate pois oxidation Active etch  TOD  RCA cleaning, HF dip  CMOS FURNACE II - DRY OXIDATION OXIDATION Gate dielectric oxidation OXIDATION Gate pois oxidation Active etch  TOD  RCA cleaning, HF dip  CMOS FURNACE II - DRY OXIDATION OXIDATION Gate dielectric oxidation OXIDATION Gate pois oxidation Alliaceansatics  LPCVD III CMOS Poly S(AE) Gate pois depo 2000A +/-10%, THK at nanospec PR TRACK PR coating, develop  NIKON STEPPER Gate photo [Reticle : PLY]  CMOS ICP POLY ETCHER Gate etch, 2000A 20% over, E/R check, pattern test  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP PR strip  PR Strip  PR TRACK PR coating, develop  NIKON STEPPER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30     | W5A(WA-5,C1-6) SC-1,2 CLEANING                            |                                 |

| Oxidation for thinning 1000A +/-10% Thickness checked by ellipsometer  PR TRACK PR coating, develop  NIKON STEPPER Active photo (Reticle : ACT)  CMOS ICP POLY ETCHER Active etch Trench etch 1000A +/-10%, E/R check a-step and SEM  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP PR strip  W3A(WA-13,C1-6)SPM-CLEANING Pre Furnace cleaning for gate oxidation, HF dip  W5A(WA-5,C1-6) SC-1,2 CLEANING RCA cleaning, HF dip  CMOS FURNACE II - DRY OXIDATION OXIDATION TURNING SIDE OXIDATION Gate delelectric oxidation Oxidation tor turning 30A +/-5% Thickness checked by alliacomates  LPCVD III CMOS Poly Si(科技) Gate doposition Gate p-Si depo 2000A +/-10%, THK at nanospec  PR TRACK PR coating, develop  NIKON STEPPER Gate photo (Reticle : PLY)  CMOS ICP POLY ETCHER Gate etch Gate etch, 2000A 20% over, E/R check, pattern test  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP PR strip  PR strip  PR Strip  PR Strip  PR Strip  PR Strip  PR Strip  PR Strip  PR Strip  PR Strip  PR Strip  PR Strip  PR TRACK PR coating, develop  NIKON STEPPER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | RCA cleaning, HF dip                                      |                                 |

| Oxidation for thinning 1000A +/-10% Thickness checked by ellipsometer  PR TRACK PR coating, develop  NIKON STEPPER Active layer pattern Active photo [Reticle : ACT]  CMOS ICP POLY ETCHER Active etch Trench etch 1000A +/-10%, E/R check a-step and SEM  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP PR strip  100 Pre Furnace cleaning for gate oxidation, HF dip  W5A(WA-13,C1-6)SPM-CLEANING Pre Furnace cleaning, HF dip  CMOS FURNACE II - DRY OXIDATION OXIDATION TO THINNING 30A +/-3% THICKNESS CHECKEU BY Alliaccanator  CMOS FURNACE II - DRY OXIDATION OXIDATION Gate dielectric oxidation OXIDATION TO THINNING 30A +/-10%, THK at nanospec  PR TRACK PR coating, develop  NIKON STEPPER Gate photo [Reticle : PLY]  CMOS ICP POLY ETCHER Gate etch, 2000A 20% over, E/R check, pattern test  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP PR strip  PR strip  PR Strip  PR TRACK PR coating, develop  NIKON STEPPER  MET STATION WA-2 SPM PR STRIP PR strip  PR Strip  PR TRACK PR coating, develop  NIKON STEPPER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40     | CMOS FURNACE II - WET OXIDATION                           | SoI thinning process            |

| PR coating, develop  NIKON STEPPER Active layer pattern  Active photo [Reticle : ACT]  CMOS ICP POLY ETCHER Active etch  Trench etch 1000A +/-10%, E/R check a-step and SEM  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP  PR strip  W13A(WA-13,C1-6)SPM-CLEANING Pre Furnace cleaning for gate oxidation, HF dip  W5A(WA-5,C1-6) SC-1,2 CLEANING  RCA cleaning, HF dip  CMOS FURNACE II - DRY OXIDATION OXIDATION TOR TURNING 30A +/-3% TRICKNESS CHECKED by allicomator  LPCVD III CMOS Poly Si(직접) Gate doposition  Gate doposition  Active layer pattern  Gate dielectric oxidation  Gate dielectric oxidation  Gate dielectric oxidation  Gate doposition  Gate p-Si depo 2000A +/-10%, THK at nanospec  PR TRACK PR coating, develop  NIKON STEPPER  Gate photo [Reticle : PLY]  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP  PR strip  PR strip  PR Strip  PR Strip  PR TRACK PR coating, develop  NIKON STEPPER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40     | Oxidation for thinning 1000A +/-10% Thickness checked by  | ellipsometer                    |

| PR coating, develop  NIKON STEPPER Active photo [Reticle : ACT]  CMOS ICP POLY ETCHER Active etch  Trench etch 1000A +/-10%, E/R check a-step and SEM  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP  PR strip  100  WSA(WA-13,C1-6)SPM-CLEANING Pre Furnace cleaning for gate oxidation, HF dip  WSA(WA-5,C1-6) SC-1,2 CLEANING RCA cleaning, HF dip  120  CMOS PRNACE II - DRY OXIDATION Gate dielectric oxidation Uxidation for trimming 30A +7-5% Thickness checked by allipcomator allipcomator Allipcomator PR TRACK PR coating, develop  NIKON STEPPER Gate photo [Reticle : PLY]  CMOS POLY ETCHER Gate etch, 2000A 20% over, E/R check, pattern test  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP PR strip  PR strip  PR STRACK PR coating, develop  NIKON STEPPER  MET STATION WA-2 SPM PR STRIP PR strip  PR strip  PR STRACK PR coating, develop  NIKON STEPPER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 50     | PR TRACK                                                  |                                 |

| Active photo [Reticle : ACT]  70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        | PR coating, develop                                       |                                 |

| Active photo [Reticle : ACT]  MOS ICP POLY ETCHER Active etch Trench etch 1000A +/-10%, E/R check a-step and SEM  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP PR strip  100 Pre Furnace cleaning for gate oxidation, HF dip  WSA(WA-13,C1-6)SPM-CLEANING Pre Furnace cleaning for gate oxidation, HF dip  CMOS FURNACE II - DRY OXIDATION CMOS FURNACE II - DRY OXIDATION CMOS FURNACE II - DRY OXIDATION Gate p-Si depo 2000A +/-10%, THK at nanospec  PR TRACK PR coating, develop  NIKON STEPPER Gate photo [Reticle : PLY]  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP PR strip  PR Strip  PR TRACK PR coating, develop  NIKON STEPPER  MET STATION WA-2 SPM PR STRIP PR strip  PR Strip  PR TRACK PR coating, develop  NIKON STEPPER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 60     | NIKON STEPPER                                             | Active layer pattern            |

| Trench etch 1000A +/-10%, E/R check a-step and SEM  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP PR strip  100  WSA(WA-13,C1-6)SPM-CLEANING Pre Furnace cleaning for gate oxidation, HF dip  WSA(WA-5,C1-6) SC-1,2 CLEANING RCA cleaning, HF dip  110  CMOS FURNACE II - DRY OXIDATION OXIDATION TO THININING 30A +/-5% THICKNESS CHECKED by dilacomotor Gate p-Si depo 2000A +/-10%, THK at nanospec  PR TRACK PR coating, develop  NIKON STEPPER Gate photo [Reticle : PLY]  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP PR strip  PR TRACK PR coating, develop  NIKON STEPPER  Gate etch, 2000A 20% over, E/R check, pattern test  CMOS PR ASHER PR strip  PR Strip  PR TRACK PR coating, develop  NIKON STEPPER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 60     | Active photo [Reticle : ACT]                              |                                 |

| Trench etch 1000A +/-10%, E/R check a-step and SEM  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP PR strip  100  WI3A(WA-13,C1-6)SPM-CLEANING Pre Furnace cleaning for gate oxidation, HF dip  W5A(WA-5,C1-6) SC-1,2 CLEANING RCA cleaning, HF dip  120  CMOS FURNACE II - DRY OXIDATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 70     | CMOS ICP POLY ETCHER                                      | Active etch                     |

| PR ashing  WET STATION WA-2 SPM PR STRIP PR strip  W13A(WA-13,C1-6)SPM-CLEANING Pre Furnace cleaning for gate oxidation, HF dip  W5A(WA-5,C1-6) SC-1,2 CLEANING RCA cleaning, HF dip  CMOS FURNACE II - DRY OXIDATION OXIDATION TO THIMMING SUA +/-3% THICKNESS CHECKED BY alliesconster LPCVD III CMOS Poly Si(직접) Gate dielectric oxidation Gate p-Si depo 2000A +/-10%, THK at nanospec PR TRACK PR coating, develop  NIKON STEPPER Gate photo [Reticle : PLY]  CMOS ICP POLY ETCHER Gate etch, 2000A 20% over, E/R check, pattern test  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP PR Strip PR TRACK PR coating, develop  NIKON STEPPER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 70     | Trench etch 1000A +/-10%, E/R check a-step and <b>SEM</b> |                                 |

| PR ashing WET STATION WA-2 SPM PR STRIP PR strip  100 PR strip  W13A(WA-13,C1-6)SPM-CLEANING Pre Furnace cleaning for gate oxidation, HF dip  W5A(WA-5,C1-6) SC-1,2 CLEANING RCA cleaning, HF dip  120 CMOS FURNACE II - DRY OXIDATION Gate dielectric oxidation UXIDATION TO THINNING 3WA +/-5% THICKNESS CHECKED BY Alliaccompater LPCVD III CMOS Poly Si(직접) Gate doposition Gate p-Si depo 2000A +/-10%, THK at nanospec PR TRACK PR coating, develop  NIKON STEPPER Gate photo [Reticle : PLY] CMOS ICP POLY ETCHER Gate etch, 2000A 20% over, E/R check, pattern test CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP PR strip PR Strip  PR TRACK PR coating, develop  NIKON STEPPER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | CMOS PR ASHER                                             |                                 |

| PR strip  W13A(WA-13,C1-6)SPM-CLEANING Pre Furnace cleaning for gate oxidation, HF dip  W5A(WA-5,C1-6) SC-1,2 CLEANING RCA cleaning, HF dip  120 CMOS FURNACE II - DRY OXIDATION OXIDATIO | 80     | PR ashing                                                 |                                 |

| PR strip  W13A(WA-13,C1-6)SPM-CLEANING Pre Furnace cleaning for gate oxidation, HF dip  W5A(WA-5,C1-6) SC-1,2 CLEANING RCA cleaning, HF dip  CMOS FURNACE II - DRY OXIDATION Oxidation for trimming 3UA +/-5% IMECKNESS CHECKED BY allipsomator LPCVD III CMOS Poly Si(직접) Gate dielectric oxidation Gate p-Si depo 2000A +/-10%, THK at nanospec  PR TRACK PR coating, develop  NIKON STEPPER Gate photo [Reticle : PLY]  CMOS ICP POLY ETCHER Gate etch, 2000A 20% over, E/R check, pattern test  CMOS PR ASHER PR ashing  WET STATION WA-2 SPM PR STRIP PR Strip  PR TRACK PR coating, develop  NIKON STEPPER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 00     | WET STATION WA-2 SPM PR STRIP                             |                                 |