#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

Disclaimer 🖃

#### Ph.D. Dissertation

# An AC-DC LED Driver with a Two Parallel Floating Buck Topology for Reducing the Light Flicker in Lighting Applications to Low-Risk Levels

조명 장치에서 플리커를 낮은 위험 수준으로 줄이기 위해 두 개의 평행한 플로팅 벅 구조를 사용한 교류-직류 엘이디 구동 회로

by

**Hyun-Chang Kim**

**August**, 2016

Department of Electrical and Computer Engineering Seoul National University

# An AC-DC LED Driver with a Two Parallel Floating Buck Topology for Reducing the Light Flicker in Lighting Applications to Low-Risk Levels

지도 교수 정 덕 균

이 논문을 공학박사 학위논문으로 제출함 2016 년 8 월

> 서울대학교 대학원 전기·컴퓨터공학부 김 현 창

김현창의 박사 학위논문을 인준함 2016 년 8 월

| 위육 | 원 장 · | (인) |

|----|-------|-----|

| 부위 | 원장    | (인) |

| 위  | 원     | (인) |

| 위  | 원     | (인) |

| 위  | 원     | (인) |

# An AC-DC LED Driver with a Two Parallel Floating Buck Topology for Reducing the Light Flicker in Lighting Applications to Low-Risk Levels

by

## Hyun-Chang Kim

A Dissertation Submitted to the Department of

Electrical and Computer Engineering

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

at

### SEOUL NATIONAL UNIVERSITY

August, 2016

## Committee in Charge:

Professor Hyuk-Jae Lee, Chairman

Professor Deog-Kyoon Jeong, Vice-Chairman

Professor Suhwan Kim

Professor Jung-Ik Ha

Professor Yong Moon

**Abstract**

This dissertation presents an ac-dc LED driver that consists of two parallel float-

ing buck converters. To buffer the twice-line-frequency energy, one floating buck

converter conveys energy to a storage capacitor, simultaneously performing the

power factor correction (PFC). The other floating buck converter regulates the LED

current to maintain a constant brightness in the LEDs for reducing the light flicker to

low-risk levels. The proposed architecture reduces the voltage stress and the size of

the storage capacitor, enabling the use of a film capacitor instead of an electrolytic

capacitor. Considering the power factor and the flicker standards, a design procedure

to achieve a high power factor, while minimizing the storage capacitance and the

LED current ripple, is presented. A prototype of the proposed LED driver has been

implemented with an on-chip controller IC fabricated in a 0.35 µm CMOS process

and its functionality and performance have been verified experimentally. It demon-

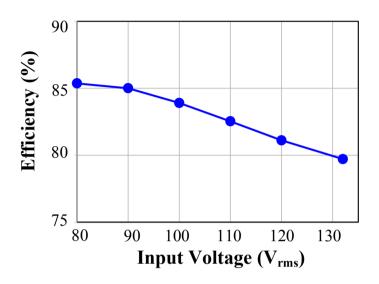

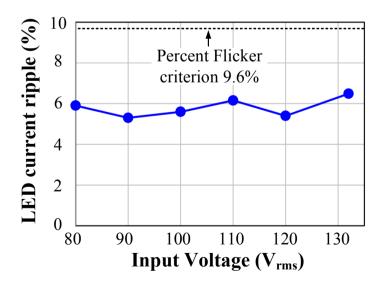

strates a power factor of 0.94 and a peak power efficiency of 85.4% with an LED

current ripple of 6.5%, while delivering 15 W to the LEDs.

**Keywords**: AC-DC power conversion, Light-emitting diodes (LEDs), LED driver,

Analog and digital integrated circuit design, Pulse width modulated power convert-

ers, flicker, floating buck converter

**Student Number: 2009-20788**

Ι

# **Contents**

| ABSTRACT                                        | I  |

|-------------------------------------------------|----|

| CONTENTS                                        | II |

| LIST OF FIGURES                                 | V  |

| LIST OF TABLES                                  | XI |

| CHAPTER 1 INTRODUCTION                          | 1  |

| 1.1 MOTIVATIONS                                 | 1  |

| 1.2 FLICKER METRICS AND STANDARDS               | 5  |

| 1.3 PRIOR WORKS                                 | 9  |

| 1.4 THESIS OBJECTIVES AND ORGANIZATION          | 15 |

| CHAPTER 2 BACKGROUND ON LED DRIVER              | 17 |

| 2.1 Power Converter Topologies                  | 17 |

| 2.1.1 LINEAR REGULATOR                          | 17 |

| 2.1.2 SWITCHED-CAPACITOR CONVERTER              | 18 |

| 2.1.3 INDUCTOR-BASED CONVERTERS                 | 19 |

| 2.2 Basics for LED Drivers                      | 31 |

| 2.2.1 LED CONFIGURATIONS                        | 31 |

| 2.2.2 CURRENT SENSING TECHNIQUES IN LED DRIVERS | 32 |

| 2.3 PFC Techniques in LED Drivers               | 35 |

| 2.3.1 POWED FACTOR                              | 35 |

| 2.3.2 PASSIVE PFC CIRCUIT                                      | 35 |

|----------------------------------------------------------------|----|

| 2.3.3 ACTIVE PFC CIRCUIT                                       | 36 |

| 2.4 DIMMING TECHNIQUES                                         | 38 |

| CHAPTER 3 DESIGN OF AN AC-DC LED DRIVER WITH A TWO             |    |

| PARALLEL FLOATING BUCK TOPOLOGY                                | 40 |

| 3.1 Proposed System Architecture and Operation Principle       | 40 |

| 3.1.1 OVERALL ARCHITECTURE                                     | 40 |

| 3.1.2 OPERATION PRINCIPLE                                      | 42 |

| 3.1.3 DISCUSSION ON DIMMING                                    | 50 |

| 3.2 DESIGN OF THE PROPOSED TOPOLOGY                            | 52 |

| 3.2.1 RELATIONSHIP BETWEEN THE INPUT CURRENT WAVEFORM AND THE  |    |

| Power Factor                                                   | 52 |

| 3.2.2 DESIGN CONSIDERATIONS FOR DECIDING THE STORAGE CAPACITOR |    |

| VOLTAGE                                                        | 54 |

| 3.2.3 Analysis of the Proposed LED Driver with Line Voltage    |    |

| VARIATIONS                                                     | 57 |

| 3.2.4 DESIGN OF THE FLOATING BUCK CONVERTER FOR PFC AND        |    |

| Energy Buffering                                               | 59 |

| 3.2.5 Design of the Floating Buck Converter for LED Current    |    |

| REGULATION                                                     | 63 |

| 3.3 CIRCUIT IMPLEMENTATION                                     | 67 |

| 3.3.1 CONTROLLER CIRCUIT ARCHITECTURE                          | 67 |

| 3.3.2 LED CURRENT REGULATION LOOP DESIGN                       | 68 |

### **CONTENTS**

| 3.3.3 BUILDING BLOCKS          | 70  |

|--------------------------------|-----|

| CHAPTER 4 EXPERIMENTAL RESULTS | 79  |

| 4.1 EXPERIMENTAL SETUP         | 79  |

| 4.2 Measurement Results        | 84  |

| CHAPTER 5 CONCLUSION           | 93  |

| BIBLIOGRAPHY                   | 94  |

| 초 록                            | 101 |

# **List of Figures**

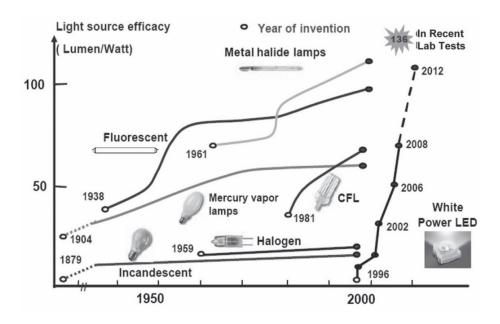

| Fig. 1.1. Advancement in lighting technology [5].                                 | 2    |

|-----------------------------------------------------------------------------------|------|

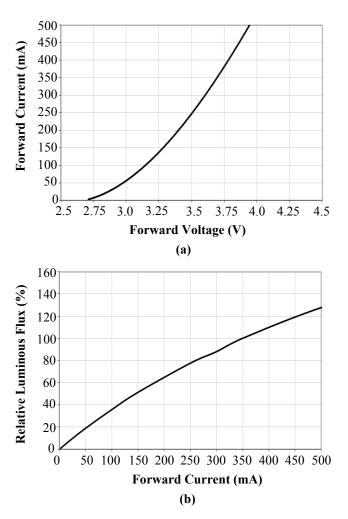

| FIG. 1.2. LED CHARACTERISTICS: (A) ELECTRICAL CHARACTERISTICS (B) RELATIVE        |      |

| LUMINOUS FLUX VERSUS FORWARD CURRENT [6]                                          | 3    |

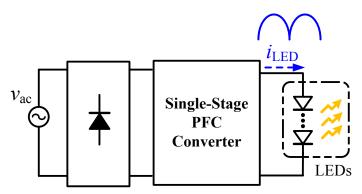

| Fig. 1.3. Conventional single-stage LED drivers that exhibits light flicker       | 4    |

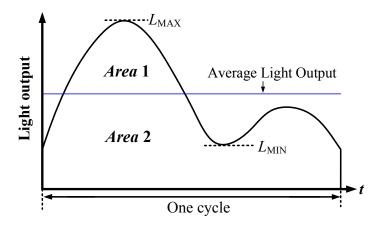

| Fig. 1.4. Periodic waveform of light output in one cycle [14].                    | 5    |

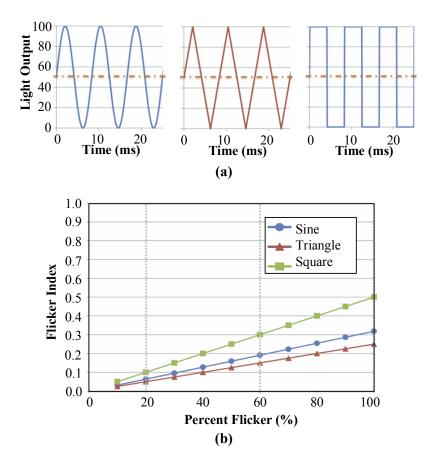

| FIG. 1.5. (A) SIMPLE PERIODIC WAVEFORMS OF LIGHT OUTPUTS (B) FLICKER INDEX VERSUS |      |

| PERCENT FLICKER [15].                                                             | 6    |

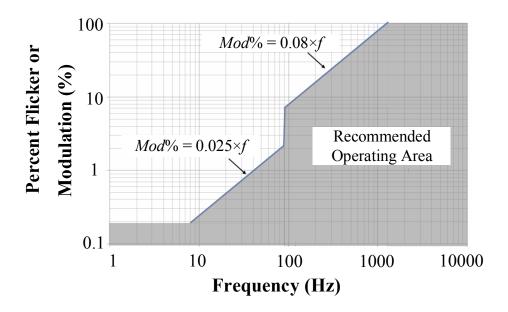

| FIG. 1.6. RECOMMENDED OPERATING AREA TO GIVE LOW RISK FOR HEADACHES AND           |      |

| PHOTOSENSITIVE EPILEPTIC SEIZURES [17].                                           | 7    |

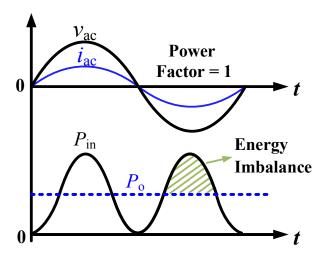

| FIG. 1.7. WAVEFORMS OF AN AC-DC LED DRIVER WITH A CONSTANT OUTPUT POWER WHEN      |      |

| THE POWER FACTOR IS UNITY.                                                        | 9    |

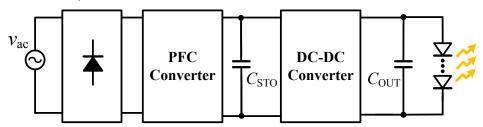

| Fig. 1.8. Conventional two-stage ac-dc LED driver consisting of a first-stage Pl  | FC   |

| CONVERTER AND A SECOND-STAGE DC-DC CONVERTER.                                     | 9    |

| FIG. 1.9. WAVEFORMS OF OUTPUT CURRENT WHEN HARMONIC CURRENTS ARE INJECTED TO      |      |

| THE INPUT CURRENT [24].                                                           | . 10 |

| Fig. 1.10. An ac-dc LED driver employing a parallel ripple cancellation           |      |

| CONVERTER [30].                                                                   | . 12 |

| Fig. 1.11. An ac-dc LED driver employing a series ripple cancellation converter   |      |

| [35]                                                                              | . 12 |

| Fig. 1.12. An ac-dc power conversion architecture consisting of two stacked       |      |

| ENERGY-STORAGE CAPACITORS [38]                                                    | 13   |

| FIG. 1.13. A SINGLE-STAGE AC-DC LED DRIVER EMPLOYING AN AVERAGE CURRENT            |    |

|------------------------------------------------------------------------------------|----|

| MODULATION METHOD [39].                                                            | 13 |

| FIG. 2.1. SCHEMATIC OF A LINEAR VOLTAGE REGULATOR.                                 | 18 |

| FIG. 2.2. A SWITCHED-CAPACITOR CONVERTER WITH A SERIES-PARALLEL TOPOLOGY           | 19 |

| FIG. 2.3. SCHEMATICS OF (A) A BUCK CONVERTER AND (B) A FLOATING BUCK CONVERTER,    |    |

| AND THE VOLTAGE AND CURRENT WAVEFORMS OF THE BUCK CONVERTER IN A CCM               |    |

| OPERATION.                                                                         | 21 |

| FIG. 2.4. VOLTAGE AND CURRENT WAVEFORMS ILLUSTRATING THE CONVERTER OPERATION       |    |

| MODES.                                                                             | 23 |

| FIG. 2.5. CONVERSION RATIOS OF THE BUCK CONVERTER ACCORDING TO THE BOUNDARY        |    |

| CONDITION K.                                                                       | 24 |

| Fig. 2.6. Schematic of (a) a boost converter and (b) its voltage and current       |    |

| WAVEFORMS IN A CCM.                                                                | 25 |

| FIG. 2.7. SCHEMATICS OF (A) A BUCK-BOOST CONVERTER AND (B) FLOATING BUCK-BOOST     |    |

| CONVERTER, AND (C) THEIR VOLTAGE AND CURRENT WAVEFORMS IN A CCM                    |    |

| OPERATION.                                                                         | 27 |

| FIG. 2.8. SCHEMATIC OF (A) A FLYBACK CONVERTER AND (B) ITS VOLTAGE AND CURRENT     |    |

| WAVEFORMS IN THE CCM OPERATION.                                                    | 29 |

| FIG. 2.9. CONVERSION RATIOS OF THE INDUCTOR-BASED CONVERTERS IN A CCM OPERATION    | ١. |

|                                                                                    | 30 |

| FIG. 2.10. LED CONFIGURATIONS IN LED DRIVERS: (A) SERIES (B) PARALLEL              | 31 |

| Fig. 2.11. Basic configuration of a constant current LED driver with a current     |    |

| SENSE RESISTOR                                                                     | 32 |

| FIG. 2.12 INDIRECT CURRENT SENSING TECHNIQUES: (A) SENSE-FET (R) AUXII JARY WINDIN | G  |

| FIG. 2.13. CONVENTIONAL PASSIVE PFC LED DRIVER: (A) RESISTIVE TYPE (B) VALLEY FILL                                           |

|------------------------------------------------------------------------------------------------------------------------------|

| TYPE                                                                                                                         |

| FIG. 2.14. A BOOST TYPE LED DRIVER WITH A PFC CONTROLLER                                                                     |

| Fig. 2.15. (a) Single stage LED driver with an input EMI filter. Voltage and                                                 |

| CURRENT WAVEFORMS OF (B) A BUCK-BOOST OR A FLYBACK, AND (C) A BUCK                                                           |

| CONVERTER IN THE CRM OPERATION                                                                                               |

| FIG. 2.16. TWO POPULAR DIMMING METHODS: (A) PWM DIMMING (B) ANALOG DIMMING 39                                                |

| FIG. 3.1. OVERALL ARCHITECTURE OF THE PROPOSED AC-DC LED DRIVER WITH TWO                                                     |

| PARALLEL FLOATING BUCK CONVERTERS. 41                                                                                        |

| FIG. 3.2. (A) ENERGY FLOW CONCEPT AND (B) INPUT AND OUTPUT WAVEFORMS OF THE                                                  |

| PROPOSED LED DRIVER WITH TWO ALTERNATING OPERATING MODES                                                                     |

| Fig. 3.3. Operating modes of the proposed LED driver: (a) <i>Mode</i> 1 when $ V_{AC}  > V_{STO}$                            |

| AND (B) $MODE\ 2$ WHEN $ V_{AC}  < V_{STO}$                                                                                  |

| FIG. 3.4. BLOCK DIAGRAM OF THE PROPOSED LED DRIVER WITH A TWO PARALLEL FLOATING                                              |

| BUCK TOPOLOGY45                                                                                                              |

| FIG. 3.5. THEORETICAL VOLTAGE AND CURRENT WAVEFORMS OF THE PROPOSED LED DRIVER.                                              |

| 46                                                                                                                           |

| FIG. 3.6. SIMULATED WAVEFORMS THAT REPRESENTS LED DIMMING OPERATION                                                          |

| Fig. 3.7. Example of the input current waveforms according to the amplitude of $I_1$                                         |

| IN <i>Mode</i> 1, when $V_{\text{STO}}(T)$ is $V_{\text{M}}/2$ (= 77.8 V) and the output power ( $P_{\text{O}}$ ) is 15 W 53 |

| FIG. 3.8. WAVEFORMS OF THE INPUT CURRENT AND INPUT POWER AT TWO DIFFERENT                                                    |

| VOLTAGE LEVELS OF $V_{\text{STO}}$ , WHEN THE OUTPUT POWER ( $P_0$ ) IS 15 W: (A) $V_{\text{STO}}$ (CASE 1: 110              |

| V. CASE 2: 77.8 V). (B) $I_{IN}$ . AND (C) $P_{IN}$                                                                          |

| Fig. 3.9. Stored energy ratio ( $E_{	ext{stored}}/E_{	ext{total}}$ ) and power factor with respect to the   |

|-------------------------------------------------------------------------------------------------------------|

| AVERAGE VALUES OF THE STORAGE CAPACITOR VOLTAGE, WHEN THE INPUT VOLTAGE                                     |

| IS 110 V <sub>RMS</sub>                                                                                     |

| Fig. 3.10. Stored energy ratio ( $E_{\text{stored}}/E_{\text{total}}$ ) and power factor with respect to an |

| INPUT VOLTAGE RANGING FROM 80 TO 132 $V_{\text{rms}}$                                                       |

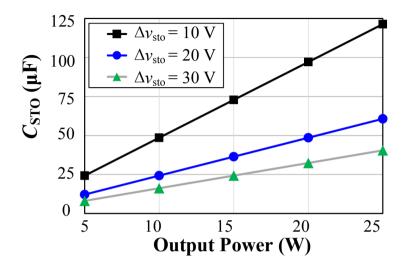

| Fig. 3.11. Required size of $C_{\rm STO}$ with a constant $\Delta V_{\rm STO}$ with respect to an input     |

| VOLTAGE RANGING FROM $80\ \text{to}\ 132\ V_{\text{rms}}.$                                                  |

| Fig. 3.12. Required capacitance for $C_{\mathrm{STO}}$ with respect to the output power, when               |

| $V_{ m STO\_AVG}$ is 50 V and the input voltage is 80 $V_{ m RMS}$                                          |

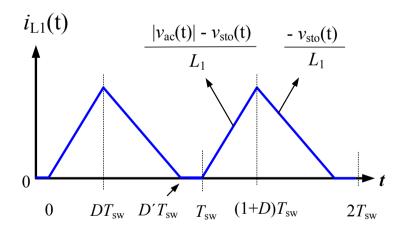

| FIG. 3.13. INDUCTOR CURRENT WAVEFORM OF THE BUCK PFC CONVERTER OPERATING IN A                               |

| DCM                                                                                                         |

| FIG. 3.14. CHARACTERISTICS OF THE CREE XLAMP MX-3 LED: (A) VOLTAGE VS. CURRENT,                             |

| (B) CURRENT VS. RELATIVE LUMINOUS FLUX [6]                                                                  |

| Fig. 3.15. Waveforms of the output voltage and the inductor current of the                                  |

| REGULATING CONVERTER OPERATING IN A CCM                                                                     |

| FIG. 3.16. BLOCK DIAGRAM OF THE PROPOSED CONTROLLER IC                                                      |

| Fig. 3.17. (a) Schematic of the LED current regulating converter and its                                    |

| SIMPLIFIED FEEDBACK LOOP (B) VOLTAGE AND CURRENT WAVEFORMS                                                  |

| FIG. 3.18. SCHEMATIC OF THE CONVENTIONAL BUCK LED DRIVER                                                    |

| FIG. 3.19. SCHEMATIC OF A CLOCKED COMPARATOR BASED ON STRONGARM LATCH                                       |

| TOPOLOGY                                                                                                    |

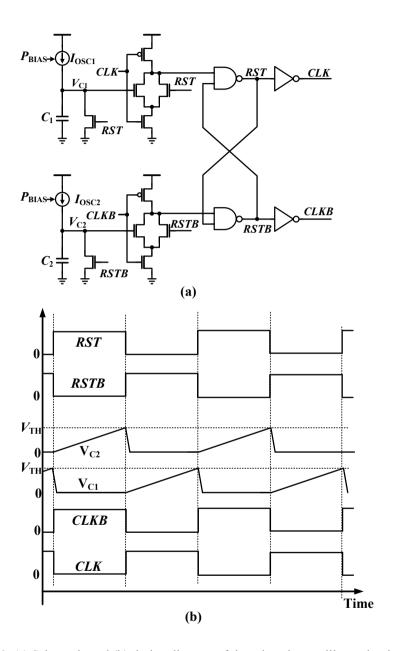

| FIG. 3.20. (A) SCHEMATIC AND (B) TIMING DIAGRAM OF THE RELAXATION OSCILLATOR                                |

| CIRCUIT72                                                                                                   |

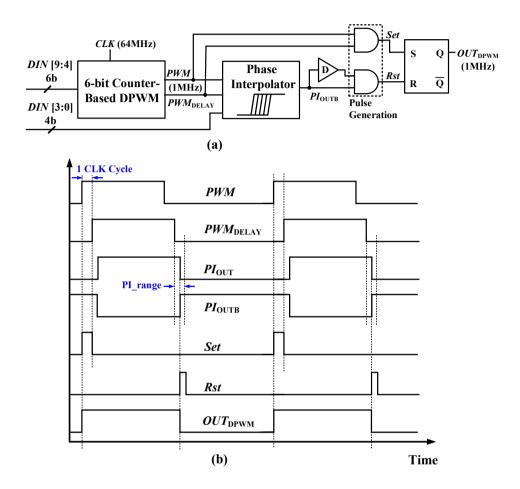

| Fig. 3.21. (a) Architecture and (b) timing diagram of the PI-based DPWM74                                   |

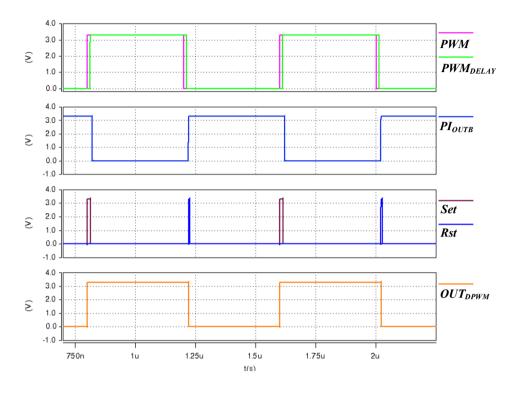

| FIG. 3.22. SIMULATED WAVEFORMS OF PI-BASED DPWM.                                                                   | 75 |

|--------------------------------------------------------------------------------------------------------------------|----|

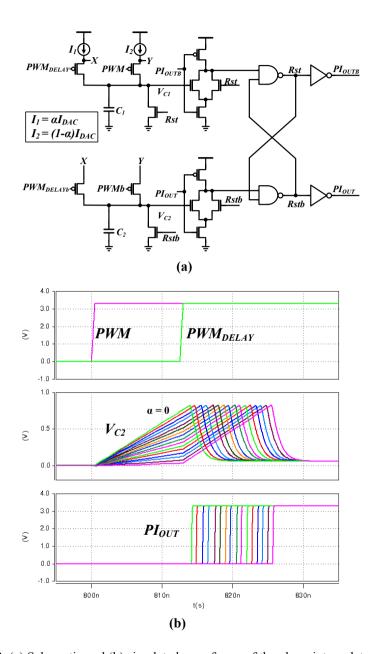

| FIG. 3.23. (A) SCHEMATIC AND (B) SIMULATED WAVEFORMS OF THE PHASE INTERPOLATOR                                     |    |

| CIRCUIT                                                                                                            | 76 |

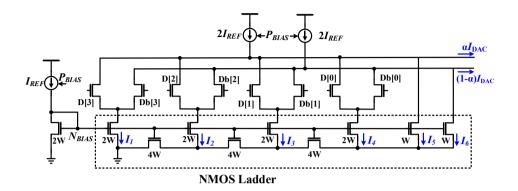

| Fig. 3.24. Schematic of an M2M-ladder-type current-steering DAC                                                    | 77 |

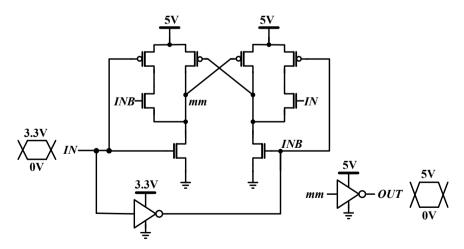

| Fig. 3.25. Schematic of a voltage level shifter circuit.                                                           | 77 |

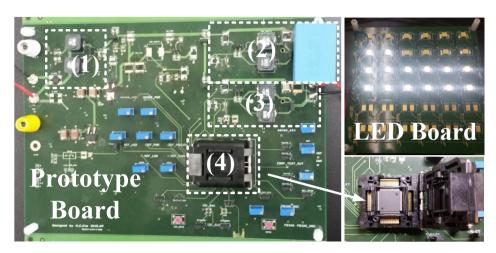

| FIG. 4.1. PROTOTYPE BOARD OF THE PROPOSED LED DRIVER                                                               | 30 |

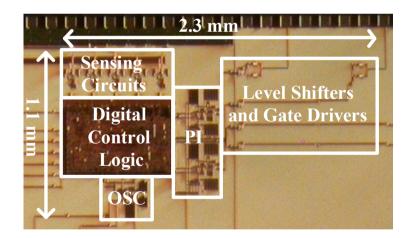

| Fig. 4.2. Photograph of the implemented controller IC                                                              | 31 |

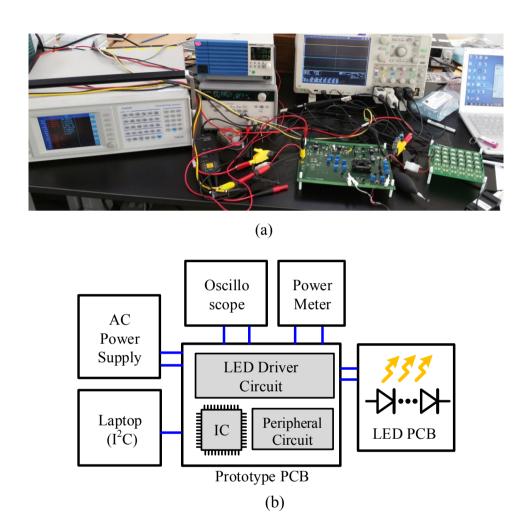

| FIG. 4.3. (A) THE PHOTOGRAPH AND (B) BLOCK DIAGRAM OF THE EXPERIMENTAL SETUP                                       | 33 |

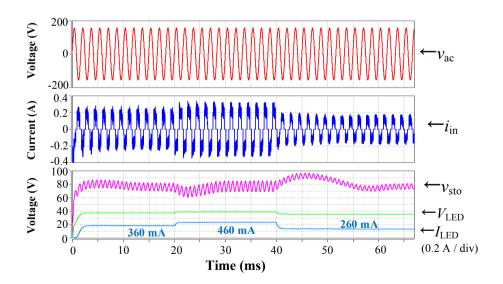

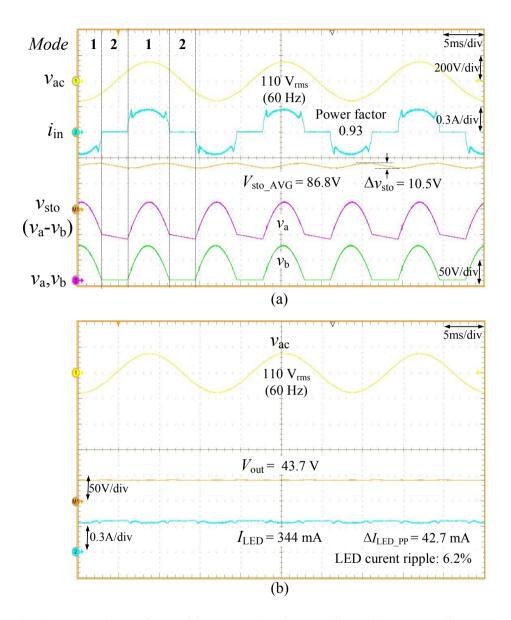

| Fig. 4.4. Measured waveforms of the proposed ac-DC LED driver with a two                                           |    |

| PARALLEL FLOATING BUCK TOPOLOGY.                                                                                   | 36 |

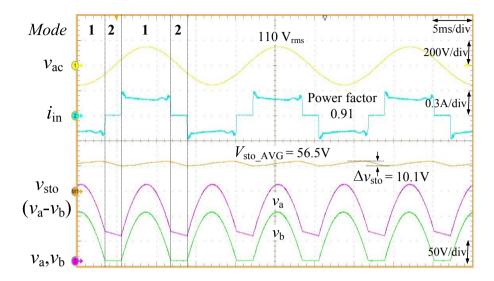

| Fig. 4.5. Measured waveforms of the proposed ac-DC LED driver to demonstrate                                       |    |

| THAT THE MINIMUM $V_{ m STO\_AVG}$ FOR PF > 0.9 is 56.5 V.                                                         | 37 |

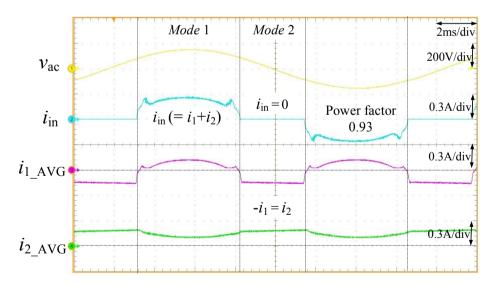

| Fig. 4.6. Measured waveforms of the AC input voltage and current ( $V_{AC}$ and $I_{IN}$ ), an                     | D  |

| THE CURRENTS FLOWING INTO THE RESPECTIVE FLOATING BUCK CONVERTERS, ( $I_1$ AND                                     | )  |

| <i>I</i> <sub>2</sub> )                                                                                            | 37 |

| FIG. 4.7. MEASURED WAVEFORMS OF THE PROPOSED AC-DC LED DRIVER WHEN THE INPUT                                       |    |

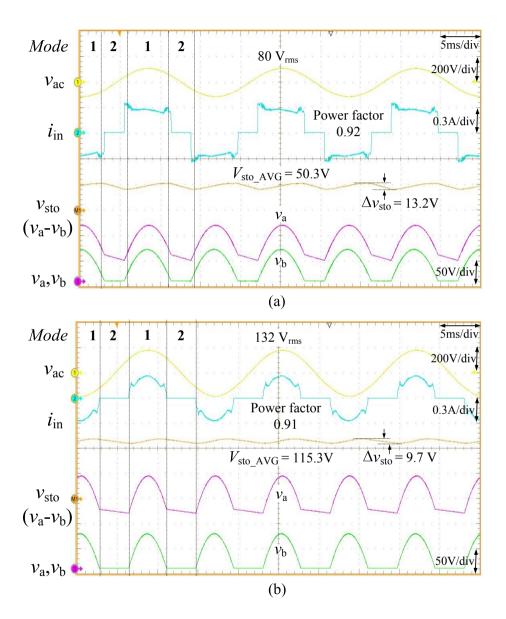

| VOLTAGE IS (A) 80 $V_{\text{RMS}}$ and (B) 132 $V_{\text{RMS}}$                                                    | 38 |

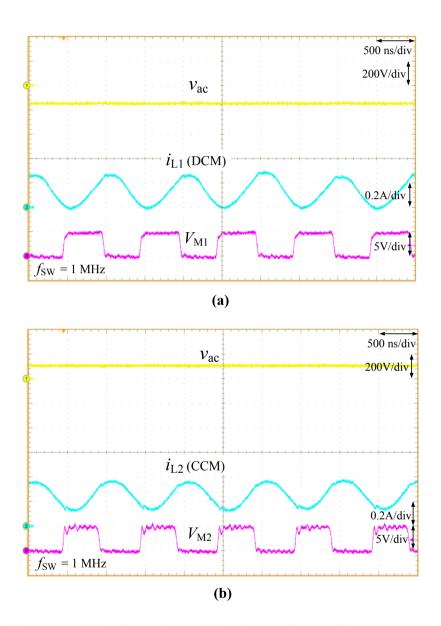

| FIG. 4.8. MEASURED CLOSE-IN WAVEFORMS OF THE AC INPUT VOLTAGE AND THE GATE-                                        |    |

| SOURCE VOLTAGES ( $V_{\rm M1}$ AND $V_{\rm M2}$ ) AND THE INDUCTOR CURRENTS ( $I_{\rm L1}$ AND $I_{\rm L2}$ ): (A) |    |

| BUCK PFC CONVERTER (B) REGULATING CONVERTER                                                                        | 39 |

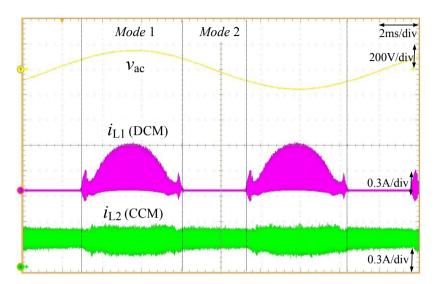

| FIG. 4.9. MEASURED WAVEFORMS OF THE AC INPUT VOLTAGE AND THE CURRENTS FLOWING                                      |    |

| THROUGH THE INDUCTORS.                                                                                             | 90 |

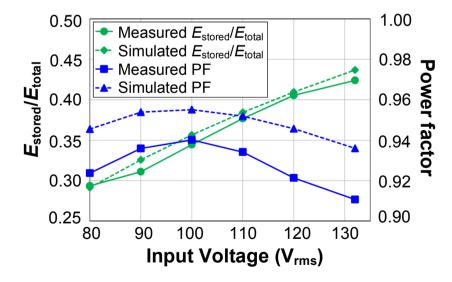

| Fig. 4.10. Measured power factor and stored energy ratio ( $E_{	ext{stored}}/E_{	ext{total}}$ ) of the             |    |

| PROPOSED LED DRIVER.                                                                                               | 90 |

### LIST OF FIGURES

| Fig. 4.11. Measured power efficiency of the proposed LED driver.         | 91 |

|--------------------------------------------------------------------------|----|

| FIG. 4.12. MEASURED 120 HZ LED CURRENT RIPPLE OF THE PROPOSED LED DRIVER | 91 |

# **List of Tables**

| TABLE 4.1. LIST OF COMPONENTS USED IN THE PROTOTYPE LED DRIVER           | 80 |

|--------------------------------------------------------------------------|----|

| TABLE 4.2. CHARACTERISTICS OF THE PROTOTYPE CONTROLLER IC                | 81 |

| TARLE 4.3 PERFORMANCE COMPARISON WITH STATE-OF-THE-ART AC-DC LED DRIVERS | 92 |

# Chapter 1

## Introduction

## 1.1 Motivations

Light-emitting diodes (LEDs) have been replacing traditional light sources like incandescent and fluorescent lamps in many lighting applications because LEDs have a wide color gamut, a high luminous efficacy, a long lifetime, and are environment friendly [1]–[4]. Although the first white LEDs were commercially introduced in the mid-1990s, they were not used widely because they were inefficient light sources at that time. Their luminous efficacy was much lower than other lighting technologies. Luminous efficacy, which has the unit of lumens per watt, represents lighting efficiency of light sources. However, the rapid development in LED technology is driving major changes in the lighting industry to keep up with the pace. Fig.1.1 shows the dramatic improvement in the efficacy of LEDs, as compared with other traditional light sources [5].

Fig. 1.1. Advancement in lighting technology [5].

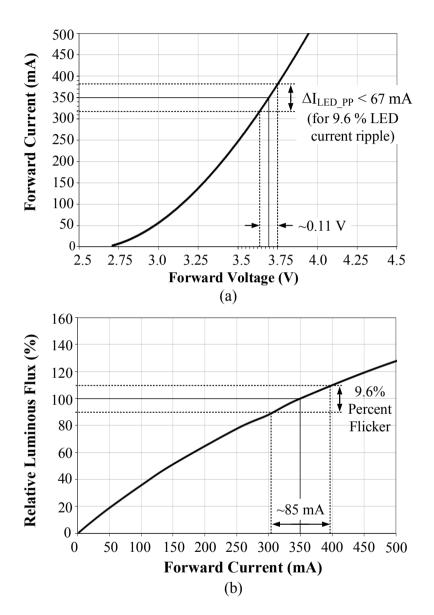

The characteristics of LEDs are very sensitive to process and temperature. Fig. 1.2 (a) indicates LED has asymmetric V-I characteristics, and Fig. 1.2 (b) shows that the luminous flux is proportional to LED currents, which means the brightness of LEDs are controlled by its forward current [6]. Due to these characteristics, driving LEDs with a fixed output voltage cannot guarantee constant brightness of LEDs. Therefore, most LED drivers must regulate the currents flowing through the LED load for achieving constant luminous intensity.

Most state-of-the-art LED drivers utilizing an off-line ac voltage source employ power factor correction (PFC) circuits to comply with standards like the IEC61000-3-2 [7] and the ENERGY STAR [8], which specifies that the power factor should be higher than 0.9 for commercial applications and 0.7 for residential applications. To

**Fig. 1.2.** LED characteristics: (a) Electrical characteristics (b) Relative luminous flux versus forward current [6].

meet these requirements, conventional single-stage LED drivers with PFC circuits that reduced the number of discrete components using simple structures with reduced costs and small form factors, were reported in [9]–[11].

However, the single-stage LED drivers [9]-[11] depicted in Fig. 1.3 exhibit light

Fig. 1.3. Conventional single-stage LED drivers that exhibits light flicker.

flicker that varies at twice the ac line frequency because they mainly focus on the PFC function only and therefore have a large LED current ripple. Flicker means a rapid and repeated change over time in the brightness of light. Although light flicker at frequencies above 70 Hz is typically invisible to most people, it may induce harmful biological effects including headache, fatigue, eyestrain, and even epileptic seizures [12], [13]. Thus, the goal of this dissertation is to design an ac-dc LED driver that can achieve acceptable power factor and reduce light flicker to low-risk levels to mitigate the harmful biological effects.

## 1.2 Flicker Metrics and Standards

According to [14], there are two common ways to measure flicker, the Flicker Index and the Percent Flicker. With reference to Fig. 1.4, the Flicker Index and Percent Flicker, which is also known as Modulation (%), can be expressed as

Flicker Index =

$$\frac{Area1}{Area1 + Area2}$$

(1.1)

Percent Flicker =

$$100 \times \frac{L_{\text{MAX}} - L_{\text{MIN}}}{L_{\text{MAX}} + L_{\text{MIN}}}$$

. (1.2)

Although the Flicker Index is mathematically able to explain differences in shape or duty cycle, the Percent Flicker is preferr—ed to calculate flickers because it needs only the measurement of maximum and minimum values, whereas calculating the Flicker Index requires the accurate sampling of complex waveforms for integral. Fig.

Fig. 1.4. Periodic waveform of light output in one cycle [14].

**Fig. 1.5.** (a) Simple periodic waveforms of light outputs (b) Flicker Index versus Percent Flicker [15].

1.5 shows the dependency between Flicker index and Percent Flicker about the three types of simple periodic waveforms: sine, triangle, and square (50% duty cycle) waveforms. Triangle waveforms always have the lowest Flicker Index when those three kinds of waveforms have the same Percent Flicker. By using this relation, calculating. By using the graph in Fig. 1.5 (b), Flicker Index can be obtained when knowing the shape of the output light waveforms and the values of Percent Flicker

**Fig. 1.6.** Recommended operating area to give low risk for headaches and photosensitive epileptic seizures [17].

[25].

Studies in [13] and [14] indicate the permissible flicker in terms of the Flicker Index or the Percent Flicker by collecting experimental data from previous flicker studies. The IEEE standard 1789-2015 in [15] provides the recommended practices for modulating current in high-brightness LEDs. According to [13] and [15], in LED lighting applications with flicker frequencies above 90 Hz, Percent Flicker for low-risk level should satisfy the following:

Percent Flicker (=Mod%)

$$< 0.08 \times f_{\text{FLICKER}}$$

(1.3)

where  $f_{\text{FLICKER}}$  is the frequency of the flickering light. Fig. 1.6 depicts the recommended operating area to limit the biological effects. For example, a Percent Flicker

of less than 9.6% is acceptable if  $f_{FLICKER}$  is 120 Hz. The relationship between the Percent Flicker and the Flicker Index is discussed in [14], where the recommended Flicker Index is:

Flicker Index

$$\leq 0.1 \ (f_{\text{flicker}} = 100 \text{ Hz}).$$

(1.4)

A Flicker Index of 0.1 is equivalent to a Percent Flicker of 20% and 30% for a square and sinusoidal light output, respectively. Thus, considering aforementioned standards about the power factor and flicker, the objective of this dissertation is to design an ac-dc LED driver that can achieve a power factor higher than 0.9 and a Percent Flicker less than 9.6% at 120 Hz.

## 1.3 Prior Works

Fig. 1.7 depicts the waveforms of an ac-dc LED driver with a constant output power, when the input power factor is unity. The input power ( $P_{in}$ ) at twice the line frequency has a pulsating waveform that periodically changes above or below the

**Fig. 1.7.** Waveforms of an ac-dc LED driver with a constant output power when the power factor is unity.

**Fig. 1.8.** Conventional two-stage ac-dc LED driver consisting of a first-stage PFC converter and a second-stage DC-DC converter.

**Fig. 1.9.** Waveforms of output current when harmonic currents are injected to the input current [24].

constant output power ( $P_o$ ). Hence, a storage capacitor as an energy buffer is required to balance out the instantaneous power differences between  $P_{in}$  and  $P_o$ . Fig. 1.8 illustrates the architecture of a conventional two-stage ac-dc LED driver with a storage capacitor ( $C_{STO}$ ) [18]–[21]. Although this approach offers a near unity power factor and a precisely regulated output voltage, it would be generally more difficult to achieve a high conversion efficiency with the two-stage architecture unless an optimized control in each stage is applied, although efficiencies up to 95% have been reported. Further, this architecture requires several components relatively, resulting in large sizes and considerable costs [22]–[24].

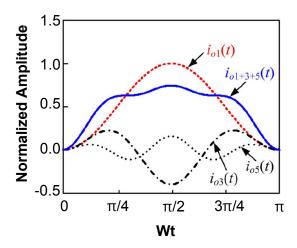

To achieve a high power factor and reduce the output LED current ripple, several methods have been proposed [23]–[39]. The first approach is to inject odd harmonic signals like the third and the fifth harmonics [24]–[26] or the third harmonic only

[27], [28] to the input current for reducing the input current pulsation, sacrificing the input power factor down to 0.9. Fig. 1.9 represents the waveform of the output current when the third and fifth harmonics are injected to the ac line frequency [24]. While the previous studies in [24], [25], and [27] show a reduction in the size of the capacitors, recent studies in [26] and [28] consider the output light flicker characteristics. Although this approach enables the single-stage architecture without the use of  $C_{\text{STO}}$ , the study in [26] requires a large output capacitor of 500  $\mu$ F for the output power of 20 W to ensure a Percent Flicker less than 40%.

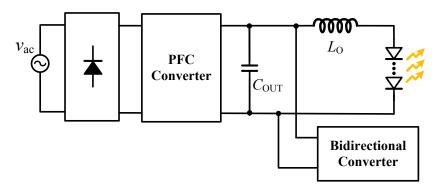

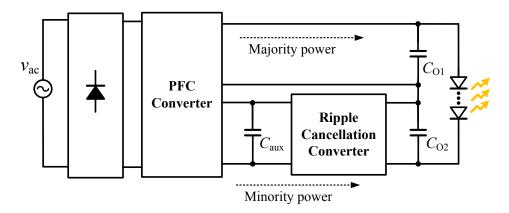

The second approach is to employ a parallel [23], [29]–[32] or a series [33]–[37] ripple cancellation converter (RCC). In [23] and [29]–[32], as illustrated in Fig. 1.10, a bidirectional converter is used as an active power filter and is placed in parallel with the LED load that is directly connected to the PFC stage, for controlling the LED current ripple. While this method can achieve a dc LED current and significantly reduce the size of the output and storage capacitors, approximately 32% of the output power is converted three times before it is delivered to the output, incurring a power loss [33]–[35]. In [33]–[37], on the other hand, the output of the RCC is connected in series with the output of the PFC stage, and the LED load is connected in parallel with the two series-connected output capacitors, which is depicted in Fig 1.11. The series RCC topology can provide a higher power efficiency than the parallel RCC topology because it further reduces the proportion of the output power converted more than once. In [33] and [34], for example, 90% of the output power is directly delivered by the PFC stage, while 10% of the output power is converted twice before being delivered to the output.

Fig. 1.10. An ac-dc LED driver employing a parallel ripple cancellation converter [30].

Fig. 1.11. An ac-dc LED driver employing a series ripple cancellation converter [35].

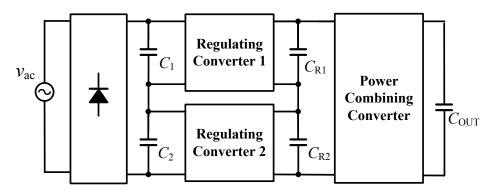

Another approach with an ac-dc power conversion architecture consisting of two stacked energy-storage capacitors across the rectifier output and two floating resonant buck converters, is proposed in [38] and depicted in Fig. 1.12. Although the stacked architecture needs an additional power combing converter composed of a switched capacitor circuit, this architecture is suitable for high-frequency operations

**Fig. 1.12.** An ac-dc power conversion architecture consisting of two stacked energy-storage capacitors [38].

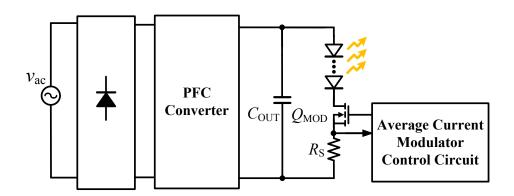

**Fig. 1.13.** A single-stage ac-dc LED driver employing an average current modulation method [39].

at 3-10 MHz, enabling the use of two 0.8 µH inductors for an LED power of 30 W. An average current modulation method for a single-stage LED driver is proposed in [39]. As illustrated in Fig. 1.13, the LED load is connected in series with a modulation switch, for pulsed current driving. To achieve a constant average level of the LED current in each modulation cycle, the duty cycle of the switch is controlled ac-

cording to the pulsating output voltage level. In [40], an ac-dc converter with a parallel PFC scheme is proposed. An isolated full-bridge boost converter is employed for the main power stage where 68% of the input power is directly delivered to the output, and the remaining 32% of the power is stored in a storage capacitor. A forward converter is placed in parallel with the boost converter and is used for the auxiliary power stage that provides the necessary power for dc output power by using the storage capacitor as its input source. Although only 32% of the power must be processed twice before being delivered to the output, this architecture requires two isolation transformers that are relatively complex and expensive.

## 1.4 Thesis Objectives and Organization

This dissertation proposes an ac-dc LED driver consisting of two parallel floating buck converters for reducing the light flicker to low-risk levels. To handle the power differences between the twice-line-frequency input power and the constant LED power, one floating buck converter conveys energy from the ac source to a storage capacitor, simultaneously performing the PFC operation. The other floating buck converter supplies constant current to the LEDs to maintain a constant brightness. The proposed architecture can achieve an input power factor higher than 0.9. Although the proposed approach offers a lower power factor than the conventional twostage approach with a boost PFC converter [18]–[21], the proposed architecture with two floating buck converters in parallel significantly reduces the average voltage of  $C_{\rm STO}$  to 56.5 V at the input voltage of 110  $V_{\rm rms}$ , whereas the average voltage of  $C_{\rm STO}$ in the two-stage must be higher than 155 V. Moreover, the size of  $C_{\rm STO}$  is reduced because less than 30% of the output power is initially stored in  $C_{STO}$  and then delivered to the LED load. Thus, the reduced voltage stress and size of  $C_{STO}$  enables ceramic or film capacitors to be utilized instead of electrolytic capacitors that have lifetime constraints.

In addition, the two floating buck converters have a low-side switch that reduces the design complexity of the gate driver circuit. Whereas the second approach employing an RCC [23], [29]–[37] requires a transformer or coupled inductor with several other components, the proposed architecture provides a low-cost solution and simple design for low-power LED lighting applications. The rest of the dissertation

is organized as follows: Chapter 2 introduces the background on LED drivers. Several power converter topologies and their characteristics are presented to help understand how power converters are employed in LED drivers. Configuration of LEDs and current sensing techniques used in LED drivers are introduced, and the active and passive PFC techniques are explained. Chapter 3 presents the system architecture and operation principle of the proposed LED driver. The design considerations for achieving a high power factor and efficiency is discussed, and the design procedure of the proposed LED driver is described. Moreover, circuit implementation and the simulation results of the controller IC are also presented. Chapter 4 presents the experimental results of the prototype LED driver, and Chapter 5 concludes this dissertation.

# Chapter 2

# **Background on LED Driver**

# 2.1 Power Converter Topologies

## 2.1.1 Linear Regulator

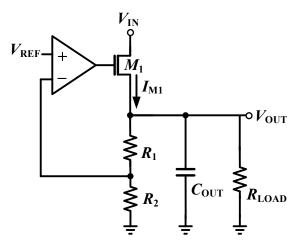

Linear voltage regulators illustrated in Fig. 2.1 are used for the dc-dc voltage conversion when the input voltage is higher than the output voltage. Here, the output voltage ( $V_{\rm OUT}$ ) can be expressed as  $V_{\rm OUT} = (1+R_1/R_2) \cdot V_{\rm REF}$ . Compared with other power converters utilizing passive energy storage elements such as inductors or capacitors, linear regulators have simple architecture and small form factor, enabling the integration with other circuits in a single chip. However, the power loss ( $P_{\rm LOSS}$ ) in the transistor  $M_1$  increases linearly with the voltage difference between the input voltage ( $V_{\rm IN}$ ) and the output voltage ( $V_{\rm OUT}$ ) because the power loss can be expressed

Fig. 2.1. Schematic of a linear voltage regulator.

as  $P_{\text{LOSS}} = (V_{\text{IN}} - V_{\text{OUT}}) \cdot I_{\text{M1}}$ . Hence, it can be seen that linear voltage regulators are suitable only when the voltage difference between  $V_{\text{IN}}$  and  $V_{\text{OUT}}$  is small.

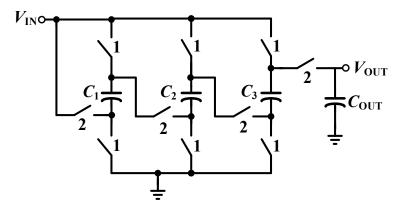

## 2.1.2 Switched-Capacitor Converter

Fig 2.2 illustrates a switched-capacitor (SC) converter with a Series-Parallel topology that is a two-phase system where switches turn on or off according to the number of phases, which changes the connection of the flying capacitors ( $C_1$ ,  $C_2$ , and  $C_3$ ) in series or parallel [41]. Hence, the ideal conversion ratio of the SC converter in Fig. 2.2 is 3 between the input voltage  $V_{\rm IN}$  and the output voltage  $V_{\rm OUT}$ , which can be expressed as  $V_{\rm OUT}$ =3 $V_{\rm IN}$ . In actual implementations,  $V_{\rm OUT}$  is smaller than 3 $V_{\rm IN}$  because of power losses such as conduction loss and switching loss. If the input and output ports are reversed in this topology, it can simply be transformed to a step-down voltage converter whose conversion ratio is 1/3.

Fig. 2.2. A switched-capacitor converter with a series-parallel topology.

Compared to inductor-based converters like buck or boost converters where an inductor occupies a large portion of the area in a printed circuit board, SC converters can be implemented with smaller area and integrated in one chip when the flying capacitors have small capacitances less than few nF. However, the possible conversion ratio is only integer or fractional number because the number of capacitors and switches are finite in actual implementations. Consequently, SC converter is not suitable for an ac-dc converter that requires a continuous conversion ratio according to the ac input voltage level.

### 2.1.3 Inductor-Based Converters

Inductor-based converters utilize inductors as a main energy storage element to deliver power to the output load. They are divided into two categories, which are isolated and non-isolated converters. Non-isolated converters include the buck,

boost, and buck-boost converters, on the other hand, isolated converters include the flyback and forward converters. Isolated converter with a transformer operates without safety issues owing to the galvanic isolation, which has different ground levels for the primary side (input) and the secondary side (output). The galvanic isolation does not allow direct conduction path from input to output. In other words, unwanted current or voltage fluctuation from input does not affect the output. However, non-isolated converters are more attractive than isolated converters because non-isolated converters have advantages such as high efficiency due to simple structure and lower fabrication cost [6], [42].

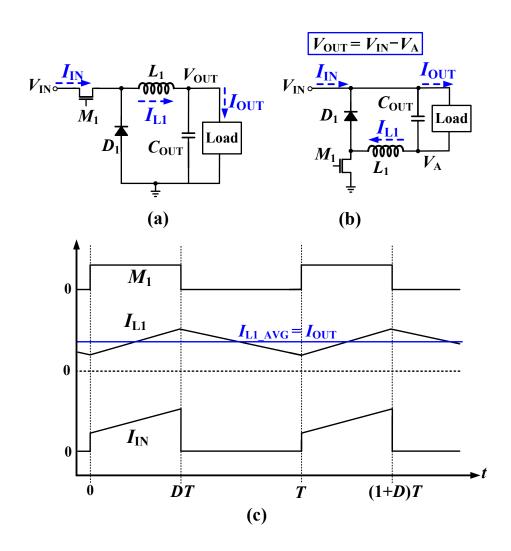

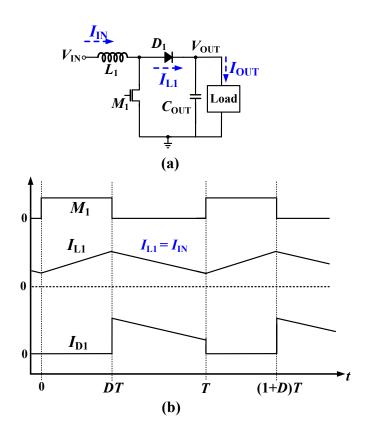

#### 2.1.3.1 Buck Converter (Floating buck Converter)

The buck converter and the floating buck converter shown in Figs 2.3 (a) and (b), respectively, are widely used as a voltage step-down converter. They consists of a power switch, an inductor, a diode, and a capacitor. In a synchronous buck converter, the diode  $D_1$  can be replaced with another power switch to reduce the conduction loss due to the forward voltage drop on diode. The difference between the two converters is that the power switch  $M_1$  is a high-side switch in the buck converter and a low-side switch in the floating buck converter. Because a hide-side switch requires a voltage bootstrapping circuit because the source of  $M_1$  is not connected to the ground, the low-side driver can reduce the complexity of its gate driver. Although their architectures are different, their operation principle is same.

Fig. 2.3 (c) illustrates the voltage and current waveforms of the buck converter

**Fig. 2.3.** Schematics of (a) a buck converter and (b) a floating buck converter, and the voltage and current waveforms of the buck converter in a CCM operation.

operating in CCM at steady-state. The conversion ratio M(D) of the buck converter can be simply derived according to the three principles in [43], which are the inductor volt-second balance, the capacitor charge balance, and the small ripple approxi-

mation. It is assumed that the input voltage  $V_{\rm IN}$  and the output voltage  $V_{\rm OUT}$  are constant and there voltage ripples are negligible. Consequently, the inductor current is equal to the output current  $I_{\rm OUT}$  and current slopes of the inductor current  $I_{\rm LI}$  are constant. Therefore, by using  $\Delta I_{\rm LI}$ =0 during one switching period, we can obtain following equations:

$$\Delta I_{L1} = \frac{(V_{IN} - V_{OUT})}{L_1} D + \frac{(-V_{OUT})}{L_1} (1 - DT) = 0$$

(2.1)

By simplifying (2.1), we can get

$$DV_{IN} = V_{OUT} \tag{2.2}$$

$$M(D) = \frac{V_{OUT}}{V_{IN}} = D \tag{2.3}$$

If we assume the efficiency is 100%, we can derive (2.6) by inserting (2.2) into (2.5).

$$P_{IN} = P_{OUT} \tag{2.4}$$

$$V_{IN}I_{IN} = V_{OUT}I_{OUT} \tag{2.5}$$

$$I_{IN} = DI_{OUT} \tag{2.6}$$

Thus, the buck converter operates as a voltage step-down converter and a current step-up converter.

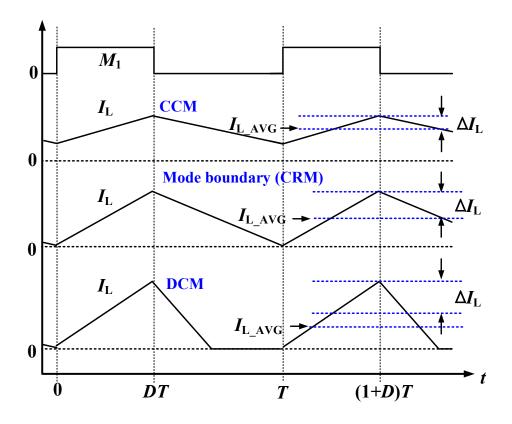

Buck converters have two operating modes according to the inductor current, which are continuous conduction mode (CCM) and discontinuous conduction mode (DCM), which is shown in Fig. 2.4. In some applications, the converter operates at the boundary condition, which is referred to as a critical conduction mode (CRM).

Fig. 2.4. Voltage and current waveforms illustrating the converter operation modes.

When the inductor current ripple  $\Delta I_{\rm L}$  is higher than average inductor current  $I_{\rm L\_AVG}$ , the converter operates in DCM. The boundary condition between CCM and DCM is  $I_{\rm L\_AVG} = \Delta I_{\rm L}$ . According to [44], the boundary condition K is defined as K=2L/RT, where R is the road resistance and T is the one switching period. If K < (1-D), the buck converter operates in DCM. Otherwise, the buck converter operates in CCM.

It can be seen that there are three important design parameters (L, R, and T) to decide whether the buck converter operates in CCM or DCM. Typical examples of the DCM operation are as follows: the converter with large inductor; the converter

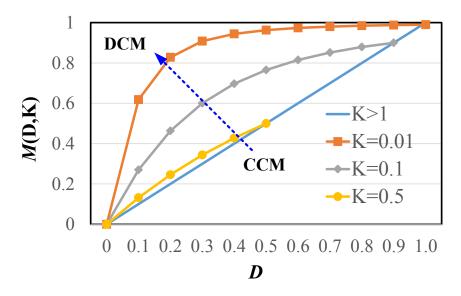

**Fig. 2.5.** Conversion ratios of the buck converter according to the boundary condition *K*.

operating at light load (small load current); the converter operating at low switching frequency. In DCM, the dynamics of converter change radically, and deriving the conversion ratio is not simple. Fig. 2.5 plots the conversion ratio versus the PWM duty cycle D, where the conversion ratio M(D,K) can be expressed as [44]:

$$M(D,K) = D$$

(K > 1-D) (2.7)

$$M(D,K) = \frac{2}{1 + \sqrt{1 + 4K/D^2}}$$

(K < 1-D). (2.8)

As the boundary condition *K* decreases, conversion ratio have more nonlinear curve. Therefore, the design parameters related to the boundary condition should be considered carefully when designing the buck converter.

## 2.1.3.2 Boost Converter

The boost converter depicted in Fig 2.6 (a) is a voltage step-up converter that the output voltage  $V_{\rm OUT}$  is higher than the input voltage  $V_{\rm IN}$  in a steady state. The boost converter has been widely used as a PFC converter because the input current is always continuous in CCM, which lead to higher power factor near unity than a buck

**Fig. 2.6.** Schematic of (a) a boost converter and (b) its voltage and current waveforms in a CCM.

converter whose input current is always discontinuous.

Fig 2.6(b) shows the voltage and current waveforms of the boost converter operating in CCM. Note that the input voltage and the output voltage is reversed in boost converter, as compared with the buck converter. When  $M_1$  is on, the input current  $I_{IN}$  flows through  $M_1$  and charges the inductor. When  $M_1$  is off, the inductor is discharged, and the inductor current  $I_{L1}$  flows from the input to the output. Hence, the inductor current is always continuous, on the other hand, the current charging capacitor is discontinuous. With the same manner in the buck converter, the conversion ratio M(D) of the boost converter can be derived as

$$\Delta I_{L1} = \frac{V_{IN}}{L_1} D + \frac{(V_{IN} - V_{OUT})}{L_1} (1 - DT) = 0$$

(2.9)

$$M(D) = \frac{V_{OUT}}{V_{IN}} = \frac{1}{1 - D}.$$

(2.10)

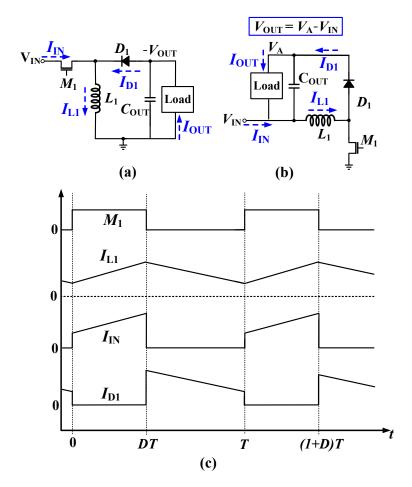

#### 2.1.3.3 Buck-boost Converter

The buck-boost converter and floating buck-boost converter are illustrated in Figs. 2.7 (a) and (b). Like in the buck converter, the buck-boost converter has a high-side power switch  $M_1$ , hence, floating buck-boost is employed for the same reason. While the buck-boost converter has the negative output voltage, the floating buck-boost converter has positive output voltage. However, their operation principle is same. As shown in Fig 2.7 (c), when charging the inductor  $L_1$ , the input current  $I_{IN}$  flows through the power switch and the inductor, which is same with the boost con-

**Fig. 2.7.** Schematics of (a) a buck-boost converter and (b) floating buck-boost converter, and (c) their voltage and current waveforms in a CCM operation.

verter operation. On the other hand, when inductor current  $I_L$  is discharged,  $I_{L1}$  flows through the diode  $D_1$  and the output capacitor  $C_{OUT}$ , which is same with the buck converter operation. Therefore, the buck-bo ost converter can be used as either a voltage step-up converter or a voltage step-down converter. The conversion ratio of the buck-boost converter covers the range combining the buck converter and the

boost converter. With the same way used before, the conversion ratio M(D) of the buck-boost converter can be derived as

$$\Delta I_{L1} = \frac{V_{IN}}{L_1} D + \frac{(-V_{OUT})}{L_1} (1 - DT) = 0$$

(2.11)

$$M(D) = \frac{V_{OUT}}{V_{IN}} = \frac{-D}{1 - D}.$$

(2.12)

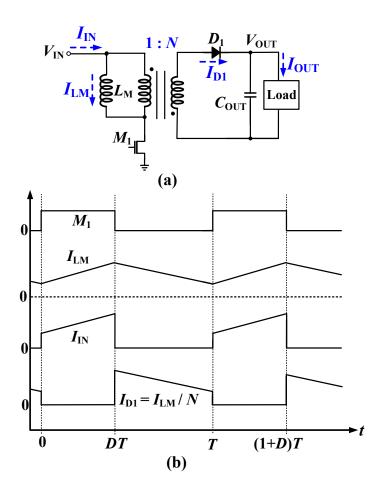

#### 2.1.3.4 Flyback Converter

Among isolated converters, the flyback converter depicted in Fig 2.8 (a) is the most popular topology in both ac-dc and dc-dc applications. The flyback converter uses coupled inductors as a transformer network. The basic operation of the flyback converter is similar with the buck-boost converter, as shown in Fig 2.8 (b). When the power switch  $M_1$  is on, the magnetization inductor  $L_M$  is charged and  $D_1$  is off due to the voltage relation due to the transformer. When  $M_1$  is off,  $L_M$  is discharged, and the transformed current  $I_{D1}$  flows through the diode and the output capacitor. The conversion ratio M(D) of the flyback converter can be expressed as

$$\Delta I_{LM} = \frac{V_{IN}}{L_M} D + \frac{(-V_{OUT} / N)}{L_M} (1 - DT) = 0$$

(2.13)

$$M(D) = \frac{V_{OUT}}{V_{IN}} = N(\frac{D}{1 - D})$$

(2.14)

where N is the turn ratio of a transformer. When N=1, the flyback converter have same conversion ratio with the buck-boost converter.

**Fig. 2.8.** Schematic of (a) a flyback converter and (b) its voltage and current waveforms in the CCM operation.

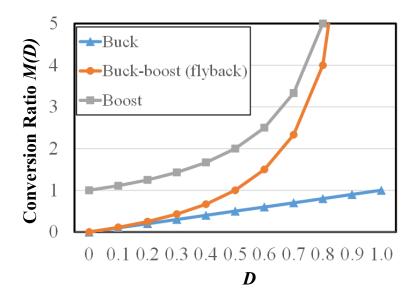

## **2.1.3.5** Summary

Fig. 2.9 plots the conversion ratios of the inductor-based converters mentioned before by using the equations (2.3), (2.10), (2.12), and (2.14). Here, it is assumed

Fig. 2.9. Conversion ratios of the inductor-based converters in a CCM operation.

that the buck -boost converter has non-inverting topology like floating buck-boost and the flyback converter has the 1:1 turn ratio between the primary and secondary side. According to the configuration of the input and output voltage level, all inductor-based converters can be adopted in ac-dc and dc-dc applications. In ac-powered LED drivers, conversion ratios needs to be controlled according to the level of the ac input voltage in order to obtain a desired level of voltage or current.

## 2.2 Basics for LED Drivers

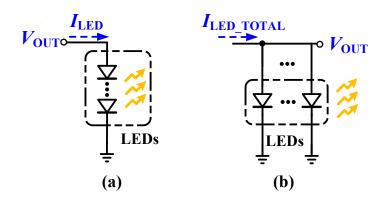

## 2.2.1 LED Configurations

In LED drivers, there are two common ways to configure LEDs, which are the series topology and parallel topology, as shown in Fig. 2.1. In series connected LEDs shown in Fig. 2.1 (a), the LED current  $I_{\text{LED}}$  flows through the all LEDs. Hence, they have same current, leading to same luminance level because the luminous flux is proportional to the LED current. However, the output voltage  $V_{\text{LED}}$  limits the number of LEDs in high power LED applications because the output voltage  $V_{\text{OUT}}$  is proportional to the number of LEDs in series.

On the other hand, the output voltage  $V_{\rm OUT}$  is relatively low in a parallel configuration of LEDs in Fig 2.1 (b), which can alleviate the voltage limit. However, LED drivers are required to have high output current to achieve desired luminance level

Fig. 2.10. LED configurations in LED drivers: (a) series (b) parallel.

because the tota l LED current  $I_{LED\_TOTAL}$  is distributed to each LED. Moreover, their brightness level m ight be different because LEDs have turn-on voltage variations during the manufacturing process because the same output voltage is applied to all LEDs.

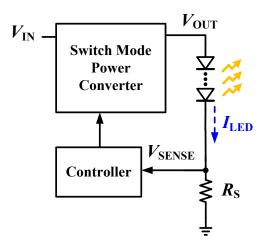

## 2.2.2 Current Sensing Techniques in LED Drivers

In order to regulate the current flowing through the LED load to a desired luminance level, first of all, a current sensing technique is required and then a feedback loop controls the PWM duty cycle D of the main power transistor. The simple and direct way to sense LED current is to place a resistor with the LEDs in series, as shown in Fig. 2.11. This method is employed in many LED drivers [3], [10], [19] because it can provide very accurate sense voltages to a feedback controller. How-

Fig. 2.11. Basic configuration of a constant current LED driver

ever, the conduction loss on  $R_{\rm S}$  (=  $I_{\rm LED}^2R_{\rm S}$ ) might be not adequate when a series resistor with large resistance is required because the sense circuit such as a comparator or an op-amp have poor resolution. In addition, this method cannot be adopted in some LED drivers due to their converter architectures. For example, floating buck or buck-boost converters have a floating output capacitor and a LED load which are not referenced to the ground [6]. Hence, they requires a differential current sensing technique and a more complicated sense circuit. In flyback converters, an additional opto-coupler is needed because the LEDs are placed in the secondary side, on the other hand, the controller circuit is placed in the primary side due to the galvanic isolation [43].

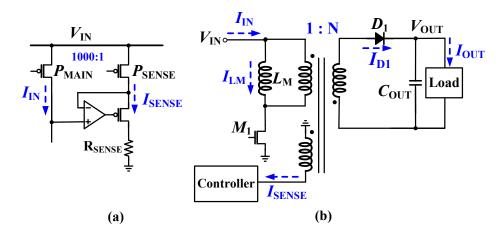

There are indirect current sensing techniques, which can sense the currents flowing through the power switch or an inductor. A sense-FET based topology shown in Fig. 2.12 (a) senses 1000 times smaller input current by forcing the drain voltage of the two PMOS transistors ( $P_{\text{MAIN}}$  and  $P_{\text{SESNE}}$ ) have same voltage level [45]. This

Fig. 2.12. Indirect current sensing techniques: (a) sense-FET (b) auxiliary winding.

method is suitable to an on-chip power converter where the current mirror network can be simply designed. With this technique, the LED current level can be obtained by sensing inductor current which have a certain relation with the LED current. For example, the average inductor current is equal to the average LED current in buck converter with a CCM operation. Moreover, this method can be used for a zero current detection (ZCD) in converters which operate at DCM or CRM. Fig. 2.12(b) shows an example of indirect current sensing technique in a converter where the magnetization inductor current  $I_{LM}$  is transformed to the sense current  $I_{SENSE}$ . However, converters adopting a coupled inductor can use this method by adding an auxiliary winding to the transformer.

## 2.3 PFC Techniques in LED Drivers

## 2.3.1 Power Factor

Power factor is a figure of merit which evaluates how effectively energy is transferred from input to the output load. It is defined as the ratio of the real power flowing to the output load to the apparent power in the ac system. It is also defined as

Power factor =

$$\frac{P_{IN\_AVG}}{V_{AC\_RMS} \times I_{AC\_RMS}}$$

(2.15)

where  $P_{\text{IN\_AVG}}$  is the average input power,  $V_{\text{AC\_RMS}}$  and  $I_{\text{AC\_RMS}}$  are the ac input voltage and current respectively. The power factor has always a value range from zero to one. When the power factor is unity, the waveforms of the input voltage and current have the same shape and same harmonic spectrum [44].

## 2.3.2 Passive PFC Circuit

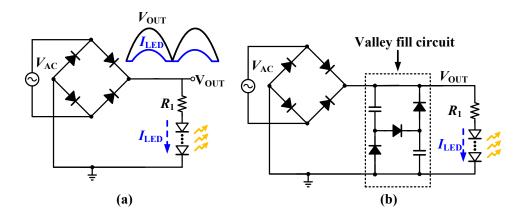

Figure 2.13 shows two conventional passive LED driver. Although they have very simple structures with only passive elements, they do not achieve high power factor. A resistive LED driver shown in Fig. 2.13 (a) have a power factor higher than 0.8. The limitation of this topology is that the conduction time of the LED current does not fully cover one ac cycle due to the turn-on voltages of the LEDs. Fig. 2.13 (b) illustrates a resistive LED driver with a valley fill circuit that is employed to increase the conduction time of the input. Hence, this valley fill type LED driver

**Fig. 2.13.** Conventional passive PFC LED driver: (a) Resistive type (b) Valley fill type. might achieve a power factor higher than 0.9.

## 2.3.3 Active PFC Circuit

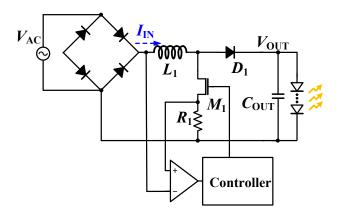

Aforementioned inductor-based converters in Chapter 2.1.3 can be adopted as an active PFC circuit. A boost converter shown in Fig. 2.14 is a suitable solution to

Fig. 2.14. A boost type LED driver with a PFC controller.

achieve high power factor because its input current is always continuous in a CCM operation. Therefore, if the controller circuit forces the input current to follow a reference voltage divided from the input voltage, it can achieves near unity power factor. However, the output voltage  $V_{\rm OUT}$  is usually above 400 V in a boost type LED driver powered by a 220 V<sub>rms</sub> input voltage because  $V_{\rm OUT}$  should be higher than the input voltage in boost converters, which results in use of a bulky electrolytic capacitors and excessive number of LEDs in series.

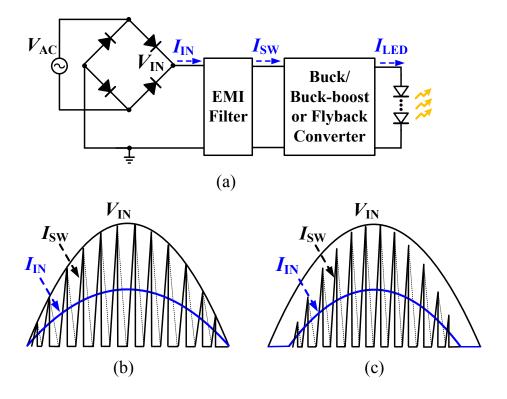

To avoid such a voltage limitation in boost converters, many LED drivers em-

**Fig. 2.15.** (a) Single stage LED driver with an input EMI filter. Voltage and current waveforms of (b) a buck-boost or a flyback, and (c) a buck converter in the CRM opera-

ploys the buck or buck-boost or flyback topologies as depicted in Fig. 2.15 (a). These topologies have discontinuous input current due to the switching behavior, which limits to achieve high power factor. However, owing to the input EMI filter, the switching input current  $I_{SW}$  is shaped, consequently, the waveform of the input current  $I_{IN}$  has the shape of averaged  $I_{SW}$ . Therefore, a buck-boost [6] or a flyback [42] converters can achieve a high power factor up to 0.99 in the CRM (or DCM) operation with a fixed PWM duty cycle, as shown in Fig. 2.15 (b). In a buck converter shown in Fig. 2.15(c), it can achieve a power factor up to 0.95 because the conduction time of the input current  $I_{IN}$  is limited in buck converters [38]. In these single-stage PFC converters, high switching frequency is desirable to minimize the size of the input EMI filter.

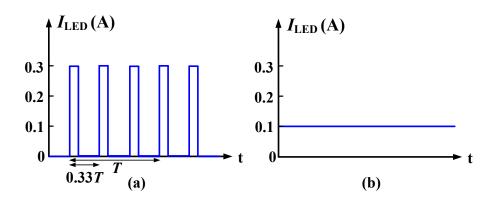

## 2.4 Dimming Techniques

There are two popular techniques for dimming LEDs that are the PWM dimming and analog dimming (also called as continuous current reduction (CCR) dimming), which is shown in Fig. 2.16. In a PWM dimming, LED turns on and off at during every dimming period. A nominal rated current flows through the LEDs while the PWM switch is on, whereas there is no LED current while the PWM switch turns off. Since the average current level is changed by the PWM duty cycle, the brightness level also varies. However, the PWM dimming might exhibit light flickers because the current amplitude fluctuates between zero and the rated current, incurring a Per-

Fig. 2.16. Two popular dimming methods: (a) PWM dimming (b) analog dimming.

cent Flicker of 100%. Thus, as presented in Chapter 1, the dimming frequency should be higher than 1.2 KHz in order to avoid harmful effects to people.

On the other hand, the LED current flows continuously in an analog dimming. Instead, output current level is directly modulated because the brightness of LEDs is proportional to its forward current. Accordingly, analog dimming can be considered as an inherently flicker-free dimming method.

## Chapter 3

Design of an AC-DC LED Driver with a Two Parallel Floating Buck Topology

# 3.1 Proposed System Architecture and Operation Principle

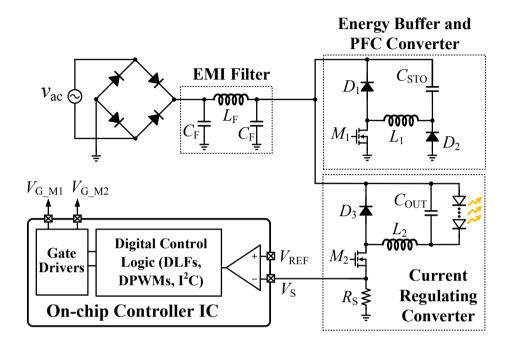

## 3.1.1 Overall Architecture

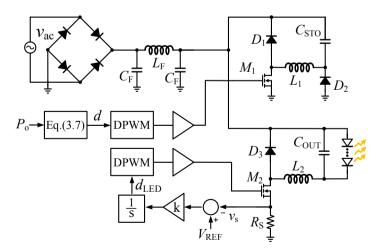

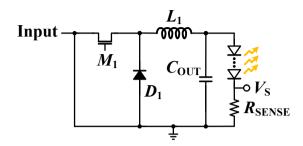

Fig. 3.1 illustrates the overall architecture of the proposed LED driver that consists of a full bridge rectifier, an EMI filter, two parallel floating buck converters, and an on-chip controller IC. The upper floating buck converter composed of  $M_1$ ,  $L_1$ ,  $D_1$ ,  $D_2$ , and  $C_{STO}$  performs the PFC function while simultaneously transmitting energy from an ac source to a storage capacitor  $C_{STO}$ , to buffer the instantaneous power

**Fig. 3.1**. Overall architecture of the proposed ac-dc LED driver with two parallel floating buck converters.

differences between the input power and the output LED power. The other floating buck converter consisting of  $M_2$ ,  $L_2$ ,  $D_3$ , and  $C_{\text{OUT}}$  regulates the output current to maintain the brightness of the LEDs to reduce light flicker. The EMI filter suppresses electrical noises from the AC source and the switching circuits, and shapes the ac input current for the PFC.

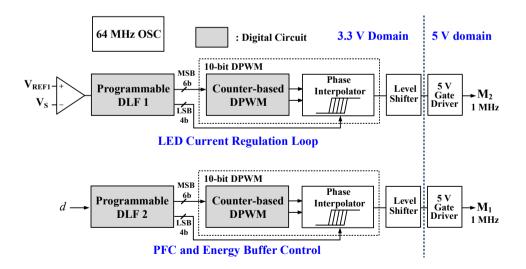

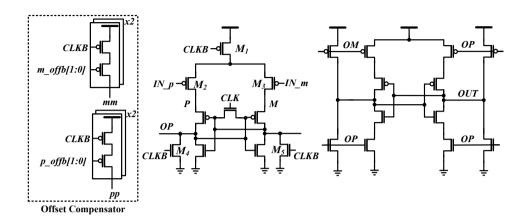

The duty cycle of the switches  $M_1$  and  $M_2$  are controlled by a digital control logic composed of programmable digital loop filters (DLFs) and digital pulse width modulators (DPWMs). For a 10 bit DPWM, the upper 6 bit resolution is realized by a counter-based DPWM and the lower 4 bit resolution is obtained by a phase interpo-

lator circuit to improve the input clock frequency requirement [46]. For example, if the input clock frequency is 64 MHz, the output switching frequency is 1 MHz.

Floating buck converters also known as inverted buck converters have been widely used as current regulators in dc-dc [47], [48] and ac-dc LED drivers [10], [11], [21], [38]. While the traditional buck converter with a high-side switch requires additional bootstrapping circuits, the floating buck converter with a low-side NFET can be easily driven by a gate driver circuit. Therefore, the proposed ac-dc LED driver with two floating buck converters in parallel can be cost effective because of a reduced component count [47]. Further, as a floating buck converter has a floating output voltage, the voltage stress of  $C_{\text{STO}}$  can be greatly reduced if the voltage across  $C_{\text{STO}}$  is well regulated by the controller circuit. Hence, ceramic or film capacitors can be employed for  $C_{\text{STO}}$  in place of electrolytic capacitors.

## 3.1.2 Operation Principle

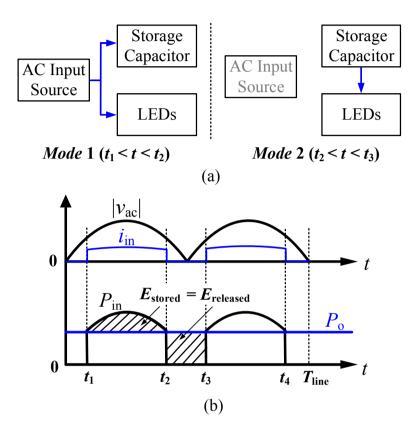

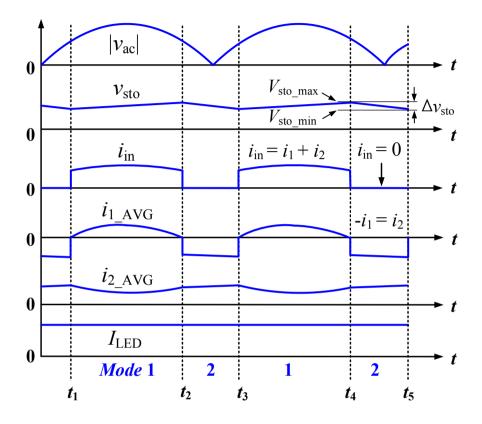

Fig. 3.2 (a) depicts the concept of energy flow in the proposed architecture with two alternating operating modes,  $Mode\ 1$  and  $Mode\ 2$ ; Fig. 3.2 (b) illustrates its theoretical input and output power waveforms. The energies stored and released by the storage capacitor, indicated as  $E_{\text{stored}}$  and  $E_{\text{released}}$ , respectively, can be expressed as

$$E_{\text{stored}} = \int_{t_1}^{t_2} (P_{\text{in}}(t) - P_{\text{O}}) dt$$

(3.1)

$$E_{released} = \int_{t_2}^{t_3} Po \ dt = P_o \times (t_3 - t_2). \tag{3.2}$$

During Mode 1, energy from the ac input source is delivered to both the LEDs and

**Fig. 3.2**. (a) Energy flow concept and (b) input and output waveforms of the proposed LED driver with two alternating operating modes.

the storage capacitor. During  $Mode\ 2$ , the stored energy  $E_{stored}$  is transferred to the LEDs without the help of the ac source. Therefore, the LED load has a constant output current regardless of the mode of operation. The detailed explanation for each mode of operation is as follows:

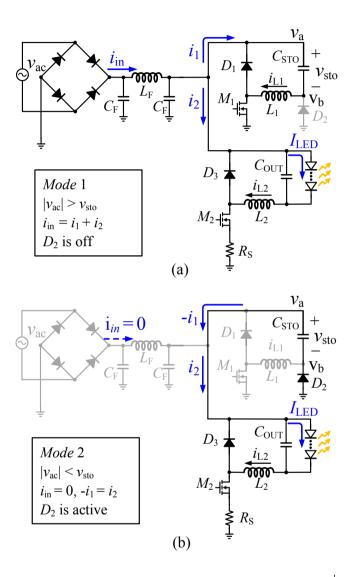

1) *Mode* 1: when  $|v_{ac}| > v_{sto}$  ( $t_1 < t < t_2$ )

Figs. 3.3 and 3.4 illustrate the operating modes and the block diagram of the proposed LED driver with two parallel floating buck converters, respectively, and Fig.

**Fig. 3.3**. Operating modes of the proposed LED driver: (a) *Mode* 1 when  $|v_{ac}| > v_{sto}$  and (b) *Mode* 2 when  $|v_{ac}| < v_{sto}$ .

3.5 shows its theoretical voltage and current waveforms. The two operating modes alternate according to the voltage relationship between the ac input voltage ( $\nu_{ac}$ ) and

the voltage across  $C_{STO}$ , denoted as  $v_{sto}$ . During  $Mode\ 1$  when  $|v_{ac}| > v_{sto}$ , the input voltage and current can be expressed as

$$v_{ac}(t) = V_{m} \sin wt \tag{3.3}$$

$$i_{\rm in} = i_1 + i_2 \tag{3.4}$$

where  $i_1$  and  $i_2$  are input currents of the two floating buck converters, respectively. As shown in Fig. 3.3 (a), the input current ( $i_{in}$ ) can be expressed as the sum of  $i_1$  and  $i_2$  because the two floating buck converters operate separately in *Mode* 1.

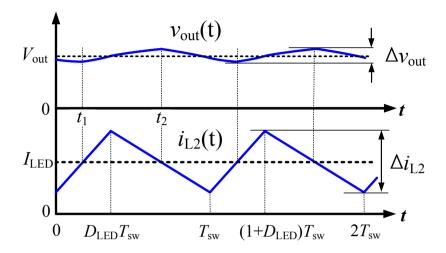

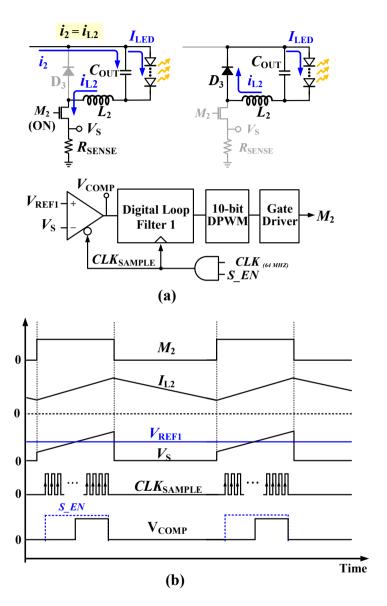

The lower floating buck converter regulates the current flowing through the LEDs regardless of the two operating modes to provide a constant current to the LEDs. This regulating converter operates in a fixed-frequency continuous conduction mode (CCM) to reduce the output voltage ripple. As shown in Fig. 3.4, the duty cycle ( $D_{\text{LED}}$ ) of switch  $M_2$  is controlled by the feedback loop to achieve the desired LED current. If we assume that the power efficiency of the current regulating con-

**Fig. 3.4**. Block diagram of the proposed LED driver with a two parallel floating buck topology.

Fig. 3.5. Theoretical voltage and current waveforms of the proposed LED driver.

verter is 100%, the averaged current ( $i_{2\_AVG}$ ), flowing into the regulating converter in one switching cycle can be expressed as

$$i_{2\_AVG}(t) = \frac{P_o}{V_m |\sin wt|}.$$

(3.5)

As shown in Fig. 3.5,  $i_{2\_AVG}$  is inversely proportional to the ac input voltage ( $v_{ac}$ ), i.e., an additional PFC circuit is required for a high power factor. Therefore, the other floating buck converter is employed for the PFC function and placed in parallel

with the current regulating converter. Although employing a bidirectional boost converter instead of a floating buck converter is a possible approach that applies to the energy flow concept shown in Fig. 3.2, the one buck and one boost approach requires higher voltage stress in  $C_{\text{STO}}$ ; i.e.,  $v_{\text{sto}}$  should be higher than the ac input voltage.

To achieve a high power factor, the upper floating buck converter shown in Fig. 3.3 (a) operates in a discontinuous conduction mode (DCM) with a fixed duty cycle (D) and the diode  $D_2$  is always off during Mode 1. As shown in Fig. 3.4, the duty cycle D of power switch  $M_1$  is obtained from (3.7) and programmed to the digital control logic through an inter-integrated circuit ( $I^2C$ ) interface. Although the buck PFC converter with a clipped-sinusoidal input current usually has a lower power factor than the boost PFC converter, it can achieve a power factor ranging from 0.82 to 0.98 and meet the harmonic requirements (IEC61000-3-2) [49]–[51]. Besides, its low output voltage permits the use of lower voltage-rated semiconductor devices and capacitors [49]–[51]. The averaged current ( $i_{1\_AVG}$ ) flowing into the buck PFC converter operating in a DCM can be expressed as

$$i_{\text{LAVG}}(t) = \frac{D^2}{2L_1 f_{\text{sw}}} (V_{\text{m}} | \sin wt | -v_{\text{sto}}(t))$$

(3.6)

where D is the duty cycle of the power switch  $M_1$  and  $f_{sw}$  is the switching frequency of the buck PFC converter [49]. It is noted that  $i_{1\_AVG}$  shown in Fig. 3.5 is proportional to the voltage difference between the input voltage ( $v_{ac}$ ) and the output voltage ( $v_{sto}$ ). Inserting (3.5) and (3.6) into (3.4), the input current ( $i_{in}$ ) is obtained as

$$i_{\text{in}}(t) = \frac{D^2}{2L_1 f_{\text{sw}}} (V_{\text{m}} | \sin wt | -v_{\text{sto}}(t)) + \frac{P_{\text{o}}}{V_{\text{m}} | \sin wt |}$$

(3.7)

where the input current  $(i_1)$  of the PFC converter cancels out the input current  $(i_2)$  of the regulating converter.

Further, the PFC converter also stores energy in  $C_{STO}$  to buffer the twice-line-frequency energy. Because this converter does not have a load to consume the output power, the energy charged onto the inductor ( $L_1$ ) by the ac input source is stored in  $C_{STO}$ . Consequently, the storage capacitor voltage ( $v_{sto}$ ) shown in Fig. 3.5 increases until it enters  $Mode\ 2$  and can be expressed as

$$v_{\text{sto}}(t) = V_{\text{sto\_min}} + \frac{1}{C_{\text{STO}}} \int_{t_1}^{t} i_{L1}(t) dt, (t_1 < t < t_2).$$

(3.8)

By using the minimum and maximum voltage values of the storage capacitor, the stored energy  $E_{\text{stored}}$  is expressed as

$$E_{\text{stored}} = \frac{C_{\text{STO}}}{2} (V_{\text{sto\_max}}^2 - V_{\text{sto\_min}}^2) = C_{\text{STO}} \cdot \Delta v_{\text{sto}} \cdot V_{\text{sto\_AVG}}$$

(3.9)

where  $\Delta v_{\text{sto}} = V_{\text{sto\_max}} - V_{\text{sto\_min}}$  and  $V_{\text{sto\_AVG}}$  is the average voltage of  $v_{\text{sto}}$  across  $C_{\text{STO}}$ .

As the floating buck converter has a floating output voltage, the positive terminal voltage  $(v_a)$  of  $C_{STO}$  is equal to  $|v_{ac}|$  in  $Mode\ 1$  and the negative terminal voltage  $(v_b)$  can be expressed as

$$v_{b}(t) = \left| v_{ac}(t) \right| - v_{sto}(t). \tag{3.10}$$

As the voltage level of  $|v_{ac}|$  decreases,  $v_b$  also decreases and approaches ground. When  $|v_{ac}|$  falls below  $v_{sto}$ ,  $v_b$  becomes negative. Consequently, a transition from *Mode* 1 to *Mode* 2 occurs when diode  $D_2$  becomes active and starts conducting.

#### 2) *Mode* 2 when $|v_{ac}| \le v_{sto}$ ( $t_2 \le t \le t_3$ )

As illustrated in Fig. 3.3 (b), the full bridge rectifier is off and the PFC converter

is idle because  $v_{\text{sto}}$  is higher than  $|v_{\text{ac}}|$ . Thus, the input current  $(i_{\text{in}})$  and the current  $(i_2)$  flowing into the lower floating buck converter are:

$$i_{in} = 0$$

and  $i_2 = -i_1$ . (3.11)

The storage capacitor  $C_{STO}$  operates like a ground-connected capacitor and acts as an energy source for the regulating converter. When the switch  $M_2$  is on, the diode  $D_2$  turns on and the energy stored in  $C_{STO}$  during  $Mode\ 1$  is delivered to the LEDs. Hence,  $v_{sto}$  decreases until it enters  $Mode\ 1$ , whereas, the averaged current  $(i_{2\_AVG})$  increases because the input current of the regulating converter is inversely proportional to the input voltage. Similar to the derivation of (3.5) in  $Mode\ 1$ ,  $v_{sto}$  and  $i_{2\_AVG}$  as shown in Fig. 3.5, can be expressed as

$$i_{2_{\text{AVG}}}(t) = \frac{P_{\text{O}}}{v_{\text{sto}}(t)}$$

(3.12)

where

$$v_{\text{sto}}(t) = V_{\text{sto}\_\text{max}} - \frac{1}{C_{\text{STO}}} \int_{t_2}^{t} i_2(t) dt \ (t_2 < t < t_3).$$

(3.13)

Here, the voltage ( $v_{\text{sto}}$ ) on the storage capacitor should be higher than the output voltage across the LED load for the buck operation, i.e.,  $V_{\text{sto}\_\text{min}} > V_{\text{out}}$ .

In the following ac cycle, when the ac input voltage increases above  $v_{\text{sto}}$ , the full bridge rectifier is turned on, the diode  $D_2$  is off and  $Mode\ 1$  starts again. It is noted that the input voltage of the regulating converter is  $v_{\text{ac}}$  in  $Mode\ 1$  and  $v_{\text{sto}}$  in  $Mode\ 2$ . Hence, the input voltage level is continuous because mode changes occur when the two voltages ( $v_{\text{ac}}$  and  $v_{\text{sto}}$ ) have the same voltage level. Therefore, the regulating converter can supply a dc current to the LEDs without causing a fluctuation in  $I_{\text{LED}}$  during the transition period between the two operating modes.

## 3.1.3 Discussion on Dimming

Although the proposed LED driver does not have the dimming function, the proposed architecture could accommodate analog dimming operation. The regulating buck converter can adjust the continuous value of the LED current while changing the dimming level of LEDs by setting the reference voltage ( $V_{\rm REF}$ ) shown in Fig. 3.4. Owing to the  $P_{\rm o}$  variations with the dimming of LEDs, the level of  $v_{\rm sto}$  varies because the amount of energy stored and released by  $C_{\rm STO}$  is proportional to  $P_{\rm o}$ . Therefore, the duty cycle D of  $M_{\rm l}$  in the PFC converter must be controlled by a feedback loop to maintain  $v_{\rm sto}$  in the proper operating range during the dimming operation. If the feedback loop for the dimming operation is added to the controller IC, we expect that analog dimming would be possible in this approach. A behavioral simulation is

**Fig. 3.6.** Simulated waveforms that represents LED dimming operation.

performed to demonstrate the dimming function, where the duty cycle of  $M_1$  is controlled by a feedback loop. As shown in Fig 3.6, the LED current settles to a new value after adjusting the reference voltage to set the LED current level.

## 3.2 Design of the Proposed Topology

## 3.2.1 Relationship Between the Input Current Waveform and the Power Factor

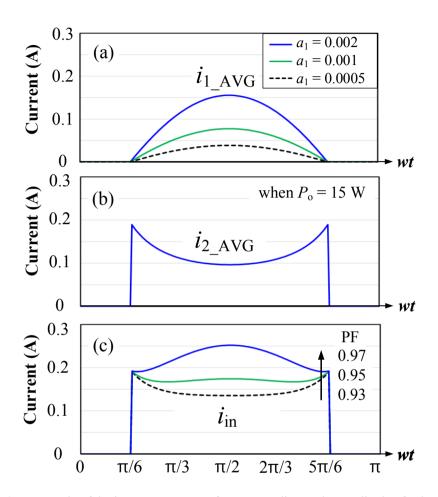

The line input current ( $i_{in}$ ) consists of two current components ( $i_1$  and  $i_2$ ) that flow into the respective floating buck converters in *Mode* 1. By substituting  $a_1 = \frac{D^2}{2L_1 f_{sw}}$  into (3.7), the input current is rearranged as

$$i_{in}(t) = a_1(V_m |\sin wt| - v_{sto}(t)) + \frac{P_o}{V_m |\sin wt|}.$$

(3.14)

The input current waveform is determined by the design parameter ( $a_1$ ), the storage capacitor voltage ( $v_{\text{sto}}$ ), and the output power ( $P_o$ ). Fig. 3.7 illustrates the variations in the input current waveform according to the amplitude of  $i_1$  that is the input current of the PFC converter, in  $Mode\ 1$ . It is assumed that the output power ( $P_o$ ) is 15 W,  $v_{\text{sto}}$  (t) has a constant value of  $V_{\text{m}}/2$  for simplicity, and the power efficiency is different in each case to show variations of the input current waveform. Figs. 3.7 (a) and 3.7 (b) show the averaged currents  $i_{1\_\text{AVG}}$  and  $i_{2\_\text{AVG}}$  in one switching cycle, respectively, and Fig. 3.7 (c) depicts an example of the input current's ( $i_{\text{in}}$ ) waveform by summing the two input current components. As the amplitude of  $i_1$  increases, the input current increasingly resembles a sine curve and achieves a higher power factor, of up to 0.97.

**Fig. 3.7.** Example of the input current waveforms according to the amplitude of  $i_1$  in *Mode* 1, when  $v_{\text{sto}}(t)$  is  $V_{\text{m}}/2$  (= 77.8 V) and the output power ( $P_{\text{o}}$ ) is 15 W.

# 3.2.2 Design Considerations for Deciding the Storage Capacitor Voltage

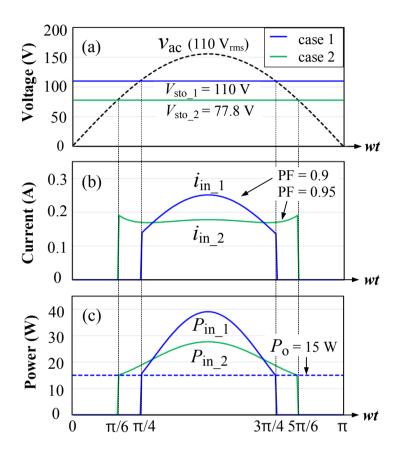

As described in section II, the storage capacitor voltage  $(v_{sto})$  increases in *Mode* 1, whereas, it decreases in *Mode* 2. The average voltage of  $v_{\text{sto}}$  settles to a certain value where the stored energy ( $E_{\text{stored}}$ ) in  $C_{\text{STO}}$  is equal to the released energy ( $E_{\text{released}}$ ) for the LED load. Fig. 3.8 describes the variations in the waveforms of the respective input currents  $(i_{in_1}$  and  $i_{in_1}$ ) and the input powers  $(P_{in_1}$  and  $P_{in_2})$  depending upon the voltage across the storage capacitors ( $V_{\text{sto}_1}$ : 110 V and  $V_{\text{sto}_2}$ : 77.8 V), respectively. Here, the output power  $(P_0)$  is 15 W; it is assumed that  $V_{\text{sto}\_1}$  and  $V_{\text{sto}\_2}$  are constant and the power conversion efficiency is 100%. The conduction periods of  $i_{\text{in 1}}$  and  $i_{\text{in 2}}$  are 1/2 and 2/3, respectively, of a half line cycle, as they are decided by the voltage levels of  $v_{\text{sto 1}}$  and  $v_{\text{sto 2}}$ , respectively. In other words, the stored energy ratio  $(E_{\text{stored}} / E_{\text{total}})$  is 1/2 in case 1 and 1/3 in case 2, where  $E_{\text{total}}$  is the total input energy for one half line cycle. Therefore, as shown in Fig. 3.8 (c), the input power  $(P_{\text{in }1})$  is higher than  $P_{\text{in }2}$  for most of the conduction period so that more energy is stored in  $C_{STO}$ . As shown in Fig. 3.8 (b), compared to  $i_{in_2}$ , it should be noted that  $i_{\text{in 1}}$  leads to a lower power factor of 0.9 owing to a shorter conduction period, although its waveform is more similar to the line voltage.

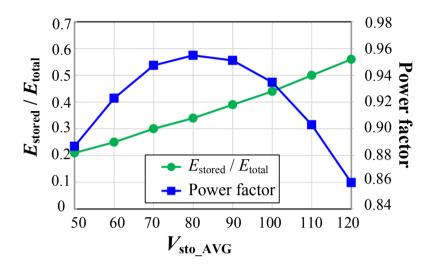

Fig. 3.9 plots the stored energy ratio ( $E_{\rm stored}/E_{\rm total}$ ) and the power factor with respect to the average values of the storage capacitor voltage denoted as  $V_{\rm sto\_AVG}$ , when the output power is 15 W and the input voltage is 110 V<sub>rms</sub>, where it is assumed that the efficiency is 100% and  $v_{\rm sto}$  has a constant value of  $V_{\rm sto\_AVG}$ . The stored energy ratio ( $E_{\rm stored}/E_{\rm total}$ ) increases from 0.21 to 0.56 with the voltage level of  $V_{\rm sto\_AVG}$  that

**Fig. 3.8.** Waveforms of the input current and input power at two different voltage levels of  $v_{\text{sto}}$ , when the output power ( $P_0$ ) is 15 W: (a)  $v_{\text{sto}}$  (case 1: 110 V, case 2: 77.8 V), (b)  $i_{\text{in}}$ , and (c)  $P_{\text{in}}$ .

decides the length of the  $Mode\ 2$  period, where the LED load is driven by the stored energy  $E_{\text{stored}}$  in the storage capacitor. Minimizing  $E_{\text{stored}}/E_{\text{total}}$  is desirable for improving the efficiency of the proposed LED driver because  $E_{\text{stored}}$  is the energy that is converted twice before it is finally delivered to the LED load. Moreover, according to (13), the voltage stress and the size of the storage capacitor can be reduced if

**Fig. 3.9.** Stored energy ratio ( $E_{\text{stored}}/E_{\text{total}}$ ) and power factor with respect to the average values of the storage capacitor voltage, when the input voltage is 110 V<sub>rms</sub>.

#### $E_{\text{stored}}$ is decreased.

As  $V_{\rm sto\_AVG}$  increases from 50 to 120 V, the values of the power factor increase from 0.89 to 0.95 until  $V_{\rm sto\_AVG}$  is 8 0 V and then they decrease from 0.95 to 0.86. When  $V_{\rm sto\_AVG}$  is below 80 V, the input power factor is primarily influenced by the amplitude of the input current component for the PFC. However, when  $V_{\rm sto\_AVG}$  is above 80 V, the power factor is degraded by the reduced conduction time of the input current. For a power factor greater than 0.9, to comply with the ENERGY STAR standards [6], the possible voltage range of  $V_{\rm sto\_AVG}$  is 55–110 V, in this example. Therefore, a design trade-off between minimizing  $E_{\rm stored}/E_{\rm total}$  and achieving a high power factor needs to be considered when deciding the storage capacitor voltage.

# 3.2.3 Analysis of the Proposed LED Driver with Line Voltage Variations

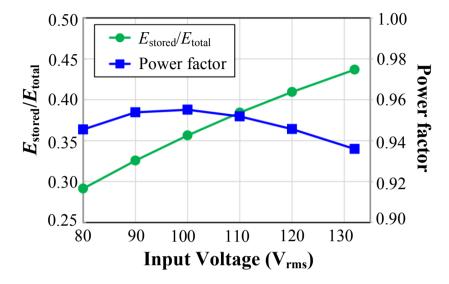

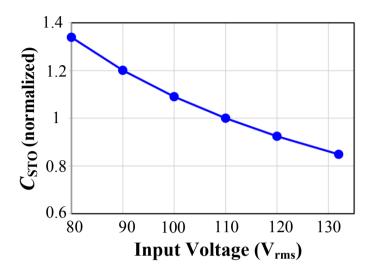

The graphs of the power factor and  $E_{\rm stored}/E_{\rm total}$  plotted in Fig. 3.9 maintain the same shape as the line voltage varies. However, the values of  $V_{\rm sto\_AVG}$  shown on the x-axis vary proportionally with the line voltage because the conduction time of the input current is decided by  $V_{\rm sto\_AVG}$ ; i.e., the operating mode changes when  $V_{\rm m}{\rm sin}wt$  =  $v_{\rm sto}$ . According to (3.7), with line voltage variations, the two current components of the input current ( $i_{\rm in}$ ) increase or decrease in opposite directions because the buck PFC converter operates with a fixed duty cycle (D). In other words, the stored energy ratio ( $E_{\rm stored}/E_{\rm total}$ ) and the ratio of  $V_{\rm sto\_AVG}/V_{\rm in,rms}$  increase with the line voltage.

To handle line voltage variations ranging from 80 to 132  $V_{rms}$ ,  $V_{sto\_AVG}$  must be maintained within a voltage range from  $V_{in,rms}/2$  to  $V_{in,rms}$  for PF > 0.9, which is equivalent to  $E_{stored}/E_{total}$  being 0.23–0.5. For example,  $V_{sto\_AVG}$  must be less than 132  $V_{rms}$  for  $E_{stored}/E_{total} < 0.5$  when the input voltage is 132  $V_{rms}$ . On the other hand,  $V_{sto\_AVG}$  must be higher than 40  $V_{sto\_AVG}/E_{total} > 0.23$  when the input voltage is 80  $V_{rms}$ . Here,  $V_{sto\_min} > V_{out}$  must be satisfied for proper operation of the LED driver. If  $V_{sto\_AVG}$  becomes too low, i.e.,  $V_{sto\_min} > V_{out}$  cannot be satisfied, the Percent Flicker increases because the LED load cannot be fully driven by  $C_{STO}$  during Mode 2.

The input voltage range of the proposed LED driver can be derived by calculating the stored energy ( $E_{\rm stored}$ ) for a half line cycle when the stored energy ratio ( $E_{\rm stored}/E_{\rm total}$ ) is 0.23 and 0.5. For simplicity of analysis, it is assumed that the efficiency is 100% and  $v_{\rm sto}$  has a constant value of  $V_{\rm sto\_AVG}$  that is higher than  $V_{\rm out}$ . According to Fig. 3.9, the two cases can be summarized as follows:

1) When

$$V_{\rm m} = V_{\rm m\_min}$$

,  $E_{\rm stored1}/E_{\rm total} = 0.23$  and  $V_{\rm sto\_AVG1} = 0.5 \times \frac{V_{\rm m\_min}}{\sqrt{2}}$

2) When

$$V_{\rm m} = V_{\rm m\_max}$$

,  $E_{\rm stored2}/E_{\rm total} = 0.5$  and  $V_{\rm sto\_AVG2} = \frac{V_{\rm m\_max}}{\sqrt{2}}$

where  $V_{\text{m_min}}$  and  $V_{\text{m_max}}$  are the minimum and maximum amplitudes, respectively, of the input voltage in each case. Because the total input energy ( $E_{\text{total}}$ ) is equal in each case, the relationship between  $E_{\text{stored1}}$  and  $E_{\text{stored2}}$  is

$$E_{\text{stored1}} = (0.23/0.5) \times E_{\text{stored2}}.$$

(3.15)

Because  $E_{\text{stored}}$  is the input power of the PFC buck converter, it can be expressed as

$$E_{\text{stored}} = \int_{t_1}^{t_2} v_{\text{ac}}(t) \times i_1(t) dt. \qquad (3.16)$$

By substituting  $v_{ac}(t)$  with (3.3) and  $i_1(t)$  with (3.6),  $E_{stored1}$  is derived as

$$E_{\text{stored1}} = \int_{t_1}^{t_2} (V_{\text{m_min}} \sin wt) \times \frac{D^2}{2L_1 f_{\text{sw}}} (V_{\text{m_min}} \sin wt - V_{\text{sto\_AVG1}}) dt$$

$$= \frac{D^2 V_{\text{m_min}}^2}{2L_1 f_{\text{sw}}} \int_{t_1}^{t_2} \sin wt \times (\sin wt - \frac{V_{\text{sto\_AVG1}}}{V_{\text{m_min}}}) dt$$

(3.17)