## 저작자표시-비영리-변경금지 2.0 대한민국

## 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

## 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

## Ph.D. DISSERTATION

# PERFORMANCE ENHANCING TECHNIQUE FOR THE SUCCESSIVE APPROXIMATION ANALOG-TO-DIGITAL CONVERTER

축차 비교형 아날로그-디지털 변환기의 성능 향상을 위한 기법에 대한 연구

BY

HYONGMIN LEE

AUGUST 2016

DEPARTMENT OF ELECTRICAL ENGINEERING AND

COMPUTER SCIENCE

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

## PERFORMANCE ENHANCING TECHNIQUE FOR THE SUCCESSIVE APPROXIMATION ANALOG-TO-DIGITAL CONVERTER

축차 비교형 아날로그-디지털 변환기의 성능 향상을 위한 기법에 대한 연구

지도교수 김 수 환 이 논문을 공학박사 학위논문으로 제출함 2016 년 8 월

> 서울대학교 대학원 전기컴퓨터 공학부 이 형 민

이형민의 공학박사 학위논문을 인준함 2016 년 8 월

| 위 원 | · 장 : | <br>(印) |

|-----|-------|---------|

| 부위  | 원장 :  | <br>(印) |

| 위   | 원 :   | <br>(印) |

| 위   | 원 :   | <br>(印) |

| 위   | 원 :   | (印)     |

## **ABSTRACT**

# PERFORMANCE ENHANCING TECHNIQUE FOR THE SUCCESSIVE APPROXIMATION ANALOG-TO-DIGITAL CONVERTER

HYONGMIN LEE

DEPARTMENT OF ELECTRICAL ENGINEERING AND

COMPUTER SCIENCE

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

This thesis is written about a performance enhancement technique for the successive-approximation-register analog-to-digital converter (SAR ADC). More specifically, it focuses on improving the resolution of the SAR ADC. The basic operation principles and the architecture of the conventional SAR ADC is examined. To gain insight on areas of improvement, a deeper look is taken at the building components of the SAR ADC. Design considerations of these components are discussed, along with the performance limiting factors in the resolution and bandwidth domains. Prior works which challenge these problems in order to improve the performance of the SAR ADC are presented. To design SAR ADCs, a high-level modeling is presented. This model includes various non-ideal effects that occur in the

design and operation. Simulation examples are shown how the model is efficient and

useful in the initial top-level designing of the SAR ADC. Then, the thesis proposes a

technique that can enhance the resolution. The SAR ADC using integer-based capacitor

digital-to-analog converter (CDAC) exploiting redundancy is presented. This technique

improves the mismatch problem that arises with the widely used split-capacitor

structure in the CDAC of the SAR ADC. Unlike prior works, there is no additional

overhead of additional calibration circuits or reference voltages. A prototype SAR ADC

which uses the integer-based CDAC exploiting redundancy is designed for automotive

applications. Measurement results show a resolution level of 12 bits even without any

form of calibration. Finally, the conclusion about the operation and effectiveness on the

proposed technique is drawn.

Keywords: successive-approximation-register(SAR) ADC, integer-based split-

capacitor DAC, redundancy, automotive applications

**Student Number**: 2010-30228

ii

## **CONTENTS**

| CHAPTER 1 INTRODUCTION                                   |           |

|----------------------------------------------------------|-----------|

| 1.1 Motivation                                           | 1         |

| 1.2 Thesis Organization                                  | 5         |

| CHAPTER 2 CONVENTIONAL SUCCESSIVE-APPROXIMATION-REGISTER | R ANALOG- |

| TO-DIGITAL CONVERTERS                                    | 7         |

| 2.1 Introduction                                         | 7         |

| 2.2 OPERATION PRINCIPLE OF THE CONVENTIONAL SAR ADC      | 8         |

| 2.2.1. OVERVIEW OF THE OPERATION                         | 8         |

| 2.2.2. SAMPLING PHASE                                    | 10        |

| 2.2.3. CONVERSION PHASE                                  | 11        |

| 2.3 STRUCTURE OF THE CONVENTIONAL SAR ADC                | 15        |

| 2.3.1. FULL STRUCTURE OF THE CONVENTIONAL SAR ADC        | 15        |

| 2.3.2. CAPACITOR DIGITAL-TO-ANALOG CONVERTER (CDAC)      | 17        |

| 2.3.3. COMPARATOR                                        | 21        |

| 2.3.4. CONTROL LOGIC                                     | 23        |

| 2.4 PERFORMANCE LIMITING FACTORS                         | 24        |

| 2.4.1. RESOLUTION LIMITING FACTORS                       | 24        |

| 2.4.2. OPERATION BANDWIDTH LIMITING FACTORS              | 28        |

| 2.5 Prior Work                                           | 30        |

| 2.5.1. Introduction                                      | 30        |

| 2.5.2. SPLIT-CAPACITOR STRUCTURE OF THE CDAC             | 31        |

| 2          | 2.5.3. REDUNDANCY AND CDAC WEIGHT DISTRIBUTION                                          | 33      |

|------------|-----------------------------------------------------------------------------------------|---------|

| 2          | 2.5.4. ASYNCHRONOUS CONTROL LOGIC                                                       | 36      |

| 2          | 2.5.5. CALIBRATION TECHNIQUES                                                           | 37      |

| 2          | 2.5.4. DOUBLE-SAMPLING TECHNIQUE FOR SAMPLING TIME REDUCTION                            | 38      |

|            | 2.5.6. Two-comparator Architecture for Comparator Decision T<br>Reduction               |         |

| 2          | 2.5.7. MAJORITY VOTING FOR RESOLUTION ENHANCEMENT                                       | 41      |

| Снарт      | ER 3 MODELING OF THE SAR ADC                                                            | 43      |

| 3.1        | Introduction                                                                            | 43      |

| 3.2        | WEIGHT DISTRIBUTION OF THE CAPACITOR DAC AND REDUNDANCY                                 | 44      |

| 3.3        | SPLIT-CAPACITOR ARRAY TECHNIQUE                                                         | 47      |

| 3.4        | PARASITIC EFFECTS OF THE CAPACITOR DAC                                                  | 48      |

| 3.5        | MISMATCH MODEL OF THE CAPACITOR DAC                                                     | 51      |

| 3.6        | SETTLING ERROR OF THE DAC                                                               | 53      |

| 3.7        | COMPARATOR DECISION ERROR                                                               | 58      |

| 3.8        | DIGITAL ERROR CORRECTION                                                                | 59      |

|            | ER 4 SAR ADC WITH INTEGER-BASED SPLIT-CDAC EXPLOITING DANCY FOR AUTOMOTIVE APPLICATIONS | 60      |

| 4.1        | Introduction                                                                            | 60      |

| 4.2        | MOTIVATION                                                                              | 61      |

| 4.3<br>THE | PRIOR WORK ON RESOLVING THE SPLIT-CAPACITOR CDAC MISMATCH SAR ADC                       |         |

| 4          | 4.3.1. CONVENTIONAL SPLIT-CAPACITOR CDAC FOR THE SAR ADC                                | 64      |

| 4          | 4.3.2. SPLITTING THE LAST STAGE OF THE LSB-SIDE OF THE CDAC                             | 66      |

| 4          | 4.3.3. CALIBRATION OF THE NON-INTEGER MULTIPLE BRIDGE CAPACITOR                         | 67      |

|            | 4.3.4. INTEGER-MULTIPLE BRIDGE CAPACITOR WITH LSB-SIDE CAPACITOR                        | R<br>68 |

| Bibliography                                                                | 120 |

|-----------------------------------------------------------------------------|-----|

| APPENDIX                                                                    | 89  |

| 5.1 CONCLUSION                                                              |     |

| CHAPTER 5 CONCLUSION AND FUTURE WORK                                        |     |

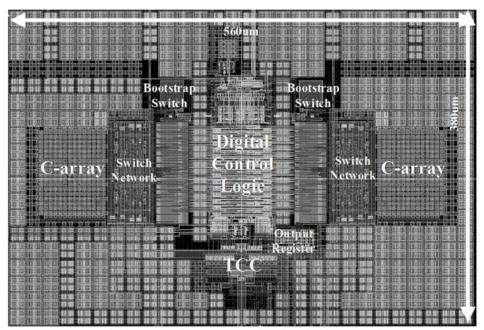

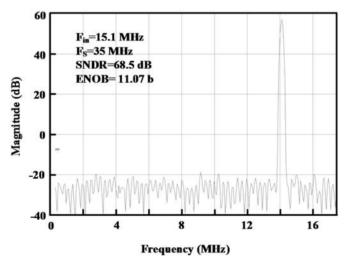

| 4.6.2. MEASUREMENT RESULTS AND CONCLUSIONS                                  | 82  |

| 4.6.1. LAYOUT                                                               |     |

| 4.6 IMPLEMENTATION AND EXPERIMENTAL RESULTS                                 |     |

| 4.5.3. CONTROL LOGIC                                                        | 75  |

| 4.5.2. Comparator                                                           | 74  |

| 4.5.1. Proposed Integer-based CDAC Exploiting Redundance ADC                |     |

| 4.5 CIRCUIT DESIGN                                                          | 72  |

| 4.4 Proposed Integer-based CDAC exploiting Redundancy for SAR ADC           |     |

| 4.3.5. OVERSIZED BRIDGE CAPACITOR WITH ADDITIONAL FRACTIO REFERENCE VOLTAGE |     |

|                                                                             |     |

## **LIST OF FIGURES**

| Fig. 1.1.1 Plot of ADC architecture versus the resolution and sampling rate [1.1.1] | .4 |

|-------------------------------------------------------------------------------------|----|

| Fig. 2.2.1 Sampling phase operation of the SAR ADC.                                 | 10 |

| Fig. 2.2.2 First conversion phase operation of the SAR ADC.                         | 12 |

| Fig. 2.2.3 Second conversion phase operation of the SAR ADC.                        | 14 |

| Fig. 2.2.4 Conversion phases waveform example for a 6-bit SAR ADC.                  | 15 |

| Fig. 2.3.1 Block diagram of the conventional SAR ADC including the CDAC, to         | he |

| comparator, and the control logic.                                                  | 16 |

| Fig. 2.3.2 Block diagram of the CDAC, including the capacitor array, the switch     | ch |

| network, and the top-plate switch.                                                  | 18 |

| Fig. 2.3.3 Schematic of the Strong Arm latch comparator.                            | 22 |

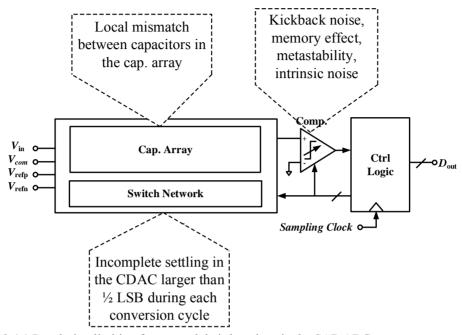

| Fig. 2.4.1 Resolution limiting factors and their locations in the SAR ADC           | 25 |

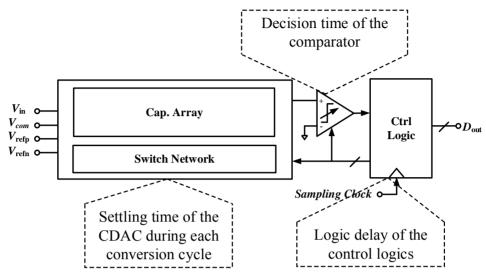

| Fig. 2.4.2 Operation bandwidth limiting factors and their locations in the SAR AD   | C. |

|                                                                                     | 29 |

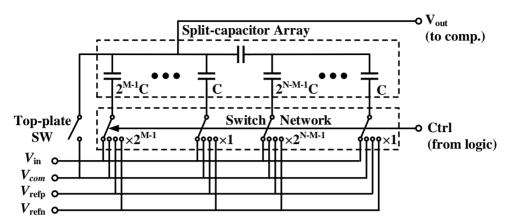

| Fig. 2.5.1 Split-capacitor structure CDAC schematic in the SAR ADC.                 | 32 |

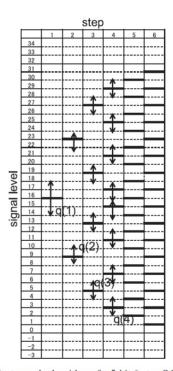

| Fig. 2.5.2 Graphical representation of comparison between binary-search algorith    | m  |

| and redundant search algorithm [2.5.1].                                             | 34 |

| Fig. 2.5.3 A self-timing DAC is used by generating the asynchronous DAC settling.   | ng |

| signal with the use of a dummy DAC [2.5.3].                                         | 37 |

| Fig. 2.5.4 Analog calibration of CDAC using trimming capacitors and memory [2.5.    | 4] |

|                                                                                     | 38 |

| Fig. 2.5.5 Double sampling schematic, with independent sampling capacitors from the | he |

| CDAC [2.5.6]                                                                              |

|-------------------------------------------------------------------------------------------|

| Fig. 2.5.6 Concept of the two-comparator architecture [2.3.4].                            |

| Fig. 2.5.7 Block diagram of the control of the majority voting technique [2.5.7]42        |

| Fig. 3.4.1 Parasitic capacitances of importance in the capacitor DAC of the SAR ADC       |

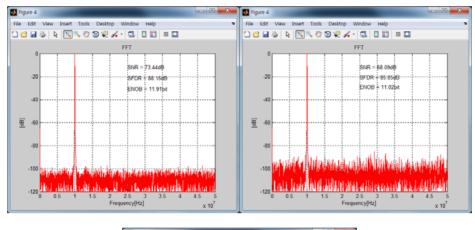

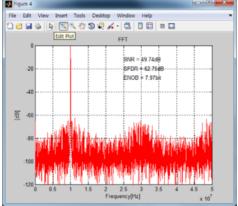

| Fig. 3.6.1 Simulation of the modeling of the 12-bit conventional SAR ADC with             |

| settling error ratios of 1, 0.99, and 0.95, respectively                                  |

| Fig. 3.6.2 Simulation of the modeling of the optimized 12-bit redundant SAR ADC           |

| with settling error ratios of 0.8, 0.75, and 0.7, respectively57                          |

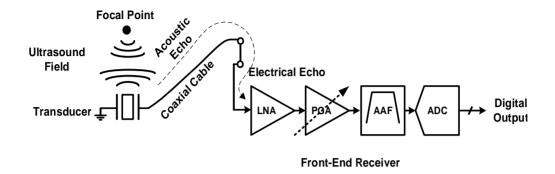

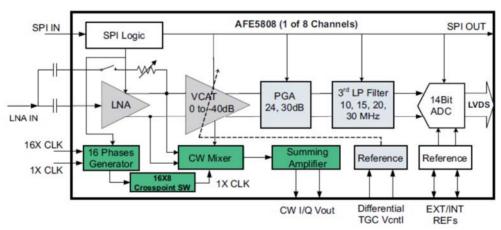

| Fig. 4.2.1 Typical commercial example of the SAR ADC for automotive applications [4.2.1]. |

| Fig. 4.3.1 Split-capacitor structure CDAC schematic in the SAR ADC65                      |

| Fig. 4.3.2 Schematic of the split-capacitor architecture with the bridge capacitor at the |

| last stage [4.3.1]66                                                                      |

| Fig. 4.3.3 Calibration of the weight mismatch of the bridge capacitor and the LSB-side    |

| capacitor to match the ratio with the MSB-side capacitors [4.3.2]67                       |

| Fig. 4.3.4 Intentional error at the bridge capacitor by using a unit capacitor, and       |

| compensating the ratio through LSB-side calibration [4.3.3]68                             |

| Fig. 4.3.5 The usage of an additional fractional reference voltage to compensate the      |

| ratio variation in using a large integer-multiple unit capacitor as the bridge            |

| capacitor [4.3.4]69                                                                       |

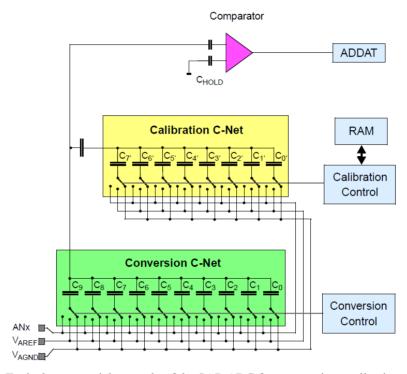

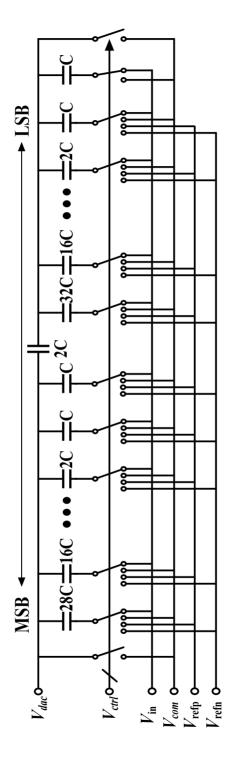

| Fig. 4.5.1 Schematic of the capacitor DAC of the proposed SAR ADC73                       |

| Fig. 4.5.2 Schematic of the double-tailed comparator                                      |

| Fig. 4.5.3 Block diagram of the control logic block, with the dynamic register bank in    |

| more detail at the bottom.                                                                |

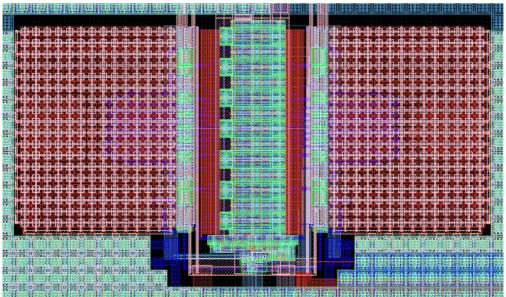

| Fig. 4.6.1 Layout of the SAR ADC utilizing integer-based split-CDAC using                 |

| redundancy. Active area is 550 μm x 300 μm78                                              |

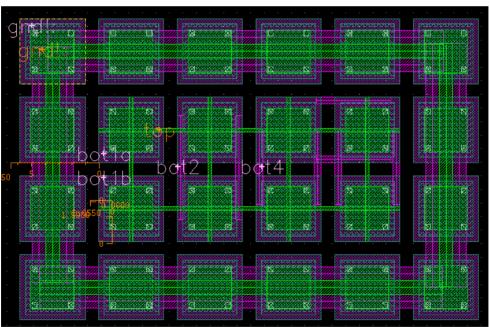

| Fig. 4.6.2 Experimental layout example for drawing the capacitor arrays with MIM          |

| capacitors. Dummy cap of C, C, 2C, and 4C stages drawn                        | 79  |

|-------------------------------------------------------------------------------|-----|

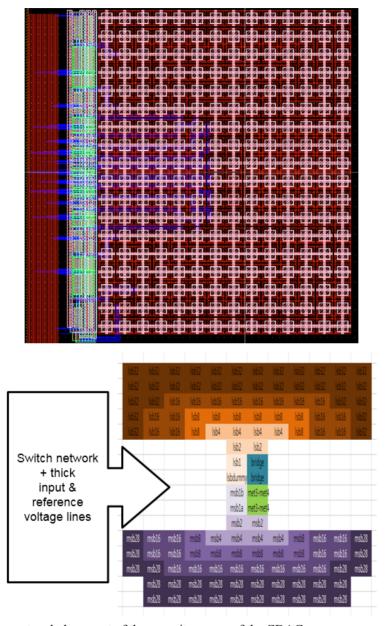

| Fig. 4.6.3 Layout and placement of the capacitor array of the CDAC.           | 81  |

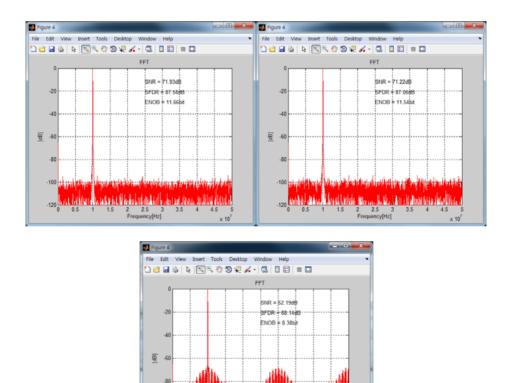

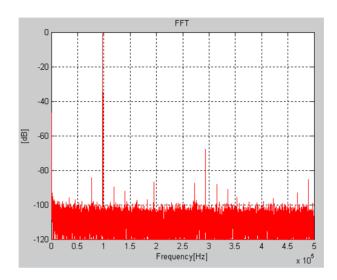

| Fig. 4.6.4 Measurement results of the proposed SAR ADC using integer-based sp | lit |

| CDAC with redundancy implemented in 0.5um CMOS process                        | .83 |

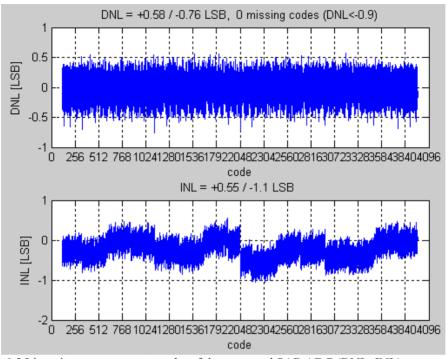

| Fig. 4.6.5 Linearity measurement results of the proposed SAR ADC (DNL, INL)   | 85  |

## CHAPTER 1

## **INTRODUCTION**

## 1.1 MOTIVATION

The successive-approximation-register analog-to-digital converter (SAR ADCs) is one of the hottest and arguably the most widely used ADC in the market today. It is well-known for its low-power characteristics and simple structure. The history of the SAR ADC goes back decades. The concept is very straight-forward; it is based on binary searching. The name "successive-approximation-register" therefore comes from the way the logic (registers) operates in a successive manner. However, until quite recently, the Nyquist ADC market have been dominated by other types of ADCs. Flash ADCs have been widely used for high-speed low resolution applications. The flash ADC is extremely fast due to a single stage of comparison for an analog-to-digital conversion. The sampled signal is compared to a series of reference voltages simultaneously by multiple comparators and the digital outputs are generated at the same time. The power consumption is inevitably high, but the flash ADC has its very

strong characteristic that stands out. Applications that require moderate-to-high resolutions typically have adopted the pipeline ADC. The pipeline ADC, has a nice balance between resolution and operation bandwidth. A sampled signal is compared to a reference voltage, and then the difference is multiplied, and the resulting voltage is sent to the consecutive stages. The pipeline ADC achieves moderate-to-high resolutions due to the multiple multiplying digital-to-analog converter (MDAC) stages which use operating amplifiers in the converting operation. Moreover, the operation bandwidth is relatively high in the region of tens of MHz up to the low hundreds due to the stages working in a 'pipeline' manner, hence the name. These serial stages that generate each digital bit progressively allow the throughput to be equal to the sampling frequency. This is a very powerful and effective advantage of the pipeline ADC. For example, the cyclic ADC works with the sample operating principles, but the difference is that there is only a single MDAC which is used repeatedly. Therefore, the throughput of the ADC is much slower - almost 1/N times for an N-bit resolution - as one sample must be iterated for N cycles. The downside of the pipeline ADC is the excessive power consumption of the MDAC stages, but nevertheless the pipeline ADC has dominated the market of Nyquist ADCs until recently.

The SAR ADC, although the history is quite long, has been left in the cold until recently. Although the SAR ADC has a very simple structure and straightforward operation principles, the major drawback is the resulting inherent operation bandwidth limit. As will be explained in detail in the following sections ahead, the SAR ADC

converts analog signals to digital codes by conducting a binary search. The generation of the digital bits are done at a single bit at a time. Unlike the pipeline ADC, however, the SAR ADC has no method of manipulating the value of the charge of the sampled signal, due to the lack of op-amps. Therefore the proceeding sampling sequence must wait until all the digital bits are generated, which results in an ADC operation bandwidth which is 1/N times lower than compared to the pipeline counterpart. This limitation in the operation speed has cut down the value of the SAR ADC until quite recently. The only non-trivial advantage that the SAR ADC held in the early days was that the power consumption in the analog domain was extremely low compared to other ADCs, and this was due to the absence of op-amps and numerous comparators. But the digital logics that comprise the SAR ADC was too costly and slow for practical usage.

The SAR ADC began to gain be reevaluated, however, as the technology continued to develop. In the analog circuit designer point of view, the technology development is in some aspects unwelcome. This is mainly due to the process scaling issue where the supply voltage continues to decrease yet the threshold voltage decrease of the transistor cannot keep up. A typical problem that arises is that with finer technology, it becomes harder and harder to reach gain levels that were met with larger scaled processes. This effects the development of the pipeline ADC, and the performance enhancement due to technology scaling was not as significant as that of digital circuits. On the contrary, the SAR ADC hardly suffers at all from these problems, since the analog circuitry required is mainly a comparator and capacitor arrays and

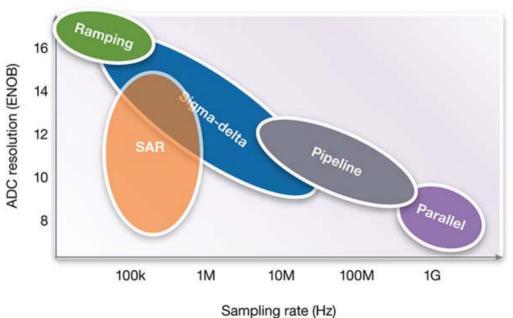

switches, and therefore quite friendly to technology scaling. Moreover, due to the speed-up of the digital logic, the successive binary-search algorithm could be now carried out more quickly, thus diminishing the operation bandwidth disadvantage. Nowadays, the SAR ADC is actively being used in applications that require moderate bandwidth and high resolution, which traditionally used pipeline ADCs. The low-power characteristics are becoming more important than ever as the supply voltages are continuously dropping. This can be explained by the plot of the ADC architecture versus the resolution and sampling rate shown in Fig. 1.1.1 [1.1.1]. The SAR ADC is currently or potentially replacing the mid-range performance domain that traditionally

Fig. 1.1.1 Plot of ADC architecture versus the resolution and sampling rate [1.1.1].

was dominated by the pipeline ADC. The SAR ADC can achieve resolutions over ten bits and more and sampling rates of a few tens of MHz.

This thesis focuses on the performance enhancement of SAR ADCs for further potential replacement of the pipeline ADC. Using a finer technology will obviously increase the performance without doubt, but the cost may be limited or other circumstances may allow only the use of less finer processes. Therefore, this thesis presents a technique that enhances the resolution of the ADC. The technique is named "SAR ADC using integer-based capacitor digital-to-analog converter (CDAC) exploiting redundancy", and focuses on reducing the mismatches in the CDAC of the SAR ADC in order to prevent resolution degradation. A prototype SAR ADC for automotive applications is designed and presented.

## 1.2 THESIS ORGANIZATION

The thesis is organized as follows. The introduction is in Chapter 1, where the motivation and the organization of the thesis is shown. In Chapter 2, the conventional SAR ADC will be covered. The contents include the characteristics and operation principle of the typical SAR ADC, and also the limitations and the critical design consideration points. To gain insight on how to enhance the performance, the trend prior works of the development of the SAR ADC will be discussed. Chapter 3 will show a MATLAB model of the SAR ADC which was actually used in the top-level

design stage. Weight distribution, redundancy, the structure of the CDAC and the non-idealities will be covered and their effects shown by simulation results. In Chapter 4, the technique in performance enhancement of the SAR ADC proposed by this thesis is presented. It is designed for automotive applications, so the background of the automotive solution will be described. Then, the "the integer-based capacitor digital-to-analog converter (CDAC) exploiting redundancy" will be illustrated in detail. The actual design of the SAR ADC will be demonstrated with simulation and measurement results. Finally, the conclusion and discussion of future work is given in Chapter 5.

## CHAPTER 2

## CONVENTIONAL SUCCESSIVE-APPROXIMATION-REGISTER ANALOG-TO-DIGITAL CONVERTERS

## 2.1 Introduction

In this chapter, the successive-approximation-register analog-to-digital converter (SAR ADC) will be described in a typical sense. Background information on the SAR ADC will be described in detail, including the operation principle and the basic structure so that a general knowledge on the concept of the SAR ADC will be delivered. Moreover, the building blocks that comprise the ADC will also be discussed in further detail. These include the capacitor digital-to-analog converter (CDAC), the comparator, and the digital control logic. Based on this information, the following sections will take a deeper look into the design considerations that must be carefully considered in the implementation of the SAR ADC for each block. The performance limiting factors will also be examined, as these problems are the motivations for improvement. These

examinations will be given in aspects of resolution and operation speed. The resolution degrading factors include the under-settling of the CDAC, mismatch and parasitic capacitance and other non-linearities in the CDAC, and comparator issues such as kickback noise, memory effects, and the intrinsic circuit noise. The operation speed limitations are broken down to respective causes; the settling of the CDAC, the comparator decision time, and the logic delay. Prior works which develop the conventional SAR ADC into higher-performing converters is studied in the final sections of the chapter. Widely-used techniques such as the split-capacitor DAC and implementation of redundancy will be discussed.

## 2.2 OPERATION PRINCIPLE OF THE CONVENTIONAL SAR ADC

#### 2.2.1. OVERVIEW OF THE OPERATION

The principle of the operation of the SAR ADC is based on the binary search algorithm. The closest digital representation of the analog signal value is determined by N binary search stages for an N-bit resolution ADC. The conversion can be divided into two phases; the sampling phase and the conversion phase. These two phases comprise the period of the conversion time, and therefore determine the sampling frequency of the ADC. In the sampling phase, the main objective is to store the analog input signal information into the sampling capacitor. Once the input signal information

is sampled with errors less than the intended resolution, the conversion phase begins. In the phase, the input signal information is compared with reference voltages in a binary search manner. For example, if the range of the input is from zero to one for simplicity, the input is first compared with 0.5. Then depending on the output, the input value is then compared with 0.25 if the previous comparison result was low, or 0.75 if the previous comparison result was high. The step of the change in the reference voltage is 0.25. In the next conversion stage, the reference voltage will change by 0.125 in the direction determined by the previous comparison result. This conversion stage is repeated and the digital representation of the input signal is the collection of the sequential comparison results.

Compared to the pipeline ADC, it is quite similar that the conversion process is processed one bit at a time in a binary manner. The difference is that while the pipeline ADC converts multiple samples at a single time, the SAR ADC converts only a sample at once. This is due to the fact that the SAR ADC cannot supply extra charge to the sampled charge. The voltage of the CDAC given by the sampled input is only manipulated through charge redistribution among the capacitors in the CDAC array. Therefore, for a sampled input, the whole conversion process must be finished before the next input can be sampled. This is unlike the pipeline ADC, where the transfer of charge is achieved by the use of amplifiers.

#### 2.2.2. SAMPLING PHASE

In the sampling phase, the input signal is sampled onto the sampling capacitor and the charge is stored. The input is sampled onto the sampling capacitor at the bottom-plate, whereas the top-plate is grounded to the common-mode voltage. A simple figure illustrates this procedure with simple block diagrams in the Fig. 2.2.1. Here, the sampling capacitor is the sum of all the capacitors of the CDAC. Therefore, the total size of the sampling capacitor  $C_s$  would be  $2^N$  C. The charge stored in the sampling capacitor can be given by the equation 2.2.1.

$$Q_S = C_S \times (V_{com} - V_{in}). \tag{2.2.1}$$

$Q_s$  is the charge sampled onto the sampling capacitor with respect to the top-plate of the sampling capacitor, namely the output of the CDAC.  $C_s$  is the capacitance of the

Fig. 2.2.1 Sampling phase operation of the SAR ADC.

sampling capacitor,  $V_{com}$  is the common-mode voltage, and the  $V_{in}$  is the sampled input voltage. This is the ideal case, and actually there will be some deviation from this ideal value due to the settling of the capacitor. The incomplete settling is caused by the finite resistance of the sampling switch, which generates an RC delay in accordance with the sampling capacitor. For the performance to match the full specified resolution, the error due to this incomplete settling must be smaller than half the least significant bit (LSB) size so that it is not larger than the quantization noise. Detailed discussion on the incomplete settling will be done in the following chapter. When the input is fully sampled onto the sampling capacitor, the DAC is now ready to redistribute the charge according to the comparator output. All switches are turned off, and the capacitor is left floating, which ideally would conserve the charge indefinitely.

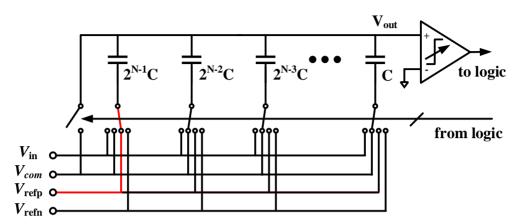

#### 2.2.3. CONVERSION PHASE

After the sampling phase has concluded, the conversion phase can now take place. Since the charge in the capacitors are now trapped, the total charge will remain unchanged for this sample due to the electrical charge conservation law. The idea now is to manipulate the voltage seen at the output of the CDAC by switching the reference voltages at the other side of the capacitors, namely the bottom-plates. Initially, the bottom-plates are all connected to  $V_{COM}$ , which is the common-mode voltage of the input range. Thus, the voltage at the output of the CDAC,  $V_{out}$ , is given by the following

equation:

$$V_{out} = V_{com} + \frac{Q_s}{C_s}. {(2.2.2)}$$

The charge  $Q_s$  in the sampling capacitors is defined by equation (2.2.1), and solving for these two equations gives the output voltage of the CDAC to be,

$$V_{out} = 2V_{com} - V_{in}. (2.2.3)$$

Therefore, the output of the DAC is a linear function of the sampled input voltage. The simplified block diagram of this step is shown in Fig. 2.2.2. The CDAC output voltage is then compared with  $V_{com}$ , and the comparator result is the first bit of the analog-to-digital conversion. For example, let's assume that the sampled input was a very small signal close to zero. Then, the output voltage of the CDAC according to equation (2.2.3) would be close to  $2*V_{Com}$ , and comparing this with  $V_{com}$  would result in a positive

Fig. 2.2.2 First conversion phase operation of the SAR ADC.

output. Due to the bottom-plate sampling, the signal of the sampled input  $V_{in}$  is negative, and therefore a positive output is the same as '0' for the most significant bit (MSB).

Next, the bottom-plate of the largest capacitor in the CDAC is switched from  $V_{\text{COM}}$  to either the top reference voltage of the bottom reference voltage. The capacitors comprising the CDAC and therefore the sampling capacitor are weighted in a binary manner in the conventional SAR ADC, and therefore the capacitance value of the largest capacitor is half of  $C_s$ . This procedure results in the output voltage of the CDAC as given in the following equation:

$$V_{out} = \frac{1}{2} (V_{com} - V_{refp}) + \frac{Q_s}{C_s}, \text{ (when MSB = 0)}$$

$$V_{out} = \frac{1}{2} (V_{com} - V_{refn}) + \frac{Q_s}{C_s}, \text{ (when MSB = 1)}$$

(2.2.3)

$V_{refp}$  and  $V_{refn}$  are respectively the top and bottom values of the reference voltage. The block diagram of this is illustrated in Fig. 2.2.3, with the input signal the same as the previous example. This output voltage is again compared with the common-mode voltage, and it can be easily seen that again, the comparator output will result in a positive output, which means '0' for the  $2^{nd}$  MSB as well.

Once a capacitor stage of the CDAC is switched to a reference voltage, it is held until the whole conversion is over. The following stage now switches the bottom-plate of the  $2^{nd}$  capacitor to either  $V_{refp}$  or  $V_{refn}$ , according to the comparator output of the previous cycle. This process is carried out until all the bits are generated, and thus the

Fig. 2.2.3 Second conversion phase operation of the SAR ADC.

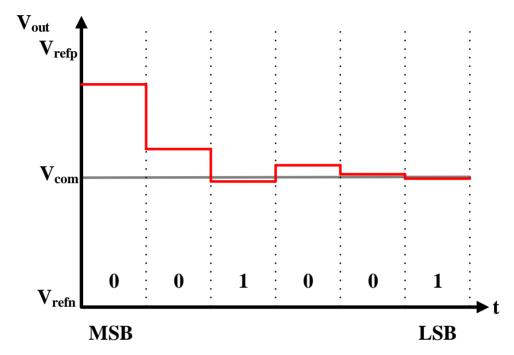

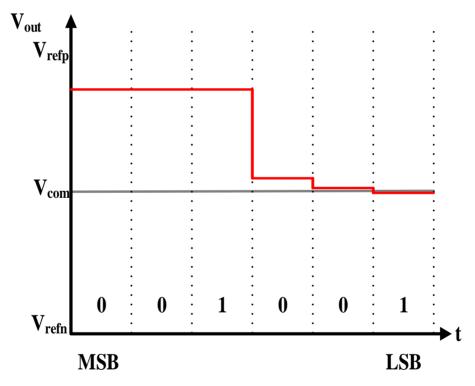

conversion of a single input sample is complete. A 6-bit example waveform with an input close to zero as explained above is shown in Fig. 2.2.4. It can be seen that as the conversion phases proceed, the DAC output voltage  $V_{\text{out}}$  seems to converge to  $V_{\text{com}}$ . This is exactly the case, since the input has been bottom-plate sampled onto the CDAC.

Fig. 2.2.4 Conversion phases waveform example for a 6-bit SAR ADC.

## 2.3 STRUCTURE OF THE CONVENTIONAL SAR ADC

## 2.3.1. FULL STRUCTURE OF THE CONVENTIONAL SAR ADC

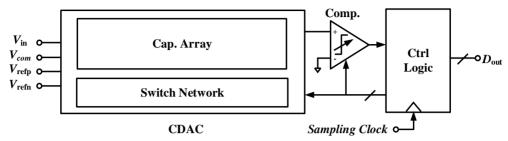

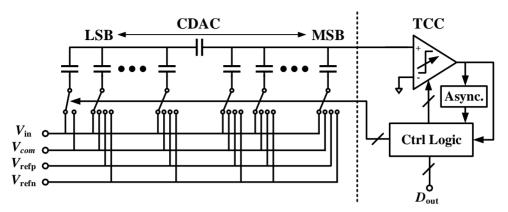

One of the main advantages of the conventional SAR ADC is the simple architecture. It can be divided into three main blocks; the CDAC, the comparator, and the control logic. A block diagram of the full structure is shown in Fig. 2.3.1. The

Fig. 2.3.1 Block diagram of the conventional SAR ADC including the CDAC, the comparator, and the control logic..

CDAC is the heart of the analog process in the analog-to-digital conversion. The trackand-hold circuit which is commonly used in ADCs is merged with the CDAC because

both are capacitive in nature. Sampling the input and the manipulation of the output

voltage for binary-searching is carried out in this block. The sampling capacitor and the

CDAC is typically merged into one structure for a more compact and simple

architecture. The analog output is connected to the input of the comparator.

The main function of the comparator is to decide whether the output of the CDAC is larger or smaller than the reference voltage in the binary search algorithm, and send this information to the logic. The comparator can be seen as the transition block between the analog domain of the CDAC and the digital domain of the control logic block. The output of the comparator is sent to the control logic.

The control logic serves three main purposes. First, it provides the clocking signals that are fed to the CDAC and the comparator for the interactive operation of the sampling and conversion cycles. It should be noted that the internal clocking signals

are over N times faster than the sampling frequency of the ADC for an N-bit resolution, and therefore the internal clocking should be considered as a high-speed digital circuit. The second function of the control logic block is the generation of the negative feedback control signals to the CDAC for the binary search operation. Based on the comparator decision for the current conversion cycle, the control logic generates the control signals for the next cycle that manipulates the switches in the CDAC to connect the relevant reference voltages for the binary search operation. The final function is the digital error correction, which refers to the generation of the final digital output bits of the ADC.

## 2.3.2. CAPACITOR DIGITAL-TO-ANALOG CONVERTER (CDAC)

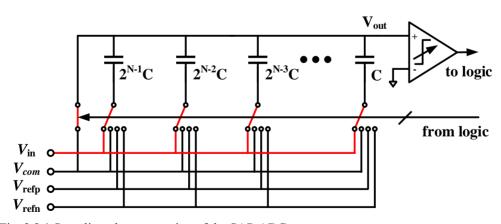

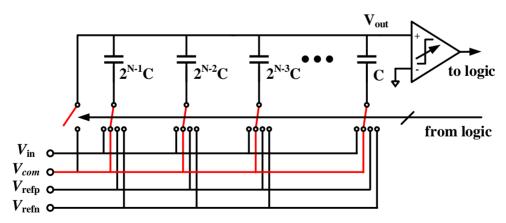

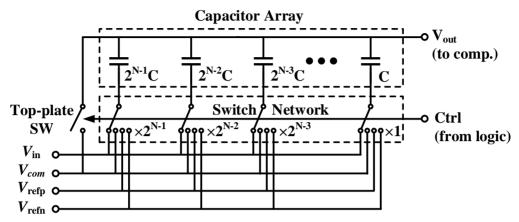

The capacitor digital-to-analog converter (CDAC) is the key block in defining the specifications of the SAR ADC. Depending on the design, the performance is decided. Fig. 2.3.2 shows the schematic of the conventional CDAC. It is typically designed in a symmetrical differential structure, but for simplicity the schematic shows the single-ended version. The CDAC is comprised of the capacitor array and the switch network. No static current is drawn in the CDAC.

The capacitor array is comprised of binary-weighted capacitors with the top-plates connected together as the output node. The bottom-plates of the capacitors are connected to the respective switches in the switch network. Bottom-plate sampling is

Fig. 2.3.2 Block diagram of the CDAC, including the capacitor array, the switch network, and the top-plate switch.

commonly used in high-resolution ADCs because it is very robust to parasitic capacitance in the CDAC. Also, charge injection that occurs when sampling the input does not affect the sampled value if the switching clocks are operated properly. The size of the capacitors affect the resolution and the power consumption of the SAR ADC. First of all, the capacitors of the CDAC also act as the sampling capacitor of the ADC, and therefore the total sum of the capacitors is bound by the kT/C noise limit. However, for high-resolution SAR ADCs, the binary-weighted capacitor array imposes a much higher lower-limit to the size of the capacitors. For example, a 12-bit resolution SAR ADC would need a total unit capacitor number of 4096. If the unit capacitor size is 10 fF, which is quite small even considering recent technologies, the total capacitance would be 40 pF, which would be quite too large for practical cases, while the kT/C

noise limit of the sampling capacitor is under 1 pF. However, if the unit capacitor value is too small, then there will be mismatch problems. For example, if the sampling capacitance is 1 pF for a 12-bit resolution SAR ADC, then the unit capacitor size would now be about 250 aF, which will have serious mismatch issues. It is known that the physical dimensions of a capacitor are inversely proportional to mismatch. The standard deviation of the mismatch that occurs in a capacitor can be shown as the following equation,

$$\sigma(\frac{\Delta C}{C}) = \frac{A_C}{\sqrt{WL}},\tag{2.3.1}$$

where C is the capacitance value,  $A_c$  is the process-dependent Pelgrom coefficient, and W and L are the physical dimensions of the capacitor. From this equation, it can be seen that the capacitor size must be increased for higher resolution, and therefore there is a tradeoff between both the settling time and the power consumption of the CDAC versus the resolution. Techniques that alleviate this trade-off will be explored in the following section in this chapter.

The switch network is the connection between the capacitor array and the input signals or reference voltages. As can be seen from the block diagram of the CDAC above in Fig. 2.3.2, there are three reference voltages in the block diagram: a high reference  $V_{\text{refp}}$ , a low reference  $V_{\text{refn}}$ , and the common voltage  $V_{\text{com}}$ . This structure is commonly called the  $V_{\text{cm}}$ -based switching, and offers such advantages as low-power characteristics and symmetrically distributed redundancy centering the decision level,

for the cost of an extra reference voltage [2.3.1]. There are four switches at the bottomplate of per capacitor stage in the CDAC; the input sampling switch and switches that connect to the three reference voltages. Bootstrapped switches are commonly used for the input signal sampling switches for high-performance ADCs [2.3.2]. This not only allows a relatively constant on-resistance of the sampling switch for different voltage levels of the input signal, it also allows to design the switches smaller, instead of CMOS switches with large dimensions. The physical size of the switches are of importance because for a capacitor stage, because not only are there four switches per capacitor, the switch sizes must be linear with the capacitor size in order for the fast settling of the CDAC [2.3.3]. The switch sizes are drawn next to the switches in the Fig. 2.3.2. This becomes a non-trivial issue as the binary-weight of the CDAC exponentially increases the capacitor sizes to very high values, especially in high-resolution SAR ADCs. For example, even if a minimum-sized transistor was used as the switch for the unit capacitor for the LSB, the MSB capacitor would be 2048 times larger, and therefore the resistance of the switch would have to be 2048 times smaller to keep the time constant the same value. This in turn means that the transistor switch width would have to be 2048 times longer, resulting in painful layout problems regarding mismatch and area.

The single switch at the common top-plate node of the capacitor array is connected to the common-mode voltage  $V_{com}$ , and is turned on when the input signal is being sampled on the bottom-plates. It is turned off after the sampling phase so that the top-

plate node of the capacitor array is left floating for the rest of the conversion phase so that the charge is conserved. A non-overlapping clock must work between the sampling switch signals and the top-plate switch so that there is no loss of charge. The size of this top-plate switch must also be carefully designed so that the inputs up to the Nyquist rate can be sampled adequately without any settling errors due to large RC time constant of the top-plate switch.

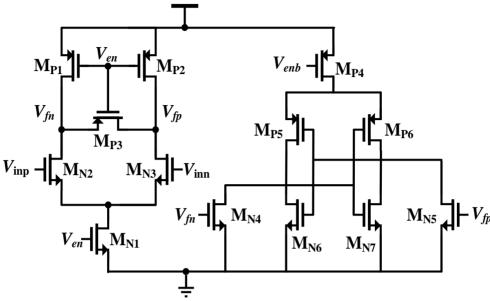

## 2.3.3. COMPARATOR

The comparator is the bridge between the analog domain and the digital domain in the ADC. It is fed the analog voltages of the differential outputs of the DAC at the inputs, and then generates a digital output which is sent to the logic control block to be processed. The structure of the comparator varies, and since the operation is relatively straightforward and simple, any type of comparator would function.

The types of comparators may be classified into two categories; comparators that have a pre-amplifier and those that do not. The former is mainly used for high resolution ADCs. The use of a preamplifier allows the reduction of input-referred noise in the comparison process [2.3.1][2.3.4], including the kick-back noise. However, the bandwidth maybe limited by the amplifier, and there will always be static power consumption. This may degrade the low-power consuming quality of the SAR ADC. The latter type of comparator, which does not use a pre-amplifier, is mostly used for

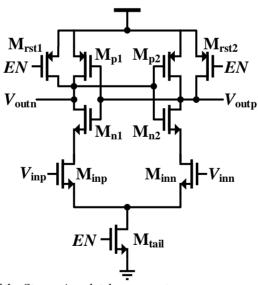

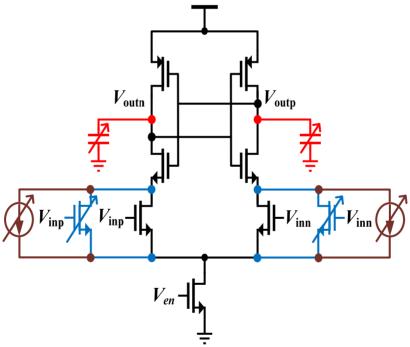

low power consumption and high-speed ADCs. A dynamic latch-type architecture such as the Strong Arm latch is widely used due to its simplicity, zero static power consumption, fast operation speed etc. However, it may be prone to error in noisy environments. Fig. 2.3.3 shows the basic latch-type comparator which is widely used in SAR ADCs. The input transistors are  $M_{inp}$  and  $M_{inn}$ , and the latchs are formed by transistors  $M_{n1-2}$  and  $M_{p1-2}$ .  $M_{rst1-2}$  are for resetting the internal nodes while the comparator is not operating, and  $M_{tail}$  is the tail current source.

For faster operation, there have been improvements on the basic dynamic-latch structure to include an extra tail current source, so that the input transistor pair and the latches operate with independent biases [2.3.5]. This allows the latch input transistor

Fig. 2.3.3 Schematic of the Strong Arm latch comparator.

pair to continuously operate in the saturation region, thus allowing faster comparison.

This does not affect the power consumption due to the fact that it still works as a dynamic latch; only a little area overhead has been included for the speed improvement.

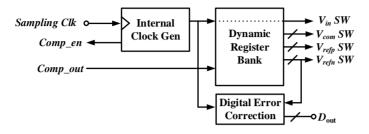

#### 2.3.4. CONTROL LOGIC

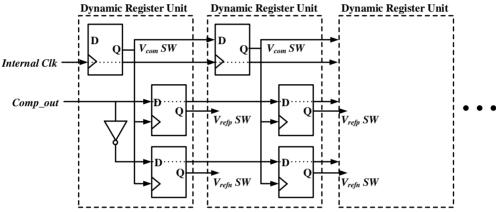

The control logic block is essentially the algorithm that performs the binary-search by manipulating the switch network in the CDAC. The control logic consists of three main blocks; the internal clock signal generator, the dynamic register bank, and the digital error correction block. The internal clock phase signal generator is the block where the phase control signals for the sampling and the conversion cycles take place. The block receives an external sampling clock, and divides it into multiple phases that are at least (N+1) times faster for an N-bit resolution ADC. These multi-phases are used for the sampling phase and the N conversion cycles, so internally the digital logic operates at a bandwidth that is an order higher than the sampling bandwidth.

The dynamic register bank is the block where the controls for the binary-search in the CDAC are generated. The dynamic registers are connected in a sequential method. It is thanks to this successive register architecture that the SAR ADC got its name. Although the same function could be written and synthesized using HDL, this simple yet powerful architecture allows seamless operation with minimal logic delay. It should be noted that this dynamic register bank is specifically for controlling the  $V_{cm}$ -based

CDAC architecture, and has an extra row of registers than the most basic successive approximation register. A more detailed explanation will be included in the following chapters in the proposed SAR ADCs.

## 2.4 Performance Limiting Factors

In this section, some major issues that degrade the performance of the SAR ADC will be illustrated. Unfortunately for the designer, simple as it is, the SAR ADC will not always perform in the ideal way as described in the previous section. Non-idealities as well as practical issues will cause undesired or unexpected effects that must be considered if the ADC is to perform as its intended specifications. The performance of the SAR ADC will be examined by the two dominant specifications; operation bandwidth and resolution.

#### 2.4.1. RESOLUTION LIMITING FACTORS

Resolution can be limited in the SAR ADC for various reasons. The resolution problem is limited to the analog domain, which includes the CDAC and the comparator. Fig. 2.4.1 shows the most critical limitation locations and the reasons in the block diagram of an SAR ADC. The most obvious problem in the resolution degradation is the settling error of the CDAC. As explained previously, the capacitor of the CDAC

Fig. 2.4.1 Resolution limiting factors and their locations in the SAR ADC.

and the corresponding switch network inevitably forms an RC time constant, and any voltage change will take time to settle to the tolerated error range. This applies to both the sampling phase and the conversion phase of the CDAC operation. At the sampling phase, a sufficient sampling period must be allocated for the input signal to be adequately tracked and sampled. The error from the ideal input and the sampled input must be smaller than the quantization noise ADC, or there will be degradation in the resolution. This is a general statement that applies to all types of ADCs. For the conversion phase, the matter is specifically for the SAR ADC. As mentioned previously, the RC time constant of each capacitor and its corresponding switch network has been

designed the same, so that ideally there will be no delay in the voltage change at the common top-plate which is the CDAC output [2.3.3]. However, the capacitance and resistance are subject to mismatch and parasitics, and therefore sufficient settling time must be allocated to each cycle of the conversion phase. The voltage error due to incomplete settling of the CDAC must be less than 1/2 LSB in order for the domination of the quantization noise.

The mismatch in the capacitance values of the capacitors in the CDAC also cause resolution degradation. Capacitor mismatch inevitably occurs in the implementation process, and depends heavily on the used technology. The local mismatch however can be determined by the model, which was explained in previous section. If the physical dimensions of the capacitors are too small, then the mismatch will be too large and this mismatch will cause resolution degradation. Moreover, other than the intrinsic mismatch between unit capacitors, the mismatch due to the parasitic capacitance is also a degradation factor. Even with symmetrical and systematic layout, connecting metals will generate parasitic capacitance which will contribute to the overall capacitance of each capacitor stage. If this capacitance gain is too large, then the binary weighting between capacitors will ultimately be non-linear, which will undoubtedly cause errors in the binary-search process.

The comparator also may affect the performance of the ADC in terms of resolution. First of all, the kickback noise may deter the voltages of the DAC. No charge is transferred, so in the long term no error is accumulated. However, the kickback is

generated when the comparator is turned on and the voltages of the internal nodes of the operating comparator alter the CDAC by the parasitic capacitance of the input transistors. This voltage change takes place at both nodes with approximately the same amount, so it is a trivial situation for most cases. However, for high resolution SAR ADCs, just a subtle amount of voltage change may cause the initial CDAC voltages for comparison to switch polarity, causing a comparison error that may not be restored in binary-search algorithms. Second, the memory effect can also cause errors in the comparator decision, causing the resolution of the ADC to suffer. Memory effects are caused by incomplete reset of the internal nodes of the comparator. The comparator must always start its comparison with all the internal nodal pairs at the same voltage level. Internal reset switches which connect the nodes of interest to either supply or ground must therefore be able to charge or discharge enough current in the given reset time. Switches that connect the internal nodal pairs to each other may also alleviate the memory effect. However, this in turn will again add additional loads to the internal nodes and therefore slow up the comparison process and cause additional power consumption. The metastability issue is also a potential cause of comparison error. In the conventional SAR ADC, time is allocated for the comparator to generate a valid output before the dynamic registers use this information to control the CDAC. The comparator must be able to generate the correct output in the allocated time for inputs with differences up to 1/2 LSB. However, the problem is that it is with uniform probability in which cycle the inputs will be the closest together. Therefore, the

comparison time allocation must take account this worst case for all the cycles. Lastly, the internal noise of the comparator itself may cause errors in the decision-making. As explained earlier, the actual operation bandwidth of the comparator is at least an order faster than the sampling bandwidth of the whole SAR ADC. Therefore, the comparator must be able to make the correct decisions even with high frequency noises. One simple way of reducing the noise would be to add capacitance at the internal nodes; however this would again slow down the operation of the comparator and increase the power consumption.

### 2.4.2. OPERATION BANDWIDTH LIMITING FACTORS

To examine the operation bandwidth limiting factors in the operation of the SAR ADC, a breakdown of the SAR ADC operation in speed aspects is done. The sampling and conversion must be done inside the given sampling bandwidth with some margin, and therefore time phases must be carefully allocated. These can be categorized according to its components: the settling time of the CDAC, the decision time of the comparator, and the logic delay of the control logics. Figure 2.4.2 shows the block diagram of the conventional SAR ADC with the location of the operation bandwidth limiting factors highlighted.

The settling time of the CDAC varies from cycle to cycle, and it is a function of the capacitor size of the cycle of interest. As explained in the previous sections on the

Fig. 2.4.2 Operation bandwidth limiting factors and their locations in the SAR ADC.

principle of the operation of the SAR ADC, the CDAC changes voltages in an attempt to binary-search the sampled voltage. These changes in the output voltage of the CDAC are proportional to the capacitor size; this means that the first cycle will have to change the voltage of a half of the input range, the second cycle change would be a quarter of the input range, and so on. Therefore it is safe to assume the earlier the cycle is in the conversion process, the longer the settling will be. Enough time must be allocated so that the DAC voltage can settle sufficiently to within half LSB, or it would results in a conversion error. If the total capacitor size is minimized and reduced to the limit bound by kT/C noise, settling time of the capacitor DAC would also be minimized. However, designing is not this simple, as minimal capacitor sizing results in critical mismatch,

which was explained using the Pelgrom coefficient.

The comparator decision time is another part of the time allocated in the conversion process. It is largely dependent on the comparator structure, and typically a dynamic latch type is used for fast operation. Generally, if more power is consumed in the comparator design, the faster the decision time will be. Comparator decision time may take extremely long in the case of inputs which are very close together, and in this case it is said that the comparator has fallen into a metastable state. However, it must be designed that if the comparator were to fall into the metastable state, the inputs difference would have been smaller than 1/2 LSB so that whatever the comparator decision is will not result in an error. The logic delay is mainly technology dependent, and as explained in the introduction, the development of faster logic due to finer process was the key in the current day research on SAR ADCs. However, the logic critical path must be kept as simple as possible, and the successive dynamic register structure is currently the best solution in the fast operation of the control logic.

### 2.5 PRIOR WORK

### 2.5.1. Introduction

There have been very many trends of development in the research for development of the SAR ADC. The main interest of research on the performance of the SAR ADC can be divided into the following; further lowering the power consumption for ultimate

figures of merit, enhancing the speed of operation which is a clear disadvantage of the SAR ADC, and enhancing the resolution of the SAR ADC without trade-offs with its other advantages. This thesis will focus on the latter two aspects; the speed enhancement and resolution enhancement. Prior works cannot all be classified into a single aspect, and therefore some very revolutionary works will be introduced as well as more recent works of interest.

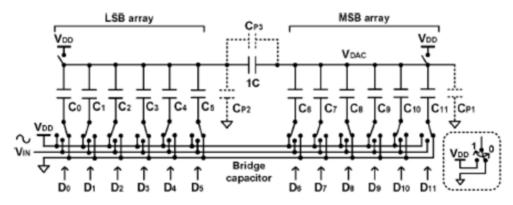

### 2.5.2. SPLIT-CAPACITOR STRUCTURE OF THE CDAC

The split-capacitor structure is a technique that is used in the capacitor array of the CDAC in order to reduce the total required number of unit capacitors. The capacitors in a conventional SAR ADC must be weighted in a binary manner for the binary-search algorithm to be processed. However, this would mean that the capacitors will become exponentially large for higher resolution SAR ADCs. For example, a conventional 12-bit SAR ADC would need a total capacitance of 4096 unit capacitors, which will be impractical to implement. Therefore, without a method for reducing the physical capacitance, the SAR ADC can only be used for low-resolution applications.

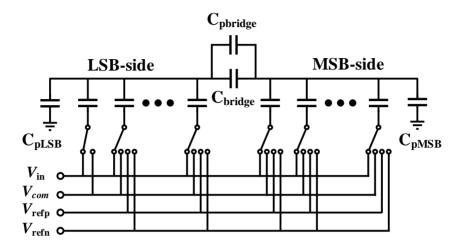

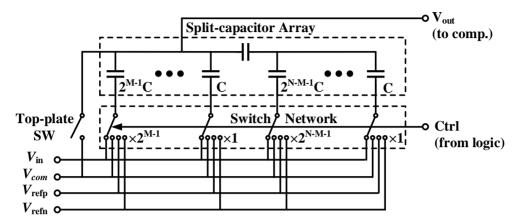

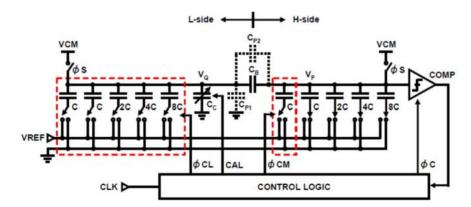

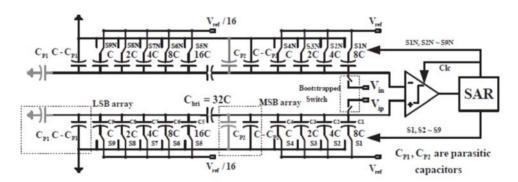

It is possible to maintain the binary ratio between the capacitance stages while reducing the total capacitance by inserting a capacitor in series with the top-plates of the capacitor array. Fig. 2.5.1 shows the bridge capacitor and the resulting split-capacitor CDAC. This inserted capacitor is called the bridge capacitor, and controls the

Fig. 2.5.1 Split-capacitor structure CDAC schematic in the SAR ADC.

effective capacitance seen by the lower split-capacitor array. This simple but efficient technique can reduce the total capacitance in an exponential manner. For example, in the same 12-bit SAR ADC the capacitor DAC resulted in a total input capacitance of 4096 unit capacitors. However, if a bridge capacitor with the appropriate sizing were to be inserted between the 6<sup>th</sup> stage and the 7<sup>th</sup> stage, the total input capacitance is now reduced to just 64 unit capacitors. Given that the unit capacitor is large enough so that the kT/C limit is met, a smaller input capacitance will increase the operation speed and lower the power consumption in the SAR ADC. Details on the values of the capacitor values and the effects of parasitics will be discussed in detail in the next chapter.

#### 2.5.3. REDUNDANCY AND CDAC WEIGHT DISTRIBUTION

Redundancy is a technique that has been used in numerous circuits, including the pipeline ADC in Nyquist ADCs[2.3.3][2.5.1]. In the SAR ADC, redundancy can also be used so that small dynamic errors in the binary-search algorithm may be corrected. It is an effective method of enhancing both the resolution and the operation speed of the SAR ADC. Redundancy can be implemented in the SAR ADC by the redistributing the conventional binary weight of the capacitors in the CDAC[2.5.2].

In a binary-weighted capacitor DAC of a basic SAR ADC, the capacitance of a stage is equal to the sum of the total sum of the capacitances of the lower stages, and the operation is based on binary-search algorithm. However, in a sub-radix-2-weighted capacitor DAC, the capacitance of a stage is now less than the total capacitances of the lower stages; this introduces some redundant ranges near the border of the decision levels. This of course comes at the cost of additional stages, as the total sum of the weights of the capacitor DAC must be a power of 2. This sub-radix-2-weighted capacitor DAC is quite simple in principle; however the values of the capacitors are non-integer multiples of the unit capacitance due to the non-integer radix. Since unit capacitances cannot be used, layout problems will induce mismatch issues and degrade the linearity of the SAR ADC. Another way to exploit redundancy is by using integer-weighted capacitance values, but with the capacitance of a stage being equal or less than the sum of the total capacitance of the lower stages. Compared to the sub-radix-2-

weighted method, the redundancy per stage is now a non-fixed number; it can be controlled by the designing of the weights. Moreover, the capacitance values now can be chosen as integer-multiple values of the unit capacitor, allowing systematic and matched layout for good linearity. Fig. 2.5.2 shows a graphical comparison between the conventional binary-search algorithm and the redundant-search algorithm [2.5.1]. The example is a 5-bit ADC. <sup>1</sup>As can be seen the binary search takes 5 steps for the whole search, but any error will not be tolerated. In the redundant search however, the whole

Binary search algorithm of a 5-bit 5-step SAR ADC. Redundant search algorithm of a 5-bit 6-step SAR ADC Fig. 2.5.2 Graphical representation of comparison between binary-search algorithm and redundant search algorithm [2.5.1].

search will now take 6 steps. That is one more step, and the search range of each step is now the same or smaller than the binary search, but now error may be correctable in the following steps depending on the error size. This correctable error size is shown with the both-sided arrows in the graphical table on the right.

The effect of redundancy is positive in both the resolution and the operation bandwidth of the SAR ADC. Comparison errors that occur in the range of redundancy can be corrected in the following cycles, whereas in non-redundant radix-two SAR ADCs, comparison errors always result in the final output error. Another interesting fact is that the operation bandwidth can also be improved by the use of redundancy. The usage of redundancy can potentially correct errors due to dynamic causes, including the pre-settling of the CDAC. Without redundancy, the CDAC must settle within 1/2 LSB and therefore much time must be allocated for every cycle. However, the use of redundancy allows up to some pre-settling of the CDAC, given that the CDAC will eventually settle after the comparison. Therefore the time allocated does not have to ensure a settling error less than 1/2 LSB, and even though through redundancy there will be extra cycles needed, this can have a large improvement in the operation bandwidth if the CDAC settling was the bottleneck in the operation of the CDAC. A detailed explanation of the implementation and effects of exploiting redundancy in SAR ADCs will be shown with simulation results in the next chapter.

### 2.5.4. ASYNCHRONOUS CONTROL LOGIC

Asynchronous control logic is used in the SAR ADC control for higher operation speed. It is effective in the fact that the allocated time for waiting for the comparator to generate a valid decision can be spread out more efficiently. In the synchronous SAR ADC, the internal clock would activate the successive dynamic register bank in the control. The operation of the SAR ADC will have at one cycle where the CDAC voltage difference is closet to V<sub>COM</sub> at a value under 1 LSB. This cycle will cause the comparator the longest time to generate its output, since the input difference is so small. Unfortunately, it is impossible to know which cycle this would be, so the worst case time must be allocated for every cycle, or it will result in an error. With asynchronous timing however, this can be alleviated by making the internal clock signal for the successive dynamic register bank. This internal clock signal can be simply made by the XOR of the comparator differential output. It means that the comparator has generated a valid output, so that the dynamic registers can use this information to process and generate the control signals for the next cycle.

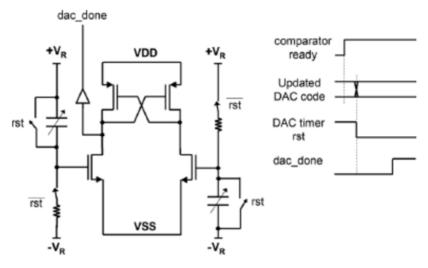

A more complex asynchronous clocking has also been introduced to efficiently allocate the timing for the settling of the DAC [2.5.3]. This work implements a self-timing DAC, which is actually a dummy DAC, and uses it to operate asynchronously to enhance the DAC settling time. The dummy DAC and the timing diagram is shown in Fig. 2.5.3.

Fig. 2.5.3 A self-timing DAC is used by generating the asynchronous DAC settling signal with the use of a dummy DAC [2.5.3].

### 2.5.5. CALIBRATION TECHNIQUES

Calibration techniques are extremely powerful, most works at resolutions of 12 bits have some kind of calibration at work. The resolution of the SAR ADC suffers from the limiting factors described previously, but the calibration techniques intend on compensating for the static limiting factors, such as the CDAC mismatch. CDAC weight calibration can be done in an analog manner, where trimming capacitors with steps much smaller than the unit capacitors are connected to the CDAC [2.5.4]. These trimming capacitors are tuned for each digital code and the tuning codes are saved in some kind of memory. In this way, the capacitor mismatch may be reduced. It requires

Fig. 2.5.4 Analog calibration of CDAC using trimming capacitors and memory [2.5.4].

excessive circuits including a fine tuning capacitor array and some kind of memory. Digital calibration is done by varying the weights of the capacitors in the digital error correction block from the ideally designed weights [2.5.5]. It requires a more complicated computing circuitry at the ADC output.

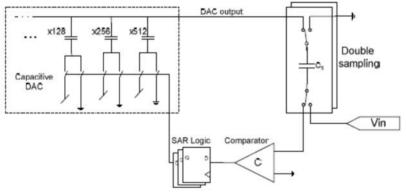

### 2.5.4. DOUBLE-SAMPLING TECHNIQUE FOR SAMPLING TIME REDUCTION

The SAR ADC suffers in the operation bandwidth in the sense that for a given sampling frequency, the actual sampling and conversion must all occur in this period. This is on the contrary to the pipeline ADC, where the sampling and conversion are all divided into stages that have the whole given sampling period to use. In the SAR ADC, a technique called double sampling is used to separate the input sampling period from

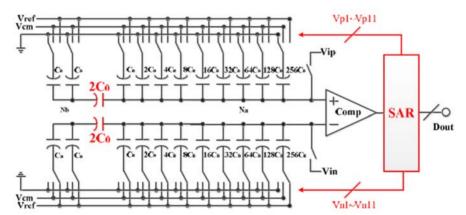

than the CDAC. Then, the charge in this sampling capacitor is connected to the CDAC so that charge redistribution can occur, while the next input sampling occurs simultaneously on another sampling capacitor. Although the sampling and conversion is now separated into different time phases which can occur simultaneously, this technique may suffer in the resolution that the effective charge may be reduced in the charge sharing between the sampling capacitor and the CDAC. The double sampling schematic is shown in Fig 2.5.5, where it can be seen that the sampling capacitors are independent from the CDAC.

Fig. 2.5.5 Double sampling schematic, with independent sampling capacitors from the CDAC [2.5.6].

# 2.5.6. Two-comparator Architecture for Comparator Decision Time Reduction

A two-comparator architecture can be used to enhance the comparator decision time, especially when an input very small may cause metastability in the comparator [2.3.4]. This can be used to speed up the comparison time of the SAR ADC, or it can be used to loosen the comparator design constraints for less power consumption. Two comparators with slightly different offsets are used together with the same inputs. When the input difference is large, then the comparators will both make the same decision quickly, and it can be used. When the input difference is small, then at least one of these comparators may fall into metastability, but since the offsets differ, both of them will not fall into metastability. Therefore, the comparator which produces the output first can be used. The scheme is shown in Fig. 2.5.6.

Fig. 2.5.6 Concept of the two-comparator architecture [2.3.4].

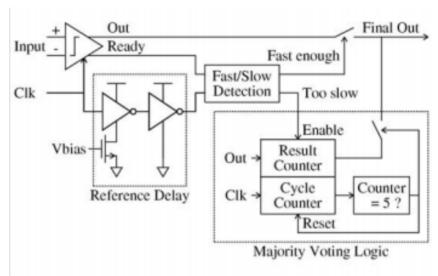

### 2.5.7. MAJORITY VOTING FOR RESOLUTION ENHANCEMENT

This work enhances the resolution an extra bit with the hardware capable of a limited resolution by making the final decision extra times [2.5.7]. The LSB decision is made 5 times, and in most cases due to noise and other uncertainties, the output will differ. A majority voting is done to decide the actual LSB. Experimental results show

that this actually increases the resolution for the sake of extra cycles for the majority voting and the additional logic.

Fig. 2.5.7 Block diagram of the control of the majority voting technique [2.5.7].

### CHAPTER 3

## MODELING OF THE SAR ADC

### 3.1 Introduction

This chapter presents the SAR ADC model used in the top-level designing of the ADC. In designing the SAR ADC, the modeling step should be taken as it offers numerous advantages. There are various aspects and characteristics with tradeoffs that must be considered when designing an SAR ADC that is appropriate for the chosen application. For example, redundancy may enhance the resolution by allowing a small amount of settling error in the earlier stages; however the extra stages may reduce the operation speed. The total capacitance of the capacitor DAC of the SAR ADC will enhance the resolution, but the settling time will be longer and therefore a tradeoff with the operation speed. Similar tradeoffs can be found with the use of the split-capacitor DAC technique and the placement of the bridge capacitor. This chapter will go through the choices in choosing the structure of the SAR ADC, and show the modeling of the SAR ADC in MATLAB which was used to see the effects of the different structures in

the performance of the ADC. The model presented in this chapter was used to decide the weights of capacitor DAC of the proposed SAR ADC, and even in the transistorlevel designing step, iterations were taken between the modeling and transistor-level schematic.

The model was exceptionally important that it can actually simulate the effect of the distributed redundancy against the reduced settling time before the transistor-level simulations, so that the CDAC weight-distribution could be designed without much painful iterations in the transistor-level. Moreover, it covers a variety of widely used structures; the conventional binary SAR ADC, the sub-radix-2 SAR ADC, the split-capacitor DAC ADC, and even the TCC-CDAC hybrid SAR ADC which will be proposed in Chapter 5.

# 3.2 WEIGHT DISTRIBUTION OF THE CAPACITOR DAC AND REDUNDANCY

Although the SAR ADC is known for its simple structure and low-power operation, the biggest limitation is its relatively low operation speed. Exploiting redundancy is an effective method of enhancing both the resolution and the operation speed of the SAR ADC. Redundancy is built into the structure of the SAR ADC by distribution of the total capacitance of the capacitor DAC into each stage. In a binary-weighted capacitor DAC of a basic SAR ADC, the capacitance of a stage is equal to the sum of the total

sum of the capacitances of the lower stages, and the operation is based on binary-search algorithm.

However, in a sub-radix-2-weighted capacitor DAC, the capacitance of a stage is now less than the total capacitances of the lower stages; this introduces some redundant ranges near the border of the decision levels. This of course comes at the cost of additional stages, as the total sum of the weights of the capacitor DAC must be a power of 2. This sub-radix-2-weighted capacitor DAC is quite simple in principle; however the values of the capacitors are non-integer multiples of the unit capacitance due to the non-integer radix. Since unit capacitances cannot be used, layout problems will induce mismatch issues and degrade the linearity of the SAR ADC. A better way to exploit redundancy is by using integer-weighted capacitance values, but with the capacitance of a stage being equal or less than the sum of the total capacitance of the lower stages. Compared to the sub-radix-2-weighted method, the redundancy per stage is now a nonfixed number; it can be controlled by the designing of the weights. Moreover, the capacitance values now can be chosen as integer-multiple values of the unit capacitor, allowing systematic and matched layout for good linearity. The operation of a weighted capacitor DAC of the SAR ADC is given as the equation below.

$$v_{dac}(i) = v_{dac}(i-1) + 2 \times (d(i-1) - 0.5) \times (W(i-1)/W_{total}) \times \frac{v_{ref}}{2},$$

(3.1.1)

where  $v_{dac}(i)$  is the output of the DAC, d(i) is the digital output of the  $i^{th}$  stage, and W(i) is the weight of the  $i^{th}$  stage. This is the most basic equation of the SAR ADC, and it

can be seen that the previous stage decision affects the current stage output voltage, which is then compared with the sampled input signal to generate the decision of this stage.

The modeling of the SAR ADC shows how changing the weight of the capacitor DAC distributes redundancy among the stages. The model calculates the redundancy that a stage is allocated so that a decision error with the error in the range of redundancy can be tolerated. By the redundancy calculations, designing the DAC becomes much more intuitive. The redundancy for each stage of a SAR ADC can be calculated as the following equation.

$$R(i) = R(i-1) + W(i-1) - 2 \times W(i), \qquad (3.1.2)$$

where R(i) is the redundancy of the i<sup>th</sup> stage. It can be seen that redundancy of a stage is not only affected by the weights of the current stage and the previous stage, but also by the redundancy of the previous stage. It can be intuitively thought as redundancy that is introduced in the previous stage can be kept or used up in the following stage. In designing the SAR ADC, with the use of equation (3.1.2), redundancy can be calculated for different weight distributions and number of stages. The effect of the distributed redundancy can be shown by simulation of the model with practical settling errors, which will be described in the following sections.

### 3.3 SPLIT-CAPACITOR ARRAY TECHNIQUE

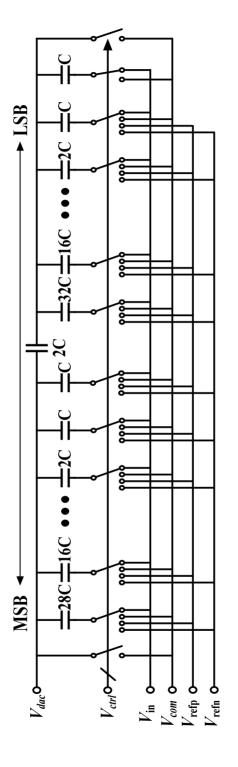

The split-capacitor array technique and the according weight distribution in the capacitor DAC is also included in the modeling of the SAR ADC [3.3.1]. The use of split-capacitor arrays in a capacitor DAC is a very effective way of reducing the overall capacitance while maintaining the ratio between the capacitance stages. This is especially useful for SAR ADCs, as total capacitance of the DAC is bound by the kT/C noise, but as the number of bits grows, the binary-weighted stages accumulate to an impractically large capacitance value. Inserting a bridge capacitor in between the common plates of the capacitors connected in parallel can reduce the total capacitance in an exponential manner. For example, in a 12-bit SAR ADC the capacitor DAC is commonly an 11-bit structure when using the V<sub>cm</sub>-based method. This results in a total input capacitance of 4096 unit capacitors. However, if a bridge capacitor with the appropriate sizing were to be inserted between the 6<sup>th</sup> stage and the 7<sup>th</sup> stage, the total input capacitance is now reduced to just 64 unit capacitors. Given that the unit capacitor is large enough so that the kT/C limit is met, a smaller input capacitance will increase the operation speed and lower the power consumption in the SAR ADC. The equation (3.1.1) is now modified accordingly as the following.

$$v_{dac}(i) = v_{dac}(i-1) + \frac{2 \times (d(i-1)-0.5) \times C_{MSB}(i-1) \times (1 + \frac{C_{bridge}}{C_{LSBtotal}})}{C_{MSBtotal} + (C_{MSBtotal} + C_{LSBtotal}) \times \frac{C_{bridge}}{C_{LSBtotal}}} \times \frac{v_{ref}}{2} . \tag{3.2.1}$$

Here,  $C_{MSB}(i)$  refers to the capacitor value of a stage in the MSB-side of the capacitor DAC.  $C_{LSB}(i)$  on the other hand refers to the capacitor value of a stage in the LSB-side.  $C_{bridge}$  is the capacitor value of the bridge capacitor. This equation looks complicated, but this is due to the fact that the capacitor values of the LSB-side do not represent the weights, but are attenuated by the bridge capacitor. With the conventional approach, where the capacitors are binary-weighted, the equation is simplified greatly. The model presented, however, is effective for all weighting and bridge capacitor values

### 3.4 PARASITIC EFFECTS OF THE CAPACITOR DAC

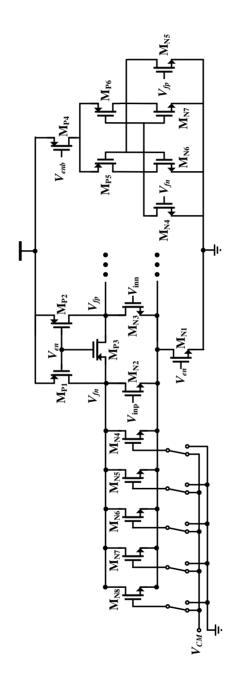

Parasitic capacitances tend to deviate the capacitor DAC of the SAR ADC from performing the ideal search-algorithm that was initially designed by proper weighting of the capacitor stages, and their effect on the resolution is included in the modeling of the SAR ADC. The parasitic capacitances that affect the resolution of the ADC can be classified into mainly three parts; the parasitic at the top plate of the MSB-side of the split-capacitor DAC, the parasitic at the top plate of the LSB-side of the split-capacitor DAC, and the parasitic that is parallel to the bridge capacitor. The location of these parasitic capacitances are shown in Fig. 3.4.1. The parasitic capacitance at the bottom plates of the capacitor stages are not included in the model, as they do not have significant effect. The bottom plates are directly connected to the input of the ADC or

Fig. 3.4.1 Parasitic capacitances of importance in the capacitor DAC of the SAR ADC.

some DC voltage at all times, and therefore parasitic capacitance does not transfer charge.

The parasitic capacitance at the top plate of the MSB-side of the split-capacitor DAC affects the overall conversion gain of the SAR ADC. In the model, the capacitance value of the parasitic is added up to the total capacitance of the capacitor DAC to the numerator. Since the parasitic capacitance is bound to be much smaller than the ideal capacitance of the DAC itself, there will be a very fractional attenuation in the conversion range. Equation (3.2.1) can be used as the same, if the parameter  $C_{MSBtotal}$  now includes the value  $C_{pMSB}$ .

The parasitic capacitance of the LSB-side top plate in the split-capacitor gives rise to much more serious linearity issues. It affects the total capacitance of the capacitor

DAC just as the parasitic of the MSB-side, but the effect is attenuated by the bridge capacitor. The more serious effect is that the total capacitance of the LSB-side of the split-capacitor DAC is increased due to the LSB-side. From an intuitive view, this will cause the same problem with the LSBs just as the MSB-side parasitic caused the total conversion: a slight attenuation in the gain of the analog-to-digital conversion. However, a slight variation of the gain in the transfer function of the LSBs means a periodic distortion of the overall transfer function, and therefore serious linearity degradation occurs. Now, equation (3.2.1) must include the value  $C_{\text{pLSB}}$  within the parameter  $C_{\text{LSBtotal}}$ .

A similar effect is shown with the parasitic of the bridge capacitor. Although the parasitic capacitance parallel to the bridge capacitor has only a minor contribution to the change in the total capacitance of the DAC, and therefore the linearity of the SAR ADC. The critical contribution is not to the gain of the total conversion, but to the gain of the transfer function of the LSBs. When ideally size, the bridge capacitor and the total capacitance of the LSB-side of the split-capacitor array that are connected in series would attenuate the total capacitance of the LSB-side so that the ratio between it and the last stage capacitor of the MSB-side is a desired radix, i.e., two in the example of a conventional non-redundant SAR ADC. However, the parallel parasitic capacitance now changes the attenuation factor of the LSB-side. To be more precise, since the parasitic capacitance increases the effective size of the bridge capacitor, the attenuated LSB-side total capacitance value increases. This, in tendency terms, is the same as the

effect of the above mentioned LSB-side top plate parasitic capacitance.

### 3.5 MISMATCH MODEL OF THE CAPACITOR DAC

In designing the size of the capacitive DAC in the SAR ADC, the total capacitance must be larger than the kT/C noise, so that the dominant noise is the quantization noise, and not the thermal noise. However, there is also mismatch to be considered. Other than the parasitic capacitance of capacitors of the DAC array, which may be minimized or kept a constant ratio to the capacitor value by careful layout techniques, the local mismatch among the capacitors is a practical issue that may not be avoided. The standard deviation of the mismatch that occurs in a capacitor is shown as the following equation,

$$\sigma(\frac{\Delta C}{C}) = \frac{A_C}{\sqrt{WL}},\tag{3.5.1}$$

where C is the capacitance value,  $A_c$  is the Pelgrom coefficient which is process-dependent, and W and L are the physical dimensions of the capacitor. As can be seen from this equation, the capacitor size must be increased to reduce the deviation of the capacitor, and therefore the mismatch between capacitors in the DAC. Of course, as the capacitors become larger, the settling time required to charge and discharge the DAC increases as well as the charge itself, and therefore there is a tradeoff between the resolution of the SAR ADC and the operation speed or the power consumption. In the

proposed model of the SAR ADC, the standard deviation of the value of the capacitors is parameterized. Local mismatch is induced into the capacitor DAC by using the MATLAB function *normrnd()*, which generates random numbers that follow the normal distribution. A capacitor is thus introduced to local mismatch by the following equation.

$$C_{mismatch} = C_{ideal} + \text{normrnd}(0, deviation} \times \sqrt{C_{ideal}})$$

(3.5.2)

Here,  $C_{mismatch}$  is the practical capacitive value affected by local mismatch of the ideal capacitance  $C_{ideal}$ , deviation is the aforementioned standard deviation that is fixed by the unit capacitor size and the process-dependent Pelgrom coefficient. The model is capable of giving local mismatch effect to the MSB-side and the LSB-side of the split-capacitor DAC and/or to the bridge capacitor to see the effects of local mismatch among capacitors in different locations in the DAC in order to gain some insight in designing and the DAC of the SAR ADC.

An example of the usage in designing will be explained. For a conventional 12-bit binary-weighted SAR ADC, the model suggests an ENOB of 11.46 bits for a capacitor mismatch given with the deviation value of 0.01. However, the capacitor values would be impractically high, and therefore a bridge capacitor is inserted, splitting the DAC into 5 MSB-side stages and 6 LSB-side stages. It is assumed that the unit capacitor size remains the same. When simulated again with the model, the ENOB now drops drastically to 8.88 bits for the same standard deviation value of 0.01. To locate the dominant factor for this degradation in resolution, the local mismatch is applied only