#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

#### 공학박사학위논문

# Extraction of Host Internal Information for External Hardware Security Monitors

하드웨어 기반 보안 모니터링을 위한 호스트 시스템의 정보 추출

2016년 2월

서울대학교 대학원 전기컴퓨터공학부 이 진 용

#### **Abstract**

Defending electrical devices against a variety of attacks is a daunting task. A lot of researchers have endeavored to address this issue by proposing security solutions that can attain high level of security while minimizing performance overhead introduced to the system. Among them, hardwarebased security solutions have been noted for high performance compared to their software-based counterparts. However, we have witnessed that these mechanisms have rarely been accepted to the market. This phenomenon may be attributed to the fact that most solutions incur non-negligible modifications to the host architecture internals and thus would substantially increase the design time and manufacturing cost. In order to answer this problem, a hardware-based external monitoring has recently been proposed. The crux of this solution is that, being located outside the host core and connected to the host via a standard bus interface, the external monitor can efficiently conduct time-consuming monitoring tasks on behalf of the host while requiring no alteration to the host internals. However, these approaches either suffer from the incapability of handling various security problems or experience unsubtle performance overhead because, being externally placed and having no dedicated communication channels, the hardware monitor has a limited access to the information produced by the host core, and consequently, the system may be forced to use memory regions or other shared hardware resources to explicitly transfer the information from the host to the monitor hardware. In this thesis, we propose a security solution that can carry out more complicated security tasks with low performance overhead while keeping the

host internal architecture intact. This can be archived by using an existing

standard debug interface, readily available in numerous modern processors,

to connect our security monitor to the host processor. In order to show the

validity of our approach and explore the implication of using the debug inter-

face for security monitoring, we present three security monitoring systems

each of which addresses one of three well-known security issues: defending

against kernel rootkits, tracking information-flow, and defense of code-reuse

attacks. The experiment results show that, when implemented on a FPGA

prototyping board, our monitoring solutions successfully detect the attack

samples (i.e., data leakage attacks and CRAs). More importantly, our systems

can attain significantly low performance overhead compared to previously

proposed security monitoring solutions. The experiments also reveal that the

area overhead of the hardware is acceptably small when compared to the

normal sizes of today's mobile processors.

**Keywords:** Security, Hardware-based Security Monitoring, Core Debug

Interface

**Student number :** 2011-30250

ii

# **Table of Contents**

| I.  | In  | troduct  | ion                                               | 1  |

|-----|-----|----------|---------------------------------------------------|----|

| II. | Ва  | ckgrou   | nd and Related Work                               | 8  |

|     | 2.1 | Backg    | round                                             | 8  |

|     |     | 2.1.1    | Core Debug Interface                              | 8  |

|     | 2.2 | Relate   | d Work                                            | 9  |

|     |     | 2.2.1    | Software-based Monitoring solutions               | 10 |

|     |     | 2.2.2    | Hardware-based Monitoring with Invasive Modifica- |    |

|     |     |          | tion                                              | 10 |

|     |     | 2.2.3    | Hardware-based Monitoring with Minimal Modifi-    |    |

|     |     |          | cation                                            | 11 |

|     |     | 2.2.4    | Hardware-based Kernel Integrity Monitors          | 12 |

|     |     | 2.2.5    | Utilizing debug interface                         | 13 |

| Ш   | . M | onitorii | ng the Integrity of OS Kernels with Data-Flow In- |    |

|     | fo  | rmation  |                                                   | 15 |

|     | 3.1 | Introd   | uction                                            | 15 |

|     | 3.2 | Motiva   | ational Example                                   | 19 |

|     | 3.3 | Assum    | nptions and Threat Models                         | 20 |

|     | 3.4 | The Ba   | aseline System                                    | 21 |

|     |     | 3.4.1    | The Overall System Design                         | 21 |

|     |     | 3.4.2    | Periodic Cache Flush for Cache Resident Attacks   | 23 |

|     | 3.5 | Extrax design                                              | 25 |

|-----|-----|------------------------------------------------------------|----|

|     |     | 3.5.1 Address Translation Unit                             | 26 |

|     |     | 3.5.2 Early Stage Filter                                   | 28 |

|     | 3.6 | Experimental Results                                       | 30 |

|     |     | 3.6.1 Prototype System                                     | 30 |

|     |     | 3.6.2 Security Evaluation                                  | 32 |

|     |     | 3.6.3 Performance Analysis                                 | 34 |

|     |     | 3.6.4 Power Consumption                                    | 36 |

|     | 3.7 | Limitation and Future Work                                 | 36 |

|     | 3.8 | Conclusion                                                 | 39 |

| IV  | M   | nitoring Dynamic Information Flow using Control Flow/Data  |    |

| 1 V |     | onitoring Dynamic Information Flow using Control-Flow/Data |    |

|     | Flo | w Information                                              | 41 |

|     | 4.1 | Introduction                                               | 41 |

|     | 4.2 | DIFT Process with an External Hardware Engine 4            | 14 |

|     | 4.3 | Building a DIFT Engine for CDI                             | 18 |

|     |     | 4.3.1 Components of the DIFT Engine                        | 18 |

|     |     | 4.3.2 Tag Propagation Unit                                 | 51 |

|     | 4.4 | Experiment                                                 | 53 |

|     |     | 4.4.1 Security Evaluation                                  | 56 |

|     |     | 4.4.2 Performance Evaluation                               | 56 |

|     | 4.5 | Conclusion                                                 | 59 |

| V.  | Me  | onitoring ROP/JOP Attacks using Control-Flow Informa-      |    |

|     | tio |                                                            | 50 |

|     |     |                                                            | 50 |

|     | , I |                                                            |    |

| 5.2     | Backg    | round and Assumptions           |  |

|---------|----------|---------------------------------|--|

|         | 5.2.1    | Background                      |  |

|         | 5.2.2    | Assumptions and Threat Model 70 |  |

| 5.3     | Overal   | Il System Architecture          |  |

|         | 5.3.1    | SoC Prototype Overview          |  |

|         | 5.3.2    | CRA Detection Process           |  |

| 5.4     | IMPLI    | EMENTATION DETAILS              |  |

|         | 5.4.1    | Binary Instrumentation          |  |

|         | 5.4.2    | Hardware Architectures          |  |

| 5.5     | EXPE     | RIMENTAL RESULTS 82             |  |

| 5.6     | Conclu   | usion                           |  |

| VI. Co  | onclusio | on                              |  |

| Bibliog | raphy .  |                                 |  |

| 초 로     |          | 99                              |  |

# **Figures**

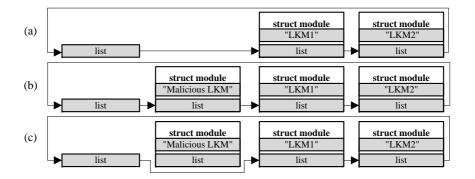

| 1.  | Cache resident LKM hiding attack                     | 20 |

|-----|------------------------------------------------------|----|

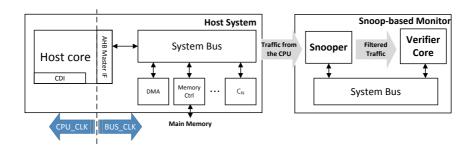

| 2.  | The overall baseline system design                   | 21 |

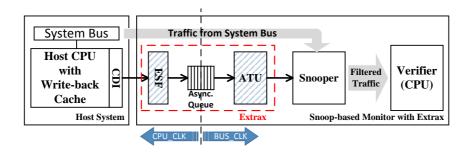

| 3.  | The augmented baseline system with Extrax            | 26 |

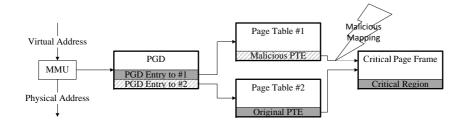

| 4.  | Multiple virtual addresses mapping example           | 27 |

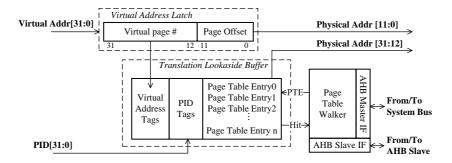

| 5.  | The structure of the ATU                             | 27 |

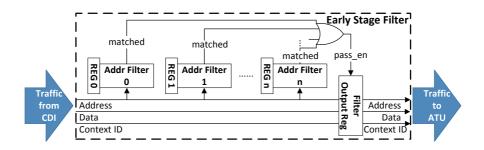

| 6.  | The overall structure of the early stage filter      | 29 |

| 7.  | Example for DLP using DIFT                           | 44 |

| 8.  | Example of tag propagation rules                     | 46 |

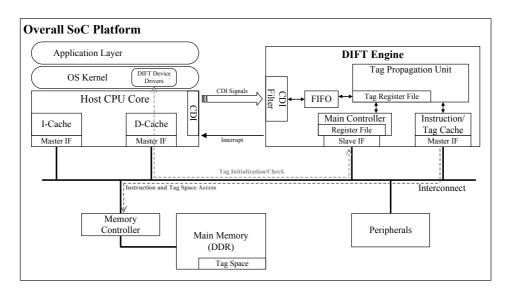

| 9.  | Overall SoC platform                                 | 49 |

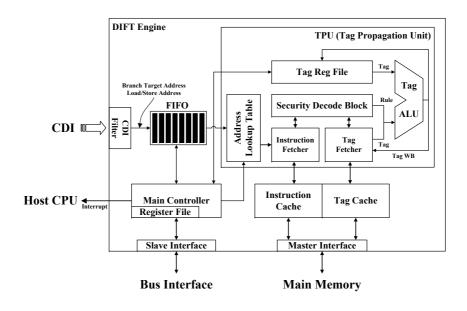

| 10. | Microarchitecture of the proposed DIFT engine        | 51 |

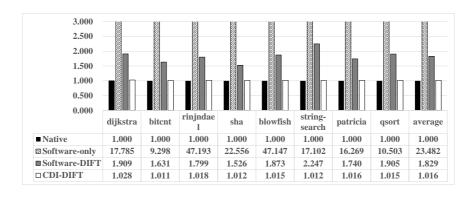

| 11. | Graph of execution time normalized to Native         | 58 |

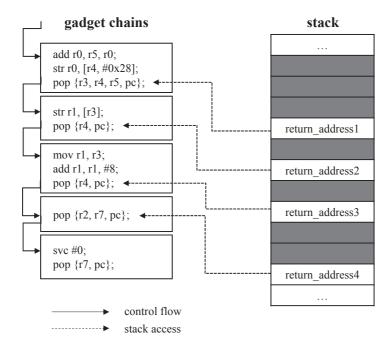

| 12. | A ROP example on ARM processors                      | 69 |

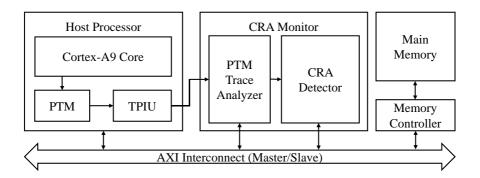

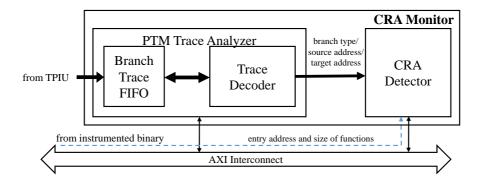

| 13. | Overall architecture of our SoC design               | 71 |

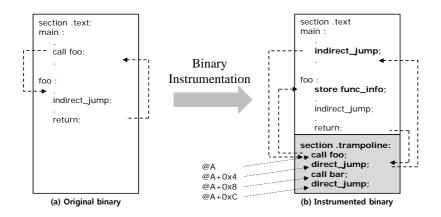

| 14. | Original vs. instrumented binary (newly added parts  |    |

|     | are written in boldface)                             | 76 |

| 15. | CRA monitor hardware architecture                    | 78 |

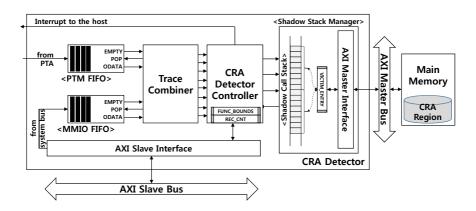

| 16. | Hardware architecture of the CRA detector            | 78 |

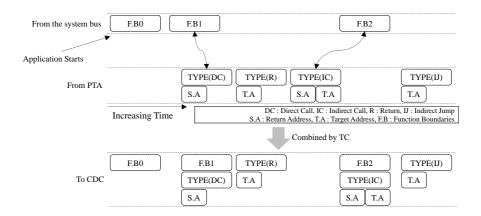

| 17. | Information flow diagram processed by the Trace Com- |    |

|     | biner                                                | 79 |

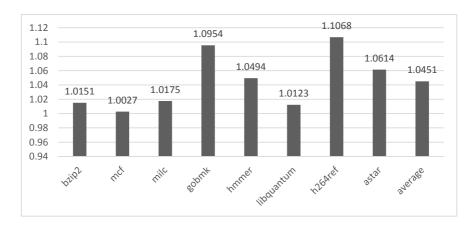

| 18. | Benchmark execution time when the CRA monitor is     |    |

|     | enabled                                              | 84 |

### **Tables**

| 1.  | Description of CDI signals for ETM                        | 9  |

|-----|-----------------------------------------------------------|----|

| 2.  | Synthesis result of the prototype system                  | 32 |

| 3.  | Rootkit detection result                                  | 32 |

| 4.  | Performance overhead                                      | 35 |

| 5.  | Bandwidth comparison                                      | 35 |

| 6.  | Power consumption analysis                                | 36 |

| 7.  | Synthesis result                                          | 54 |

| 8.  | Comparison table of execution time normalized to Native   | 57 |

| 9.  | The description of implemented CRAs and detection re-     |    |

|     | sults of the attacks                                      | 83 |

| 10. | Comparison of binary sizes between ours and [1]           | 85 |

| 11. | Frequency gap tolerance of ours and [1]                   |    |

|     | (IP_CLK is for both the monitor and the DDR memory) $\ .$ | 86 |

# Chapter 1

#### Introduction

As technology rapidly evolves, we are nowadays surrounded by a myriad electrical devices, including desktops, laptops, tablets, mobile phones, and smart watches. With these devices, we can do various things; they include seemingly trivial tasks such as sending emails and accessing social network sites to considerably more serious business like online banking and measuring medical information. As the amount of private information managed in these devices drastically increases, they are becoming more appealing targets of attackers.

In order to protect these devices (which we call the *system* from now on) against various attacks, a number of *security solutions* have been proposed in literature [2, 3, 4, 5, 6, 7, 8, 9, 10, 11]. Techniques they employ in their solutions can roughly be categorized as follows: (1) *encryption* (2) *obfuscation* (3) *isolation* (4) *system monitoring*. Encryption is a process of converting one data form into another, called *ciphertext*, basically making the original data impossible to be read or be understood by unauthorized users. Unlike encryption techniques that use *keys* to convert the whole data, obfuscation deliberately changes the layout of the structure of original data or

inserts redundant logics to original source code in a way that malicious users cannot easily understand the original meaning of the code/data. Isolation is, as the name implies, the way of protecting information by placing it in a reserved, isolated space that cannot be accessed without proper authority. Lastly, system monitoring is an act of watching a specific set of system behaviors and checking whether the behaviors deviate from the ones of the legitimate system.

More specifically, the system monitoring technique mainly checks the execution behaviors of a program running on the host system to find any symptom of attacks. For monitoring, users or system administrators firstly define a set of *rules* (or *invariants*) that mostly signify the legitimate behaviors of target applications during normal code execution. At runtime, a security *monitor* deployed on the system checks whether there is any violation of these rules. If there is any detection of such an event, then the system administrators are notified of a possible attack.

Among many techniques, this system monitoring techniques have been adopted in many security solutions addressing a variety of attacks from monitoring the integrity of OS kernels [10, 12, 13, 14, 8, 9, 11] to monitoring application behaviors to detect any suspicious activities, for instance, by performing *dynamic information flow tracking* or *control flow integrity checking* [15, 16, 17, 18, 19, 20, 21]. These security monitoring schemes can be implemented in various forms. Two mainstream research directions are *software-based* [14, 8, 9, 22, 23, 15, 16, 17] and *hardware-based* approaches [7, 13, 10, 12, 11, 18, 19].

In general, the former approaches have popularity in the security com-

munity as they do not necessitate underlying hardware modification, thus allowing the easy deployment of such solutions to commodity hardware platforms. Moreover, they can easily adapt to new types of attacks as their core algorithms exist in the form of software, which can be readily updated in the field. Not surprisingly, however, they have a drawback in that they may impose substantial computational loads upon the host machine, which is not desirable for these solutions to be deployed in practice. For instance, in the case of DIFT, the flow of critical data needs to be monitored at every instruction that possibly moves the data from a secure storage to some other places. Even after aggressive optimizations [16, 17], the overhead still remains one or two orders of magnitude higher than that of hardware approaches [18, 19] in which extra hardware for monitoring operations is designed and integrated into an existing processor for acceleration. The main source of such a performance loss is that these software-based monitors are another software layer that competes with other software in the system for computing resources.

The hardware-based approaches, on the contrary, utilize an isolated hardware module which is physically independent of the monitored host system, thus unaffecting the operation of the tasks running on the host. Several works introduced in [13, 24, 25, 10, 12, 11, 26, 27, 28, 29, 30, 18, 19]. These hardware solutions tend to exhibit high performance by accelerating the monitoring process with the assistance of customized hardware logics for the task.

Despite their dramatic performance enhancement, they have a few drawbacks. The first one is that they may require the redesign of the existing processor architecture if one wants to maximize the overall performance while attaining high level of security. For instance, authors in [27, 28, 29] present solutions in which their hardware logics are tightly coupled with the host CPU for close monitoring of every control transfer during code execution. Such a close coupling requires major modifications to processor internal components such as pipeline datapaths or the structure of registers[31, 27, 28, 29], which would stymie the direct deployment of these solutions into commercial platforms.

The second drawback is that, if one chooses to avoid the aforementioned problem and places the monitor at the outside the host procesor as proposed in [12, 10, 11, 13, 20, 21], they may either have their system experiencing non-negligible performance overhead or have their monitor less useful than it should be. Undoubtedly, in their approaches, the host processor can concentrate on the execution of its own code while the time-consuming monitoring task is offloaded to the specialized hardware module outside the processor; in the literature, they empirically demonstrated that their monitoring scheme can be carried out in a great speed by external hardware, relieving significant burden for the extra computation from the host.

Nevertheless, there still remains an inefficiency. It originates from the limited ability of an external module to watch every internal state change dynamically made by the code running on the host. For precise security monitoring, the external monitor should be able to receive from the host various runtime information such as branch targets, memory addresses and register moves. Without such information, the effectiveness of such hardware monitors are subtatially reduced, and are allowed to perform only simple

tasks such as monitoring memeoy access patterns as proposed in [13, 10, 11]. To conduct more sophisticated monitoring tasks, researchers in [21, 20] sugest the use of share memory regions to explicitly deliver the essential information from the host to the monitor. Even though their approaches exhibit a substantial performance improvement compared to software-based approaches, there still remains non-negligible performance overhead mainly due to the tremendous amount of traffic for communication. As reported in [21, 20], the overehad is up to 30% of the total execution time even after all their optimizations through hardware communication buffers and special instructions.

In this thesis, we propose a new security *monitoring solution* that can resolve the problems of the previous works; the monitoring system implemented under the guidance of our solution can carry out more complicated security tasks with negligible performance overhead while keeping the host internal architecture intact. Complex as it sounds, but our monitoring solution merely suggests that the monitoring engine be placed externally to the host processor, similar to those introduced in [21, 20, 12, 10, 13], and that the engines be connected to the host processor via an existing standard interface, called the *core debug interface* (CDI), which is readily available for debugging purposes in various modern processors including ARM Cortex series and Intel x86 architectures [32, 33, 34].

Once they are plugged into CDI, our monitor engines can access bountiful information transmitted in the form of signals from CDI. The signals from CDI can largely be categorized into two groups. The first group of signals convey information relavant to the control-flow transfer of code executed

on the host system. The second group of signals present memory access behaviors such as target addresses of a memory access with its corresponding (written/read) value for the access. In our solution, these groups of signals, which we hereafter call the *control-flow information* and *data-flow information* respectively, are the key element that enable us to build a variety of security monitoring mechanisms on external hardware monitors.

Simple as it may sound, but using these signals for building up a security system can involve several complications majorly because the initial set of signals from CDI cannot simply be fed into the security monitor as they are in their present form. Some signals originally generated for debugging may need to be translated into another form that is required for security monitoring. Therefore, in order to show the implication of using CDI for security monitoring, this thesis presents in its main chapters three well-known security problems, each of which monitoring solution requires different groups of signals to address the corresponding problem. In Chapter 3, attacks that target the integrity of an OS kernel is presented. The chapter shows, under the vigilance of our proposed monitor and thanks to the data-flow information transferred via CDI, no attack launched on the system can compromise the kernel. Chapter 5 describes a well-known attack technique that attackers tweak the control flow of a legitimate code into performing malicious operations. The second monitorng system presented in this chapter uses the control-flow information coming from CDI to detect any suspicious control-flow change. Chapter 4 presents a monitoring system that uses both control-flow and data-flow information to monitor the trace of secret data. At runtime, every data derived from the secret data is tainted and tracked

throughout the operation, and if any tainted data is involed in potentially illegal activities, our monitoring system raises an alarm.

This thesis is organized as follows: Chapter 1 introduces and sumarizes the thesis. Chapter 2 provides a brief explanation of CDI and presents past work in the area of software-based and hardware-based monitoring solutions. Chapter 3 describes a monitoring solution that makes use of data-flow information to detect attacks targetting OS kernels. In Chapter 5, a monitoring solution that uses the control-flow information is explained. Chapter 4 shows the third monitoring solution that, to detect the misuse of critical data, makes use of both control-flow and data-flow information. And finally, Chapter 6

## Chapter 2

#### **Background and Related Work**

#### 2.1 Background

#### 2.1.1 Core Debug Interface

As the complexity of software running on a processor drastically increases, recent commodity processor vendors tend to include rich debug features in thier hardware. The *On-chip debug* (OCD) unit [35, 34] is such a hardware feature that supports efficient real-time debugging/tracing without affecting the performance of the target processor. Provided by OCD, a rich set of information allows developers (or users), on their debugging environment (usually on desktop machines), to follow the path that the target CPU takes as a result of code execution and monitor values in various registers and memories. Representative examples of OCD are the ARM CoresSight modules [32] supported in ARM Cortex series processors such as the *embedded trace macrocell* (ETM) and the *program trace macrocell* (PTM).

CDI is an interface placed on the CPU side, whose main role is to provide OCD with the CPU's internal status information that is essential for debug/trace. In general, the OCD modules provide various signals to

| Signal         | Description                  |

|----------------|------------------------------|

| ETMICTL [20:0] | ETM instruction control bus  |

| ETMIA [31:1]   | ETM instruction address      |

| ETMDCTL [10:0] | ETM data control bus         |

| ETMDA [31:0]   | ETM data address             |

| ETMDD [63:0]   | ETM data write data value    |

| ETMCID [31:0]  | Current processor Context ID |

table 1: Description of CDI signals for ETM

developers such as instruction address, current context ID (or process ID), and data address/value of memory access instructions, which are useful information to keep track of the behavior of a monitored program. Thus, CDI for the OCD modules also provide such information through the dedicated signal lines [32]. As an example, in Table 1, the signals to ETM provided by ARM processors through CDI is described. Although the types of information supported by CDI can vary from one processor architecture to another, the signals presented in Table 1 are generally provided in most CDIs.

#### 2.2 Related Work

As introduced in Chapter 1, there have been much research conducted to defend computer systems from various security attacks. In this section, we present a number of security solutions which mainly rely their detection techniques on monitoring the behaviors or patterns exhibited on the host system as a result of target program code execution. Starting from the description of the software-based monitoring solutions, we revisit past work on hardware-based monitoring solutions, and finally we address some work

relavant to the use of debug interfaces to other purposes than their original usages.

#### 2.2.1 Software-based Monitoring solutions

To defend the computer systems from various security attacks, there have been proposed a number of monitoring techniques, such as DIFT [22], memory bound checking and control flow integrity checking [15]. The most popular way to realize security monitoring schemes is to implement them in software. Most software monitoring approaches [22, 16, 36, 17, 37, 15] have relied upon either source-code instrumentation or dynamic binary translation (DBT) [38] for the defense against diverse attacks at execution time. However, the main drawback of them is that they experience excessively high performance overhead. For example, in [22] that proposes a softwarebased DIFT implementation, the overhead reaches up to about 40 times the original code execution time in the worst case. The performance overhead of DROP [23], which proposes a ROP detection scheme, ranges from 1.9X to 21X. MoCFI [39], which introduces a CFI checking technique on ARMbased mobile devices, shows the performance loss about 5X. Considering that these techniques are usually employed for runtime monitoring, the performance degradation is not acceptable to be deployed in real machines.

#### 2.2.2 Hardware-based Monitoring with Invasive Modification

To address the shortcoming of software-based monitoring, some early hardware approaches [18, 19, 27, 28, 40, 20] tried to improve performance by inserting into the host processor core dedicated hardware modules that

accelerate monitoring computations. The main advantage of these approaches is that they do not need to instrument the host code and thus they could bring the overhead down to under 5%. However, they have a disadvantage in that invasive modifications to the processor internal (e.g., registers and pipeline data paths) are required. For instance in [18], inside the core, they installed hardware tagging units to conduct DIFT, called the *flow tracker* and *tag checker*, and widened the widths of registers, internal datapaths and caches, to accommodate tag bits, all of which call for major changes of the processor internal. In fact, modern microprocessor development may take several years and hundreds of engineers from an initial design to production [31]. Therefore, the substantial costs of development to integrate the customized logic would hamper processor vendors to adopt them, unless the necessity is clearly established.

#### 2.2.3 Hardware-based Monitoring with Minimal Modification

In an attempt to minimize the internal architecture changes, the researchers in [20, 21] suggested security monitoring solutions in the existing multi-core environment where one general-purpose core is devoted solely to run a *helper thread* that performs tag propagation for the main code running concurrently on a different core. In [31, 41], they proposed an external device that performs monitoring outside the host. By dedicating the monitoring task to a separate core or an external hardware, these approaches can manage to enhance the performance drastically. However, as discussed earlier, the fundamental problem of these approaches is that a vast amount of information must be continuously delivered to the external hardware for accurate

monitoring operations [41]. To cope with this communication issue, they modified either the x86 architecture to supplement special hardware queues and new instructions [20, 21], or the CPU pipeline datapath to provide a customized channel between the host and the external device [31]. Our work is somewhat similar to the work in [31] since both propose the external hardware optimized for DIFT. But ours is different from theirs in that we exploit the standard interface CDI for communication. The security engines proposed in our work have been specially designed to perform the monitoring tasks by interpreting the signals for debugging from CDI.

#### 2.2.4 Hardware-based Kernel Integrity Monitors

The idea of using a separate hardware module to secure the kernel was first proposed by Hollingworth et al [42]. In the work, they used a symmetric multi-processor to secure the kernel. Later, Zhang et al. [43] suggested deploying an intrusion detection system on a coprocessor to monitor the host. Petroni et al. designed and implemented Copilot [13], a snapshot-based kernel integrity monitor based on a coprocessor PCI card. Originally, Copilot focused on monitoring only *immutable kernel regions*, where the residing code or data should not be changed during runtime, but additional effort had been made in [25] to monitor *kernel dynamic regions*, where the data can be modified as a result of legitimate kernel operations, as well. Baliga et al. presented a PCI card-based two-phase rootkit detection technique in which the first phase automatically extracts the invariants of kernel data structures and the second phase enforces the invariants at run-time [24]. Even though these monitors employed external hardware module to secure the

kerel, they employed snapshot-based approach, which periodically takes snapshot of memory contents to detect suspicious activities. Therefore, they cannot constantly monitor the memory contents since doing so would impose performance overhead on the system. Moreover, their periodic monitoring opens up a new vulnerability, which can be exploited by *transient attacks* as reported in [10].

Recently, researchers who are aware of the problem of transient attacks proposed snoop-based external monitors. Vigilare [10] was the first work that leverages an external hardware monitor to constantly snoop the system bus to protect immutable kernel regions. In [11], they also proposed snooping techniques. They especially has shown the feasibility of the approach by showing that only small portion of all memory access are related to operating system kernel and the portion of write in the access is again small. KI-Mon [12] extended the Vigilare to monitor both immutable and mutable kernel regions. These monitors have the capacity of defending a system with negligible performance overhead, but the scope of attacks they can address is somewhat limited in that they can monitor only memory access patterns placed on the standard bus interface.

#### 2.2.5 Utilizing debug interface

The idea of using debug interface for other purpose rather than debugging has been proposed in other works, especially in the field of fault-tolerent computing [44, 45, 46, 47, 48, 49, 50]. In [44, 45, 46, 47], they proposed methods of injecting faults to the host system by accessing internal resources such as registers and memory via existing OCD. In doing so, they tried to

facilitate fault tolerance evaluation. Their works are different from ours because they use OCD to intrusively modify the internal state of the host CPU to inject faults while ours are directly connected to CDI to monitor the trace of memory access events so as to detect malicious attempt. In [48, 49, 50], they presented error detection approaches utilizing available debugging interface, CDI or trace buffer in OCD, to retrieve control flow information as well as load/store information. The overall concept of exploiting information flowing out of CDI is same to the of our monitoring system, but the main objective is different in that theirs is to detect faults while ours is to defend the host system against various security attacks.

# **Chapter 3**

# Monitoring the Integrity of OS Kernels with Data-Flow Information

#### 3.1 Introduction

As electronic devices such as PCs and smartphones become essential parts of our everyday life, the potential privacy and security risks due to numerous *malwares* on the devices are rapidly growing. As a means to protect such devices from these attacks, current OSes support a variety of anti-malware solutions. These solutions usually depend on the services from the underlying OS kernel, implying that they would only work as designed when the integrity of the kernel is ensured. However, the kernel integrity has been seriously threatened since the advent of *kernel level rootkits* that manipulate the kernel so as to achieve certain goals (i.e., concealing their existence or providing backdoor accesses). Because the kernel operates at the highest privilege level in the system, the compromised kernel may nullify the effectiveness of any anti-malware measures that have their root of trust on the kernel.

The threat of rootkits have urged researchers to conduct much study to

seek a more secure computing base that can safely monitor the system and ensure the kernel integrity even in the presence of rootkits. Two mainstream of the research directions are *hypervisor-based* [14, 8, 9] and *hardware-based* approaches [7, 13, 10, 12, 11]. In general, the former approaches have popularity in the security community as they do not necessitate underlying hardware modification while providing a higher privileged, thus safer, software layer for monitoring than the kernel does. However, the latest attacks [51] and reported vulnerabilities [52] pointed toward the probability that the code and data of hypervisors can also be compromised at runtime. Although the known vulnerabilities have been fixed shortly, the growing complexity of hypervisors implicates that there would be more vulnerabilities revealed in the near future.

The hardware-based approaches utilize an isolated hardware module physically independent of the monitored host system [13, 10, 12, 11]. In particular, prominent monitoring schemes are recently proposed in [10, 12, 11]. At the center of these approaches, there is a hardware monitor, which we hereafter call the *snoop-based monitor*, whose role is to detect malicious attempts to alter the kernel by snooping every data traffic between the host CPU and main memory. Being located at the outside of the host as a dedicated hardware unit, the monitor is not only immune to rootkits attacks on the host, but also able to constantly observe the memory access behaviors of rootkits revealed on the system bus without affecting the host performance.

Although snoop-based monitors have been working well in their environments and assumptions, we have recently discovered a potential vulnerability which future attackers might exploit. It comes from the fact that most computer systems employ write-back caches. Being located in between the host CPU and main memory, caches hold copies of data or instructions recently accessed by CPU, thereby boosting the overall system performance to a large extent. However, for the perspective of snoop-based monitors, the existence of caches can be disadvantageous because they shall reduce the number of events that the monitors can watch. For example, if a rootkit tries to compromise the kernel by modifying sensitive data, and the very data hits in the cache, then the write traffic would not appear on the system bus, rendering the monitor oblivious of the write event.

Even though some previous works discussed the possibility that this problem may seriously undermine the effectiveness of their approaches [10, 12, 11], none of them has properly addressed this *cache-induced hiding* (CIH) effect problem. In [12], they tried to avert the problem by restricting the usage of their monitors to the systems with write-through caches. In [11], they merely mentioned a simple scheme of using periodic cache flush. Unfortunately, they did not provide any empirical data about how much loss their scheme may suffer on performance, detection rate or power consumption. However, as we will see later, our study evinces that frequent cache flush might increase the host performance overhead to a large extent.

In this chapter, we present a hardware-assisted low-overhead solution which thwarts the CIH effect by enabling the external monitors to directly access the *cache resident information* (CRI) which includes all the internal data residing within the cache without being exposed on the system bus. To implement this solution, we utilized the existing hardware logic, CDI, which can be found in several processors available today such as ARM Cortex series

and Xilinx MicroBlaze[35, 34]. If CDI is plugged into a security monitor, the bountiful information provided by CDI, which contains memory access events issued by CPU, would certainly help monitor perform its desired task without the CIH effect.

This task, however, involves several complications in implementation majorly because the initial set of signals from CDI cannot be simply fed into the security monitor as they are in their present form. Some signals originally generated for debugging must be translated into another form that is required for security monitoring. Therefore, we have developed an extra hardware unit, called the *Extrax*, that being located between CDI and security monitors, carefully examine and properly refine or transform each individual signal from the interface before delivering it to the monitor.

To validate our design and further explore the implication of this additional circuits to the overall system, we have implemented a full snoop-based monitoring system in which the host system has been augmented with Extrax. With the system prototyped on a FPGA platform, we evaluated and compared the performance, power and area of our full system against the baseline system in which Extrax is not deployed. Experiment results exhibit that our monitor, with modest area and power overhead but with the host performance being almost unaffected, successfully detects rootkit attacks regardless of the type of caches while the baseline monitor often fails.

The rest of the chapter is organized as follows. We first present a motivational example in Section 3.2. Then in Section 3.3, the assumption and threat model are presented. In Section 3.4, the baseline system is presented to show the overall operation of hardware-based monitoring. Section 3.5

describes the details of the proposed security extension, Extrax. After Section 3.6 shows our experimental results, we conclude this chapter in Section 3.8.

#### 3.2 Motivational Example

We define *cache resident attacks* as malicious attacks that, intentionally or unintentionally take advantage of the CIH effect; the existence of writeback caches can unintentionally blindfold snoop-based monitors by impeding memory write events from appearing on the system bus, or attackers can intentionally hide the evidence of attacks by overwriting the malicious data residing in caches with benign one, thereby prohibiting the monitors to detect the symptom of attacks. To better explain, we chose the *loadable kernel module (LKM) hiding* technique as a representative cache resident attack example since many rootkits in the wild employ the technique to hide themselves. LKMs are initially designed to support extension of the kernel code at runtime without recompiling the entire kernel. However, they are often used by attackers to conceal malicious processes, files or even themselves from detection mechanisms. Adversaries achieve their goal of hiding LKMs by directly modifying the kernel data structures that maintain the list of loaded LKMs.

Figure 1 shows how the LKM hiding technique is affected by write-back caches. In (a), there are several LKMs, each of which is represented by the **struct module**. The kernel handles the LKMs by maintaining the **modules** list, which is a linked list of **struct module**. Upon the module load request, in this case a request from the malicious LKM depicted in (b), the kernel

Figure 1: Cache resident LKM hiding attack

adds the corresponding **struct module** to the **list**, which is the head of the **modules** list. In a system with write-back cache, the **list** will be cached after this step, and subsequent accesses to the data structure will also hit in the cache. Thus, even if the malicious LKM removes itself from the **modules** list by directly manipulating the pointers of the **modules** list as depicted in (c), this event might not be placed on the system bus. Consequently, recently proposed snoop-based monitors might no longer guarantee the integrity of the kernel since they detect attacks by snooping the system bus. Hence, a novel way to nullify CIH effect should be devised.

#### 3.3 Assumptions and Threat Models

We use the assumption taken by previous snoop-based monitors, especially by KI-Mon [12]. Therefore, we assume that adversaries have already gained administrators' privilege on the host system and thus are able to install rootkits to hide themselves or leave backdoors to the host system; for instance, the attackers can install LKMs or place hooks on critical system

calls. However, we rule out *physical attacks* by an insider who has direct access to the host system and *direct kernel structure manipulation attacks* proposed in [53].

In addition, we also assume that the host system uses write-back caches, and provides CDI, that can be connected to OCD. Side-channel attacks that exploit the information from OCD/CDI are not considered in this work.

#### 3.4 The Baseline System

#### 3.4.1 The Overall System Design

Figure 2 shows a high level view of the baseline system. Since our monitoring system employs the snoop-based monitoring scheme, it is similar to the prototype of KI-Mon[12]. To ensure the integrity of the kernel, the monitor side core dynamically configures the hardware ASIC units, especially the *snooper*, based on a security policy.

We designed our baseline monitor to support various policies on detecting attacks on immutable regions and *mutable objects* that have *invariant* value sets, as KI-Mon proposed in [12]. Immutable regions contain data that

Figure 2: The overall baseline system design

should not be modified after the boot process is complete, such as the *system* call table (SCT) and *interrupt descriptor table* (IDT). Kernel mutable object with a invariant value set is data object in which data can be updated by the kernel at run-time, but the updated value is chosen among the set of possible values that can be profiled prior to run-time; for instance, many function pointers within kernel objects are known that each function pointer points to one of its possible candidate landing sites [12].

According to the security policy of the host CPU, the snooper is configured with appropriate address ranges of the kernel data objects or regions to be monitored on main memory. Then the snooper constantly acquires write events placed on the system bus, filters out every benign event that is not relevant to the monitored regions, and transfers only the ones that violate the current security policy to the *verifier core* for further investigation.

While attacks on immutable regions can be easily detected by simply snooping the bus for write events on the region, catching evidence of malicious modifications on kernel mutable objects with invariant value sets is not straightforward since mere write events cannot be regarded as a symptom of attacks. Therefore, we employ techniques similar to the ones proposed in [12] such as the *whitelisting-based verification* and *callback-based semantic verification* that basically verifies the written values as well. The detailed explanation of these techniques are omitted in this chapter since our work is focused on overcoming the CIH effect rather than suggesting new detection schemes. Therefore, readers interested in these techniques are kindly referred to [12].

The key difference between our baseline system and the prototype of

[12] is that ours uses write-back caches. Therefore, snooping only the system bus may cause detection failure because of the aforementioned CIH effect.

#### 3.4.2 Periodic Cache Flush for Cache Resident Attacks

As mentioned in [11], periodically flushing caches might help reveal more CRI on the bus when write-back caches are deployed in the system. To show the effectiveness of the scheme, we applied it to the baseline system. When implementing the scheme, the flush period should be decided with great care because a reckless choice of the period may induce either non-negligible overhead or detection failure.

For attacks that aim at immutable regions [10], the cache flush period, **p**, can be selected arbitrarily because any write attempt on the regions is deemed malicious [10], and the cacheline where the written data is located will eventually be evicted to main memory regardless of the period **p**. However, the decision of the period **p** for attacks that target kernel mutable objects is far more difficult since attackers can usually figure out a way to avoid detection by slightly modifying the original attacks.

To better explain, consider the case shown in Figure 1. Assume that the state of the **modules** list changes from the state (a) to (b) on time **s**, and from the state (b) to (c) on time **e**. In principle, the baseline monitor concludes that an LKM is malicious when the LKM is removed from the **modules** list (state change from (b) to (c)) while the corresponding memory region for the LKM remains in memory [12]. Thus, the period of cache flush **p** should be shorter than the interval **d=e-s** so that every event on **modules** list can be revealed on the system bus before the adversary achieve her own goal. Since **d** in a

primitive LKM hiding technique is sufficiently large, **p** of our baseline with periodic cache flush could be long as well, so as to detect the attack with acceptable performance overhead.

However, by slightly changing the original LKM hiding technique, it is possible for attackers to reduce **d** substantially. The devised technique requires two LKMs, one of which is the malicious LKM and the other is an LKM that merely hides the first one. We call the latter the *hider LKM* whose role is to insert a callback function to the kernel timer, and set the timer with a period **q**. Then the callback function is periodically invoked to check whether the malicious LKM, which ultimately achieves the attacker; so goal, is inserted or not, and hide the newly added one upon detection. To insert and hide a malicious LKM, attackers first insert the hider LKM with an arbitrary period **q**, and insert the malicious one sometime later. Since the hider LKM does not hide itself and is thus added and removed legitimately, the monitor has no way of distinguishing the hider LKM from other normal LKMs.

Thus, to defend against such cache resident attacks, the flushing period **d** should be adjusted to a very small value. Our preliminary study showed that, in order to attain 100% detection rate, the period **d** need to be reduced to 30us, resulting in increased performance overhead of up to 84%. From this result, we claim that the detection with periodic cache flush might not only induce huge performace overhead, but would also cause failing in detection if attackers know the existence of periodic cache flush and modify their attacks to reduce **d**.

#### 3.5 Extrax design

As long as CRI is accurately sent via CDI to snoop-based monitors, many security threats due to cache resident attacks would be resolved without modifying the host internal architecture. Unfortunately, realizing precise and efficient deliverance of these signals in an actual system comes at a cost with some implementation challenges, as briefly stated in Section 3.1. Below is summarized two of those that must be resolved in order to efficaciously transfer the host internal information to snoop-based monitors through the existing CDI.

- 1. CDI is originally designed to send a virtual address (VA) to the OCD unit for each memory access while the monitor demands physical addresses (PA) so as not to be disrupted by the certain type of attacks which will be discussed shortly. Therefore, the original VAs from CDI cannot be directly used for a snoop-based monitor.

- 2. The number of memory events coming from CDI is far larger than that of those appearing on the system bus because a majority of write events originating from CPU are hidden by caches on the way to the bus. This excessive number of events sent from CDI could be burdensome to the monitoring system in terms of performance.

These key issues are tackled respectively by two new hardware units, the *address translation unit* (ATU) and the *early stage filter* (ESF), both of which constitute our Extrax. Figure 3 depicts a block diagram of our proposed system where the baseline is extended with Extrax. It is noteworthy here that even though the information conveyed through ATU can cover all

Figure 3: The augmented baseline system with Extrax

memory events, the original path from the system bus remains the same. The purpose of the path is mainly to detect attacks from other *bus masters* such as DMA. In this section, we will focus our discussion on these hardware units.

#### 3.5.1 Address Translation Unit

Upon receiving VAs from CDI, a snoop-based monitor should decide whether the current memory access targets the regions it monitors. It seems that such a decision can be made based on VAs, but there are cases in which the monitor necessities PAs. For instance, consider the case depicted in Figure 4 where the monitor is protecting a kernel data structure contained in the critical page frame. Since this data structure is critical to the integrity of the system and is thus managed by the kernel through the *kernel page table*, no arbitrary mapping should be made to the data structure. However, in the presence of kernel-level rootkits, it would be possible for attackers to simply insert an LKM that generates another page table mapping for the data structure, denoted as the *malicious mapping* in the figure. Thus in this situation, if the monitor used the original VA to protect this type of kernel structures, the attackers could indirectly modify the kernel data with the

Figure 4: Multiple virtual addresses mapping example

newly mapped VA, hence successfully escaping the vigilance of the monitor.

To deal with the cases where PAs must be supplied for security monitors, we have installed ATU that translates VAs from CDI into physical ones. The overall architecture of ATU is displayed in Figure 5. ATU is configured by the monitor through the advanced high-performance bus (AHB) slave interface. On a translation lookaside buffer (TLB) miss, a *page table walk* is initiated through the AHB master interface, which is connected to the host system bus. The input to ATU includes a VA, the *context ID* and the base address of the Linux page global directory (PGD). The former two inputs are provided by CDI, while the latter one is configured through the AHB master interface immediately after the current context ID is updated. TLB is a fully

Figure 5: The structure of the ATU

associative table in which the number of entries can be configured from 16 to 32. It has a random replacement policy.

#### 3.5.2 Early Stage Filter

With the help of CDI, our monitor is now able to snoop every write event generated by the host CPU without suffering from the CIH effect. This abundant information continuously streaming into the monitor will certainly enhance the chance to detect cache resident attacks. However, it may also create an excessively large volume of information flow that will inevitably impose heavy burdens on the monitor.

Though, if we remind that the monitors usually need to watch only a subset of the memory events of the host depending on security policies, it would be wasteful if ATU exhaustively translates all incoming addresses for the monitor. The problem can be alleviated if we can filter out benign events based on a security policy. As an example, for one of the policies considered in our experiments, the monitor is interested in write attempts to the kernel data. Therefore, any read memory events can be safely discarded before reaching either the monitor or even ATU. The filter operations in this case is in fact rather straightforward since memory access types are easily discernable right after the events occur. However, we often need to apply more aggressive filtering to the events. As briefly mentioned in Section 3.4, the kernel data of interest occupy relatively small amount of memory compared to the whole range of main memory. Therefore, the monitor just needs to watch the access events on this limited region. Unfortunately, it is not always straightforward to decide whether or not an event just emitting from

CDI falls into this region, since its address remains virtual before reaching ATU.

Nevertheless, there is still a way to provide a solution to this decision problem. For this, consider Figure 5 where we see that an address translation step does not require the *page offset* field; in fact, this field is identical for both VAs and PAs. Inspired by this fact, we implemented ESF which, being placed between CDI and ATU, removes unnecessary memory events based on page offset before the events reach ATU, thereby reducing the number of events delivered to ATU.

Figure 6 represents the internal block diagram of ESF, which rearranges the signals from CDI and filters out as many events as possible. The implementation of output rearrangement is somewhat simple in that it merely reorganizes and extracts signals that are needed for the monitors to detect attacks. Among the signals introduced in Section 2.1.1, the addresses/values of memory write instructions and context IDs are selected and rearranged for monitors.

In the current implementation, ESF has eight 12-bit *address range register* pairs and comparators. The address range register pairs of ESF contain the

Figure 6: The overall structure of the early stage filter

page offset field of start/end addresses that need to be monitored. The register values can be configured by the verifier core at any time. Therefore, whenever the critical kernel regions of interest are updated, the monitor configures the snooper and ESF simultaneously.

After the configuration, ESF compare the page offset field of a VA that comes from CDI with the values of address range register pairs. If the address is included in any of the monitoring regions, ESF enables the filter output register so that the event can flow to ATU. Otherwise, ESF blocks the address, thus obviating unnecessary operations in ATU.

As mentioned before, current ESF implementation has 8 pairs of address range register, limiting the number of concurrent monitoring regions. Note that the number of registers can be adjusted for the environment of deployment. Alternatively, we can loosely set the address range register pairs, so that each pair contains more than one monitored region. Although it would produce unnecessary events for ATU to handle, ESF still do not miss any access to the monitored regions.

#### 3.6 Experimental Results

#### 3.6.1 Prototype System

We have implemented our baseline system as close as possible to the design proposed in [12], as an FPGA prototype where the host CPU is the SPARC V8 processor, a 32-bit synthesizable core [54] which uses a single-issue, in-order, 7-stage pipeline. It has separate 16kB L1 caches for instruction and data. In addition, the host CPU also has a 256kB L2 cache

which employs the write-back policy. The host system bus compliant with the AMBA2 AHB/APB protocol is used to interconnect all modules in the system, and Linux 2.6.21.1 is used as the host OS. The snoop-based monitor system is also implemented with the same processor and the system bus. The snooper has eight sets of address range registers which can be configured according to the security policy of the monitor.

To evaluate our approach, we augmented the baseline system with Extrax. Although our host processor, open-source synthesizable core [54], provides their own CDI specification, the information comes out of CDI is quite restricted compared to that of commercial product, such as ARM. Therefore, we slightly extended it to support the CDI signals equivalent to those of ARM architecture (see Table 1). Thus, both ESF and ATU are implemented to be compatible with ARM CDI specification [55]). Since CDI is connected to both Extrax and OCD, we designed Extrax to disable signals to OCD when snoop-based monitoring is turned on. ESF is configured to have 8 address range register pairs. Our ATU, compliant with SPARC V8 Reference MMU [56], has been configured to have 16 TLB entries and 16 input queue entries.

Based on the parameters for the prototype as described above, we synthesized our system onto a prototyping board with a Xilinx SC5VLX330 FPGA. Table 2 provides the area of the baseline system and Extrax in terms of lookup tables for logic (LUTs), block RAMs (BRAMs) and DSP slices (DSP48E). It shows that Extrax incurs 12.09% overhead for LUTs as compared to the baseline hardware. Even though the area overhead of our Extrax seems non-negligible, it is noteworthy here that our baseline system, the

| Category | Component                                           | LUTs   | BRAMs | DSP48E |

|----------|-----------------------------------------------------|--------|-------|--------|

|          | SPARC V8 Core with L1/L2 Cache (Host System)        | 6856   | 86    | 4      |

|          | SPARC V8 Core with L1 Cache Only (External Monitor) | 5878   | 15    | 4      |

| Baseline | Bus components (AHB Buses + AHB/APB bridges)        | 908    | 0     | 0      |

| System   | Memory Controller                                   | 57     | 0     | 0      |

| System   | Snooper                                             | 3318   | 0     | 1      |

|          | Peripherals (TIMER, UART, and etc.)                 | 2480   | 4     | 2      |

|          | Total Baseline System                               | 19497  | 105   | 11     |

|          | Early Stage Filter (ESF)                            | 502    | 0     | 0      |

| Extrax   | Address Translator Unit (ATU) including queue       | 1855   | 0     | 0      |

| Extrax   | Total Extrax                                        | 2357   | 0     | 0      |

|          | % Extrax over Baseline System                       | 12.09% | 0.00% | 0.00%  |

table 2: Synthesis result of the prototype system

open-source synthesizable core based on SPARC V8 architecture [54], has indeed very small size. Therefore, we claim that the area overhead of Extrax might be quite acceptable if deployed on the system with commercial CPU core such as Cortex-A9.

#### 3.6.2 Security Evaluation

To evaluate the security monitoring capability of our approach, we chose several well-known attack techniques that are employed in real-world rootkits [11] and implemented four rootkits that target either immutable regions or kernel mutable objects. Table 3 lists the rootkits, of which the specific target can be deduced by their names. The first two target immutable regions while the others, the LKM and *virtual file system* (VFS) hooking attacks

| Example Name |             | BaseWT   | BaseWB       | Ours-Extrax |  |

|--------------|-------------|----------|--------------|-------------|--|

| Immutable    | IDT Hooking | Detected | Detected     | Detected    |  |

| regions      | SCT Hooking | Detected | Detected     | Detected    |  |

| Mutable      | LKM Hiding  | Detected | Not detected | Detected    |  |

| objects      | VFS Hooking | Detected | Not detected | Detected    |  |

table 3: Rootkit detection result

target mutable objects that have invariant value sets. We also implemented monitoring software that runs on our verifier core to configure the peripheral units for monitoring, such as the snooper, ESF and ATU. The current address range registers of ESF is configured to capture memory accesses only on kernel mutable objects and other related data structures such as page tables for the objects. Memory events on immutable regions can be safely filtered out by ESF since, as mentioned before, snooping the system bus would be enough to catch attacks on immutable regions.

To demonstrate the effectiveness of Extrax, we injected the four rootkits into three system versions: (BaseWT) the baseline system with write-through caches as in [12], (BaseWB) the baseline system with write-back caches and (Ours-Extrax) our proposed system with Extrax. As seen in Table 3, the monitor in BaseWT could immediately detect all the rootkits since the host uses a write-through cache, thus immediately sending every write event onto the system bus. The monitor in BaseWB, however, was unable to detect attacks on kernel mutable objects because of the CIH effect. Ours-Extrax, on the contrary, could detect all the attacks (whether cache resident or not), thanks to our Extrax and CDI support.

Recent attackers tend to avoid launching attacks that are easily detectable like those on immutable regions. Instead, of more importance becomes the detection of attacks on mutable regions [25]. We have just seen that a snoop-based monitor deployed on the host core with a write-back cache is easily nullified when cache resident attacks are made on mutable objects. Therefore, we claim that Extrax can play a critical role in assisting such monitors, thereby increasing the security level of the systems.

#### 3.6.3 Performance Analysis

Since CDI does not introduce any performance impact on the host, the main factor which incurs the overhead is the traffic generated by ATU as a result of address translation. To measure the performance overhead, we chose seven applications from the *SPEC 2006 benchmark suites* [57], and implemented two versions of the host system: the baseline and the proposed full system with ESF turned off. The reason of turning ESF off is to strain the system with the excessive traffic generated by CDI.

Table 4 presents this worst-case performance overhead, which is around 3.24%. The reason for this low overhead might be explained in a way that even if there seem to be a number of memory events coming from CDI, the number of events that really need memory translation in ATU is relatively small because our ATU has TLB and most memory translation end up retrieving values from the TLB. We also conducted the same experiment, with ESF turned on, monitoring the mutable objects related to the VFS hooking and LKM hiding attacks. As seen in the table, there is virtually no overhead caused by Extrax because ESF filters out most memory events that do not access the monitored memory regions.

Since turning off ESF does not cause serious performance overhead of 3.24%, some might think that ESF is not essential. As explained before, however, its main goal is to reduce the amount of CRI delivered to ATU. Reduced number of memory events would not only help ATU decrease the number of events that need address translation (main memory access), but it would also drastically reduces the number of TLB accesses, which in turn

| Application | Baseline System | Proposed System with ESF turned-off | Proposed System with ESF turned-on |

|-------------|-----------------|-------------------------------------|------------------------------------|

| h264        | 10.46s          | 10.57s                              | 10.46s                             |

| bzip2       | 788.05s         | 813.62s                             | 788.05s                            |

| hmmer       | 39.96s          | 39.96s                              | 39.96s                             |

| libquantum  | 10.11s          | 10.11s                              | 10.11s                             |

| parser      | 1.41s           | 1.41s                               | 1.41s                              |

| omnetpp     | 969.1s          | 975.35s                             | 969.1s                             |

| xalan       | 3.43s           | 3.46s                               | 3.43s                              |

table 4: Performance overhead

might possibly save hugh amount of power consumed by ATU.

As a complementary experiment, the bandwidth of Extrax is shown in Table 5. This result is acquired by running the *STREAM* benchmarks [58] on our proposed system in order to obtain the worst-case bandwidth that can be produced by ATU, (meaning that no TLB hit occurs) meaning that it constantly requires page table walk and generates memory traffic on the system bus. Even in this unrealistically extreme case, the traffic placed on the system bus by ATU is relatively small compared to that of other components widely used and attached to the system bus of modern SoCs, indicating that the performance impact on the host system caused by Extrax should not be a serious concern.

| Component                                       | Bandwidth        |

|-------------------------------------------------|------------------|

| USB 2.0 HS (High-Speed)                         | ~ 480Mb/s        |

| H.264 Codec (Full HD, 16-bpp, 60fps)            | ≥ 1.85Gb/s       |

| Camera Input Processing (Full HD, 24-bpp, 60fps | $\geq 2.78$ Gb/s |

| CPU Security Extension (Running at 200MHz       | ~ 275Mb/s        |

table 5: Bandwidth comparison

#### 3.6.4 Power Consumption

To assess the power consumption of Extrax, we used Synopsys Design Compiler, Mentor Graphics ModelSim, and synthesized netlists of Snooper, ATU and ESF. Switching activity interchange format (SAIF) files were extracted from Modelsim with synthesized input test sequences that maximizes the power consumption of each component. Then the SAIF files and netlists were given as the input to Synopsys Design Compiler with a commercial 45 nm process library to estimate power consumption. The results are presented in Table 6 with other commodity processors as reference machines. As shown in the figure, Extrax consumes relatively small power as being compared to commodity processor cores in products ranging from low- to high-end computing devices.

#### 3.7 Limitation and Future Work

Our monitoring system could overcome the problem of previous snoopbased monitors by employing hardware security extension, Extrax, that provides the external monitor with CRI. Even though our scheme has made a progress in raising the security level that snoop-based monitors can provide, the snoop-based monitoring is still not at its full maturity. In this section, we

| Component   | ARM Cortex-A9<br>(Dual Core,<br>no L2) | ARM Cortex-A15<br>(Dual Core,<br>1MB L2) | SPARC V8<br>(Single Core,<br>256KB L2) | Snooper   | ATU       | ESF       |

|-------------|----------------------------------------|------------------------------------------|----------------------------------------|-----------|-----------|-----------|

| Process     | 40nm                                   | 30nm                                     | 45nm                                   | 45nm      | 45nm      | 45nm      |

| Power       | 0.5W (@ 800 MHz)                       | 3W                                       | 188mW                                  | 7.24mW    | 4.84mW    | 560.8uW   |

| Consumption | /1.9W (@ 2GHz)                         | (@ 1.7GHz)                               | (@200 MHz)                             | (@200MHz) | (@200MHz) | (@200MHz) |

table 6: Power consumption analysis

describe the limitations of our monitoring system.

Our prototype system is currently equipped with a total of 8 pairs of configuration registers, in both Snooper and ESF, to store the start/end addresses of monitored regions. Although we can increase the exact number of registers for the systems that allows it, we cannot say that it is always possible to store all the address pairs. In such a case, we can set a pair of registers to represent a memory region that include more than one regions that we have to watch. This allows us to monitor more than one regions with a pair of registers, since we still do not miss any access to the memory regions. Since this loosely set monitoring region would produce unnecessary memory events, Monitor software should perform extra work to drop these events. Our future work includes the investigation of trade-offs between the number of registers, hardware size, and the performance overhead caused by additional workload of Monitor Processor.

Our current system does not assume a type of attacks that target page tables, such that a rootkit manipulates the page table to allocate new physical pages, copy over the content of the physical pages that are being monitored, and change the mapping to the new physical pages. However, we claim that Extrax can detect them with slight modification that enables monitoring both virtual and physical addresses simultaneously. Even though the attack mentioned above changes the content of page table so that the virtual address can point to the different physical address, it still uses the same virtual address. Therefore, the augmented Extrax will be able to detect such type of attacks.

In this work, DoS attack by attackers who are aware of the existence

and internals of Extrax is not considered. Such DoS attacks might be possible if attackers delicately craft their attacks to satisfy the following criteria. First, attacks should consist of consecutive memory writes. Second, the target addresses of the events should have the same 12-bit page-offset to that of the address monitored by ESF in order for the events to be delivered to the queue placed in between ESF and ATU. Third, the remaining 20-bit in each target address is different from each other to avoid TLB hit. Since the current Extrax is designed to drop events when the queue is full (even though, with the current setting, the queue never became full in our experiment), attackers might be able to conceal their trail by placing malicious write events among the benign consecutive write events that satisfy the above criteria. However, we claim that detection of such attack is not impossible because, as described above, the memory access behavior of the attack is quite restricted and have certain patterns. Therefore, Extrax could be augmented to detect this type of patterns and notify the monitor so as to log the incident for later inspection.

Our system does not assume attacks that Bahram et. al proposed in [53]. In their work, the attack named DKSM is introduced to show the vulnerability of virtual machine introspection tools. Since the attacks basically exploit the semantic gap between the external monitor and the host system, our monitoring system is also vulnerable to such attacks. However, such a vulnerability is not our monitoring system's own weakness, but is an innate weakness of all external monitors. One possible way to overcome the issue is to employ in-host agent [53, 59] that can deliver useful information to external monitors to bridge the semantic gap.

In the current work, we do not consider attacks that are performed by

tampering with only processor registers. Even though devising such attacks, which leave the evidence only in registers but not in memory, caches or system bus, might seem to be quite difficult, it is theoritically possible. The most conceivable attack is to change the content of a special register such as TTBR of ARM or CR3 of x86 architecture [60, 61] to modify the base address of *page global directory (PGD)*. If such an attack is successfully launched, our monitor has no way to figure out the exact location of the page tables that the processes is really using. Since ATU of Extrax rely on the integrity of the exact location of the page tables, the attack would nullify Extrax. Our future works include a development of a mechanism that can safely deliver the content in registers to the outside the host.

Even though our current prototype is implemented with a rather old-fashioned processor and old linux version, but the implementation is not restricted to the technology or specific linux version because the purpose of our work is to show readers the proof of concept of our system. Currently, we are migrating this prototype system to the platform on which ARM Cortex series is used as the host processor.

#### 3.8 Conclusion

In this work, we proposed to reuse the CDI feature readily available for debugging in modern CPU cores in an effort to elevate the effectiveness of existing snoop-based monitors. We first discussed several implementation complications involved in the transfer of CDI signals for snoop-based monitors located outside the host CPU. Then we suggested Extrax which

is an ASIC module plugged into CDI in order to convey the host internal information from CDI to the external monitor. For precise and efficient monitoring, the module performs the tasks of address translations and filtering out benign memory write events. To validate our proposed design, we have implemented a prototype on FPGA, and evaluated the security capabilities in addition to the performance, power and area overhead. Empirical results showed that our monitor, regardless of the type of caches, successfully detect all our rootkit samples, which the previous monitoring systems often failed to catch owing to CIH effect, with modest area and power overhead increase along with virtually no host performance overhead.

## **Chapter 4**

# Monitoring Dynamic Information Flow using Control-Flow/Data-Flow Information

#### 4.1 Introduction

DIFT detects a variety of malicious system behaviors that intend to compromise computer systems or leak sensitive information [22]. Generally, DIFT sets up rules to tag (or taint) internal data of interest and keeps track of the taintness of their tags throughout the system [31]. At run time, every data derived from the one with tainted tag has its tag tainted. An alarm will be triggered as soon as any of the tainted data involves in potentially illegal activities, such as pointing inside the prohibited code or being included in a data stream on the output channels. DIFT does not depend on static patterns or signatures of attackers but on their dynamic behaviors at run time. So, it is effective to defend against new attacks whose patterns are not known yet, and to block any unsafe operations on sensitive data even if the data is encrypted [16].

DIFT has been implemented in various forms of either software or

hardware. Most software approaches add instrumented code into the original application to track the propagation of tainted data [16, 22]. The key advantage is that they can perform DIFT simply by programming their algorithms. Not surprisingly, however, they show too large computing overhead to be deployed in practice. Even after much effort [16, 17], the overhead still remains one or two orders of magnitude higher than that of hardware approaches [18, 19] in which extra hardware for DIFT operations is designed and integrated into an existing processor for acceleration. The hardware typically consists of logic blocks that monitor the execution of each instruction in the processor and keep track of tag information flowing from the execution unit at every cycle.

Unfortunately, the remarkable speed of hardware DIFT comes at a cost. To maximize the performance, the hardware has been tightly integrated inside the processor. However, such integration mandates major modifications to processor internal components such as registers and pipeline datapaths, thus substantially increasing the time and cost for re-manufacturing existing processor core architecture [31]. As alternatives to mitigate this problem, there have been more recent studies [31, 20, 21] that propose the techniques aiming to minimize the change to the processor core internal. In their approaches, the host processor can concentrate on the execution of its own code while the time-consuming tag propagation work for DIFT is offloaded to the DIFT hardware device outside the processor. In the literature, they empirically demonstrated that DIFT can be carried out in a great speed by external hardware, relieving significant burden for DIFT computation from the host. However, there still remains a great challenge to overcome for the success

of these approaches. The challenge originates from the limited ability of an external device to monitor every internal state change dynamically made by the code running on the host. For precise DIFT, the external monitor should be able to receive from the host virtually all essential runtime information including branch targets, memory addresses and register moves, which will incur a tremendous amount of traffic for communication between the two devices. In [21, 20], they report that the communication overhead may account for up to 30% of the total execution time even after all their optimizations through hardware communication buffers and special instructions. In [31], this overhead issue was treated more aggressively by modifying the host architecture in a way that a customized interface can be embedded into the processor pipelines. Through this interface, their external device was able to have a special connection for extracting any runtime information for DIFT computation directly from the internal pipelines with very little overhead.

In this chapter, we introduce our recent work on building a hardware DIFT engine. Our approach is similar to those in [21, 20, 31] in that our engine is also connected externally to the host processor. But looking at the details, ours is different from them in several aspects. One main difference is that our approach does not modify internally the host architecture to provide a DIFT-customized interface or connection for the external engine. In our system, the engine is connected to the processor via CDI.