#### 공학박사학위논문

# CPU/GPU 이종 병렬 플랫폼을 위한 GPU-in-the-loop 시뮬레이션 기법 GPU-in-the-loop Simulation for CPU/GPU Heterogeneous Platform

2016년 2월

서울대학교 대학원

전기컴퓨터 공학부

고영섭

## Abstract

A mobile GPU has been widely adopted in most embedded systems to handle the complex graphics computations required in modern 3D games and highly interactive UI (User Interface). Moreover, as mobile GPUs are gaining more computation power and becoming increasingly programmable, they are also used to accelerate general-purpose computations in various fields such as physics and math, and so on. Unlike server GPUs, mobile GPUs usually have fewer cores since a limited amount of power is available in a battery. Thus, it is important to efficiently utilize both CPUs and GPUs in mobile platforms to satisfy the performance and power constraints.

For design space exploration of such a CPU-GPU heterogeneous architecture or debugging the SW in the early design stage, a full system simulator is typically used, in which simulation models of all HW components in the target system is included. Unfortunately, building a full system simulator with GPU simulator is not always possible because there is no available GPU simulator, or if any, it is prohibitively slow since they are mainly developed for architecture exploration varying the internal micro-architecture of GPUs.

To solve these problems, this thesis proposes a GPU-in-the-loop (GIL) simulation technique that integrates a real GPU with a full system simulator for CPU/GPU heterogeneous platforms.

In the first part of this thesis, we propose a system call-level simulation technique in which a full system simulator interacts with a GPU board at system call level. Since the shared on-chip memory in the target system is modeled by two separate memories in the simulator and the board, memory synchronization is the most challenging problem in the proposed technique. To handle this problem in the system call-level technique, address translation tables are maintained for the shared memory regions and these memory regions are synchronized whenever the system calls which trigger the GPU execution are invoked in the board. To model the GPU execution in the simulator, interrupt-based modeling technique is proposed, in which the GPU interrupt is generated in consideration of the GPU execution time obtained from the real board.

In the second part of this thesis, we propose an API-level simulation technique in which a simulator and a board interact with each other at API level. Since the device driver in the original software stack makes it difficult to support various GPUs, a synthetic library is defined and it replaces the GPU library in the original software stack in order to ensure that the device driver is not used. To model timing of the API execution in the simulator, the sleep function is called in the synthetic driver so that the measured API time in the board elapses in the simulated time.

From the existing GPU APIs, we propose API-level simulation techniques for three commonly used APIs which are OpenCL, CUDA and OpenGL ES. And several challenging problems such as asynchronous behavior, multi-process support and memory synchronization for complex data structures are properly handled by several methods for correct simulation.

From the experimental results, we can confirm that the proposed technique can

provide fast simulation speed with a reasonable timing accuracy. Therefore, it can be used not only for SW development but also for system level performance estimation. Moreover, the proposed technique makes the full system simulation for CPU/GPU heterogeneous platforms feasible even if a GPU simulator is not available.

*Keywords* : CPU/GPU heterogeneous platform, GPU Simulation, Virtual prototyping system, GPU-in-the-loop simulation, System call, API

Student Number : 2009-20750

# Contents

| Abstract.   | i                                          |

|-------------|--------------------------------------------|

| Contents    | iv                                         |

| List of Fig | guresvii                                   |

| List of Ta  | blesx                                      |

| Chapter 1   | Introduction1                              |

| 1.1         | Motivation                                 |

| 1.2         | Contribution                               |

| 1.3         | Thesis Organization                        |

| Chapter 2   | Related Works                              |

| 2.1         | Acceleration techniques for GPU simulation |

|             | 2.1.1 Parallel Simulation                  |

|             | 2.1.2 Sampled Simulation                   |

|             | 2.1.3 Statistical Simulation               |

|             | 2.1.4 HW-accelerated Simulation            |

| 2.2         | CPU/GPU Simulation framework               |

| 2.3         | Summary                                    |

| Chapter 3   | GPU-in-the-loop Simulation                 |

| 3.1         | Basic Idea                                 |

| 3.2         | Different levels of CPU/GPU Interaction    |

| 3.3         | Detection Mechanism                        |

| ,    | 3.4    | Memory Coherency Problem                                       | . 23 |

|------|--------|----------------------------------------------------------------|------|

| ,    | 3.5    | Overall GIL simulation flow                                    | . 23 |

| Chap | oter 4 | System call- level GIL Simulation                              | .26  |

| 2    | 4.1    | Target System                                                  | . 26 |

|      |        | 4.1.1 Typical Execution Scenario of the Systems                | . 27 |

| 4    | 4.2    | Memory Synchronization                                         | . 29 |

|      |        | 4.2.1 Address Translation Table                                | . 30 |

| 4    | 4.3    | Timing Modeling                                                | . 32 |

|      |        | 4.3.1 Interrupt Modeling                                       | . 33 |

|      |        | 4.3.2 Regression based timing correction for GPU time          | . 34 |

|      |        | 4.3.3 An Example of System-level GIL Simulation Scenario       | . 35 |

| 4    | 4.4    | Experiments                                                    | . 37 |

|      |        | 4.4.1 Parallelization for diff operation                       | . 37 |

|      |        | 4.4.2 Simulation Time Analysis                                 | . 39 |

|      |        | 4.4.3 Contention overhead in Pixel Processors (PP)             | . 40 |

|      |        | 4.4.4 Internal System Behavior Profiling                       | . 41 |

|      |        | 4.4.5 Accuracy Evaluation                                      | . 42 |

| 4    | 4.5    | Summary                                                        | . 43 |

| Chap | oter 5 | API-Level GIL Simulation                                       | . 44 |

|      | 5.1    | Differences between API-level and System call-level techniques | 45   |

|      |        | 5.1.1 Synthetic Library                                        | . 47 |

| :    | 5.2    | Timing Modeling                                                | . 49 |

|      |        | 5.2.1 Regression-based compensation for timing error           | . 51 |

| 5.3      | Memory Synchronization                          |    |

|----------|-------------------------------------------------|----|

| 5.4      | GPGPU API (CUDA & OpenCL) Implementation Case   | 55 |

|          | 5.4.1 Asynchronous Behavior Modeling            | 55 |

|          | 5.4.2 Implementation Issues                     |    |

|          | 5.4.3 Experiments                               | 61 |

|          | 5.4.4 Simulation Overhead                       |    |

| 5.5      | OpenGL ES Implementation Case                   |    |

|          | 5.5.1 Background                                | 69 |

|          | 5.5.2 Additional modification for SW stack      | 71 |

|          | 5.5.3 Memory synchronization                    |    |

|          | 5.5.4 Multi-Process Support                     | 77 |

|          | 5.5.5 High-level Timing Modeling for other GPUs |    |

|          | 5.5.6 Porting To a New GPU Board                |    |

|          | 5.5.7 Experiments                               |    |

| 5.6      | Summary                                         |    |

| Chapter  | 6 Conclusion and Future Work                    | 94 |

| Bibliogr | aphy                                            |    |

# **List of Figures**

| Figure 1-1. Simulation performance comparison results from [22] and [26]             |

|--------------------------------------------------------------------------------------|

| Figure 3-1. The overall GIL simulation framework                                     |

| Figure 3-2. Typical GPU execution scenario                                           |

| Figure 3-3. Extension for CPU simulator and detection code in the host interface. 22 |

| Figure 3-4. Simulation flow between host/board interfaces                            |

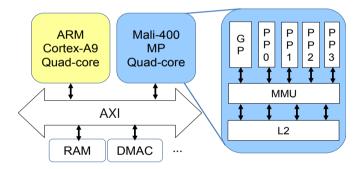

| Figure 4-1. CPU/GPU heterogeneous system that integrates an ARM CPU and a Mali       |

| 400 GPU: a GPU core represented as PP stands for Pixel Processor, and as GP          |

| for Geometry Processor                                                               |

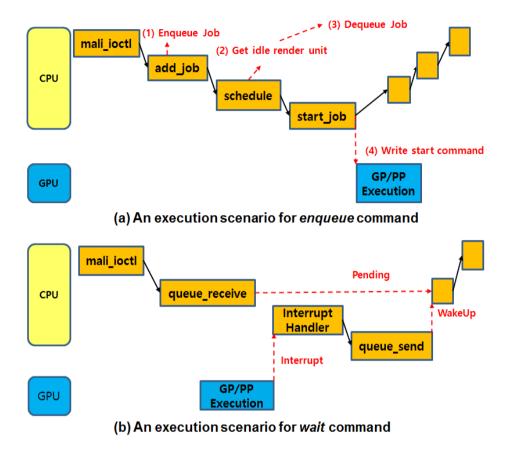

| Figure 4-2. Typical execution scenarios on a CPU/GPU system with the Linux kernel    |

|                                                                                      |

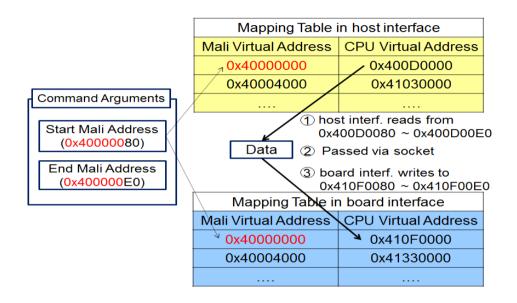

| Figure 4-3. Address translation table to match the same memory region                |

| Figure 4-4. Typical execution scenario on the target platform                        |

| Figure 4-5. An example of the HIL simulation sequence with the scenario shown in     |

| Figure 4-2                                                                           |

| Figure 4-6. The execution time for <i>diff</i> operation for sequential and parallel |

| implementations                                                                      |

| Figure 4-7. Simulation time (sec) for two benchmarks                                 |

| Figure 4-8. Execution time distribution for PPs                                      |

| Figure 5-1. Modified SW stack in API-level GIL simulation                            |

| Figure 5-2. An example code of the synthetic library for <i>cudaMemcpy</i> API47      |

|---------------------------------------------------------------------------------------|

| Figure 5-3. Synthetic driver code used in GIL simulation                              |

| Figure 5-4. Two ways to share data between CPU and GPU in GPU applications . 52       |

| Figure 5-5. Synthetic Library code for <i>gpuMap</i> API                              |

| Figure 5-6. Real execution scenario for the synchronization API                       |

| Figure 5-7. Simulation scenario for Figure 5-6                                        |

| Figure 5-8. Original (a) and modified (b) CUDA code                                   |

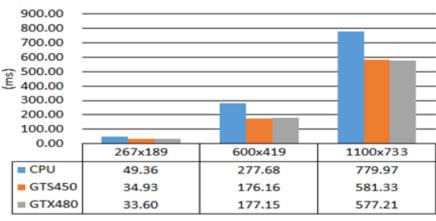

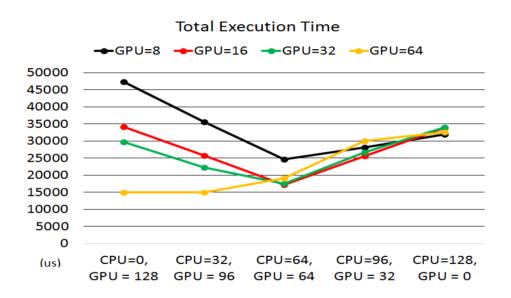

| Figure 5-9. The execution times of the two applications (CUDA, OpenCL)                |

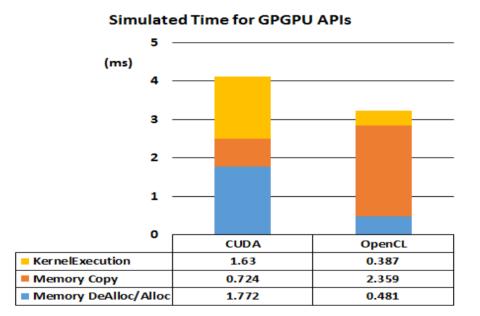

| Figure 5-10. Simulated time for GPGPU API (267x189)                                   |

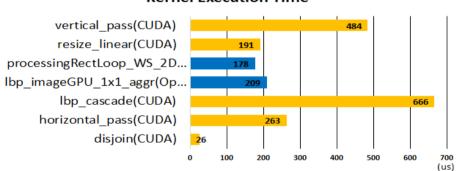

| Figure 5-11. The execution time of kernel executed for the face detection application |

| (267x189)                                                                             |

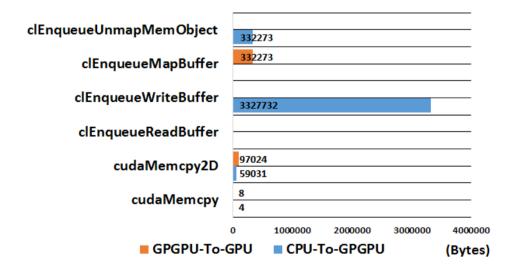

| Figure 5-12. Communication overhead for memory APIs (267x189)                         |

| Figure 5-13. The execution time for the matrix multiplication varying the number 67   |

| Figure 5-14. Simulation time composition in the GIL simulation                        |

| Figure 5-15. Overview for Android Graphics                                            |

| Figure 5-16. Modification for Software stack in OpenGL ES API                         |

| Figure 5-17. Code extension for the native window in synthetic library73              |

| Figure 5-18. Modified code for <i>gralloc</i> module                                  |

| Figure 5-19. Multi-thread structure for Board Interface in OpenGL ES API GIL          |

| simulation77                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------|

| Figure 5-20. Rendering times for three benchmarks with three boards                                                    |

| Figure 5-21. Accuracy results for three benchmarks with three boards                                                   |

| Figure 5-22. Linear regression analysis result for two benchmarks                                                      |

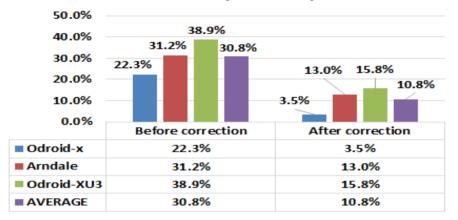

| Figure 5-23. The error ratio before and after the correction factor is applied                                         |

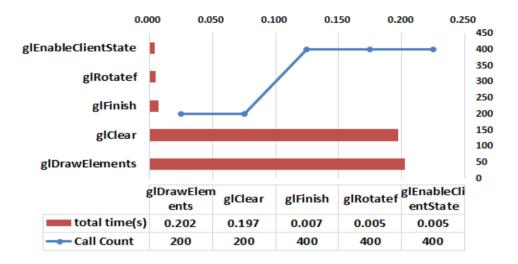

| Figure 5-24. The total execution time and the call count for each API                                                  |

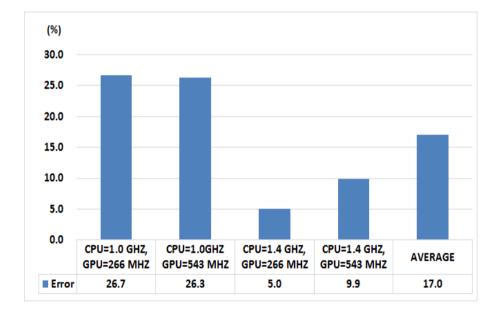

| Figure 5-25. The error ratio for Lesson16 benchmark with 4 combinations of CPU/GPU frequencies on the Odroid-XU3 board |

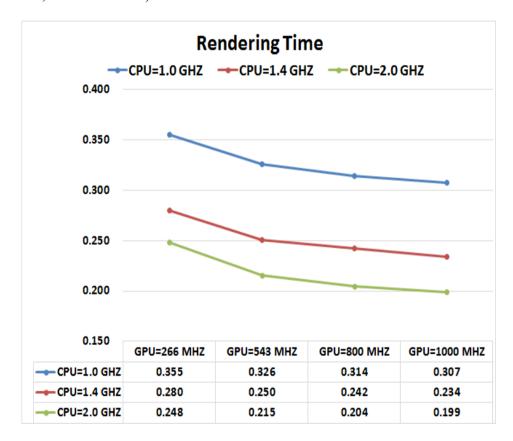

| Figure 5-26. The rendering time for Lesson16 benchmark on the odroid-xu3 board                                         |

| varying CPU/GPU frequencies                                                                                            |

## **List of Tables**

| Table 2-1. Comparison of the acceleration techniques for GPU simulation | 16 |

|-------------------------------------------------------------------------|----|

| Table 2-2. Comparison of CPU/GPU simulation frameworks                  | 17 |

| Table 4-1. GPU response time for Cubic app                              | 42 |

| Table 4-2. GPU execution time and utilization for Cubic app             | 42 |

| Table 4-3. Accuracy evaluation for the Android apps                     | 42 |

| Table 5-1. Common structure (common_s)                                  | 48 |

| Table 5-2. API-specific structure for cudaMemcpy API (cuda_memcpy_s)    | 48 |

# **Chapter 1** Introduction

### **1.1 Motivation**

With ever increasing demand for computation in the embedded systems, a mobile GPU has become an essential component in most embedded systems. We can easily find many SoCs that integrate both a CPU and a GPU: Tegra from NVIDIA, Snapdragon from Qualcomm, and Exynos from Samsung, to name a few. These chips are widely used on many platforms ranging from automobiles to high-performance smart phones and tablet PCs. Since low power consumption is the major design constraint in most computer systems these days, the trend towards CPU/GPU heterogeneous platforms will continue, also with the increasing number of cores in CPUs and GPUs.

To design such a CPU/GPU heterogeneous platform efficiently, it is crucial to profile the target applications and utilize both a CPU and GPU better by identifying the performance bottleneck and capturing the dynamic system behaviors between CPU and GPU. There exist many profiling tools [1][2][3], where a predefined set of hardware performance counters is collected and displayed to the designer to provide an overview of performance. However, this approach is only applicable to the exiting target platforms.

For the target platform under design, a virtual prototype is commonly used for performance estimation. Especially, full system simulation is performed in virtual prototypes since complete software stacks can run without modification by modeling all components of the target system including processors (CPUs, GPUs), memory, interconnections as well as peripherals. Generally, full system simulation is used for early software development or system-level DSE (Design Space Exploration) in early design stage. In these purposes, since SW implementation is modified frequently and lots of design candidates are verified, a large number of simulations are performed repetitively and fast simulation is really important. Moreover, as the complexity of the embedded system is increased greatly, much more HW components are integrated in a single system and the importance of the fast simulation is even more highlighted.

Upon the current move toward CPU/GPU heterogeneous platforms, many researches have been performed to simulate these platforms by integrating a CPU simulator with a GPU simulator. However, in this approach, there are some problems due to the existing GPU simulators. Since most of the existing GPU simulators [4][5][6][7][10][11] are mainly developed for architecture exploration varying the internal micro-architecture of GPUs, GPUs are modeled accurately in

cycle-level, but the simulation speed is prohibitively slow. In previous researches [22][26], they present some experimental results for the simulation speed of some GPU simulators [6][11].

| Application          | Native GPU execution time (ms) | Simulation time (ms) | Slowdown |

|----------------------|--------------------------------|----------------------|----------|

| matrixmul            | 0.128                          | 30578                | 177784   |

| MersenneTwister      | 11                             | 7511800              | 682891   |

| scan                 | 0.337                          | 253300               | 751632   |

| QuasirandomGenerator | 1.33                           | 2766411              | 2080009  |

| MonteCarlo           | 2.59                           | 4213485              | 1646536  |

| clock                | 0.037                          | 6491                 | 175432   |

| scalarProd           | 0.177                          | 94022                | 531201   |

| BlackScholes         | 0.749                          | 1574676              | 2102372  |

| Time       | NB    | SP    | SSSP | PTA  | TSP  | DMR  | MM    |

|------------|-------|-------|------|------|------|------|-------|

| GPU        | 28557 | 18779 | 7067 | 4485 | 4456 | 3391 | 881   |

| (msec)     |       |       |      |      |      |      |       |

| Simulation | 3.78  | 2.48  | 6.54 | 4.15 | 4.13 | 3.14 | 19.58 |

|            | weeks | weeks | days | days | days | days | hours |

| Figure 1- | <ol> <li>Simulat</li> </ol> | ion performance | e comparison resu | lts from | [22] | and | [26] |  |

|-----------|-----------------------------|-----------------|-------------------|----------|------|-----|------|--|

|-----------|-----------------------------|-----------------|-------------------|----------|------|-----|------|--|

From the results shown in Figure 1-1, the slowdown is around  $170,000x \sim 2,000,000x$  for GPGPU-Sim [6] and 80,000x for MacSim [11] compared with native execution, which means that it takes more than a day to simulate a GPU for 1 second. However, this is not acceptable speed for early SW development or system-level DSE (Design Space Exploration) since a large number of simulations are repeated for these objectives. Moreover, for some mobile GPUs such as Mali and PowerVR, there is no publicly available simulator. Thus, it is impossible to

build a full system simulator for the target platforms consisting of these GPUs.

To deal with these problems, we propose GPU-in-the-loop simulation technique that integrates a real GPU and a CPU simulator for fast simulation. The full system simulator and a GPU board can interact with each other at three different levels; API (Application Programming Interface), system call, and register/memory access. From them, two interactions at the system call and the API is covered in this thesis.

There are two major challenges in the proposed technique. First, since the on-chip shared memory in the target system is modeled with the two separate memories in the simulator and the board, we must synchronize the duplicated shared memory models to maintain the coherence. Second, since the detailed behavior of the GPU cannot be observed in the board, it is not easy to model the timing of the GPU in the proposed technique. To handle these problems, several methods for memory synchronization and timing modeling are proposed for each interfacing mechanism.

## **1.2** Contribution

The contribution of this thesis can be summarized as follows.

- We propose a GPU-in-the-loop (GIL) simulation technique that integrates an existent GPU hardware with a full system simulator.

- A. Unlike previous works, since real GPU HW is used instead of slow

GPU simulators, the full system simulation becomes fast enough for early software development in the early stage with sacrificing some timing accuracy.

- B. Moreover, it make the full system simulation feasible for CPU/GPU heterogeneous platforms even if a GPU simulator is not available for the target platforms.

- 2) As well as the simulation speed is increased in the proposed technique, approximate timing of GPU can be modeled by novel modeling techniques

- A. The proposed technique can be used to estimate the performance for system level design space exploration such as task partitioning problem between CPUs and GPUs

- The proposed interfacing mechanisms can also be applied in integrating a HW other than GPU with a full system simulator

## **1.3** Thesis Organization

This thesis is organized as follows. In Chapter 2, the representative previous researches on acceleration technique for GPU simulation and CPU/GPU simulation frameworks are reviewed. Chapter 3 explains the basic idea of the "GPU-in-the-loop" simulation technique and overall simulation flow will be briefly explained in this chapter. In Chapter 4 and Chapter 5, two simulation interface mechanisms, system call-level and API-level, are explained. Finally, we draw the conclusion and address future work in Chapter 6.

# **Chapter 2** Related Works

# 2.1 Acceleration techniques for GPU simulation

Since GPUs have become an important component in many platforms ranging from mobile devices to desktop PCs, the research interest in the GPU architecture is increasing and several GPU simulators are developed for the research purpose. For the architecture research, since micro-architecture of GPUs should be modeled accurately, current GPU simulators are really slow as mentioned in Chapter 1. To accelerate the slow GPU simulators, various techniques are proposed and they can be categorized into four approaches: parallel simulation, sampled simulation, statistical simulation and HW-accelerated simulation. In this chapter, we review the some exiting acceleration techniques for GPU simulations in these approaches.

#### 2.1.1 Parallel Simulation

To accelerate the simulation for the many-core architectures, several parallel simulation frameworks have been proposed such as HSim [20] and Graphite [21], in which the simulation work for each processor is partitioned into multiple threads and performed in parallel on multi-core CPUs or multi-host machines. Since there are a large number of cores in a GPU, parallel simulation technique might be a viable solutions to accelerate the GPU simulation and several researches are proposed recently [22][23].

In [22], they proposed the work-group parallel simulation technique. Among the internal components in a GPU, the simulation for Computing Units (CU) are parallelized by multiple simulation threads; A CU corresponds to a Stream Multiprocessor (SM) in Nvidia GPU and a Data Parallel Processor (DPP) array in AMD GPU where several cores are executed in a SIMD manner. And, the other components such as a work control unit, interconnection networks and memory sub systems are simulated by two separate threads: Work distribution and control (WDC) and Interconnect-memory subsystem (IMS) threads. Since the lock-step synchronization method suffers from the synchronization overhead, they proposed the work-group based synchronization method in which synchronization is performed at the end of work-group execution on a CU to keep the same work-group distribution in the single-threaded simulation as much as possible. To improve the accuracy of the simulation for interconnection networks and memory

sub systems, two additional synchronization mechanisms are applied to maintain the memory request order and model the contention in the interconnection network and the memory system more accurately.

Since the CU threads and the IMS thread are simulated independently in [22], the global memory request sequence can be different with that in the single-threaded simulation and this incurs the simulation error. To address this problem, error predictive synchronization (EPS) is proposed in [23] as an extended work for [22]. In this synchronization method, the instruction history is recorded within a specific cycle range to count the number of memory instructions executed in a CU. And, if the total memory instruction count for all CUs is larger than a given threshold, the parallel simulation is disabled and the simulation is performed sequentially until the total memory instruction count is below the threshold to reduce the memory latency error.

#### 2.1.2 Sampled Simulation

Sampling is a well-known technique to speed up architecture simulation of long-running workloads by simulating only a small but representative portion of the application in detail while maintaining the accuracy. Several sampling techniques for single-threaded and multi-threaded CPU applications are proposed so far [24][25], they cannot be directly applied to GPU simulation, since it may lead to

large sampling sizes and need to re-profile the target platform when the simulated configuration is changed.

In TBPoint [26], they proposed a new profile-based sampling technique for GPU simulation. For the hardware independency, it uses GPUOcelot [29] profile tool to collect the information about each thread block. Using the profiled information, it designs feature vectors for each kernel and thread blocks, then they are used for inter-launch sampling and intra-launch sampling technique to reduce simulation time. In inter-launch sampling, the kernels are clustered based on the kernel feature vectors and only the kernel selected as a simulation point is simulated by a detailed simulator such as MacSim [11] and other kernels in the same cluster re-use the IPC of the simulated kernel without the simulation. In intra-launch sampling, the thread blocks are clustered based on stall probability and region ID is assigned to each cluster. During the simulation, the homogeneous regions are identified when the region IDs for all concurrently running thread blocks are same. Then, the simulation is skipped just using the sampled IPC until the one of the region ID for concurrent thread blocks differs from others. Since the proposed technique leverages the regular execution behaviors in GPGPU kernels, GPGPU kernels with irregular execution pattern can incur high sampling size and the slow simulation is still a problem.

#### 2.1.3 Statistical Simulation

In a statistical simulation, it measures a well-chosen set of program characteristics during GPGPU execution and generates a small synthetic benchmark with those characteristics. Then, the architecture simulation is performed using the small benchmarks. In [27], to keep the original characteristic, it first profiles the original GPGPU workloads through a fast functional simulator and the characteristics such as thread hierarchy, instruction mix, control flow and memory access pattern are collected. Then, loop patterns of the GPGPU kernel are analyzed based on the Divergence Flow Statistics Graph (DFSG) and the synthetic benchmark is generated by reducing the iteration counts of loops while maintaining the original characteristics. Since it requires some loops to increase the simulation speed, speed-up is limited for GPGPU kernels with small loop counts and a large number of thread blocks.

#### 2.1.4 HW-accelerated Simulation

In software-based parallel simulation, due to the synchronization overhead, only coarse-grained parallelism can be exploited and the speed-up is limited. However, in a FPGA, since the cycle-level synchronization is much faster than SW implementation, fine-grained parallelism can be exploited. Thus, the simulation work performed sequentially in software-based parallel simulation can be done in parallel on the FPGA to further reduce the simulation speed.

In FastLanes [28], since modern GPUs are too complex to fit into even the largest single-chip FPGA, only a smaller number of multi-processors in the target GPU is implemented on the FPGA and they are re-used to simulate all multi-processors in a time-division multiplexing manner. Since only small number of threads are simulated on FPGA at a given moment, the contexts of the threads which are swapped out from the FPGA should be reserved in off-chip- memory. Since this incurs non-negligible performance overhead, the duration of a time slice is determined by an analytical performance model to balance the simulation speed and accuracy. The FPGA-based acceleration technique can provide fast simulation speed enough for full system simulation. However, it requires significant effort to develop since the simulator should written in a hardware description language (HDL) such as Verilog or VHDL.

## 2.2 CPU/GPU Simulation framework

To simulate the CPU/GPU heterogeneous platforms, a common practice is to integrate a GPU simulator with a CPU simulator. In [10][11][12], application-only simulators are implemented to simulate the GPGPU applications, in which only applications are simulated and OS services such as system calls are emulated by the

simulation host. In FusionSim [12], several existing simulators (PTLSim [35], GPGPU-Sim [6] and MARSSx86 [36]) are integrated and two kinds of CPU/GPU systems (fused and discrete system) are modeled. In Multi2Sim [10], the functional simulator and the architecture simulator (timing model) are decoupled and the instruction traces obtained from the functional simulator are feed to the architecture simulator to accurately model the latencies of the instructions. In MacSim [11], only the trace-driven architecture simulator is implemented and the trace generators such as (Pin [34] and GPUOcelot [29]) are used to generate the CPU and GPU traces for the architecture simulator. And the OS is modeled in the process manager considering process and thread scheduling.

Since the significant errors can be introduced if the OS effect is not modeled [37], several researches are conducted based on the full system simulator such as gem5 [8], QEMU [9] and MARSSx86 [36]. In [13][14], they integrate the gem5 simulator with GPGPU-Sim by providing a common memory interface for both simulators. In SCHP [13], each process is created for gem5 and GPGPU-Sim respectively and the overall simulation is performed in lockstep. In order to ensure that both simulators are running in lock-step, the shared memory region is defined for inter-process-communication (IPC) and gem5 triggers the simulation of GPGPU-SIM by setting a flag in the shared memory and blocks until GPGPU-Sim completes the execution of a GPU cycle and the flags is reset. Also, since the memory system is modeled in the gem5, the memory requests from the GPGPU-SIM are stored in the shared memory to be handled in the gem5 simulator.

Unlike SCHP, gem5-gpu [14] combines two simulator as one process by integrating GPGPU-Sim's CU model into gem5.

Since the exiting CPU/GPU simulation frameworks only consider GPGPU applications written with CUDA or OpenCL, several full system simulation frameworks are developed to simulate the graphics applications [15][16][17][18]. In [15], it integrates the gem5 with ATTILA simulator [4] and can support Multi-CPU and Multi-GPU heterogeneous architecture.

In other CPU/GPU simulation frameworks [16][17][18], since fast simulation is really important and their concern is not in the CPU, QEMU full system simulator is used since it can achieve fast simulation based on dynamic binary translation. In [16], to verify the software and hardware architecture for multi-view GPU in the early design stage, QEMU simulator is integrated with multi-view GPU model implemented in SystemC or RTL codes. Since the unimportant HW components are simulated quickly with the QEMU simulator and only the important part is simulated in detail with SystemC model, the co-design for hardware and software can be performed efficiently. In [18], it develops cycle-accurate GPU simulators which can models two types of micro-architectures in modern GPUs such as Tile-Based Renderer (TBDR) and Immediate-Mode Rendering (IMR). Also, it provides a power model for a GPU using McPAT [19] to analyze energy consumption in GPUs. In [17], the full system simulator for many-core heterogeneous SoCs is developed using GPU and QEMU semi-hosting [46]. Though this work targets the many-core accelerator not a typical GPU, the

14

semi-hosting interface mechanism proposed in this work can be used to integrate the QEMU simulator with a GPU simulator such as GPGPU-Sim.

#### 2.3 Summary

Table 2-1 shows the comparison result of the acceleration techniques for GPU simulation. From the result, they shows remarkable speed-up results in comparison with original GPU simulators with some reasonable errors. However, there some limitations for each approach and these approaches are only applicable when GPU simulators are available. But, the proposed technique can perform the full system simulation even if GPU simulators are not available.

Table 2-2 shows the comparison result of existing CPU/GPU simulation frameworks. They are classified based on three criteria: GPU functionality, simulation scope, and simulation detail. Since the accurate but slow GPU simulators are used in exiting CPU/GPU simulation frameworks, they will suffers from slow simulation speed and they are not suitable for SW development or System-level DSE purposes.

| Pro                                                    | FPG,                                  | Stat                                                      | Prot                                                                                                          | Pa                                                                         |                              |

|--------------------------------------------------------|---------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------|

| Proposed Technique                                     | FPGA-based Simulation<br>[28]         | Statistical Simulation<br>[27]                            | Profile based Sampled<br>Simulation<br>[26]                                                                   | Parallel Simulation<br>[22]                                                | Acceleration<br>Technique    |

| No sii                                                 | GPGPU-Sim                             | GPGPU-Sim                                                 | Mac-Sim                                                                                                       | GPGPU-Sim                                                                  | Baseline<br>GPU<br>Simulator |

| No simulator                                           | about 100x<br>(2 orders<br>magnitude) | $1x \sim 589x$                                            | $2x \sim 50x$                                                                                                 | Up to 4.15x<br>on quad-core                                                | Speed-up                     |

| Functionally<br>Correct                                | Functionally<br>Correct               | No<br>Functionality                                       | No<br>Functionality                                                                                           | Functionally<br>Correct                                                    | Functional<br>Correctness    |

| Up to 20%<br>(Total<br>Execution<br>Time)              | No<br>Information                     | Up to 16 %<br>(Total IPC)                                 | Up to 14.0 %<br>(Total IPC)                                                                                   | 0.05 ~<br>26.61 %<br>(Total Cycle)                                         | Timing<br>Accuracy<br>(%)    |

| Only model the CPU/GPU<br>platforms with existing GPUs | Hard to implement the simulator       | Speed-up is limited for kernels<br>with short loop counts | The sample size can be up to<br>50% of total instructions for<br>kernels with irregular<br>execution patterns | The speed-up is limited by the<br># of CPU cores in the<br>simulation host | Limitations                  |

Table 2-1. Comparison of the acceleration techniques for GPU

simulation

| Existing      | GPU Func. | Full System/ | Functional    | Timing     | Accuracy      |

|---------------|-----------|--------------|---------------|------------|---------------|

| Researches    |           | App. Only    | Correctness   | CPU        | GPU           |

| MacSim        | GPGPU     | Application  | No            | Cycle-Acc. | Cycle-Acc.    |

| [11]          |           | Only         | Functionality | (Own)      | (Own)         |

| Multi2Sim     | GPGPU     | Application  | Functionally  | Cycle-Acc. | Cycle-Acc.    |

| [10]          |           | Only         | Correct       | (Own)      | (Own)         |

| FusionSim     | GPGPU     | Application  | Functionally  | Cycle-Acc. | Cycle-Acc.    |

| [12]          |           | Only         | Correct       | (PTLSim)   | (GPGPU-sim)   |

| SCHP [14]     | GPGPU     | Full System  | Functionally  | Cycle-Acc. | Cycle-Acc.    |

| gem5-gpu [13] |           |              | Correct       | (gem5)     | (GPGPU-sim)   |

| MCMG          | Graphics  | Full System  | Functionally  | Cycle-Acc. | Cycle-Acc.    |

| [15]          |           |              | Correct       | (gem5)     | (ATTILA)      |

| QEMU          | Graphics  | Full System  | Functionally  | No timing  | Cycle-Acc.    |

| +SystemC      |           |              | Correct       | (QEMU)     | (SystemC)     |

| [16]          |           |              |               |            |               |

| TEAPOT        | Graphics  | Full System  | Functionally  | No timing  | Cycle-Acc.    |

| [18]          |           |              | Correct       | (QEMU)     | (Own)         |

| Proposed      | GPGPU     | Full System  | Functionally  | Cycle-Acc. | Cycle-Approx. |

| Technique     | Graphics  |              | Correct       | (gem5)     | (Real HW)     |

Table 2-2. Comparison of CPU/GPU simulation frameworks

# Chapter 3 GPU-in-the-loop Simulation

### 3.1 Basic Idea

The basic idea for the GIL simulation technique is to integrate a real GPU with a CPU simulator in full system simulation framework instead of a GPU simulator. Since the proposed technique is not designed to be applicable for a specific simulator, any full system simulators can be used. In this thesis, as an example, the proposed technique is implemented based on gem5 simulator [8].

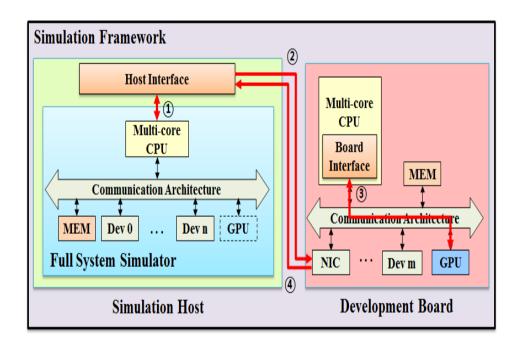

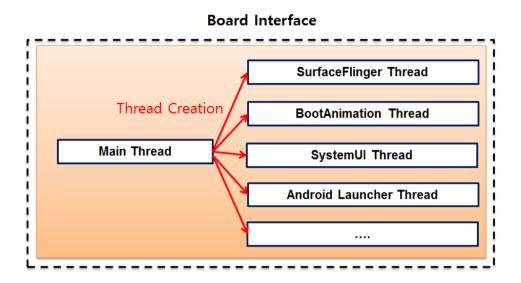

Figure 3-1 illustrates an overview of GPU-in-the-loop (GIL) simulation technique. In the simulation framework, a full system simulator is configured for the target CPU/GPU heterogeneous system using the gem5 simulator, which includes the simulation model of a multi-core CPU and other HW components except for the GPU, and actually runs the Android full software stack with Full system (FS) mode. To connect the full system simulator with the GPU board, the host interface is added in the simulation host and it interacts with the CPU model to detect GPU requests and obtain the additional information for the requests (①). In the GPU board, the board interface is implemented in Android application in which GPU requests are received from the host interface through the network interface (②) and they are processed using real GPU in the board (③). After the requests are completed, the output results are sent to the host interface (④) and they are reflected to the simulator for both functional and timing correctness.

Figure 3-1. The overall GIL simulation framework

# **3.2 Different levels of CPU/GPU** Interaction

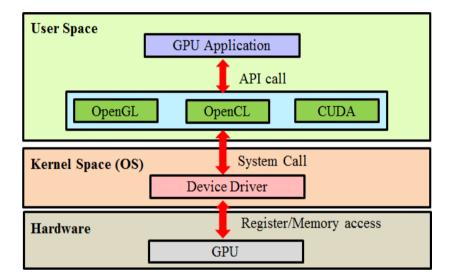

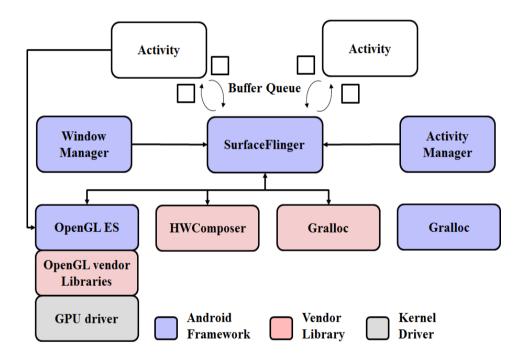

Figure 3-2. Typical GPU execution scenario

Figure 3-2 illustrates the typical GPU SW stacks in most CPU/GPU platforms in which three different levels of GPU requests are used to deliver some tasks on the GPU. In the GPU application, it invokes the API functions in the GPU libraries which are provided to enable the application developers to utilize the graphics (OpenGL ES) or GPGPU (OpenCL and CUDA) functionalities of the GPU. In the GPU libraries, each API request is translated into several low-level GPU commands and they are passed to the GPU device driver using system calls such as *ioctl* and *mmap*. In the GPU device driver, the shared memory and the GPU registers are

accessed to directly pass the requested commands to the GPU.

Since the board interface is implemented as a user-level application in the proposed technique, from the three types of GPU requests, only the API and system call requests can be used in the board interface to pass the requests to the GPU. Thus, the API-level and system call-level GIL simulation techniques will be covered in this paper.

## **3.3 Detection Mechanism**

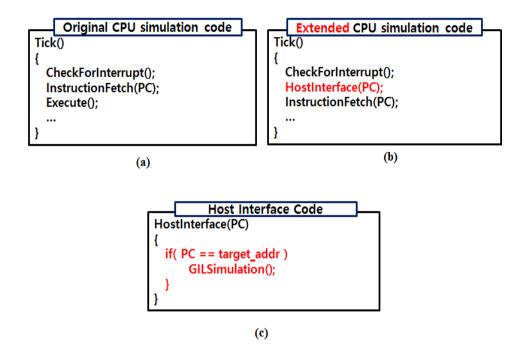

The first process that happens in the proposed technique is to detect GPU requests from the CPU model. In the proposed technique, since a GPU request is defined as a function call (system call or API), it can be detected by comparing the current instruction address (PC) of the CPU model with the start address of the target function. For this, first we should obtain the address information for the target functions. Since the target functions are included in OS kernel, the target address can be obtained from the OS kernel image used in the simulation by disassembling the image using *objdump* utility. Using this address information, the detection mechanism is implemented in the host interface as shown in Figure 3-3 (c). And since the PC value is only available in CPU model, the original CPU model (Figure 3-3 (a)) is extended to pass the PC value to the host interface (Figure 3-3 (b)).

Figure 3-3. Extension for CPU simulator and detection code in the host interface

Instead of comparing the address, it is possible to detect GPU requests by using special instructions such as pseudo instructions available in the simulator or SW interrupt instruction (svc) used in ARM semi-hosting [46]. In this approach, unlike the address-based detection mechanism mentioned above, the original source code of the GPU library or the device driver should be provided to insert the special instructions to the detection point in the code and the binaries are re-built from the modified source code. However, it is possible to detect the functions in both user space and kernel space in this approach. Whereas, only the functions in the kernel address can be detected in the address-based detection mechanism since the address of the user space is determined by the dynamic linker during the simulation. For this

reason, the synthetic driver is added should be added in the API-level technique. However, if we apply the instruction-base detection mechanism, the synthetic driver is not required.

## 3.4 Memory Coherency Problem

In most mobile platforms, on-chip memory is shared by a CPU and a GPU. However, in the proposed technique, the shared memory is modeled by two separate memories in the simulator and the board, and the CPU model and the real GPU accesses the different memory in each side. Thus, the modification in one memory is not reflected to the other memory and in-correct simulation result can be obtained. To solve this problem, memory synchronization should be performed between two memories. Details of the memory synchronization mechanisms will be explained in later sections.

## **3.5 Overall GIL simulation flow**

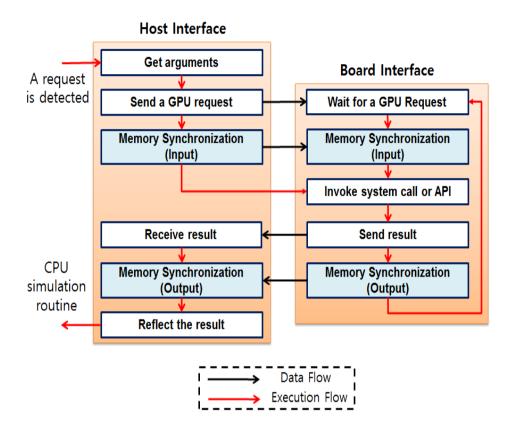

Figure 3-4 shows the simulation flow between host/board interfaces after a GPU request is detected by the detection mechanism in the host interface. First, the arguments for the GPU request are obtained using *readIntReg()* and *readMem()*

Figure 3-4. Simulation flow between host/board interfaces

functions. These gem5 functions read the value of registers (e.g. r0-r3 that are used for arguments by ARM call conventions) and memory. After that, the GPU request and arguments are sent to the board interface and memory synchronization is performed for input data in the arguments. In the board interface, the GPU request is processed by invoking system call or API with the received arguments. Once it is returned, which means that the GPU execution is completed, the result for the GPU request is sent to back to the host interface and memory synchronization is performed for output data in the arguments. After that, in the host interface, it reflects the result of the GPU request to the related simulation components and the original CPU simulation routine is executed as usual.

# Chapter 4 System call- level GIL Simulation

Depending on the GPU, types of system calls and parameters for system calls are varied. Thus, the implementation issues to be considered in the system call-level GIL simulation technique may be slightly different depending on the GPU. For this reason, we assumes the target platform with Mali 400 GPU [38] as shown in Figure 4-1 and the system call level GIL simulation technique will be described with respect to this platform.

### 4.1 Target System

As low power and energy consumption being the crucial design constraints, GPU has become an inevitable component in the recent embedded systems. Figure 4-1

shows a typical CPU/GPU heterogeneous system: multi-core CPU and multi-core GPU are connected to the on-chip bus where the shared memory and other peripherals are connected to. The GPU usually has its own MMU so that it can directly access the memory on the bus with its own virtual address.

In this platform, GPU requests are processed using several system calls such as *gpu\_ioctl()* and *gpu\_mmap()*. Thus, whenever these calls are detected inside the host interface, it delivers the corresponding request to the board interface that runs on the real CPU on the board, which in turn requests to the real GPU on the board as explain in Figure 3-1.

Figure 4-1. CPU/GPU heterogeneous system that integrates an ARM CPU and a Mali 400 GPU: a GPU core represented as PP stands for Pixel Processor, and as GP for Geometry Processor

### 4.1.1 Typical Execution Scenario of the Systems

The typical software stack in the target platform includes the Linux kernel and

the Android: An Android app runs on top of the Android, which in turn requests services to the Linux kernels. Suppose we have an Android app that utilizes the GPU by calling OpenGL ES APIs. In the APIs, each request for graphics computation is translated into a set of *gpu\_ioctl()* calls that have different commands and arguments. There are many use cases of *gpu\_ioctl()* with different commands.

Figure 4-2 shows typical scenarios for job enqueue and wait commands in Mali GPU as an example. *mali\_core\_session\_add\_job()* in the Linux driver is called first in *enqueue* command. It enqueues the target job to the GPU job queue, and calls *mali\_core\_subsystem\_schedule()*. In this scheduling function, it checks *idle\_render\_unit\_list* to find any idle render unit in the GPU. If there is no idle render unit, it returns without performing any operation. But if there is any, it dequeues a job from the GPU job queue and calls *susbsystem\_(gp/pp)\_start\_job()* with the arguments (job and render unit). In *start\_job()*, it writes commands and arguments (start address of input) to GPU registers to execute target job. Lastly, it writes start command to command register, and GPU starts to process the target job.

In wait command, *mali\_osk\_notificaion\_queue\_receive()* is called first. In this function, it checks if there is any notification in the notification queue. If there is no notification, it sleeps and current process stops. After some time passed, this process will be woken up by *mali\_osk\_notification\_queue\_send()*, which is called by the interrupt handler for the GPU completion.

Figure 4-2. Typical execution scenarios on a CPU/GPU system with the Linux kernel

### 4.2 Memory Synchronization

In the target platform, the memory region shared by a CPU and a GPU is allocated by *gpu\_mmap()* system call which is called from a GPU library. Since a CPU virtual address is returned to the GPU library as a return value of the system

call, in the GPU library, the input data for a GPU is stored to the shared memory region using the address. After that, to allocate some tasks to a GPU, *gpu\_ioctl()* system call is invoked with *start* command and the addresses for the input/output data are passed as arguments. In the GPU, a given task is processed using the input data pointed by the input data address and the result is stored to the memory region pointed by the output data address.

Since the memory synchronization is required before/after GPU actually is executed on the board, the memory synchronization is performed when *gpu\_ioctl()* is invoked with *start* command. While arguments of *gpu\_ioctl()* are memory addresses not real data, input data exists only in the simulator and output data exists only in the board. Before *gpu\_ioctl()* is invoked in the board interface, the input data must be sent to the board and the board interface must update the board memory using *memcpy()*. After *gpu\_ioctl()* is finished, on the other hand, the modified memory region by the GPU execution must be sent back to the simulator so that the host simulation interface can update the modified memory region in the gem5 simulator.

### 4.2.1 Address Translation Table

To copy the contents of the memory mapped region for synchronization, a CPU virtual address is needed in the host and board interfaces; The host interface can

access the memory only through the CPU model and the board interface itself is a CPU task that actually runs on a CPU on the board, thus it cannot access the mapped memory with the GPU virtual address.

Figure 4-3. Address translation table to match the same memory region

However, since GPU virtual addresses are provided as arguments of *gpu\_ioctl()*, we maintain translation tables for GPU to CPU virtual address in each interface as depicted in Figure 4-3. Whenever *gpu\_mmap()* is called in the CPU (gem5) side during the simulation, the host interface update its address translation table using the mapping information obtained from the *gpu\_mmap()*. Then, when this system call is processed in the board interface, it also update its address translation table.

Figure 4-3 illustrates an example of address translation. When the address given as a command argument in the *gpu ioctl()* is 0x40000080, the host interface

searches the mapping table with 0x40000000 and find out the corresponding CPU virtual address is 0x400D0000 (①). It reads the data from the address considering the offset (0x80), and sends it to the board interface via socket (②). The board interface looks up its translation table and figures out its CPU virtual address to be 0x410F0000 (③). Finally, it writes the received data to the address considering the offset. With such a mechanism, the gem5 simulator and the GPU have an illusion that they share the same memory, although they are in fact two separate memories in different machines in the framework.

From the arguments of *gpu\_ioctl()* system call, we can't know which memory regions are modified in the whole memory area. Thus, the simple solution is to synchronize all the shared memory regions. However, since this incurs significant communication overhead between the host interface and the board interface, only diffed data in the shared memory region is synchronized by performing diff operation.

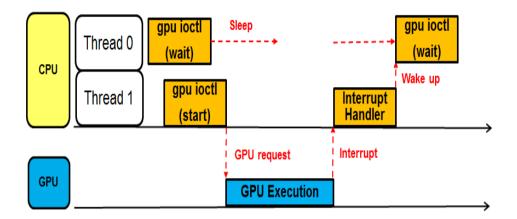

### 4.3 Timing Modeling

Figure 4-4 shows the typical scenario where GPU execution is controlled by two commands explained in Figure 4-2, *start* command and *wait* command. In this scenario, two commands are called from the two separate threads (*Thread 0*, *Thread 1*). When *wait* command is invoked from *Thread 0*, it is blocked inside *gpu ioctl()*

Figure 4-4. Typical execution scenario on the target platform

to wait for the notification of the GPU job completion. In the meanwhile, in *Thread 1*, *start* command is invoked and it will trigger the GPU execution. When the GPU execution is completed, an interrupt in generated by the GPU and an interrupt handler will be invoked. In last, the interrupt handler sends a notification signal which awakes the waiting thread (*Thread 0*).

### 4.3.1 Interrupt Modeling

Since the original software stack is used in the simulation without modification, the CPU parts in Figure 4-4 simulated by the CPU model. Thus, only GPU part should be modeled in this technique for functional and timing correctness. For functional correctness, the GPU interrupt should be modeled since the waiting thread in Figure 4-4 will be blocked indefinitely if the GPU interrupt is not generated in the simulation. For timing correctness, the waiting timing in the CPU part should be accurately modeled. For this, the GPU interrupt should be generated at accurate timing considering the GPU execution.

To generate the interrupt in the simulator, the virtual GPU model is implemented in the gem5 simulator in which only interrupt related part is modeled without the details of GPU micro-architecture. And the GPU execution time ( $\Delta$ ) can be obtained from the result of *gpu\_ioctl(*) when it is invoked with *start* command in the board. Once the result is passed to the host interface, an interrupt event is inserted at timestamp  $t1 + \Delta$ , when  $\Delta$  is the execution time of the GPU and t1 is the current simulate time. Then, when the simulation is progressed to  $t1 + \Delta$ , the interrupt is generated by the virtual GPU model.

# 4.3.2 Regression based timing correction for GPU time

In this technique, GPU execution time ( $\Delta$ ) is obtained from the real board. However, this value does not include contention overhead between multiple PPs. In the real system, when multiple *gpu\_ioctl()* requests for PPs can be made simultaneously and executed in parallel by multiple PPs. As PPs share the resources (cache, memory, bus, etc.), the execution time of each *gpu\_ioctl()* request becomes longer than the case when only one PP is executed. In contrast, in the GIL simulation, multiple *gpu\_ioctl()* requests are actually processed sequentially.

To consider the contention overhead, we measured the ratio  $\alpha$ , which is the ratio of the average execution time with contention ( $\Delta$ ) to the one without contention ( $\Delta$ ) in the real board. Then, interrupt is generated at  $tI + \alpha \cdot \Delta$  (=  $\Delta$ ) in the simulation. We will explain in more detail how to measure  $\Delta$  in the experiment section.

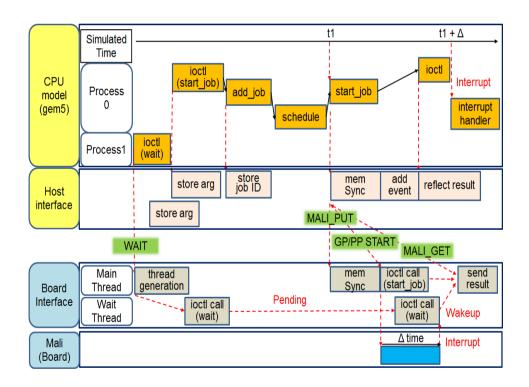

## 4.3.3 An Example of System-level GIL Simulation Scenario

The System call-level GIL simulation sequence for the scenario shown in Figure 4-2, which assumes Mali GPU as an example, is illustrated in Figure 4-5 assuming that a *wait* command is called first, followed by an *enqueue* command as shown in Figure 4-4. When the host interface detects the *wait* command, it sends the command to the board interface running on a real CPU in the board. The board interface creates a new thread (*wait* thread) waiting for the completion of the GPU execution to avoid any possible dead-lock. Simulation continues and detects *gpu\_ioctl()* for *enqueue* command. Then, the host interface stores *gpu\_ioctl()* arguments and calls *add\_job()*, *schedule()*, *start\_job()* in sequence. In *add\_job()*, a job ID is assigned for *start\_job()* by which the GPU execution is finally triggered. On the GPU execution, it first sends a memory synchronization message

(MALI\_PUT) for input data, and the board interface updates the memory accordingly. Then, it sends *ioctl* messages (GP/PP\_START) that are handled by the main thread in the board interface. The main thread sleeps until the completion of the GPU execution is notified by the *wait* thread. On the completion, the main thread sends a message to the host interface, and finally, the host interface sends a memory synchronization message (MALI\_GET) to update the modified memory region by the GPU execution.

Figure 4-5. An example of the HIL simulation sequence with the scenario shown in Figure 4-2

### 4.4 **Experiments**

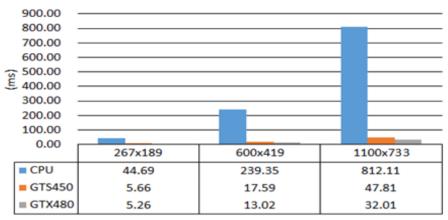

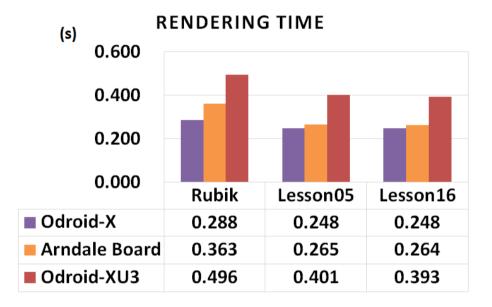

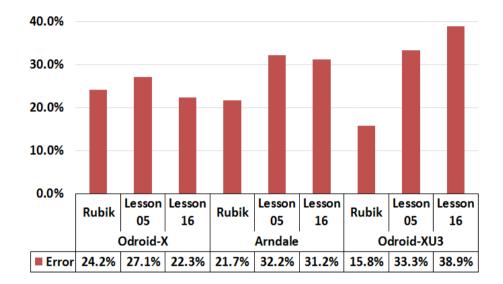

In our experiments, we simulated the Exynos 4412 system [39]. The system has a quad-core ARM Cortex-A9 CPU and ARM Mali-400MP GPU that has four Pixel Processors and one Geometry Processor. They are connected to an AXI bus where also 256KB on-chip memory is connected. We used ODROID-X board [40] to execute the Mali GPU hardware, and used gem5 simulator for a quad-core ARM Cortex-A9 CPU modeling. We ran Android apps, Lesson09 that moves and blends textured objects in a 3D space [30] and Cubic [31]. In Android OpenGL ES application, a rendering function called *onDrawFrame* in the application is invoked repeatedly to draw the current frame. In the Lesson09 benchmark, the rendering function only includes the API call sequence without any computation. However, in the Rubik benchmark, the rendering function includes both the computation and the API call sequence, in which the proportions of two parts are 37.4% (computation) and 63.6 % (API call sequence) respectively. We ran these apps on the proposed GIL simulation framework for 3 seconds in real time (i.e., the time in the ODROID-X board) and measured the execution time of the rendering function.

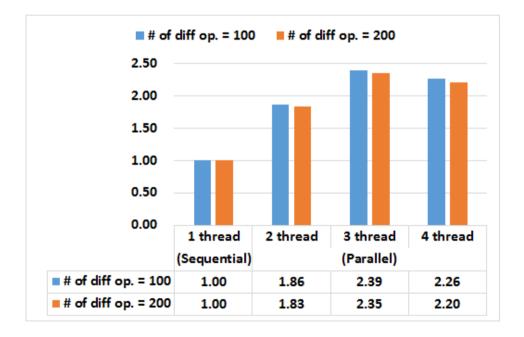

### 4.4.1 Parallelization for diff operation

As mentioned in 4.2.1, to reduce the communication overhead between the

simulator and the board, *diff* operation is performed in the host interface and the board interface. Since the size of shared memory region is significantly large, the overhead for the *diff* operation takes large portion of the total simulation time, especially in the board interface. To reduce the *diff* overhead, we parallelize the *diff* operation in the board interface. Figure 4-6 shows the normalized speed-up for the parallel implementations (2, 3, 4 threads) compared with the sequential implementation (1 thread) when *diff* operation is performed 100 and 200 times during the simulation. From the result, we can know that the speed-up of x1.83 ~ x2.39 can be achieved in the parallel implementation and the maximum performance can be achieved when the number of thread is 3.

Figure 4-6. The execution time for *diff* operation for sequential and parallel implementations

Figure 4-7. Simulation time (sec) for two benchmarks

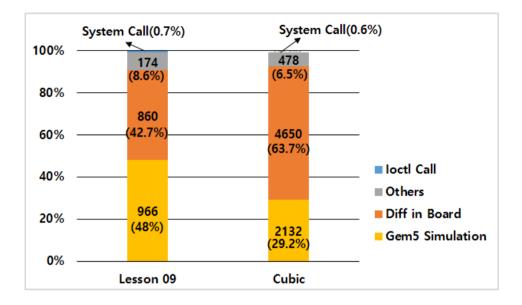

### 4.4.2 Simulation Time Analysis

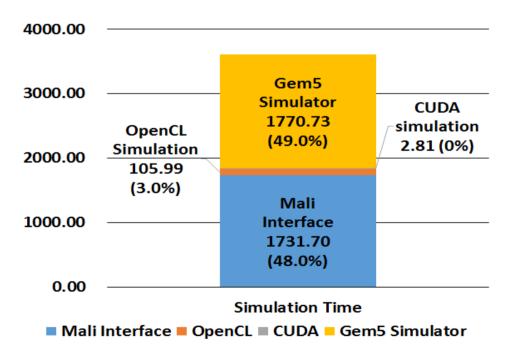

In the system-level GIL simulation technique, the simulation time is decomposed as shown in Figure 4-7. For Lesson09 app, the total GIL simulation takes about 2014 seconds, among which gem5 simulation time takes 48% and the interfacing time between two interfaces takes 52%. It corresponds to about 1.5M cycles per second of simulation performance. In the interfacing time, 860 seconds is spent for memory synchronization, which is 42.7% of the total time.

For Cubic app, the total simulation time is 7304 seconds and achieves about 0.8 M cycles per second of simulation performance. This is because the portion of

memory synchronization increased in this application and GPU execution portion is larger than Lesson09.

Figure 4-8. Execution time distribution for PPs

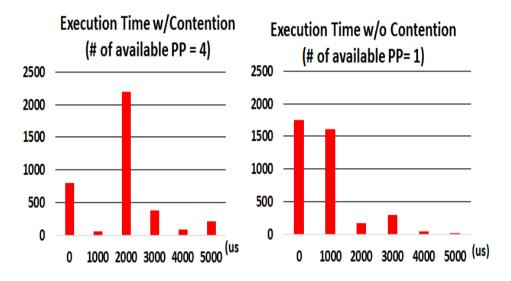

### 4.4.3 Contention overhead in Pixel Processors (PP)

As explained in 4.3.2, we estimate the contention overhead of PPs of the GPU by modifying the number of available PPs from Linux driver. We measured two GPU execution time,  $\Delta$ ` and  $\Delta$ , for 4000 *gpu\_ioctl()* requests in the real target board;  $\Delta$ ` is measured by setting the number of available PPs to 4 (all cores are available), and  $\Delta$ is measured by setting the number to 1 (only 1 core is available so that there is no contention). Figure 4-8 shows the histogram for  $\Delta$ ` and  $\Delta$ , where x axis represents the execution time of a single  $gpu_ioctl()$  request and y axis the occurrence count. The average execution time for the  $\Delta$ ` and  $\Delta$  are 3059 (us) and 1460 (us) respectively, which results in the ratio  $\alpha$  to be 2.1. Thus GPU execution time was scaled by this ratio in the simulation.

### 4.4.4 Internal System Behavior Profiling

With the proposed GIL simulation framework, we could observe the internal system behavior during the app execution. Table 4-1 shows the execution time, the waiting time, and the response time for each processor (1 GP and 4 PPs). Also, as shown in Table 4-2, we could obtain the GPU utilization. If the app utilizes the GPU not only for the rendering or shading job, but also for the general purpose job such as OpenCL kernel, this observability would be more useful. We could not use OpenCL applications in the current implementation for Exynos system, since Mali 400 GPU does not support GPGPU.

Table 4-1. GPU response time for Cubic app

| Processor        | Avg. Exec. | Avg. Waiting | Avg. Response |

|------------------|------------|--------------|---------------|

| Туре             | Time(ms)   | Time(ms)     | Time(ms)      |

| Geometry Proc.   | 0.178      | 0.029        | 0.207         |

| Pixel Processor  | 1.847      | 0.036        | 1.884         |

| $(PP0 \sim PP3)$ | ~ 1.866    | ~ 0.041      | ~ 1.906       |

Table 4-2. GPU execution time and utilization for Cubic app

| Processor        | # of GPU  | <b>Total Exec</b> | GPU             |

|------------------|-----------|-------------------|-----------------|

| Туре             | Execution | Time (ms)         | Utilization (%) |

| Geometry Proc.   | 506       | 90.195            | 1.53            |

| Pixel Processor  | 505       | 932.966           | 15.85           |

| $(PP0 \sim PP3)$ | ~ 506     | ~ 943.994         | ~ 15.99         |

Table 4-3. Accuracy evaluation for the Android apps

| Accumulated           | <b>Real Board</b> | Simulation       | Error Ratio       |

|-----------------------|-------------------|------------------|-------------------|

| <b>Execution</b> Time | (sec)             | (sec)            | (%)               |

| Lesson09              | 1.21 ~ 1.57       | 0.99 ~ 1.42      | -29.66 ~ - 5.22   |

| Cubic                 | 0.76 ~ 1.02       | $0.77 \sim 2.09$ | - 1.53 ~ + 104.91 |

### 4.4.5 Accuracy Evaluation

To evaluate the timing accuracy of the proposed framework, we measured the execution time of a rendering function that calls several OpenGL ES APIs, by inserting time stamping code to the application. We accumulated the execution time

for 50 invocations of the rending function. We performed the experiment for 5 runs both on ODROID-X board and on the simulation framework. The range of execution time and the error ratio are shown in Table 4-3. It confirms that the accuracy of the proposed GIL simulation technique is about the same order of the gem5 simulator that is simulated at the instruction-level. We observed that the accuracy error gets smaller as we run an app longer. Since Cubic runs longer than Lesson09, the accuracy error of Cubic gets smaller than Lesson09. More detailed analysis on the accuracy is left for future investigation.

### 4.5 Summary

In this chapter, we have proposed a system call-level GIL simulation technique for CPU/GPU platforms that integrates a real GPU hardware instead of GPU simulator for full system simulation, running complete software stack without modification. We devised a novel interfacing mechanism between a CPU simulator and the GPU hardware. For correct operation, several issues had to be considered, including memory synchronization, address translation, and interrupt handing. We took Exynos 4412 system as our case study and ran two Android apps where a number of OpenGL ES APIs were called. To the best of our knowledge, it is the first example of full system simulation of a CPU/GPU heterogeneous system. We can achieve simulation performance up to 1.5 M cycles per second.

# Chapter 5 API-Level GIL Simulation

System call-level GIL simulation technique has a limited extensibility. In GPU, *ioctl* system call is widely used to process the device-specific operations. It takes a parameter specifying a request code and the request code is often device-specific. Therefore, to support other GPUs, the simulation framework should be modified to consider the new request code unless other GPUs have the same request codes for *ioctl* system call. Moreover, to correctly simulate the device driver in the original software stack, some GPU specific functionalities such as GPU registers and interrupts should be modeled for functional correctness, which requires considerable effort to understand interactions between the device driver and the GPU registers.

## 5.1 Differences between API-level and System call-level techniques

An API (Application Programming Interface) is usually defined independent of the HW for portability. For GPU APIs such as OpenGL ES and OpenCL, the application written with APIs can run on various CPU/GPU platforms without any modification. Thus, if the GIL simulation technique is performed at API level instead of system call level, the GIL simulation can be performed with various GPU boards with minor modification for the simulation framework.

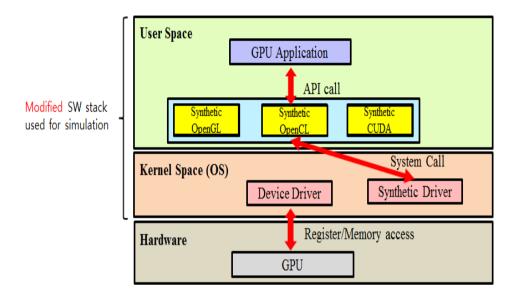

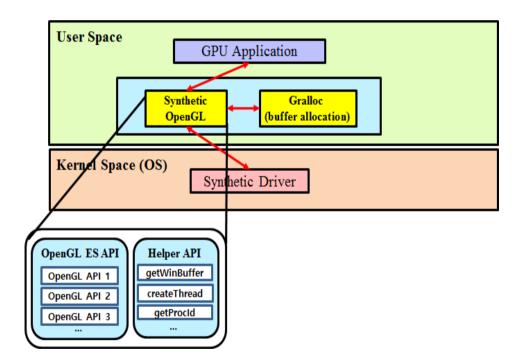

Even if the simulation is performed at API level, if the original software stack is used in the simulation, some GPU specific functionalities related with the device driver in original software stack need to be modeled. To further reduce the GPU dependency from the simulation code, the device driver in original software stack should not be used in the simulation. Since the device driver is accessed from the GPU libraries through system calls, if the original GPU libraries are not used in the simulation, the device driver is also no longer used during the simulation. For this reason, in the API-level GIL simulation, the GPU libraries in the original software stack is replaced by the synthetic library which implements stub functions for the APIs of the original GPU libraries as shown in Figure 5-1.

Figure 5-1. Modified SW stack in API-level GIL simulation

For the API-level simulation technique, the GPU request should be detected when an API is invoked from the GPU applications. Since the target address is required in our detection mechanism explained in section 3.3, the start address of APIs defined in the synthetic library should be known to detect the API request. However, it is not easy to know the address since the synthetic library is located in user space and the address is determined when the library is loaded by a dynamic linker. To know the address, we should track the linking process during the simulation, but this would incur considerable overhead to the simulator. Instead, since the addresses of functions in kernel space can be obtained from the kernel image before the simulation, the synthetic driver is added in OS kernel for this purpose. Thus, in the synthetic library, it just forwards the API requests to the synthetic driver without any operation and the API request is detected in the synthetic driver by the detection mechanism.

### 5.1.1 Synthetic Library

Figure 5-2 shows an example code of the synthetic library for *cudaMemcpy* API in the CUDA library. To share the API information between the simulator and the board, two structures represented in Table 5-1 and Table 5-2 are used.

The common structure (*common\_s*) contains the data commonly used in all APIs. It has 5 variables; *api id* variable is used to notify which API is invoked from the

```

cudaError t cudaMemcpy(void * dst, const void * src, size t count,

enum cudaMemcpyKind kind)

ł

common_s arg;

cuda memcpy s a pi arg;

api_arg.dst = dst;

api arg.src = src;

api arg.count = count;

api_arg.kind = kind;

arg.api id = CUDA MEMCPY;

arg.api_arg = &(api_arg);

arg.process id = getProcld();

arg.thread id = getThreadId();

int ret = ioctl(gil_dev, GIL_SIMULATION, &arg);

return api arg.ret;

}

```

Figure 5-2. An example code of the synthetic library for cudaMemcpy API

Table 5-1. Common structure (common s)

| Variable name | Description                                |  |

|---------------|--------------------------------------------|--|

| api_id        | An identifier for target API               |  |

| thread_id     | Thread id for the thread calling the API   |  |

| process_id    | Process id for the process calling the API |  |

| api_arg       | A pointer to an API specific structure     |  |

| api_time      | API time measured in the board             |  |

#### Table 5-2. API-specific structure for cudaMemcpy API

| (cuda_n | emcpy_ | <u>s</u> ) |

|---------|--------|------------|

|---------|--------|------------|

| Variable name | Description                |  |

|---------------|----------------------------|--|

| src           | Source memory address      |  |

| dst           | Destination memory address |  |

| count         | Copied memory size         |  |

| kind          | Direction for memory copy  |  |

| ret           | Return value               |  |

application. *thread\_id* and *process\_id* variables are used to distinguish the thread and process calling the API. *api\_time* variable is used to store the API time measured in the board and this variable is set by the host interface when the API time is passed from the board interface. And, *api\_arg* variable is a pointer to an API-specific structure.

The API-specific structure contains all arguments for the target API and it is varied depending on the target API. For example, in case of *cudaMemcpy* API, *cuda\_memcpy\_s* structure is used and contains four variables: destination memory address (dst), source memory address (src), copied memory size (count), and

direction for memory copy (kind). After variables in the two structures are set using arguments passed from the application, *ioctl* system call is called with a pointer to the common structure to pass the API request to the synthetic driver. Once the *ioctl* is returned, since the return value has been set in *ret* variable in API-specific structure by the host interface, it is returned to the application.

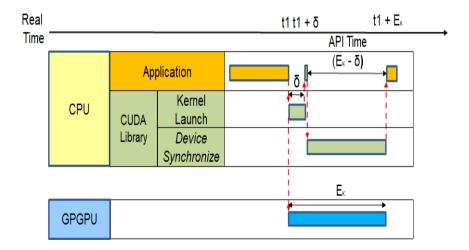

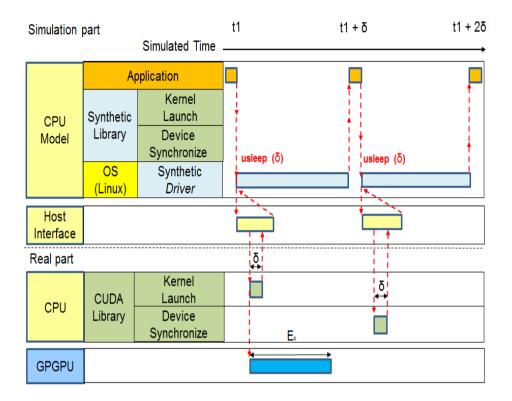

### 5.2 Timing Modeling

In the system call-level GIL simulation technique, the GPU execution time is reflected to the simulator by the interrupt. However, since the device driver is not simulated in the API-level GIL simulation technique, the interrupt-based timing modeling technique can't be used. Instead, since we can measure the API execution in the board by inserting timestamping code before/after the API invocation, the API execution time is reflected to the simulator by spending that amount time in the synthetic driver.

Figure 5-3 illustrates the implementation of the synthetic driver. In Linux booting phase, *gil\_simulation\_driver\_init* is invoked and it creates the virtual device named *gil\_dev*. After the initialization of the device, it can be accessed as a file using *open* and *ioctl* system calls from the synthetic library. When *ioctl* is called for *gil\_dev* device from the synthetic library as shown in Figure 5-2 (the first argument of *ioctl* call), *gil\_simulation\_ioctl()* will be invoked. When the first instruction for this

function is executed on the CPU simulator, it is detected by the detection routine in the host interface and the API is request sent to the board interface. In the board interface, target API is invoked and the API execution time is measured using time functions such as *gettimeofday()* and *clock\_gettime()*. Then, the return value and the execution time for the API are sent back to the host interface and the API execution time is stored into *api\_time* variable in the common structure. After the simulation for the target API has been completed, the original CPU simulation routine executes *gil\_simulation\_ioctl* code shown in Figure 5-3. To model the timing, it simply calls the *usleep* function so that the measured API time (*api\_time*) elapses in the simulated time.

```

Static int gil_simulation_ioctl( ..., cmd, arg) {

if( arg.api_tmie_usec > 0 ) {

usleep(arg.api_time_usec);

}

}

int gil_simulation_driver_init() {

...

device_create(..., "gil_dev");

...

return 0;

}

void hil_simulation_driver_exit() {

...

}

```

Figure 5-3. Synthetic driver code used in GIL simulation

# 5.2.1 Regression-based compensation for timing error

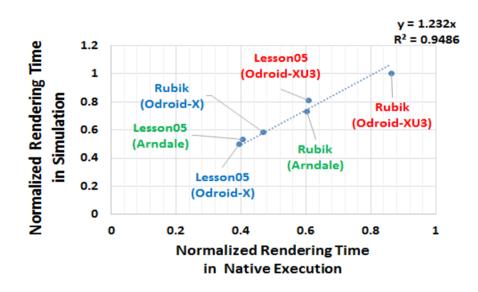

In the API-level simulation technique, the timing accuracy is first bounded by the processor simulator that measures the execution time only at the instruction level. For timing estimation of GPU execution, we estimate the execution time of each API by measuring the execution time directly in the board. The GPU execution time is modeled by simply summing up all the estimated API times and added to the CPU simulation time by using the *usleep* function explained in the section 5.2. This simple method itself is a source of timing inaccuracy. There are other sources of timing inaccuracy. In the board, time stamping is inserted before and after an API is called and the execution time is estimated by subtracting two time stamps. If the simulated system architecture or API implementation is not the same as the board, timing inaccuracy is inevitable. Even if we use the same architecture, time stamping affects the internal behavior. Also, *usleep* function has some overhead to set up the timer and this makes the elapsed time by the *usleep* will be larger than the measured API time.

Since most internal implementation of GPU libraries are proprietary and the source code is not available, it is impossible to model the low level details of API interaction. Hence we perform a simple linear regression analysis to compensate the unknown sources of time inaccuracy with some selected benchmarks. We compute the ratio between the measured execution time of an application in the actual board

and the simulated time in the proposed simulator. We adjust the simulated time of another benchmark by this ratio and compare it with the measured execution time.

### 5.3 Memory Synchronization

Since the fact that one logical memory is modeled by two separate memories in the simulator and board is not changed, the memory synchronization is also a key

(a) int main() {

int \* gpu\_addr = gpuMalloc(mem\_size);

int \* cpu\_addr = malloc(mem\_size);

for ( int i = 0; i < 1024; i++ ) {

cpu\_addr[i] = i;

}

gpuMemcpy(gpu\_addr, cpu\_addr, mem\_size);

...

}</pre>

(b) int main() {

int \* gpu\_addr = gpuMalloc(mem\_size);

int \* cpu\_addr = gpuMap(gpu\_addr, mem\_size);

for ( int i = 0; i < 1024; i++ ) {

cpu\_addr[i] = i;

}

gpuUnmap(gpu\_addr);

...

}

</pre>

# Figure 5-4. Two ways to share data between CPU and GPU in GPU applications

issue for correctness in API-level GIL simulation. However, since the original SW tack is not used in the API-level simulation, memory synchronization is somewhat different.

In API-level GIL simulation, there are two types of memory sharing between a CPU and a GPU. In the first way shown in Figure 5-4 (a), the application allocates a memory region (*cpu\_addr*) and it is copied to a GPU memory (*gpu\_addr*) using memory copy API (*gpuMemcpy*) after it is modified. Since the memory region allocated by *malloc* is not simulated in the board, it is only allocated in the simulator memory and not exist in the board. When *gpuMemcpy* is simulated in the board, it will access the board memory using the given CPU address (*cpu\_addr*), but invalid pointer error would occur since this address is not defined in the board memory. To solve this problem, a new memory region is allocated temporally in the board memory and the input data in the simulated memory is copied to newly allocated board memory. Then, the address for the allocated memory region is passed as an argument of *gpuMemcpy* instead.

In the second way shown in Figure 5-4 (b), to directly access the GPU memory in this application, *gpuMap* API is invoked to obtain a CPU virtual address for the GPU memory. When this API is simulated in the board, the pointer for the board memory (*cpu\_addr*) is returned and it is used to access the GPU memory in the application. However, since this address is not defined in the simulator memory, segmentation fault error will occur in the simulator when the address is accessed and the application will be aborted. To solve this problem, similar to the former case,

temporal memory region is allocated in the simulator memory and it is used as a return value for *gpuMap* API by modifying the *gpuMap* API code in the synthetic library like Figure 5-5.

```

cudaError_t gpuMap(void *gpu_addr, int size)

{

common_s arg;

gpu_map_api_s a pi_arg;

int ret = ioctl(gil_dev, GIL_SIMULATION, &arg );

api_arg.temp_mem = malloc(size);

return api_arg.temp_mem;

}

```

Figure 5-5. Synthetic Library code for gpuMap API

# 5.4 GPGPU API (CUDA & OpenCL) Implementation Case

### 5.4.1 Asynchronous Behavior Modeling