#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

#### 공학박사학위논문

# 낸드 플래시 기반 저장장치의 수명 향상을 위한 계층 교차 최적화 기법

Cross-Layer Optimization Techniques for Extending Lifetime of NAND Flash-Based Storage Devices

2016년 2월

서울대학교 대학원 전기·컴퓨터 공학부 정재용

## 낸드 플래시 기반 저장장치의 수명 향상을 위한 계층 교차 최적화 기법

### Cross-Layer Optimization Techniques for Extending Lifetime of NAND Flash-Based Storage Devices

지도교수 김지홍

이 논문을 공학박사 학위논문으로 제출함 2015년 11월

> 서울대학교 대학원 전기·컴퓨터 공학부 정재용

정재용의 공학박사 학위논문을 인준함 2015년 12월

| 위 원 | <sup>担</sup> 장 | 문 봉 기 | (인)  |

|-----|----------------|-------|------|

| 부위  | 원장             | 김 지 홍 | (인)  |

| 위   | 원              | 유 승 주 | (인)  |

| 위   | 원              | 경계현   | (인)  |

| 위   | 위              | 전 면 수 | (o]) |

#### **Abstract**

Replacing HDDs with NAND flash-based storage devices (SSDs) has been one of the major challenges in modern computing systems especially in regards to better performance and higher mobility. Although uninterrupted semiconductor process scaling and multi-leveling techniques lower the price of SSDs to the comparable level of HDDs, the decreasing lifetime of NAND flash memory, as a side effect of recent advanced device technologies, is emerging as one of the major barriers to the wide adoption of SSDs in high-performance computing systems.

In this dissertation, we propose new cross-layer optimization techniques to extend the lifetime (in particular, endurance) of NAND flash memory. Our techniques are motivated by our key observation that erasing a NAND block with a lower voltage or at a slower speed can significantly improve NAND endurance. However, using a lower voltage in erase operations causes adverse side effects on other NAND characteristics such as write performance and retention capability. The main goal of the proposed techniques is to improve NAND endurance without affecting the other NAND requirements.

We first present Dynamic Erase Voltage and Time Scaling (DeVTS), a unified framework to enable a system software to exploit the tradeoff relationship between the endurance and erase voltages/times of NAND flash memory. DeVTS includes erase voltage/time scaling and write capability tuning, each of which brings a different impact on the endurance, performance, and retention capabilities of NAND flash memory.

Second, we propose a lifetime improvement technique which takes advantage of idle times between write requests when erasing a NAND block with a slower speed or when writing data to a NAND block erased with a lower voltage. We have implemented a DeVTS-enabled FTL, called dvs-FTL, which optimally adjusts the erase voltage/time and write performance of NAND devices in an automatic fashion. Our experimental results show that dvsFTL can improve NAND endurance by 62%, on average, over DeVTS-unaware FTL with a negligible decrease in the overall write performance.

Third, we suggest a comprehensive lifetime improvement technique which exploits variations of the retention requirements as well as the performance requirement of SSDs when writing data to a NAND block erased with a lower voltage. We have implemented dvsFTL+, an extended version of dvsFTL, which fully utilizes DeVTS by accurately predicting the write performance and retention requirements during run times. Our experimental results show that dvsFTL+ can further improve NAND endurance by more than 50% over dvsFTL while preserving all the NAND requirements.

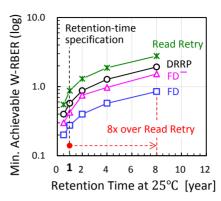

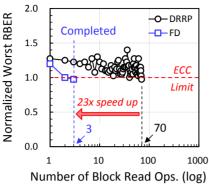

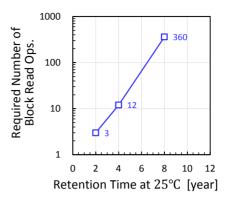

Lastly, we present a reliability management technique which prevents retention failure problems when aggressive retention-capability tuning techniques are employed in real environments. Our measurement results show that the proposed technique can recover corrupted data from retention failures up to 23 times faster over existing data recovery techniques. Furthermore, it can successfully recover severely retention-failed data, such as ones experienced 8 times longer retention times than the retention-time specification, that were not recoverable with the existing technique.

Based on the evaluation studies for the developed lifetime improve-

ment techniques, we verified that the cross-layer optimization approach has

a significant impact on extending the lifetime of NAND flash-based storage

devices. We expect that our proposed techniques can positively contribute

to not only the wide adoption of NAND flash memory in datacenter envi-

ronments but also the gradual acceleration of using flash as main memory.

Keywords: NAND Flash Memory, Solid State Drive, Storage Management,

Storage Reliability, Storage Lifetime, Embedded Software

**Student Number:** 2012-30229

iii

### **Contents**

| I.  | In    | troducti | on                                                  | 1  |

|-----|-------|----------|-----------------------------------------------------|----|

|     | 1.1   | Motiva   | tion                                                | 1  |

|     | 1.2   | Dissert  | ation Goals                                         | 3  |

|     | 1.3   | Contrib  | outions                                             | 4  |

|     | 1.4   | Dissert  | ation Structure                                     | 5  |

| II. | Ba    | ckgrou   | nd                                                  | 7  |

|     | 2.1   | Thresh   | old Voltage Window of NAND Flash Memory             | 7  |

|     | 2.2   | NAND     | Program Operation                                   | 10 |

|     | 2.3   | Related  | l Work                                              | 11 |

|     |       | 2.3.1    | System-Level SSD Lifetime Improvement Techniques    | 12 |

|     |       | 2.3.2    | Device-Level Endurance-Enhancing Technique          | 15 |

|     |       | 2.3.3    | Cross-Layer Optimization Techniques Exploiting NANI | )  |

|     |       |          | Tradeoffs                                           | 17 |

| Ш   | l. Dy | namic l  | Erase Voltage and Time Scaling                      | 20 |

|     | 3.1   | Erase V  | Voltage and Time Scaling                            | 22 |

|     |       | 3.1.1    | Motivation                                          | 22 |

|     |       | 3.1.2    | Erase Voltage Scaling                               | 23 |

|     |       | 3.1.3    | Erase Time Scaling                                  | 26 |

|     | 3.2   | Write (  | Capability Tuning                                   | 28 |

|     |       | 3.2.1    | Write Performance Tuning                            | 29 |

|      | 3.2.2    | Retention Capability Tuning                                                                                                                                         | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 3.2.3    | Disturbance Resistance Tuning                                                                                                                                       | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.3  | NAND     | Endurance Model                                                                                                                                                     | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| . Li | fetime I | mprovement Technique Using Write-Performance                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Tu   | ning .   |                                                                                                                                                                     | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.1  | Design   | and Implementation of dvsFTL                                                                                                                                        | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | 4.1.1    | Overview                                                                                                                                                            | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | 4.1.2    | Write-Speed Mode Selection                                                                                                                                          | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | 4.1.3    | Erase Voltage Mode Selection                                                                                                                                        | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | 4.1.4    | Erase Speed Mode Selection                                                                                                                                          | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | 4.1.5    | DeVTS-wPT Aware FTL Modules                                                                                                                                         | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.2  | Experi   | mental Results                                                                                                                                                      | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | 4.2.1    | Experimental Settings                                                                                                                                               | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | 4.2.2    | Workload Characteristics                                                                                                                                            | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

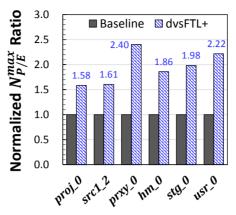

|      | 4.2.3    | Endurance Gain Analysis                                                                                                                                             | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | 4.2.4    | Overall Write Throughput Analysis                                                                                                                                   | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | 4.2.5    | Detailed Analysis                                                                                                                                                   | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Lit  | fetime I | mprovement Technique Using Retention-Capability                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |          |                                                                                                                                                                     | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | _        |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |          |                                                                                                                                                                     | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      |          |                                                                                                                                                                     | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      |          | •                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |          |                                                                                                                                                                     | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | 4.1 4.2  | 3.2.3 3.3 NAND  Lifetime I Tuning 4.1 Design 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 4.2 Experi 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5  Lifetime I Tuning 5.1 Design 5.1.1 5.1.2 5.1.3 | 3.2.3 Disturbance Resistance Tuning  3.3 NAND Endurance Model  Lifetime Improvement Technique Using Write-Performance Tuning  4.1 Design and Implementation of dvsFTL  4.1.1 Overview  4.1.2 Write-Speed Mode Selection  4.1.3 Erase Voltage Mode Selection  4.1.4 Erase Speed Mode Selection  4.1.5 DeVTS-wPT Aware FTL Modules  4.2 Experimental Results  4.2.1 Experimental Settings  4.2.2 Workload Characteristics  4.2.3 Endurance Gain Analysis  4.2.4 Overall Write Throughput Analysis  4.2.5 Detailed Analysis  Lifetime Improvement Technique Using Retention-Capability Tuning  5.1 Design and Implementation of dvsFTL+  5.1.1 Overview  5.1.2 Retention Requirement Prediction |

| 5.2 |      | Experi    | mental Results                                  | 9  |

|-----|------|-----------|-------------------------------------------------|----|

|     |      | 5.2.1     | Experimental Settings 6                         | 59 |

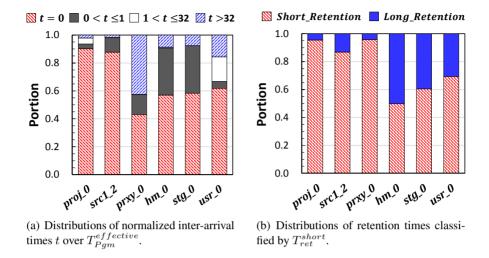

|     |      | 5.2.2     | Workload Characteristics                        | 70 |

|     |      | 5.2.3     | Endurance Gain Analysis                         | 72 |

|     |      | 5.2.4     | NAND Requirements Analysis                      | 73 |

|     |      | 5.2.5     | Detailed Analysis of Retention-Time Predictor 7 | 76 |

|     |      | 5.2.6     | Detailed Analysis of Endurance Gain 8           | 33 |

| VI. | Re   | liability | Management Technique for NAND Flash Memory 8    | 37 |

|     | 6.1  | Overvi    | ew                                              | 39 |

|     | 6.2  | Motiva    | ution                                           | )1 |

|     |      | 6.2.1     | Limitations of the Existing Retention-Error     |    |

|     |      |           | Management Policy                               | 1  |

|     |      | 6.2.2     | Limitations of the Existing Retention-Failure   |    |

|     |      |           | Recovery Technique                              | )2 |

|     | 6.3  | Retenti   | ion Error Recovery Technique                    | 95 |

|     |      | 6.3.1     | Charge Movement Model                           | 95 |

|     |      | 6.3.2     | A Selective Error-Correction Procedure 9        | 9  |

|     |      | 6.3.3     | Implementation                                  | 0  |

|     | 6.4  | Experi    | mental Results                                  | )3 |

| VII | . Co | nclusio   | ns                                              | )8 |

|     | 7.1  | Summa     | ary and Conclusions                             | )8 |

|     | 7.2  | Future    | Work                                            | 0  |

|     |      | 7.2.1     | Lifetime Improvement Technique Exploiting       |    |

|     |      |           | The Other NAND Tradeoffs 11                     | Λ  |

| Bibliography |                                           |

|--------------|-------------------------------------------|

| 7.2.3        | Development of Specialized SSDs           |

|              | DRAM-Flash Hybrid Main Memory Systems 111 |

| 7.2.2        | Development of Extended Techniques for    |

# **List of Figures**

| Figure 1.  | An example of <i>Vth</i> distributions for MLC NAND flash       |    |

|------------|-----------------------------------------------------------------|----|

|            | memory and primary Vth design parameters for the                |    |

|            | NAND requirements                                               | 8  |

| Figure 2.  | A conceptual timing diagram of the ISPP scheme                  | 11 |

| Figure 3.  | Normalized $T_{PROG}$ variations over different $V_{ISPP}$      |    |

|            | scaling ratios                                                  | 12 |

| Figure 4.  | An overall organization of CaFTL                                | 13 |

| Figure 5.  | Examples of the counter updating and the hot data               |    |

|            | identification of an LBA                                        | 15 |

| Figure 6.  | Illustration of self-healing SSD and an example of self-        |    |

|            | healing process                                                 | 16 |

| Figure 7.  | The effect of the self-heating on increasing $N_{P/E}^{max}$    | 16 |

| Figure 8.  | Example distributions of the data retention requirements.       | 17 |

| Figure 9.  | Experimental results for the SSD write response time            |    |

|            | speedup                                                         | 18 |

| Figure 10. | Comparison of the impacts of lowering $V_{Pgm}$ and $V_{Erase}$ |    |

|            | on NAND retention errors                                        | 23 |

| Figure 11. | The effect of erase voltage scaling on NAND endurance.          | 24 |

| Figure 12. | An illustration of an erase voltage control for the pro-        |    |

|            | posed erase time scaling                                        | 27 |

| Figure 13. | The effect of erase time scaling on NAND endurance              | 27 |

| Figure 14. | An example of NAND capability tuning for writing                       |    |

|------------|------------------------------------------------------------------------|----|

|            | data to a shallowly erased NAND block                                  | 28 |

| Figure 15. | The proposed write performance tuning                                  | 29 |

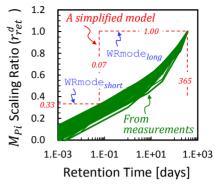

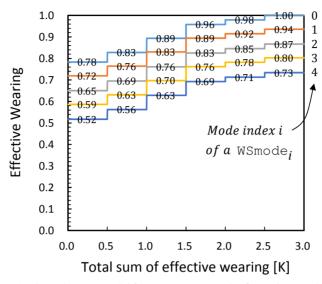

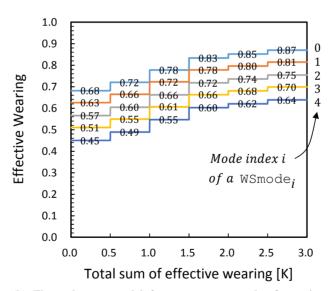

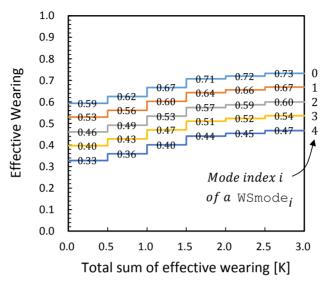

| Figure 16. | The simplified $M_{Pi}$ scaling models for retention capa-             |    |

|            | bility tuning                                                          | 32 |

| Figure 17. | The proposed NAND endurance models for DeVTS-                          |    |

|            | enabled NAND chips when long-retention write mode                      |    |

|            | WRmode $_{long}$ is used                                               | 37 |

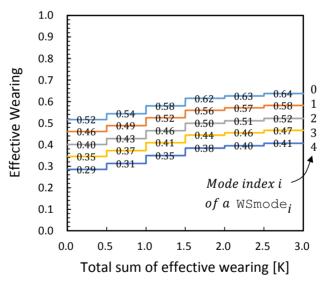

| Figure 18. | The proposed NAND endurance models for DeVTS-                          |    |

|            | enabled NAND chips when short-retention write mode                     |    |

|            | WRmode $_{short}$ is used                                              | 38 |

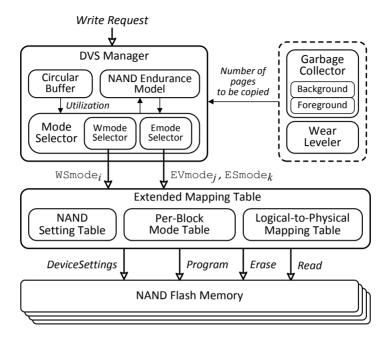

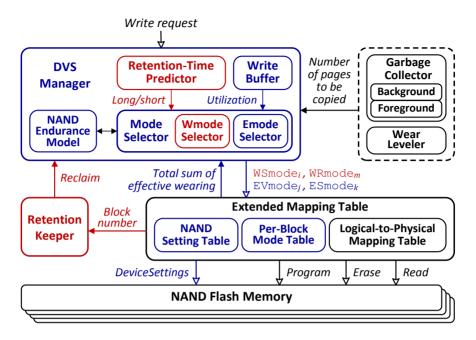

| Figure 19. | An organizational overview of dvsFTL                                   | 42 |

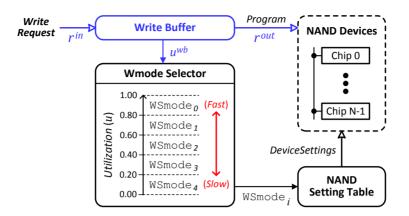

| Figure 20. | An overview of the write-speed mode selection in dvs-                  |    |

|            | FTL                                                                    | 43 |

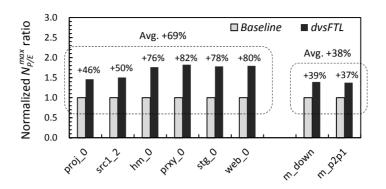

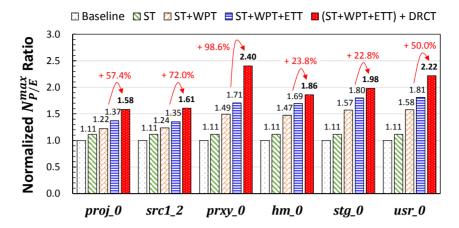

| Figure 21. | Comparisons of normalized $N_{P/E}^{\it max}$ ratios for eight traces. | 56 |

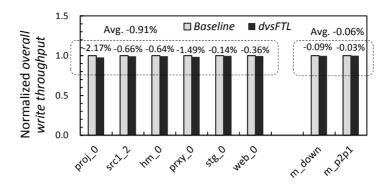

| Figure 22. | Comparisons of normalized overall write throughputs                    |    |

|            | for eight traces                                                       | 57 |

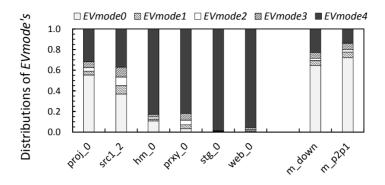

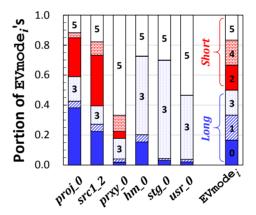

| Figure 23. | Distributions of EVmode's used                                         | 58 |

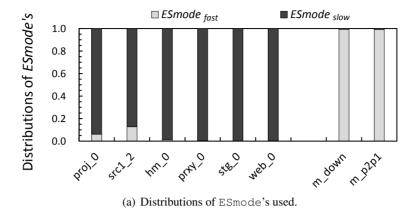

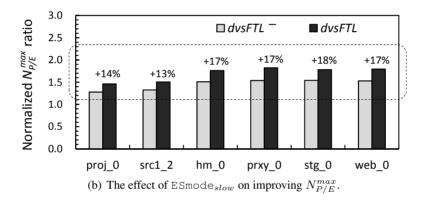

| Figure 24. | Distributions of ESmode's used and the effect of ESmode                | 's |

|            | on $N_{P/E}^{max}$                                                     | 59 |

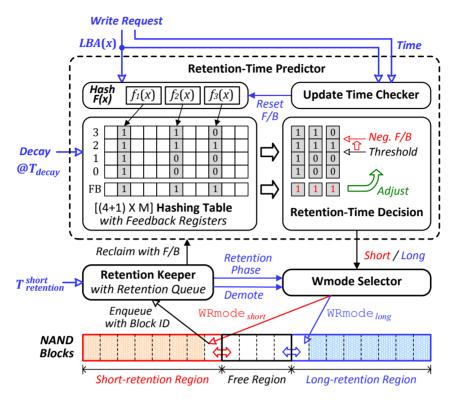

| Figure 25. | An organizational overview of dvsFTL+                                  | 63 |

| Figure 26. | A functional overview of the write-retention mode se-                  |    |

|            | lection and retention requirement management proce-                    |    |

|            | dures                                                                  | 65 |

| Figure 27  | Characteristics of write requests for six traces                       | 72 |

| Figure 28. | Comparisons of the endurance gain and distributions                |     |

|------------|--------------------------------------------------------------------|-----|

|            | of the $EVmode_i$ 's for six traces                                | 74  |

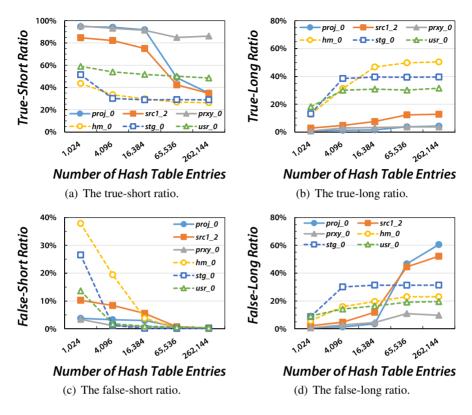

| Figure 29. | Variations of the prediction accuracy over different num-          |     |

|            | bers of hash table entries                                         | 80  |

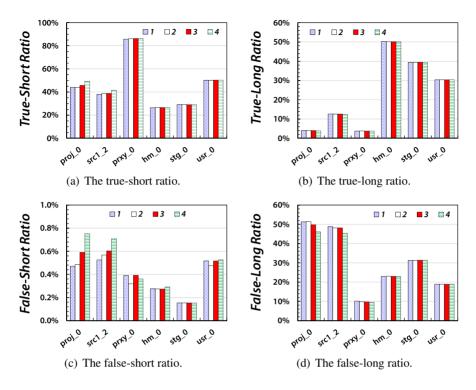

| Figure 30. | The effects of different numbers of hash functions on              |     |

|            | the accuracy of the retention-time predictor                       | 81  |

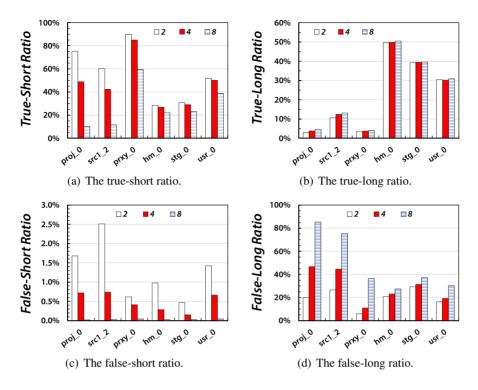

| Figure 31. | The effects of different decision levels on the accuracy           |     |

|            | of the retention-time predictor                                    | 83  |

| Figure 32. | Variations of the normalized $N_{P/E}^{\it max}$ ratios under dif- |     |

|            | ferent endurance-enhancing techniques for six traces               | 84  |

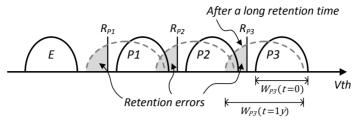

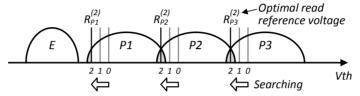

| Figure 33. | Examples of a NAND retention-error management pol-                 |     |

|            | icy                                                                | 92  |

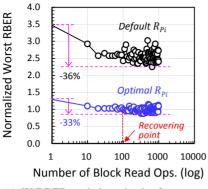

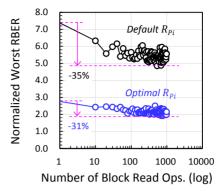

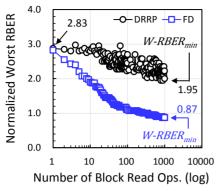

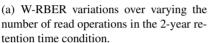

| Figure 34. | Normalized worst-case RBER (W-RBER) variations                     |     |

|            | over varying numbers of read operations under DRRP                 | 94  |

| Figure 35. | An example of charge movement after $n$ read pulse                 |     |

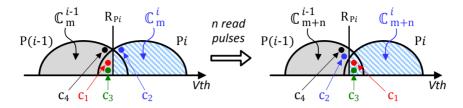

|            | applications                                                       | 96  |

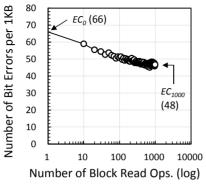

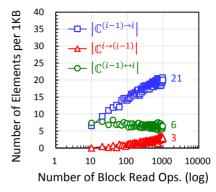

| Figure 36. | Measurement results for tracing the CM-component                   |     |

|            | changes in response to multiple read pulses                        | 98  |

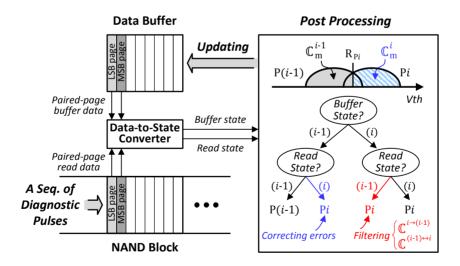

| Figure 37. | An overview of the current FD implementation with a                |     |

|            | selective error-correction procedure                               | 101 |

| Figure 38. | Comparisons of the data recovery capability under dif-             |     |

|            | ferent data recovery techniques                                    | 104 |

| Figure 39. | Comparisons of the data recovery speed between DRRP                |     |

|            | and FD                                                             | 105 |

### **List of Tables**

| Table 1. | A simplified $r_{dist}$ model over varying P/E cycles                | 34 |

|----------|----------------------------------------------------------------------|----|

| Table 2. | An example of a parameter set used to estimate effective             |    |

|          | wearing                                                              | 35 |

| Table 3. | The ${\tt EVmode}_j$ decision rule                                   | 36 |

| Table 4. | The latency variations of NAND functions used in the                 |    |

|          | experiments                                                          | 51 |

| Table 5. | Summary of two extFlashBench configurations                          | 52 |

| Table 6. | Normalized inter-arrival times of write requests for eight           |    |

|          | traces used for evaluations                                          | 55 |

| Table 7. | Comparisons of the overall write performance for six                 |    |

|          | traces                                                               | 75 |

| Table 8. | Accuracy of the retention-time predictor under different             |    |

|          | data separation techniques                                           | 78 |

| Table 9. | Variations of $N_{P/E}^{\max}$ ratios and the overall write through- |    |

|          | put over different buffer sizes for six traces                       | 86 |

| Table 10 | .Required numbers of read pulses to complete FD 1                    | 06 |

#### **Chapter 1**

#### Introduction

#### 1.1 Motivation

NAND flash-based solid-state drives (SSDs) are widely used in personal computing systems as well as mobile embedded systems. However, in enterprise environments, SSDs are employed in only limited applications because SSDs are not yet cost competitive with HDDs [1]. Fortunately, the prices for SSDs have fallen to the comparable level of HDDs by continuous semiconductor process scaling (e.g., 10 nm-node process [2]) combined with multi-leveling technologies (e.g., MLC [3] and TLC [4]). However, the limited endurance of NAND flash memory, which have declined further as a side effect of the recent advanced device technologies, is emerging as another major barrier to the wide adoption of SSDs. (NAND endurance is the ability of a memory cell to endure program/erase (P/E) cycling, and is quantified as the maximum number  $N_{P/E}^{max}$  of P/E cycles that the cell can tolerate while maintaining its reliability requirements [5].) For example, although the NAND capacity per die doubles every two years, the actual lifetime (which is proportional to the total NAND capacity and  $N_{P/E}^{\max}$ ) of SSDs does not increase as much as projected in the past seven years because  $N_{P/E}^{max}$  has declined by 70% during that period [6]. In order for SSDs to be commonplace in enterprise environments, the issues concerning NAND endurance

should be properly resolved.

Since the Lifetime  $L_C$  of an SSD with the total capacity C is proportional to the maximum number  $N_{P/E}^{max}$  of P/E cycles, and is inversely proportional to the total written data  $W_{day}$  per day,  $L_C$  (in days) can be expressed as follows (assuming a perfect wear leveling):

$$L_C = \frac{N_{P/E}^{max} \times C}{W_{day} \times WAF} \quad , \tag{1.1}$$

where WAF is a write amplification factor which represents the efficiency of an FTL algorithm. Many existing lifetime-enhancing techniques have mainly focused on reducing WAF by increasing the efficiency of an FTL algorithm. For example, by avoiding unnecessary data copies during garbage collection, WAF can be reduced [7]. In order to reduce  $W_{day}$ , various system-level techniques were proposed. For example, data de-duplication [8], data compression [9], and write traffic throttling [10] are such techniques. On the other hand, only a few system/software-level techniques have been proposed to increase  $N_{P/E}^{max}$ . Although several conceptual device-level techniques (e.g., a self-healing SSD [11]) were suggested regarding  $N_{P/E}^{max}$ , it is difficult for these to be employed in real systems because of their unrealistic hardware settings and critical side-effects.

By exploiting the tradeoff relationships between the NAND characteristics (e.g., capacity, performance, retention, and endurance), several cross-layer optimization techniques have been suggested. In order to improve SSD performance, for example, the retention relaxation technique [12] temporarily relaxes the NAND retention capability while FlexFS [13] flexibly reorga-

nizes the NAND capacity between SLC and MLC regions. Although these techniques exploited the device-level physical characteristics in the similar fashion of our work, their main goals are quite different from ours. Up until now, there have been a few particular suggestions to improve the NAND endurance by exploiting the tradeoff relationships between the NAND capabilities.

#### 1.2 Dissertation Goals

In this dissertation, we propose new cross-layer optimization techniques to extend the lifetime of NAND flash-based storage devices by exploiting the tradeoff relationship among NAND capabilities such as endurance, performance, and retention. The primary goals of this dissertation is as follows:

- Enabling a system software to exploit the tradeoff relationship between the endurance and the other capabilities of NAND flash memory.

- Developing system-level techniques to improve NAND endurance while maintaining the other NAND requirements.

- Providing reliability preservation techniques for NAND flash-based storage systems when flash-optimization techniques are widely employed in real environments.

#### 1.3 Contributions

The proposed cross-layer approach in this dissertation adds a new dimension to the decreasing lifetime problem of NAND flash-based storage devices as follows:

- A unified NAND endurance model which captures the tradeoff relationship between NAND endurance and the performance/retention capabilities of NAND flash memory is proposed. We reveal that endurance degradation is primarily caused by excessive erase operations, and suggest effective device-level means (i.e., various write-capability tuning techniques) of alleviating the negative impact of erase operations on NAND endurance. Based on the proposed NAND endurance model, a system software can adjust the internal operation voltages and times of NAND flash memory in a reliable fashion.

- System-level lifetime improvement techniques for NAND flash-based storage devices are presented. Based on the NAND endurance model, the proposed techniques dynamically change the NAND performance and retention capabilities for each program operation so that endurance-enhancing erase operations can be frequently used. Since the proposed lifetime improvement techniques can efficiently adapt to varying characteristics of I/O workload by accurately predicting the write performance and retention requirements, the overall performance and reliability requirements of storage systems are maintained while significantly improving NAND endurance.

• Reliability management techniques for NAND flash-based storage systems are suggested. Since the proposed lifetime improvement techniques aggressively tune down the NAND retention capability to improve NAND endurance, the retention-failure problem can be a serious technical issue for power/temperature-unstable computing environments. In order to preserve the data durability of the stored data in NAND flash memory, we introduce a novel data recovery technique which can efficiently and quickly recover corrupted data from retention failures.

Although this dissertation has mainly focused on improving NAND endurance, our proposed techniques can be extended to improve other requirements (e.g., performance, retention, and read-disturbs resistance) of storage systems. Moreover, since our techniques are entirely independent on data content, the existing flash-optimization techniques can be easily integrated into our proposed framework.

#### 1.4 Dissertation Structure

This dissertation consists of seven chapters. The first chapter presents a introduction to this dissertation while the last chapter serves as a conclusion with a summary and future work. The five intermediate chapters are organized as follows:

Chapter 2 reviews the operational principles of NAND flash memory and explains existing SSD lifetime improvement techniques closely related to this dissertation. Chapter 3 describes the dynamic NAND voltage and time scaling framework which includes erase voltage/time scaling and write capability tuning. Combining erase scaling and write tuning, a unified NAND endurance model for estimating their effects on NAND endurance is also suggested.

Chapter 4 proposes an SSD lifetime improvement technique using writeperformance tuning. We explain how to use a lower voltage and a slower speed for an erase operation and how to write data to a NAND block erased with a lower voltage. In addition, the effect of the proposed technique on NAND endurance is presented in detail.

Chapter 5 presents a comprehensive SSD lifetime improvement technique using both write-performance tuning and retention-capability tuning. We describe reliable prediction schemes to accurately predict the write performance and retention requirement and present efficient adaptation schemes to manage the NAND capabilities. We then show how much NAND endurance is improved and whether the overall NAND requirements are preserved.

Chapter 6 suggests a reliability management technique in order to recover data loss due to retention failures. Finally, we show how efficient the proposed technique is in terms of data recovery power and speed.

#### Chapter 2

#### **Background**

In order to improve NAND endurance, reliability and performance parameters are dynamically changed during run time in this dissertation. In this chapter, we review the basics of key *Vth* design parameters and the principals of a NAND program operation.

# 2.1 Threshold Voltage Window of NAND Flash Memory

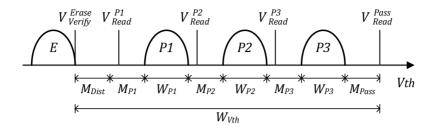

NAND flash memory stores data into cells by changing their *Vth* states depending on bit information, and restores data from cells by sensing their *Vth* states. Figure 1 illustrates an example of *Vth* distributions for an MLC NAND device which stores two bits in a cell by using four distinct *Vth* states distinguished by three read reference voltages.

Aside from serving as a non-volatile storage medium, MLC NAND devices are also required to meet the specified NAND requirements [5]. For example, read and program operations of an MLC device should be completed within 100  $\mu$ s and 1,600  $\mu$ s, respectively [6]. Moreover, even after 3,000 P/E cycles, it is required to support up to 400,000 read operations [6] as well as to retain its stored data for up to 1 year at 30 °C [14]. Since the *Vth* design parameters shown in Figure 1 are closely related to the NAND

Figure 1: An example of *Vth* distributions for MLC NAND flash memory and primary *Vth* design parameters for the NAND requirements.

requirements, the overall *Vth* distributions should be carefully designed to meet all the NAND requirements under the worst-case operating conditions for a storage product.

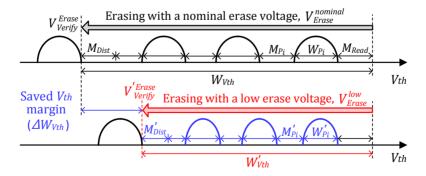

The upper Vth target  $V_{Verify}^{Erase}$  of the E state is one of the key factors in determining the total width  $W_{Vth}$  of Vth distributions. As  $V_{Verify}^{Erase}$  is lowered,  $W_{Vth}$  gets widened so that it is easier to optimize the Vth parameters for higher performance or longer retention capability. However, as a side-effect of the lowered  $V_{Verify}^{Erase}$ , NAND endurance may deteriorate because NAND blocks are more deeply erased [15]. Conversely, when a higher  $V_{Verify}^{Erase}$  is used, designing Vth distributions becomes more complex because less  $W_{Vth}$  is available.

The width  $W_{Pi}$  of a Vth distribution is mostly determined by the NAND write performance requirement. Since NAND flash memory generally uses the incremental step pulse programming (ISPP) scheme to form Vth distributions,  $W_{Pi}$  and the program time are directly affected by the ISPP step control. For example, when a fine-grained ISPP step control is used for a program operation,  $W_{Pi}$  can be shortened while the program time increases [15]. As a result,  $W_{Pi}$  is determined by the minimum achievable

width of a Vth distribution under the given program-time requirement.

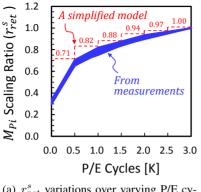

The Vth gap  $M_{Pi}$  between two adjacent states is mainly determined by the NAND retention requirement. When NAND memory cells are programmed and left for a long time, charge loss may occur because stress-induced damage in the tunnel oxide layer is likely to loosen stored charges. Since this charge-loss phenomenon may cause Vth changes, it is necessary for a sufficient  $M_{Pi}$  to tolerate the Vth changes. In order to guarantee the NAND retention requirement under the worst-case operating condition,  $M_{Pi}$  is determined by the maximum Vth change after the maximum number of P/E cycles and the specified retention time.

The Vth gap  $M_{Dist}$  between the E state and  $V_{Read}^{P1}$  primarily affects the program-disturbance resistance and read-disturbance resistance of NAND flash memory. When NAND memory cells are programmed or read, neighbor cells that belong to the E state may be softly programmed so that their Vths move to the right [5][16]. In order to compensate for the Vth changes due to these disturbances, a sufficient  $M_{Dist}$  should be reserved in the Vth window as shown in Figure 1. Typically,  $M_{Dist}$  is decided by the Vth changes after the maximum number of P/E cycles followed by the maximum number of read cycles.

The read pass voltage  $V_{Read}^{Pass}$  which affects the NAND read disturbance is another key factor in deciding the value of  $W_{Vth}$ . Since the NAND read disturbance has an exponential dependence on the  $V_{Read}^{Pass}$  [17],  $V_{Read}^{Pass}$  is usually fixed as low as possible in device design times. The Vth gap  $M_{Pass}$  between the P3 state and  $V_{Read}^{Pass}$  is also essential to fully turn on all the NAND memory cells in a block [5].

When the Vth design parameters are designated accordingly, all the Vth states are placed between  $V_{Verify}^{Erase}$  and  $V_{Read}^{Pass}$ . Therefore, the total width  $W_{Vth}$  of the Vth window is expressed as follows (for an MLC NAND device):

$$W_{Vth} = V_{Read}^{Pass} - V_{Verify}^{Erase}$$

$$= M_{Dist} + \sum_{i=1}^{3} W_{Pi} + \sum_{i=1}^{3} M_{Pi} + M_{Read}.$$

(2.1)

Since the *Vth* design parameters are highly related to one another, if a certain design parameter is to be changed, we should check its effect on the whole *Vth* window.

#### 2.2 NAND Program Operation

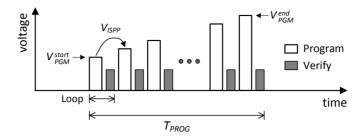

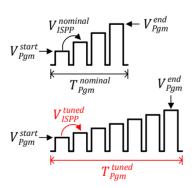

In order to form a threshold voltage distribution within a desired region, NAND flash memory generally uses the incremental step pulse programming (ISPP) scheme. As shown in Figure 2, the ISPP scheme gradually increases the program voltage by the  $V_{ISPP}$  step until all the memory cells in a page are located in a desired threshold voltage region. While repeating ISPP loops, once NAND cells are verified to have been sufficiently programmed, those cells are excluded from subsequent ISPP loops.

Since the program time is proportional to the number of ISPP loops (which are inversely proportional to  $V_{ISPP}$ ), the program time  $T_{PROG}$  can

Figure 2: A conceptual timing diagram of the ISPP scheme.

be expressed as follows:

$$T_{PROG} \propto \frac{V_{PGM}^{end} - V_{PGM}^{start}}{V_{ISPP}}.$$

(2.2)

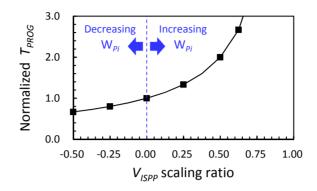

Figure 3 shows normalized  $T_{PROG}$  variations over different  $V_{ISPP}$  scaling ratios. (When a  $V_{ISPP}$  scaling ratio is set to x%,  $V_{ISPP}$  is reduced by x% of the nominal  $V_{ISPP}$ .) When a narrow threshold voltage distribution is needed,  $V_{ISPP}$  should be reduced for a fine-grained control, thus increasing the program time. Since the width of a threshold voltage distribution is proportional to  $V_{ISPP}$  [18], for example, if the nominal  $V_{ISPP}$  is 0.5 V and the width of a threshold voltage distribution is reduced by 0.25 V,  $V_{ISPP}$  also needs to be reduced by 0.25 V (i.e., a  $V_{ISPP}$  scaling ratio is 0.5), thus increasing  $T_{PROG}$  by 100%.

#### 2.3 Related Work

Since the lifetime of SSDs is inversely proportional to the total written data  $W_{day}$  per day and the write amplification factor WAF, existing lifetime-enhancing studies for SSDs have mainly focused on reducing  $W_{day}$

Figure 3: Normalized  $T_{PROG}$  variations over different  $V_{ISPP}$  scaling ratios.

or WAF. In this section, we briefly review typical examples of existing lifetime-enhancing techniques that reduce  $W_{day}$  and WAF, and explain a device-level technique for improving NAND endurance. Finally, we describe one of the cross-layer optimization techniques for better SSD performance, which is an integral motivation behind our work.

# 2.3.1 System-Level SSD Lifetime Improvement Techniques

#### **Data Compression Technique**

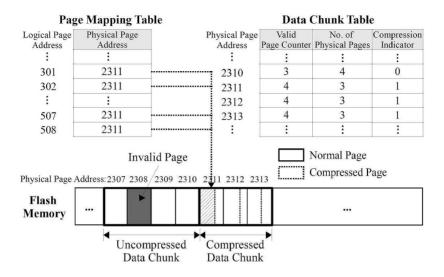

In order to reduce  $W_{day}$ , many types of flash-aware data compression techniques have been proposed to reduce the logical amount of write traffic to NAND chips. For example, the compression-aware flash translation layer (CaFTL) [9] was suggested to make key FTL modules (e.g., address mapping table and garbage collector) compression-aware so that compression efficiency could be maximized. Figure 4 shows the overall architecture of CaFTL with a page mapping table and a specially-designed data structure

(i.e., a data chunk table) for managing compressed data.

Figure 4: An overall organization of CaFTL.

In order to mitigate page fragmentation issues, CaFTL temporarily stores compressed data in a data buffer, and flushes four stored pages to NAND flash memory simultaneously. After flushing, compression-related information as shown in Figure 4 is updated to the data chunk table. Based on the data chunk table, CaFTL efficiently handles read requests and finds the most appropriate victim block during garbage collection. Moreover, CaFTL monitors the compression-ratio changes of input data so that unnecessary compression is avoided. Although data compression is an effective solution for reducing  $W_{day}$  in general, when poorly compressed data (e.g., multimedia data) are continuously incoming, the method's effectiveness in extending the SSD lifetime is significantly degraded. However, since our proposed techniques does not depend on data content, it can improve SSD lifetime

even when all the requested data is not compressed.

#### **Data Separation Technique**

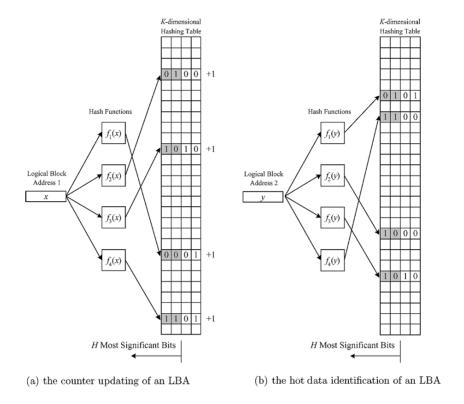

Since NAND flash memory does not allow *in-place-updates*, unnecessary data copies occur during garbage collection so that the logical amount of written data is actually amplified by WAF. In order to minimize WAF, several flash optimization techniques (e.g., advanced mapping schemes, TRIM command and data separation techniques) have been introduced. For example, Hsieh et al. suggested a multi-hash function based data separation technique for separating hot data (i.e., frequently updated data) and cold data (i.e., rarely updated data) with a reasonable hardware overhead [7]. Since hot data are updated within a short time, if such hot data are aggregated in the same NAND block, there is a high probability that a dead block (i.e., a NAND block where all the pages are invalidated) or a near-dead block can be selected during garbage collection, thus reducing WAF. Figure 5 shows an example of the hot data identification process with K independent hash functions to hash a given LBA into the multiple entries of an M-entry hash table [7]. Whenever write requests are issed, each counter entry corresponding to a hashed value is incremented. In order to capture recent hot data, all the counter entries are decayed every predefined number of input requests. If the H most significant bits of every counter corresponding to K hash functions contain a non-zero value, that LBA is classified as hot data. Although the main purpose of the data separation technique is quite different from our proposed technique, its ability to identify hot data can contribute to increasing the efficiency of the proposed lifetime improvement techniques. For ex-

Figure 5: Examples of the counter updating and the hot data identification of an LBA.

ample, if the data separator can accurately identify hot data, the retentiontime requirements of such hot data can be relaxed because hot data will be updated in the near-future.

#### 2.3.2 Device-Level Endurance-Enhancing Technique

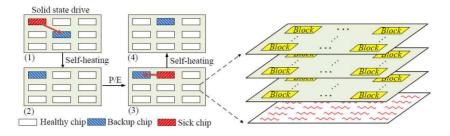

Wu *et al.* presented a device-level endurance enhancement technique that boosts self-recovery speed by heating a flash chip under high temperature [11]. Figure 6 shows the self-healing SSD architecture and its self-healing process. When a sick chip (i.e., a NAND chip that is almost worn-

Figure 6: Illustration of self-healing SSD and an example of self-healing process.

Figure 7: The effect of the self-heating on increasing  $N_{P/E}^{max}$ .

out) is detected, its entire data is copied to the extra backup chip during device idle times. After data copy operations are completed, a sick chip is heated at  $200\,^{\circ}\mathrm{C}$  for 35 minutes. Figure 7 shows the effect of self-heating on increasing  $N_{P/E}^{max}$ . By leveraging the temperature-accelerated recovery, it improved the endurance of SSDs up to fivefold. A major drawback of this approach is that it requires extra energy consumption to heat flash chips and lowers the reliability of a storage device. Our proposed technique improves

Figure 8: Example distributions of the data retention requirements.

the endurance of NAND devices by lowering the erase voltage and slowing down the erase speed without any serious side effects.

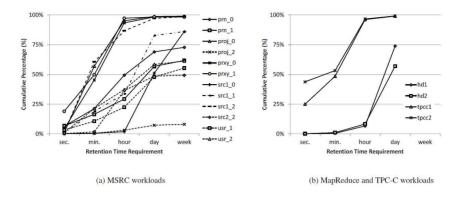

# 2.3.3 Cross-Layer Optimization Techniques Exploiting NAND Tradeoffs

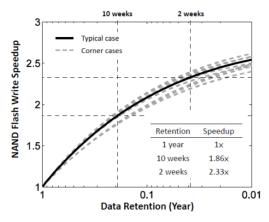

Liu *et al.* proposed a retention relaxation technique to improve SSDs by relaxing their NAND retention capabilities [12]. This technique is motivated by their observation that in typical enterprise workloads, a considerable portion of written data to SSDs is likely to be updated soon (e.g., less than a day as shown in Figure 8). Since this observed updated time is much shorter than the NAND retention-time specification (i.e., 1 year), the retention relaxation technique increases the ISPP step voltage so that the NAND write performance is increased while shortening the retention capability.

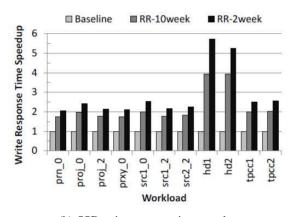

Figure 9(a) shows how much the write speed increases as the retentiontime requirements are relaxed. For example, if the retention-time requirement is relaxed to 2 weeks, the NAND write speed can be increased to 2.33x

(a) Relationship between the NAND retention times and the NAND write speedup.

(b) SSD write response time speedup.

Figure 9: Experimental results for the SSD write response time speedup.

of the write speed when 1-year retention-time is required. Figure 9(b) shows the overall write speedup of SSDs for 11 workloads under different retention capabilities. When the retention capability is relaxed to only 2 weeks, the overall SSD write response time was reduced by 160% on average.

The main weakness of this technique is that its effectiveness on improving SSD performance is entirely dependent on the workload conditions. Since this technique always relaxes the NAND retention capability without consideration of data characteristics (e.g., the update frequency), when most of the written data are not updated within a predefined retention time, this data should be rewritten by a background data refresh process. When there is enough idle times between consecutive write requests, the side-effect of such background data refresh operations can be hidden as shown in the hd1 and hd2 cases of Figure 9(b). However, when the idle time is not sufficient, the write performance speedup may decrease as shown in the prn\_0 case of Figure 9(b).

Another technical issue is that this technique did not take into account *retention-failure problems*. When a power failure occurs and continues for a long time, retention-relaxed data may not be retrieved because a background data refresh process does not work during power failures. In order for this kind of aggressive flash optimization techniques to be widely employed, the retention-failure problem should be adequately resolved.

Although the main goal of this technique is quite different from ours, its technical concept is one of the important motivations in the way that it actively exploited the tradeoff relationships between the NAND capabilities. For example, the concept of a retention relaxation substantially contributed to the development of our write-age tuning mode.

#### **Chapter 3**

# **Dynamic Erase Voltage and Time Scaling**

In this chapter, we propose a unified framework, called **D**ynamic **E**rase Voltage and Time Scaling (DeVTS), which enables a system software to exploit the tradeoff relationship between the NAND endurance and erase voltages/times. The DeVTS framework is motivated by our NAND device physics study that NAND endurance is degraded primarily during erase operations. Since the probability of oxide damage (which is known as the main cause of endurance degradation) has an exponential dependence on the stress voltage [19], reducing the stress voltage (i.e., the erase voltage) is the most effective means of improving NAND endurance. Moreover, given an erase operation, since a nominal erase voltage tends to excessively damage NAND memory cells in the beginning of an erase operation [20], slowing down the erase speed (i.e., monotonically increasing the erase voltage from a low voltage to the nominal voltage over a sufficiently long time period) can minimize the damage [15][21], thus additionally improving NAND endurance. By modifying a NAND device to support multiple erase voltage and time scaling modes (which have different impacts on NAND endurance), and allowing a flash software to select the most appropriate erase scaling modes depending on a workload, DeVTS has a significant potential to increase  $N_{P/E}^{max}$ .

However, in order to write data to a NAND block erased with a lower erase voltage, it is required to use special write modes that can form threshold voltage (*Vth*) distributions within a narrower *Vth* window. Since the *Vth* window (i.e., the total width of *Vth* margins for a NAND cell) is tightly designed to guarantee all the specified NAND requirements (i.e., endurance, performance and retention), in order to assign more *Vth* margin to the endurance, the *Vth* margin for the other requirements needs to be reduced instead. For example, a slow write mode with a fine-grained program control can shorten the width of a *Vth* distribution so that the required *Vth* margin for performance can be saved while the NAND program time increases [15]. Similarly, a short-retention write mode, which reduces the *Vth* gap between two adjacent *Vth* states, can save the required *Vth* margin for retention while the retention capability is sacrificed [16] [12].

In order to estimate the impact of the special write modes (i.e., slow write modes or short-retention write modes) on NAND endurance, we develop a unified NAND endurance model which accurately captures the trade-off relationships between NAND endurance and NAND performance/retention capabilities. Based on the NAND endurance model, when a slow or short-retention write mode is used at the expense of the performance or retention capability, we can estimate how much the erase voltage can be lowered and its impact on NAND endurance.

#### 3.1 Erase Voltage and Time Scaling

#### 3.1.1 Motivation

The physical mechanism of endurance degradation is closely related to stress-induced damage in the tunnel oxide layer of a NAND memory cell [16]. Since the probability of oxide damage has an exponential dependence on the stress voltage [19], lowering the stress voltage (i.e., the program voltage  $V_{Pgm}$  or the erase voltage  $V_{Erase}$ ) during P/E cycles can be an effective means of improving NAND endurance.

Although the maximum  $V_{Pgm}$  to complete a program operation is usually higher than  $V_{Erase}$ , NAND endurance is primarily degraded during erase operations. This is because the stress time interval of an erase operation is about 100 times longer than that of a program operation. Furthermore, since written data on a certain cell is likely to be changed randomly, the probability that the cell consecutively experiences the maximum  $V_{Pgm}$  during P/E cycles is very low. On the contrary, all the cells in a NAND block experience  $V_{Erase}$  at all times during P/E cycles. Therefore, we can assume that changing  $V_{Erase}$  has a more significant impact on NAND endurance.

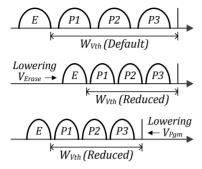

In order to verify our assumption, we evaluated the effects of two different stress-voltage-reduction policies, shown in Figure 10(a), on NAND endurance. In the 'lowering  $V_{Erase}$ ' policy,  $W_{Vth}$  shrinks to the right direction (compared to the default case) so that  $V_{Erase}$  is lowered by 1 V while  $V_{Pgm}$  is not changed. On the other hand, in the 'lowering  $V_{Pgm}$ ' policy,  $W_{Vth}$  shrinks to the left direction so that the maximum  $V_{Pgm}$  is reduced by 1 V while  $V_{Erase}$  is maintained. In our evaluation, ten blocks out of two

(a) Illustrations of two different stressvoltage-reduction policies over the default case.

(b) Variations of the numbers of retention errors per 1 KB under three different policies.

Figure 10: Comparison of the impacts of lowering  $V_{Pgm}$  and  $V_{Erase}$  on NAND retention errors.

20-nm node NAND chips were selected for each policy. As the main evaluation metric, we measured the number of retention errors (i.e., bit errors after 3K pre-cycling and 1 hour's baking at  $100\,^{\circ}$ C [22]) per 1-KB cells because it reflects the effective degree of NAND wearing [15]. As shown in Figure 10(b), when the 'lowering  $V_{Pgm}$ ' policy was used, the number of retention errors was reduced by only 5.3%, on average, over the default case. However, when the 'lowering  $V_{Erase}$ ' policy was used, the number of retention errors was reduced by 34.7%, on average, over the default case. These results clearly show that lowering  $V_{Erase}$  is much more effective than lowering  $V_{Pgm}$  in improving NAND endurance.

# 3.1.2 Erase Voltage Scaling

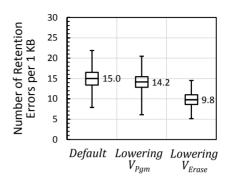

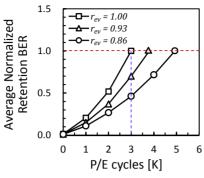

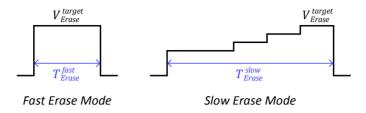

In order to evaluate the effect of erase voltage scaling on NAND endurance, we performed NAND cycling tests by using different  $V_{Erase}$ 's. In a

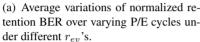

(b) Variations of effective wearing over varying  $r_{ev}$ 's.

Figure 11: The effect of erase voltage scaling on NAND endurance.

cycling test, program and erase operations are repeated 3,000 times. Our cycling tests for each case were performed with 100 blocks out of five 20-nm node NAND chips. After cycling tests, we measured the NAND retention BER (i.e., the number of retention errors divided by the total number of cells) for each block as a measure of wearing degree of NAND memory cells. The measured BERs were normalized over the retention BER when the nominal erase voltage  $V_{Erase}^{nominal}$  was used. Figure 11(a) shows how the retention BER changes, on average, as the number of P/E cycles increases while different  $V_{Erase}$ 's are used. We represent different  $V_{Erase}$ 's using an erase voltage scaling ratio  $r_{ev}$  ( $0 \le r_{ev} \le 1$ ). When  $r_{ev}$  is set to x,  $V_{Erase}$  is reduced by  $(1-x)\times V_{Erase}^{nominal}$ . As shown in Figure 11(a), the more  $V_{Erase}$  is reduced (i.e., the lower  $r_{ev}$ 's), the lower the retention BERs. For example, when  $r_{ev}$  is set to 0.93, the normalized retention BER is reduced by 30% after 3K P/E cycles over the  $V_{Erase}^{nominal}$  case.

Since different  $V_{Erase}$ 's affect NAND endurance by different amounts,

we introduce a new endurance metric, called *effective wearing*, which represents the effective degree of NAND wearing per a P/E cycle. Based on a linear approximation model<sup>1</sup> which simplifies the NAND wear-out behavior over P/E cycles as shown in Figure 11(a), we represent effective wearing with a normalized retention BER after 3K P/E cycles. For example, when  $V_{Erase}^{nominal}$  is used (i.e.,  $r_{ev} = 1.00$ ), effective wearing is 1.00. On the other hand, when  $V_{Erase}$  is reduced by 7% (i.e.,  $r_{ev} = 0.93$ ), effective wearing becomes 0.70. As shown in Figure 11(b), since effective wearing has a near-linear dependence on  $r_{ev}$ , effective wearing for a different  $r_{ev}$  can be estimated by a linear regression model. In this dissertation, we will use a NAND endurance model with five erase voltage modes  $EVmode_i$ 's which have five different  $r_{ev}$ 's.

The effect of lowering  $V_{Erase}$  on NAND endurance can be estimated by accumulating effective wearing for each P/E cycle. After 3K P/E cycles, for example, the total sum  $\Sigma EW$  of effective wearing with  $V_{Erase}^{nominal}$  is  $3,000~(=1.00\times3000)$ , but when  $r_{ev}$  is set to 0.93,  $\Sigma EW$  is only 2,100  $(=0.70\times3000)$ . Since NAND reliability is maintained until  $\Sigma EW$  reaches 3,000,  $N_{P/E}^{max}$  can be increased by 1,286 (=(3000-2100)/0.70) when  $V_{Erase}$  is reduced by 7% over  $V_{Erase}^{nominal}$ .

Since we did not have access to NAND chips from different manufacturers, we could not prove that our test results can be generalized. However,

<sup>&</sup>lt;sup>1</sup>In this dissertation, we use a linear approximation model which simplifies the wear-out behavior over P/E cycles. Our current linear model can overestimate the effective wearing under low erase voltage scaling ratios while it can underestimate the effective wearing under high erase voltage scaling ratios. We verified that, by the combinations of over-/underestimations of the effective wearing in our model, the current linear model achieves a reasonable accuracy with an up to 10% overestimation [20] while supporting a simple software implementation.

since our tests are based on widely-known device physics which have been investigated by many device engineers and researchers, we are convinced that the consistency of our results would be maintained as long as NAND flash memories use the same physical mechanism (i.e., FN-tunneling) for program and erase operations. We believe that our results will also be effective for future NAND devices as long as their operations are based on the FN-tunneling mechanism. It is expected that current 2D NAND devices will gradually be replaced by 3D NAND devices, but the basis of 3D NAND is still the FN-tunneling mechanism.

## 3.1.3 Erase Time Scaling

Endurance degradation is directly proportional to  $V_{Erase}$  in an erase operation as described in Section 3.1.2. When  $V_{Erase}$  is applied to a NAND block, however, NAND memory cells are likely to be over-damaged by  $V_{Erase}$ . Since the actual voltage across the tunnel oxide layer is the sum of  $V_{Erase}$  and the  $V_{th}$  of a cell [20], an unintended higher (than  $V_{Erase}$ ) voltage may cause additional damage (which is dependent on the cell's  $V_{th}$ ) to the cell until all the programmed cells are sufficiently erased. For example, NAND memory cells which have higher  $V_{th}$ 's (e.g., the  $P_{th}$ 3 state) are more damaged than those that have lower  $V_{th}$ 's (e.g., the  $E_{th}$ 5 state).

In order to minimize oxide damage in the beginning of an erase operation, it is necessary to properly control the applied  $V_{Erase}$  so that the actual voltage across the tunnel oxide layer does not exceed  $V_{Erase}$  throughout the erase operation. We implemented this idea by modifying the existing incremental step pulse erasing (ISPE) scheme [23] so that the applied  $V_{Erase}$

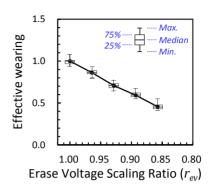

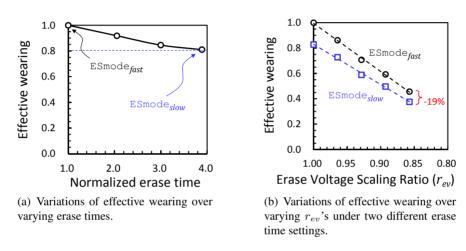

Figure 12: An illustration of an erase voltage control for the proposed erase time scaling.

Figure 13: The effect of erase time scaling on NAND endurance.

gradually increases from a low voltage (e.g.,  $V_{Erase}$  — the average Vth of the P3 state) to  $V_{Erase}$  over a sufficiently long time period as shown in Figure 12. However, when the modified ISPE scheme is used for an erase operation, the erase time (e.g.,  $T_{Erase}^{slow}$  shown in Figure 12) inevitably increases because more ISPE loops are needed to complete the erase operation.

As shown in Figure 13(a), effective wearing decreases near-linearly as the erase time increases. For example, when the erase time increases three-fold, effective wearing is reduced, on average, by 19%. We represent the erase speed mode with a default erase time by  $ESmode_{fast}$  while that with

a long erase time is represented by  $ESmode_{slow}$ . As shown in Figure 13(b), the effect of  $ESmode_{slow}$  on improving NAND endurance can be exploited whenever longer erase times are acceptable regardless of  $r_{ev}$ .

## 3.2 Write Capability Tuning

If a NAND block is *shallowly erased* (i.e., erased with a lower voltage), the available Vth window for a program operation is also reduced. This is because  $W_{Vth}$  is mainly affected by  $V_{Verify}^{Erase}$  (which determines the requirement of  $V_{Erase}$ ) as explained in Section 2.1. For example, as shown in Figure 14, if a NAND block is shallowly erased with a low erase voltage  $V_{Erase}^{low}$  (which is lower than  $V_{Erase}^{nominal}$ ),  $W_{Vth}$  is reduced by a saved Vth margin  $\Delta W_{Vth}$  (which is proportional to the voltage difference between  $V_{Erase}^{nominal}$  and  $V_{Erase}^{low}$ ). Since Vth distributions should be formed within the given Vth window, when  $V_{Erase}^{low}$  is used in an erase operation, it is necessary to use special write modes which adjust Vth design parameters (e.g.,  $W_{Pi}$ ,  $M_{Pi}$  and  $M_{Dist}$ ) so that  $W_{Vth}$  is reduced by at least  $\Delta W_{Vth}$ . In this sec-

Figure 14: An example of NAND capability tuning for writing data to a shallowly erased NAND block.

tion, we describe several write capability tuning techniques to save  $W_{Vth}$ , and present the NAND endurance model to estimate the impact of the proposed tuning techniques on NAND endurance.

## 3.2.1 Write Performance Tuning

In order to reduce  $W_{Pi}$ 's, a fine-grained ISPP step control is needed because  $W_{Pi}$  is directly proportional to the ISPP step voltage  $V_{ISPP}$  [18]. However, since the number of ISPP loops to complete a program operation is inversely proportional to  $V_{ISPP}$  [15], the program time  $T_{Pgm}$  inevitably increases as shown in Figure 15(a) if narrow Vth distributions are required. Figure 15(b) shows how much  $V_{ISPP}$  can be reduced as  $T_{Pgm}$  increases.  $T_{Pgm}$  was normalized over the nominal program time  $T_{Pgm}^{nominal}$  (e.g., 1,300  $\mu$ s [3]). We denote  $V_{ISPP}$  scaling ratio over the nominal ISPP step voltage  $V_{ISPP}^{nominal}$  by  $T_{ISPP}$  ( $0 \le T_{ISPP} \le 1$ ). When  $T_{ISPP}$  is set to  $T_{ISPP}$  is reduced by  $T_{ISPP}$  ( $T_{ISPP}$ ).

(a) An illustration of the write performance tuning technique.

(b) The relationship between the normalized  $T_{Pgm}$  and  $r_{ISPP}$ .

Figure 15: The proposed write performance tuning.

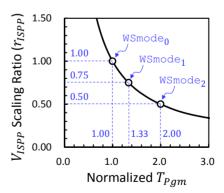

In our proposed write-performance tuning technique, we define three different write-speed modes,  $WSmode_0$ ,  $WSmode_1$ , and  $WSmode_2$ , as shown in Figure 15(b).  $WSmode_0$  is the fastest write mode which has the same  $T_{Pgm}$  as that of the nominal write mode, but cannot reduce  $V_{ISPP}$ . Alternatively,  $WSmode_2$ , the slowest write mode, has a  $T_{Pgm}$  two times longer (i.e., the normalized  $T_{Pgm}$  is 2.0) than the nominal write mode, but can reduce  $V_{ISPP}$  by 50% (i.e.,  $r_{ISPP}$  is 0.50) over  $V_{ISPP}^{nominal}$ .

Since  $W_{Pi}$  has a linear dependence on  $V_{ISPP}$  (which is determined by the write-performance requirement as shown in Figure 15(b)),  $\Delta W_{Vth}$  by tuning  $T_{Pqm}$  is expressed as follows (for an MLC NAND device):