공학박사학위논문

# Write Avoidance Schemes for Non-Volatile Memory based Last-Level Cache

비휘발성 메모리 기반의 최종 레벨 캐시를 위한 쓰기 회피 기법

2016년 2월

서울대학교 대학원 전기·컴퓨터공학부

최주희

## ABSTRACT

Non-volatile memory (NVM) is considered to be a promising memory technology for last-level caches (LLC) due to its low leakage of power and high storage density. However, NVM has some drawbacks including high dynamic energy when modifying NVM cells, long latency for write operations, and limited write endurance. To overcome these problems, the thesis focuses on two approaches: cache coherence and NVM capacity management policy for hybrid cache architecture (HCA).

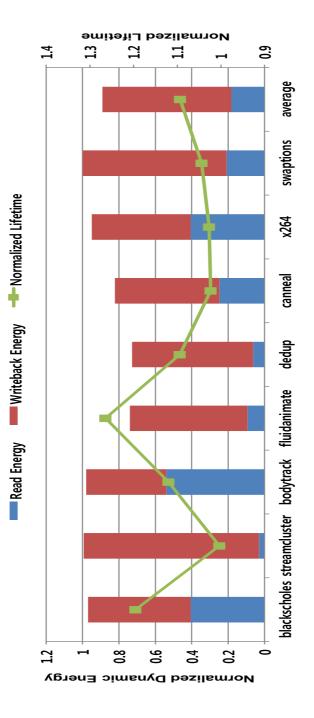

First, we review existing cache coherence protocols under the condition of NVM-based LLCs. Our analysis reveals that the LLCs perform unnecessary write operations because legacy protocols have very pay little attention to reducing the number of write accesses to the LLC. Therefore, a write avoidance cache coherence protocol (WACC) is proposed to reduce the number of write operations to the LLC.

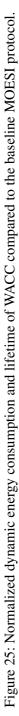

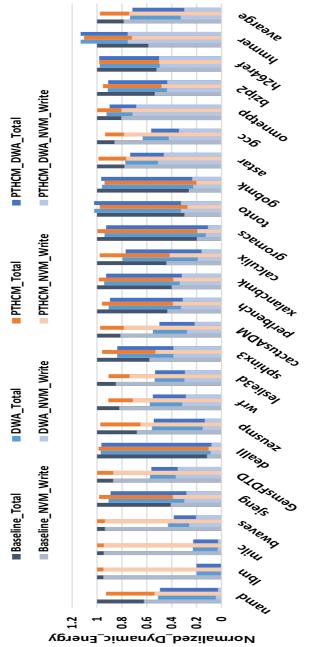

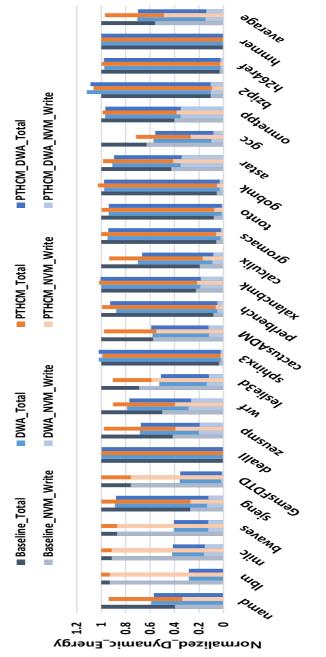

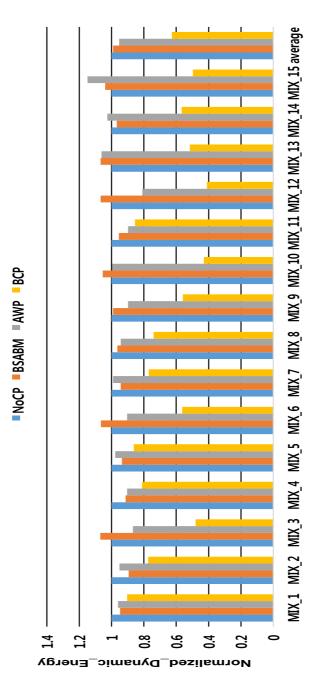

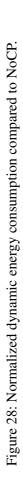

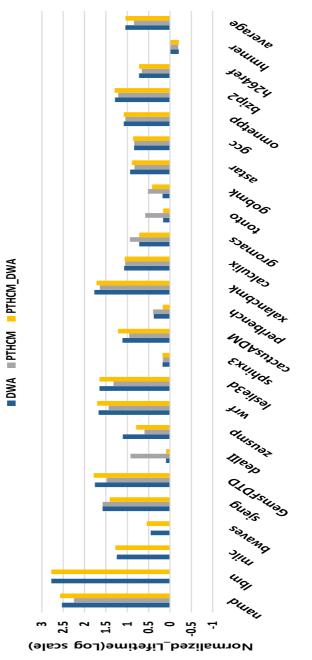

In addition, novel HCA schemes are proposed to efficiently utilize SRAM in the thesis. Previous studies on HCA have concentrated on detecting write-intensive blocks and placing them into the SRAM ways. However, unlike other studies, a dynamic way adjusting algorithm (DWA) and a linefill-aware cache partitioning (LCP) calculate the optimal size of NVM ways and SRAM ways in order to minimize the NVM write counts and assigning the corresponding number of NVM ways and SRAM ways to cores. The simulation results show that WACC achieves a 13.2% reduction in the dynamic energy consumption. For HCA schemes, the dynamic energy consumption of DWA and LCP is reduced by 26.9% and 37.2%, respectively.

**Index Terms :** Cache memories, Emerging technologies, Heterogeneous (hybrid) memory systems, Low-power design, Cache coherence, Cache partitioning

Student Number: 2012-30234

# CONTENTS

| I.  | In  | troduction               |                                         |      | 1  |

|-----|-----|--------------------------|-----------------------------------------|------|----|

|     | 1.1 | Purpose of the thesis .  |                                         |      | 1  |

|     | 1.2 | Background               |                                         |      | 3  |

|     | 1.3 | Motivation               |                                         |      | 4  |

|     | 1.4 | Contributions            |                                         |      | 5  |

|     | 1.5 | Organization of the thes |                                         |      | 8  |

| II. | Re  | elated work              |                                         |      | 9  |

|     | 2.1 | Hybrid cache architectu  | • • • • • • • • • • • • • • • • • • • • |      | 9  |

|     |     | 2.1.1 Write intensity p  | ediction studies                        |      | 11 |

|     |     | 2.1.2 Static approache   |                                         |      | 11 |

|     |     | 2.1.3 Hybrid cache ar    | nitecture for main me                   | mory | 12 |

|     | 2.2 | Cache partitioning scher | es                                      |      | 14 |

| ш   | . W | rite avoidance cache col | rence protocol                          |      | 15 |

|    | 3.1  | Limita  | tion of existing cache coherence protocol       | 15 |

|----|------|---------|-------------------------------------------------|----|

|    | 3.2  | Write   | avoidance cache coherence protocol              | 19 |

| IV | . NV | VM cap  | acity management policy for hybrid cache archi- |    |

|    | tec  | cture . |                                                 | 22 |

|    | 4.1  | NVM     | capacity management policy                      | 22 |

|    |      | 4.1.1   | Concept of NVM capacity management policy       | 23 |

|    |      | 4.1.2   | Feasibility of NVM capacity management policy   | 27 |

|    | 4.2  | Dynan   | nic way adjusting                               | 37 |

|    |      | 4.2.1   | Maximum stack distance                          | 37 |

|    |      | 4.2.2   | Adjusting the number of NVM ways                | 41 |

|    |      | 4.2.3   | Algorithm of dynamic way adjusting              | 42 |

|    | 4.3  | Cache   | partitioning for hybrid cache architecture      | 46 |

|    |      | 4.3.1   | Linefill-aware cache partitioning               | 49 |

|    |      | 4.3.2   | Metrics for cache partitioning                  | 50 |

|    |      | 4.3.3   | Algorithm for cache partitioning                | 59 |

|    | 4.4  | Overhe  | ead of NVM capacity management policy           | 68 |

| V. | Ex     | perimental results         |

|----|--------|----------------------------|

|    | 5.1    | Experimental environment   |

|    | 5.2    | Write access to NVM        |

|    | 5.3    | Dynamic energy consumption |

|    | 5.4    | Lifetime                   |

|    | 5.5    | Multi-core environment     |

| VI | . Co   | nclusion                   |

|    | 6.1    | Conclusion                 |

|    | 6.2    | Future work                |

| Re | feren  | ces                        |

| Ab | ostrac | t in Korean                |

# **List of Figures**

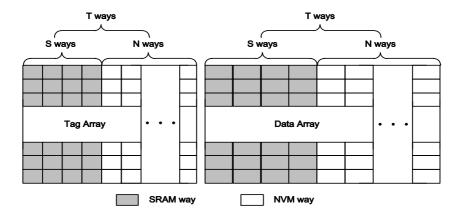

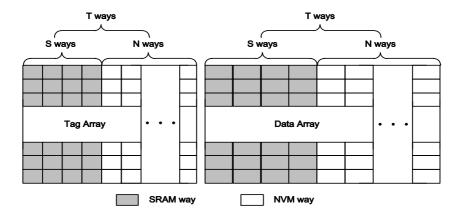

| Figure 1.  | Basic structure of hybrid cache architecture (HCA) | 10 |

|------------|----------------------------------------------------|----|

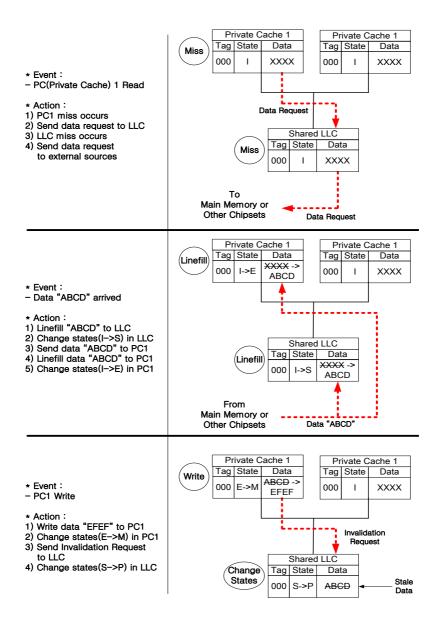

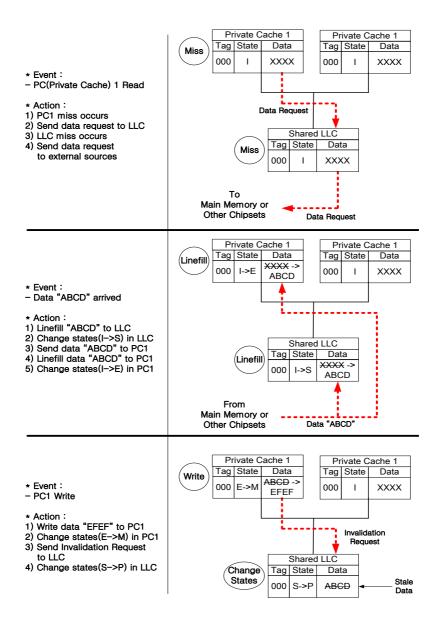

| Figure 2.  | Conventional cache coherence protocol              | 17 |

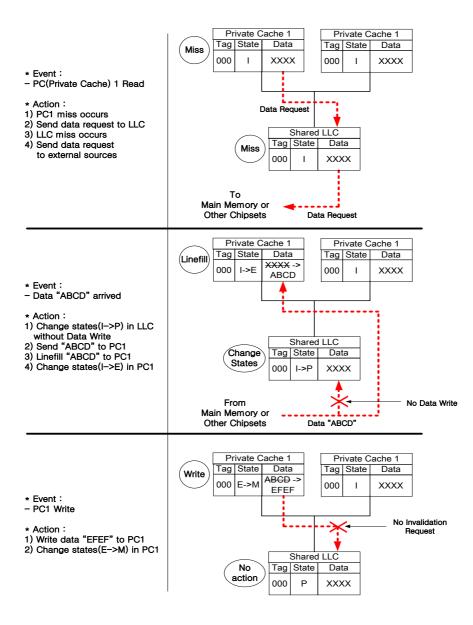

| Figure 3.  | Write avoidance cache coherence protocol (WACC).   | 18 |

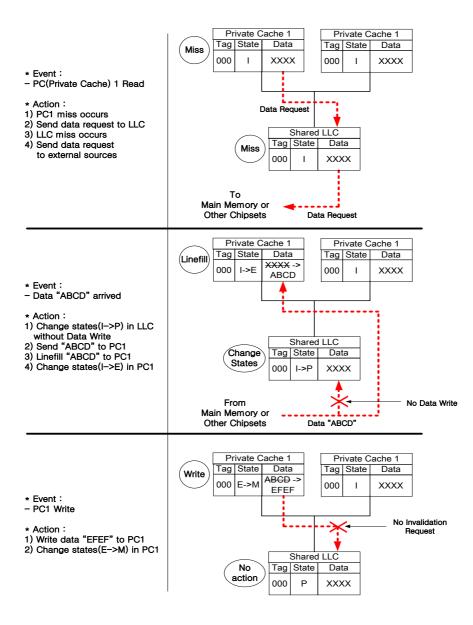

| Figure 4.  | State transition diagrams for WACC                 | 20 |

| Figure 5.  | Example for NVM capacity management policy         | 26 |

| Figure 6.  | Miss rates with various number of NVM ways         | 32 |

| Figure 7.  | Normalized total write counts of HCA               | 34 |

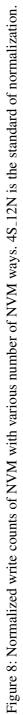

| Figure 8.  | Normalized total write counts of NVM               | 36 |

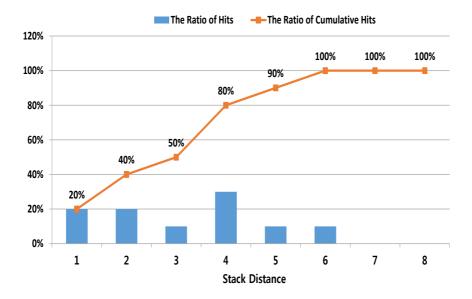

| Figure 9.  | Stack distance histogram                           | 38 |

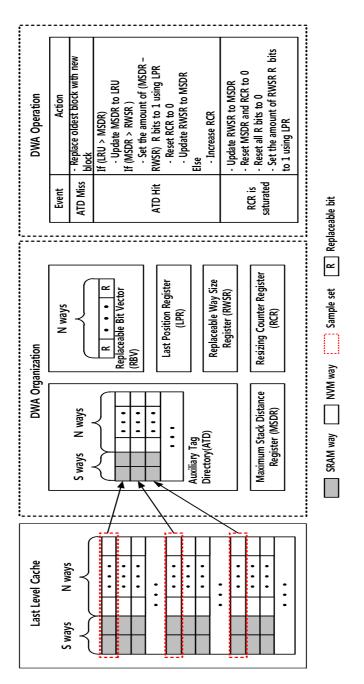

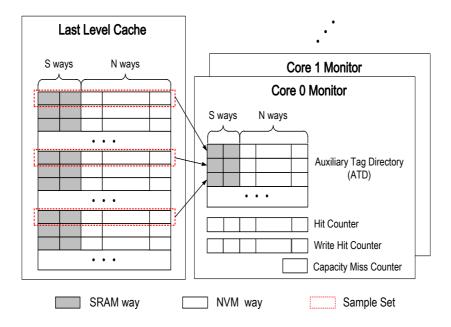

| Figure 10. | Overall structure of dynamic way adjusting (DWA)   | 40 |

| Figure 11. | Example of way shifting                            | 44 |

| Figure 12. | Algorithm for DWA.                                 | 45 |

| Figure 13. | Examples of cache partitioning for HCA             | 48 |

| Figure 14. | Example of stack property.                         | 51 |

| Figure 15. | Examples of miss counts change $(\Delta M)$ and write counts |    |

|------------|--------------------------------------------------------------|----|

|            | change ( $\Delta W$ )                                        | 56 |

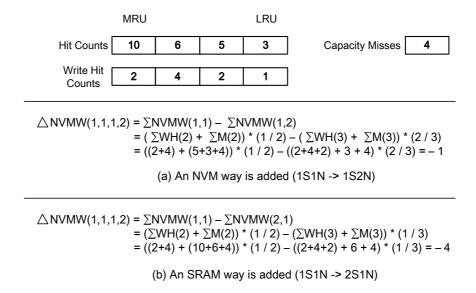

| Figure 16. | Examples of NVM write counts change ( $\Delta NVMW$ )        | 59 |

| Figure 17. | Algorithm of linefill-aware cache partitioning (LCP).        | 60 |

| Figure 18. | Overall structure of LCP                                     | 63 |

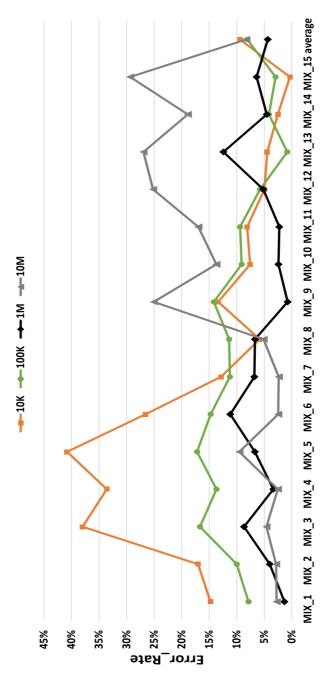

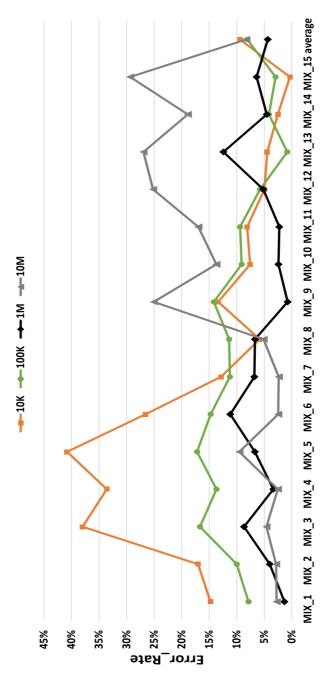

| Figure 19. | Error rates for LCP.                                         | 65 |

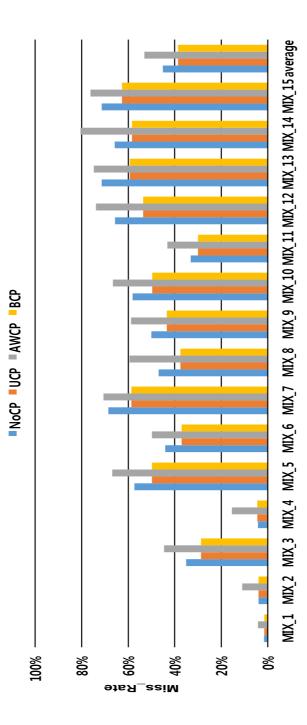

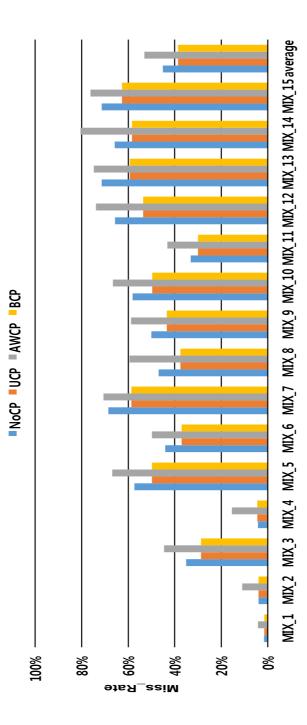

| Figure 20. | Miss rates for LCP.                                          | 67 |

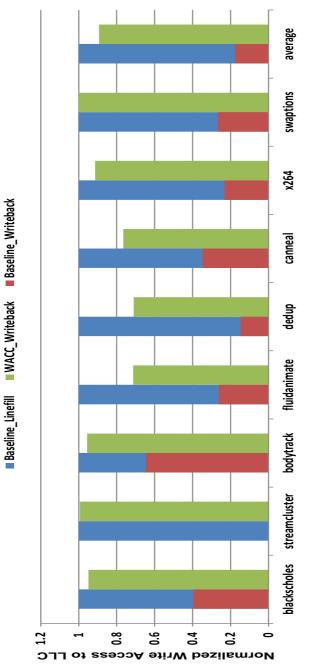

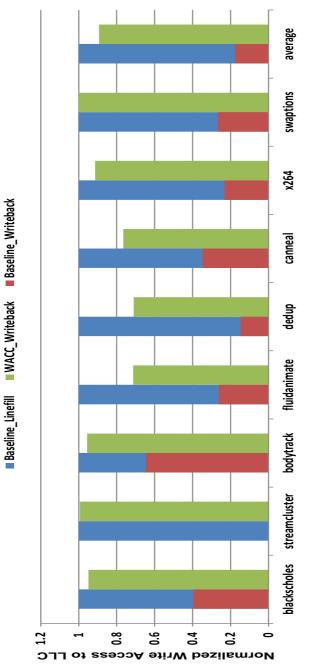

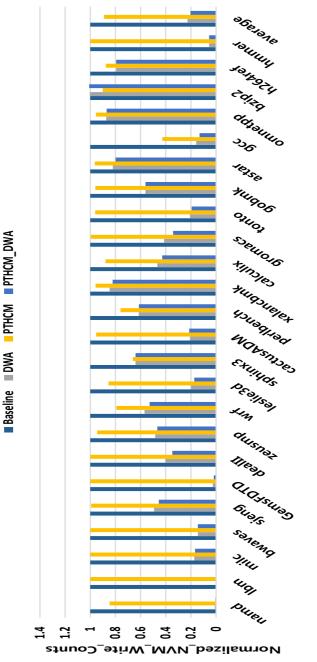

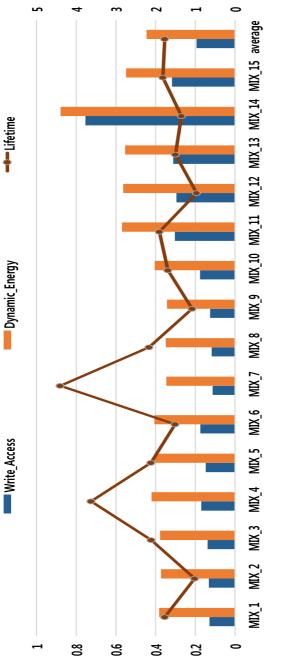

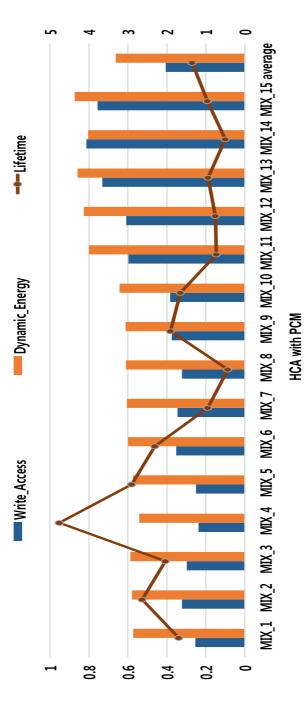

| Figure 21. | Normalized write counts of WACC                              | 77 |

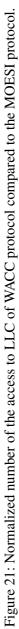

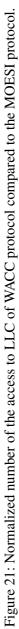

| Figure 22. | Normalized NVM write counts of DWA with STT-RAM.             | 80 |

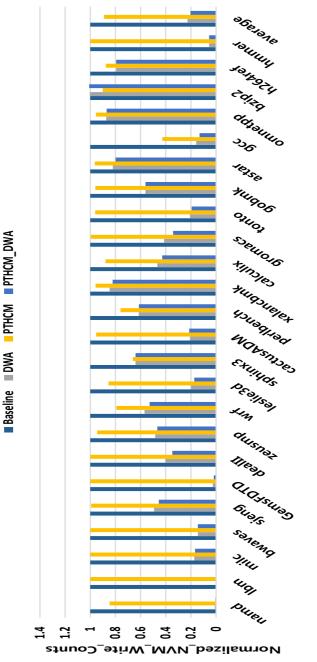

| Figure 23. | Normalized NVM write counts of DWA with PCM                  | 81 |

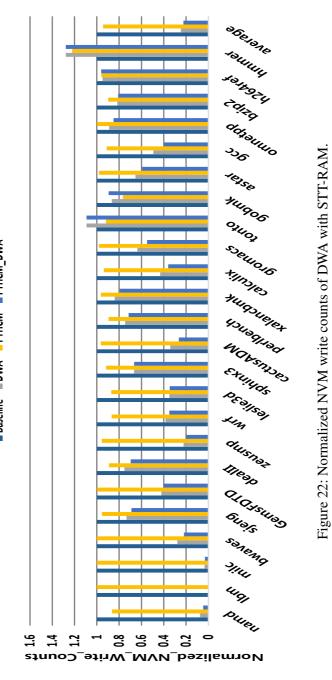

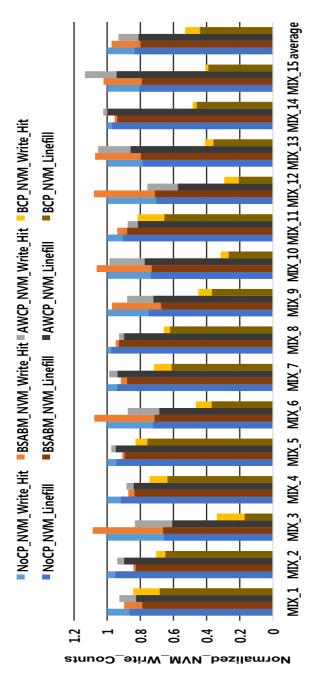

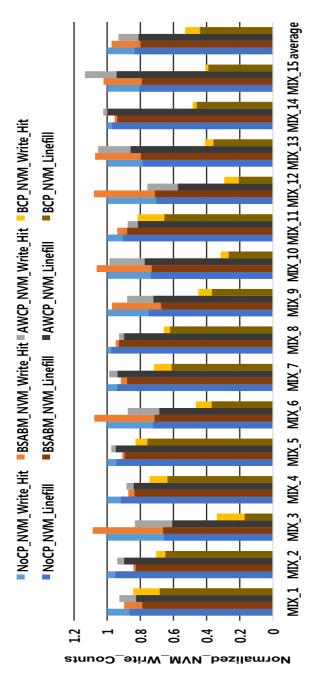

| Figure 24. | Normalized NVM write counts for LCP                          | 82 |

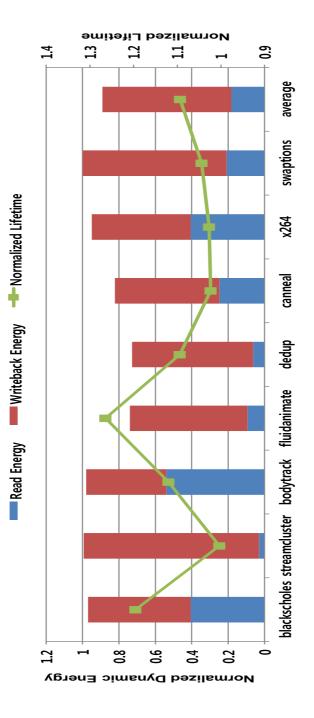

| Figure 25. | Normalized dynamic energy consumption and lifetime           |    |

|            | of WACC                                                      | 84 |

| Figure 26. | Normalized dynamic energy consumption of DWA with            |    |

|            | STT-RAM.                                                     | 87 |

| Figure 27. | Normalized dynamic energy consumption of DWA with            |    |

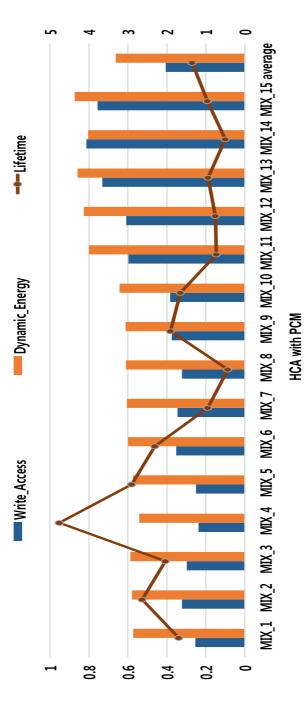

|            | РСМ                                                          | 88 |

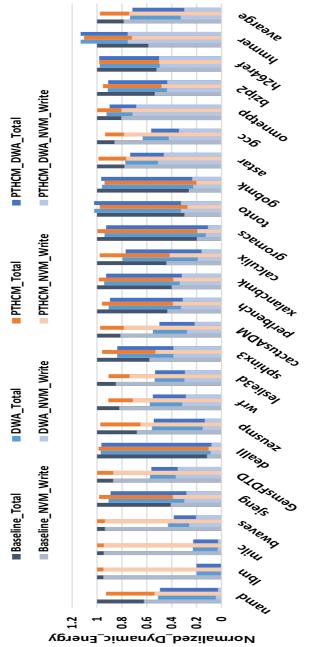

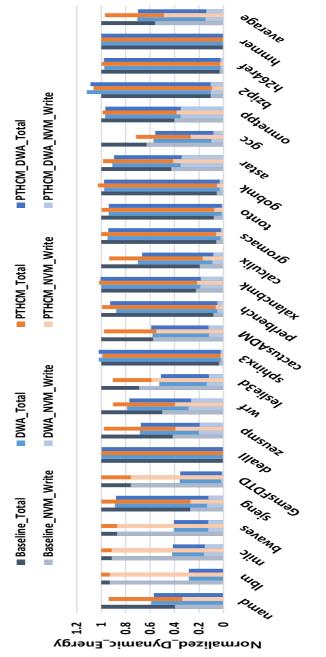

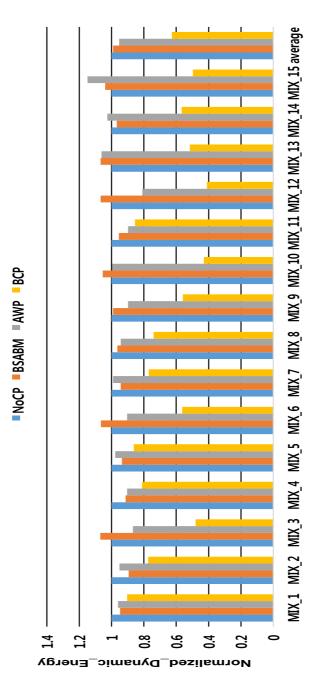

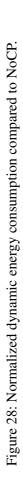

| Figure 28. | Normalized dynamic energy consumption for LCP                | 89 |

| Figure 29. | Normalized lifetime of DWA with STT-RAM 9              | 1 |

|------------|--------------------------------------------------------|---|

| Figure 30. | Normalized lifetime of DWA with PCM 9                  | 2 |

| Figure 31. | Miss rates with various DWA configurations with STT-   |   |

|            | RAM                                                    | 4 |

| Figure 32. | Miss rates with various DWA configurations with PCM. 9 | 5 |

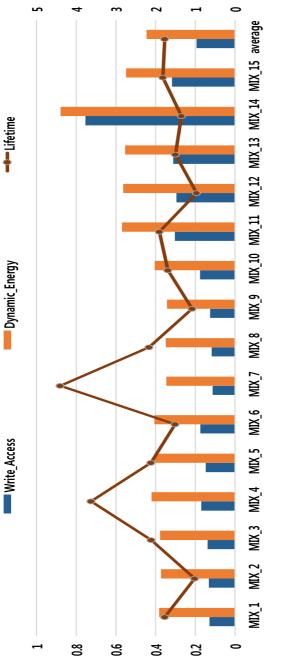

| Figure 33. | DWA with STT-RAM in multi-core environment 9           | 7 |

| Figure 34. | DWA with PCM in multi-core environment 9               | 8 |

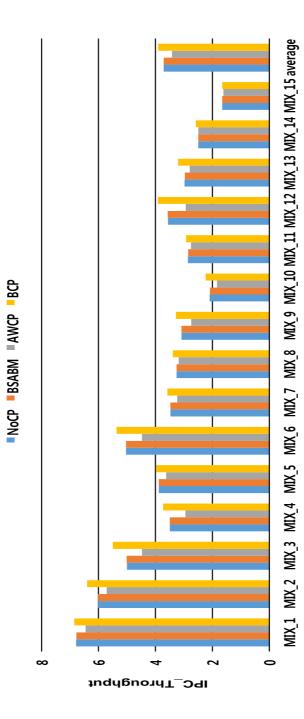

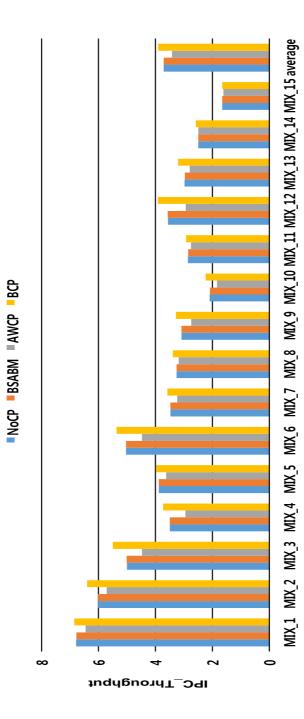

| Figure 35. | IPC throughput for LCP                                 | 0 |

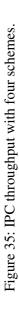

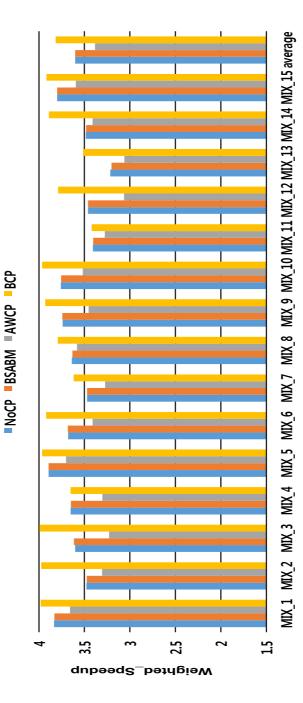

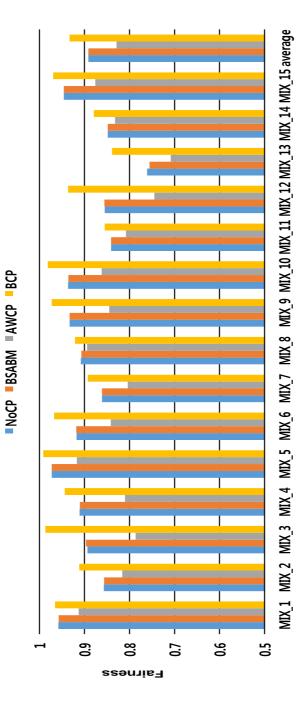

| Figure 36. | Weighted speedup for LCP                               | 1 |

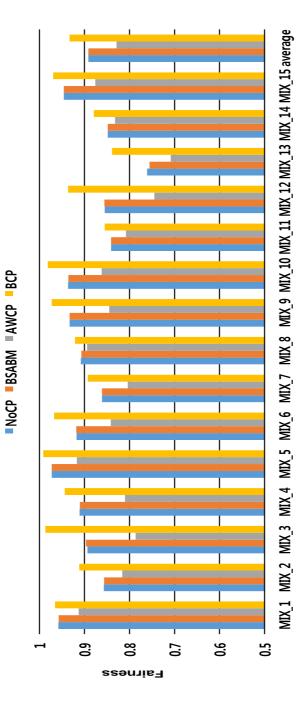

| Figure 37. | Fairness for LCP                                       | 2 |

## **List of Tables**

| Table 1. Comparison of area, latency, and energy                  | 4 |

|-------------------------------------------------------------------|---|

| Table 2. Summary of proposed schemes.    .    .    .    .         | 8 |

| Table 3. States and descriptions for write avoidance cache coher- |   |

| ence protocol (WACC)                                              | 9 |

| Table 4. Signals/actions and descriptions for WACC.    2          | 1 |

| Table 5. Notation descriptions for metrics of LCP.    50          | 0 |

| Table 6. Notation descriptions for algorithms of LCP.    6        | 1 |

| Table 7. Storage overhead.    69                                  | 9 |

| Table 8. Timing overhead.    70                                   | 0 |

| Table 9. Processor configurations.    7.                          | 3 |

| Table 10.Write counts per kilo-instructions for LCP.    7         | 5 |

| Table 11.Multi-core workloads for LCP.    73                      | 5 |

| Table 12.Multi-core workloads for DWA                             | 6 |

### Chapter 1

## Introduction

#### **1.1 Purpose of the thesis**

The purpose of the thesis is to reduce the write counts of LLC to overcome drawbacks of NVM. To this end, three schemes are proposed in the thesis: write avoidance cache coherence protocol (WACC), dynamic way adjusting scheme (DWA), and linefill-aware cache partitioning (LCP).

Non-volatile memory (NVM) has been investigated as a resource to replace volatile memories such as SRAM or DRAM since their tendency to waste energy has grown to a substantial portion of total energy consumption [1, 2, 3, 4, 5, 6]. With conventional memory, static power is dissipated by transistors even when they make no switching. On the contrary, NVM adopts its own material as memory storage, instead of an electric charge, which limits leakage power dissipation.

However, there are some drawbacks to be considered when employing NVM as last level cache (LLC) directly: inefficient write operations and limited write endurance. Changing values in NVM requires long operating time and high level current. Thus, write operations generate long latency and high dynamic energy consumption in the NVM cache system. Moreover, an NVM cell is worn out after a limited number of writing. Therefore, the lifetime of the NVM based cache is shorter than that of the SRAM cache due to the write limitation.

To overcome these drawbacks, the thesis introduces a new cache coherence protocol to reduce the write operations of the LLC [7]. The block data of the LLC is updated only if the cache block is written-back from a private cache, which leads to avoiding useless write operations in the LLC.

In addition, it is found that the previous researchers have overlooked that the capacity of NVM is also one of important factors affecting the number of write accesses to NVM. This discovery leads to the necessity of NVM capacity management policy such that the size of NVM is dynamically adjusted according to the demand of applications. To implement the idea, we propose a dynamic way adjusting (DWA) algorithm which dynamically monitors the optimal number of NVM ways using the stack property and disabling the unnecessary NVM ways [8].

Finally, the thesis proposes a cache partitioning scheme called linefillaware cache partitioning (LCP) mechanism, taking into account the NVM linefill counts as well as the NVM write hit counts during cache partitioning. Most previous works have concentrated on managing write-intensive blocks by allocation these blocks to SRAM to reduce the number of the write operations to NVM. However, those schemes have not considered that reducing the number of linefill operations to NVM is important to reduce the total number of write operations to NVM. To overcome this weakness, an algorithm for cache partitioning of LCP considers the NVM linefill counts.

The proposed schemes are simulated with the gem5 simulator [9] for WACC and macsim [10] for DWA and LCP. We used the PARSEC benchmark suite [11] for evaluating WACC and SPEC CINT2006 and SPEC CFP2006 of the SPEC CPU2006 benchmark suite [12] for DWA and LCP. The experitmental results show that WACC achieves a 13.2% reduction in the dynamic energy consumption. For HCA schemes, the dynamic energy consumption of DWA and LCP are reduced by 26.9% and 37.2%, respectively.

#### **1.2 Background**

According to the material used in NVM, several kinds of NVM [1, 2, 3, 4, 5, 6] have been introduced such as spin-torque transfer RAM (STT-RAM), phase change memory (PCM), and ferroelectric RAM (FeRAM). Even though their compositions are different, all NVM can be considered similar in terms of cache architecture. First, they sustain their information without electric power; this is the reason why they called non-volatile memory. Their main advantage comes from their characteristics of extremely low leakage power consumption. In addition, their density is much higher than that of SRAM even that of DRAM for some kinds of NVM. Table 1 shows comparison of parameters of SRAM and STT-RAM obtained from the modified CACTI [13, 14] in previous work [15].

| Parameters             | SRAM             | STT-RAM       | РСМ             |

|------------------------|------------------|---------------|-----------------|

| Cache Size             | 128KB            | 512KB         | 2MB             |

| Area(mm <sup>2</sup> ) | 3.262            | 3.30          | 3.85            |

| Read Latency(ns)       | 2.252            | 2.318         | 4.636           |

| Write Latency(ns)      | 2.264            | 11.024        | 23.180          |

| Read Energy(nJ)        | 0.895            | 0.858         | 1.732           |

| Write Energy(nJ)       | 0.797            | 4.997         | 3.475           |

| Static power(80°C)(W)  | 1.131            | 0.016         | 0.031           |

| Write Endurance        | 10 <sup>16</sup> | $4 * 10^{12}$ | 10 <sup>9</sup> |

Table 1: Comparison of area, latency, and energy [15].

#### 1.3 Motivation

The thesis focuses on two approaches such as cache coherence protocol and NVM capacity management policy for hybrid cache architecture (HCA). For cache coherence protocol, the existing studies have not concentrated on reducing the write operations because it does not matter in the SRAM-based LLC. Since there is no drawback of write operation compared to read operation, the number of write access is not taken into account. However, reducing the write operations is an important issue in NVM-based LLC. The dynamic energy consumption largely depends on the write operations, because the dynamic energy of write operation is greater than that of read operation. Moreover, the lifetime is inversely proportional to the number of write access. Therefore, a new protocol for NVM to minimize the write operations is needed.

In addition, it is found that there is a relationship between the capacity of NVM in HCA and the write counts of NVM. The analysis implies the necessity of efficient NVM capacity management policy: the HCA dynamically manages the capacity of NVM according to the demand of applications. As the first step of realizing this idea, we use the number of active NVM ways in a set as the measure of the capacity of NVM. The capacity of NVM is expressed by the number of currently available NVM ways and the demand of NVM is converted to the requested number of NVM ways.

#### **1.4 Contributions**

Firstly, the thesis introduces a new cache coherence protocol for NVM to decrease the number of write access to the LLC [7]. In our protocol, the data array of the LLC is not updated during the linefill operation, while the tag array is changed to maintain the inclusion property. The data array is modified only when the cache block is written-back from the private cache. Our protocol reduces the number of write access to the LLC; thus, the dynamic energy consumption is reduced and the lifetime is enhanced in our protocol.

- We investigate the existing cache coherence protocol for NVM and reveal the drawback of them.

- We propose a cache coherence protocol for NVM, which avoids unnecessary write operation in the LLC based on the analysis.

• We present experimental results of a write avoidance coherence protocol with number of write accesses to LLC, dynamic energy consumption, and lifetime.

In addition, hybrid cache architecture (HCA) has been proposed to overcome these limitations of NVM [16, 17, 18, 19, 20]. Most previous works have concentrated on managing write-intensive blocks by storing these blocks to SRAM to reduce the number of the write operations to NVM. However, we show the concept of NVM capacity management policy for reducing the number of write accesses to NVM and propose a dynamic way adjusting algorithm [8]. It dynamically resizes the number of active NVM ways to improve the dynamic energy consumption and the lifetime. To adjust the number of NVM ways, the maximum stack distance is monitored and rearranging the replaceable NVM ways is regularly performed.

- We investigate the relationship between the number of write operations and the capacity of NVM in HCA by performing both analysis based on the devised analytical model and experiments.

- We find out that decreasing the number of active NVM ways can be beneficial to reduce the number of write accesses to NVM ways, only if it does not increase the miss rate significantly.

- We propose a dynamic way adjusting algorithm (DWA) to find the optimal number of NVM ways and dynamically adjust active NVM ways without physical change of the cache.

• We conduct a simulation to evaluate the effectiveness of the proposed policy in terms of the reduction in the write counts of NVM, the decrement of the dynamic energy consumption, the lifetime extension, and the variation of the miss rate.

While previous studies focus on reducing NVM write counts due to the write-intensive blocks, they have not considered the NVM write operation is also occurred by linefill operation to NVM. Reducing the NVM write counts due to linefill operations are also very important for minimizing overall NVM write counts in chip-multiprocessor (CMP) environments. The thesis proposes a cache partitioning scheme called a linefill-aware cache partitioning (LCP) mechanism, taking into account the NVM linefill counts as well as the NVM write hit counts during cache partitioning.

- We propose a linefill-aware cache partitioning scheme (LCP) for HCA, which takes into account the reduction in the number of linefill operations to NVM to minimize the NVM write counts.

- We devise new metrics for LCP: write counts change ( $\Delta W$ ) and NVM write counts change ( $\Delta NVMW$ ), which are based on the miss counts change ( $\Delta M$ ).

- We propose an algorithm to make partitions by predicting metrics according to the change of the number of allocated ways for each core.

| Scheme                                                | Aim                                                                                         | Description                                                                                                              |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Write avoidance<br>cache coherence<br>protocol (WACC) | Reduction in the number<br>of write access to LLC                                           | The data array is modi-<br>fied only when the cache<br>block is written-back<br>from the private cache.                  |

| Dynamic way adjust-<br>ing algorithm (DWA)            | Reduction in the number<br>of write access to NVM                                           | The number of active NVM ways is dynamically resized.                                                                    |

| Linefill-aware cache<br>partitioning (LCP)            | Reduction in the number<br>of write access to NVM<br>and increase in the hit<br>rate of LLC | The NVM linefill counts<br>is taken into account as<br>well as the NVM write<br>hit counts during cache<br>partitioning. |

Table 2: Summary of proposed schemes.

• We present experimental results of LCP with the prediction accuracy, number of write accesses to NVM, miss rates, performance for multicore workloads, and dynamic energy consumption.

The schemes in the thesis are summarized in Table 2.

#### **1.5** Organization of the thesis

The rest of the thesis is organized as follows. Chapter 2 provides related work about NVM. In Chapter 3, a new cache coherence protocol for NVM called a write avoidance cache coherence protocol is proposed. Chapter 4 describes NVM capacity management policy for HCA. The conclusion is given in Chapter 5.

#### **Chapter 2**

## **Related work**

#### 2.1 Hybrid cache architecture

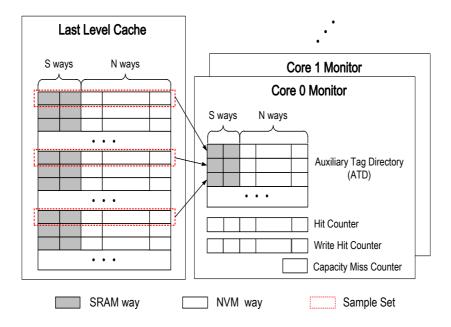

Researchers have merged two types of memory into a single cache system, which is called HCA, to reduce the number of write access to NVM to alleviate the shortcomings of it especially related to a write operation [16, 17, 18, 19, 21]. As described in above section, the shortcomings of NVM come from write operation of NVM. In other terms, the number of write access to NVM is the most important factor for both the dynamic energy consumption and the lifetime. Since the write energy consumption of NVM is much larger than read energy of NVM or dynamic energy of SRAM, the write energy consumption. Furthermore, the lifetime is proportional to the number of write access to NVM is one of the most important methods to mitigate the drawbacks of NVM. For this reason, a small number of SRAM ways are used to accommodate heavily written blocks in the hybrid cache system as depicted in Figure 1.

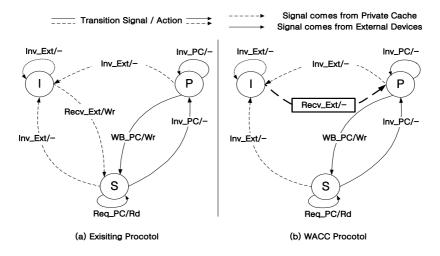

Figure 1: Basic structure of hybrid cache architecture (HCA).

First, swapping or migration schemes between SRAM and NVM in a hybrid cache system were proposed. Wi et al. introduced the region based cache architecture in [16]. They divided a single level of cache into two regions: read region which consists of STT-RAM and write region which consists of SRAM. If a block is predicted as write-intensive, the block is placed or swapped to the write region. Besides the schemes, merging set schemes were proposed [17] and [18]. The authors noticed that non-uniformity of write operations among sets. While some sets are frequently utilized, other sets receive relatively small requests. Therefore, write-intensive blocks in the highly utilized sets are forwarded to the idle sets. In addition, a predictor was equipped to find the correlation between write intensive blocks and addresses of trigger instructions [19]. In summary, existing policies focused on placing write-intensive blocks into the SRAM.

#### 2.1.1 Write intensity prediction studies

Almost all papers on HCA have focused on devising methods to identify write-intensive blocks and place them to SRAM ways. Wi et al. suggested the region based cache architecture in [16]. They separated a single level of cache into two regions: read and write regions. The read region is prepared for non-write-intensive blocks composed of NVM, while the write region is composed of SRAM for write-intensive blocks. When a block is considered as write-intensive, the block is migrated or placed to the write region. On top of these schemes, combining set schemes were proposed [17, 22, 23]. This insight came from the fact that the write operations among sets are not uniformly distributed. While some sets receive relatively small write requests, other sets are highly utilized. To take advantage of these characteristics, some blocks in the frequently utilized sets are moved to the other sets. To elaborate the prediction algorithm, Quan et al. introduced a prediction table [18] containing the history of the write requests of the LLC. Another prediction table is proposed to store the value of combining addresses of the blocks and program counter of instructions [19]. What distinguishes these works from our scheme is that they have not focused on the CMP environment.

#### 2.1.2 Static approaches

Various methods utilizing the compiler have been proposed. Chen et al. [24] proposed a scheme in which the compiler provides hints to find the write-

intensive block and the hardware is modified to correct the hints. Software dispatch was presented to detect write reuse patterns in [25]. In addition, the migration-intensive blocks are loaded into the SRAM region with the compiler assistance in [26] to mitigate the burden of migration blocks. Moreover, a loop retiming framework was proposed for loops with intensive data array operations to relieve the migration overhead [27]. Another study improves the read performance and energy efficiency guided by the analysis of read bottlenecks [28]. They focused on the recompilation or profiling schemes, while our proposed mechanism modifies the hardware structure and logics.

#### 2.1.3 Hybrid cache architecture for main memory

As the write endurance problem has become important for the main memory, which is based on NVM, many methods have been proposed to prolong its lifetime. They have employed DRAM as a cache for NVM. Qureshi et al. firstly suggested the concept of a small DRAM cache to overcome the latency gap between DRAM and PCM [29]. The mechanism exploits both the short latency of DRAM and the large capacity of PCM by preventing unnecessary access to PCM. They also have shown advanced approaches such as write cancellation and write pausing policies [30] to mitigate the long read access time due to the long write latency. Meanwhile, a scheme proposed in Meza et al. [31] stores the metadata for the last accessed rows into a small buffer to manage the difficulty of fine-granularity DRAM caches. It is found that row buffer misses generate long latencies, and a policy is devised to exploit this observation [32]. They predict the data incurring a row buffer miss and store it into a DRAM buffer by investigating the row buffer miss counts in PCM. Writeback-aware partitioning offers a new perspective on cache partitioning, taking into account the writeback information [33]. It is innovative in regard to reducing the amount of write access to the PCM main memory by managing the cache partition.

Another approach for the hybrid cache architecture is based on OS support. For PDRAM [34], the researchers introduced a hybrid solution related to software as well as hardware to extend the lifetime of the PCM pages. They modified the OS-level page manager and added a small device to contain the number of write requests for PCM at a page level granularity. Ferreira et al. [35] also inserted a DRAM buffer to decrease the number of read and write requests to PCM via page partitioning. Zhang and Li [36] improved the write endurance and reduced write latency of PCM by exploiting the workload characteristics as an aspect of an OS level paging. New page migration schemes were proposed to track read-bound access NVM pages [37].

All schemes described above are based on the physical features of DRAM or characteristics of OS, thus they are inadequate applied to the SRAM and NVM based LLC, which is the target of the thesis.

#### 2.2 Cache partitioning schemes

To improve the cache efficiency, several methods using stack property have been proposed. The number of cache hit counts of LRU position is monitored to calculate the cache utility of each application or core. Based on the information, the cache is partitioned to minimize the number of total cache misses. Suh et al. [38] dynamically partitioned the LLC and assigned the guided number of cache ways to each application. Even though it successfully raised the cache utility, there was a problem in that the utility information of an application was affected by other applications. To avoid this drawback, Qureshi and Patt [39] introduced a separate utility monitor, which counts the number of hits without interference by other applications. An adaptive placement policy [40] was proposed to load a new block into the local or remote cache for enhancing the efficiency of cache based on stack distance profiling. In addition, compliers used the information to predict the memory behavior of the application [41]. For a real-time system, Liu and Zhang [42] suggested the compilation technique, which improves the worst case data cache performance using the stack distance approach. Most papers on cache partitioning assumed that the LLC consists of SRAM only, hence they do not consider the NVM write counts in their schemes.

#### Chapter 3

# Write avoidance cache coherence protocol

## 3.1 Limitation of existing cache coherence protocol

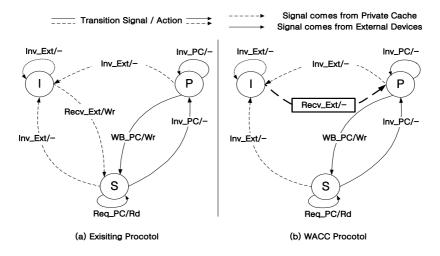

We review the legacy cache coherence protocols to get a new insight to reduce the write operations. There are useless write operations in the existing protocol. Generally, memory systems of CMPs are composed of a shared LLC and several private caches which are dedicated to cores [43]. In addition, the cache block is divided into two arrays: tag array and data array. Tag array stores tag bits and cache coherence state, while data array stores block data. When a linefill operation occurs, the requested block data is written to the data array, and the tag bits and cache coherence state are updated to the tag array. Then, the cache block is forwarded and linefilled to the private cache. When a core tries to modify the cache block in the private cache, an invalidation signal is sent to the shared LLC and other private caches to maintain the cache coherence. Thus, the previous write access to the LLC during the linefill operation is considered as the useless write operation, if the cache block in the LLC has been never used until it is invalidated. Figure 2 illustrates an example of write inefficiency in widely used cache coherence protocols such as MESI or MOESI [44]. In the example, we assume that a core reads and writes a block data of the PC (Private Cache) 1. Table 3 lists the cache states in the figure and their descriptions. When the core tries to read the block data, since the PC1 has no valid block data, the cache controller sends the request for the block data to the LLC.

However, the LLC also has no valid copy; thus, the request is sent to the external sources such as the main memory or other chipsets. When the block data "ABCD" is arrived at the LLC, it is written into the LLC and the state of the LLC is changed to S state, which means the cache block is valid and other private caches may have the same cache block. Then, the block data "ABCD" is forwarded to the PC1.

When the block data is received in the PC1, it is written into the PC1 and the state of the PC1 is changed to E state. After the linefill operation is completed, if the core tries to modify the block data "ABCD" to "EFEF", an invalidation request is sent to the LLC to maintain cache coherence. The purpose of the invalidation request is indicating that the block data of the PC1 is modified and the cache block in the LLC should be invalidated. If the block data "ABCD" in the LLC has not been used until it is invalidated, writing the block data "ABCD" to the LLC during the linefill operation was a useless write operation.

Figure 2: Conventional cache coherence protocol.

Figure 3: Write avoidance cache coherence protocol (WACC).

Table 3: States and descriptions for write avoidance cache coherence protocol (WACC).

| State           | Description                                                                                                                                                 |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I(nvalid)       | The cache block is invalid                                                                                                                                  |

| S(hared)        | The cache block has valid block data and other private caches may have valid copy.                                                                          |

| E(xclusive)     | The cache block has valid block data with exclusive permission<br>and other caches have no valid copy.                                                      |

| M(odified)      | The cache block has valid and modified block data. Other caches have no valid copy. This state appears in the private cache only.                           |

| P(rivate cache) | The cache block in the LLC has no valid block data, but more<br>than one of the private caches has valid block data. This state<br>appears in the LLC only. |

\* P state is introduced due to keeping the inclusion property. Modern multiprocessors have employed the inclusive LLC to filter the cache coherence traffic from other chipset or the main memory. Thus, it is needed that a state represents one of the private caches has valid data even the LLC has no valid data.

#### **3.2** Write avoidance cache coherence protocol

To deal with this problem, we suggest a new cache coherence protocol which is called Write avoidance cache coherence (WACC) protocol. In our protocol, the block data of the cache block is not written into the LLC during the linefill operation, while the tag bits and the cache coherence state are updated. Since the block data is not placed in the LLC, one of the private caches has responsibility to provide the valid block data. The block data in the LLC is only updated when it is written-back from the private cache. The writeback is initiated only when no other private cache has the block data in WACC protocol. Therefore, we avoid useless write operation due to modifications of the block data in the private cache.

Figure 4: State transition diagrams for WACC.

Figure 3 shows an example of WACC protocol. Unlike the conventional protocols, when the block data ABCD is arrived at the LLC, it is not written to the LLC. Instead, the state is changed to P state and the block data is forwarded to the PC1. When the PC1 is modified to EFEF, there is no need to send an invalidation request to the LLC for the block data ABCD is not written to the LLC. Therefore, one write operation of the LLC and one request for cache coherence is decreased compared to the baseline protocols.

We compare a simple version of the existing MOESI protocol with its modified protocol in Figure 4. Table 4 shows the coherence signals and actions. The transition signal is divided into two parts: {signal}\_{source} and the action indicates the operation of the data array. For example, WB\_PC/Wr means that if the block is P state and receives the WB signal from a private cache, the block data is written to the data array.

| Signal | Description                                                                                                                |

|--------|----------------------------------------------------------------------------------------------------------------------------|

| Inv    | Invalidate the cache block if it is valid. This signal is generated<br>when another device tries to modify the block data. |

| Recv   | Provide the block data in the cache block. This signal is gener-<br>ated when a cache hit occurs.                          |

| Req    | Request the block data for read operation. This signal is gener-<br>ated when a cache miss occurs.                         |

| WB     | Writeback the block data to the LLC. This signal is generated when a private cache evicts the cache block.                 |

| Action | Description                                                                                                                |

| Wr     | Write the block data of the received cache block into the data array.                                                      |

| Rd     | Read the block data and provide it with the requestor.                                                                     |

Table 4: Signals/actions and descriptions.

As shown in Figure 4(a), when a new cache block is received in the LLC, the state of the cache is transition to S state and the block data is written to the data array in the existing protocol. On the contrary, the state is transition to P state instead of S state in our protocol under the same condition. Furthermore, the write operation is omitted as shown in Figure 4(b). This is because the block data is forwarded without write access to the data array in WACC protocol.

Another point to be considered is that the protocol of the private cache should be changed. The writeback operation is initiated if the cache block in the private cache is modified and evicted in the existing protocols. However, the cache block should be written-back to the LLC in WACC protocol when it is evicted in the private cache regardless of whether the cache block is dirty or not.

#### **Chapter 4**

# NVM capacity management policy for hybrid cache architecture

#### 4.1 NVM capacity management policy

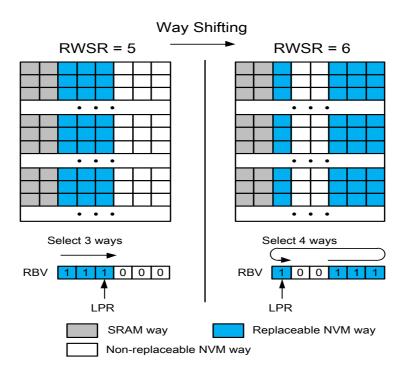

In this section, we propose two schemes for NVM capacity management policy. First, we introduce a dynamic way adjusting algorithm (DWA) that monitors the optimal number of NVM ways and dynamically adjust the number of active NVM ways [8]. In addition, we also propose a linefillaware cache partitioning scheme (LCP) to save the dynamic energy consumption by efficiently allocating SRAM ways and NVM ways to cores.

The DWA keeps track of maximum stack distance (MSD), which means the minimum number of ways to maintain the miss rate. If the number of the current active NVM ways is not the optimal value, it is adjusted according to the MSD. In addition, an efficient method to disable NVM ways is required because it is impossible that NVM ways are physically added or removed during execution. Thus, the DWA prevents deactivated NVM ways from victim selection. A newly fetched block is prohibited to be loaded into the disabled NVM ways, which has the effect of virtually deactivating them. The basic idea of LCP comes from cache partitioning [38, 39, 40], which has been a well-known scheme to improve the performance in CMP systems. The key idea of the cache partitioning is that all cache ways should be efficiently allocated for each application to maximize the hit rate of the LLC. They have contributed the studies of the LLC. However, it is inefficient to apply them directly into HCA because their models assume that all cache ways consist of the same memory type. Even though the cache misses are minimized by the previous cache partitioning schemes, if the linefill operations heavily occur in NVM ways, it fails to reduce the linefill counts of NVM. Therefore, LCP assigns the SRAM ways and the NVM ways to each core based on the change of the NVM linefill counts as well as the NVM write hit counts according to partitioning.

#### 4.1.1 Concept of NVM capacity management policy

This section presents an NVM capacity management policy that resizes the number of NVM ways to fit the demand of applications. This policy comes from the observation that reducing the size of NVM usually decreases the write counts of NVM if the miss rate does not grow. The thesis will propose an analytical model and perform a simulation to verify this observation.

Cache researchers have been investigating the relationship between the size of cache and the miss rate [39]. For many programs, as the cache size grows, the miss rate becomes small. On the contrary, the miss rates of some programs are saturated or remain despite incremental growth of the cache

size. In addition, even the same program always does not require the fixed size of cache. Therefore, the number of requested ways of the cache varies during execution, and the unnecessary ways are disabled without performance degradation.

The number of write accesses to the cache is strongly coupled with the miss rate. Generally, the cache operations are divided into three categories: read hit, write hit, and linefill. Among these operations, write hits and linefill operations compose the write requests. If some read hits are changed to cache misses due to the increasing miss rate, new linefill operations occur as much as the removed read hits. This implies that the total number of write operations are increased. Alternately, if the number of cache misses is not increased, the number of write accesses to the cache remains because the hit counts and miss counts is not changed.

Assume that we minimize the number of NVM ways without generating significant extra cache misses. In that case, the write operations which originally occurred in the deactivated NVM ways are forwarded to SRAM ways or other NVM ways. If a part of write accesses is sent to SRAM ways, the number of write accesses to NVM ways is reduced. Therefore, partial deactivating NVM ways with the stable miss rate highly tends to decrease the write counts of NVM ways.

An illustration is provided in Figure 5 to aid in the understanding of this concept. There are two caches in the example. One of the caches consists of one SRAM and three NVM ways, and another cache is composed of one

SRAM and two NVM ways. The program in our example needs only three ways. For the sake of convenience, suppose that all memory references are write requests.

When the program starts, cache accesses are performed according to the sequence in Figure 5. There is no difference between the two caches in the first three accesses. However, when "d" miss is encountered, two caches behave differently. While "d" is placed in the fourth way in cache A, "a" is replaced with "d" in cache B. Writing "d" in the second iteration, SRAM access is made instead of NVM access in cache B. As a result, the number of write to NVM ways is reduced in cache B. The linefill operation of "d" is forwarded to a SRAM way, and thus one linefill operation and one write hit of NVM ways is reduced.

| Memory Reference Sequence: a, b, c, d, b, c, d |                                                                                                  |                            |                                                                                                                                      |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                | Cache A                                                                                          |                            | Cache B                                                                                                                              |  |

| a                                              | Linefill_S (a)                                                                                   |                            | Linefill_S (a)                                                                                                                       |  |

| Ь                                              | a <u>b</u>                                                                                       | Linefill_N (b)             | a <u>b</u> Linefill_N (b)                                                                                                            |  |

| с                                              | a b c Linefill_N (c)                                                                             |                            | a b <u>c</u> Linefill_N (c)                                                                                                          |  |

| d                                              | a b c <u>d</u>                                                                                   | Linefill_N (d)             | d b c Linefill_S (d)                                                                                                                 |  |

| Ь                                              | a <u>b</u> c d                                                                                   | ] Write_Hit_N (b)          | d <u>b</u> c Write_Hit_N (b)                                                                                                         |  |

| с                                              | a b <u>c</u> d                                                                                   | ] Write_Hit_N (c)          | a b <u>c</u> Write_Hit_N (c)                                                                                                         |  |

| d                                              | a b c <u>d</u>                                                                                   | ] Write_Hit_N (d)          | d b c Write_Hit_S (d)                                                                                                                |  |

|                                                | SRAM Lir     SRAM Wi     SRAM Wi     NVM Line     NVM Writ     OVM Writ     SRAM To     NVM Tota | tal Write : 1              | SRAM Linefill : 2     SRAM Write Hit : 1     NVM Linefill : 2     NVM Write Hit : 2     SRAM Total Write : 3     NVM Total Write : 4 |  |

| Linefill_S                                     |                                                                                                  | Linefill o                 | lata into SRAM way                                                                                                                   |  |

| Linefill_N                                     |                                                                                                  | Linefill data into NVM way |                                                                                                                                      |  |

|                                                | Write_Hit_S                                                                                      |                            | ata into SRAM way                                                                                                                    |  |

|                                                | Write_Hit_N                                                                                      | Write o                    | data into NVM way                                                                                                                    |  |

| SRAM way NVM way                               |                                                                                                  |                            |                                                                                                                                      |  |

Figure 5: Example for NVM capacity management policy.

#### 4.1.2 Feasibility of NVM capacity management policy

A metric, write intensity of a way (WI), is defined as the portion of write accesses to the way over the write accesses to all ways. It is given by

$$WI_i = \frac{W_i}{W_{total}} \ (1 \le i \le T) \tag{4.1}$$

where  $W_i$  is the number of write accesses to *ith* way and  $W_{total}$  means the number of total write accesses to the cache, while T is the number of all cache ways. This metric indicates the distribution of write requests among the ways. If all ways have the same write intensity, the write requests are evenly distributed. Unless, write operations occur more frequently in some ways which have higher value than other ways.

Since the total number of write counts is calculated by summation of write counts of each way, it is expressed as

$$W_{total} = \sum_{i=1}^{T} W_i \tag{4.2}$$

The above equation is expressed as form of WI as follows

$$W_{total} = \sum_{i=1}^{T} (WI_i * W_{total})$$

$$= W_{total} * \sum_{i=1}^{T} W I_i \tag{4.3}$$

We rewrite the above equation as form of SRAM ways and NVM ways, and it is given by

$$W_{total} = W_{sram} + W_{nvm}$$

$$= W_{total} * \sum_{i=1}^{S} WI_i + W_{total} * \sum_{i=S+1}^{T} WI_i$$

(4.4)

$$W_{sram} = W_{total} * \sum_{i=1}^{S} WI_i$$

(4.5)

$$W_{nvm} = W_{total} * \sum_{i=S+1}^{S+N} WI_i = W_{total} * \sum_{i=S+1}^{T} WI_i$$

(4.6)

where S is the number of SRAM ways and N is the number of NVM ways, while  $W_{sram}$  means the number of write accesses to SRAM ways and  $W_{nvm}$ is the number of write accesses to NVM ways. We found that there are three factors that influence the write counts of NVM ways: the number of total counts ( $W_{total}$ ), the write intensity per way (WI), and the number of NVM ways (N = T - S).

So far, the main strategy for reducing the number of write counts of NVM ways has been keeping average WI of NVM ways lower than that of SRAM ways. Throughout previous HCA research, WI is thought as the only important factor among the three factors. It is assumed that N is fixed and  $W_{total}$  is not significantly changed. Therefore, they have focused on minimizing WI of NVM ways by detecting write intensive blocks and placing them into SRAM ways. These approaches are successful to reduce write accesses to NVM.

Different from previous approach, we consider N as a variable instead of a constant value. When the number of NVM ways is reduced to N' (N' < N),  $W'_{total}$ ,  $W'_{sram}$ , and  $W'_{nvm}$  are defined as the number of write accesses to the cache, SRAM ways, and NVM ways:

$$W'_{total} = W'_{sram} + W'_{nvm} \tag{4.7}$$

In addition, we define the altered number of all ways as T' (T' = S + N' < T), and Eq. 4.6 is transformed below:

$$W_{nvm} = W_{total} * \left(\sum_{i=S+1}^{T'} WI_i + \sum_{i=T'+1}^{T} WI_i\right)$$

$$= \sum_{i=S+1}^{T'} WI_i * W_{total} + \sum_{i=T'+1}^{T} WI_i * W_{total}$$

(4.8)

The second term indicates the number of write accesses to the NVM ways that will be removed. If we adjust the number of NVM ways to N', the remaining ways should absorb the write requests of the amount of second term. For simplicity, this term substitute for X and Eq. 4.6 is expressed as follows:

$$X = \sum_{i=T'+1}^{T} W I_i * W_{total}$$

(4.9)

$$W_{total} = W_{sram} + (W_{nvm} - X) + X \tag{4.10}$$

Hereby, we introduce a condition that the total write counts are not changed  $(W'_{total} = W_{total})$ . Under the condition,  $W'_{total}$  is given by

$$W'_{total} = W_{sram} + (W_{nvm} - X) + X$$

(4.11)

If we divide X into  $X_{sram}$  and  $X_{nvm}$  that are the write requests of the amount of forwarded to SRAM ways and NVM ways, we obtain

$$W'_{total} = W_{sram} + (W_{nvm} - X) + X_{sram} + X_{nvm}$$

=  $(W_{sram} + X_{sram}) + ((W_{nvm} - X) + X_{nvm})$  (4.12)

Because  $W'_{sram}$  and  $W'_{nvm}$  are defined as the number of write accesses to SRAM and NVM in the resized cache, they can be expressed by as following equation:

$$W'_{sram} = W_{sram} + X_{sram} \tag{4.13}$$

$$W'_{nvm} = W_{nvm} - X + X_{nvm}$$

(4.14)

Before advancing the discussion, we state that it is assumed that  $X_{sram}$  is greater than zero for the simplicity of the model. When the number of ways is changed, the blocks are placed differently than they were. There is a possibility that some write intensive blocks that were originally located in SRAM ways are inserted into NVM ways. In that case,  $X_{sram}$  could be zero or minus value. To avoid this problem, we adopt a policy for placing write intensive blocks into SRAM ways as presented [16] to our scheme.

Since X is summation of  $X_{sram}$  and  $X_{nvm}$ , if  $X_{sram}$  is greater than zero,  $X_{nvm}$  is given by

$$X_{nvm} < X \tag{4.15}$$

By transforming Eq. 4.14 and substitution  $W_{nvm}$  into Eq. 4.15, we obtain

$$W'_{nvm} - W_{nvm} + X < X$$

(4.16)

$$W_{nvm}' < W_{nvm} \tag{4.17}$$

Thus, we conclude that fewer NVM ways causes lower write requests to NVM if the miss rate does not grow.

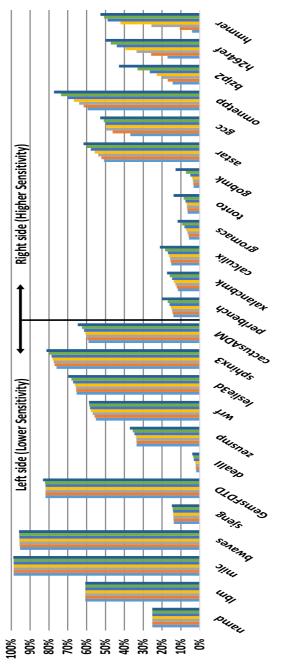

We examined the impact of NVM capacity management on the miss rate, the total write counts, and the write accesses to NVM ways. We assume that the hybrid cache has 4 SRAM ways and 12 NVM ways and that the number of NVM ways varies from 12 to 0. The results are sorted in decreasing order by the number of NVM ways among each application. To improve the readability, we abbreviate SRAM ways to "S" and NVM ways to "N". For example, 4S\_2N in the figure means that 4 SRAM ways and 2 NVM ways are used during the simulation.

32

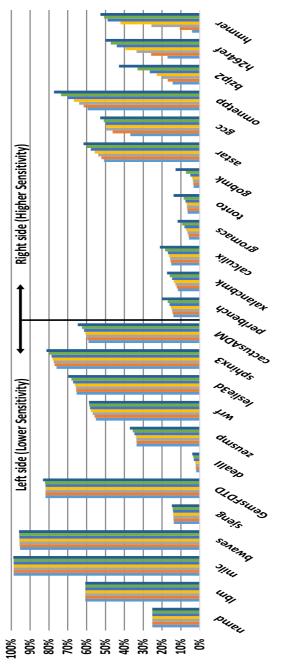

Figure 6: Miss rates with various number of NVM ways.

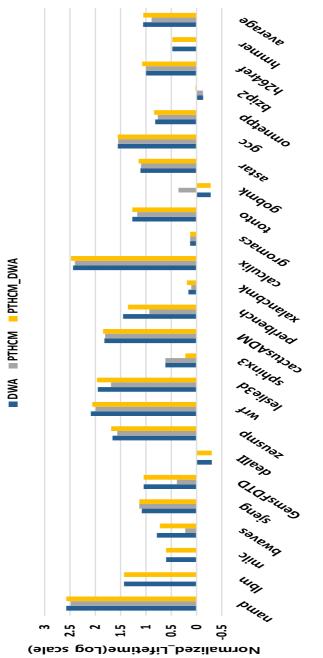

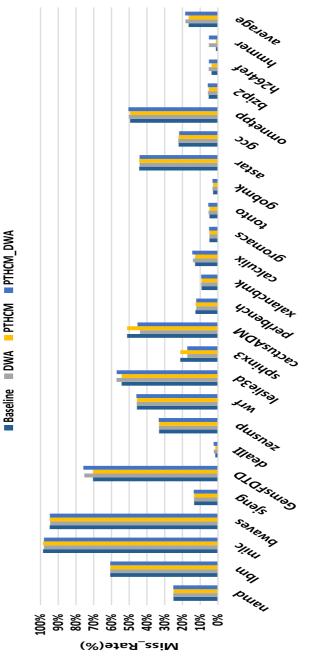

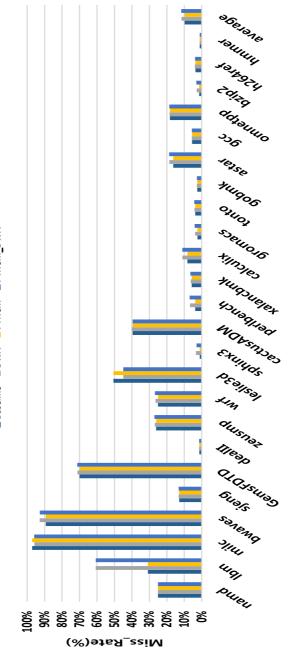

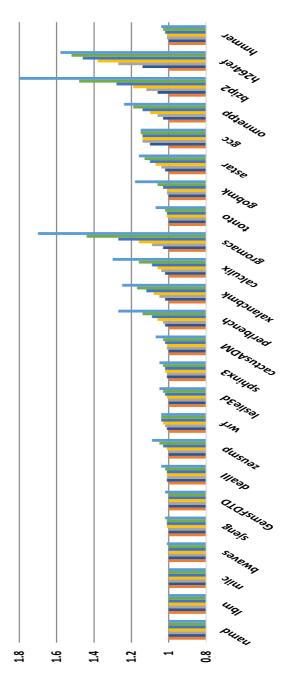

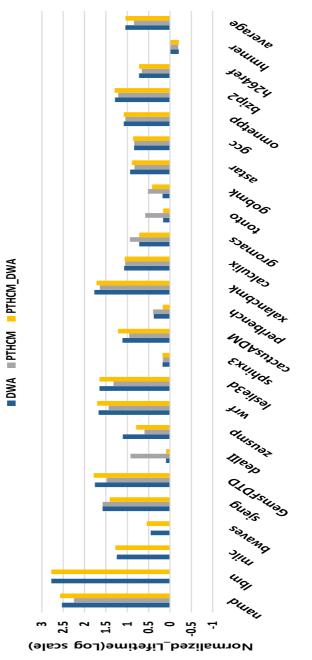

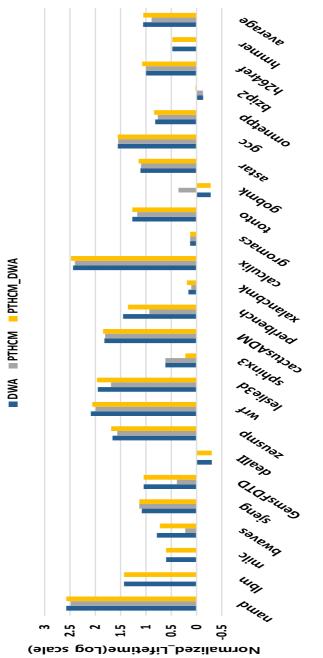

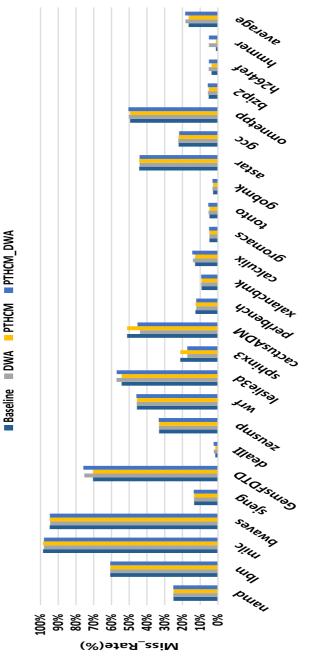

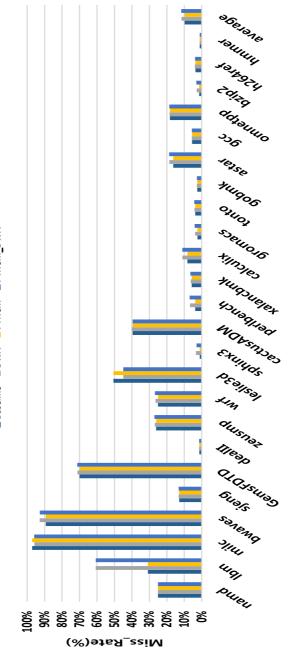

Figure 6 represents the miss rates with various number of NVM ways to show sensitivity of the miss rate to the size of NVM. We sort all applications by geometric standard deviation (GSD), which represents the amount of dispersion from the geometric mean. In Figure 6, the miss rates of the left applications are not less influenced by the number of NVM ways, while the right side applications are more sensitive to the number of NVM ways. The miss rates of two left most applications such as *namd* and *lbm* remain even when all NVM ways are removed. Part of NVM ways are unnecessary for some left side applications: *milc, bwaves, sjeng, GemsFDTD, dealII,* and *zeusmp*. On the contrary, the growth of the miss rates of the higher sensitive applications is large. Especially, the miss rates of *bzip2* and *h264ref* is multiplied about three times and the miss rate of *hmmer* soars to 12.8 times.

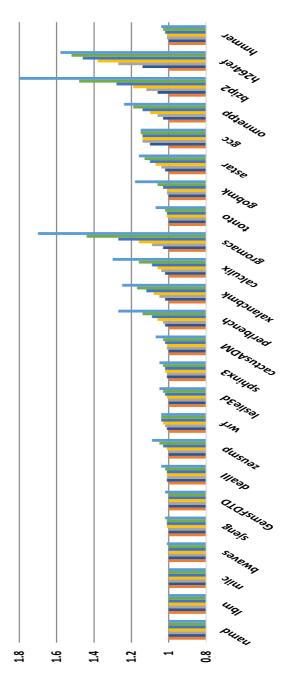

Figure 7 shows normalized write accesses to the HCA with various sizes of NVM. We find that the total write counts of the lower sensitive applications are not greatly increased, while many higher sensitive applications show rapid growth. For the left side applications, only 2.8% of average extra write operations occur. Especially, no change is detected through all sizes of NVM in *namd,lbm*, and *milc*. The number of NVM ways can be decreased to 2 without increasing write counts in *bwaves* and *GemsFDTD*. Other benchmarks such as *sjeng* and *zeusmp* have the same values when NVM ways varies from 12 to 8. On the other hand, the total write counts of the right side applications increase by 29.4% on average.

■45\_12N ■45\_10N ■45\_8N ■45\_6N ■45\_4N ■45\_2N ■45

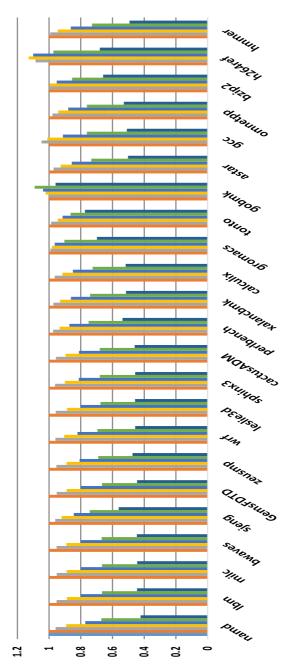

The normalized write accesses to NVM ways with various number of NVM ways is depicted in Figure 8. As we expected, reducing the number of NVM ways decreases the write accesses to NVM ways in lower sensitive applications. On the other hand, the reduction in the write counts of NVM ways is not guaranteed by resizing the number of active NVM ways in higher sensitive applications. Adjusting NVM ways even results in increasing the write operations of NVM ways in *gobmk*, *gcc*, and *h264ref*. Some applications such as *gromacs*, *tonto*, *bzip2*, and *hmmer* show the similar pattern of the left applications, but their reduction ratios are small.

In summary, we find out that the number of write accesses to NVM ways is usually reduced if resizing the number of active NVM ways does not significantly increase the miss rate by adopting efficient NVM capacity management policy.

**45\_12N 45\_10N 45\_8N 45\_6N 45\_4N 45\_2N**

# 4.2 Dynamic way adjusting

We propose a dynamic way adjusting algorithm (DWA) to implement NVM capacity management policy. To discover the optimal size of NVM, the maximum stack distance (MSD) is dynamically monitored. Using the MSD, the DWA marks all NVM ways either as "replaceable way" or "non-replaceable way" to realize adjusting the number of NVM ways. Replaceable ways are regularly changed to prevent write requests from concentrating on a few NVM ways. This section explains these key ideas and the operations of the DWA.

#### 4.2.1 Maximum stack distance

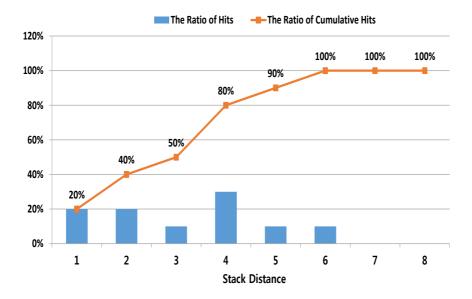

In order to find the minimum number of ways which sustain the miss rate, we introduce the MSD based on the stack property [39]. It is well known that the LRU replacement policy follows the stack property [45], which means that a cache of a size C always contains all blocks of the cache of size less than C. Assume that the number of sets is a constant value. If a cache block is in an N way cache, it is guaranteed that the block is in the cache, which has more than N ways. A metric related to stack property is the "stack distance". When a cache hit regardless of a read hit or a write hit, the stack distance is defined as the LRU order of the hit block. For example, the stack distance of the block at MRU position is one, and that of the LRU position is N in the N way cache. Figure 9 presents the stack distance histogram of a hypothetical application. If the number of the ways is reduced to 3 from 8, the number of

Figure 9: Stack distance histogram.

hits will be halved because the cumulative hits for stack distance 3 is 50%. This means that the miss rate of three-way cache will be increased to 50% in this case. However, if we use 6 ways instead of 8 ways, no additional cache miss occurs. Therefore, the maximum value of the stack distance indicates the minimum number of ways to maintain the hit rate.

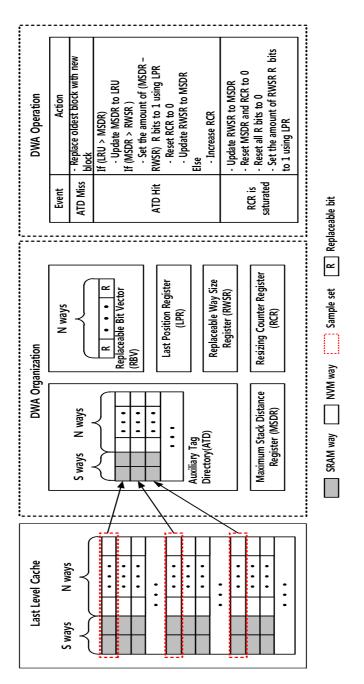

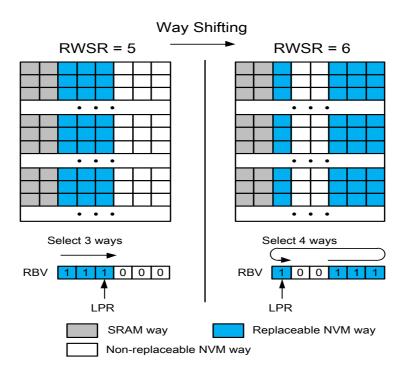

We employ an auxiliary tag directory (ATD), a maximum stack distance register (MSDR), and a replaceable way size register (RWSR) to monitor the MSD as shown in Figure 10. The ATD is a separate storage constructed with the same associativity as the main tag array of the cache. It keeps track of the LRU order information and tag bits. When an ATD hit occurs, the MSDR is updated if LRU of the hit block is larger than the current value of the MSDR. The RWSR is updated in two cases. First, if the MSDR exceeds the RWSR, the RWSR is increased to the MSDR. The condition that the RWSR is smaller than the MSDR means that the current working set needs more cache capacity. Thus additional NVM ways should be replaceable ways by increasing the RWSR. Second, when the value of the RWSR has been larger than that of the MSDR for a while, it is decreased to the value of the MSDR. Keeping the situation in which the RWSR is larger than the MSDR means that unnecessary NVM ways have been used. Therefore, some NVM ways should be deactivated by decreasing the RWSR. To detect this situation and initiate resizing the number of NVM ways, a resizing counter register (RCR) is added. The RCR is increased by 1 when the RWSR is larger than RWSR during the ATD hit operation. Whenever the RWSR is updated to the MSDR, the RCR is reset to 0.

Another consideration in adopting the ATD is the storage overhead. If the ATD has tag information of all sets, the size of the tag array will be doubled. Therefore, to reduce the storage overhead, we use a set sampling policy [46]. The ATD is designed to have only a part of sets which is sampled every 32nd in the proposed algorithm. It is verified that the sampled sets are enough to correctly capture the stack distance value in [46] instead of using all sets.

#### 4.2.2 Adjusting the number of NVM ways

Since physical NVM cells are not inserted or deleted according to the change of the MSD, we devise a method to dynamically activate or deactivate NVM ways. To disable unnecessary NVM ways, we introduce the concept of "replaceable way" and "non-replaceable way" The replaceable way implies the normal way that participates in all kinds of cache operations, such as read access, write access, and replacement. The non-replaceable way means that it is excluded from block replacement; thus, a new block is not placed into the way. However, when a cache hit occurs, read access and write access are performed, same as the replaceable way. All NVM ways in the DWA are divided into replaceable ways and non-replaceable ways.

The role of the replaceable bit vector (RBV) in Figure 10 is indicating that each way is non-replaceable or not by controlling replaceable (R) bits. Since each R bit is corresponded to each NVM way, the size of R bits is identical to the number of NVM ways. The RBV is altered when the RWSR is changed. If the RWSR is increased, additional R bits are set to 1. Unless, all R bits are updated to rearrange non-replaceable ways.

The cache operation for non-replaceable ways should be different from that for replaceable ways. When a cache hit is occurred to a non-replaceable way, the LRU information is not updated. In the case of a cache miss, the non-replaceable ways are not involved in the victim selection. A detailed description of the management policy is as follows:

- Cache hit in the replaceable way: If a requested block is in the replaceable ways, the cache operations do not differ from the conventional cache. When a read hit occurs in the replaceable ways, the data is sent to the requestor. In case of a write hit, the data is modified. LRU information is updated in both cases.

- 2. Cache hit in the non-replaceable way: When the block is in the non-replaceable way, the data is sent to the requestor or the data is written the same as the replaceable way. However, no operation for updating LRU bits occurs because the LRU information of the non-replaceable way is useless in the DWA.

- 3. Cache Miss: A new block is only placed into the replaceable way. When a cache miss occurs and a requested block arrives, the LRU block in the replaceable ways is selected to load the requested block.

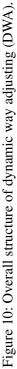

#### 4.2.3 Algorithm of dynamic way adjusting

We rearrange the replaceable ways to avoid lifetime shortening when the replaceable NVM ways are reduced. If some NVM ways are frequently selected as replaceable way during execution, these ways will be worn out earlier than other NVM ways. Thus, we shift the start point of replaceable ways to allow write operations be performed as evenly as possible through the ways. The basic concept is similar to the round robin policy. At the time of selecting the replaceable ways, the NVM way next to the current replaceable ways is chosen for the first replaceable way. The last position register

(LPR) remembers the current last replaceable way to support way shifting. This policy is initiated when RCR is saturated.

Figure 11 shows an example of how this policy works. Assume that the number of the replaceable ways is five and the first three NVM ways are assigned to the replaceable ways. Note that two SRAM ways are always considered the replaceable ways. If the number of the replaceable ways is increased to six, from the fourth NVM way to the sixth NVM way, then the first NVM way is chosen as the replaceable ways.

Figure 12 presents the DWA in detail. When a cache access is confirmed to an ATD hit (line 1), the MSDR is updated if it is not the maximum LRU value (line 2-4). Then, we compare the RWSR with the MSDR to check whether the current size of NVM ways is less than the minimum size of NVM ways (line 5). If the MSDR exceeds the RWSR, some nonreplaceable NVM ways are changed to be replaceable from the last NVM way of the current replaceable NVM ways. The amount of activated NVM ways is the difference between the MSDR and the RWSR. The LPR is automatically updated during way adjusting within range from 0 to  $W_{nvm}$  (line 6-9). After this adjustment, the RWSR is updated to the MSDR and the RCR is reset to 0 (line 10-11). The replaceable NVM ways are rearranged when the MSDR does not exceed RWSR when RCR is saturated (line 13). If the MSDR is larger than the number of SRAM ways, the RWSR is updated to MSDR (line 14-15). Unless, the RWSR is set to the number of SRAM ways because all SRAM ways are replaceable (line 16-17). As a first step of shifting replaceable ways, all R bits are set to 0 (line 19). Then, from the last

Figure 11: Example of way shifting.

replaceable NVM way, NVM ways of the amount of RWSR are assigned to be replaceable (line 20-23). To keep track of the maximum stack distance again, the MSDR is initialized to 0 and RCR is reset to 0 (line 24-25). If RCR is smaller than the threshold, RCR is increased by 1 (line 27).

```

Algorithm : Adjust_Replaceable_Ways

Parameters:

RWSR: Replaceable way size register

MSDR: Maximum stack distance register

LPR: Last position register (1 \le LPR \le W_{nvm})

RCR: Resizing counter register

R[x]: Replaceable bit at xth NVM way

Initial conditions:

RWSR \leftarrow W_{nvm} + W_{sram}

MSDR \leftarrow 1

LPR \leftarrow W_{nvm} - 1

RCR \leftarrow 0

All R[x] \leftarrow 1

During execution:

1: if ATD hit then

2: if hit_block.LRU > MSDR then

3:

MSDR \leftarrow hit\_block.LRU

4: end if

5:

if MSDR > RWSR then

for i \leftarrow 1 to (MSDR - RWSR) do

6:

7:

LPR \leftarrow (LPR+1) \% W_{nvm}

8:

R[LPR] \leftarrow 1

9:

end for

10:

RWSR \leftarrow MSDR

RCR \leftarrow 0

11:

12: else

13:

if RCR is saturated then

14:

if MSDR > W_{sram} then

15:

RWSR \leftarrow MSDR

16:

else

17:

RWSR \leftarrow W_{sram}

18:

end if

19:

All R[x] \leftarrow 0

20:

for i \leftarrow 1 to (RWSR - W_{nvm}) do

21:

LPR \leftarrow (LPR+1) \% W_{nvm}

22:

R[LPR] \leftarrow 1

23:

end for

24:

MSDR \leftarrow 0

25:

RCR \leftarrow 0

26:

else

27:

RCR \leftarrow RCR + 1

28:

end if

29: end if

30: end if

```

Figure 12: Algorithm for DWA.

# 4.3 Cache partitioning for hybrid cache architecture

Modern chip-multiprocessors (CMP) have employed multi-level on-chip caches to address the memory wall problem that is caused by the difference between access latencies of the memory and the processor. Generally, the last-level cache (LLC) occupies the largest area in the cache system and consumes a significant static energy in the CMP. To reduce the area and the leakage power, researchers have considered using non-volatile memory (NVM) [1, 3, 5] as LLC. Unlike the SRAM-based LLC, the NVMbased LLC consumes little leakage power and requires less area with higher density than SRAM. While NVM has these advantages, they also suffer from shortcomings such as longer latency to complete a write operation and higher dynamic energy consumption for a write operation compared to SRAM. Most researchers have focused on minimizing the write counts of NVM because the number of write operations strongly affects the dynamic energy consumption as well as performance.

Hybrid cache architectures (HCA) have been proposed [16, 17, 18, 19, 47] to overcome these limitations of NVM. HCA mainly consists of NVM, but some of them are replaced with SRAM to reduce the number of write requests on NVM. Previous studies concerning HCA have attempted to detect the write-intensive blocks, sets, or ways to allocate these to the SRAM. However, their schemes have not usually focused on reducing the NVM linefill counts, while the portion of NVM linefill operations is larger than

that of NVM write hit operations over the total of write operations to NVM for many applications. In addition, there is no accurate prediction model to estimate the change of the write counts of NVM when the number of SRAM and NVM ways allocated to each core are changed in CMP environments. Since the number of cache ways is closely related to the cache misses, assigning cache ways or releasing cache ways influences the miss rate of the LLC. Even though the write intensity of NVM ways of a core is larger than other cores, providing more SRAM ways with the core does not guarantee reducing the NVM write counts. If a core which hands over SRAM ways to other core generates much more cache misses with the reduced cache capacity, the write counts can be increased due to the extra linefill operations. However, they have not considered this kind of side effects in their schemes.

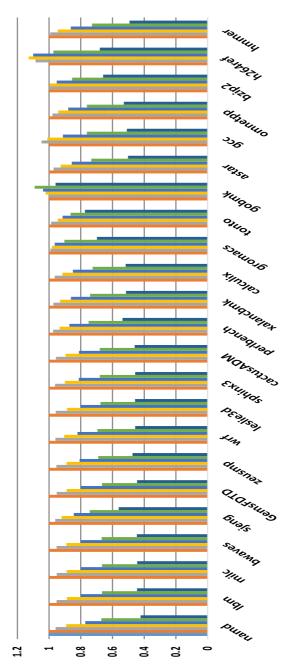

We propose a novel cache partitioning that is called a linefill-aware cache partitioning scheme (LCP) to reduce the dynamic energy consumption by efficiently allocating SRAM ways and NVM ways to cores. To this end, the thesis presents appropriate metrics and an algorithm for partitioning to realize LCP. We introduce three metrics that represent change of miss counts ( $\Delta M$ ), write counts ( $\Delta W$ ), and NVM write counts ( $\Delta NVMW$ ), respectively. An algorithm for cache partitioning of LCP consists of two steps. First, the number of cache ways for each core is determined in order to reduce the miss counts. Next, the SRAM ways and the NVM ways are allocated to cores to minimize write counts of NVM.

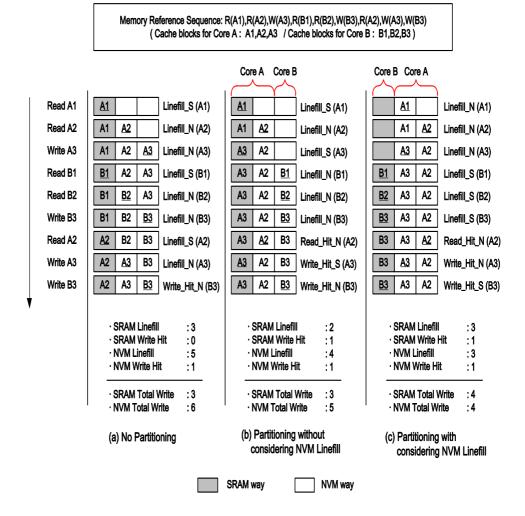

Figure 13: (a) No partitioning is applied. (b) Partitioning without NVM linefill. (c) Partitioning with NVM linefill.

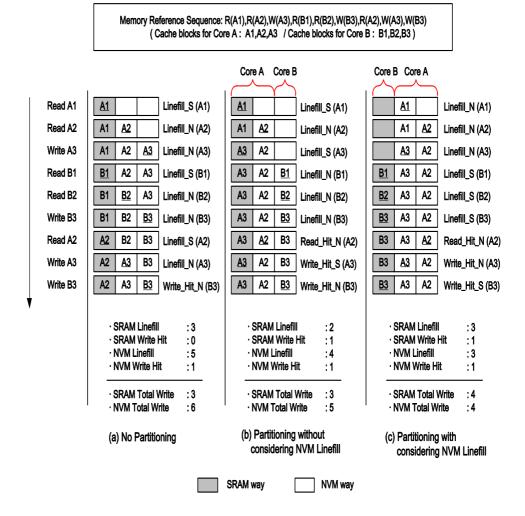

#### 4.3.1 Linefill-aware cache partitioning

To optimize the NVM write counts in HCA, SRAM ways and NVM ways should be efficiently allocated to cores. To help the understanding, we provide an illustration in Figure 13. The cache in this example consists of one SRAM way and two NVM ways. We assumed that there are two cores: core A and core B. A1, A2, and A3 are cache blocks for core A, and B1, B2, and B3 are cache blocks for core B. The cache accesses occur as the memory reference sequence shown in the box of the top in Figure 13.

When there is no special care for the LLC, the total write for the SRAM way is 3 (3 for SRAM linefill) and the NVM total write is 6 (5 for NVM linefill and 1 for NVM write hit), as shown in Figure 13(a). If the cache partitioning only considering the cache misses is applied [39], core A can occupy two cache ways and only one cache way can be assigned to core B (Figure 13(b)). Even though this partitioning decreases two cache misses and one NVM total write, the NVM write counts are not optimized. If a partitioning algorithm can predict the NVM linefill counts as well as the NVM write hit counts for every possible partitioning, the SRAM way should be allocated to core B to minimize the NVM write counts, as shown in Figure 13(c).

Therefore, a new scheme is required to reduce both the NVM write hit counts and the NVM linefill counts, which saves dynamic energy consumption of HCA. This paper devises new metrics to evaluate the effectiveness of cache partitioning schemes and proposes a linefill-aware cache partition-

| Notation                                              | Description                                                                                                                                                                           |  |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| H[i]                                                  | Hit counts of <i>i</i> th recency position                                                                                                                                            |  |

| WH[i]                                                 | Write hit counts of <i>i</i> th recency position                                                                                                                                      |  |

| M <sub>CONF</sub>                                     | Conflict misses which are the number of cache misses due to partitioning                                                                                                              |  |

| M <sub>NON</sub> _CONF                                | Non-conflict misses which are the number of cache misses re-<br>gardless of partitioning                                                                                              |  |

| H(N)                                                  | Total cache hit counts when the number of allocated ways is N                                                                                                                         |  |

| M(N)                                                  | Total cache misses when the number of allocated ways is N                                                                                                                             |  |

| W(N)                                                  | Total write counts when the number of allocated ways is N                                                                                                                             |  |

| WH(N)                                                 | Total write hit counts when the number of allocated ways is N                                                                                                                         |  |

| $\Delta M(N,N')$                                      | Miss counts change when the number of allocated ways is changed from N to N'                                                                                                          |  |

| $\Delta W(N,N')$                                      | Write counts change when the number of allocated ways is changed from N to N'                                                                                                         |  |

| $\Delta NVMW(N_{SRAM}, N'_{SRAM}, N_{NVM}, N'_{NVM})$ |                                                                                                                                                                                       |  |

|                                                       | NVM write counts change when the number of allocated SRAM ways is changed from $N_{SRAM}$ to $N'_{SRAM}$ and the number of allocated NVM ways is changed from $N_{NVM}$ to $N'_{NVM}$ |  |

Table 5: Notation descriptions for metrics.

ing scheme (LCP) based on these metrics. Table 5 provides a description of notation we define in this section.

## 4.3.2 Metrics for cache partitioning

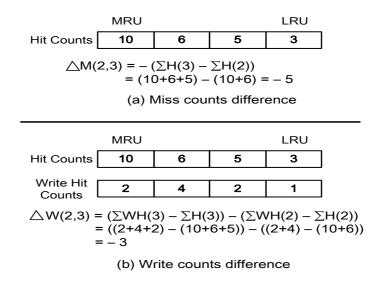

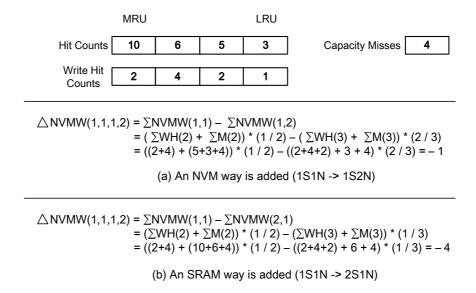

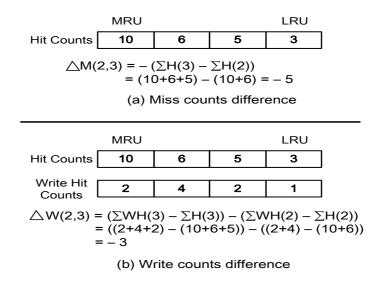

This section describes three metrics for a partitioning decision: Miss counts change ( $\Delta M$ ), write counts change ( $\Delta W$ ), and NVM write counts change ( $\Delta NVMW$ ). We newly devise  $\Delta W$  and  $\Delta NVMW$  and redefine  $\Delta M$  by revisiting the concept of "the utility" in the previous work [39].

Figure 14: Example of stack property.

- Δ*M*: the change of the number of cache misses according to adjusting cache capacity for each core. This metric has been usually adopted to decide the cache partition to improve the performance in previous studies.

- $\Delta W$ : the change of the write counts for both the SRAM write counts and the NVM write counts according to the change of cache capacity.

- $\Delta NVMW$ : the change of the NVM write counts. It is used for the HCA when memory elements are heterogeneous, while two other metrics can be applied in the cache consisting of the same memory element.

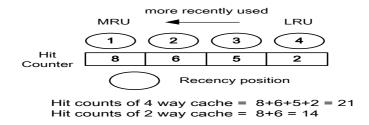

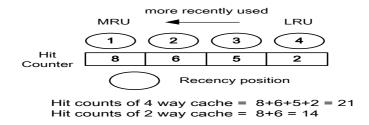

The concept of the utility [39] is used to estimate the reduction in the number of cache misses when a core has extra cache ways. The original paper named this concept as "the utility", but we redefine it " $\Delta M$ " to clarify its meaning. They noticed that LRU replacement policy followed the stack property [45]. If a cache has the stack property, the cache having more cache ways always contains all blocks of the cache having smaller cache ways when the number of sets remains. Figure 14 presents the hit counts of each

recency position in a 4-way cache. In general, the recency position of the block at MRU position is called position 1, and that of the LRU position is called position 4. In this example, if the number of cache ways is reduced to 2 from 4, we expect that the hit counts of the cache will decrease by one-thirds without performing the experiments for a 2-way cache.

$\Delta M$  indicates the change of the miss counts with the change of the number of allocated ways<sup>1</sup>. Let H[i] denote the hit counts of *i*th recency position of a core and H(N) be the total hit counts when the number of allocated ways is *N* of the core. A relationship is established between two metrics.

$$H(N) = \sum_{i=1}^{N} H[i]$$

(4.18)

Since the increase in the miss counts is the same as the reduction in the hit counts, when the number of allocated ways is changed from N to N' of a core,  $\Delta M(N,N')$  is given by

$$\Delta M(N,N') = -(H(N') - H(N)) = \sum_{i=1}^{N} H[i] - \sum_{i=1}^{N'} H[i]$$

(4.19)

A new model is built to estimate the change of the number of write operations with the change of the capacity in the cache. Since improving the hit rate is the most important goal in previous studies,  $\Delta M$  is the only

<sup>&</sup>lt;sup>1</sup>To clear the meaning of the terminology, the number of cache ways assigned for a core are called "the number of allocated cache ways of the core"

metric for cache partitioning in SRAM-based LLC in CMP environment. However, minimizing the write counts should be considered as well as maximizing the overall hit counts in HCA. Thus, we define a new metric ( $\Delta W$ ) for representing the change of the number of write accesses caused by the change of partitioning.