#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

#### Ph.D. DISSERTATION

# Approaches to the Design of Machine Learning System

기계학습 시스템 설계를 위한 방법

**DECEMBER 2015**

# DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE COLLEGE OF ENGINEERING SEOUL NATIONAL UNIVERSITY

Kyounghoon Kim

#### Approaches to the Design of Machine Learning System

기계학습 시스템 설계를 위한 방법

지도교수 최 기 영

이 논문을 공학박사학위논문으로 제출함 2015년 12월

서울대학교 대학원 전기·컴퓨터 공학부 김 경 훈

김경훈의 박사학위논문을 인준함 2015 년 12 월

Approaches to the Design of Machine Learning System

| 위  | 원 장 | :김태환 | (인) |

|----|-----|------|-----|

| 부위 | 원장  | :최기영 | (인) |

| 위  | 원   | :이혁재 | (인) |

| 위  | 원   | :유승주 | (인) |

| 위  | 원   | :이종은 | (인) |

#### **Abstract**

#### Approaches to the Design of Machine Learning System

Kyounghoon Kim

Department of Electrical Engineering and Computer Science

The Graduate School

Seoul National University

Machine learning has been paid attention because intelligence such as recognition, decision making, and recommendation is a helpful utility in industrial, medical, transportation, entertainment systems, and others that human need to interact with. As machine learning techniques are extensively applied to various areas, the needs for more robust algorithms and more efficient hardware have been increased. In order to develop an efficient machine learning system, we have researched from high-level algorithm down to low-level hardware logic; the main focus of our work is on ensemble machine learning and stochastic computing (SC).

The first work is to combine multiple components, i.e., multiple feature extractors (FE) and multiple classifiers in the aspect of pattern recognition. Ensemble of multiple components is one of challenging approaches for constructing a more accurate classifier [3]. It can handle difficult problems where a single classifier easily makes a wrong decision due to lack of training or parameter optimization [4]. Combining the decisions of participating classifiers statistically reduces the risk of wrong decision. We suggest a hierarchical ensemble framework of multiple feature extractors and multiple classifiers (MFMC).

The second work is to construct efficient hardware building blocks for machine learning in order to reduce system complexity and generate high area- and energy-efficient logic, where we exploit the property of machine learning systems that does not require accurate computations. We select stochastic computing (SC),

which is an alternative paradigm to conventional binary arithmetic computing [5].

SC can boost efficiency in terms of area, power, and error tolerance [6], while

relaxing the accuracy of computation.

The third work is to combine both machine learning and stochastic computing,

where we select deep learning. This work presents an efficient DNN design with

stochastic computing. Observing that directly adopting stochastic computing to

DNN has some challenges including random error fluctuation, range limitation,

and overhead in accumulation, we address these problems by removing near-zero

weights, applying weight-scaling, and integrating the activation function with the

accumulator. The approach allows an easy implementation of early decision

termination with a fixed hardware design by exploiting the progressive precision

characteristics of stochastic computing, which was not easy with existing

approaches. Experimental results show that our approach outperforms the

conventional binary logic in terms of gate area, latency, and power consumption.

**keywords**: Machine learning, Stochastic computing, Ensemble learning,

Deep learning, Deep neural networks.

**student number** : 2012-30193

ii

### **Contents**

Contents iii

List of Figures viii

List of Tables xviii

| 1. Ir              | troduction                                              | 1                    |

|--------------------|---------------------------------------------------------|----------------------|

| 1.1Hierarch        | ical Ensemble Learning Framework                        | 1                    |

|                    | e Building Block for Machine I                          | <i>.</i> .           |

| 1.2.1 computing    | Dynamic energy-accuracy tradeng in deep neural networks | <u> </u>             |

| 2. A               | Design Framework for Hierarchical                       | Ensemble of Multiple |

| Feature Extractors | and Multiple Classifiers                                | 7                    |

| 2.1Introduct       | ion                                                     | 7                    |

| 2.2Related v       | vork                                                    | 9                    |

| 2.3 Proposed r   | nierarchical ensemble system 1 2                        |

|------------------|---------------------------------------------------------|

| 2.3.1            | Local Mapping Block and Global Mapping Block $\ 1\ 2$   |

| 2.3.2<br>LMB 1 5 | Complexity comparison according to composition of       |

| 2.3.3 mappings   | Motivation for differentiating local and global 1 7     |

| 2.3.4            | Reinforcement learning for LMB                          |

| 2.3.5            | Construction of Bayesian network from GMB $2\ 4$        |

| 2.4Experimen     | atal results                                            |

| 2.4.1            | Measure of effectiveness for WMV and RL 3 3             |

| 2.4.2            | Pedestrian detection dataset                            |

| 2.4.3            | Comparison between GMB and AdaBoost 4 1                 |

| 2.4.4            | UCI Multiple Features dataset                           |

| 2.4.5            | LMB selection                                           |

| 2.4.6            | Discussion                                              |

| 2.5 Conclusion   | n                                                       |

| 3. Syr           | nthesis of Efficient Stochastic Logic for Many-Variable |

| Expressions 4    | 9                                                       |

| 3.1 Introduction | on                                                      |

| 3.2Related W     | ork                                                     |

| 3.3SC Logic S    | Synthesis for Multivariate Expressions 5 4              |

| 3.3.1           | Probabilistic Logic                                                                                                                          | 5                 | Э                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.3.2           | Definitions                                                                                                                                  | 5                 | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.3.3           | Overview of the Proposed Method                                                                                                              | 6                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

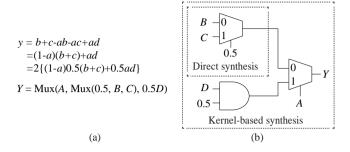

| 3.3.4           | Direct Synthesis VS. Kernel-based Synthesis                                                                                                  | 6                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.3.5           | SC Kernel                                                                                                                                    | 6                 | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.3.6           | Prime SC Kernel                                                                                                                              | 6                 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.3.7           | iSC Kernel                                                                                                                                   | 6                 | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.3.8           | Relationship Between iSC Kernels                                                                                                             | 7                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.3.9           | Hybrid Scheme                                                                                                                                | 7                 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.3.10          | Cost Function                                                                                                                                | 7                 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.3.11          | SC Synthesis Algorithm                                                                                                                       | 7                 | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.4Experimen    | tal Results                                                                                                                                  | 8                 | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

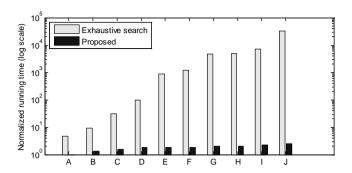

| 3.4.1           | Performance of SC Logic Synthesis Algorithm                                                                                                  | 8                 | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

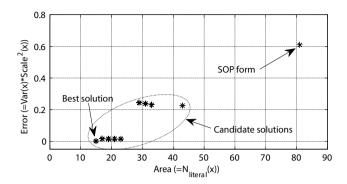

| 3.4.2           | Quality of Synthesis Results                                                                                                                 | 8                 | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.4.3           | Comparison of Accuracy                                                                                                                       | 8                 | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.5Conclusion   | 1                                                                                                                                            | 9                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| An              | Energy-Efficient Random Number Generator                                                                                                     | f                 | or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| astic Circuits  |                                                                                                                                              | 9                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.1 Introductio | n                                                                                                                                            | 9                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.2II. Backgro  | ound                                                                                                                                         | 9                 | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                 | 3.3.2 3.3.3 3.3.4 3.3.5 3.3.6 3.3.7 3.3.8 3.3.9 3.3.10 3.3.11 3.4Experimen 3.4.1 3.4.2 3.4.3 3.5Conclusion An astic Circuits 4.1Introduction | 3.3.2 Definitions | 3.3.2       Definitions       5         3.3.3       Overview of the Proposed Method       6         3.3.4       Direct Synthesis VS. Kernel-based Synthesis       6         3.3.5       SC Kernel       6         3.3.6       Prime SC Kernel       6         3.3.7       iSC Kernel       6         3.3.8       Relationship Between iSC Kernels       7         3.3.9       Hybrid Scheme       7         3.3.10       Cost Function       7         3.3.11       SC Synthesis Algorithm       7         3.4Experimental Results       8         3.4.1       Performance of SC Logic Synthesis Algorithm       8         3.4.2       Quality of Synthesis Results       8         3.4.3       Comparison of Accuracy       8         3.5Conclusion       9 |

|    | 4.2.1              | Preliminaries 9 2                                       |

|----|--------------------|---------------------------------------------------------|

|    | 4.2.2              | Shortcomings of Conventional Approaches 9 3             |

|    | 4.3III. Propos     | sed Stochastic Number Generator                         |

|    | 4.3.1              | Overview of the Proposed SNG                            |

|    | 4.3.2              | Even-distribution Encoding                              |

|    | 4.3.3              | Inter-group Randomization                               |

|    | 4.3.4              | Proposed Building Block for Bit Shuffling $1 \ 0 \ 0$   |

|    | 4.3.5              | Intra-group Randomization                               |

|    | 4.4Experimer       | ntal Results                                            |

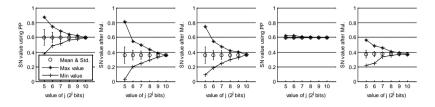

|    | 4.4.1              | Accuracy of Generated Stochastic Bit Stream $1 \ 0 \ 4$ |

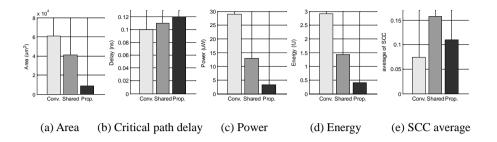

|    | 4.4.2              | Area, Delay, Power, Energy and SCC Average $1\ 0\ 4$    |

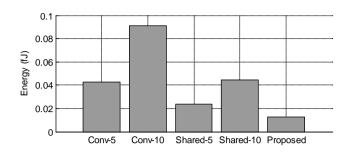

|    | 4.4.3<br>Precision | Energy Efficiency When Operated under Maximal 1 0 5     |

|    | 4.5 Conclusion     | on                                                      |

| 5. | Ap                 | proximate De-randomizer for Stochastic Circuits 1 0 7   |

|    | 5.1 Introduction   | on                                                      |

|    | 5.2Proposed        | Approximate Parallel Counter                            |

|    | 5.2.1              | Analysis for Gate Count in 1-layer Approximate PC 1 0 9 |

|    | 5.2.2              | Analysis for Error in 1-layer Approximate PC 1 1 0      |

|    | 5.3Experimer       | ntal Results                                            |

|    | 5.4Conclusion      | n 1 1 2                                                 |

| 6.   | D              | ynamic    | Energy-Accuracy      | Trade-off    | Using    | Stoc | has | tic |

|------|----------------|-----------|----------------------|--------------|----------|------|-----|-----|

| Comp | outing in Deep | Neural    | Networks             |              | •••••    | 1    | 1   | 3   |

|      | 6.1Introduct   | ion       |                      |              |          | ]    | 1   | 3   |

|      | 6.2Backgrou    | ınd       |                      |              |          | 1    | 1   | 5   |

|      | 6.4DNN Usi     | ing Stoc  | hastic Circuit       |              |          | 1    | 1   | 7   |

|      | 6.4.1          | Overv     | view of the Propose  | d DNN usii   | ng SC    | 1    | 1   | 7   |

|      | 6.4.2          | Remo      | oving Near-Zero We   | ights        |          | 1    | 1   | 9   |

|      | 6.4.3          | Apply     | ving Weight Scaling  | ·            |          | 1    | 2   | C   |

|      | 6.4.4          | Activ     | ation Function with  | Accumulat    | tion     | 1    | 2   | 1   |

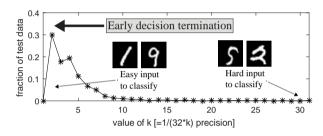

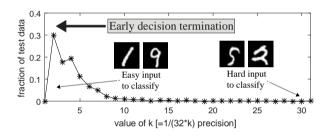

|      | 6.5Early De    | cision Te | ermination           |              |          | 1    | 2   | 5   |

|      | 6.5.1          | Movi      | ng Average Trackin   | g Output Ti  | ends     | ]    | 2   | 6   |

|      | 6.6Experime    | ental Res | sults                |              |          | 1    | 2   | 7   |

|      | 6.6.1          | Accui     | racy of DNN Using    | SC           |          | 1    | 2   | 8   |

|      | 6.6.2          | Effec     | tiveness of Early De | ecision Terr | nination | ı 1  | 2   | S   |

|      | 6.6.3          | Comp      | parison of Synthesis | Results      |          | 1    | 3   | C   |

|      | 6.7Conclusio   | on        |                      |              |          | 1    | 3   | 2   |

| 7.   | C              | onclusio  | n                    |              |          | 1    | 1 3 | 4   |

Bibliography 1 3 6

## **List of Figures**

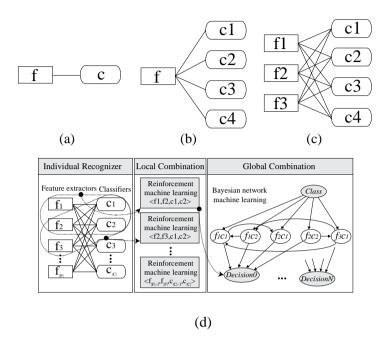

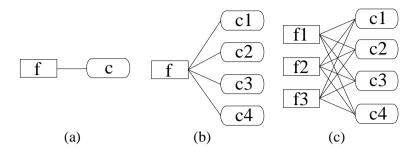

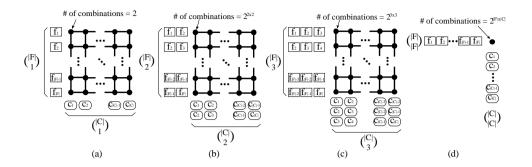

| Fig. 1. Example of machine learning system regarding the number of components.                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| stands for a feature extractor; 'c' stands for a classifier. (a) Traditiona                                                                                                                                                                                                                                                                                                                                                |

| single feature extractor (FE) and single classifier. (b) Single FE and multiple classifiers represented by AdaBoost. (c) Multiple feature extractors and multiple classifiers (MFMC). (d) Proposed hierarchical ensemble of MFMC by using local and global combinations                                                                                                                                                    |

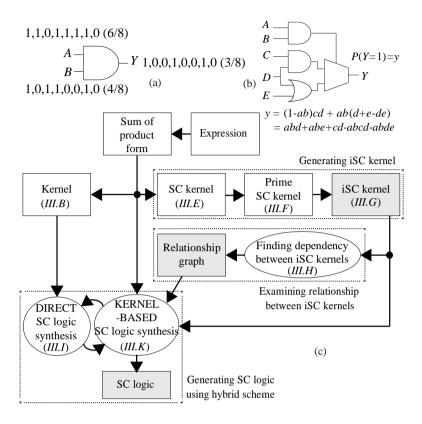

| Fig. 2. Stochastic computing (SC) and the proposed algorithm for SC logic synthesis. (a) Stochastic number representation and the multiplication of SC numbers. (b) SC logic example with operations representing y= abd+abe+cd-abcd-abde. (c) Overall process for the proposed SC logic synthesis algorithm.                                                                                                              |

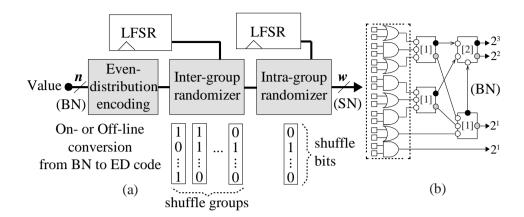

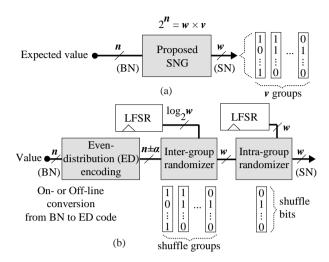

| Fig. 3. Overview of the proposed randomizer and de-randomizer for SC. (a) The proposed stochastic number generator (SNG) consists of three parts such as even-distribution (ED) encoding, inter-group, and intra-group randomizer with linear feedback shift register (LFSR) input. (b) The proposed de-randomizer using an approximate unit (AU), converting 16-bit stochastic number (SN) into 4-bit binary number (BN). |

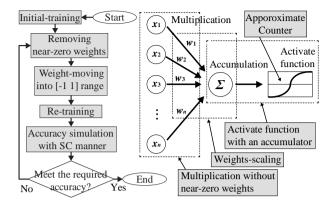

| Fig. 4. Overview of the proposed procedures and main idea for deep neural                                                                                                                                                                                                                                                                                                                                                  |

|      | floating-point computation. (b) SC neurons are operated with SC exploiting the suggested solutions in testing phase. (c) Early decision termination by using progressive precision of SC.                                                                                                                                                                                                                                                                                                                                              |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. | 5. Example of detection system regarding the number of components. 'f' stands                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | for a feature extractor; 'c' stands for a classifier. (a) Traditional single feature                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | extractor and single classifier. (b) Single feature extractor and multiple classifiers represented by AdaBoost. (c) Multiple feature extractors and multiple classifiers (MFMC)                                                                                                                                                                                                                                                                                                                                                        |

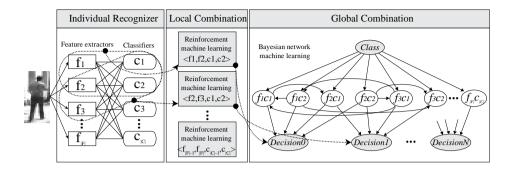

| Fig. | 6. Overview of the design framework for hierarchical ensemble of MFMC $1$                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

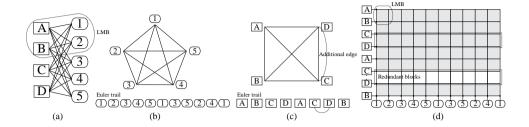

| Fig. | 7. Constructing GMB from LMBs. (a) 4x5 ensemble of MFMC. (b) Euler trail for a complete graph containing odd number vertexes. (c) Euler path for a graph having even number vertexes where additional edges are inserted in order to build an Euler trail. (d) GMB consisting of LMBs, where redundant blocks show up due to additional edges                                                                                                                                                                                          |

| Fig. | 8. Different ways of combining FEs and classifiers to make an LMB and using it as the building block for making a GMB. (a) An LMB contains only one FE and one classifier. Although it reduces the complexity, it cannot consider the interaction between FEs or between classifiers. (b) An LMB contains two FEs and two classifiers, which is the proposed scheme. (c) Three FEs and three classifiers belong to an LMB. (d) An LMB has all the relations for  F  FEs and  C  classifiers; and thus there is only one LMB in the GMB |

| Fig. | 9. Two directions for combining multiple classifiers. Weighted majority vote takes the vertical direction, while regression and generalization takes the horizental direction. Two methods can generate different results even for                                                                                                                                                                                                                                                                                                     |

|      | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                              |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. | 10. Psedo-code of the reinforcement learning algorithm for calculating weights for an LMB                                                                                                                                                                                                                                                                                                                                         |

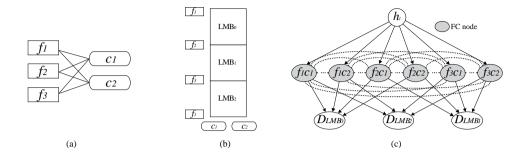

| Fig. | 11. Construction of Bayesian networks. (a) The system consists of three feature extractors and two classifiers. (b) GMB is created by LMBs for the system. (c) Bayesian network is composed of 1) class node denoted as hl, 2) FC nodes denoted as fick, which correspond to FE-classifier pairs, and 3)                                                                                                                          |

|      | decisions of LMBs denoted as DLMBk                                                                                                                                                                                                                                                                                                                                                                                                |

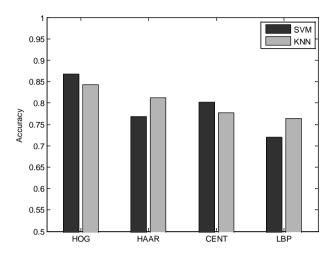

| Fig. | 12. Accuracy comparison between feature extractors (HOG, HAAR, CENT, LBP) and classifiers (SVM, KNN) in DaimlerChrysler dataset. It depicts that feature extractors are more significant than classifiers                                                                                                                                                                                                                         |

| Fig. | 13. Learning algorithm of Bayesian network for GMB                                                                                                                                                                                                                                                                                                                                                                                |

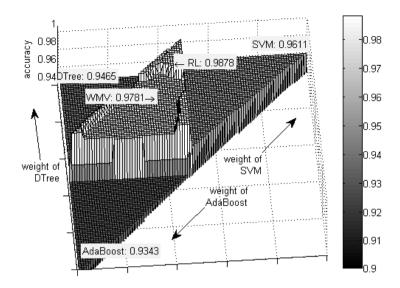

| Fig. | 14. Accuracy of individual classifiers (SVM, AdaBoost, and decision tree), ensemble using optimal WMV weight not considering dependency, and RL weight for Banknote Authentication in UCI dataset. For the illustration, the plane wS+wA+wD=1 (the sum of weights should be one) is projected into xy-plane, where wS, wA and wD are the weights of SVM, AdaBoost, and decision tree, respectivly; z-axis represents the accuracy |

| Fig. | 15. Examples of DaimlerChrysler Pedestrian dataset. The upper ones are pedestrian samples while the lower ones are non-pedestrian samples 3 4                                                                                                                                                                                                                                                                                     |

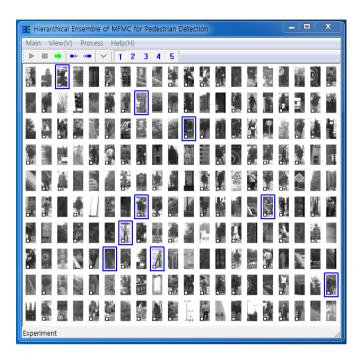

| Fig. | 16. Screenshot of an experimental application of hierarchical ensemble of MFMC to pedestrian detection using DaimlerChrysler dataset, which is developed based on OpenCV with the C++ language                                                                                                                                                                                                                                    |

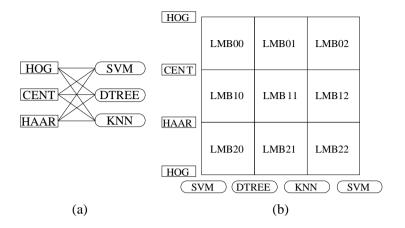

| Fig. | 17. Experimental system in the paper. (a) The system consists of full connections between feature extractors and classifiers: HOG, CENT, HAAR as feature extractors and SVM, DTREE, KNN as classifiers. (b) GMB is comprised of nine LMBs, each of which has 2x2 combinations                                                                                                                                                     |

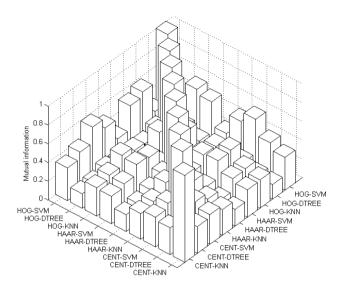

| Fig. | 18. Mutual information for all pairs of nine classifiers. Dependency between                                                                                                                                                                                                                                                                                                                                    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | classifiers actually exists                                                                                                                                                                                                                                                                                                                                                                                     |

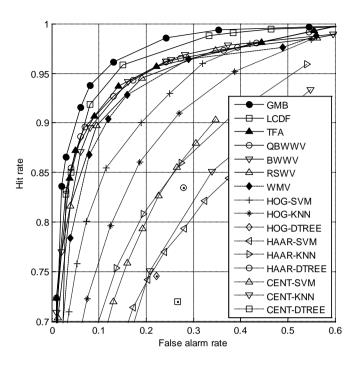

| Fig. | 19. Performance comparison between the proposed framework and the other schemes                                                                                                                                                                                                                                                                                                                                 |

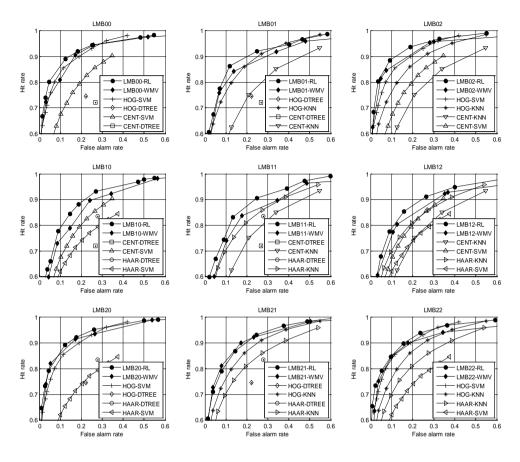

| Fig. | 20. ROC curves of all the LMBs. Construction of the LMBs is identical to that in Fig. 17                                                                                                                                                                                                                                                                                                                        |

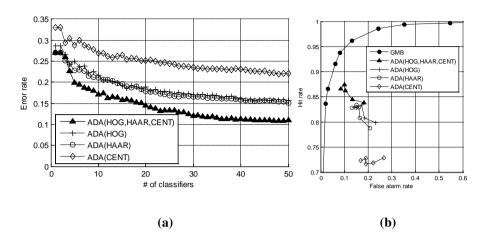

| Fig. | 21. Performance comparison between GMB and AdaBoost. (a) Error rate of AdaBoost according to the number of classifiers; the parentheses represent the used feature set(s). (b) ROC curve, where the points of AdaBoost depict 10, 20, 30, 40, and 50 classifiers, respectively                                                                                                                                  |

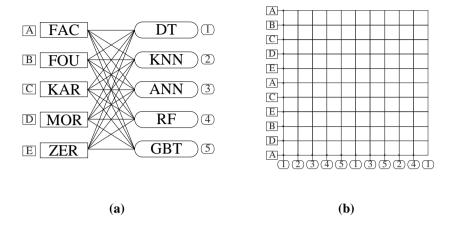

| Fig. | 22. GMB composition for UCI Multiple Feature dataset, where five FEs and five classifiers are used. (a) MFMC combination between FEs and classifiers. (b) GMB consists of 10x10 LMBs                                                                                                                                                                                                                            |

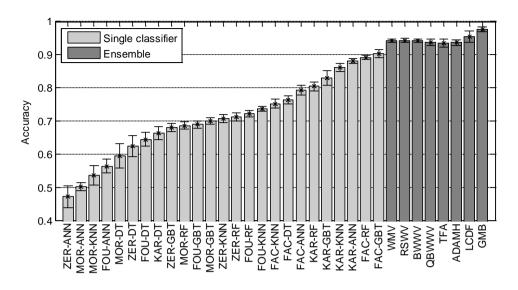

| Fig. | 23. Experimental result for UCI Multiple Features dataset for single classifiers and ensemble methods                                                                                                                                                                                                                                                                                                           |

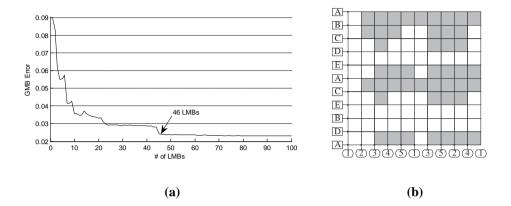

| Fig. | 24. LMB selection while closely maintaining the accuracy of the original GMB containing all the LMBs. (a) GMB error decreases as the number of LMBs increases, but beyond 46 LMBs the decrease saturates. (b) The selected 46 LMBs with gray color                                                                                                                                                              |

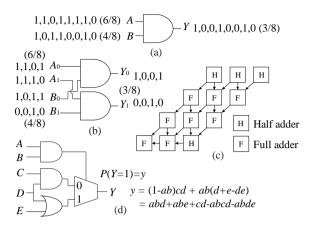

| Fig. | 25. Example of stochastic logic. (a) Multiplication with a single AND gate. (b) Partially parallel version for multiplication with two AND gates. (c) Three-bit multiplication using half adders and full adders with conventional binary radix encoding. (d) SC logic example with operations representing $y=abd+abe+cd-abcd-abde$ , where simple Boolean gates are mapped to compound arithmetic operations. |

| Fig. | 26. SC gates and their arithmetic operations in unipolar encoding 5. 5.                                                                                                                                                                                                                                                                                                                                         |

| Fig. | 27. Overview of the proposed SC logic synthesis with many variables. (a) The proposed scheme begins with a basic block (BB) and its data flow graph (DFG). (b) Example of correlation. (c) Method to solve the correlation problem by using different random sources and a D flip-flop. (d) Swapping the wire can |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | remove the correlation in the parallel version. 5 6                                                                                                                                                                                                                                                               |

| Fig. | 28. Overall process for the proposed algorithm                                                                                                                                                                                                                                                                    |

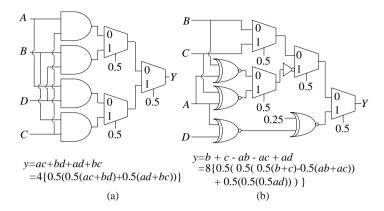

| Fig. | 29. Examples of direct synthesis. (a) $ac+bd+ad+bc$ , where scale factor is 4. (b) $b+c-ab-ac+ad$ ; the scale factor is 8. It is implemented with bipolar encoding because of scaled subtraction.                                                                                                                 |

| Fig. | 30. SC kernels for expression $t$ in Example 2. (a) SOP expression for $t$ and the synthesis result T. (b) Schematic diagram for T. (c) DAG for SC-kernel 6 6                                                                                                                                                     |

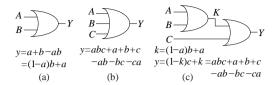

| Fig. | 31. Decomposition of three-input OR gate. All the gates contain (1-P) expression. (a) Two-input OR gate. (b) Three-input OR gate. (c) The decomposed three-input OR gate contains (1-P) form such as (1-a) and (1-k).                                                                                             |

| Fig. | 32. Finding iSC kernels from prime SC kernels for Example 3. (a) SOP form of expression $z$ . (b) SC logic for expression $z$ . (c) DAG of prime SC kernels derived by expression $z$ . (d) Final DAG of iSC kernels derived from (c) 6 8                                                                         |

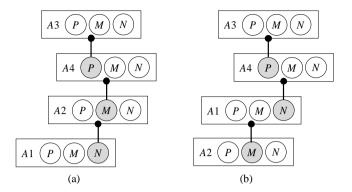

| Fig. | 33. Relationship between two iSC kernels. (a) The procedure to find the relationships between them. (b) An example of iSC kernel relationship graph for Fig. 30                                                                                                                                                   |

| Fig. | 34. Examples of relationships between iSC kernels in Fig. 30. A3 exists in P of A4, M of A2, and N of A1; A4 exists in M of A2 and N of A1                                                                                                                                                                        |

| Fig. | 35. Example of hybrid scheme combining both kernel-based and direct synthesis. (a) Expression of Fig. 29b and their SC logic. (b) Schematic diagram for the example in unipolar encoding                                                                                                                          |

| Fig.      | 36.                                                | Pseudo-code of the top-level function for the proposed algorithm $7\ 7$                                                                                                                                               |

|-----------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig.      | 37.                                                | Pseudo-code for Kernel-Based-Synthesis function                                                                                                                                                                       |

| Fig.      | 38.                                                | Pseudo-code for Containing-Search function. 7 9                                                                                                                                                                       |

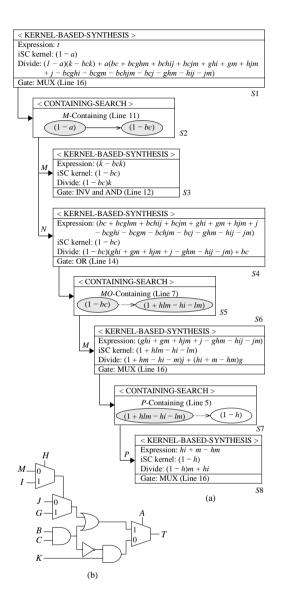

| Fig.      | com                                                | SC logic synthesis example for Fig. 30. The result is a different candidate pared with Fig. 30b. (a) Synthesis steps according to each iSC kernel. (b) smatic diagram for the result.                                 |

| Fig.      | 40.                                                | Comparison of the proposed algorithm with exhaustive search $8\ 2$                                                                                                                                                    |

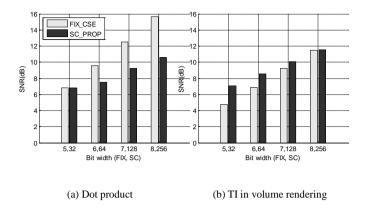

| Fig.      |                                                    | Area and error values of candidate solutions for TI used to calculate the function (19).                                                                                                                              |

| Fig.      | algo<br>arith                                      | Comparison of TI implementations. (a) SC logic generated by the proposed rithm. (b) SC logic expression of (a). (c) Data flow of conventional metic operations optimized with CSE. (d) Arithmetic expressions for the |

|           | node                                               | s in (c)                                                                                                                                                                                                              |

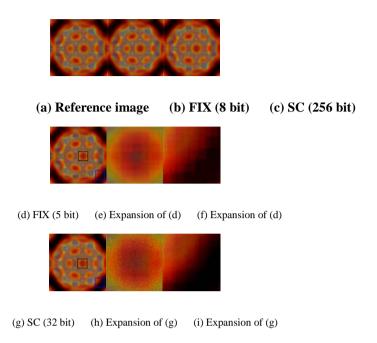

| Fig.      |                                                    | Result images for TI in volume rendering. 8 5                                                                                                                                                                         |

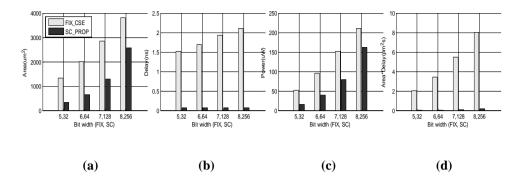

| Ü         | 43.<br>44.<br>conv                                 |                                                                                                                                                                                                                       |

| Fig.      | 43.<br>44.<br>conv<br>(d) A<br>45.                 | Result images for TI in volume rendering                                                                                                                                                                              |

| Fig.      | 43.<br>44.<br>conv<br>(d) A<br>45.<br>(c) P<br>46. | Result images for TI in volume rendering                                                                                                                                                                              |

| Fig. Fig. | 43. 44. conv (d) A 45. (c) P 46. (b) S 47. gene    | Result images for TI in volume rendering                                                                                                                                                                              |

|      | one stochastic bit is generated by using one store unit (i.e., D-flip/flop). (b) Partitioning of stochastic bit-stream. $9\ 3$                                                                                                                                                                                                                                                                                                   |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

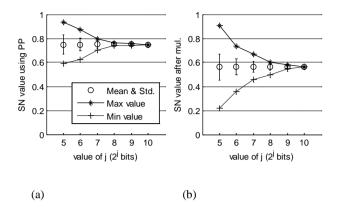

| Fig. | 49. SN generation for 0.75 with progressive precision (PP) in 2 <sup>10</sup> bits SC circuit. (a) Distribution of SN values. (b) Multiplication of two SNs generated with PP using an AND gate                                                                                                                                                                                                                                  |

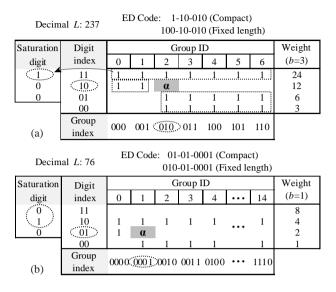

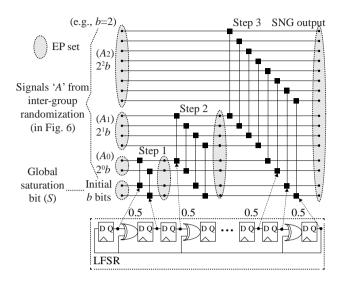

| Fig. | 50. Overview of the proposed SNG. (a) SNG with BN input and SN output, where $v$ groups are generated and each group has $w$ bit-width. (b) The proposed SNG consists of three parts such as even-distribution (ED) encoding, inter-group, and intra-group randomizer with LFSR input. 9 5                                                                                                                                       |

| Fig. | 51. Even-distribution (ED) encoding, where white space means zero. (a) ED code represents decimal number 204 with seven groups (column) and four digits (row) per group when $b$ is 3. (b) Example of ED code with 15 groups when $b$ is 1                                                                                                                                                                                       |

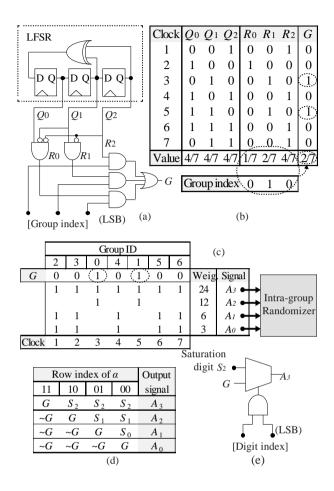

| Fig. | 52. Inter-group randomization, where the group index is from Fig. 51a. (a) Shuffling circuit for inter-group randomization. (b) Final signal $G$ is a scrambled one and the value $2/7$ matches with the number of BGs. (c) Shuffling of groups according to the value of $G$ . (d) Method to actually generate the output signal, where $'\sim G'$ means negation of $G$ . (e) Example of                                       |

|      | logic for output signal $A_3$ 9 9                                                                                                                                                                                                                                                                                                                                                                                                |

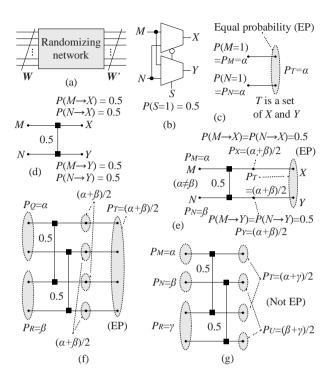

| Fig. | 53. Analysis of randomness after swapping signals. (a) Overview of randomizing network. (b) Swapping logic. (c) Definition of equal probability (EP) set. (d) Probability for input signals to be passed onto output signals. (e) Constructing an EP set by using a swapper. (f) Constructing an EP set of output signals from two different EP sets of input signals. (g) A case that output signals do not belong to an EP set |

| Fig. | 54. Logic for intra-group randomization consisting of randomizing network and an LFSR. The input signals is from inter-group randomization                                                                                                                                                                                                                                                                                       |

| Fig. | PP                                                                                                                                                                                                                                                                                                                                                                                        |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. | 56. Comparison of area, critical path delay, power, energy, and SCC average value to generate a 2 <sup>10</sup> -bit stream for conventional SNG, SNG sharing two LFSRs [1], and the proposed SNG. For fair comparison, all cases are implemented in parallel manner. The length of LFSRs in two previous approaches is 10 while the number of bits in a group of the proposed SNG is 32. |

| Fig. | 57. Energy to generate 2 <sup>5</sup> bits. Conv-5 and Conv-10 represent that the length of LFSR in the conventional SNG are 5 and 10, respectively. Shared-5 and Shared-10 mean the shared SNGs                                                                                                                                                                                          |

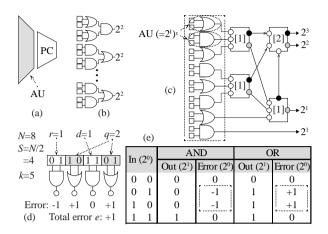

| Fig. | 58. Stochastic numbers (SNs) and conventional counters, where the numbers in brackets represent the bit index of binary numbers (BNs). (a) Multiplication of two SNs. (b) Accumulative serial counter. (c) Accumulative parallel counter (APC). (d) Example of a parallel counter (PC) converting 15 bits SN into 4 bits BN.                                                              |

| Fig. | 59. The proposed parallel counter (PC). (a) Overview of the PC. (b) 2-layer approximate unit (AU). (c) The proposed PC using 1-layer AU, converting 16-bit SN into 4-bit BN. (d) Example of 1s distribution in 1-layer AU. (e) Output and error for all inputs in AND and OR gate                                                                                                         |

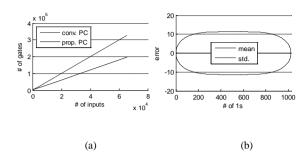

| Fig. | 60. Theoretical analysis of the proposed scheme. (a) The number of gates for the conventional PC and the proposed PC with 1-layer AU. (b) The mean and standard deviation of number of errors for 1-layer PC with 1024 input bits 1 1 1                                                                                                                                                   |

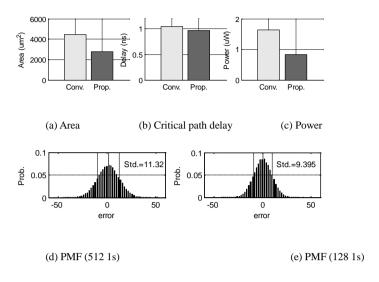

| Fig. | 61. Experimental results of the proposed approximate PC compared with the conventional PC in 1024-bit stream. (a) Area. (b) Critical path delay. (c) Power (d) PMF when 512 1s among 1024 bits. (e) PMF when 128 1s                                                                                                                                                                       |

| Figure 62. Deep neural network (DNN) using stochastic computing. (a) Stochastic multiplication in unipolar encoding with the range [0 1]. (b) Bipolar stochastic multiplication with $[-1 \ 1]$ range. (c) DNN layers with weight vector $W^k$ in layer $k$                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 63. Random error problem occurs when applying SC to DNN. (a) Random error of XNOR gate in 1024-bit stream as absolute value. (b) 20000 weights distribution in 200x100 networks (left Y-axis) and error multiplying by zero (right Y-axis).                                                                                                                |

| Figure 64. Overview of the proposed procedures and main idea. (a) Training procedure for DNN using SC with 32-bit floating-point computation. (b) SC neurons are operated with SC exploiting the suggested solutions in testing phase. (c) Early decision termination by using progressive precision of SC 1 1 7                                                  |

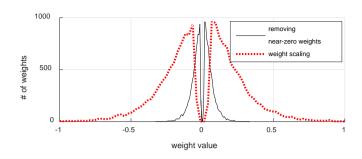

| Figure 65. The distribution of weights after removing near-zero weights and weight-scaling. 1 1 9                                                                                                                                                                                                                                                                 |

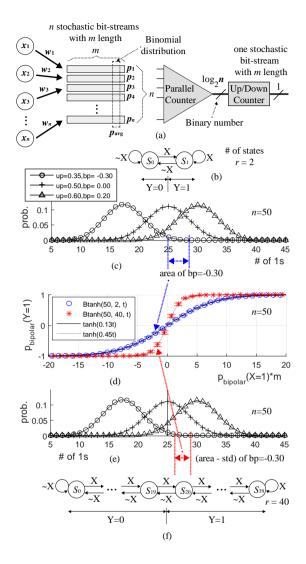

| Figure 66. A stochastic neuron and the mechanism of state-machine based activate function. (a) A single neuron using SC. (b) state-machine having two states in an up/down counter. (c) Using binomial distribution for the logistic function. (d) The proposed activate function. (e) Binomial distribution with many states. (f) state-machine having 40 states |

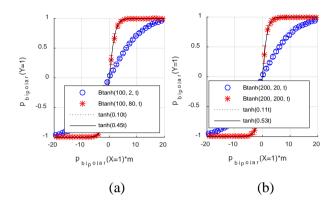

| Figure 67. The result comparison between the proposed hyperbolic tangent $Btanh(\cdot)$ and the original $tanh(\cdot)$ . (a) The number of states is two and 80 for 100 bit-streams. (b) 20 and 200 states for 200 bit-streams                                                                                                                                    |

| Figure 68. Pseudo-code for the proposed <i>Btanh</i> (*)                                                                                                                                                                                                                                                                                                          |

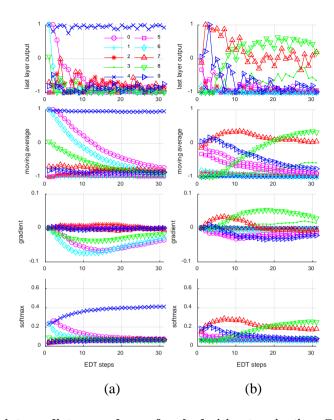

| Figure 69. The intermediate procedures of early decision termination. Ground truths are 4 and 8, respectively                                                                                                                                                                                                                                                     |

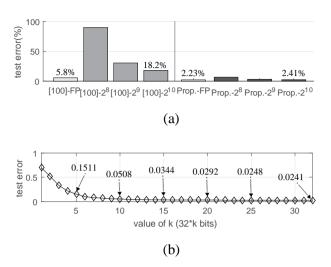

| Figure 70. Comparison misclassification error. MNIST test data error in 32-bit                                                                                                                                                                                                                                                                                    |

| floating point is 2.23%. The proposed method is 2.41% while the previous              |  |  |  |

|---------------------------------------------------------------------------------------|--|--|--|

| work [11] is 18.2% in 2 <sup>10</sup> -bit stream                                     |  |  |  |

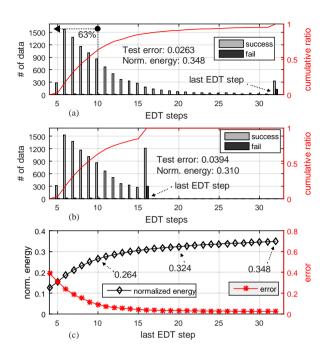

| Figure 71. Experimental result for early decision termination (EDT) where one EDT     |  |  |  |

| step use 32 stochastic bits. (a) Applying EDT to 1024 bits. (b) The last step of      |  |  |  |

| EDT is set to the 16 <sup>th</sup> step (i.e., 16x32=512 bits). (c) Normalized energy |  |  |  |

| reduction between using and not using EDT and test error according to the last        |  |  |  |

| EDP step                                                                              |  |  |  |

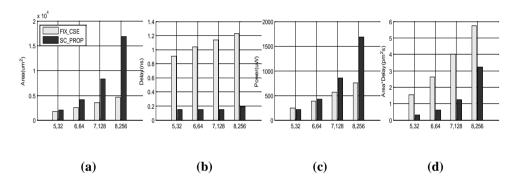

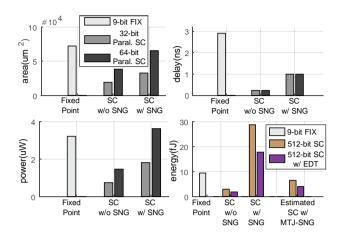

| Figure 72. Synthesis results. All cases are compared with 9-bit fixed-point (9-b      |  |  |  |

| FIX). In case of area, critical path delay, and power, 32- and 64-bit parallel SC     |  |  |  |

| circuits are used. In case of energy, SC circuit executes $2^9$ (=512) bits 1 3 2     |  |  |  |

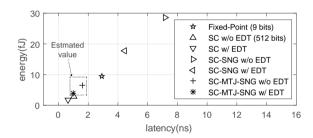

| Figure 73. Iso-area performance comparison. Energy and latency for each case are      |  |  |  |

| compared under same area. The values for SC circuits using MTJ-SNG are                |  |  |  |

| estimated according to [2]. Fixed-point computes with 9-bit width while all SC        |  |  |  |

| circuits compute 2 <sup>9</sup> (=512) bits                                           |  |  |  |

### **List of Tables**

| TABLE I    | 1 | 6 |

|------------|---|---|

| TABLE II   | 3 | 3 |

| TABLE III  | 3 | 9 |

| TABLE IV   | 4 | 4 |

| TABLE V    | 4 | 7 |

| Table VI   | 5 | 8 |

| Table VII  | 6 | 2 |

| Table VIII | 6 | 4 |

| Table IX   | 7 | 2 |

| Table X    | 8 | 2 |

| Table XI   | 8 | 8 |

#### 1. Introduction

#### 1.1 Hierarchical Ensemble Learning Framework

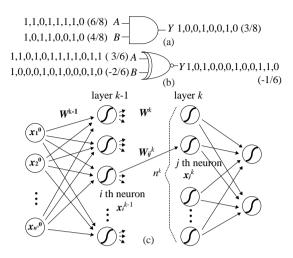

Classification systems can be classified into three categories according to the number of FEs and classifiers as shown in Fig. 1: a single FE and a single classifier (a), multiple classifiers sharing the same feature vector (b), and multiple FEs as well as multiple classifiers (c) which we call MFMC.

As illustrated in Fig. 1 (d), the proposed ensemble system consists of three steps for MFMC: constructing all possible FE-classifier pairs, building a set of local combinations from the set of pairs using reinforcement machine learning, and making a final decision by constructing a global combination based on Bayesian network. In the first step, each FE generates a feature set in a vector format from an input image. The feature vectors from an FE are used by each classifier pairing with the FE for training and testing, which is identical to conventional approach for creating individual recognizers. In the following steps, hierarchical approach is adopted in order to reduce the complexity due to the exponential number of possible combinations. Thus, in the second step, a limited number of FE-classifier pairs are combined to make a group (there can be many different combinations and each combination generates its own group), and weights for the pairs in the group are adjusted according to their effectiveness by using reinforcement learning. Then, in the last step, for a final decision, the groups are merged into a single decision structure called Bayesian network. Experimental results show that the proposed approach gives accuracy higher than any other existing approaches.

# 1.2 Hardware Building Block for Machine Learning By Using Stochastic Computing

For applications such as machine learning that tolerate a certain level of

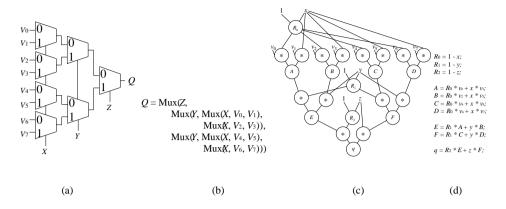

Fig. 1. Example of machine learning system regarding the number of components. 'f' stands for a feature extractor; 'c' stands for a classifier. (a) Traditional single feature extractor (FE) and single classifier. (b) Single FE and multiple classifiers represented by AdaBoost. (c) Multiple feature extractors and multiple classifiers (MFMC). (d) Proposed hierarchical ensemble of MFMC by using local and global combinations.

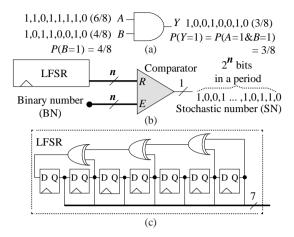

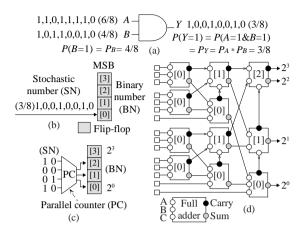

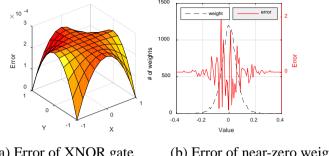

inaccuracy, stochastic computing (SC) can be a good alternative to conventional binary arithmetic. SC uses the probability of 1's in a (pseudo) random bit stream to represent a number as shown in Fig. 2 (a), and allows for an extremely efficient implementation of complex functions (such as multiplication and exponentiation), typically with a few logic gates. (b) shows a complex arithmetic operation using a small number of gates.

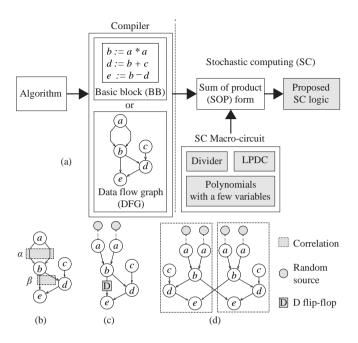

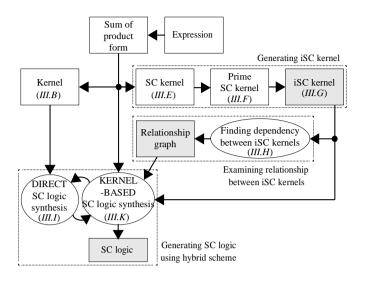

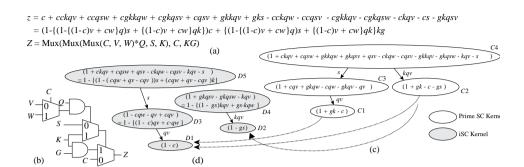

Given expressions such as kernels in machine learning, it is very important to generate efficient SC circuits. Thus, we present a SC logic synthesis scheme. As illustrated in Fig. 2, the overall process for the proposed method consists of three

Fig. 2. Stochastic computing (SC) and the proposed algorithm for SC logic synthesis. (a) Stochastic number representation and the multiplication of SC numbers. (b) SC logic example with operations representing y= abd+abe+cd-abcd-abde. (c) Overall process for the proposed SC logic synthesis algorithm.

parts: i) generating iSC kernels, i.e., implementable SC kernels, ii) finding relationship between iSC kernels, and iii) synthesizing SC logic from the original input expression using the iSC kernels and their relationships.

The basic idea is to decompose the input expression into iSC kernels, each of which can be implemented using the SC gates. If some decomposition is derived from the original expression, it is accepted as a solution. There can be many different solutions, and for the exploration, the algorithm tries to divide the given polynomial expression by each iSC kernel. The algorithm pre-examines the

Fig. 3. Overview of the proposed randomizer and de-randomizer for SC. (a) The proposed stochastic number generator (SNG) consists of three parts such as even-distribution (ED) encoding, inter-group, and intra-group randomizer with linear feedback shift register (LFSR) input. (b) The proposed de-randomizer using an approximate unit (AU), converting 16-bit stochastic number (SN) into 4-bit binary number (BN).

relationships between iSC kernels and exploits them during the search. In the final step, an SC logic network is synthesized for the original expression by using the iSC kernels and the relationships represented as a graph.

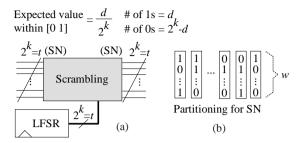

Since SC is based on random numbers, a randomizer and a de-generation are very important components. In case of stochastic number generator (SNG) as a randomizer, instead of generating new 0s and 1s, the proposed SNG shuffles 1s in the existing bit stream by using a random source. The basic idea of the proposed SNG is to evenly distribute 1s over the entire bit stream, which is named as *low-discrepancy* (LD). Fig. 3(a) shows the outline of the proposed SNG, which consists of three parts: even-distribution (ED) encoding, inter-group randomizer, and intra-group randomizer.

In case of de-randomizer, we propose an approximate parallel counter (PC) as shown in Fig. 3. (b), which consists of two parts: an approximation unit (AU) and a conventional accurate PC. The approximate PC exploiting an AU is shown in (b).

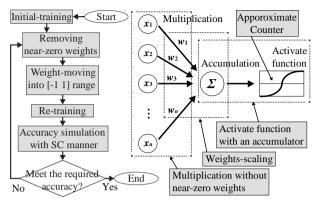

(a) Training procedures

(b) Testing with the SC neuron

(c) Early decision termination

Fig. 4. Overview of the proposed procedures and main idea for deep neural networks (DNNs). (a) Training procedure for DNN using SC with 32-bit floating-point computation. (b) SC neurons are operated with SC exploiting the suggested solutions in testing phase. (c) Early decision termination by using progressive precision of SC.

The input weight of AU is  $2^0$  while the output weight becomes  $2^l$ , where l is the number of layers.

#### 1.2.1 Dynamic energy-accuracy trade-off using stochastic computing in

#### deep neural networks

Since bringing to break-through in terms of classification accuracy, deep neural

networks (DNNs) have been recently paid great attention. This work presents a method of implementing a DNN using stochastic computing (SC), Based on the observation that directly adopting stochastic computing to DNN has some challenges such as random error fluctuation, range limitation from -1 to 1, and overhead in accumulating many products of inputs and synaptic weights, we address these problems by removing near-zero weights, applying weight-scaling, and using state machine based activation function integrated with the accumulator. We also suggest the early decision termination (EDT) which is very useful in terms of energy and decision speed because most of test inputs are far from decision boundary. The experimental results demonstrate that the accuracy of DNN using SC meets that of conventional floating-point system and the gains in terms of area, power, critical path delay, and energy is meaningful compared with conventional fixed-point arithmetic.

# 2. A Design Framework for Hierarchical Ensemble of Multiple Feature Extractors and Multiple Classifiers

#### 2.1 Introduction

Ensemble of multiple classifiers is one of promising approaches for constructing a more accurate classifier. It can handle difficult problems where a single classifier easily makes a wrong decision due to lack of training or parameter optimization. Combining the decisions of participating classifiers statistically reduces the risk of wrong decision. In addition, such an ensemble system can generate a sensible solution in a special environment, where several classifiers should be trained with different training datasets due to temporal or spatial constraints. It can also solve instability problems that frequently occur in a single classifier like neural networks with different initial conditions. Another benefit comes from a fact that no single classifier solution can tackle all problems according to the no free lunch theorem (NFL) [3] [4] [7]. Due to these advantages, classifier ensemble has been an active research area in the literature of machine learning and pattern recognition [8] [9] [10]. According to these researches, an ensemble system generates more stable and accurate results compared to conventional single classifier systems.

Considering multiple feature extractors (FEs) and classifiers used for constructing an ensemble system, classification systems can be classified into three categories according to the number of FEs and classifiers as shown in Fig. 1. Conventional classification systems use a single FE and a single classifier as shown in Fig. 1(a). There are systems that use multiple classifiers sharing the same feature vector generated by an FE as shown in Fig. 1(b). AdaBoost is a well-known machine

Fig. 5. Example of detection system regarding the number of components. 'f' stands for a feature extractor; 'c' stands for a classifier. (a) Traditional single feature extractor and single classifier. (b) Single feature extractor and multiple classifiers represented by AdaBoost. (c) Multiple feature extractors and multiple classifiers (MFMC).

learning algorithm that supports this model [11]. There have been various researches to extend the concept of AdaBoost for better performance [12] [13]. The third category shown in Fig. 1(c) has been introduced [14] [15] [16]; it uses multiple FEs as well as multiple classifiers and thus we call it MFMC.

One of most representative applications of classifier ensemble is pedestrian detection, which is a key problem in transportation, surveillance, robotics, entertainment systems, and other systems that need to recognize and interact with human [17] [18] [19] [20]. In pedestrian detection, vision based approach is the most effective and popular way. However, it is still quite challenging due to large variations in many aspects such as human clothing, pose, size, background, weather, and illumination. In order to overcome the difficulty, many studies have been conducted in many different ways [21]. However, the achieved accuracy is still insufficient to be used for real applications including advanced driver assistance system (ADAS), thus leaving room for improvement as mentioned by Dollar *et al.* [22]. Especially, in case that a pedestrian is far from the camera or under partial occlusion, the accuracy degrades dramatically. In order to improve the accuracy or detection rate, many studies have tried to find more effective extractors and classifiers such as those in [23] [24] [25] [26] [27] and [28]. The researches have

focused on finding good features as well as good classifiers. Meanwhile, utilizing combination(s) of multiple FEs and classifiers has also been studied; it has a strong advantage compared to single FE, single classifier counterparts.