#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

### Ph.D. DISSERTATION

# METHODOLOGIES FOR RELIABLE CLOCK NETWORKS FOR HIGH-SPEED AND LOW-POWER DIGITAL SYSTEMS

저전력 고성능 디지털 시스템을 위한 고신뢰도의 클럭 네트워크 설계 방법론

BY

Hyungjung Seo

August 2015

DEPARTMENT OF ELECTRICAL ENGINEERING AND

COMPUTER SCIENCE

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

### Ph.D. DISSERTATION

# METHODOLOGIES FOR RELIABLE CLOCK NETWORKS FOR HIGH-SPEED AND LOW-POWER DIGITAL SYSTEMS

저전력 고성능 디지털 시스템을 위한 고신뢰도의 클럭 네트워크 설계 방법론

BY

Hyungjung Seo

August 2015

DEPARTMENT OF ELECTRICAL ENGINEERING AND

COMPUTER SCIENCE

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

## METHODOLOGIES FOR RELIABLE CLOCK NETWORKS FOR HIGH-SPEED AND LOW-POWER DIGITAL SYSTEMS

저전력 고성능 디지털 시스템을 위한 고신뢰도의 클럭 네트워크 설계 방법론

지도교수 김 태 환 이 논문을 공학박사 학위논문으로 제출함 2015 년 5 월

> 서울대학교 대학원 전기 컴퓨터 공학부 서 형 중

서 형 중의 공학박사 학위논문을 인준함 2015 년 6 월

| 위 원 장 |  |

|-------|--|

| 부위원장  |  |

| 위 원   |  |

| 위 원   |  |

| 위 원   |  |

## Abstract

As the process variation is dominating to cause the clock timing variation among chips to be much large, conventional clock tree based clock network is not able to guarantee the timing constraint of a digital system. To overcome the limitations of traditional clock design techniques, various techniques have been studied. This dissertation addresses three techniques that have been widely used for designing robust clock network and proposes developed methods.

First, it is widely accepted that post-silicon tunable (PST) clock buffers can effectively resolve the clock timing violation. Since PST buffers, which can reset the clock delay to flip-flops after the chip is manufactured, impose a non-trivial implementation area and control circuitry, it is very important to minimally allocate PST buffers while satisfying the chip yield constraint. In this dissertation, we (1) develop a graph-based chip yield computation technique which can update yields very efficiently and accurately for incremental PST buffer allocation, based on which we (2) propose a systematic (bottom-up and top-down with refinement) PST buffer allocation algorithm that is able to fully explore the design space of PST buffer allocation.

Second, clock skew scheduling is one of the essential steps that must be carefully performed during the design process. This dissertation addresses the clock skew optimization problem integrated with the consideration of the inter-dependent relation between the setup and hold skews, and clk-to-Q delay of flip-flops, so that the time margin is more accurately and reliably set aside over that of the previous methods, which have never taken the integrated problem into account. Precisely, based on an accurate flexible model of setup skew,

hold skew, and clk-to-Q delay, we propose a stepwise clock skew scheduling

technique in which at each iteration, the worst slack of setup and hold skews is

systematically and incrementally relaxed to maximally extend the time margin.

Lastly, clock tree with cross links and clock spine have an intermediate

characteristics for skew tolerance and power consumption, compared to clock

tree and clock mesh which are two extreme structures of clock network. Unlike

the clock tree with links between clock nodes, which is a sort of an incremental

modification of the structure of clock tree, clock spine network is a completely

separated structure from the structures of tree and mesh. Consequently, it is

necessary and essential to develop a synthesis algorithm for clock spines, which

will be compatible to the existing synthesis algorithms of clock trees and clock

meshes. To this end, this dissertation first addresses the problem of automating

the synthesis of clock-gated clock spines with the objective of minimizing total

clock power while meeting the clock skew and slew constraints. The key idea of

our proposed synthesis algorithm is to identify and group the flip-flops with tight

correlation of clock-gating operations together to form a spine while accurately

predicting and maintaining clock skew and slew variations through the buffer

insertion and stub allocation.

In summary, this dissertation presents clock tuning techniques with consid-

eration of post-silicon tuning, flexible flip-flop timing model, and clock-gated

clock spine synthesis algorithm.

Keywords: VLSI&CAD, post-silicon tuning, static timing analysis, flexible

flip-flop timing model, clock spine synthesis

**Student Number**: 2011-30237

ii

# Contents

| Abstra | uct                                                                                  | i  |

|--------|--------------------------------------------------------------------------------------|----|

| Chapte | er 1 INTRODUCTION                                                                    | 1  |

| 1.1    | Clock Distribution Network                                                           | 1  |

| 1.2    | Process Variation                                                                    | 2  |

| 1.3    | Flexible Flip-flop Timing Model                                                      | 3  |

| 1.4    | Clock Spine                                                                          | 3  |

| 1.5    | Contributions of This Dissertation                                                   | 6  |

| Chapt  | er 2 POST-SILICON TUNABLE CLOCK BUFFER AL-<br>LOCATION BASED ON FAST CHIP YIELD COM- |    |

|        | PUTATION                                                                             | 8  |

| 2.1    | Introduction                                                                         | 8  |

| 2.2    | Systematic Exploration of PST Buffer Allocation                                      | 10 |

|        | 2.2.1 Observations                                                                   | 10 |

|        | 2.2.2 Problem Definition                                                             | 15 |

|        | 2.2.3 Allocation Algorithm                                                           | 16 |

| 2.3    | Fast Timing Yield Computation                                                        | 17 |

|        | 2.3.1 Preliminaries                                                                  | 17 |

|        | 2.3.2 Incremental Yield Computation                          | 22 |

|--------|--------------------------------------------------------------|----|

| 2.4    | Experimental Result                                          | 24 |

| 2.5    | PST Buffer Configuration Techniques                          | 31 |

| 2.6    | Summary                                                      | 32 |

| Chapte | er 3 POST-SILICON TUNING BASED ON FLEXIBLE                   |    |

|        | FLIP-FLOP TIMING                                             | 34 |

| 3.1    | Introduction                                                 | 34 |

| 3.2    | Preliminary and Definitions                                  | 40 |

|        | 3.2.1 Flexible Flip-Flop Timing Model                        | 40 |

|        | 3.2.2 Definitions                                            | 40 |

| 3.3    | Motivational Examples                                        | 42 |

| 3.4    | Clock Skew Scheduling for Slack Relaxation Based on Flexible |    |

|        | Flip-Flop Timing                                             | 46 |

|        | 3.4.1 Overall Flow                                           | 46 |

|        | 3.4.2 Finding Local Clock Skew Schedule                      | 48 |

| 3.5    | Experimental Results                                         | 51 |

| 3.6    | Summary                                                      | 57 |

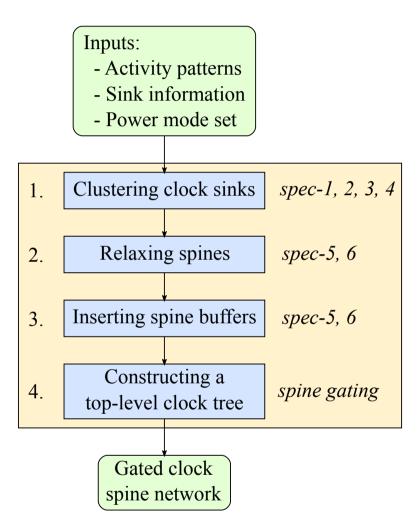

| Chapte | er 4 SYNTHESIS FOR POWER-AWARE CLOCK SPINES                  | 61 |

| 4.1    | Introduction                                                 | 61 |

| 4.2    | Preliminaries and Motivation                                 | 64 |

|        | 4.2.1 Clock Spine                                            | 64 |

|        | 4.2.2 Activity Patterns                                      | 67 |

|        | 4.2.3 Power Computation                                      | 67 |

| 4.3    | Algorithm for Clock Spine Synthesis                          | 68 |

|        | 4.3.1 Problem Definition                                     | 68 |

|        | 4.3.2 Power-Aware Sink Clustering                            | 70 |

|         | 4.3.3 Spine Relaxation            | . 77 |

|---------|-----------------------------------|------|

|         | 4.3.4 Spine Buffer Allocation     | . 80 |

|         | 4.3.5 Top-Level Tree Construction | . 86 |

| 4.4     | Experimental Results              | . 86 |

| 4.5     | Summary                           | . 91 |

| Chapte  | er 5 CONCLUSION                   | 95   |

| 5.1     | Chapter 2                         | . 95 |

| 5.2     | Chapter 3                         | . 95 |

| 5.3     | Chapter 4                         | . 96 |

| Bibliog | graphy                            | 97   |

| 초목      |                                   | 106  |

# List of Figures

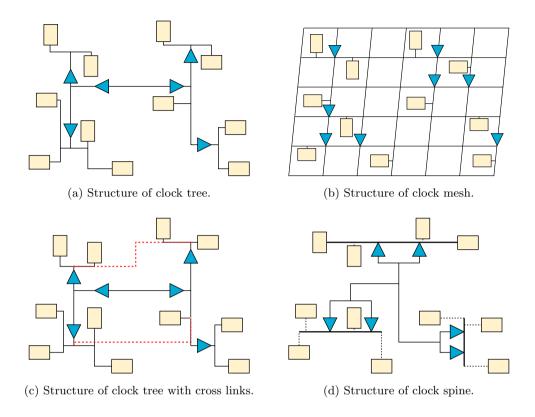

| Figure 1.1 | Two extreme structures of clock networks in (a) and (b) and     |   |

|------------|-----------------------------------------------------------------|---|

|            | intermediate structures in (c) and (d) with terms of the clock  |   |

|            | skew variability and power dissipation                          | 5 |

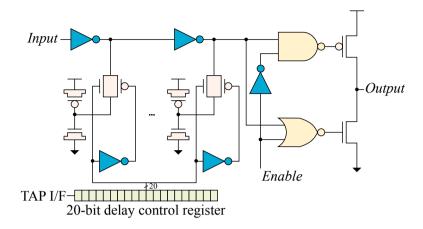

| Figure 2.1 | The structure of PST buffer. The delay from Input to Out-       |   |

|            | put is adjusted by the delay control register which selectively |   |

|            | switches the transistors according to the information from the  |   |

|            | TAP point. [11]                                                 | ) |

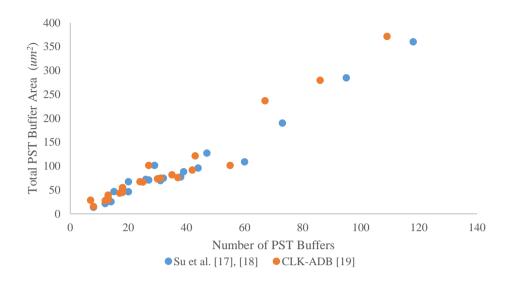

| Figure 2.2 | The relation between the number of PST buffers allocated        |   |

|            | and the resulting total PST area                                | ) |

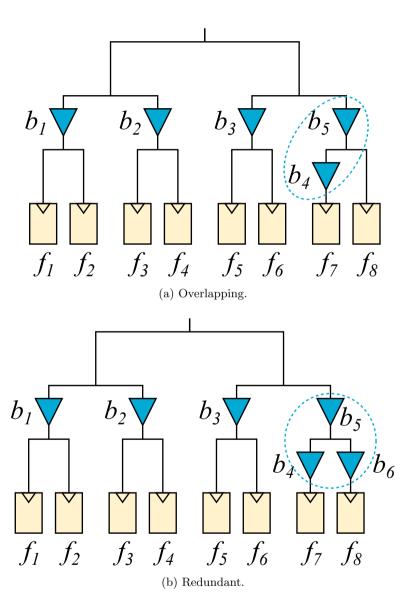

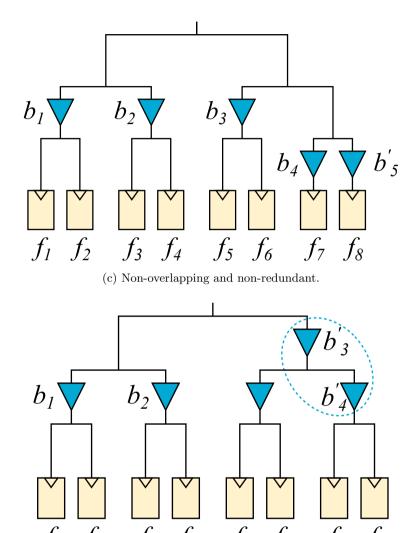

| Figure 2.3 | Classification of PST buffer allocations: (a) overlapping PST   |   |

|            | buffer allocation; (b) redundant PST buffer allocation; (c)     |   |

|            | non-overlapping and non-redundant PST buffer allocation of      |   |

|            | (a) and (b); (d) a possibly better overlapping PST allocation   |   |

|            | than (c)                                                        | 3 |

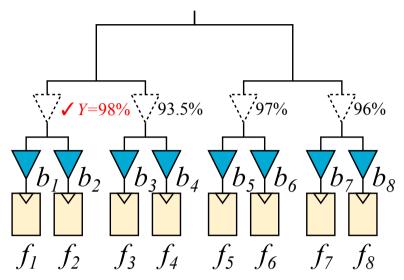

| Figure 2.4 | An example illustrating the bottom-up exploration of PST                                                            |    |

|------------|---------------------------------------------------------------------------------------------------------------------|----|

|            | buffer allocation. A refinement step after the last iteration                                                       |    |

|            | follows, which iteratively checks if some of the PST buffers                                                        |    |

|            | can be removed while meeting the yield constraint                                                                   | 19 |

| Figure 2.5 | A portion of circuit with PST buffers to adjust the time to                                                         |    |

|            | trigger flip-flops $f_i$ and $f_j$                                                                                  | 20 |

| Figure 2.6 | Constraint graph representing the timing relation between                                                           |    |

|            | flip-flops: (a) a portion of circuit instance, $I$ , with the allo-                                                 |    |

|            | cation of PST buffers $b_1$ , $b_2$ , and $b_3$ that are used to adjust                                             |    |

|            | clock arrival times to flip-flips $f_1$ , $f_2$ , and $f_3$ , respectively; (b)                                     |    |

|            | constraint graph $G(I)$                                                                                             | 21 |

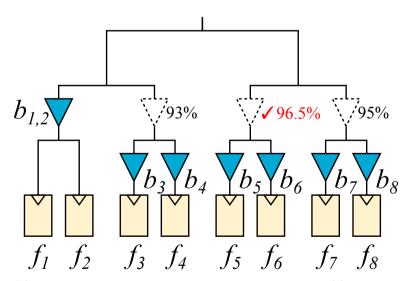

| Figure 2.7 | Enumeration of all loops in an instance of PST buffer alloca-                                                       |    |

|            | tion and generation of reuse relation between loops and merg-                                                       |    |

|            | ing candidates: (a) an instance, $I,$ of PST buffer allocation in                                                   |    |

|            | a clock tree. Six PST buffers $b_1, \cdots b_4, b_{5,6}, b_{7,8}$ are allocated;                                    |    |

|            | (b) constraint graph $G(I)$ and PST buffer merging candidates                                                       |    |

|            | $MG_1, MG_2,$ and $MG_3$ in $G(I)$ ; (c) list $L$ of loops in $G(I)$ ; (d)                                          |    |

|            | reuse table $R[-,-]$ to represent the $T_l$ reuse relation between                                                  |    |

|            | the loops and merging candidates                                                                                    | 26 |

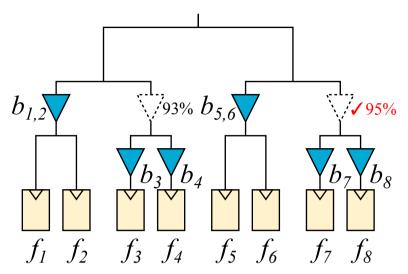

| Figure 2.8 | Generation of a sequence for $\max$ operations. Reusable par-                                                       |    |

|            | tial max results for trials of merging candidates are: (a) initial                                                  |    |

|            | result table $R$ ; (b) $\max\{T_{l_5}, T_{l_6}\}$ followed by $\max\{T_{l_1}, T_{l_2}\}$ ,                          |    |

|            | $\max\{T_{l_3},T_{l_4}\}, \text{ and } \max\{T_{l_7},T_{l_8}\}; \text{ (c) } \max\{T_{(l_3,l_4)},T_{l_5},T_{l_6}\}$ |    |

|            | $(=T_{(l_3,l_4,l_5,l_6)}); (d) \max\{T_{(l_1,l_2)},T_{l_3,l_4,l_5,l_6)}\} (=T_{(l_1,\cdots,l_6)}); (e)$             |    |

|            | $max\{T_{(l_1,\dots,l_6)},T_{(l_7,l_8)}\}\ (=T_{l_1,\dots,l_8)}. \dots \dots \dots \dots \dots$                     | 28 |

| Figure 2.9 | Comparing the exploration space and the number PST buffers                   |    |

|------------|------------------------------------------------------------------------------|----|

|            | allocated by exhaustive enumeration of all instances and our                 |    |

|            | PST-alloc.                                                                   | 33 |

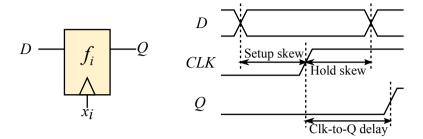

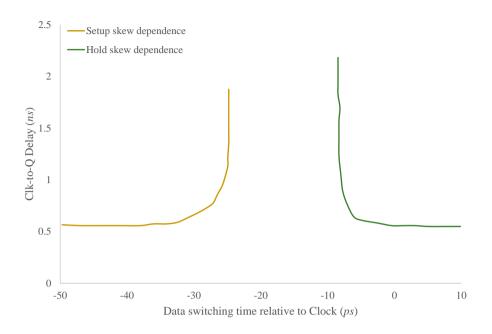

| Figure 3.1 | Description of setup skew $t_S$ , hold skew $t_H$ , and clk-to-Q delay       |    |

|            | $t_Q$ for a flip-flop with input ${\cal D}$ and output $Q$ [29]. The values  |    |

|            | of $t_S$ and $t_H$ of flip-flop $f_i$ determine the value of $t_Q$ of the    |    |

|            | flip-flop, which in turn affects the values of $t_S$ and $t_H$ of a          |    |

|            | flip-flop that will be driven by flip-flop $f_i$                             | 35 |

| Figure 3.2 | Relation among setup skew, hold skew, and clk-to-Q delay [29].               | 36 |

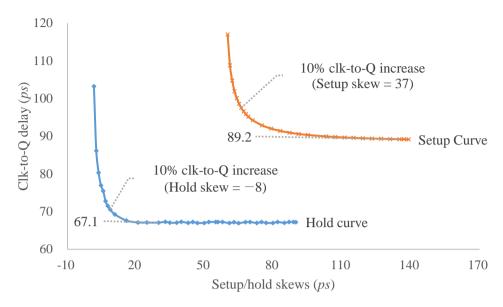

| Figure 3.3 | Setup curve: the change of clk-to-Q delay $t_Q$ as the setup skew            |    |

|            | $t_S$ changes, in which the hold skew $t_H$ is fixed to $-8ps.\ Hold$        |    |

|            | $\mathit{curve}$ : the change of clk-to-Q delay $t_Q$ as the hold skew $t_H$ |    |

|            | changes, in which the setup skew $t_S$ is fixed to $37ps.$                   | 37 |

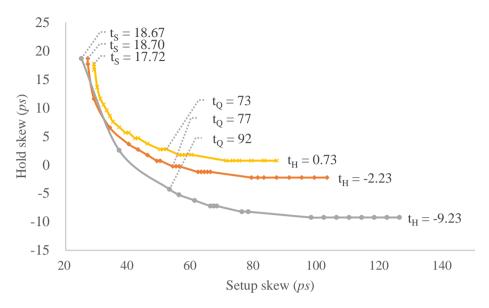

| Figure 3.4 | Three curves showing the trade-off between the setup skew $t_S$              |    |

|            | and hold skew $t_H$ for clk-to-Q delay $t_Q = 73, 77, \text{ and } 92ps.$    |    |

|            | As the clk-to-Q delay is shortened, the flexibility of trading               |    |

|            | the setup skew with hold skew is reduced                                     | 38 |

| Figure 3.5 | Comparison of the conventional STAs which use nonflexible                    |    |

|            | flip-flop timing and the enhanced STAs ([33, 35, 34, 36]) using              |    |

|            | flexible setup and hold times, but not clk-to-Q delay                        | 43 |

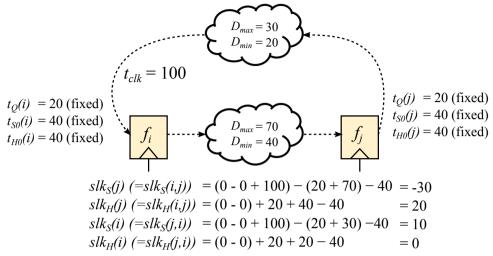

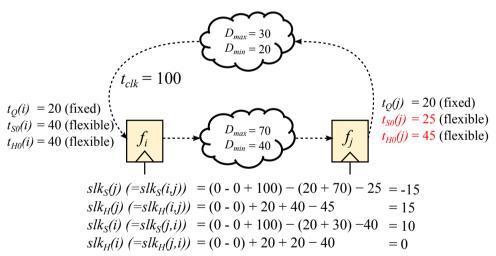

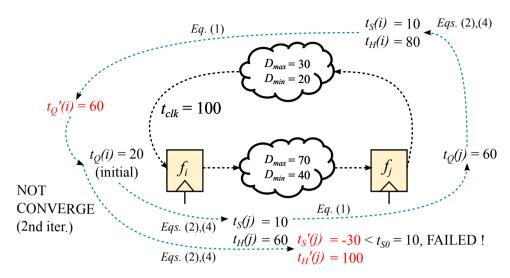

| Figure 3.6  | Conventional STAs [37, 38] which fully use flexible flip-flop                 |    |

|-------------|-------------------------------------------------------------------------------|----|

|             | timing in which the inter-dependent relation between clk-to-                  |    |

|             | Q delay, setup skew, and hold skew are utilized. Initially, clk-              |    |

|             | to-Q delay of a flip-flop is set $(t_Q(i) = 20$ in this example).             |    |

|             | Then, setup skew $t_S(j) = 100 - 20 - 70 = 10$ and hold skew                  |    |

|             | $t_H(j) = 20 + 40 = 60$ , from which $t_Q(j)$ (= 60) is computed.             |    |

|             | In turn, $t_S(i) = 100 - 60 - 30 = 10$ and $t_H(i) = 60 + 20 = 80$ ,          |    |

|             | from which $t_Q(i)$ is computed to 60. This large value of $t_Q(i)$           |    |

|             | causes $t_S(j) = 100 - 60 - 70 = -30$ , which is far less than 10             |    |

|             | $(=t_{S_0})$ . Thus, the STAs report a time failure at $f_j$                  | 44 |

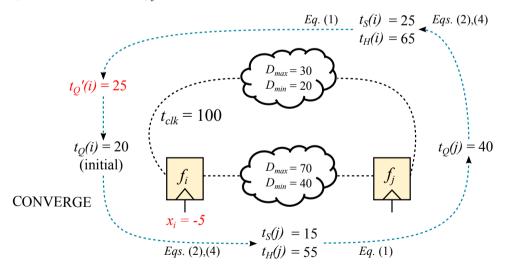

| Figure 3.7  | Clock skew scheduling integrated with flexible flip-flop timing.              |    |

|             | Tuning the clock arrival time at $f_i$ to $-5$ causes to update the           |    |

|             | setup and hold skews, and clk-to-Q delays of flip-flops in the                |    |

|             | circuit, resulting in all nonnegative value of setup and hold                 |    |

|             | slacks, indicating no time violation in the circuit                           | 44 |

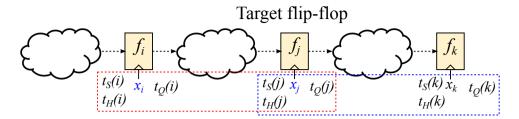

| Figure 3.8  | A partial circuit structure with three flip-flops $f_i$ , $f_j$ , and $f_k$ , |    |

|             | in which CSS-FT wants to improve the worst slack time at $f_j$                |    |

|             | by rescheduling clock arrival time $x_i$ at $f_i$ or $x_j$ at $f_j$ while     |    |

|             | satisfying the three constraints in Step 2                                    | 48 |

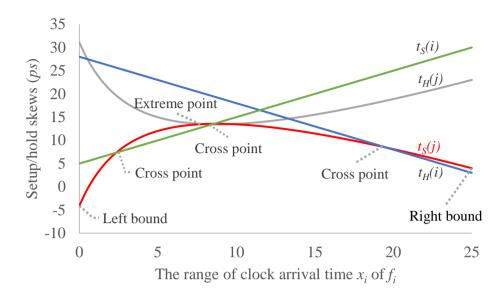

| Figure 3.9  | Illustration of curves, derived by Case 1 in Step 2 of CSS-                   |    |

|             | FT, of the setup and hold skews $(t_S(i), t_H(i), t_S(j), t_H(j))$ at         |    |

|             | flip-flops $f_i$ and $f_j$ in Fig. 3.8 with respect to $x_i$                  | 49 |

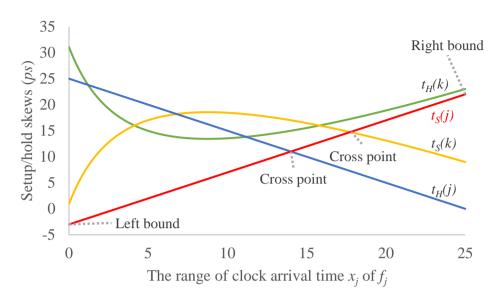

| Figure 3.10 | Illustration of curves, derived by Case 2 in Step 2 of ${\sf CSS\text{-}FT},$ |    |

|             | of the setup and hold skews $(t_S(j), t_H(j), t_S(k), t_H(k))$ at             |    |

|             | flip-flops $f_j$ and $f_k$ in Fig. 3.8 with respect to $x_j$                  | 50 |

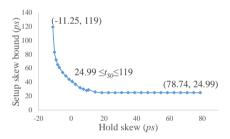

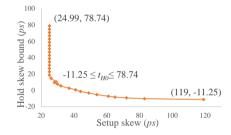

| Figure 3.11 | (a) Curve showing the change of the setup skew lower bound                      |    |

|-------------|---------------------------------------------------------------------------------|----|

|             | $(t_{S_0})$ as the hold skew changes. $(t_{S_0}$ for a value of hold skew       |    |

|             | is used for calculating the setup slack in $Eq$ (3.3)). (b) Curve               |    |

|             | showing the change of the hold skew lower bound $(t_{H_0})$ as the              |    |

|             | setup skew changes. ( $t_{H_0}$ for a value of setup skew is used for           |    |

|             | calculating the hold slack in $Eq$ (3.5))                                       | 51 |

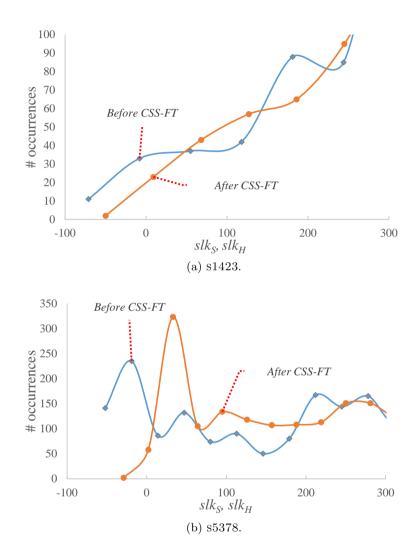

| Figure 3.12 | The distribution of the numbers of setup and hold slacks of                     |    |

|             | all flip-flops for designs $\$1423$ and $\$5378$ before (blue curve)            |    |

|             | and after (orange curve) the application of CSS-FT to the                       |    |

|             | initial timing analysis results produced by the flexible flip-                  |    |

|             | flop timing based STA in [37]. $T_{clk}$ is set to $T_{clk0} \times 0.95$ in    |    |

|             | Table 3.1                                                                       | 55 |

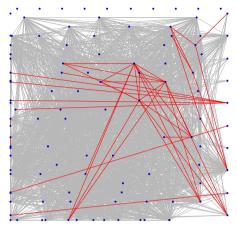

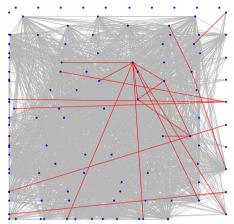

| Figure 3.13 | The distribution of time violations before and after the appli-                 |    |

|             | cation of CSS-FT to the timing results of $\pm 1423$ and $\pm 5378$             |    |

|             | produced by the STA in [37]. The blue dots indicate flip-flops.                 | 58 |

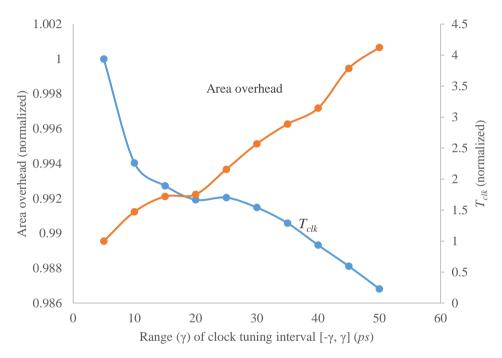

| Figure 3.14 | The curves showing the trade-off between the minimum clock                      |    |

|             | period and the area overhead required for clock skew reschedul-                 |    |

|             | ing used by CSS-FT where the data are extracted and aver-                       |    |

|             | aged over the results of ISCAS89 circuits                                       | 59 |

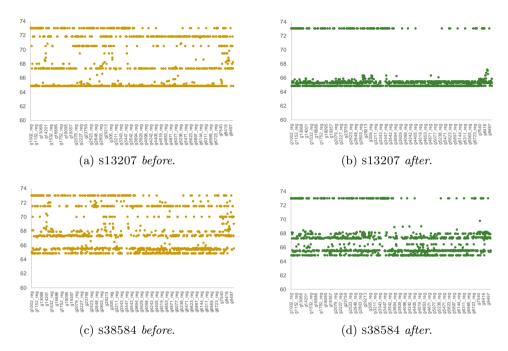

| Figure 3.15 | The distributions of clk-to-Q delays of all flip-flops for designs              |    |

|             | ${\bf s}13207$ and ${\bf s}38584$ before (yellow points) and after (green       |    |

|             | points) the application of ${\sf CSS\text{-}FT}$ to the initial timing analysis |    |

|             | results produced by the flexible flip-flop timing based STA in                  |    |

|             | [37]. $T_{clk}$ is set to $T_{clk0}$ in Table 3.1. All the clk-to-Q delays of   |    |

|             | $\rm s13207~are~decreased$ and only 10 clk-to-Q delays are slightly             |    |

|             | increased in the results of s38584                                              | 60 |

| Figure 4.1 | Clock mesh synthesis given by $Synopsys\ IC\ Compiler\ [53].$          | 63 |

|------------|------------------------------------------------------------------------|----|

| Figure 4.2 | Comparison among clock spine and other two clock structures.           |    |

|            | Clock is transitted from clock source(red triangle) to every           |    |

|            | clock sinks. Compared to clock tree which has a single clock           |    |

|            | path for each clock source to sink, clock mesh and clock spine         |    |

|            | structure have multiple clock paths. Buffers in clock tree only        |    |

|            | drive their own isolated subtree but those in clock mesh and           |    |

|            | clock spine structure drive mesh grid or spine together                | 65 |

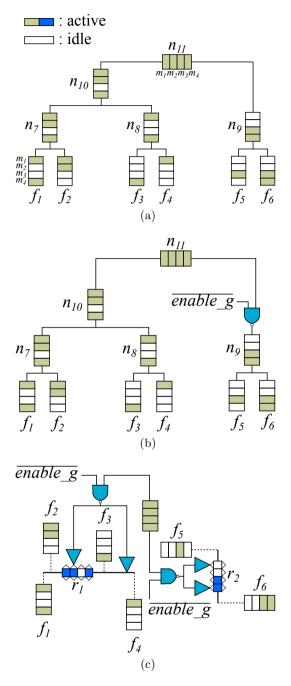

| Figure 4.3 | An example illustrating activity patterns and clock gating in          |    |

|            | clock tree and clock spine networks. (a) The generation of             |    |

|            | activity pattern by the bottom-up process, in a clock tree,            |    |

|            | from the activity patterns of sinks. (b) The clock tree gating         |    |

|            | at node $n_{10}$ in (a). (c) A clock spine network with two spines     |    |

|            | being gated separately                                                 | 66 |

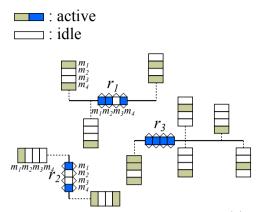

| Figure 4.4 | Comparison of the structure and energy consumption for three           |    |

|            | instances of clock spine network. (a) A clock spine network            |    |

|            | with $ R  = 3$ . (b) A clock spine network different from that         |    |

|            | in (a) and $ R =3$ , but less energy consumption. (d) A clock          |    |

|            | spine network different from that in (a), but $ R  = 5$ and less       |    |

|            | energy consumption                                                     | 69 |

| Figure 4.5 | Four steps of the proposed power-aware clock spine synthesis           |    |

|            | algorithm                                                              | 71 |

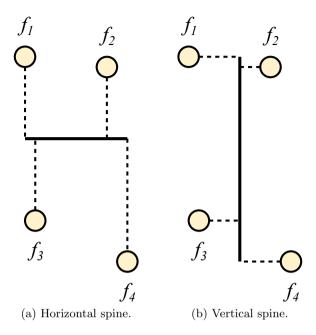

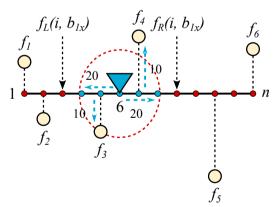

| Figure 4.6 | Spine allocation and placement for covering four sinks $f_1$ , $f_2$ , |    |

|            | $f_3, f_4$ . (a) Horizontal spine, (b) Vertical spine                  | 72 |

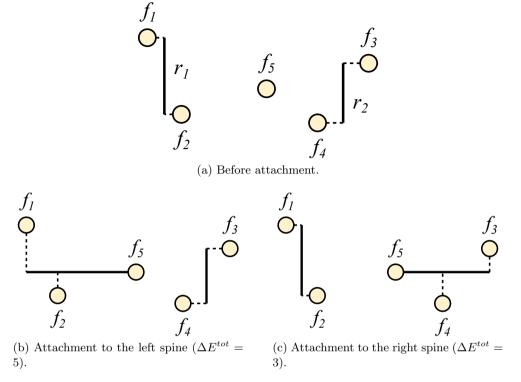

| Figure 4.7 | Two possible spines updated by attaching sink $f_5$ . (a) Before       |    |

|            | attachment. (b) Attachment to the left spine. (c) Attachment           |    |

|            | to right spine                                                         | 73 |

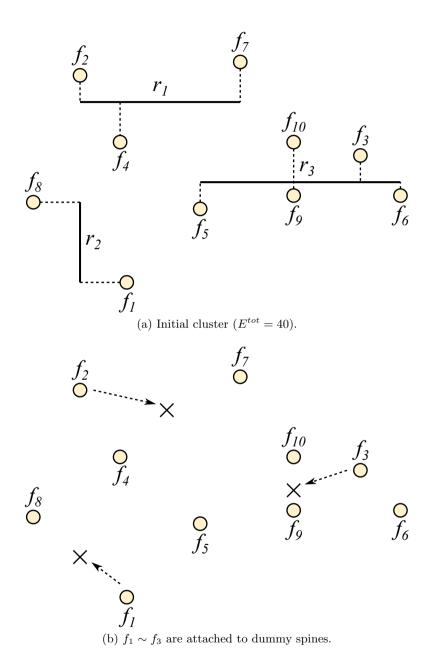

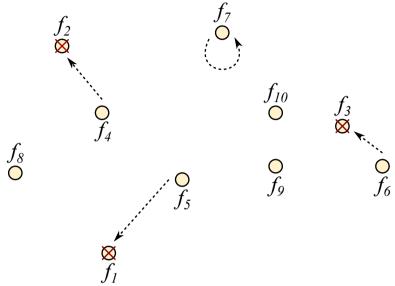

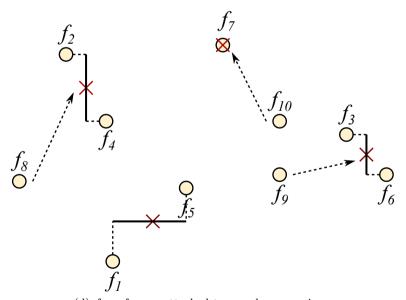

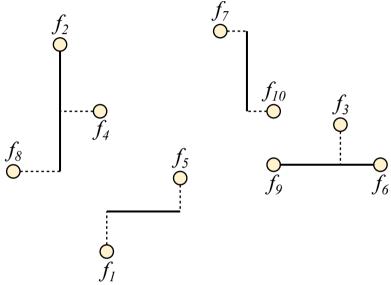

| Figure 4.8  | An example illustrating the step-by-step procedure of the                |    |

|-------------|--------------------------------------------------------------------------|----|

|             | inner-loop of sink clustering in CSPINE. (a) A spine network             |    |

|             | produced from the prior $outer$ -loop. (b) Generation of a $dummy$       |    |

|             | spine for each sink. (c) From the first four iterations, $f_4$ , $f_5$ , |    |

|             | and $f_6$ are respectively attached to the dummy spines of $f_2$ ,       |    |

|             | $f_1$ , and $f_3$ to form non-dummy spines while $f_7$ still main-       |    |

|             | tains a dummy spine. (d) From the next three iterations, $f_8$ ,         |    |

|             | $f_9$ , and $f_{10}$ are attached to non-dummy spines. (e) The final     |    |

|             | clock spine network                                                      | 76 |

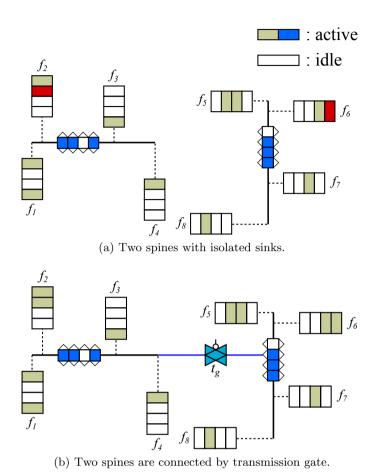

| Figure 4.9  | Example illustrating the concept of isolated sink. (a) A spine           |    |

|             | with four sinks with activation patterns. (b) The sinks to be            |    |

|             | enabled in power mode $m_1$ . (c) The sinks to be enabled in             |    |

|             | power mode $m_2$ . $f_2$ is an isolated sink in $m_2$ of the spine in    |    |

|             | (a). The spine alone has no control to mitigate the clock skew           |    |

|             | related to $f_2$ . (d) The sinks to be enabled in power mode $m_3$ .     | 79 |

| Figure 4.10 | Example showing the spine structure relaxation for two spines            |    |

|             | to improve the clock skew variability by removing isolated               |    |

|             | sinks. (a) Before relaxation. (b) After relaxation by $temporally$       |    |

|             | connecting them. $t_q$ is a transmission gate                            | 81 |

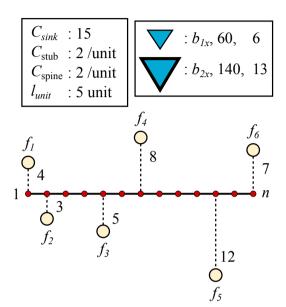

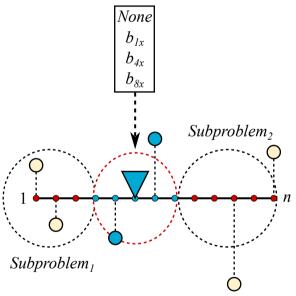

| Figure 4.11 | Example illustrating the application of dynamic programming                |

|-------------|----------------------------------------------------------------------------|

|             | for solving the problem of buffer allocation. (a) The specifica-           |

|             | tion of a spine with the unit-length capacitances of spine and             |

|             | stub, load capacitance of sinks, buffer library $\mathcal L$ and spine po- |

|             | sition candidates. (b) Allocation of buffer $b_{1x}$ to position 6,        |

|             | covering sub-spine $r[4,8]$ . (c) Allocation of buffer $b_{2x}$ to po-     |

|             | sition 6, covering a bigger sub-spine than that in (c). (d) An             |

|             | optimal allocation for the specification in (a). (e) An opti-              |

|             | mal allocation for the specification in (a) with more fine spine           |

|             | positions, producing a reduced cost of buffer allocation. (f)              |

|             | Decomposition of problem into two subproblems 84                           |

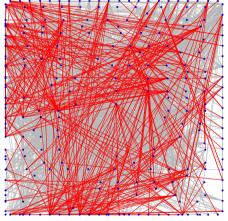

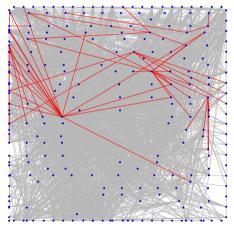

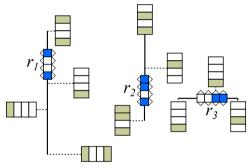

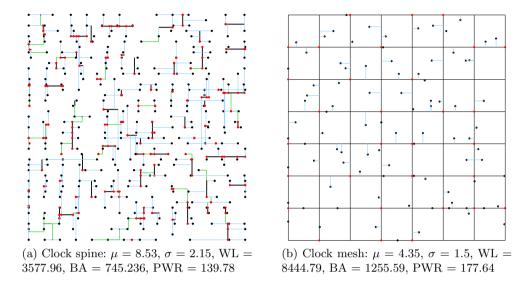

| Figure 4.12 | Comparison of clock spine and mesh structures of s13207. In                |

|             | (a) black dots, red dots, black lines, and green lines represent           |

|             | sinks, buffers, spines, and connection between spines. In (b)              |

|             | sky blue lines represent stubs                                             |

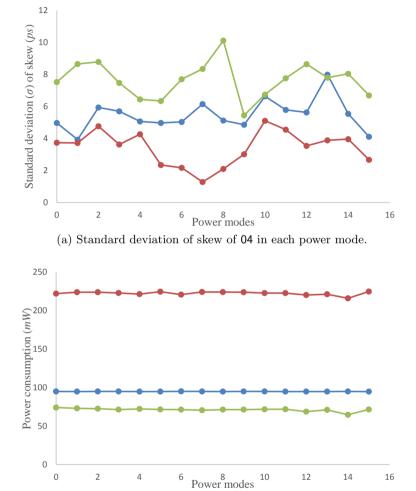

| Figure 4.13 | Comparison of clock tree, clock mesh, and clock spine struc-               |

|             | tures of circuit $04$ for all power modes. Green lines, blue lines,        |

|             | and red lines represent clock tree, clock mesh, and clock spine            |

|             | networks, respectively                                                     |

# List of Tables

| Table 1.1 | The characteristics of clock spine                              | 6  |  |  |  |

|-----------|-----------------------------------------------------------------|----|--|--|--|

| Table 2.1 | Comparison the accuracy of yield (Y) computation by Monte-      |    |  |  |  |

|           | Carlo simulation and PST-alloc. $(Y(PST-alloc) - Y(MC))$        | 29 |  |  |  |

| Table 2.2 | Comparison of results by [12] and our PST-alloc                 | 30 |  |  |  |

| Table 2.3 | Comparison of the number of PST buffers by [12] and our PST-    |    |  |  |  |

|           | alloc (Top-down)                                                | 31 |  |  |  |

| Table 3.1 | Comparison of the numbers of setup and hold time violations,    |    |  |  |  |

|           | for various values of clock period, before and after the appli- |    |  |  |  |

|           | cation of our CSS-FT starting from as input the timing analy-   |    |  |  |  |

|           | sis results produced by the flexible flip-flop timing based STA |    |  |  |  |

|           | in [37]. Clock skew tunable range of each flip-flop is set to   |    |  |  |  |

|           | [-30ps, 30ps].                                                  | 53 |  |  |  |

| Table 3.2 | Minimum clock period before and after the application of our    |    |  |  |  |

|           | CSS-FT. Clock skew tunable range of each flip-flop is set to    |    |  |  |  |

|           | [-30ps, 30ps].                                                  | 54 |  |  |  |

| Table 3.3 | Running time and overhead of our CSS-FT                         | 56 |  |  |  |

| Table 4.1 | Comparison of the clock skew variability $(\mu, \sigma)$ , wire<br>length and |    |

|-----------|-------------------------------------------------------------------------------|----|

|           | buffer area (WL, BA), and power consumption (PWR) of the                      |    |

|           | clock trees with clock gating by [59], the clock mesh by [58]                 |    |

|           | and a subsequent application of clock gating, and clock spines                |    |

|           | by CSPINE                                                                     | 88 |

| Table 4.2 | Comparison of the clock skew variability $(\mu, \sigma)$ , wire<br>length and |    |

|           | buffer area (WL, BA), and power consumption (PWR) of the                      |    |

|           | clock trees with clock gating by [59] when its slew rate con-                 |    |

|           | straints are changed                                                          | 90 |

| Table 4.3 | Comparison of the clock skew variability $(\mu, \sigma)$ , wire<br>length and |    |

|           | buffer area (WL, BA), and power consumption (PWR) of the                      |    |

|           | clock spines by CSPINE                                                        | 91 |

| Table 4.4 | The analyzed characteristics of clock spine.                                  | 92 |

## Chapter 1

## INTRODUCTION

#### 1.1 Clock Distribution Network

In a synchronous digital system, clock distribution network delivers a clock signal to clock sinks (i.e., flip-flops and latches). The signal should be arrived at all sinks at the same time. The objectives for clock network design is making the difference among clock latencies called *(global) clock skew* as zero, and it is very difficult task. Due to the effect of the increased variation caused by the CMOS process technology scaling down to sub-100nm, controlling clock skew became more challenging problem in electronic design automation (EDA).

In addition to the problem of increasing the performance of clock distribution networks, the power consumption of clock network should be carefully considered. According to the works of [1, 2], clock distribution network accounts for up to 40% of the total power. Increased requirements for designing robust clock network makes the power problem worse.

Traditional clock tree has been used for a long time for its simple structure.

However, increased variations produce uncertainties and the clock tree could not handle the problem at all. Clock mesh is proposed as an alternatives of clock tree. The structure gives multiple clock paths to clock sinks. Signals transitted to sinks are overlapped, thus the variation is decreased. However, multiple clock paths accompanies large cost, various researches to minimize the overhead have been studied.

#### 1.2 Process Variation

The effect of process variation is one of the most important factors to be considered in the clock tree synthesis. As CMOS scaling down to sub-100nm, clock skew is regarded as an unpredictable value. Process variations to channel length/width, oxide thickness, threshold voltage, and wire width/thickness affect the delay variation of interconnect and it produces maximally 25% clock skew variation [3].

Traditionally, the worst-case timing analysis is used to consider the delay variation caused by the process variation. However, as the delay variation increases, the timing margin given by designer based on the analysis occupies a significant portion of clock timing, causing to degrade circuit performance. To cope with the worst-case timing analysis, the statistical static timing analysis (SSTA) has been developed.

While some researchers (e.g., [4, 5, 6]) focus on SSTA to analyze the effect of process variation, other researchers have tried to control and reduce design margin due to the process variation. One of the noticeable solutions is using Post-Silicon Tunable (PST) clock buffers [7]. A PST buffer is used to adjust clock signal delay after manufacturing. The details of PST buffer are going to be introduced in the Chapter 2.

### 1.3 Flexible Flip-flop Timing Model

Static Timing Analysis (STA) analyzes the timing paths of sequential circuit based on flip-flop timing parameters, which are composed of setup time and hold time, and clk-to-Q delay (delay from the clock signal to the output Q of flip-flop). The traditional STAs specify setup and hold time as lower bounds of setup and hold skews, to be satisfied to assure stable data propagation passing through flip-flops. Most STAs have used a particular pair of setup and hold times that produces a clk-to-Q delay as the lower bounds to facilitate the easy computation of timing analysis, even though there are many pairs of setup and hold time values for a clk-to-Q delay. To accurately analyze the timing of circuits, full understanding and exploitation of the inter-dependent relation of setup time, hold time, and clk-to-Q delay are required. In Chapter 3, the concept of flexible flip-flop timing parameters is introduced and clock skew optimization algorithm that exploits the new timing model is proposed.

### 1.4 Clock Spine

The role of clock distribution network is to deliver a clock signal from clock source to the clock sinks in a synchronous digital system. Due to the high complexity in clock distribution networks under the various variations in design and process parameters, the latencies of the clock paths to sinks become large in difference as the delay variation increases. The maximum imbalance among the clock latencies is referred to as (global) clock skew and it causes harmful effects on high performance digital systems. In general, the increase of clock skew degrades the clock speed of circuits, eventually failing circuit functions. Thus, it is very important for the circuit designers to reduce the clock skew or maintain the clock skew in a certain bound in synthesizing clock networks.

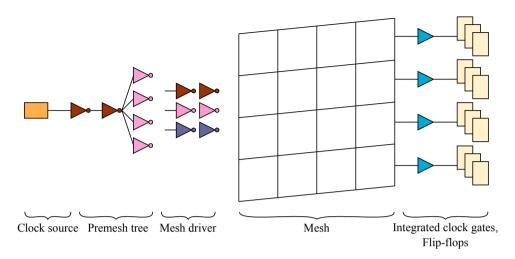

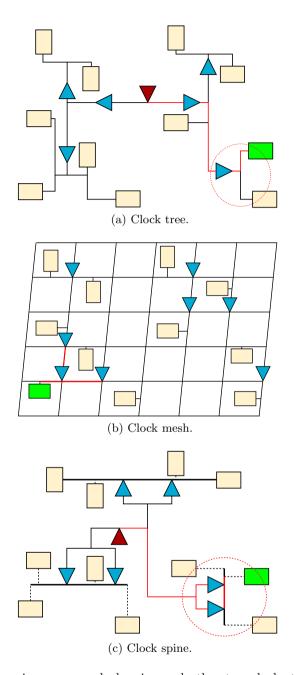

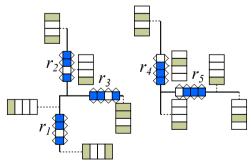

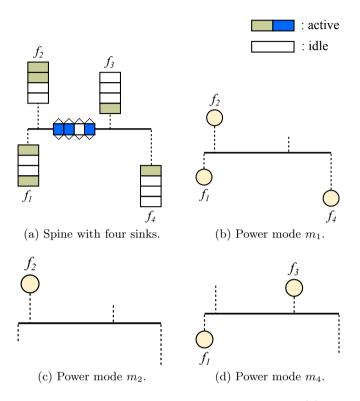

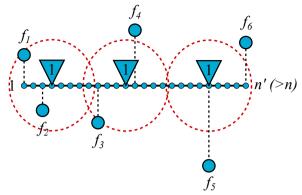

With the aim of mitigating the effect of the increased variation caused by the CMOS process technology scaling down to sub-100nm on the clock skew, designers and researchers have analyzed the structures of existing clock networks and attempted to explore alternative structures. Clock tree has been the most widely used clock network for its simplicity of the structure. Fig. 1.1(a) shows an example of the structure of clock tree where the yellow squares and blue triangles represent sinks and clock buffers, respectively. Since every clock sink receives the clock signal from the clock source through exactly one clock path, the delay variation on the clock wire and buffers in the clock path directly induces the variation of the clock arrival time at the sink, resulting in a high variability of clock skew. One extreme structure as opposed to that of clock tree to mitigate the variability is clock mesh, whose example of structure is shown in Fig. 1.1(b), since it allows multiple clock paths to a sink through the mesh grid [8].

Though the clock mesh has a high variation tolerance, its power consumption is a big obstacle. On the other hand, clock tree with cross links, shown in Fig. 1.1(c), offers reasonable solution that compromises power consumption with clock skew variation by inserting cross links to proper points in the clock tree [9]. Since the placement locations in the clock tree where links are added greatly influence the degree of clock skew variation, most existing works have looked for finding a minimal number of clock locations at which the links (dotted lines in Fig. 1.1(c)) are inserted to satisfy the constraint of clock skew variation. Besides clock tree with links, clock spine, shown in Fig. 1.1(d), is another compromising solution [10], but the structure is completely different from clock tree with links. The clock spine network contains a set of vertical and horizontal clock wires (heavy lines in Fig. 1.1(d)), which we call *spines* and every sink is attached to the spine in the closest distance. Since each spine

Figure 1.1: Two extreme structures of clock networks in (a) and (b) and intermediate structures in (c) and (d) with terms of the clock skew variability and power dissipation.

will have more than one clock buffer to drive the sinks attached in spine, (blue triangles in Fig. 1.1(d)), each sink can have multiple clock signal paths from the clock source. Unlike the clock tree with cross links, no work has investigated a systematic exploration of clock spine structures as yet. In Chapter 4, we develop a methodology to automate the exploration and synthesis of clock spine networks and fill the blanks in the Table. 1.1.

Table 1.1: The characteristics of clock spine.

|             | Clock tree | Cross links | Clock spine | Clock mesh |

|-------------|------------|-------------|-------------|------------|

| Performance | Low        | Medium      |             | High       |

| Cost        | Low        | Medium      | ?           | High       |

| Analysis    | Simple     | Less simple |             | Complex    |

#### 1.5 Contributions of This Dissertation

In this dissertation, each chapter presents algorithms and optimization techniques for solving the problems of clock network which relate to clock skew. At first, PST buffer allocation algorithm are developed in Chapter 2. To predict the efficiency of PST buffer in the design time, a graph-based yield computation technique is implemented in the algorithm. In Chapter 3, clock skew optimization with flexible flip-flop timing model is developed. Flexible timing model is integrated in the clock skew scheduling to resolve the timing violation. Finally, clock spine structure that is able to fix the skew problems in the early stage of design flow is presented in Chapter 4. The contributions of this dissertation are summarized as follows:

- Chapter 2 proposes a comprehensive graph-based PST buffer allocation algorithm. The algorithm includes (1) a graph-based chip yield computation technique for incremental PST buffer allocations and a systematic PST buffer allocation algorithm that is able to explore more extended design space of PST buffer allocation to minimize the number of allocated PST buffers.

- Chapter analyzes flexible flip-flop timing that describes the relation of setup time, hold time, and clk-to-Q delay. In addition, a new problem of

clock skew optimization integrated with flexible filp-flop timing is addressed and a step-by-step localized slack time relaxation is developed for a solution to the problem.

• Chapter4 addresses the problem of power-aware clock spine synthesis. In the chapter, four synthesis steps, in which the key task is to identify and group the flip-flops with tight correlation of clock-gating operations together to form a spine while accurately predicting and maintaining clock skew and slew variations through the buffer insertion and stub allocation

## Chapter 2

# POST-SILICON TUNABLE CLOCK BUFFER ALLOCATION BASED ON FAST CHIP YIELD COMPUTATION

#### 2.1 Introduction

The structure of a PST buffer is shown in Fig. 2.1 in which the delay is adjusted by the capacitors, each of which is controlled i.e., switch-on or switch-off by the control logic after manufacturing. The delay adjustment will be done through the TAP port. Since at the post-silicon stage, all process variations already affect the circuit, PST buffers can help fix the timing violations in the circuit, resulting in enhancing the chip yield. Tsai et al. [12] proposed a pre-silicon clock scheduling and a post-silicon PST buffer allocation in which they identified the 'timing critical' flip-flops and allocated PST buffers at the frond of the flip-flops. The determination of timing critical flip-flops is based on a certain threshold value given by designer. Subsequently, Tsai et al. [13] addressed two

Figure 2.1: The structure of PST buffer. The delay from *Input* to *Output* is adjusted by the delay control register which selectively switches the transistors according to the information from the TAP point. [11]

problems: one is the problem is to minimize the total tunable delay range of PST buffers to be allocated under the target yield constraint, and the other problem to minimize the number of PST buffers to be allocated under the target yield constraint. The PST buffer allocation of their algorithm was performed according to the slack values of flip-flops, and the yields are calculated by the Monte-Carlo simulation. On the other hand, Khandelwal and Srivastava [14] combined gate sizing into PST buffer placement algorithm for a fixed number of PST buffers produced by the algorithm in [13]. The integrated algorithm used Monte-Carlo simulation to compute the yields. Nagaraj and Kundu [15] also studied PST buffer placement problem for a given number of PST buffers.

There are two critical limitations of the previous PST allocation methods [12, 13, 14, 15], which are the use of slow Monte-Carlo simulation in computing the chip yield and a limited design space exploration of PST buffer allocation. This chapter overcomes the two limitations in the PST buffer allocation. Precisely, (1) we develop a graph-based chip yield computation technique which is

Figure 2.2: The relation between the number of PST buffers allocated and the resulting total PST area.

able to compute yields very efficiently and accurately for incremental PST buffer allocations, and based on the technique, (2) we propose a systematic (bottom-up and top-down) PST buffer allocation algorithm that is able to fully explore the design space of allocation to minimize the number of PST buffers. We have confirmed through experiments that our proposed algorithm drastically increasing chip yield while allocating limited number of PST buffers.

### 2.2 Systematic Exploration of PST Buffer Allocation

#### 2.2.1 Observations

Due to the large area overhead of PST buffers, the use of PST buffers should be constrained. The area overhead of PST buffers is composed of two parts. One is the tunable range of PST buffers, the other is the number of PST buffers. For simplicity, we assume that all the PST buffers have the same the tunable

range. On the other hand, one of the previous research works has clarified the relationship between the area overhead and the number of PST buffers. The work by Kim et al. [16] provides dot curves in Fig. 2.2 that show the relation between the number of PST buffers and the total PST buffers area, produced by applying the PST buffer allocation algorithms proposed in the previous works [17, 18, 19]. The curves show that the total PST buffer area is highly correlated with the number of PST buffers allocated, implying that minimizing the number of PST buffers to be allocated consistently leads to the least total area of PST buffers.

A simplest way to find a minimal allocation of PST buffers is to enumerate all the combinations of assigning PST buffers to the nodes in the clock tree, run the Monte-Carlo simulation or SSTA to each of the allocations to estimate the timing yield, and select the allocation which uses the least number of PST buffers while meeting the yield constraint. However, this leads to an extraordinarily long computation time, which is unacceptable in practice. Thus, it is needed to employ a clever mechanism of exploring the space of PST buffer allocations. Some analyses on the three cases of PST buffer allocation illustrated in Fig. 2.3 may incite how an ideal exploration of PST buffer allocations could be looked like.

• Converting an overlapping allocation into a non-overlapping one: The clock tree in Fig. 2.3(a) has five PST buffers  $b_1$ ,  $b_2$ , and  $b_3$ ,  $b_4$ , and  $b_5$  by which the clock arrival times to flip-flops  $f_1$  and  $f_2$ ,  $f_3$  and  $f_4$ , and  $f_5$  and  $f_6$  are respectively tuned by  $b_1$ ,  $b_2$ , and  $b_3$ . However, the time to  $f_8$  is tuned by  $b_5$  and the time to  $f_7$  is tuned by both  $f_4$  and  $f_5$ , which is then translated into an independent delay control to  $f_7$  and  $f_8$ . That is, the PST buffer allocation instance in Fig. 2.3(a) can be translated into that in Fig. 2.3(c), still using five PST buffers. This equivalence, in terms of the number of PST buffers allocated

Figure 2.3: Classification of PST buffer allocations: (a) overlapping PST buffer allocation; (b) redundant PST buffer allocation; (c) non-overlapping and non-redundant PST buffer allocation of (a) and (b); (d) a possibly better overlapping PST allocation than (c).

(d) Possible allocation superior to (c).

and the delay control capability, of the two PST buffer allocation instances in Figs. 2.3(a) and (c) implies that we are able to safely exclude one of them from our consideration of allocation space exploration.

**Definition 2.1**: (**PST depth**) *PST depth*,  $\rho(p_i)$ , of a signal path from clock source to flip-flop  $f_i$  of an *PST* allocation instance I in a clock tree is defined to the number of *PST* buffers on  $p_i$  and  $\rho(I) = \max\{\rho(p_i)|p_i \in P(I)\}$  where P(I) is the set of all clock signal paths in I.

**Definition 2.2**: (Overlapping PST allocation) An instance, I, of PST buffer allocation in a clock tree  $\mathcal{T}$  is said to be an overlapping PST allocation if  $\rho(I) \geq 2$ .

For example, for the instance of PST buffer allocation in Fig. 2.3(a), all  $\rho(p_i) = 1, i = 1, \dots, 8$  except  $\rho(p_7) = 2$ . Thus,  $\rho(I) = 2$  and it is an overlapping PST allocation, whereas for the instance of PST buffer allocation in Fig. 2.3(c), its  $\rho(I) = 1$  and it is not an overlapping PST allocation.

• Converting a redundant allocation into a non-redundant one: The clock tree in Fig. 2.3(b) has six PST buffers  $b_1, \dots, b_6$ , in which  $b_5$  controls the clock arrival times to both of  $f_7$  and  $f_8$ . Since the times to  $f_7$  and  $f_8$  also controlled independently by  $b_4$  and  $b_6$ , respectively, the allocation of  $b_5$  is redundant. Thus, the PST buffer allocation in Fig. 2.3(b) can be translated to that in Fig. 2.3(c) by removing  $b_6$ , suggesting that the PST buffer allocation instances with redundant PST buffer can be disregarded in the allocation space exploration.

**Definition 2.3**: (Redundant PST allocation) An instance, I, of PST buffer allocation in a clock tree  $\mathcal{T}$  is said to be a redundant PST allocation if it is an overlapping PST allocation and there exists a PST buffer in the allocation such that its removal from I does not cause to degrade the yield.

From the two examples of (overlapping and redundant) PST buffer allocation instances, it is obvious that the allocations that are meaningful to explore are

those that include non-overlapping and non-redundant ones like that shown in Fig. 2.3(c) whose PST depth  $\rho(I) \leq 1$ .

#### 2.2.2 Problem Definition

The PST buffer allocation problem can be formally described as:

**Problem 2.1** (**PST** buffer allocation) For a given buffered clock tree  $\mathcal{T}$ , statistical timing distributions between sinks (i.e., flip-flops) on  $\mathcal{T}$ , and timing yield constraint  $\Upsilon$ , minimize the number of PST buffers to be allocated to replace some of the normal buffers in  $\mathcal{T}$  so that the yield constraint  $\Upsilon$  is met.

Based on the observations, we narrow down the exploration space of Problem 2.1 by proposing to solve Problem 2.2:

**Problem 2.2** (**PST** buffer allocation with  $\rho(I) = 1$ ) Solve Problem 2.1 with the additional constraint that the allocation instance, I, should satisfy PST depth  $\rho(I) = 1^1$

Note that since an optimal allocation for Problem 2.1 does not always mean an optimal allocation for Problem 2.2, solving Problem 2.2 may leads to a sub-optimal allocation for Problem 2.1. For example, the allocation in Fig. 2.3(d) could be an optimal solution for Problem 2.1 while the allocation in Fig. 2.3(b) could be an optimal solution for Problem 2.2. However, the merits of tackling Problem 2.2 is that (1) the allocation exploration space can be greatly reduced by effectively uncovering (many unnecessary) overlapping and redundant allocations; (2) the constraint of allocations with  $\rho(I) = 1$  leads to a graph-theoretic formalization (e.g., Lemma 2.1) that facilitates the ease of statistical timing yield computation.

$<sup>^{1}\</sup>rho(I)=0$  refers to the allocation instance with only one PST buffer, allocating at the root of clock tree, thus  $(\rho(I)=1)$ . But, the PST buffer can be safely removed to be  $\rho(I)=0$ .

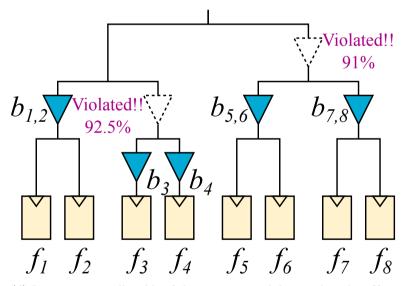

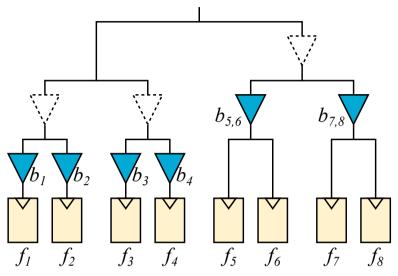

#### 2.2.3 Allocation Algorithm

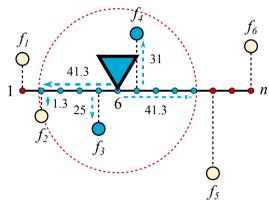

Our proposed exploration of PST buffer allocations are performed in two directions: bottom-up and top-down, followed by a refinement. Fig. 2.4 illustrates how the bottom-up exploration is carried out: Initially, we allocate a distinct PST buffer at the front of each sink as shown in Fig. 2.4(a). Thus, timing yield for this initial allocation will be the highest. Suppose yield constraint  $\Upsilon = 93\%$ . Then, we compute the yield for each of the reallocations resulting from merging the PST buffers in the siblings into one. For example, in Fig. 2.4(a) merging PST buffers  $b_1$  and  $b_2$  into  $b_{1,2}$ , merging  $b_3$  and  $b_4$  into  $b_{3,4}$ , merging  $b_5$  and  $b_6$  into  $b_{5,6}$ , and merging  $b_7$  and  $b_8$  into  $b_{7,8}$ , produce yields of 98%, 92.5%, 97%, and 96%, respectively. In the second iteration, we select the one with the highest yield, which is  $b_{1,2}$  among the merging candidates as indicated in Fig. 2.4(b). Then, the yields of the remaining merging candidates are recomputed. In the third iteration, according to the yields computed,  $b_{5,6}$  is selected as shown in Fig. 2.4(c). We repeat this process as long as there is a merging candidate whose yield is no less than  $\Upsilon$ . Figs. 2.4(d) show the mergings in the last iterations, in which all of merging into  $b_{7,8}$  and merging into  $b_{5,6,7,8}$  violate yield constraint  $\Upsilon$ . Thus, our bottom-up exploration allocates 5 PST buffers as shown in Figs. 2.4(d). In the subsequent refinement step, we attempt to remove each PST buffer and compute the resulting yield. Then, we eliminate the PST buffer which has the highest yield while the yield constraint is still satisfied. We repeat this removal until the yield constraint does not met.

Our top-down exploration is exactly towards the reverse direction of the bottom-up, replicating a PST buffer in parent node and moving them down to its children nodes. Thus, the final PST allocation we choose is the one with the less number of PST buffers between the two allocation results produced by the

bottom-up and top-down explorations.

### 2.3 Fast Timing Yield Computation

#### 2.3.1 Preliminaries

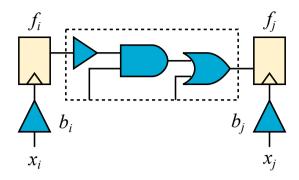

A portion of input circuit with PST buffers for timing analysis is depicted in Fig. 2.5 where the two PST buffers adjust the arrival times of clock signal to flip-flops in the post-silicon stage so that the (setup and hold) time constraints imposed in the circuits should be met. For simplicity, here, only the setup time constraint is reviewed. (The hold time constraint can be similarly explained.) If we assume that the clock signals arrive at  $f_i$  and  $f_j$  in Fig. 2.5 in the reference time of zero, only the delay values of PST buffers  $b_i$  and  $b_j$  determine the clock arrival times. To guarantee the setup time constraint at  $f_j$  from  $f_i$ , the clock period T of a circuit must satisfying the left inequality in the following expression:

$$x_i + D_{ij} \le T + x_j - s_j \Longleftrightarrow x_j - x_i \ge w_{ij} - T \tag{2.1}$$

where  $x_i$  and  $x_j$  are the delay of PST buffers  $b_i$  and  $b_j$ ,  $D_{ij}$  represents the maximum delay from  $f_i$  to  $f_j$ , T is the clock period, and  $s_j$  is the setup time of  $f_j$ . The inequality on the left side can be expressed into the one on the right side one by replacing  $D_{ij} + s_j$  with  $w_{ij}$ . The delay range  $r_i$  of a PST buffer,  $b_i$ , will be determined by circuit designer and can be expressed as:

$$-r_i \le x_i \le r_i \tag{2.2}$$

Since process variations affect  $D_{ij}$  and  $s_j$  values, these values are represented as statistical random variables. A circuit after manufacturing is considered working if there are values of  $x_i$  and  $x_j$  that satisfy Eq.(2.1) and Eq.(2.2). Then, the delay of PST buffers  $b_i$  and  $b_j$  are adjusted to  $x_i$  and  $x_j$ . To compute the

(a) First iteration: an initial PST buffer allocation followed by computing yield for each of mergings of sibling PST buffers.

(b) Second iteration: replacing PST buffers  $b_1$  and  $b_2$  in (a) with one PST buffer  $b_{1,2}$  followed by recomputation of yields of remaining merging candidates.

(c) Third iteration: replacing  $b_5$  and  $b_6$  in (b) with  $b_{5,6}$  followed by recomputation of yields of remaining merging candidates.

(d) Last iteration: all yields of the merging candidates is less than  $\Upsilon=93$ .

Figure 2.4: An example illustrating the bottom-up exploration of PST buffer allocation. A refinement step after the last iteration follows, which iteratively checks if some of the PST buffers can be removed while meeting the yield constraint.

Figure 2.5: A portion of circuit with PST buffers to adjust the time to trigger flip-flops  $f_i$  and  $f_j$ .

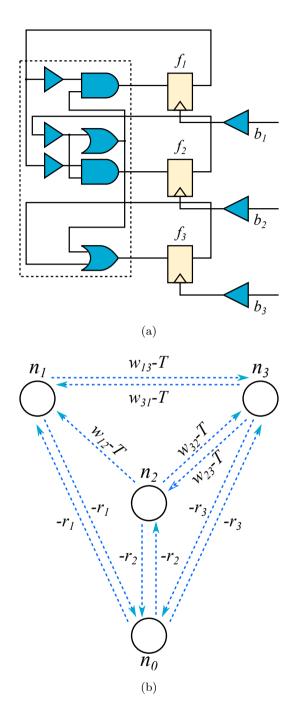

timing yield of circuit which refers to the percentage of chips that work for the clock period T, the previous work [20] builds a form of constraint graph [21] first. For example, Fig. 2.6(b) shows the constraint graph corresponding to the timing relations among three flip-flops  $f_1$ ,  $f_2$ , and  $f_3$  in Fig. 2.6(a). Nodes  $n_i$ , i = 1, 2, 3, in the constraint graph corresponds to PST buffers  $b_i$ , i=1,2,3, and the weight on the arc from  $n_i$  to  $n_j$ , i,j=1,2,3 and  $i\neq j$  is the right term in  $x_j - x_i \ge w_{ij} - T$  in Eq.(2.1). Node  $n_0$  is a dummy node to be used to incorporate the inequality in Eq.(2.2). The weights on the arcs from  $n_0$  to  $n_i$  and from  $n_i$  to  $n_0$ , i = 1, 2, 3, are the right terms in  $x_i \geq -r_i$ and  $-x_i \ge -r_i$  (=  $x_i \le r_i$ ), respectively. Then, the constraints that there are value assignments of  $x_i$ ,  $i = 1, 2, \dots$ , that satisfy the Eq.(2.1) and Eq.(2.2) is equivalent to the constraint that all the loops in the corresponding constraint graph are nonpositive. (The detailed proof of the equivalence can be found in [21].) To solve Problem 2.2 efficiently, we extend the idea of representing the constraints in Eq.(2.1) and Eq.(2.2) into a constraint graph for any PST allocation instance I with  $\rho(I) = 1$ .

**Lemma 2.1** Any PST allocation instance I with  $\rho(I) = 1$  can be represented into a constraint graph G(I) such that the following holds: there is a delay

Figure 2.6: Constraint graph representing the timing relation between flip-flops: (a) a portion of circuit instance, I, with the allocation of PST buffers  $b_1$ ,  $b_2$ , and  $b_3$  that are used to adjust clock arrival times to flip-flips  $f_1$ ,  $f_2$ , and  $f_3$ , respectively; (b) constraint graph G(I).

assignment to the PST buffers in I that satisfies Eq.(2.1) and Eq.(2.2) if and only if all the loops in G(I) are nonpositive. (We leave the proof out due to the space limitation.)

For convenience as does in [20], all arc weights in the constraint graph are replaced by the form of  $w_{ij} - k_{ij}T$  where for arcs connected to the dummy node  $w_{ij} = -r_i$  and  $k_{ij} = 0$ , and for others  $k_{ij} = 1$ . Finding a minimal clock period  $(T_{min})$  that meets the inequalities of Eq.(2.1) and Eq.(2.2) is equivalent to (Step 1) finding the value of  $T_l$  for every loop  $l \in L$  in the constraint graph such that

$$W_l = \sum_{i,j} (w_{ij} - k_{ij}T) \le 0 \Longleftrightarrow T \ge \sum_{ij} w_{ij} / \sum_{ij} k_{ij} = T_l$$

(2.3)

where L is the set of loops and  $W_l$  is the weight of loop  $l \in L$  in the constraint graph and (Step 2) compute  $T_{min}$ :

$$T_{min} = \max_{l \in L} T_l. \tag{2.4}$$

Then, yield Y of the circuit can be derived as:

$$Y = prob\{T_{min} \le T\}. \tag{2.5}$$

#### 2.3.2 Incremental Yield Computation

The most time consuming parts in computing yield for an instance, I, of PST buffer allocation is (1) the derivation of the distribution of random variable  $T_l$  in Eq.(2.3) for every loop l in G(I) and (2) the max operation on all the random variables  $T_{l_i}$ ,  $i = 1, \dots, |L|$  in Eq.(2.4) to produce the distribution of  $T_{min}$ , where L is the set of loops in G(I). However, in the framework of our bottom-up and top-down explorations of PST buffer allocations with PST depth  $\rho(\cdot) = 1$ , the yield computation time can be greatly reduced. In the following, we

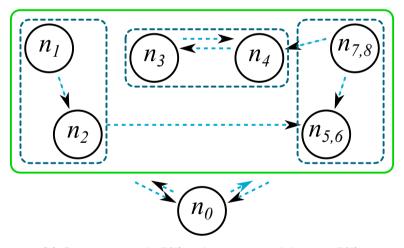

describe, using an illustrative example, our fast yield computation technique for the bottom-up allocation exploration case. (The yield computation strategy for the top-down case is almost identical to that of the bottom-up case.) Consider the allocation instance, I, in Fig. 2.7(a). Now, we want to find a merging which produces the highest value of Y in Eq.(2.5) among the merging candidates.

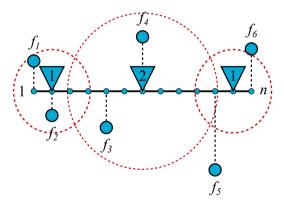

- (1) Derivation of  $T_l$  in Eq.(2.3): Fig. 2.7(b) shows the constraint graph G(I) of the allocation instance I in Fig. 2.7(a). There exists three merging candidates  $MG_1$ ,  $MG_2$ , and  $MG_3$  in G(I) that correspond to merging  $b_1$  and  $b_2$ , merging  $b_3$  and  $b_4$ , and merging  $b_{5,6}$  and  $b_{7,8}$  in I, respectively. In addition, all the loops in G(I) are listed in Fig. 2.7(c). Then, for trial of each merging candidate  $MG_j$ , we partition the set of loops L in G(I) in two subsets  $L_{reuse}$  and  $L_{recomp}$  such that

- $L_{reuse} = \{l_i | l_i \in L \text{ and no arcs between the nodes in } MG_j \text{ are in } l_i\}.$

- $L_{recomp} = \{l_i | l_i \in L \text{ and at least one arc between the nodes in } MG_j \text{ are in } l_i \}.$

Since  $T_{l_i}$  in Eq.(2.3) of every loop  $l_i \in L_{reuse}$  has already been computed in the previous iteration and trial of merging candidate  $MG_j$  does not change  $l_i$ , the value of  $T_{l_i}$  can be reused in computing  $T_{min}$  in Eq.(2.4) for the incremental reallocation by  $MG_j$ . Thus, only for each  $l_i \in L - L_{reuse} (= L_{recomp})$ ,  $T_{l_i}$  needs to be recomputed for the incremental reallocation by  $MG_j$ . Table R[-,-] in Fig. 2.7(d), which we call **Reuse table**, contains the reuse-ability information. For example, R[3,1] = 0 means that  $T_{l_3}$  of loop  $l_3$  can be reused for the incremental reallocation by  $MG_1$ , while R[4,2] = 1 means that  $T_{l_4}$  of loop  $l_4$  should be recomputed for the incremental reallocation by  $MG_2$ .

(2) Derivation of  $T_{min}$  in Eq.(2.4): Since  $T_{min}$  derived from random variables  $T_{l_1}, \dots, T_{l_{|L|}}$  entails repeated application of max operations, if we can keep some

of the results by max operations, they can be reused in the trials of merging candidates. To maximize the reuse, we exploit the information in the reuse table R. For example, in the reuse table in Fig. 2.8(a), since loops  $l_5$  and  $l_6$  has never been changed for any of the trial of merging candidates  $MG_1$ ,  $MG_2$ , and  $MG_3$ , the result of  $max\{T_{l_5}, T_{l_6}\}$  is stored to be reused for computing  $T_{min}$  in Eq.(2.4) of the incremental reallocation by any merging candidate. Once  $max\{T_{l_5}, T_{l_6}\}$ is computed and stored, the reuse table is updated by merging rows of  $l_5$ , and  $l_6$  into a row  $(l_5, l_6)$  and setting  $R[(l_5, l_6), j] = OR(R[l_5, MG_j], R[l_6, MG_j]),$ j = 1, 2, 3, as shown in Fig. 2.8(b). In the next iteration, select the two loops whose bitwise-OR operation to the reuse table leads to the smallest number of 1's. The less the number of 1's by the bitwise-OR of two rows  $l_i$  and  $l_j$  in R is, the more it is likely that trials of merging candidates can reuse the result of  $T_{(l_i,l_j)}$  (=  $max\{T_{l_i},T_{l_j}\}$ ). As a results, loops  $l_1$  and  $l_2$ , loops  $l_3$  and  $l_4$ , and then loops  $l_7$  and  $l_8$  are selected and performed  $max\{T_{l_i}, T_{l_j}\}$  operations as shown in the first row of table in Fig. 2.8(b). Then, in the next iterations, bitwise-OR operations to the pairs of rows in the reuse table produce the sequence of max operations:  $max\{T_{(l_3,l_4)},T_{(l_5,l_6)}\}$  in Fig. 2.8(c),  $max\{T_{(l_1,l_2)},T_{(l_3,l_4,l_5,l_6)}\}$  in Fig. 2.8(d), and  $max\{T_{(l_1,l_2,l_3,l_4,l_5,l_6)},T_{(l_7,l_8)}\}$  in Fig. 2.8(e).

# 2.4 Experimental Result

Our proposed PST buffer allocation algorithm called PST-alloc is implemented in Python3 and C++ and tested using 2.67 GHz linux machine. We used IS-CAS89 [22] and ITC99 [23] benchmark circuits for experiments. The devices in the benchmark circuits are mapped to Nangate 45nm technology library [24]. We use SSTA engine developed in [5] and supplemented in [20]. We compare the results produced by PST-alloc with that by the previous work in [12] as well

(a) An instance, I, of PST buffer allocation.

(b) Constraint graph G(I) and merging candidates in G(I).

| $n_0  ightarrow n_1  ightarrow n_2  ightarrow n_0$                        |

|---------------------------------------------------------------------------|

| $n_0 \rightarrow n_1 \rightarrow n_2 \rightarrow n_{5,6} \rightarrow n_0$ |

| $n_0  ightarrow n_2  ightarrow n_{5,6}  ightarrow n_0$                    |

| $n_0  ightarrow n_3  ightarrow n_4  ightarrow n_0$                        |

| $n_0  ightarrow n_4  ightarrow n_3  ightarrow n_0$                        |

| $n_0  ightarrow n_{7,8}  ightarrow n_4  ightarrow n_0$                    |

| $n_0  ightarrow n_{7,8}  ightarrow n_4  ightarrow n_3  ightarrow n_0$     |

| $n_0  ightarrow n_{7,8}  ightarrow n_{5,6}  ightarrow n_0$                |

|                                                                           |

|                   | $MG_1$ | MG <sub>2</sub> | <b>MG</b> <sub>3</sub> |

|-------------------|--------|-----------------|------------------------|

| Loop <sub>1</sub> | 1      | 0               | 0                      |

| Loop <sub>2</sub> | 1      | 0               | 0                      |

| Loop <sub>3</sub> | 0      | 1               | 0                      |

| Loop <sub>4</sub> | 0      | 1               | 0                      |

| Loop <sub>5</sub> | 0      | 0               | 0                      |

| Loop <sub>6</sub> | 0      | 0               | 0                      |

| Loop <sub>7</sub> | 0      | 1               | 0                      |

| Loop <sub>8</sub> | 0      | 0               | 1                      |

(c) Loops in G(I).

(d) Reuse table R for G(I).

Figure 2.7: Enumeration of all loops in an instance of PST buffer allocation and generation of reuse relation between loops and merging candidates: (a) an instance, I, of PST buffer allocation in a clock tree. Six PST buffers  $b_1, \dots b_4, b_{5,6}, b_{7,8}$  are allocated; (b) constraint graph G(I) and PST buffer merging candidates  $MG_1$ ,  $MG_2$ , and  $MG_3$  in G(I); (c) list L of loops in G(I); (d) reuse table R[-,-] to represent the  $T_l$  reuse relation between the loops and merging candidates.

as Monte-Carlo simulation in terms of run time the number of PST buffers, and the accuracy of yield computation.

- Checking the accuracy of yield computation: To assess the accuracy of our SSTA engine, we compared our SSTA results to compute yields during the exploration of PST allocations in PST-alloc with the results by Monte-Carlo simulations with 10,000 iterations. Table 2.1 summarizes the error rate between the values by our SSTA and by Monte-Calo simulation for two circuits s382 and s5378 in which MG[i],  $i=1,\cdots,10$ , in the first column of the table represents the allocation instance produced at the i-th iteration transforming from the initial PST allocation instance INIT. In summary, the error rate of yield is below 0.2% in the mean value and 2% in the standard deviation. It also should be noted that the speed of our SSTA is nearly zero while that of Monte-Carlo simulation is over 10,000 times slower.

- Comparing PST-alloc with previous work: We compare our results with that produced by the PST buffer allocation algorithm, which we called Tsai's, in [12]. Tsai's repeatedly find flip-flops with the smallest slack and place PST buffers at the front of the flip-flops. Although the slacks on flip-flops are computed by SSTA, the PST buffer allocations are set by a certain threshold given by designer. Furthermore, the yield computation is done by the slow Monte-Carlo simulation. (For accurate yield computation, all yield results are replaced by the result produced by [20].) Table 2.2 summarizes the results. The comparison shows that PST-alloc (Bottom-up) produces the higher yield than that by Tsai's while the same number of PST buffers are allocated. Similarly, PST-alloc (Top-down) increases chip yield. Due to the different directions of exploration and converging points, results of PST-alloc (Bottom-up) and PST-alloc (Top-down) for circuits s382, s15850, and s38584 produce different results. However, the number of PST buffers are different, the yield results of both approaches are

| loop                  | $MG_1$ | $MG_2$ | $MG_3$ |

|-----------------------|--------|--------|--------|

| $l_1$                 | 1      | 0      | 0      |

| $l_2$                 | 1      | 0      | 0      |

| $l_3$                 | 0      | 1      | 0      |

| $l_4$                 | 0      | 1      | 0      |

| $l_5$                 | 0      | 0      | 0      |

| $l_6$                 | 0      | 0      | 0      |

| $l_7$                 | 0      | 1      | 0      |

| <i>l</i> <sub>8</sub> | 0      | 0      | 1      |

| 1 | (a) | Initial | rougo | tabla | D     |

|---|-----|---------|-------|-------|-------|

| ( | (a) | шша     | reuse | table | $\Pi$ |

| loop                                   | $MG_1$ | $MG_2$ | $MG_3$ |

|----------------------------------------|--------|--------|--------|

| $(l_1, l_2)$                           | 1      | 0      | 0      |

| $(l_3, l_4)$                           | 0      | 1      | 0      |

| $(\boldsymbol{l_5}, \boldsymbol{l_6})$ | 0      | 0      | 0      |

| $(l_7, l_8)$                           | 0      | 1      | 1      |

(b) max for  $l_5$  and  $l_6$ , max for  $l_1$  and  $l_2$ , max for  $l_3$ , and  $l_4$ , max for  $l_7$  and  $l_8$

| loop                       | $MG_1$ | $MG_2$ | $MG_3$ |

|----------------------------|--------|--------|--------|

| $(l_1, l_2)$               | 1      | 0      | 0      |

| $((l_3, l_4), (l_5, l_6))$ | 0      | 1      | 0      |

| $(l_7, l_8)$               | 0      | 1      | 1      |

| ( | $(\mathbf{c})$ | max | for ( | $(l_3, l$ | 4) | and | l (1 | $l_5, l$ | 6 | ) |

|---|----------------|-----|-------|-----------|----|-----|------|----------|---|---|

|---|----------------|-----|-------|-----------|----|-----|------|----------|---|---|

| loop                                   | $MG_1$ | $MG_2$ | $MG_3$ |

|----------------------------------------|--------|--------|--------|

| $((l_1, l_2), (l_3, l_4), (l_5, l_6))$ | 1      | 1      | 0      |

| $(l_7, l_8)$                           | 0      | 1      | 1      |

(d) max for  $(l_1, l_2)$  and  $(l_3, \dots, l_6)$

| loop                                               | $MG_1$ | $MG_2$ | $MG_3$ |

|----------------------------------------------------|--------|--------|--------|

| $((l_1, l_2), (l_3, l_4), (l_5, l_6), (l_7, l_8))$ | 1      | 1      | 0      |

(e)

$$max$$

for  $(l_1, \dots, l_6)$  and  $(l_7, l_8)$

Figure 2.8: Generation of a sequence for max operations. Reusable partial max results for trials of merging candidates are: (a) initial result table R; (b)  $max\{T_{l_5}, T_{l_6}\}$  followed by  $max\{T_{l_1}, T_{l_2}\}$ ,  $max\{T_{l_3}, T_{l_4}\}$ , and  $max\{T_{l_7}, T_{l_8}\}$ ; (c)  $max\{T_{(l_3, l_4)}, T_{l_5}, T_{l_6}\}$  (=  $T_{(l_3, l_4, l_5, l_6)}$ ); (d)  $max\{T_{(l_1, l_2)}, T_{l_3, l_4, l_5, l_6}\}$  (=  $T_{(l_1, \dots, l_6)}$ ); (e)  $max\{T_{(l_1, \dots, l_6)}, T_{(l_7, l_8)}\}$  (=  $T_{l_1, \dots, l_8}$ ).

Table 2.1: Comparison the accuracy of yield (Y) computation by Monte-Carlo simulation and PST-alloc. (Y(PST-alloc) - Y(MC))

| Alloc. | s3     | 82       | s5378  |          |  |  |  |

|--------|--------|----------|--------|----------|--|--|--|

| Anoc.  | $\mu$  | $\sigma$ | $\mu$  | $\sigma$ |  |  |  |

| INIT   | 0.052% | 0.669%   | 0.051% | 1.163%   |  |  |  |

| MG[1]  | 0.029% | 0.151%   | 0.130% | 0.375%   |  |  |  |

| MG[2]  | 0.044% | 0.575%   | 0.008% | 0.958%   |  |  |  |

| MG[3]  | 0.117% | 0.214%   | 0.080% | 0.297%   |  |  |  |

| MG[4]  | 0.049% | 0.085%   | 0.059% | 0.555%   |  |  |  |

| MG[5]  | 0.152% | 0.399%   | 0.095% | 0.394%   |  |  |  |

| MG[6]  | 0.063% | 0.609%   | 0.065% | 0.391%   |  |  |  |

| MG[7]  | 0.012% | 1.712%   | 0.035% | 0.231%   |  |  |  |

| MG[8]  | 0.031% | 1.638%   | 0.001% | 0.451%   |  |  |  |

| MG[9]  | 0.015% | 0.205%   | 0.053% | 0.339%   |  |  |  |

| MG[10] | 0.059% | 0.158%   | 0.086% | 1.200%   |  |  |  |

the same. Due to the timing problems which are solved by PST buffers in PST-alloc (Bottom-up) dominate that by additional PST buffers in PST-alloc (Top-down), many PST buffers in design of PST-alloc (Top-down) are useless. Table 2.3 shows the number of PST buffers when [12] produces the similar level of chip yield to that of PST-alloc (Top-down). PST-alloc uses 26% less number of PST buffers than that by the previous works while maintaining the similar yield constraint. Note that the run time of PST-alloc (Bottom-up) is quite large, but much faster than that of Tsai's.

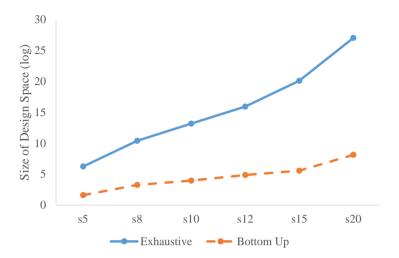

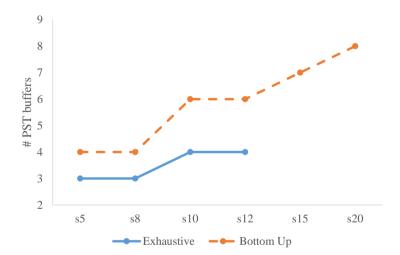

• Comparing PST-alloc with exhaustive enumeration: Figs. 2.9(a) and (b) show the comparison of the size of design space explored by the exhaustive search

Table 2.2: Comparison of results by [12] and our PST-alloc.

| G: :    | // DD   | T            | Tsa     | i's [12] |

|---------|---------|--------------|---------|----------|

| Circuit | # FF    | (ps)         | Yield   | # PST    |

| s386    | 20      | 503.193      | 0.97    | 4        |

| s382    | 30      | 574.799      | 0.927   | 6        |

| s1423   | 74      | 1354.41      | 0.942   | 9        |

| s5378   | 247     | 798.285      | 0.09    | 6        |

| s13207  | 482     | 836.713      | 0.905   | 6        |

| s15850  | 235     | 860.383      | 0.452   | 19       |

| s38584  | 1458    | 1396.93      | 0.829   | 33       |

| Circuit | Р       | ST-alloc (B  | ottom U | Jp)      |

| Circuit | # iter. | Time $(s)$   | Yield   | # PSTs   |

| s386    | 17      | 1.85         | 0.97    | 4        |

| s382    | 26      | 14           | 0.995   | 5        |

| s1423   | 103     | 1354.41      | 0.886   | 9        |

| s5378   | 242     | 6128.26      | 0.903   | 6        |

| s13207  | 477     | 1044.76      | 0.977   | 6        |

| s15850  | 229     | 53.14        | 0.918   | 7        |

| s38584  | 1444    | 6137.75      | 0.871   | 15       |

| Circuit | F       | PST-alloc (T | op Dow  | m)       |

| Circuit | # iter. | Time $(s)$   | Yield   | # PSTs   |

| s386    | 3       | 0.01         | 0.97    | 4        |

| s382    | 5       | 0.01         | 0.995   | 6        |

| s1423   | 8       | 3.66         | 0.886   | 9        |

| s5378   | 5       | 9.36         | 0.903   | 6        |

| s13207  | 5       | 5.81         | 0.977   | 6        |

| s15850  | 18      | 1.73         | 0.918   | 19       |

| s38584  | 32      | 1116.46      | 0.871   | 33       |

Table 2.3: Comparison of the number of PST buffers by [12] and our PST-alloc (Top-down).

| G: .1   | Tsai's [12] |       | PS    | T-alloc |        |

|---------|-------------|-------|-------|---------|--------|

| Circuit | (ps)        | Yield | # PST | Yield   | # PSTs |

| s386    | 503.193     | 0.97  | 4     | 0.970   | 4      |

| s382    | 574.799     | 0.994 | 7     | 0.995   | 5      |

| s1423   | 1354.41     | 0.942 | 9     | 0.886   | 9      |

| s5378   | 798.285     | 0.902 | 40    | 0.903   | 6      |

| s13207  | 836.713     | 0.905 | 6     | 0.977   | 6      |

| s15850  | 860.383     | 0.917 | 31    | 0.918   | 7      |

| s38584  | 1396.93     | 0.829 | 14    | 0.871   | 15     |

and our PST-alloc and the numbers of PST buffers allocated. We can see that the design space explored by PST-alloc is much smaller than the exhaustive one, but the numbers of PST buffers allocated by PST-alloc is closer to the optimal ones.

# 2.5 PST Buffer Configuration Techniques

This chapter proposed a PST buffer allocation algorithm to increase yield of the circuit. However, the timing problem of the circuit is able to be solved when the delay values of all PST buffers are configured after manufacturing process. Previous works have been tried to solve the problem by using measurements produced at post-silicon time. In this section, techniques which defined the PST buffer delay configuration problem and proposed an algorithm to solve it. [25] introduced Genetic Algorithm-based clock adjustement method to increase chip yield. The work assumed that all flip-flops have their own PST buffers. Other

reseachers proposed a technique to reduce the effect of process variation on the same environment [26]. The work found an unique tuning setting for each die to maximize performance. The problem of above two works is that the algorithms find solution for a single die, so they are quite expensive. In test process, a large number of chips should be tested and the number of applied tests is also big. AutoRex [27] pointed out scalability issues of the previous works and proposed the algorithm which finds a tuning setting based on information of a batch of chips. The algorithm used Satisfiability Modulo Theory (SMT) solvers to process large data and generate results. In addition, Lak and Nicolici [28] extended the algorithm of Tadesse et al. to consider hold time violation.

## 2.6 Summary

In this chapter, we proposed a comprehensive graph-based algorithm for PST buffer allocation to overcome the two critical limitations of the prior works, which are (1) the use of slow Monte-Carlo simulation in computing the chip yield and (2) a limited design space exploration of PST buffer allocation. Precisely, we develop a graph-based chip yield computation technique which is able to compute yields very efficiently and accurately for incremental PST buffer allocations, and based on the technique, we developed a systematic (bottom-up and top-down) PST buffer allocation algorithm that is able to fully explore the design space of allocation to minimize the number of PST buffers. The speed of proposed algorithm is much faster than the prior algorithms and it significantly improves yield while the same number of PST buffers are allocated.

(a) The design space explored by PST-alloc is much smaller than the exhaustive one