#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

#### Ph.D. Dissertation

# **Event-Driven Simulation Methodology for Analog/Mixed-Signal Systems**

혼성 신호 시스템을 위한 사건 구동 방식 모의 실험 방법

by

Ji Eun Jang

**August 2015**

School of Electrical Engineering and Computer Science College of Engineering Seoul National University

# **Event-Driven Simulation Methodology for Analog/Mixed-Signal Systems**

#### 지도 교수 김 재 하

이 논문을 공학박사 학위논문으로 제출함 2015 년 8 월

> 서울대학교 대학원 전기·컴퓨터공학부 장 지 은

장지은의 박사 학위논문을 인준함 2015 년 8 월

| 위 원 | ! 장 | (인) |

|-----|-----|-----|

| 부위  | 원장  | (인) |

| 위   | 원   | (인) |

| 위   | 원   | (인) |

| 위   | 원   | (인) |

ABSTRACT

### **Abstract**

Recent system-on-chip's (SoCs) are composed of tightly coupled analog and digital components. The resulting mixed-signal systems call for efficient system-level behavioral simulators for fast and systematic verifications. As the system-level verifications rely heavily on digital verification tools, it is desirable to build the mixed-signal simulator based on a digital simulator. However, the existing solutions in digital simulators suffer from a trade-off between simulation speed and accuracy. This work breaks down the trade-off and realizes a fast and accurate analog/mixed-signal behavior simulation in a digital simulator SystemVerilog.

The main difference of the proposed methodology from existing ones is its way of representing continuous-time signals. Specifically, a clock signal expresses accurate timing information by carrying an additional real-value time offset, and an analog signal represents its continuous-time waveform in a functional form by employing a set of coefficients. With these signal representations, the proposed method accurately simulates mixed-signal behaviors independently of a simulator's time-step and achieves a purely event-driven simulation without involving any numerical iteration.

The speed and accuracy of the proposed methodology are examined for various types of analog/mixed-signal systems. First, timing-sensitive circuits (a phase-locked loops and a clock and data recovery loop) and linear analog circuits (a channel and linear equalizers) are simulated in a high-speed I/O interface example. Second, a switched-linear-behavior simulation is demonstrated through switching

**ABSTRACT** II

power supplies, such as a boost converter and a switched-capacitor converter.

Additionally, the proposed method is applied to weakly nonlinear behaviors

modeled with a Volterra series for an RF power amplifier and a high-speed I/O

linear equalizer. Furthermore, the nonlinear behavior simulation is extended to three

different types of injection-locked oscillators exhibiting time-varying nonlinear

behaviors. The experimental results show that the proposed simulation methodology

achieved tens to hundreds of speed-ups while maintaining the same accuracy as

commercial analog simulators.

Keywords: Event-driven simulation, Behavioral modeling, Mixed-signal system,

SystemVerilog, High-speed I/O interface, Switching-mode power supply, Volterra

series model, Injection-locked oscillator

Student Number: 2011-30974

CONTENTS

# **Contents**

| ABSTRACT                                             | I   |

|------------------------------------------------------|-----|

| CONTENTS                                             | III |

| LIST OF FIGURES                                      | V   |

| LIST OF TABLES                                       | XII |

| CHAPTER 1 INTRODUCTION                               | 1   |

| 1.1 BACKGROUND                                       | 1   |

| 1.2 Main Contribution                                | 6   |

| 1.3 THESIS ORGANIZATION                              | 8   |

| CHAPTER 2 EVENT-DRIVEN SIMULATION OF ANALOG/MIX      | ED- |

| SIGNAL BEHAVIORS                                     | 9   |

| 2.1 PROPOSED CLOCK AND ANALOG SIGNAL REPRESENTATIONS | 10  |

| 2.2 SIGNAL TYPE DEFINITIONS IN SYSTEMVERILOG         | 14  |

| 2.3 EVENT-DRIVEN SIMULATION METHODOLOGY              | 16  |

| CHAPTER 3 HIGH-SPEED I/O INTERFACE SIMULATION        | 21  |

| 3.1 CHARGE-PUMP PHASE-LOCKED LOOP                    | 23  |

| 3.2 BANGBANG CLOCK AND DATA RECOVERY                 | 37  |

| 3.3 CHANNEL AND EQUALIZERS                           | 45  |

| 2 4 High Cheen I/O Cyctem Charles attoni             | 50  |

CONTENTS

| CHAPTER 4 SWITCHING POWER SUPPLY SIMULATION       |     |

|---------------------------------------------------|-----|

| 4.1 BOOST CONVERTER                               | 57  |

| 4.2 TIME-INTERLEAVED SWITCHED-CAPACITOR CONVERTER | 66  |

| CHAPTER 5 VOLTERRA SERIES MODEL SIMULATION        | 72  |

| 5.1 VOLTERRA SERIES MODEL                         | 74  |

| 5.2 CLASS-A POWER AMPLIFIER                       | 79  |

| 5.3 CONTINUOUS-TIME EQUALIZER                     | 84  |

| CHAPTER 6 INJECTION-LOCKED OSCILLATOR SIMULATION  | 89  |

| 6.1 PPV-BASED ILO MODEL                           | 91  |

| 6.2 LC OSCILLATOR                                 | 99  |

| 6.3 RING OSCILLATOR                               | 104 |

| 6.4 BURST-MODE CLOCK AND DATA RECOVERY            | 109 |

| CONCLUSION                                        | 116 |

| BIBLIOGRAPHY                                      | 118 |

| 초 록                                               | 126 |

LIST OF FIGURES V

# **List of Figures**

| Fig. 1.1 A simple example of a forward-Euler time-integration method for an     |

|---------------------------------------------------------------------------------|

| RC filter                                                                       |

| Fig. 1.2 An example of an analog sampler in a high speed receiver. The          |

| sampler is triggered by a noisy clock to sample a continuous-time input         |

| signal3                                                                         |

| Fig. 1.3 Existing analog simulation methods in digital simulators are not truly |

| event-driven as one input event may trigger multiple output events4             |

| Fig. 2.1 The proposed xbit-type expressing an accurate clock waveform by        |

| supplementing the timing offset11                                               |

| Fig. 2.2 The xreal-type expressing the continuous-time analog signal as a       |

| sum of complex exponential functions                                            |

| Fig. 2.3 Signal examples of the <i>xreal</i> representation                     |

| Fig. 2.4 The struct data type definitions of (a) xbit and (b) xreal in          |

| SystemVerilog15                                                                 |

| Fig. 2.5 The event-driven, s-domain computation of a linear RC filter           |

| response                                                                        |

| Fig. 2.6 A complete RC filter response with an initial condition included20     |

| Fig. 2.7 A pseudo-model of a linear RC filter in SystemVerilog20                |

| Fig. 3.1 An example of a high-speed I/O interface                               |

| Fig. 3.2 A third-order CP-PLL example; the clock and timing-sensitive           |

| signals are defined as the xbit, while the analog signal is defined as the      |

LIST OF FIGURES VI

| xreal                                                                         |

|-------------------------------------------------------------------------------|

| Fig. 3.3 Modeling with accurate timing: (a) the D flip-flop and (b) the AND   |

| gate25                                                                        |

| Fig. 3.4 A pseudo-model of the D flip-flop in SystemVerilog25                 |

| Fig. 3.5 A pseudo-model of the AND gate in SystemVerilog                      |

| Fig. 3.6 (a) The charge pump with a second-order loop filter, and (b) signal  |

| waveforms illustrating its operation                                          |

| Fig. 3.7 A pseudo-model of the charge-pump loop filter in SystemVerilog28     |

| Fig. 3.8 The voltage-controlled oscillator generates its digital clock output |

| based on <i>xreal</i> -type frequency and phase signals30                     |

| Fig. 3.9 A pseudo-model of the voltage-controlled oscillator in               |

| SystemVerilog30                                                               |

| Fig. 3.10 The input and output waveforms of the synchronous frequency         |

| divider with a division factor of 431                                         |

| Fig. 3.11 A pseudo-model of the frequency divider in SystemVerilog31          |

| Fig. 3.12 (a) The locking transient waveform of the input control voltage of  |

| the VCO, and (b) its zoomed-in view33                                         |

| Fig. 3.13 The Simulated jitter histogram of the output clock34                |

| Fig. 3.14 The simulated jitter transfer function of the charge-pump PLL34     |

| Fig. 3.15 The power spectral densities of the output phase simulated with (a) |

| the proposed method and (b) the Verilog-A model, when the up and              |

| down currents show a mismatch of 20%35                                        |

| Fig. 3.16 (a) The reference spurs of the output clock and (b) static phase    |

| offsets between the input and output clocks as a function of the charge-      |

| pump current mismatch36                                                            |

|------------------------------------------------------------------------------------|

| Fig. 3.17 The block diagram of the bangbang clock and data recovery                |

| example37                                                                          |

| Fig. 3.18 A pseudo-model of the Alexander phase detector in SystemVerilog.         |

| 39                                                                                 |

| Fig. 3.19 A pseudo-model of the comparator in SystemVerilog39                      |

| Fig. 3.20 The digital loop filter description in pure Verilog40                    |

| Fig. 3.21 A pseudo-model of the digitally-controlled oscillator in                 |

| SystemVerilog41                                                                    |

| Fig. 3.22 The locking transient waveform of the CDR clock frequency and its        |

| recovered data when (b) the CDR is not locked and (c) the CDR is                   |

| locked43                                                                           |

| Fig. 3.23 The jitter transfer functions with different digital loop filter delays. |

| 44                                                                                 |

| Fig. 3.24 The jitter transfer functions with different input data patterns44       |

| Fig. 3.25 A high-speed I/O interface with three equalization techniques: a         |

| pre-emphasis equalizer, a continuous-time linear equalizer (CTLE), and             |

| a decision-feedback equalizer (DFE)45                                              |

| Fig. 3.26 (a) The channel transfer function extracted from its measured S-         |

| parameter, and (b) the CTLE transfer function with one zero at 0.5GHz              |

| and two poles at 1.0GHz and 2.0GHz, respectively46                                 |

| Fig. 3.27 The output signal of the FIR filter with a finite transition time48      |

| Fig. 3.28 A pseudo-model of the FIR filter in SystemVerilog48                      |

| Fig. 3.29 The addition of two xreal signals is a linear combination of             |

LIST OF FIGURES VIII

| functions, and can be modeled as a combination of input parameter sets.             |

|-------------------------------------------------------------------------------------|

| 49                                                                                  |

| Fig. 3.30 A pseudo-model of the analog adder in SystemVerilog49                     |

| Fig. 3.31 The waveforms of (a) the TX driver output, (b) the channel output,        |

| (c) the CTLE output, and (d) the adder output, simulated with the                   |

| proposed method; (e), (f), (g), and (h) the waveforms of the same                   |

| signals simulated with Verilog-A models in HSPICE51                                 |

| Fig. 3.32 Eye diagrams of (a) the channel output, (b) the CTLE output, and (c)      |

| the adder output53                                                                  |

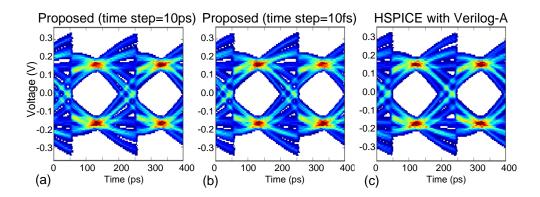

| Fig. 3.33 (a), (b) Eye diagrams simulated with the proposed method with             |

| simulation time steps of 10ps and 10fs, respectively, and (c) eye                   |

| diagram simulated with Verilog-A models in HSPICE53                                 |

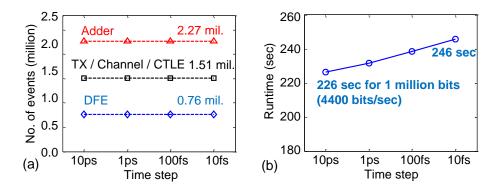

| Fig. 3.34 (a) The number of events processed in each block, and (b) the             |

| simulation runtimes for one-million bit input with different time steps.            |

| 54                                                                                  |

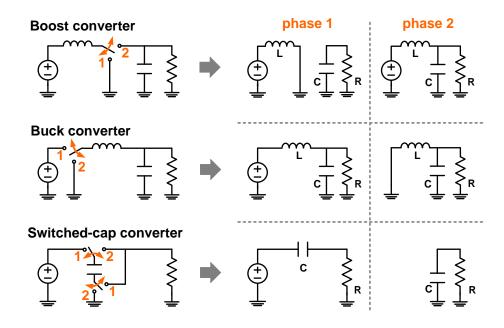

| Fig. 4.1 Switched-linear system examples                                            |

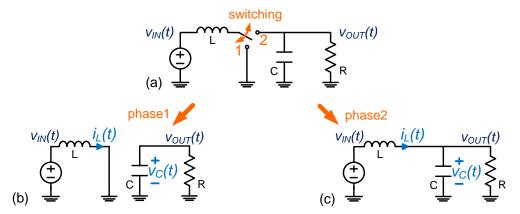

| Fig. 4.2 (a) A boost converter circuit and its linear system model in (b)           |

| switching phase 1 and (c) switching phase 257                                       |

| Fig. 4.3 The s-domain event-driven simulation of the boost converter                |

| example60                                                                           |

| Fig. 4.4 A pseudo-model of the boost converter in SystemVerilog61                   |

| Fig. 4.5 A power factor correction boost converter                                  |

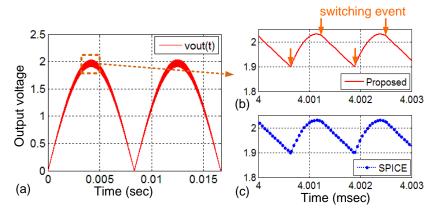

| Fig. 4.6 (a) The output voltage waveform $v_{OUT}(t)$ simulated for one 60-Hz       |

| input cycle, (b) 5000× zoom-in view of $v_{OUT}(t)$ , (c) $v_{OUT}(t)$ simulated by |

LIST OF FIGURES IX

| HSPICE65                                                                          |

|-----------------------------------------------------------------------------------|

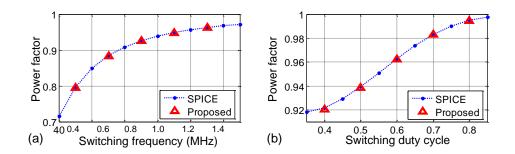

| Fig. 4.7 The comparison of the simulated power factors vs. (a) frequency and      |

| (b) switching duty cycle65                                                        |

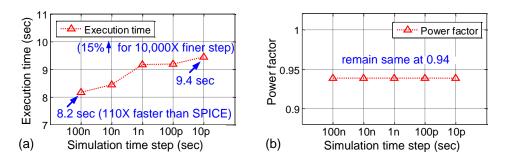

| Fig. 4.8 (a) Execution time and (b) simulated power factor for different time     |

| steps65                                                                           |

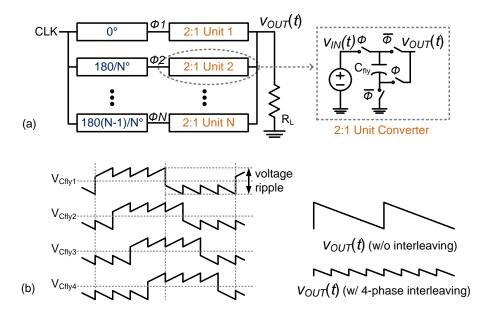

| Fig. 4.9 (a) N time-interleaved 2:1 step-down switched-capacitor DC-DC            |

| converter, (b) the waveforms of its internal capacitor voltages and final         |

| output voltage when N=4 [34]66                                                    |

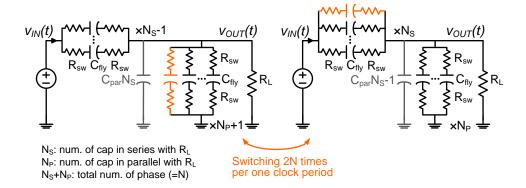

| Fig. 4.10 Switched linear circuit model of an N time-interleaved, 2:1 step-       |

| down TI-SC converter69                                                            |

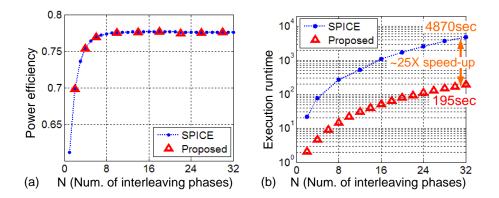

| Fig. 4.11 (a) The simulated power efficiency of the TI-SC converter and (b)       |

| execution time vs. the number of time-interleaving phases (N)71                   |

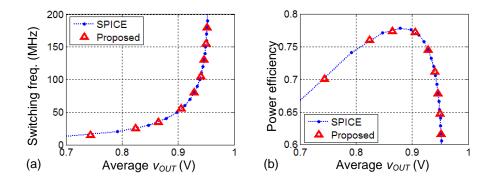

| Fig. 4.12 The simulated (a) switching frequency and (b) power efficiency of       |

| the TI-SC converter vs. the average output voltage71                              |

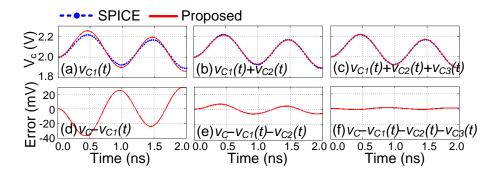

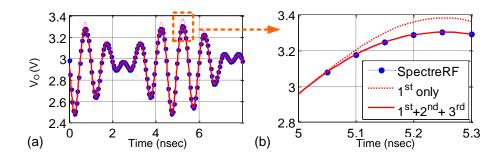

| Fig. 5.1 Output response up to (a) the first-order, (b) the second-order, and (c) |

| the third-order responses, and output error with (d) the first-order, (e)         |

| the second-order, and (f) the third-order responses                               |

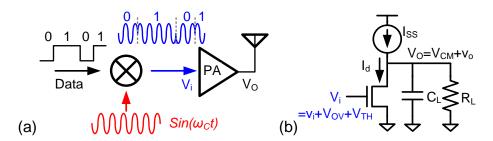

| Fig. 5.2 (a) An RF transmitter employing a phase-shift keying modulation          |

| scheme and (b) a class-A power amplifier79                                        |

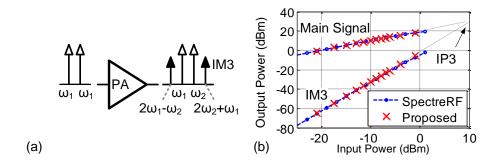

| Fig. 5.3 (a) A two-tone testbench for an RF power amplifier and (b)               |

| simulated third-order intercept point (IP3)81                                     |

| Fig. 5.4 (a) Transient waveforms of the two tone test and (b) their zoom-in       |

| view82                                                                            |

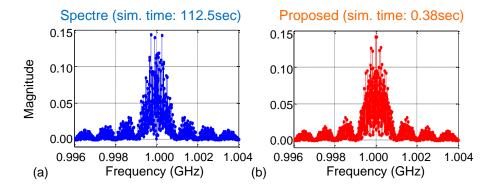

| Fig. 5.5 Output spectra of the power amplifier with data-modulated inputs         |

LIST OF FIGURES X

| simulated by (a) Spectre and (b) the proposed method82                                 |

|----------------------------------------------------------------------------------------|

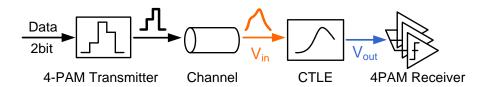

| Fig. 5.6 A 4-PAM high-speed I/O interface example.                                     |

| Fig. 5.7 Circuit schematics of the continuous-time linear equalizer85                  |

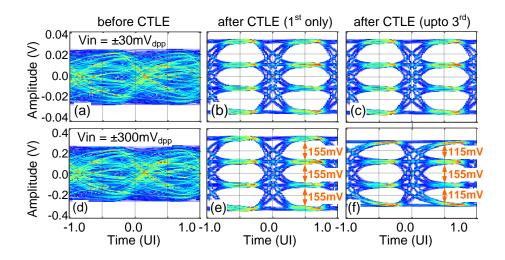

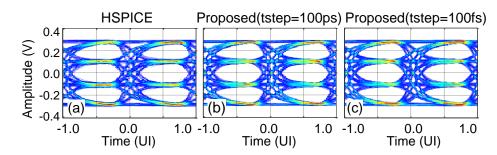

| Fig. 5.8 The simulated eye diagrams for two swing levels: $\pm 30 \text{mV}_{dpp}$ and |

| $\pm 300 mV_{dpp}.$ The eye diagrams before the CTLE (a,d) and after the               |

| CTLE without (b,e) and with the third-order distortion included (c,f). 88              |

| Fig. 5.9 Eye-diagrams of the CTLE output added up to a third-order response            |

| simulated by (a) SPICE with a maximum time step of 10ps, (b) the                       |

| proposed method with a time step of 100ps, and (c) the proposed                        |

| method with a time step of 100fs88                                                     |

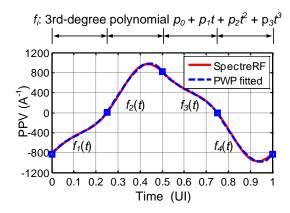

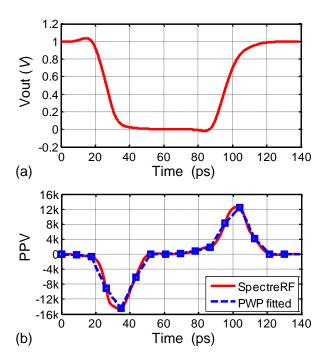

| Fig. 6.1 Piecewise polynomial expansion example of a PPV extracted by                  |

| SpectreRF94                                                                            |

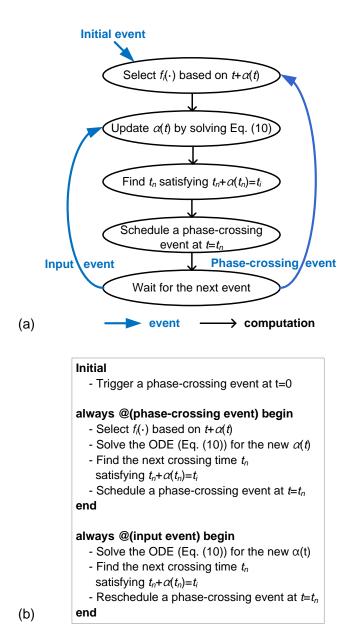

| Fig. 6.2 The procedure for the event-driven simulation of the ILO mode                 |

| using a piecewise polynomial expansion of the PPV: (a) a process                       |

| flowchart and (b) Verilog pseudo-code98                                                |

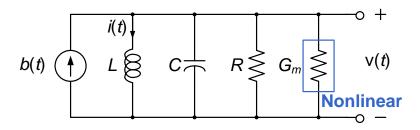

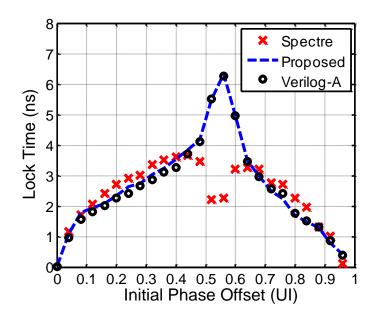

| Fig. 6.3 An LC oscillator example [51]99                                               |

| Fig. 6.4 (a) its oscillating output waveform and (b) measured perturbation             |

| projection vector (PPV) at node $v(t)$                                                 |

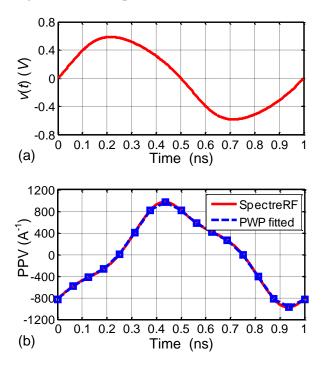

| Fig. 6.5 (a) A phase shift of $\pi$ in the input perturbation $b(t)$ , (b) a locking   |

| transient of the ILO phase, and (c) a simulation error in ILO's phase                  |

| response compared to Spectre simulation                                                |

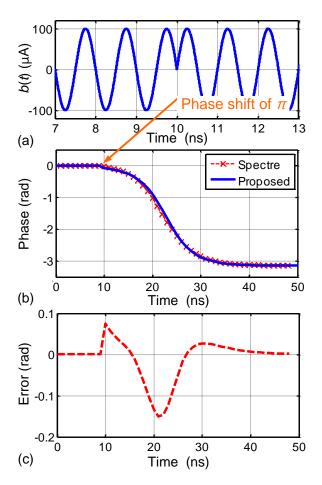

| Fig. 6.6 The worst-case phase errors and execution times while varying the             |

| degree of piecewise polynomials describing the PPV ((a) and (b)                        |

| respectively) and maximum distortion order included while solving                      |

LIST OF FIGURES XI

| each piecewise nonlinear ODE ((c) and (d), respectively)103                    |

|--------------------------------------------------------------------------------|

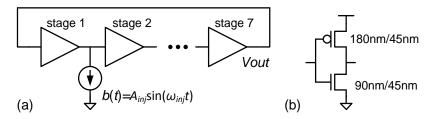

| Fig. 6.7 (a) A 7-stage injection-locked ring oscillator and (b) a circuit      |

| schematic of each stage                                                        |

| Fig. 6.8 (a) An oscillating waveform of the ring oscillator and (b) a measured |

| perturbation projection vector (PPV) at the injection node                     |

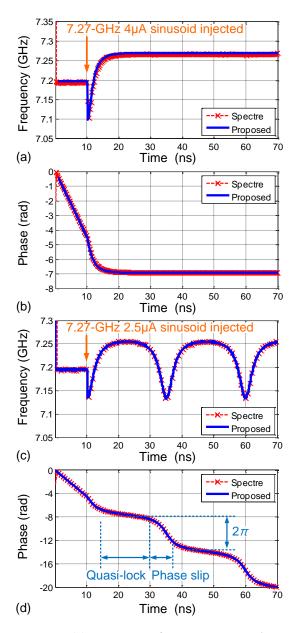

| Fig. 6.9 (a) Frequency and (b) phase waveforms when the ring oscillator is     |

| injection-locked. (c) Frequency and (d) phase waveforms when the ring          |

| oscillator is injection-pulled                                                 |

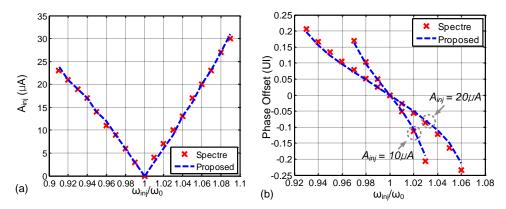

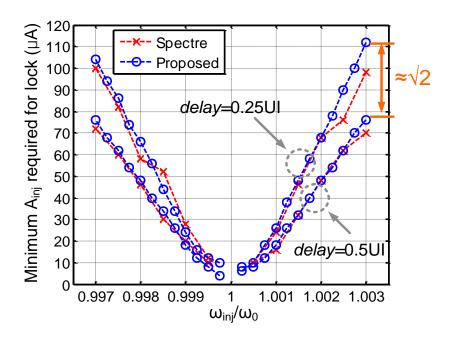

| Fig. 6.10 (a) Minimum injection amplitude required for injection-locking and   |

| (b) static phase offset between the output and the input injection signal      |

| for different injection frequencies                                            |

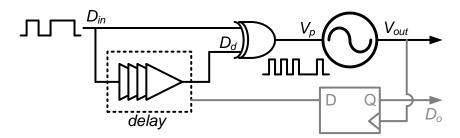

| Fig. 6.11 Burst-mode clock recovery circuits [44]                              |

| Fig. 6.12 (a) An LC oscillator used for the burst-mode clock recovery, (b) its |

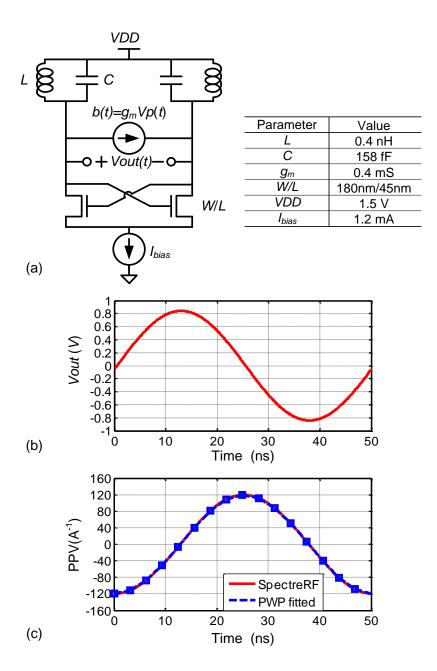

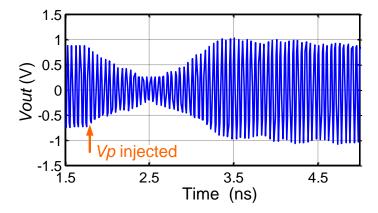

| oscillating waveform, and (c) PPV at the output node111                        |

| Fig. 6.13 (a) A locking transient of the burst-mode clock recovery and (b) its |

| zoomed-in view (c) with the input signal <i>Vp</i> 113                         |

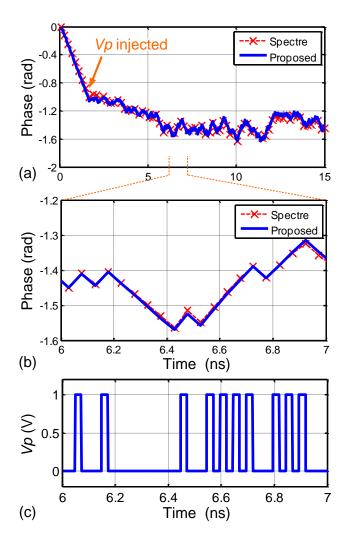

| Fig. 6.14 A lock time of the burst-mode clock recovery circuit for different   |

| initial phase offsets of the input from the LC oscillator114                   |

| Fig. 6.15 An output waveform of the LC oscillator for the case with an initial |

| phase offset of 0.56UI114                                                      |

| Fig. 6.16. The minimum injection amplitude required for the burst-mode         |

| clock recovery circuit to achieve a phase lock for different data rates.       |

| 115                                                                            |

LIST OF TABLES XII

# **List of Tables**

| Table 3.1. Design parameters for the charge-pump PLL simulation | 32 |

|-----------------------------------------------------------------|----|

| Table 3.2. Design parameters for the Bangbang CDR simulation    | 42 |

# Chapter 1

### Introduction

## 1.1 Background

Today's high-performance system-on-chip's (SoCs) are complex, consisting of tightly coupled analog and digital components. For example, an RF front-end can include a digital calibration loop that compensates for mismatches between I/Q channels [1]. A high-speed wireline receiver may employ various digital adaptation loops to adjust the timing, voltage offsets, and equalization coefficients [2]. These systems contain multiple feedback loops with complex interactions between analog and digital blocks. Such a mixture of analog and digital presents challenges in verifying them, as it is very time-consuming to verify the entire system using a transistor-level SPICE simulation. A practical solution to achieve reasonable simulation speed is to employ behavioral models.

However, existing analog behavioral simulators such as Verilog-A and Matlab

Simulink are associated with a trade-off between speed and accuracy. The main cause is that they employ ordinary differential equation (ODE) solvers to simulate analog responses. ODE solvers numerically solve differential equations based on a time-integration method (e.g., forward-Euler, backward-Euler, or trapezoidal integration methods), which approximates the derivative of a continuous-time signal with a finite difference between two data points as shown in Fig. 1.1 [3]-[6]. This finite difference approximation is inaccurate once the two data points are positioned too far away. Therefore, the time steps between data points should be fine enough to achieve the accuracy at the cost of the simulation speed.

On the other hand, there have been many efforts to model analog behaviors entirely in digital simulators such as Verilog or VHDL [7]-[10]. However, the analog simulation still poses a speed bottleneck of the system simulation. These so-called real-number modeling (RNM) approaches model analog signals as discrete-time data using *real* data types in digital simulators. The main advantages of the RNM is that it inherits the digital simulator's natural features of fast speed and

$$x(t)$$

$$R$$

$$C\dot{y}(t) + y(t) = x(t)$$

$$\dot{y}(t_k) \approx \frac{y(t_{k+1}) - y(t_k)}{t_{k+1} - t_k}$$

Finite difference approximation

Fig. 1.1 A simple example of a forward-Euler time-integration method for an RC filter.

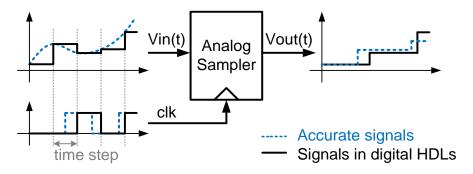

event-driven simulation. However, the event-driven simulation of analog behaviors cannot be as efficient as digital behaviors due to digital simulator's quantized time steps. Fig. 1.2 illustrates this using a high-speed receiver example. A clock-triggered comparator in the receiver detects 0 or 1 by sampling the analog signal Vin(t) at the rising edge of the clock clk. As Vin(t) continuously changes, the sampled signal Vout(t) is highly dependent on the clock timing. However, when both signals are quantized by a fixed time step of the simulator, the accuracy can be lost. For instance, the fixed time step forces the analog signal to be expressed in a piecewise-constant waveform and limits the resolution of the clock jitter that can be expressed. Some techniques can be applied to improve the accuracy [11]-[12]. For instance, [11] uses interpolated values between discrete time points to obtain approximated continuous-time signals. [12] models clock signals as samples having an amplitude proportional to the pulse width in that fixed time interval. The proposed method takes a similar approach with [12] to express accurate clock timing information, yet in a more explicit way.

Fig. 1.2 An example of an analog sampler in a high speed receiver. The sampler is triggered by a noisy clock to sample a continuous-time input signal.

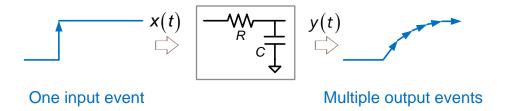

Another issue for the analog simulation in the digital simulator is that it is not truly event-driven in the sense that a single event at the input triggers multiple events at the output. Consider a low-pass RC filter that receives an one-time step change at its input (Fig. 1.3). To simulate its exponential response, the output events are required to be triggered multiple times even though there was only one input event. To relieve this inefficiency, some research employed a non-uniform time step [13]-[14]. [13] approximated an analog signal as a piecewise linear (PWL) waveform and updates its slope and offset values only when the approximation error exceeds a certain tolerance. [14] introduced connecting modules that suppress analog events when their changes are small enough. Nonetheless, they still could not realize a truly event-driven simulation.

Some recent research mitigated the speed-accuracy trade-off and realized a truly event-driven simulation of analog behaviors [15]-[17]. [15] built an event-driven model of a digitally-controlled oscillator in VHDL. For digital control codes and oscillator's phase noise characteristics, it computes perturbations of the fundamental oscillator's period. Then, the oscillator's digital output event is scheduled according

Fig. 1.3 Existing analog simulation methods in digital simulators are not truly event-driven as one input event may trigger multiple output events.

to the period. [16] presented an event-driven model for a channel ISI and a limited sampler bandwidth in Matlab. Fixing the input signal types to a pulse, the step response of a channel followed by a sampler is predetermined in a look-up table. For a series of input pulse events, the output is reconstructed as a sum of responses to each pulses. [17] implemented an event-driven simulator for a 3rd-order charge-pump PLL in C. It solved a set of governing differential equations for a loop filter and a voltage-controlled oscillator to obtain an exact phase expression in a functional form. At every clock event, it updates the phase expression and schedule the next clock switching event. While all these approaches achieved a truly event-driven simulation of analog behaviors, they share the limitations that they are not generally applicable to arbitrary systems or input types.

#### 1.2 Main Contribution

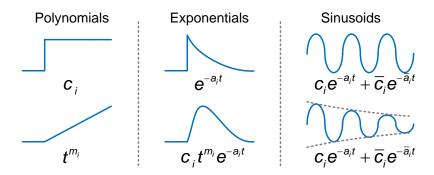

This work proposes an event-driven simulation methodology that accurately simulates analog/mixed-signal behaviors without sacrificing the simulation speed. The key idea is the manner of expressing the clock and analog signals; rather than implicitly relying on fine time steps, it explicitly attaches the key information of interest to the signals. For the clock signal, a *real*-valued variable indicating exactly when the clock made the last transition is attached. For continuous-time analog signals, coefficients describing the signals as time-domain functions (e.g.,  $c_i$ ,  $m_i$ , and  $a_i$  of the complex exponential function  $c_i t^{m_i} e^{-a_i t}$ ) are supplemented. With these signal representations, the clock and analog signals can be evaluated at any arbitrary time precision regardless of the simulator's time step. In addition, the analog behaviors can be simulated in a truly event-driven fashion without involving numerical time-integration methods.

The proposed methodology is implemented in a single digital hardware description language SystemVerilog. As most of recent SoCs include a large number of digital components, it is desirable to build a mixed-signal simulator based on a digital simulator. Also, the digital simulator inherently provides an event-driven engine supporting the proposed event-driven simulation. The supplemental variables for clock and analog signals are bundled as one signal using a composite data type *struct* in SystemVerilog, which keeps module ports pin-compatible.

The thesis demonstrates that the proposed method can simulate complex mixedsignal systems employing various classes of analog circuit behaviors: timeinvariant/time-varying linear behaviors and time-invariant/time-varying nonlinear behaviors. The first demonstrative example is a high-speed I/O interface with timing sensitive circuits (a phase-locked loop and a clock-and-data recovery loop) and linear analog blocks (a channel and linear equalizers). The second examples are switching power supplies which exhibit time-varying linear behaviors. In addition, weakly nonlinear behaviors are simulated in an RF transmitter and a multi-level pulse amplitude modulation receiver. Finally, the proposed method is extended to time-varying nonlinear behaviors like an injection-locked oscillator. Simulation results show that the proposed method can accurately simulate various mixed-signal systems in a truly event-driven fashion with tens to hundreds of speed-ups compared to existing analog simulators.

## 1.3 Thesis Organization

Chapter 2 describes the proposed representations of clock and analog signals, and their corresponding type definitions in SystemVerilog. Using those data types, the event-driven simulation of analog/mixed-signal behaviors is presented. Chapter 3 explains modeling details of linear systems on the proposed simulation platform using a demonstrative example of a high-speed I/O interface. Chapter 4 provides modeling examples of linear time-varying systems with various power converters. Chapter 5 applies the proposed method to nonlinear systems modeled with a Volterra series. Chapter 6 further demonstrates nonlinear time-varying system simulations with injection-locked oscillator examples.

# Chapter 2

# Event-Driven Simulation of Analog/Mixed-Signal Behaviors

This chapter explains main ideas of the proposed event-driven simulation methodology for analog/mixed-signal behaviors. The proposed method introduces new ways to express accurate clock and analog signals in digital hardware description languages (HDLs). To break the speed-accuracy trade-off explained in the introduction, new signal expression explicitly carries the supplementary information: transition timing information to the clock signal and a functional representation to the analog signal. The analog signal representation allows event-driven simulation of analog behaviors modeled in ordinary differential equations. The newly introduced signal types are implemented in a digital HDL, particularly SystemVerilog. These main ideas are demonstrated through a simple RC filter example.

## 2.1 Proposed Clock and Analog Signal

## Representations

As described in Chapter 1.1, digital simulators such as Verilog and VHDL use quantized time steps, which limit the accuracy and speed when modeling and simulating timing-critical clock signals and continuous-time analog signals. The proposed method overcomes this limitation by introducing two new signal types: *xbit* for clock signals and *xreal* for analog signals.

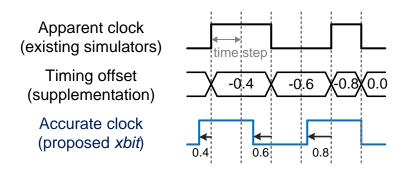

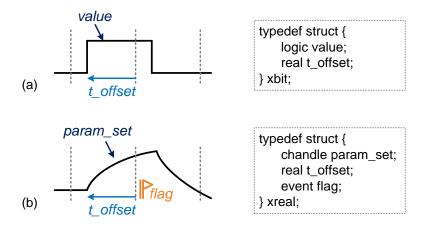

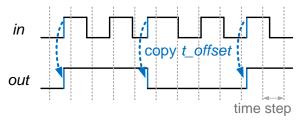

An *xbit*-type signal expresses accurate clock transition times by attaching its timing offset explicitly to the signal, as illustrated in Fig. 2.1. In digital simulators, the simulation time is quantized with a fixed time step, and the actual clock transition is snapped to the nearest integer multiple of the time step. The only way to make this apparent transition close to the actual transition is to decrease the time step. In contrast, the timing offset information attached to the *xbit* signal indicates where the actual transition is located relative to the apparent transition time. For instance, if the clock signal switches from 0 to 1 at an apparent time of 10 with the timing offset having a value of -0.4, this implies that the actual transition occurred at 0.4 before 10 (i.e., at a time of 9.6). This timing offset ranges [-1 x time step, 0] and takes a double-precision floating-point value. Therefore, the *xbit*-type signal can achieve a virtually infinite timing resolution regardless of the simulator's time step.

Fig. 2.1 The proposed *xbit*-type expressing an accurate clock waveform by supplementing the timing offset.

On the other hand, an *xreal*-type signal carries a set of coefficients expressing a continuous-time analog waveform in a functional form. Specifically, the analog signal x(t) is represented as a linear combination of complex exponential functions:

$$x(t) = \sum_{i} c_{i} t^{m_{i}} e^{-a_{i}t} . {2-1}$$

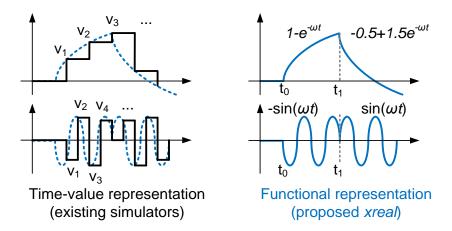

This functional form is parameterized with three real-valued coefficients,  $c_i$ ,  $m_i$ , and  $a_i$ . Any change in this set of coefficients constitutes an xreal event, and the analog waveform is represented as a series of these events. For example, Fig. 2.2 compares cases in which an exponential and a sinusoidal waveforms are expressed using a set of discrete data points and a series of xreal events. The existing digital simulators describe the waveform with the discrete data points (e.g., a real-type variable), and it requires fine time steps to improve its accuracy. In contrast, the xreal representation expresses the accurate waveform with only two events at  $t_0$  and  $t_1$ , and its accuracy is independent of the simulation time step.

Fig. 2.2 The *xreal*-type expressing the continuous-time analog signal as a sum of complex exponential functions

In addition, the family of the *xreal* functional form in Eq. (2-1) includes most of signal types a designer may encounter in analog circuits. For instance, the *xreal* functional form expresses a family of polynomials with  $a_i = 0$ , exponentials with a real  $a_i$  value, sinusoids with complex  $c_i$  and  $a_i$  values, and any linear combination of these signal families (Fig. 2.3).

Fig. 2.3 Signal examples of the xreal representation.

Another advantage of the *xreal* functional form is that it can express outputs of both linear and nonlinear systems. Scrutinizing Eq. (2-1), the *xreal* functional form is a general expression of a linear system response, where  $a_i$  and  $m_i$  correspond to the eigenvalues (poles) and their multiplicities of the system, respectively. Therefore, this form encompasses all possible outputs of linear systems with *xreal* inputs. For nonlinear systems, the nonlinear distortions are often modeled as modulations between signals (e.g. Talyor or Volterra seires models [20]-[22]). As the *xreal*-type is in a sum-of-exponential form, multiplication between those exponentials results in the sum-of-exponential form, which is again the *xreal*-type.

## 2.2 Signal Type Definitions in

## **SystemVerilog**

The two proposed signal types *xbit* and *xreal* are defined as the *struct*-type in SystemVerilog. SystemVerilog is a language extension to Verilog [23], which supports a composite data type *struct* bundling multiple variables into one and allows the *struct*-type variable to pass through port boundaries. Therefore, the *struct*-type can attach the supplementary information (i.e., the timing offset in *xbit* and the coefficients in *xreal*) to the signal variables without adding new ports at the module interface.

Fig. 2.4 shows signal definitions of *xbit* and *xreal* in SystemVerilog. The *xbit* type has two member variables: value and  $t_{-}offset$  where value denotes the logic level of the signal, and  $t_{-}offset$  denotes the timing offset of the last transition. On the other hand, the xreal type has three member variables:  $param_{-}set$ ,  $t_{-}offset$ , and flag.  $param_{-}set$  is a C-pointer to the parameter set, which is an array containing the values of three coefficients:  $c_i$ ,  $m_i$ , and  $a_i$ . For  $param_{-}set$ , a dynamic data structure such as linked lists is necessary as the number of elements in the s-domain parameter set can vary from signal to signal.  $t_{-}offset$  is the timing offset of the last change event. flag is an event variable to indicate whether the change event has occurred. Since the member variable  $param_{-}set$  is merely a C-pointer whose address does not change once it is initialized, a separate variable is necessary to notify the blocks consuming this signal of the change in coefficients. Therefore, a block that

produces an *xreal* signal must trigger the event variable *flag* whenever it updates the parameter set (e.g. '->' operator in Verilog).

Fig. 2.4 The struct data type definitions of (a) xbit and (b) xreal in SystemVerilog.

## 2.3 Event-Driven Simulation Methodology

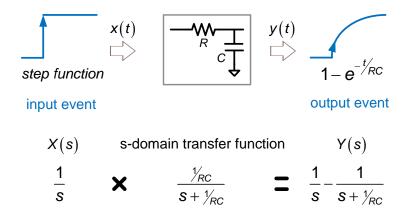

This section explains how the *xreal* representation of continuous-time signals enables a purely event-driven simulation of analog systems without involving any numerical iteration. The *xreal* form in Eq. (2-1) has a Laplace s-domain equivalence:

$$X(t) = \sum_{i} c_i t^{m_i} e^{-a_i t} \xrightarrow{\mathcal{L}} X(s) = \sum_{i} \frac{c_i \times m_i!}{(s+a_i)^{m_i+1}}.$$

(2-2)

This implies that if the s-domain transfer function of a linear system H(s) is given, its response to the input x(t) can be computed simply as a product of the two s-domain functions, X(s) and H(s). Assuming that the transfer function is expressed in the residue form,

$$H(s) = \sum_{j} \frac{q_{j}}{\left(s + p_{j}\right)^{n_{j}}} \tag{2-3}$$

the process of computing the output is simply calculating the cross-products between the terms in X(s) and H(s) and adding them, as expressed by Eq. (2-4). The resulting cross-products can be decomposed back into the residue form via partial-fraction decomposition. It is noteworthy that this computation is fully algebraic; there is no numerical iteration or time-step integration involved.

$$\sum_{i} \frac{b_{i}}{(s+a_{i})^{m_{i}}} \times \sum_{j} \frac{q_{j}}{(s+p_{j})^{n_{j}}} = \sum_{i,j} \frac{b_{i}}{(s+a_{i})^{m_{i}}} \times \frac{q_{j}}{(s+p_{j})^{n_{j}}}$$

$$= \sum_{i,j} \left( \sum_{k=1}^{m_{i}} \frac{c_{k}}{(s+a_{i})^{k}} + \sum_{l=1}^{n_{j}} \frac{d_{l}}{(s+p_{j})^{l}} \right) \tag{2-4}$$

$$\begin{aligned} \text{where, } c_k &= \begin{cases} \frac{b_i \cdot q_j}{(p_j - a_i)^{n_j}}, \ \ for \ k = m_i \\ \\ \frac{b_i \cdot q_j}{(p_j - a_i)^{m_i + n_j - k}} \cdot \frac{\left(-1\right)^{m_i - k}}{(m_i - k)!} \cdot \prod_{z = i}^{m_i - 1} \left(m_i + n_j - 1 - z\right), \ \ for \ k = m_i - 1, \cdots, 1 \end{cases} \\ d_l &= \begin{cases} \frac{b_i \cdot q_j}{(a_i - p_j)^{m_i}}, \ \ for \ l = n_j \\ \\ \frac{b_i \cdot q_j}{(a_i - p_j)^{n_j + m_i - l}} \cdot \frac{\left(-1\right)^{n_j - l}}{(n_j - l)!} \cdot \prod_{z = i}^{n_j - 1} \left(n_j + m_i - 1 - z\right), \ \ for \ l = n_j - 1, \cdots, 1 \end{cases} \end{aligned}$$

The described computation is purely event-driven; computation is required only once when the coefficients describing the input change. In the other words, when there is an event involving a change to the input coefficients, the coefficients of the output are updated according to Eq. (2-4), and the results remain valid until the next input event arrives. This stands in contrast to SPICE, where the output value keeps being updated between the events. In case of multiple input events, the output of the linear system can be evaluated based on the superposition principle; responses to each input event is computed as outlined in Eq. (2-4), and then the final output is a sum of those responses.

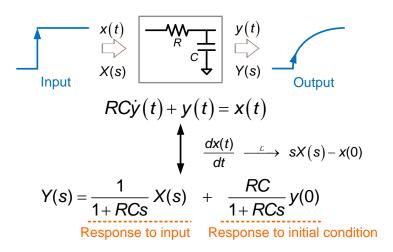

Fig. 2.5 illustrates the proposed event-driven computation using an RC filter. When a step input arrives at  $t_0$ , which is equivalent to a change in the coefficient  $c_i$ , this triggers a computation. As the RC filter has a transfer function of 1/(RCs+1), and the step input is 1/s in the s-domain, its output is simply a product of these two factors. The resulting output is 1/s - 1/(s+1/RC) according to Eq. (2-4), which corresponds to  $1-e^{-t/RC}$  in the time-domain. This output is valid until the next input event, realizing therefore an event-driven simulation of analog blocks.

Fig. 2.5 The event-driven, s-domain computation of a linear RC filter response.

While initial conditions are omitted for brevity in Fig. 2.5, their effects should be considered once a system includes reactive elements. For instance, a Laplace transform of the governing differential equation of the RC filter results in two parts: a response to an input  $X(s) \cdot 1/(RCs+1)$  and a response to an initial condition  $y(0) \cdot RC/(RCs+1)$ , where y(0) is an initial voltage across a capacitor (Fig. 2.6). The response to initial conditions always results in the same form as the *xreal* form in Eq. (2-4), and hence it is additive to the responses to the input events.

Fig. 2.7 shows a pseudo-model of the RC-filter example in SystemVerilog using the proposed event-driven simulation method. The input and output variables, *x* and *y*, are defined as *xreal* types. Whenever an input event occurs (as indicated by *x.flag*), the instructions within the *always* statement are executed to compute the output event. First, initial conditions of the circuits are sampled using a DPI function *sample*(). Note that as analog signals are expressed in a functional form, initial conditions can be accurately computed at any time point. Then, the output responses

to the initial condition and the input event are computed by multiplying the sampled initial condition  $y_i$  and the input coefficients  $x.param_set$  with the transfer functions  $tf_i$  and  $tf_i$ , respectively.  $tf_i$  and  $tf_i$  are transfer functions from the initial condition and from the input event to the output response.  $compute_coeff()$  is a DPI function that performs the multiplying operation outlined in Eq. (2-4). Because the output event is always triggered simultaneously to the input event,  $y.t_offset$  is set equal to  $x.t_offset$ . Finally, the event flag y.flag is triggered to notify the subsequent blocks that the signal y has been updated.

Fig. 2.6 A complete RC filter response with an initial condition included.

Fig. 2.7 A pseudo-model of a linear RC filter in SystemVerilog.

# Chapter 3

# **High-Speed I/O Interface**

## **Simulation**

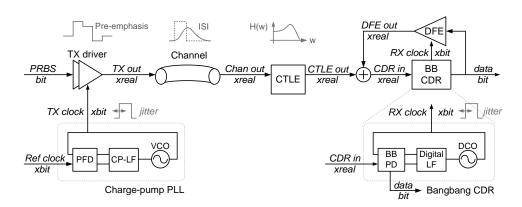

This chapter demonstrates how to apply the proposed method to model and simulate systems including time-invariant linear analog blocks through a high-speed I/O interface example. The exemplary high-speed I/O system consists of a transmitter with a charge-pump phase-locked loop (PLL), a receiver with a bangbang clock and data recovery (CDR) loop, continuous/discrete-time equalizers, and a channel (Fig. 3.1). The modeling accuracy of the system relies strongly on the accurate clock timing information and the analog signal waveform. For instance, it requires a sub-pico-second time resolution to measure the jitter performances of a PLL and a CDR. It also demands a sub-mV voltage resolution to simulate channel distortions and equalizer performances. Each sub-section will show that the proposed method can accurately model and simulate those sub-blocks in a truly event-driven fashion. In the final sub-section, the system-level behaviors are simulated and compared with Verilog-A models simulated in HSPICE.

Fig. 3.1 An example of a high-speed I/O interface.

## 3.1 Charge-Pump Phase-Locked Loop

The first sub-block is a third-order charge-pump phase-locked loop (PLL) on the transmitter side. As the clock signal affects digital system performances, it is desirable to simulate such systems in digital simulators. However, a PLL is analog in nature, requiring an accurate simulation of a clock jitter and a loop filter waveform.

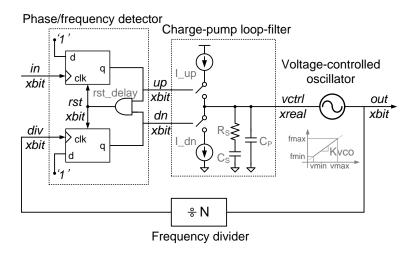

The exemplary charge-pump PLL is composed of a phase/frequency detector (PFD), a charge pump with a second-order loop filter (CP-LF), a voltage-controlled oscillator (VCO), and a frequency divider. The signals carrying the timing information, such as the reference input clock *in*, the VCO output clock *out*, the frequency-divided clock *div*, and the PFD output pulses *up/dn* are *xbit*-type signals, while the analog control voltage *vctrl* is an *xreal*-type signal (Fig. 3.2).

Fig. 3.2 A third-order CP-PLL example; the clock and timing-sensitive signals are defined as the *xbit*, while the analog signal is defined as the *xreal*.

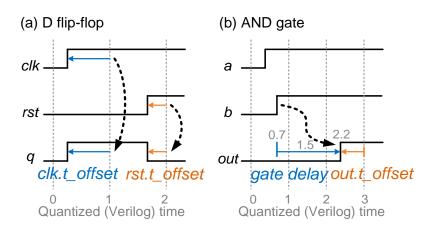

## 3.1.1 Phase/Frequency Detector

With *xbit* representations, a PFD model can achieve a sub-time-step resolution for the timing difference between the input clock edges. The PFD employs two D flip-flops (DFF) with asynchronous reset and one AND gate. The DFF sets the output to '1' at the rising edge of the clock clk and resets the output to '0' at the rising edge of the reset rst (Fig. 3.3(a)). Therefore, its output q copies the timing offsets of clk for the rising edge and rst for the falling edge. In this way, all the timing information of clk and rst can be transferred to the output without degrading the accuracy. The AND gate produces the output '1' when both DFF outputs rise. Its timing offset for the rising edge is determined by the  $t_{-}$  offset of the signals arriving later, as shown in Fig. 3.3(b). The pseudo-models of the DFF and the AND gate are given in Fig. 3.4 and Fig. 3.5.

Moreover, not only the signal timing offset but also the gate delay can be accurately simulated regardless of the simulator's time step. Especially, the AND gate delay on the reset path,  $rst\_delay$ , plays an important role in the PLL non-idealities [24]. Fig. 3.3(b) depicts a case in which the gate delay is not a multiple integer of the time step; for instance, when the AND gate input arrives at a time of 0.7 with a gate delay of 1.5, the output rises at a time of 2.2. A model of this in SystemVerilog is described in Fig. 3.5. First, the AND gate determines the Verilog delay in a quantized time step ( $ceil(delay+t\_offset)$ ). Then, after this quantized delay, it sets the output value to '1' and computes its timing offset. In Fig. 3.3(b), the AND gate waits for two time steps and sets the output to '1' with a  $t\_offset$  of -0.8.

Fig. 3.3 Modeling with accurate timing: (a) the D flip-flop and (b) the AND gate.

```

module dff (

output xbit q,

input_xbit d,

input xbit clk,

input xbit rst);

always @(posedge clk.value) begin

q.value = d.value;

q.t_offset = clk.t_offset;

end

always @(posedge rst.value) begin

q.value = 0;

q.t_offset = rst.t_offset;

end

endmodule

```

Fig. 3.4 A pseudo-model of the D flip-flop in SystemVerilog.

```

module and (

output xbit out,

input xbit a,

input xbit b);

always @(posedge a.value or posedge b.value) begin

if (a.value ==1 && b.value ==1) begin

t_offset = (a.t_offset > b.toffset)?

a.t_offset: b.t_offset;

#(ceil(delay+t_offset)) out.value = 1;

out.t_offset = delay+t_offset - ceil(delay+t_offset);

end

end

always @(negedge a.value) begin

t_offset = a.t_offset;

#(ceil(delay+t_offset)) out.value = 0;

out.t_offset = delay+t_offset - ceil(delay+t_offset);

end

always @(negedge b.value) begin

t offset = b.t offset;

#(ceil(delay+t_offset)) out.value = 0;

out.t_offset = delay+t_offset - ceil(delay+t_offset);

end

endmodule

```

Fig. 3.5 A pseudo-model of the AND gate in SystemVerilog.

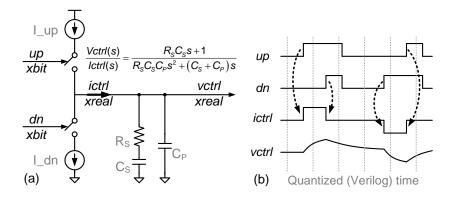

## 3.1.2 Charge-Pump Loop Filter

A charge-pump loop filter generates the control voltage in an event-driven fashion by computing the filter response only when the up or dn signal changes. The charge pump applies a positive current when up is high and a negative current when dn is high (Fig. 3.6). This current flows into the following loop filter, which is composed of a resistor, Rs, and two capacitors, Cs and Cp. The output voltage vctrl is a product of the charge-pump current ictrl and the impedance transfer function Z(s):

$$Z(s) = \frac{vctrl(s)}{ictrl(s)} = \frac{R_{S}C_{S}s + 1}{R_{S}C_{S}C_{P}s^{2} + (C_{S} + C_{P})s} .$$

(3-1)

The charge-pump pseudo-model is given in Fig. 3.7. The charge-pump determines the value of the output current  $I\_cur$  upon every change in the up/dn signals. The xreal representation of this current is a constant with the parameter set of  $\{(I\_cur, 0, 0)\}$ . The  $t\_offset$  of the output current ictrl is identical to that of the up/dn signal. The change in ictrl triggers the computation of the output voltage vctrl, which is then computed as a response of a linear filter with a transfer function of Z(s) to the ictrl input as described in Chapter 2.3.

Fig. 3.6 (a) The charge pump with a second-order loop filter, and (b) signal waveforms illustrating its operation.

```

module cp_lf (

output xreal vctrl,

input xbit up,

input xbit dn);

chandle tf:

// impedance of loop filter

always @(up.value) begin

I_cur = I_up*up.value - I_dn*dn.value;

ictrl.param_set = create_params(I_cur,0,0);

ictrl.t_offset = up.t_offset;

->ictrl.flag;

always @(dn.value) begin

I_cur = I_up*up.value - I_dn*dn.value;

ictrl.param_set = create_params(I_cur,0,0);

ictrl.t_offset = dn.t_offset;

->ictrl.flag;

end

always @(Ictrl.flag) begin

vctrl.param_set = compute_coeff(ictrl.param_set, tf);

vctrl.t_offset = ictrl.t_offset;

->vctrl.flag;

end

endmodule

```

Fig. 3.7 A pseudo-model of the charge-pump loop filter in SystemVerilog.

## 3.1.3 Voltage Controlled Oscillator

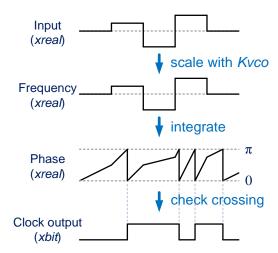

The voltage-controlled oscillator (VCO) model generates an *xbit*-type clock of which frequency is controlled by an *xreal*-type input *vctrl*. The frequency of the oscillator is a linearly scaled version of the input, and its phase is an integral of that frequency (Fig. 3.8). This integration can be carried by multiplying 1/s in the s-domain without time-step integration. This is in contrast to other simulators which must accumulate the frequency for every time step, thus degrading the simulation speed. Finally, the *xbit*-typed output clock is toggled every time the *xreal*-type phase reaches the value of  $\pi$ .

A pseudo-model of the VCO in SystemVerilog is shown in Fig. 3.9. When the input control voltage vctrl has an event, the VCO updates its frequency signal by scaling vctrl using a DPI function scale(). The phase signal is then computed by multiplying the frequency signal by 1/s in the s-domain, after which the DPI function  $find\_cross()$  checks when the phase signal crosses  $\pi$ . Based on the crossing time  $t\_cross$ , the timing offset  $t\_offset$  and the quantized time stamp at which the output event needs to be scheduled are determined. For instance, if  $t\_cross$  is 2.5ns and the Verilog time step is 1ns, the VCO model waits for three time steps (3ns) and toggles the output with a  $t\_offset$  of -0.5ns. When the scheduled output event is triggered, the phase is shifted by  $-\pi$  using the DPI function subtract() to prevent the phase from overflowing. At the same time, the next  $\pi$ -crossing event is scheduled, and the clock continues to toggle whenever the phase crosses  $\pi$ .

Fig. 3.8 The voltage-controlled oscillator generates its digital clock output based on *xreal*-type frequency and phase signals.

```

module vco (

output xbit out,

input xreal vctrl);

always @(vctrl.flag) begin

freq.param_set = scale(vctrl.param_set, Kvco);

tf = create_params(1,0,0);

phase.param_set = compute_coeff(freq.param_set, tf);

t_cross = find_cross(phase.param_set);

#(ceil(t_cross)) -> out_event;

end

always @(out_event) begin

out.value = ~out.value;

out.t_offset = t_cross - ceil(t_cross);

phase.param_set = subtract(phase.param_set,pi);

always @(out.value) begin

t_cross = find_cross(phase.param_set);

#(ceil(t_cross)) -> out_event;

end

endmodule

```

Fig. 3.9 A pseudo-model of the voltage-controlled oscillator in SystemVerilog.

## 3.1.4 Frequency Divider

A synchronous divider is modeled by aligning the output clock timing to the input clock timing. The divider model counts the number of rising transitions of the input and toggles its output whenever it reaches a predetermined division factor. If there is no delay, the *t\_offset* value of the output is set equal to that of the triggering input. Fig. 3.10 illustrates this operation with a division factor of 4. Fig. 3.11 shows a pseudo-model of the frequency divider in SystemVerilog.

Fig. 3.10 The input and output waveforms of the synchronous frequency divider with a division factor of 4.

```

module freq_div (

output xbit out,

input xbit in);

always @(posedge in.value) begin

count = count + 1;

if (count == div_factor/2) begin

out.value = 1;

out.t offset = in.t offset;

end

else if (count == div_factor) begin

out.value = 0;

out.t offset = in.t offset;

count = 0:

end

end

endmodule

```

Fig. 3.11 A pseudo-model of the frequency divider in SystemVerilog.

### 3.1.5 Simulation Results

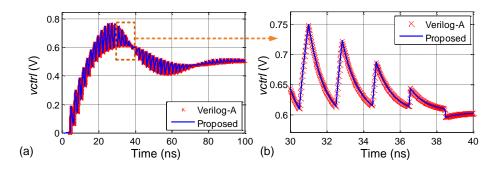

The described charge-pump PLL model is simulated with the design parameters listed in Table 3.1. The initial VCO output frequency is 1.5GHz at a control voltage *vctrl* of 0V. Its target output frequency is 2.0GHz for a reference frequency of 0.5GHz and a frequency division factor of 4. To verify the accuracy, the simulation results are compared with those of Verilog-A models simulated in HSPICE. The Verilog-A models of the PFD with the charge pump, digital logic gates and VCO are those found in [25]-[26], and the loop filter is modeled using the *laplace\_nd* function [6].

Fig. 3.12 shows the locking transient waveform of the VCO control voltage *vctrl* in comparison with the Verilog-A waveform. The value of *vctrl* is increased from its initial value of 0V and is locked at 0.5V. This value corresponds to a VCO frequency of 2.0GHz for an initial frequency of 1.5GHz and a *Kvco* of 1GHz/V. The zoomed-in view in Fig. 3.12(b) shows that the simulated waveform is in good agreement with the Verilog-A waveform. The measured maximum and the root

| Module     | Parameter | Description                    | Value  |

|------------|-----------|--------------------------------|--------|

| PFD        | rst_delay | AND gate delay on a reset path | 30ps   |

| CP-LF      | I_up/I_dn | Up/down current amplitude      | 20μΑ   |

|            | Rs        | Series resistance              | 20kΩ   |

|            | Cs        | Series capacitance             | 500fF  |

|            | Ср        | Parallel capacitance           | 50fF   |

| VCO        | Kvco      | Voltage-to-frequency gain      | 1GHz/V |

| Freq. Div. | N         | Frequency division factor      | 4      |

Table 3.1. Design parameters for the charge-pump PLL simulation

Fig. 3.12 (a) The locking transient waveform of the input control voltage of the VCO, and (b) its zoomed-in view.

mean square (RMS) differences between the two waveforms are 0.74mV and 0.23mV, respectively.

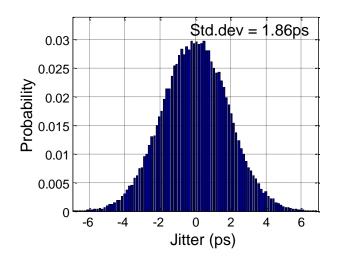

Fig. 3.13 and Fig. 3.14 show the simulated jitter histogram and jitter transfer function. In Fig. 3.13, the jitter histogram of the output clock signal is simulated when the PLL is locked to a reference at 0.5 GHz with a RMS jitter of 4ps. The simulated jitter histogram shows a standard deviation of 1.86ps, which matches well with a Verilog-A result of 1.82ps. Note that the proposed method uses a time step as coarse as 10ps, yet still can obtain a jitter histogram with a fine resolution. Fig. 3.14 shows the jitter transfer function. The jitter transfer function is simulated by applying a sinusoidal jitter to the reference clock and measuring the amplitude of the resulting sinusoidal jitter of the output clock. Fig. 3.14 plots the ratio between the input and output jitter amplitudes when the jitter frequency is swept from 100kHz to 0.5GHz. The simulated results are in good agreement with the theoretical jitter transfer function of a third-order charge-pump PLL, given as:

$$H(s) = \frac{T(s)}{1 + T(s)/N},$$

where  $T(s) = \frac{I_{cp} \cdot Kvco}{2\pi s} \frac{R_s C_s s + 1}{R_s C_s C_P s^2 + (C_s + C_P)s}.$

(3-2)

Fig. 3.13 The Simulated jitter histogram of the output clock.

Fig. 3.14 The simulated jitter transfer function of the charge-pump PLL.

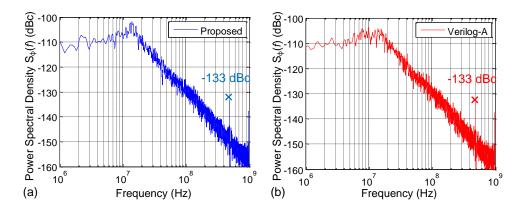

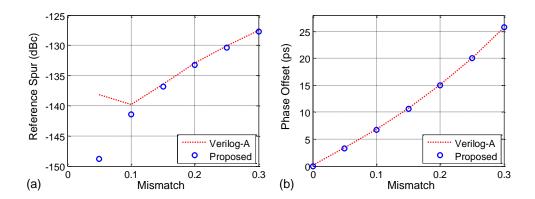

To assess the non-ideality effects, the reference spurs and static phase offsets are measured as a function of the mismatch between the up and down currents. Fig. 3.15 shows the reference spurs at 0.5GHz in the power spectral density  $S_{\phi}(f)$  of the output phase when the up and down currents are mismatched by 20%. In Fig. 3.15(a), the current mismatch causes a reference spur of -133dBc, which is in good agreement with the Verilog-A results in Fig. 3.15(b). Fig. 3.16(a) plots the reference spur level as the mismatch varies from 0 to 30%. These results show good agreement with the Verilog-A results except when the mismatch is 5%, where the reference spur is smaller than the noise level of -145dBc. The current mismatch also causes the phase offset between the reference and the output clock signals. Fig. 3.16(b) shows that the static phase offset increases to 25ps when the charge-pump current mismatch reaches 30%.

Fig. 3.15 The power spectral densities of the output phase simulated with (a) the proposed method and (b) the Verilog-A model, when the up and down currents show a mismatch of 20%.

Fig. 3.16 (a) The reference spurs of the output clock and (b) static phase offsets between the input and output clocks as a function of the charge-pump current mismatch.

## 3.2 Bangbang Clock and Data Recovery

The second sub-block is a bangbang clock and data recovery (CDR) circuit. The bangbang CDR is often considered pure digital circuits as the loop filter is digital and the oscillator is digitally controlled. However, the timing information of clock signals is critical in the phase detector, and the oscillator is still an analog block. Therefore, the bangbang CDR cannot be accurately simulated in a pure digital simulator.

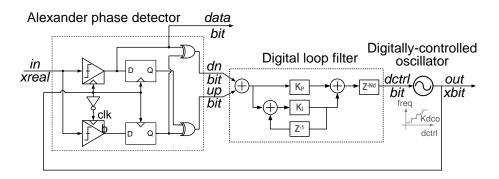

This sub-section provides modeling details and simulation results of a bangbang CDR. An bangbang CDR example consists of three blocks (Fig. 3.17): an Alexander phase detector (PD), a digital loop filter (LF), and a digitally controlled oscillator (DCO). The difference with regard to the previous PLL model is that the PD output takes a binary value and the DCO is controlled by a digital value. Therefore, the loop filter is implemented in digital and described in pure Verilog.

Fig. 3.17 The block diagram of the bangbang clock and data recovery example.

#### 3.2.1 Alexander Phase Detector

The Alexander PD employs two analog comparators, two DFFs, and two XOR gates. One of the comparators determines the data at the clock's rising edges, while the other extracts the edges at the clock's falling edges. The following DFF and XOR gates determine whether the timing is early or late; their models are similar to the logic gate models in the charge-pump PLL example. While these DFFs and XORs consume *xbit*-type signals, their outputs, *data*, *up*, and *dn*, are converted to *bit*-type signals using *assign* (Fig. 3.18). This conversion occurs because the subsequent digital loop filter is purely digital.

Fig. 3.19 outlines the analog comparator model in the Alexander PD. The analog comparator computes the sampled value based on the input's functional representation. Therefore, this model accurately compares the input signal independently of the simulator's time step. For example, if the input is an exponential signal of  $exp(-10^9/t)$  and the clock is triggered at a Verilog time of 1ns with a time offset of -0.6ns, the sampled value is  $exp(-10^9/0.4ns)$ . The sampling is performed in C using the DPI function sample(). Finally, the comparator output is determined by comparing the sampled value with the comparator threshold.

```

module alexander_pd (

output bit data,

output bit up,

output bit dn,

input xbit clk,

input xreal in);

comparator data comp(data d, in, clk);

comparator edge_comp(edge_d, in, clkb);

dff data_dff(data_q, data_d, clk);

dff edge_dff(edge_q, edge_d, clk);

inv clk inv(clkb, clk);

xor up_xor(up_xbit, data_q, edge_q);

xor dn_xor(dn_xbit, data_d, edge_q);

/* casting to bit-type */

assign data = data_d.value;

assign up = up xbit.value;

assign dn = dn_xbit.value;

endmodule

```

Fig. 3.18 A pseudo-model of the Alexander phase detector in SystemVerilog.

```

module comparator (

output xbit out,

input xreal in,

input xbit clk);

always @(posedge clk.value) begin

t_clk = $realtime + clk.t_offset;

in_value = sample(in.param_set, t_clk);

out.value = (in_value > threshold)? 1: 0;

out.t_offset = clk.t_offset;

end

endmodule

```

Fig. 3.19 A pseudo-model of the comparator in SystemVerilog.

## 3.2.2 Digital Loop Filter

The digital loop filter can be described in pure Verilog. In this example, the digital loop filter has a proportional and an integral path (Fig. 3.17). The integral path accumulates the input with an integral gain of *Ki*, and the proportional path scales the input with a proportional gain of *Kp*. These two values added to determine the output, and the output is delayed by *Nd* clock cycles to model the filter delay. Fig. 3.20 shows a digital loop filter model in Verilog.

```

module digital_lf (

output reg[width out-1:0] out,

input xbit clk,

input bit up,

input_bit dn);

reg [width out-1:0] out d [Nd-1:0];

reg [width out-1:0] acc;

reg [width_out-1:0] out_p;

always @(posedge clk) begin

acc = acc + Ki*(up - dn);

end

always @(acc or up or dn) begin

out p = Kp^*(up - dn) + acc;

end

assign out = out_d[Nd-1];

always @(posedge clk) begin

for (i=Nd-1; i>0; i--) out d[i] = out d[i-1];

out_d[0] = out_p;

end

endmodule

```

Fig. 3.20 The digital loop filter description in pure Verilog.

## 3.2.3 Digitally Controlled Oscillator

The modeling of a digitally controlled oscillator (DCO) is identical to that of the VCO in the charge-pump PLL example except that its input signal is a *bit*-type signal. The DCO frequency is the input *dctrl* linearly scaled by a factor of *Kdco*. Its phase is obtained by integrating the frequency, and the output *out* is toggled every time the phase crosses  $\pi$ .

```

module dco (

output xbit out,

input bit [width dctrl-1:0] dctrl);

always @(dctrl) begin

freq.param set = create params(Kdco*real'(dctrl),0,0);

tf = create params(1,0,0);

phase.param set = compute coeff(freq.param set, tf);

t cross = find cross(phase.param set);

#(ceil(t_cross)) -> out_event;

end

always @(out event) begin

out.value = ~out.value;

out.t_offset = t_cross - ceil(t_cross);

phase.param_set = subtract(phase.param_set,pi);

end

always @(out.value) begin

t cross = find cross(phase.param set);

#(ceil(t_cross)) -> out_event;

end

endmodule

```

Fig. 3.21 A pseudo-model of the digitally-controlled oscillator in SystemVerilog.

### 3.2.4 Simulation Results

The bangbang CDR example is simulated with the design parameters listed in Table 3.2. The bangbang CDR input is a 2-Gbps pseudo random bit sequence (PRBS) data stream which is transmitted through a lossy channel. The transmitter and channel models are identical to those explained in the next sub-section.

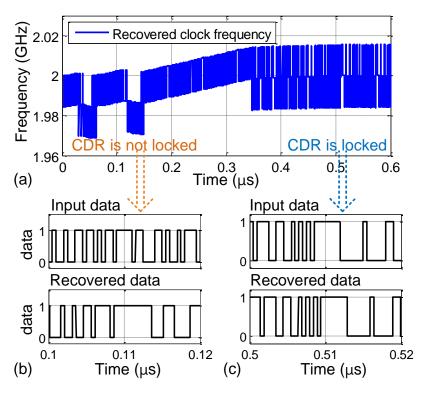

Fig. 3.22 shows the locking transient waveforms of the CDR. Fig. 3.22(a) plots its DCO frequency as a function of time. The DCO frequency is initially 1.984GHz and increases to 2GHz. The sudden changes in the frequency arise from its proportional path, which increases the phase of the DCO instantaneously. Fig. 3.22(b) and (c) compare the recovered data during this locking transient period. The recovered data show errors when the CDR frequency is lower than the input data rate (Fig. 3.22(b)), while the recovered data match the input data when the CDR frequency is at the input data rate (Fig. 3.22(c)).

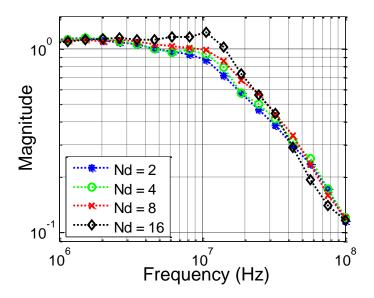

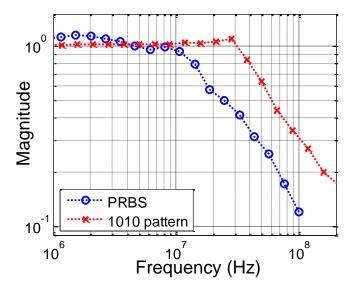

The effects of the digital loop filter delay and the input transition density on the jitter transfer function are investigated. Fig. 3.23 shows the jitter transfer functions for different digital loop filter delays. As the filter delay increases from 2 to 16, the

| Module     | Parameter | Description                 | Value                    |

|------------|-----------|-----------------------------|--------------------------|

| Digital LF | Кр        | Proportional gain           | 256                      |

|            | Ki        | Integral gain               | 1                        |

|            | Nd        | Digital loop filter delay   | 4 clock cycles           |

|            | Width     | Bit-width of digital output | 14                       |

| DCO        | Kdco      | Digital-to-frequency gain   | 2 <sup>-14</sup> GHz/LSB |

Table 3.2. Design parameters for the Bangbang CDR simulation

peaking of the transfer function increases. Fig. 3.24 compares the jitter transfer functions when two different inputs of a pseudo random bit sequence (PRBS) data pattern and a '1010' data pattern are applied. This figure illustrates that the CDR bandwidth is wider for the '1010' pattern than for the PRBS pattern. This wider bandwidth arises due to the higher transition density of the '1010' pattern, which allows the CDR to lock faster with more frequent updates of the control signals.

Fig. 3.22 The locking transient waveform of the CDR clock frequency and its recovered data when (b) the CDR is not locked and (c) the CDR is locked.

Fig. 3.23 The jitter transfer functions with different digital loop filter delays.

Fig. 3.24 The jitter transfer functions with different input data patterns.

## 3.3 Channel and Equalizers

This sub-section explains modeling and simulation of a channel and three equalization schemes: a transmitter-side pre-emphasis equalization, and a receiver-side continuous-time linear equalization (CTLE) and a decision-feedback equalization (DFE) as shown in Fig. 3.25.

Fig. 3.25 A high-speed I/O interface with three equalization techniques: a pre-emphasis equalizer, a continuous-time linear equalizer (CTLE), and a decision-feedback equalizer (DFE).

### 3.3.1 Channel and Continuous-Time Linear

## **Equalizer**

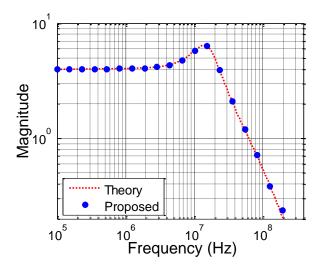

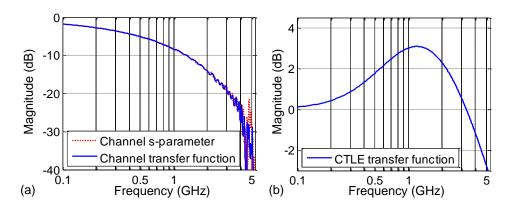

The channel and CTLE are modeled as linear filters with s-domain transfer functions. The channel transfer function is extracted from the s-parameters by fitting S21 into a rational polynomial form using the *rationalfit* function in Matlab. Fig. 3.26(a) shows the transfer function extracted with 47 poles, when the delay of 3.001ns is factored out. The CTLE transfer function has a high-pass characteristic with one zero and two poles. Fig. 3.26(b) plots its transfer function when it has a zero at 0.5GHz and poles at 1 and 2GHz. Then, these linear analog behavior can be modeled in the same way as described in Section 2.3.

Fig. 3.26 (a) The channel transfer function extracted from its measured S-parameter, and (b) the CTLE transfer function with one zero at 0.5GHz and two poles at 1.0GHz and 2.0GHz, respectively.

## 3.3.2 Pre-Emphasis and Decision-Feedback

## **Equalizer**

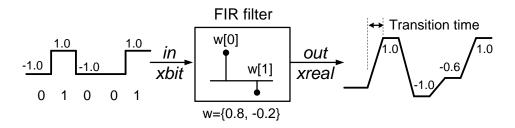

The pre-emphasis equalization and DFE can be modeled using a finite impulse response (FIR) filter, which determines the output as a weighted sum of the input data. For instance, Fig. 3.27 shows the output signal with weighting coefficients of {0.8, -0.2}. Fig. 3.28 outlines the FIR filter model in SystemVerilog. The FIR filter computes the output value and triggers an output event at every rising clock edge. If the output has a finite transition time, two events are required to define the start and end points of the transition; the first event starts the transition with a finite transition slope, and the second event ends the transition with the final value after the transition time.

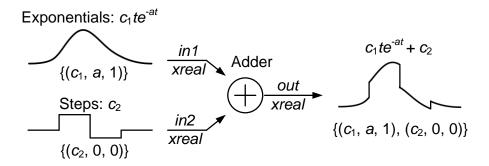

The analog adder combines the CTLE output and the DFE output. As the CTLE and DFE outputs are in the *xreal* functional form, their addition is a linear combination of those functions. For example, if the CTLE output is an exponential function of  $c_1te^{-at}$  and the DFE output is a step function of  $c_2$ , the added output is a sum of those two functions,  $c_1te^{-at} + c_2$ , as shown in Fig. 3.29. Therefore, the parameter set of the adder output is a union of the parameter sets of the CTLE and DFE outputs. This operation in SystemVerilog is outlined in Fig. 3.30. Whenever either input changes, the output parameter set is updated to a union of input parameter sets using the DPI function union().

Fig. 3.27 The output signal of the FIR filter with a finite transition time.

```

module fir_filter (

output xreal out,

input xbit in,

input xbit clk);

always @(posedge clk.value) begin

value = 0.8*in.value - 0.2*p_in;

/* start the transition */

slope = (value - p_value)/t_tran;

out.param_set = create_params(slope, 0, 1);

out.t_offset = clk.t_offset;

->out.flag;

/* finish the transition */

// transition time

#(t_tran);

out.param_set = create_params(value, 0, 0);

out.t offset = clk.t offset;

->out.flag;

p_value = value; p_in = in.value;

end

endmodule

```

Fig. 3.28 A pseudo-model of the FIR filter in SystemVerilog.

Fig. 3.29 The addition of two *xreal* signals is a linear combination of functions, and can be modeled as a combination of input parameter sets.

```

module adder (

output xreal out,

input xreal in1,

input xreal in2);

always @(in1.flag) begin

out.param_set = union(in1.param_set, in2.param_set);

out.t_offset = in1.t_offset;

->out.flag;

end

always @(in2.flag) begin

out.params = union(in1.param_set, in2.param_set);

out.t_offset = in2.t_offset;

->out.flag;

end

endmodule

```

Fig. 3.30 A pseudo-model of the analog adder in SystemVerilog.

### 3.3.3 Simulation Results

The design parameters of the high-speed I/O interface example are as follows. The weighting coefficients of the pre-emphasis and decision-feedback equalizers are {0.8, -0.2} and {-0.14, -0.03}. The continuous-time linear equalizer has one zero at 0.5GHz and two poles at 1 and 2GHz. The transmitted data rate is 5Gb/sec.

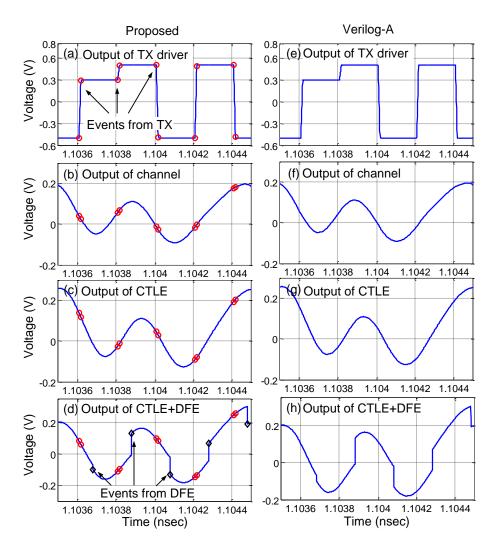

Fig. 3.31 shows the analog waveforms of the transmitter (TX) driver, channel, CTLE, and DFE adder. The analog events are denoted with the circles, and these events propagate multiple analog blocks without introducing any additional events. In Fig. 3.31(a), the TX driver generates two events per input bit to start and end the ramp signal. In Fig. 3.31(b) and Fig. 3.31(c), these events propagate through the channel and the CTLE without adding any new event, yet still describing accurate continuous-time waveforms. In Fig. 3.31(d), the events from the CTLE and the DFE are combined by the adder. Fig. 3.31(e)-(h) compare the waveforms with Verilog-A models simulated in HSPICE. For the Verilog-A model, the digital logic gates and oscillators are based on the Verilog-A model library provided in [25]-[26], while the analog filters are modeled using the *laplace\_nd* function [6]. The simulation results of the proposed method are in good agreement with the Verilog-A models. The measured maximum and the root-mean square (RMS) differences between those waveforms are 0.12mV and 32μV for a time period of [0,100ns], respectively.

Fig. 3.31 The waveforms of (a) the TX driver output, (b) the channel output, (c) the CTLE output, and (d) the adder output, simulated with the proposed method; (e), (f), (g), and (h) the waveforms of the same signals simulated with Verilog-A models in HSPICE.

## 3.4 High-Speed I/O System Simulation

This sub-section summarizes system-level simulation results; the simulation includes all the sub-blocks outlined in previous sub-sections. The data rate is increased to 5Gb/s (from 2Gb/s in the bangbang CDR example) by the aid of equalizers. The charge-pump PLL and bangbang CDR use the same design parameters as the preceding examples, except that the center frequencies of the VCO and DCO are 5GHz.

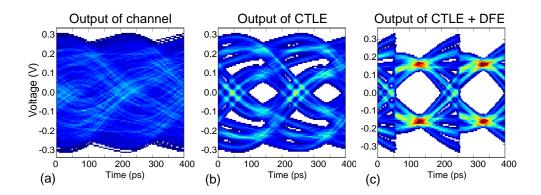

Fig. 3.32 and Fig. 3.33 show simulated eye diagrams in comparison with the Verilog-A model. Fig. 3.32 shows the three eye diagrams of the channel, the CTLE, and the DFE adder, showing that their eye openings are enlarged as the signal goes through the equalizers. Fig. 3.33(a) and Fig. 3.33(b) compare eye diagrams simulated with different time steps of 10ps and 10fs. These two eye diagrams are identical, demonstrating that the accuracy is independent of the simulation time step. Fig. 3.33(b) and Fig. 3.33(c) compare eye diagrams simulated with the proposed method and the Verilog-A model. These figures illustrate that the simulation results of the proposed method are in good agreement with those of the Verilog-A model.

Fig. 3.32 Eye diagrams of (a) the channel output, (b) the CTLE output, and (c) the adder output.

Fig. 3.33 (a), (b) Eye diagrams simulated with the proposed method with simulation time steps of 10ps and 10fs, respectively, and (c) eye diagram simulated with Verilog-A models in HSPICE.

Fig. 3.34(a) shows the number of events processed in the TX driver, channel, CTLE, and DFE adder for one million input data. The number of events in each block remains the same regardless of the simulation time step, demonstrating that the proposed method is truly event-driven. Fig. 3.34(b) summarizes the simulation runtime on a Linux machine with an Intel Core i5-3570 CPU. The runtime of the proposed method for one million bits is 226 sec for a time step of 10ps, which is equivalent to 4400 bits/sec. The runtime increases slightly to 246 sec (by 8%) for a time step of 10fs, but this increase is minimal considering that the time step becomes finer by a factor of 1000. These steady simulation speeds arise because the amount of computation is unaffected by the simulation time step due to the event-driven simulation. For reference, the simulation runtime of the Verilog-A model was 168min for one million bits, which is 45× slower than the proposed method.

Fig. 3.34 (a) The number of events processed in each block, and (b) the simulation runtimes for one-million bit input with different time steps.

# Chapter 4

# **Switching Power Supply Simulation**

A switching power supply includes one or more switches which change the system input-to-output relationship depending on their connections, but the system can be modeled as a linear time-invariant system between switching instants (i.e. a switched linear system). The switching power supplies like a boost converter, a buck converter, and a switched-capacitor converter are typical examples of a switched linear system (Fig. 4.1) [27]. The main difficulty in simulating them is that the time-integration methods of analog simulators cannot efficiently handle such abrupt changes due to switching activities [28]. Moreover, most switching power supplies are characterized by high-frequency switching activities that demand fine-grained simulation for accuracy, but also by slow transients that require long simulation times.

Fig. 4.1 Switched-linear system examples.

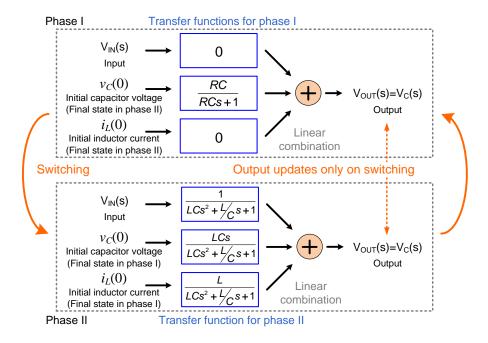

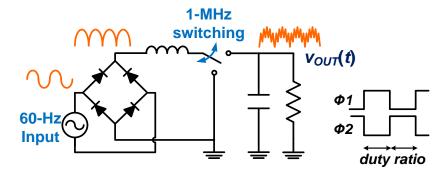

This chapter demonstrates how to apply the proposed method to switched linear systems and compares its simulation accuracy and speed with existing analog simulators. The main difference from linear system simulation described in Chapter 3 is that switched linear system is modeled with multiple transfer functions, each of which describes the circuit network during each switching phase. At every switching event, one transfer function is selected depending on the switch connections and compute the output response. In other words, in addition to the input events, the switching event can also trigger an output event. The switched linear system simulation is demonstrated through two power converter examples, a power factor correction (PFC) boost converter [33] and a time-interleaved switched-capacitor DC-DC converter [34].

### **4.1 Boost Converter**

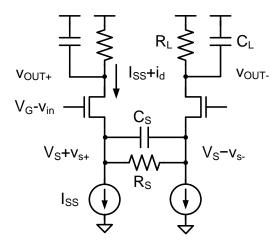

Boost converters are widely used for DC/AC-to-DC power conversion with an output voltage greater than its input voltage. A basic architecture is composed of an inductor, a capacitor, a resistor, and a switch (Fig. 4.2). The boost converter has two operation phases alternated by a switch connection as shown in Fig. 4.2(a). With the switch in position 1 (phase 1), the right-hand side of the inductor is connected to the ground, resulting in the network shown in Fig. 4.2(b). With the switch in position 2 (phase 2), the inductor is connected to the output, leading to the circuit shown in Fig. 4.2(c).

Fig. 4.2 (a) A boost converter circuit and its linear system model in (b) switching phase 1 and (c) switching phase 2.

## 4.1.1 System Model