#### 저작자표시-비영리-동일조건변경허락 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

- 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

- 이차적 저작물을 작성할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

동일조건변경허락. 귀하가 이 저작물을 개작, 변형 또는 가공했을 경우 에는, 이 저작물과 동일한 이용허락조건하에서만 배포할 수 있습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

Disclaimer

### Ph.D. DISSERTATION

# Reliability in Floating-Gate NAND Flash Memory Devices

Floating-Gate를 갖는 Flash Memory 소자의 신뢰성분석

BY

**SUNG-MIN JOE**

February 2015

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING COLLEGE OF ENGINEERING SEOUL NATIONAL UNIVERSITY

# Reliability in Floating-Gate NAND Flash Memory Devices

# Floating-Gate를 갖는 NAND Flash Memory소자의 신뢰성분석

指導教授 李宗昊

이 論文을工學博士 學位論文으로 提出함 2015년2월

서울大學校 大學院

電氣·情報 工學部

曺 誠 敏

曺誠敏의 工學博士 學位論文을 認准함

2015년 2월

委員長: 박영준

副委員長:이 종 호 重要

委 員: 박병국(印)

委員: 송기환(前)

委 員: 권혁인

# **Abstract**

As flash memory cells continue to decrease in scale, random telegraph noise (RTN) caused by electron capture or emission at trap sites has become an important issue. Fluctuations in the threshold voltage ( $\Delta V_{th}$ ) due to RTN can cause serious problems, such as read errors and device instability. As the thickness of the inter-poly dielectric IPD continues to decrease, the traps in the IPD also lead to reliability issues related to the leakage current and data retention.

In this thesis, we investigate the reliability of NAND flash memory with respect to traps not only in the tunneling oxide but also in the IPD of the cell device.

We first focus on traps that produce RTN in the tunneling oxide during a read operation. The trap position with respect to the channel surface and the floating-gate ( $x_T$ ) and the trap position along the channel length direction ( $y_T$ ) in the fabricated NAND flash memories were obtained by considering the channel resistance of the pass cells. The RTN in the floating-gate NAND flash cell strings interfered with the adjacent bit-line cell, and the effects of such on the fluctuations in the bit-line current ( $\Delta I_{BL}$ = high  $I_{BL}$  – low  $I_{BL}$ ) were characterized.

The electron current density  $(J_e)$  of a read cell was found to be appreciably different depending on the position in the channel width direction relative to the

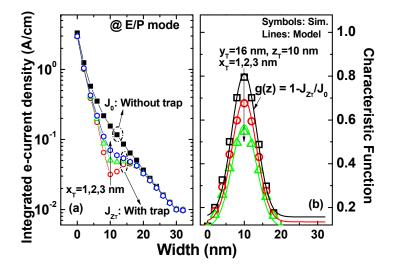

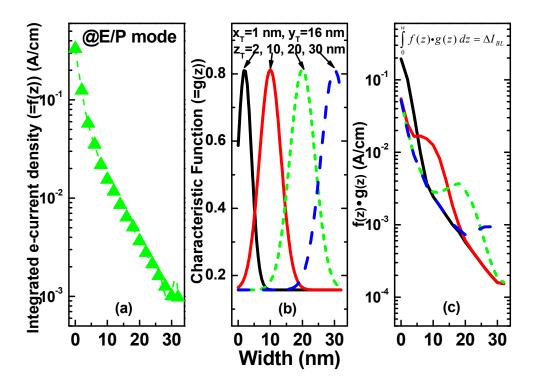

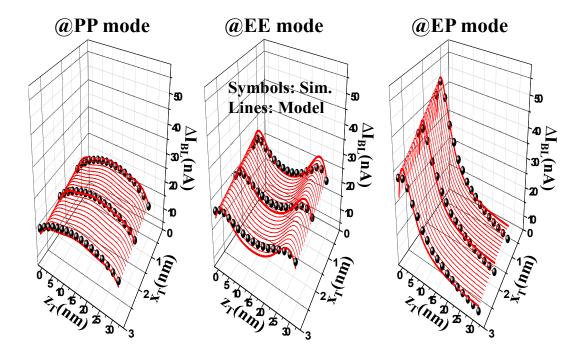

interference produced by the adjacent bit-line cells. We verified that  $\Delta I_{\rm BL}$  due to RTN increases as a high  $J_{\rm e}$  position is controlled to be close to a trap position in 32 nm NAND flash memory strings. The adjacent cell interference was shown to affect not only  $\Delta I_{\rm BL}$  but also the ratio between the capture and the emission time constants  $[\ln(\tau_c/\tau_e)]$ . We used the interference between the adjacent bit-lines (BLs) to obtain the trap position along the width direction and to represent the 3-D position of the traps in 32 nm and 26 nm NAND flash memory cells for the first time. We propose a new read method that reduces the effects on  $\Delta I_{\rm BL}$  resulting from RTN. The pre-bias is controlled in the us range, and our method was confirmed to effectively suppress the effect of the RTN during read operations in NAND flash memory. Second of all, we investigate the hysteresis phenomenon in the floating-gate NAND flash memory strings, which originates from the traps in the bottom oxide of the oxide/nitride/oxide blocking dielectric (IPD). The hysteresis phenomenon in the floating-gate NAND flash memory strings is analyzed by measuring pulsed I-V and fast transient  $I_{BL}$ . A new read method that suppresses the effect of the hysteresis phenomena was also proposed in order to reduce the read failures in NAND flash memory. In the Appendix,  $\Delta I_{\rm BL}$  is modeled with the trap position as a parameter for the state (program or erase) of the adjacent bit-line cells, and it is observed to appreciably affect the current density distribution.  $\Delta I_{\rm BL}$  is modeled by determining the integrated electron current density  $[J_0=f(z)]$  and the electric blockade length  $(L_t)$  by considering the

effect of the interference on the adjacent cells. A characteristic function [g(z)]

with a Gaussian functional form is defined based on  $L_{\rm t}$  and the trap position

within the tunneling oxide from the channel surface  $(x_T)$ . Finally,  $\Delta I_{\rm BL}$  is

extracted by integrating f(z) and g(z). Our model accurately predicts  $\Delta I_{\rm BL}$ , with

the trap position as a parameter of the state of the bit-line cells, showing good

agreement with data from a 3-D simulation.

Key Words: Reliability, NAND flash memory, Random Telegraph Noise, Bit-line

interference, Bit-line current fluctuation, Floating-gate, Inter-poly dielectrics (IPD),

Hysteresis.

**Student Number**: 2010-30998

3

# **Contents**

| Abstract 1 |                                                                                                                                                                          |                                                                                                                                             |  |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Contents 4 |                                                                                                                                                                          |                                                                                                                                             |  |  |  |  |

| Chapter 1  |                                                                                                                                                                          |                                                                                                                                             |  |  |  |  |

| Intr       | oduction                                                                                                                                                                 | 1  tion                                                                                                                                     |  |  |  |  |

| 1.1        | RELIABILITY ISSUES IN NAND FLASH MEMORY                                                                                                                                  | 7                                                                                                                                           |  |  |  |  |

| 1.2        | MOTIVATION AND ORGANIZATION                                                                                                                                              | 14                                                                                                                                          |  |  |  |  |

| Cha        | pter 2                                                                                                                                                                   |                                                                                                                                             |  |  |  |  |

| Exti       | Reliability issues in NAND flash memory 7 Motivation and organization 14  apter 2  raction of trap profiles considering channel stance of pass cells 16  Introduction 16 |                                                                                                                                             |  |  |  |  |

| resis      | stance of pass cells                                                                                                                                                     | tion 7  ABILITY ISSUES IN NAND FLASH MEMORY 7  IVATION AND ORGANIZATION 14  2  Ion of trap profiles considering channel ce of pass cells 16 |  |  |  |  |

| 2.1        | Introduction                                                                                                                                                             | 16                                                                                                                                          |  |  |  |  |

| 2.2        | DEVICE STRUCTURE AND MEASUREMENT METHOD                                                                                                                                  | 17                                                                                                                                          |  |  |  |  |

| 2.3        | EQUATIONS OF TRAP PROFILES IN A NAND FLASH MEMORY STRING                                                                                                                 | 19                                                                                                                                          |  |  |  |  |

| 2.4        | VERIFICATION OF PROPOSED EQUATIONS                                                                                                                                       | 24                                                                                                                                          |  |  |  |  |

| 2.5        | DISTRIBUTION OF TRAP POSITIONS IN TUNNELING OXIDE OF NAND FLA                                                                                                            | ASH MEMORY 29                                                                                                                               |  |  |  |  |

# **Chapter 3**

Effect of bit-line interference on RTN in NAND

| flas | h memory                                                      | 30     |

|------|---------------------------------------------------------------|--------|

| 3.1  | Introduction                                                  | 30     |

| 3.2  | DEVICE STRUCTURE AND SIMULATION CONDITION                     | 31     |

| 3.3  | RESULTS OF 3-D TCAD SIMULATION                                | 31     |

| 3.4  | RTN MEASUREMENT RESULTS WITH THE STATE OF ADJACENT BIT-LINE C | ELLS38 |

| 3.5  | 3-D TRAP POSITION IN TUNNELING OXIDE                          | 45     |

|      | pter 4                                                        |        |

| A no | ew read method suppressing random tel                         | egraph |

| nois | e                                                             | 49     |

| 4.1  | Introduction                                                  | 49     |

| 4.2  | DEVICE STRUCTURE AND MEASUREMENT SETUP                        | 50     |

| 4.3  | MEASUREMENT RESULTS AND DISCUSSION                            | 52     |

| Cha  | pter 5                                                        |        |

| Hys  | teresis phenomena in floating-gate                            | NAND   |

| flas | h memory                                                      | 64     |

| 5.1  | Introduction                                                  | 64     |

| 5.2  | DEVICE STRUCTURE AND MEASUREMENT SETUP                        | 67     |

| 5.3  | HYSTERESIS PHENOMENA IN ABNORMAL CELLS                        | 69     |

| 5.4  | ORIGIN OF HYSTERESIS PHENOMENON IN THE ABNORMAL CELL          | 76     |

| 5.5  | HYSTERESIS PHENOMENA WITH BIAS AND P/E CYCLING STRESS         | 90     |

| 5.6  | EFFECT OF HYSTERESIS PHENOMENA ON READ OPERATION              | 96     |

|      |                                                               |        |

| Conclusions 104                                                 |                                                                                                                       |     |  |  |  |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| Appendix                                                        |                                                                                                                       |     |  |  |  |

| Modeling of $\Delta I_{\rm BL}$ due to RTN considering bit-line |                                                                                                                       |     |  |  |  |

| inte                                                            | pendix deling of ΔI <sub>BL</sub> due to RTN considering bit-line erference 106 Introduction 106 Device structure 108 |     |  |  |  |

| A.1                                                             | Introduction                                                                                                          | 106 |  |  |  |

| A.2                                                             | DEVICE STRUCTURE                                                                                                      | 108 |  |  |  |

| A.3                                                             | RESULTS AND DISCUSSION                                                                                                | 108 |  |  |  |

| Bibl                                                            | liography                                                                                                             | 120 |  |  |  |

| Abs                                                             | stract in Korean                                                                                                      | 129 |  |  |  |

# Chapter 1

# Introduction

## 1.1 Reliability issues in NAND flash memory

Currently, NAND flash memory has evolved as a result of the increase in diversity in computing environments. NAND flash memory has been extensively adopted as the main storage device for mobile and multimedia products due to its smaller dimensions, lower power consumption, and higher access speed relative to magnetic core memory. Moreover, hard disk drives (HDD) will be completely replaced with solid state drives (SSD) in the near future. The reason for such success can be explained by the rapid reduction in the feature size of memory cells and multi-level-cell (MLC) operation, which have led to a reduction in the cost per bit and a resulting increase in consumer demand. The 2013 International Technology Roadmap for Semiconductors (ITRS) projects

that the physical gate length of NAND flash memory can be scaled down to 12 nm and that the maximum number of bits per cell will be three bits due to the lower cost per bit that can be achieved in 2015 [1]. However, as the dimensions of NAND flash memory cells are reduced near the final scaling limit in the nanometer regime and the maximum number of bits per cell increases, NAND flash memory has begun to face challenges related to reliability.

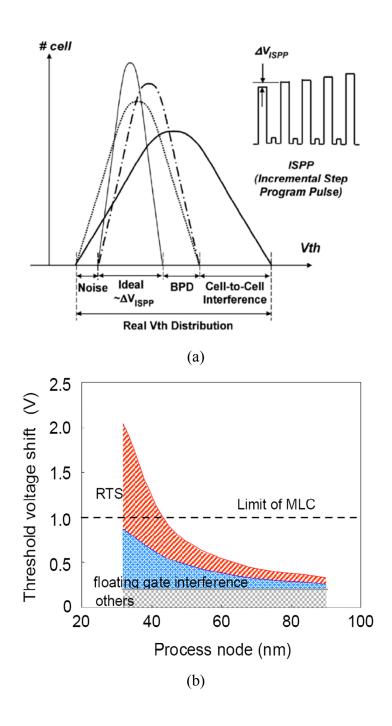

In contrast with NOR flash memory, NAND flash memory suffers from various problems – such as cell-to-cell interference, background pattern dependency, read disturbance and so on – due to the intrinsic characteristics of its architecture and the corresponding operating scheme. These problems cause a broad distribution in  $V_{\rm th}$  and influence the read operations, as shown in Fig. 1.1 [2, 3]. In order to overcome these issues, many groups have studied new solutions from an operation standpoint as well as from an architectural point of view. However, these solutions have led to an increase in the complexity of the algorithms used in the operation scheme as well as in the manufacturing process.

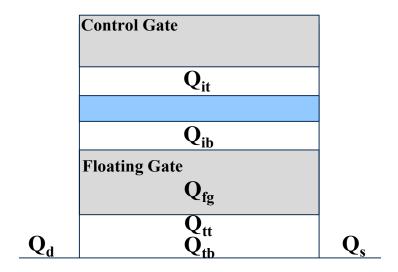

Fundamental physical limits have led to a reduction in the number of electrons that are stored per bit in the floating-gate, resulting in a discreteness of the cell state in NAND flash memory strings. Table I and Fig. 1.2 show the locations of the charge in the floating-gate flash memory cell as well as the number of electrons required to produce a shift of 100 mV in the threshold voltage ( $\Delta V_{th}$ ) at each location as a function of the technology node [3]. As

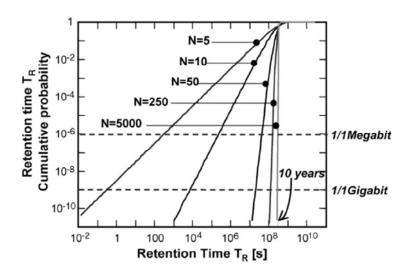

shown in Fig. 1.2, the number of electrons that produce a  $\Delta V_{\rm th}$  of 100 mV are dramatically reduced as the devices are scaled further down, and the  $V_{\rm th}$  of the cell becomes more sensitive to a charge trapped in each location. In addition, a severe failure can occur during cell state verification if a charge loss from floating-gate occurs during the read operation. Fig. 1.3 shows the cumulative probability of the retention time for the floating-gate flash memory with a reduced number of electrons per bit [4]. As the devices are scaled down, the impact of a single electron has a tremendous influence on the retention characteristics because the amplitude of  $\Delta V_{\rm th}$  due to a single electron increases.

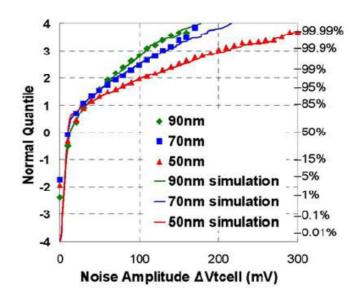

Random telegraph noise (RTN) causes a capture/emission of an electron at a trap site, and it has become a critical issue for NAND flash memory because it can cause an error during read operations that will make the memory become unreliable. The effect of RTN is known to be more severe in floating-gate NAND flash memories because they have a thicker tunnel oxide relative to other CMOS devices. The effect of RTN would be more significant in a device that is scaled down, and the  $\Delta V_{th}$  reported as a result of RTN was of ~0.3 V in 50 nm NAND flash memory, as shown in Fig. 1.4. [6]. Since there is a positional effect in a NAND cell string, a cell located closer to the bit-line has a higher  $\Delta V_{th}$  due to the RTN because it has a lower trans-conductance due to a higher equivalent source resistance [7]. Furthermore, the power of the low-frequency noise (LFN) and the  $\Delta V_{th}$  of a cell string have been reportedly influenced by the state of the

cells in the bit-line (BL) direction, the bias conditions, and the program/erase (P/E) cycling [8], [9].

Fig. 1.1. (a) Parasitic effects on distribution of  $V_{\rm th}$  in NAND flash memory [2]. (b)  $\Delta V_{\rm th}$  due to parasitic effects as a parameter of the technology node [3].

Fig. 1.2. Locations of charge in a floating-gate flash memory cell [4].

|                           | 50 nm | 35 nm | 20 nm |

|---------------------------|-------|-------|-------|

| Qtb                       | 4     | 2     | 1     |

| Qtt                       | 9     | 7     | 4     |

| Qib                       | 22    | 17    | 9     |

| Qit                       | 149   | 103   | 100   |

| $\mathbf{Q}_{\mathbf{s}}$ | 33    | 9     | 5     |

| $\mathbf{Q}_{\mathbf{d}}$ | 61    | 16    | 10    |

| $Q_{fg}$                  | 18    | 12    | 10    |

Table I. Number of electrons required for threshold voltage shift ( $\Delta V_{\rm th}$ ) of 100 mV at each location as a function of the technology node [4].

Fig. 1.3. Cumulative probability of retention time of floating-gate memories with reduced number of electrons per bit [5]

Fig. 1.4. Cumulative distributions of  $\Delta V_{\text{th}}$  due to RTN at each technology node in NAND flash memory [6].

## 1.2 Motivation and organization

As previously mentioned, reliability issues are one of the major concerns that arise when scaling down technology, so extensive research has focused on addressing the reliability of such devices, particularly for RTN due to traps in the insulator of the cell. Previous studies have usually observed a distribution in  $\Delta V_{\rm th}$  due to RTN when scaling down and have focused on extracting the trap location in the tunneling oxide of a cell. However, such studies have investigated the characteristic of RTN without considering the effects of the channel resistance of the pass cells and the adjacent bit-line cell interference, which originates from the characteristic of the NAND structure. Therefore, it is necessary to study the RTN in NAND flash memory by considering these effects. In addition, reliability problems and their causes due to traps in the inter-poly dielectric (IPD) are studied since no other paper has presented a systematic report that investigates these cases in NAND flash memory with a  $SiO_2/Si_xN_y/SiO_2$  (ONO) stack as the IPD, even if the ONO stack is still used as the IPD by the industry.

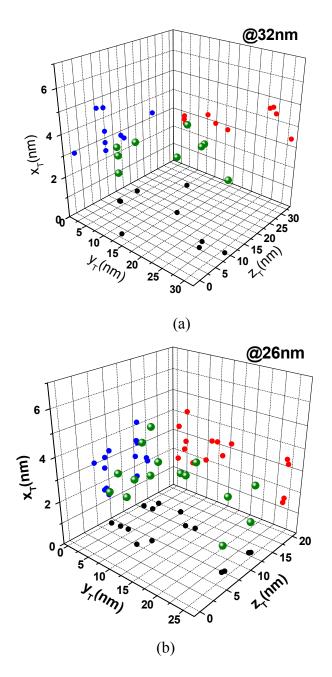

This dissertation consists of the following four chapters. In Chapter 2, the trap positions ( $x_T$  and  $y_T$ ) that cause channel resistance in the pass cells are obtained. Chapter 3 discusses the effects of the adjacent bit-line cell interference on RTN in NAND flash memory and also determines the trap position along the

channel width direction ( $z_T$ ). The  $x_T$ ,  $y_T$  and  $z_T$  of the traps, which are obtained for 32 nm and 26 nm NAND flash memory cell strings, are illustrated in a 3-D plot. In Chapter 4, we propose a new read method that reduces the effects of  $\Delta I_{\rm BL}$  due to RTN. In Chapter 5, the hysteresis phenomenon due to the traps in the IPD is introduced and is systematically investigated through a pulsed I-V and a fast transient bit-line current ( $I_{\rm BL}$ ) measurement in the NAND flash memory strings.

The Appendix at the end of the dissertation provides an explanation of the modeling used for the bit-line current fluctuation ( $\Delta I_{\rm BL}$ = high  $I_{\rm BL}$  – low  $I_{\rm BL}$ ) due to RTN, by considering the bit-line interference in the NAND flash memory.

# Chapter 2

# Extraction of trap profiles considering channel resistance of pass cells

#### 2.1 Introduction

As scaling down in the flash memory cell, random telegraph noise (RTN) leads to broaden threshold voltage distribution [3]. Especially in a NAND flash memory string, there is a cell position dependence of threshold voltage change ( $\Delta V_{th}$ ) due to the RTN [10]. This indicates that the channel resistances of pass cells in a cell string are affecting to RTN characteristics of a selected cell. Until now, trap positions from the channel surface to the floating-gate ( $x_T$ ) and along channel length direction ( $y_T$ ) has never been tried to extract with considering channel resistances of pass cells. In this work, we extracted the exact position and energy of a trap with considering channel resistances of pass cells for the first time.

#### 2.2 Device structure and measurement method

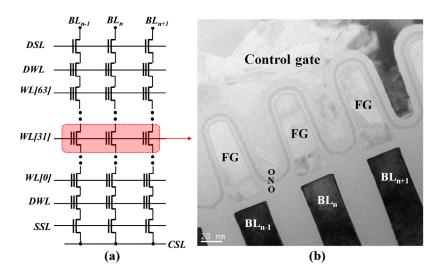

The floating-gate NAND flash memory in this work was fabricated at a semiconductor company by applying 32 nm and 48 nm technology. As shown in Fig. 2.1 (a), a 32 nm NAND string consists of sixty-four unit cells, two dummy cells, a drain select line (DSL) transistor and a source select line (SSL) transistor. The cross-sectional TEM view of the 32 nm NAND flash memory cells in the WL direction is shown in Fig. 2.1 (b). Cells of NAND flash memories in this work have nearly the same channel length (L) and width (W). Tunneling oxide thickness is 8.7 nm, and inter-poly O/N/O layer has a stack of 4/4/6 nm.

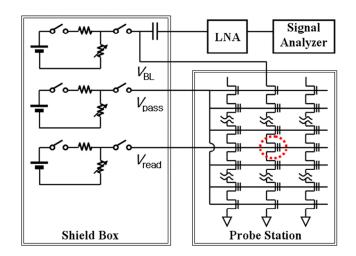

The block diagram of noise measurement system is represented in Fig. 2.2. To observe the bit-line current fluctuation ( $\Delta I_{\rm BL}$ = high  $I_{\rm BL}$  – low  $I_{\rm BL}$ ) exactly, the biases are applied to Word-Lines (WLs) and Bit-Line (BL) in the string by using a DC power source (batteries are shielded by grounded metal box). The  $\Delta I_{\rm BL}$  is amplified by the low-noise amplifier (LNA) and is displayed on the dynamic signal analyzer (Agilent 35670A).

Fig. 2.1. (a) Schematic view of NAND flash memory strings and (b) Cross-sectional TEM view of 32nm NAND flash memory cells in the WL direction.

Fig. 2.2. Block diagram of the low frequency noise measurement system. The selected cell is represented by a dotted circle. Control-gate bias ( $V_{\rm CG}$ ) and  $V_{\rm pass}$  were applied to the WL of a selected cell and unselected cells in the string, respectively.

# 2.3 Equations of trap profiles in a NAND flash memory string

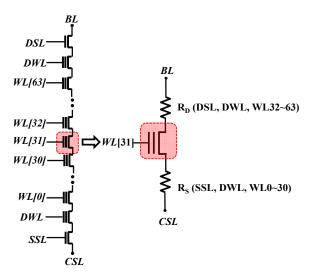

Fig.2.3 shows the schematic circuit diagram showing three NAND cell strings and an equivalent circuit of a string when a cell is read. A NAND string can be analyzed with an equivalent circuit shown in of Fig. 2.3. When we read a cell in a cell string by applying a read voltage to the WL corresponding to the read cell, pass cells biased by a pass voltage ( $V_{pass}$ ) have channel resistances. For this reason, the pass cells except a read cell can be modeled as linear resistors [11]. When we read a cell in the string, remaining pass cells become equivalent resistance which gives significant error in extracting RTN profile (position and energy).

Fig. 2.3. Schematic circuit view of a NAND cell string and its equivalent model.

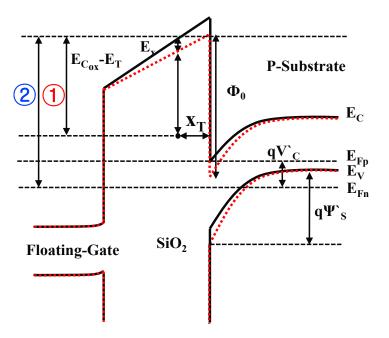

As the control gate voltage increases, potential drops at the drain and source of a read cell gradually increase due to voltage drop across the channel resistances of pass cells. So, the surface potential ( $\Psi_s$ ) slightly increases by the source voltage ( $V_s$ ) and the channel potential ( $V_c$ ) decreases due to voltage drop across the channel resistances of pass cells. Fig. 2.4 shows the energy band diagram of a read cell, which is used to extract the trap profile of a trap in the tunnel oxide. This figure includes the effect of source voltage ( $V_s$ ) and channel potential variation ( $dV_c/dV_{GB}$ ) due to the channel resistances of pass cells.

Fig. 2.4. Energy band diagram including the effect of the channel resistance of pass cells.

In order to extract the trap profiles, the relationship between time constants and trap energy level usually is used as following Eq. (2.1),

$$\frac{\tau_c}{\tau_e} = g \cdot \exp\left(\frac{E_T - E_F}{k_B T}\right)$$

Eq. (2.1)

where, g is the degeneracy factor, k is the Boltzmann constant, T is the temperature,  $\tau_c$  and  $\tau_e$  are the mean capture and emission time, respectively,  $E_T$  is trap energy level and,  $E_F$  is Fermi energy level. Eq. (2.1) can rewrite Eq. (2.2) as,

$$k_{B}T \ln \frac{\tau_{c}}{\tau_{e}} = \left[ \varphi_{0} - q\psi_{s} - qV_{C} + (E_{C} - E_{Fp} + qV_{C}) \right]$$

$$- \left[ q \frac{x_{T}}{T_{ox}} \left( V_{GS} - V_{FB} - \psi_{p} - \psi_{s} - V_{C} \right) + (E_{Cox} - E_{T}) \right]$$

Eq. (2.2)

where,  $E_{\text{Cox}}$  is the conduction band edge of the oxide,  $E_{\text{C}}$  is the conduction band edge of silicon,  $\varphi_0$  is the difference between the electron affinities of silicon and SiO<sub>2</sub>,  $V_{\text{FB}}$  is the flat-band voltage,  $x_{\text{T}}$  is the trap position from the channel surface to the floating-gate and  $T_{\text{ox}}$  is the tunneling oxide thickness.

In a NAND flash memory cell string, the drop of potential at drain and source side of a cell gradually occurs as increasing  $V_{CG}$  due to  $R_S$  and  $R_D$ . So,  $\Psi_S$

slightly increases as increasing  $V_{\rm S}$ . Using approximation of gradual  $V_{\rm C}$ , the term of  $V_{\rm C}$  is also dependent of  $V_{\rm GB}$  because  $V_{\rm C}$  can express as  $[y_{\rm T}\{V_{\rm D}-I_{\rm D}(R_{\rm S}+R_{\rm D})\}]/L_{\rm eff}$ . Here,  $y_{\rm T}$  and  $L_{\rm eff}$  are the trap position along channel length direction and the effective gate length, respectively. Consequently,  $d\ln(\tau_{\rm c}/\tau_{\rm e})/dV_{\rm GB}$  is represent by Eq. (2.3),

$$\frac{d \ln \frac{\tau_c}{\tau_e}}{dV_{GB}} = -\frac{1}{k_B T} \left[ \frac{d\psi_{S0}}{dV_{GB}} + q \frac{x_T}{T_{ox}} \left( 1 - \frac{d\psi_p}{dV_{GB}} - \frac{d\psi_{S0}}{dV_{GB}} - \frac{dV_s}{d(V_{GB})} - \frac{dV_C}{dV_{GB}} \right) \right]$$

Eq. (2.3)

Where, where g is the degeneracy factor, k is the Boltzmann constant, T is the temperature,  $\tau_c$  and  $\tau_e$  are the mean capture and emission time, respectively,  $E_T$  is trap energy level and,  $E_F$  is Fermi energy level. From the Eq. (2.3),  $x_T$  can express as Eq. (2.4) and Eq. (2.5).

$$x_{T} = \frac{\left(\frac{kT}{q} \left(\frac{d \ln \frac{\tau_{c}}{\tau_{e}}}{d (V_{GB})}\right) + \left(\frac{d \psi_{S}}{d (V_{GB})}\right)_{f}\right)}{\left(\left(\frac{d V_{C\_forward}}{d (V_{GB})}\right)_{f} + \left(\frac{d \psi_{P}}{d (V_{GB})}\right)_{f} + \left(\frac{d \psi_{S}}{d (V_{GB})}\right)_{f} + \left(\frac{d V_{S}}{d (V_{GB})}\right)_{f} - 1\right)}$$

Eq. (2.4)

$$x_{T} = \frac{\left(\frac{d \ln \frac{\tau_{c}}{\tau_{e}}}{d (V_{GB})}\right)_{r} + \left(\frac{d \psi_{s}}{d (V_{GB})}\right)_{r}}{\left(\left(\frac{d V_{C\_reverse}}{d (V_{GB})}\right)_{r} + \left(\frac{d \psi_{p}}{d (V_{GB})}\right)_{r} + \left(\frac{d \psi_{s}}{d (V_{GB})}\right)_{r} + \left(\frac{d V_{s}}{d (V_{GB})}\right)_{r} - 1\right)} \qquad \text{Eq. (2.5)}$$

where,  $V_{\text{C\_forward}}$  is the channel potential of a selected cell when selected BL and common source line (CSL) are biased to  $V_{\text{CC}}$  and ground, respectively, and  $V_{\text{C\_reverse}}$  is the channel potential of a selected cell when selected BL and common source line (CSL) are biased to ground and  $V_{\text{CC}}$ , respectively. Here,  $V_{\text{C\_forward}}$  and  $V_{\text{C\_reverse}}$  can express as  $[y_T\{V_D-I_D(R_S+R_D)\}]/L_{\text{eff}}$  and  $[(L_{\text{eff}}-y_T)\{V_D-I_D(R_S+R_D)\}]/L_{\text{eff}}$ , respectively. So, we can obtain accurate  $x_T$  and  $y_T$  by solving these simultaneous equations.

## 2.4 Verification of proposed equations

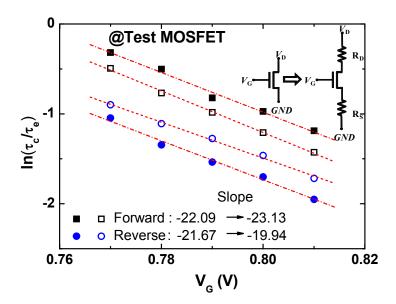

To verify clearly the effect of source potential variation ( $dV_S/dV_{GB}$ ) and channel potential variation ( $dV_C/dV_{GB}$ ) with gate bias, two resistors ( $R_S$ ,  $R_D = 20$  $k\Omega$ ) are connected to the drain and the source of an MOSFET (test device), respectively. The test device has L and W of 110 nm and 130 nm, respectively, and 2.5 nm thick SiO<sub>2</sub> as a gate insulator. Fig. 2.5 shows the changes of slope of  $\ln(\tau_c/\tau_e)$  with respect to gate bias  $(d\ln(\tau_c/\tau_e)/dV_{GB})$  in the test device. Solid symbols and open symbols stand for the value of  $\ln(\tau_c/\tau_e)$  in the device with and without the resistors, respectively. Square symbols and circle symbols represent the value of  $\ln(\tau_0/\tau_e)$  with the forward and reverse drain biases, respectively. When the resistors are connected to the test device,  $d\ln(\tau_c/\tau_e)/dV_{GB}$ s with the forward and reverse drain bias are changed as shown in Fig. 2.5. In Fig. 2.6, the  $d\ln(\tau_c/\tau_e)/dV_{GB}$  with the forward and reverse BL bias also changes in a cell of 48nm NAND flash memory string. From the results of Fig. 2.5 and Fig. 2.6, we can notice that the slope of  $\ln(\tau_c/\tau_e)$  are changed due to source potential variation and channel potential since  $d\ln(\tau_c/\tau_e)/dV_{GB}$  is a dominant parameter to extract the trap profile. So, the resistance effect should be considered when the trap profiles are extracted in a NAND flash memory string.

Fig. 2.5. Changes of  $d\ln(\tau_c/\tau_e)/dV_{GB}$  in a test MOSFET with and without series resistors.

Fig. 2.6. Changes of  $dln(\tau_c/\tau_e)/dV_{GB}$  in a cell of a NAND cell string with forward and reverse BL-bias.

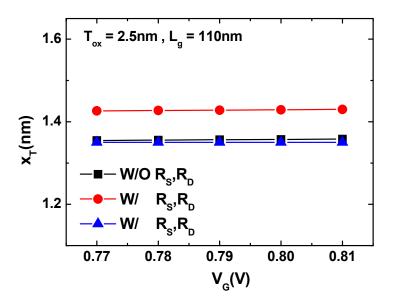

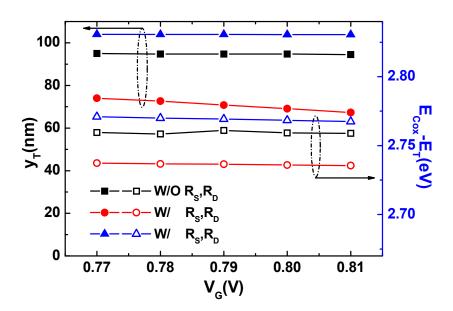

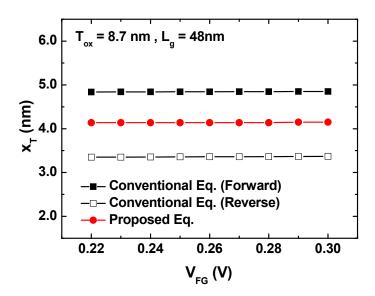

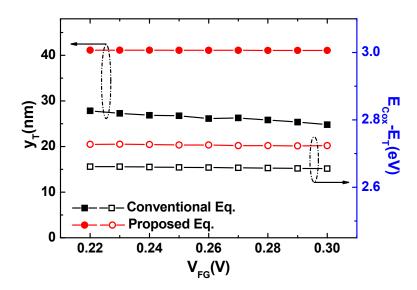

Figs. 2.7 and 2.8 compare  $x_T$ ,  $y_T$  and  $E_{COX}$ - $E_T$  extracted from conventional and proposed equations, respectively, in the test device with and without the resistors. The reference (exact) values are extracted by using conventional equation when Rs and  $R_D$  are not connected to the test device. As shown in Figs. 2.7 and 2.8,  $x_T$ ,  $y_T$  and  $E_{COX}$ - $E_T$  extracted by using proposed equations are more accurate than those from conventional equation. Thus we verified proposed equations are more accurate. Finally, Figs. 2.9 and 2.10 compare  $x_T$ ,  $y_T$  and  $E_{COX}$ - $E_T$  obtained from conventional and proposed equations in NAND flash memory strings.

Fig. 2.7.  $x_T$  extracted from conventional and proposed equation in a test MOSFET.

Fig. 2.8.  $y_T$  and  $E_{COX}$ - $E_T$  extracted from conventional and proposed equations in a test MOSFET.

Fig. 2.9.  $x_T$  extracted from conventional and proposed equation in a 48nm NAND flash memory string.

Fig. 2.10.  $y_T$  and  $E_{COX}$ - $E_T$  extracted from conventional and proposed equations in a 48nm NAND flash memory string.

# 2.5 Distribution of trap positions in tunneling oxide of NAND flash memory

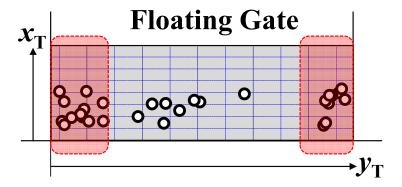

It is meaningful to study the distribution of position of traps responsible for RTN. We extracted the position of traps  $(x_T, y_T)$  by using the proposed equations. Fig. 2.11 shows the extracted  $x_T$  and  $y_T$  from process induced traps with 30 samples. We understand the traps are roughly located around both edges of the channel because of double etch damage during the fabrication and the negative charge buildup on the sidewall of the dielectric due to the ion sheath during the etch process, resulting in the bent of the trajectories of ions and their bombardment on the sidewall [12].

Fig. 2.11 Distribution of extracted trap position  $(x_T, y_T)$  of process induced traps in the tunneling oxide.

# Chapter 3

# Effect of bit-line interference on RTN in NAND flash memory

#### 3.1 Introduction

In a previous section, we introduced a methodology to extract the trap position by considering the effect of series channel resistance of pass cells. In this section, we focus on a detailed explanation about the effect of adjacent BL cell interference on a read cell by using 3-D TCAD simulation, and also measure the bit-line current fluctuation ( $\Delta I_{\rm BL}$ = high  $I_{\rm BL}$  – low  $I_{\rm BL}$ ) due to RTN of a read cell in a NAND flash cell string by changing state (program (P) or erase (E)) of adjacent BL cells in the word-line (WL) direction. In addition, we investigate the effect of adjacent BL cell interference on the relationship between  $\Delta I_{\rm BL}$  and the ratio of mean capture and emission time constants ( $\ln(\tau_c/\tau_e)$ ).

#### 3.2 Device structure and simulation condition

The floating-gate NAND flash memory in this work was fabricated at a semiconductor company by applying 32 nm technology and has the same structure as mentioned in the chapter 2. For 3-dimensional (3-D) device simulation, a NAND flash memory cell array which consists of one word-line (WL) and 3 BLs was prepared to have the same structure as the measured device. The cells in the simulation have channel length and width of 32 nm, tunneling oxide thickness of 7.9 nm, constant channel doping of  $2\times10^{17}$  cm<sup>-3</sup>, and peak source/drain doping of  $1\times10^{19}$  cm<sup>-3</sup>. The simulation data are obtained by solving the Poisson and drift-diffusion equations at the read condition (BL bias  $(V_{\rm BL})$ =0.5 V, control-gate bias for an  $I_{\rm BL}$  of 100 nA). Although the boron ion segregation depends on the process and following heat cycles, we assumed constant body doping in this work.

#### 3.3 Results of 3-D TCAD simulation

NAND flash memories are influenced by the severe cell-to-cell interference due to increased parasitic capacitances with the continued scaling of NAND flash memory beyond 50 nm [13]-[16]. The effect of adjacent BL cell's state (P or E) on the read cell (BL<sub>n</sub> cell) is investigated by using 3-D TCAD simulation.

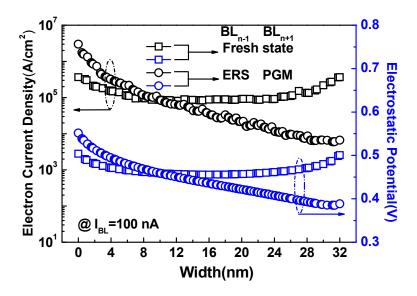

Since each of adjacent BL cells ( $BL_{n-1}$  and  $BL_{n+1}$  cells) has P or E state, we can consider four different modes (E/E, E/P, P/E, and P/P). Here, adjacent BL cells are programmed to have a  $V_{\rm th}$  of 3 V or erased to have a  $V_{\rm th}$  of -3 V. As shown in Fig. 3.1, a part of a control-gate in NAND flash memories is inserted between floating-gates of adjacent BL cells to increase the coupling ratio and minimize the floating -gate interference. And there is the tip effect at the edges in zdirection because the corner of the active area is sharp as shown in Fig. 3.1. Therefore the distribution of the electrostatic potential and electron current density  $(J_e)$  along the channel width direction (z-direction) in the read cell (particularly near the edges in z-direction) are influenced not only by the electric field from the floating-gate of adjacent BL cells but also by that from the recessed control-gate and the tip effect [17]. Before discussing the effect of adjacent BL cell's state on a read cell, we need to investigate the effect of the electric-field from the recessed control-gate on the read cell. To see the effect, the distribution of electrostatic potential and  $J_{\rm e}$  in a read cell was checked by changing the state of adjacent BL cells. Fig. 3.1 shows simulation results depicting the electrostatic potential and  $J_{\rm e}$  of a read cell when adjacent BL cells are in a fresh state (zero net charge in the floating-gate) or E/P mode. Here, the read cell was controlled to have a V<sub>th</sub> of nearly 0 V by which a WL bias of 0 V is applied to the control-gate of the read and two adjacent BL cells during read operation. By doing so, the electric field from the recessed control-gate can be

minimized, which minimizes the channel modulation of the read cell. Consequently, we can observe clearly the effect of the state of adjacent BL cells. The distribution of electrostatic potential and  $J_e$  is extracted at 1 Å below the channel surface along the z-direction when  $I_{\rm BL}$  is 100 nA at a given BL bias ( $V_{\rm BL}$ ) of 0.5 V. As shown in Fig. 3.1, the  $J_e$  and electrostatic potential at the channel edge region are slightly increased due to the tip effect and the effect of the electric field from the recessed control-gate when adjacent BL cells are in a fresh state. But, we can notice that the electric field from the floating-gate of adjacent BL cells is more dominant by comparing the electrostatic potential and  $J_e$  in the fresh state with those in E/P mode when a  $V_{\rm th}$  of the read cell is nearly 0 V [16].

Fig. 3.1. Simulated electrostatic potential and  $J_e$  of a read cell along the channel width (z) direction when adjacent BL cells are in a fresh state or in E/P mode, respectively.

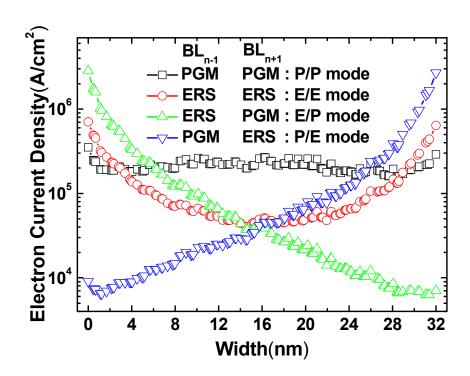

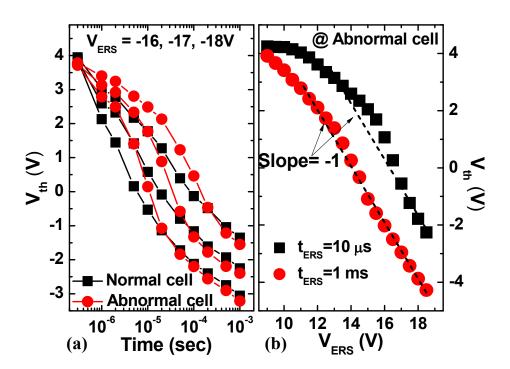

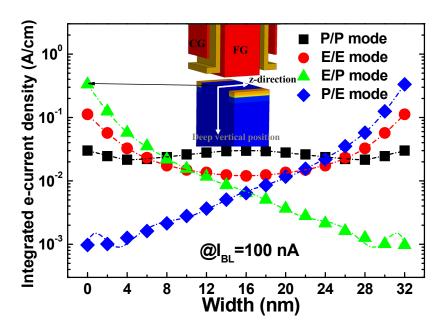

Fig. 3.2 shows the simulated distribution of  $J_e$  along the z-direction with 4 different modes of the state of adjacent BL cells. Each distribution of  $J_e$  is extracted at 1 Å below the surface along the z-direction when  $I_{BL}$  is 100 nA at a given  $V_{BL}$  of 0.5 V. From the results of Fig. 3.2,  $J_e$  along z-direction in a read cell is changed significantly with the state of adjacent BL cells. Since the distance between the channel of a read cell and the floating-gate of adjacent BL cells is so close, the distribution of  $J_e$  along the z-direction in the read cell is directly changed by the electric field from the floating-gate of adjacent BL cells when adjacent BL cells are programmed or erased [13]-[17]. For example,  $J_e$  of a read cell is crowded toward the BL<sub>n-1</sub> side (a position from the center to the left edge of the channel width) in z-direction as shown by open triangles in Fig. 3.2 when BL<sub>n-1</sub> and BL<sub>n+1</sub> cells are erased and programmed, respectively.

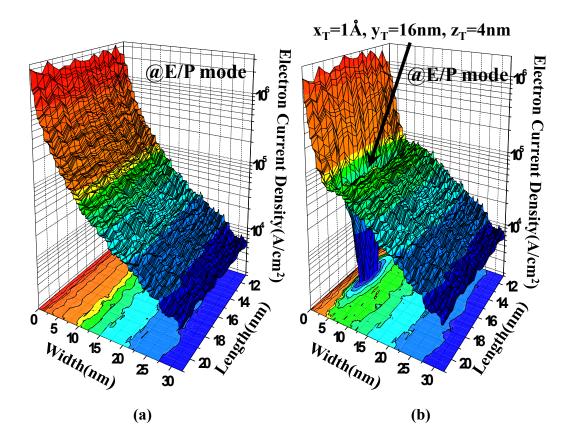

Fig. 3.3 (a) and (b) show the distribution of  $J_e$  without and with a trapped electron in E/P state as an example, respectively. Here, the trap position from the channel surface to the floating-gate  $(x_T)$ , the trap position along the channel length direction  $(y_T)$ , and a trap position along the channel width direction  $(z_T)$  are 1 Å, 16 nm, and 4nm, respectively. Bias conditions in Fig. 3.3 are exactly the same as those in Fig. 3.2. When an electron is captured into a trap in the tunneling oxide,  $J_e$  under a trapped electron decreases dramatically as shown in Fig. 3.3 (b), which leads to the decrease of  $I_{BL}$ .

Fig. 3.2. Simulated distribution of  $J_e$  along the z-direction with four different modes of the state of adjacent BL cells. Each distribution of  $J_e$  is extracted at 1 Å below from the channel surface along the z-direction.

Fig. 3.3. Simulated distribution of  $J_e$  (a) without and (b) with an electron trap in the tunneling oxide when adjacent BL cells are in E/P mode. Here,  $x_T$ ,  $y_T$ , and  $z_T$  are 1 Å, 16 nm, and 4 nm, respectively.  $J_e$  is extracted at 1 Å below from the channel surface along the z-direction.

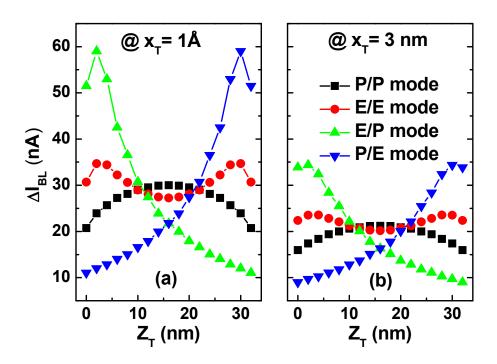

Fig. 3.4 (a) and (b) show the change of simulated  $\Delta I_{\rm BL}$  with  $z_{\rm T}$  as a parameter of the state of adjacent BL cells when  $x_T$  is 1 Å and 3 nm, respectively. The  $\Delta I_{\rm BL}$ s are obtained at an  $I_{\rm BL}$  of 100 nA. Bias conditions are exactly the same as those in Fig. 3.2. From the results of Figs. 3.2 and 3.4, we can understand that an electron trap existing above higher  $J_{\rm e}$  region gives the larger  $\Delta I_{\rm BL}$  at a fixed  $x_{\rm T}$ . A trap located closer to the surface makes the larger  $\Delta I_{\rm BL}$  at a fixed  $z_{\rm T}$ . Thus the state of adjacent BL cells can control a sort of percolation path (~high  $J_e$  region) along z-direction and the  $\Delta I_{BL}$  of a read cell becomes a maximum value when the path is aligned to  $z_T$ . There were several reports that a trap which is closely located above a percolation path increases the amplitude of RTN [18]-[19]. For example, when an electron trap is located near  $z_{\rm T}$  of 0 nm, the E/P mode gives much larger  $\Delta I_{\rm BL}$  than the P/E mode because E/P mode makes a percolation path near  $z_T$  of 0 nm as shown by open triangles in Fig. 3.2. Furthermore, the effect of random dopant fluctuations (RDF) which leads to the percolation path in the channel has been studied by using the "atomistic" doping method and the RDF is the important to analyze the characteristics of RTN in the nano-scale devices. [20], [21]. Because the simulation was done with the continuous doping in this work, the distribution of  $\Delta I_{\rm BL}$ s as shown in Fig. 3.4 can be changed if we include the effect of RDF. We predict that maximum  $\Delta I_{\rm BL}$  for each mode will be increased when the effect of adjacent bit-line interference is superimposed on the effect of RDF.

Fig. 3.4. Simulated  $\Delta I_{\rm BL}$  with a trap position ( $z_{\rm T}$ ) along the z-direction as a parameter of the state of adjacent BL cells when the trap position ( $x_{\rm T}$ ) from the channel surface to the floating-gate is 1 Å (a) and 3 nm (b).

# 3.4 RTN measurement results with the state of adjacent bit-line cells

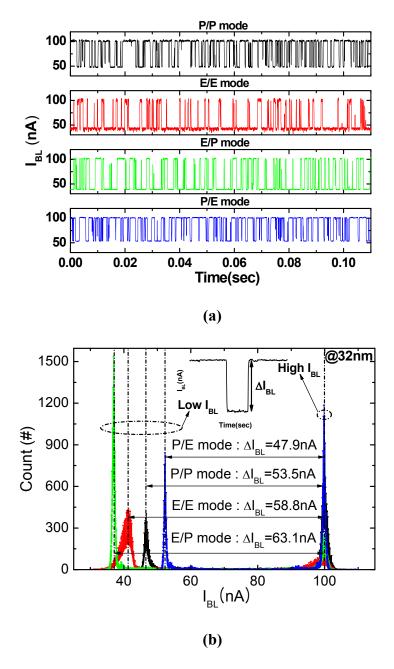

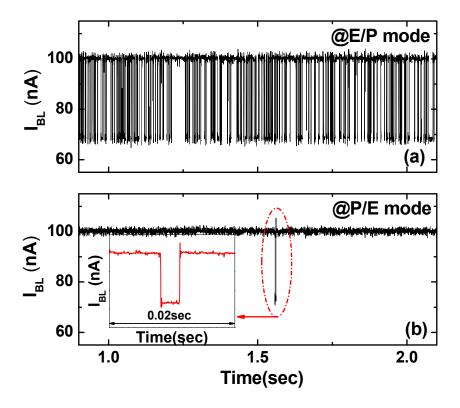

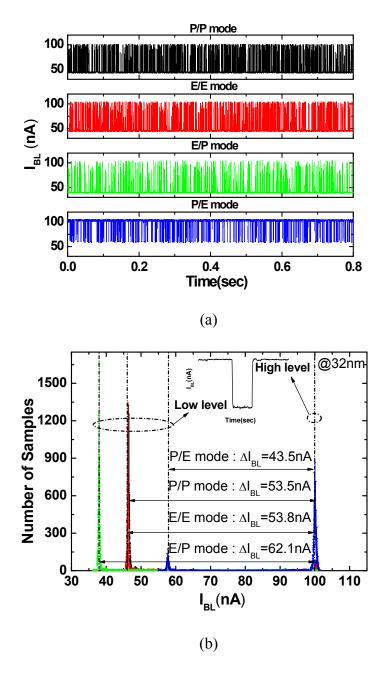

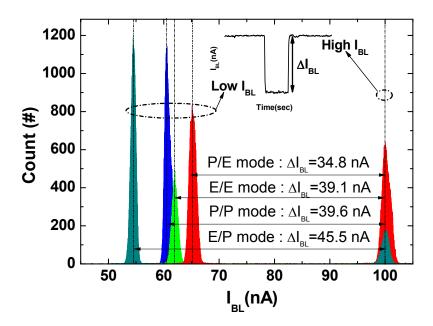

Fig. 3.5 shows an example of measured  $\Delta I_{\rm BL}$  with the state of adjacent BL cells in a 32 nm NAND flash memory cell string. Fig. 3.5 (a) shows the  $\Delta I_{\rm BL}$  of a

read cell with 4 different modes of the state of adjacent BL cells in time domain. Fig. 3.5 (b) shows the distribution of  $\Delta I_{\rm BL}$  extracted from the results of Fig. 3.5 (a). The inset of Fig. 3.5 (b) represents a part of measured RTN waveform where the low  $I_{\rm BL}$  is changed with the state of adjacent BL cells. Here, low and high  $I_{\rm BL}$ s correspond to the capture and emission of an electron at a trap, respectively. To observe the effect of adjacent BL cell interference on  $\Delta I_{\rm BL}$  due to RTN, the adjacent BL cells are programmed to have a  $V_{th}$  of 3 V or erased to have a  $V_{th}$  of -3 V. The read cell is set to have a  $V_{\rm th}$  of 0 V. Here, high  $I_{\rm BL}$  was fixed at 100 nA by controlling the control-gate bias of the read cell at a  $V_{\rm BL}$  of 0.8 V and a pass bias ( $V_{\text{pass}}$ ) of 6.5 V. In this example,  $\Delta I_{\text{BL}}$  due to RTN ranges from ~48 nA to ~63 nA with 4 different modes of the state of adjacent BL cells. From the result in Fig. 3.5,  $\Delta I_{\rm BL}$  increases by about 30 % when the mode of adjacent BL cells is changed from P/E mode to E/P mode. We can notice that the trap responsible for the  $\Delta I_{\rm BL}$  behavior in Fig. 3.5 is estimated roughly to be located near the BL<sub>n-1</sub> side in z-direction by considering the results of Figs. 3.4 and 3.5. As the cell size scales down further, the change of  $\Delta I_{\rm BL}$  would be more severe due to the increased interference of adjacent BL cell when the state of adjacent BL cells changes.

Fig. 3.5. (a) Measured  $\Delta I_{\rm BL}$  of a read cell with four different modes of the state of adjacent BL cells in time domain and (b) distribution of  $\Delta I_{\rm BL}$  extracted from the results of Fig. 3.5 (a).

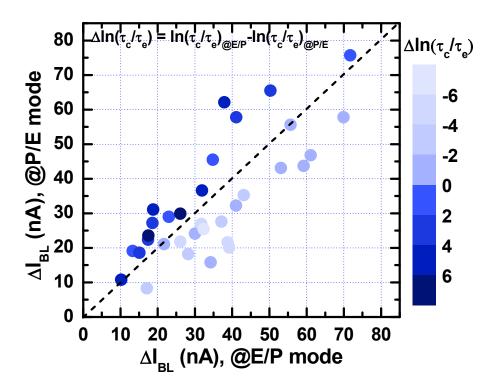

Fig. 3.6 shows the  $\Delta I_{\rm BL}$  relationship between E/P and P/E modes extracted from 33 cells in 32 nm NAND flash memory strings. The strength of color of circular symbol shows the  $\Delta \ln(\tau_c/\tau_e)$ , which is to subtract the  $\ln(\tau_c/\tau_e)$  in P/E mode from that in E/P mode. Bias condition for measurement is the same as that mentioned in Fig. 3.5. The dashed line represents the point where the  $\Delta I_{\rm BL} {\rm s}$  in E/P and P/E modes are the same. For example, a symbol is located below the dashed line when the  $\Delta I_{\rm BL}$  in E/P mode is larger than that in P/E mode. By comparing the simulation result in Fig. 3.4 with the measured result in Fig. 3.6, we can notice that the percolation path exists in the channel of cells due to the intrinsic parameter fluctuation [22]. At least, the cells showing more than ~60 nA are affected by the percolation path. In Fig. 3.6, the strength of color of symbols below the dashed line is generally bright, which means the  $\ln(\tau_c/\tau_e)$ s in P/E mode are larger than those in E/P mode. From the result of Fig. 3.6, we can notice that the correlation between the  $\Delta I_{\rm BL}$  and  $\ln(\tau_{\rm c}/\tau_{\rm e})$  obviously exists with changing the state of adjacent BL cells.

For more detailed explanation of the results of Fig. 3.6, we prepared RTN of a read cell for both E/P and P/E modes as shown in Fig. 3.7. Bias condition for measurement is the same as those mentioned in Fig. 3.5. Here,  $\Delta I_{\rm BL}$ s in E/P mode and P/E modes are 32 nA and 26 nA, respectively. When the state of adjacent BL cells changes from E/P mode to P/E mode,  $\ln(\tau_{\rm c}/\tau_{\rm e})$  changes from 1.20 to 5.99. These results will be explained as follows. By considering the

results of Figs. 3.4 and 3.7, we can estimate that a trap which generates RTN in Fig. 3.7 is located near the  $BL_{n-1}$  side in *z*-direction.

Fig. 3.6.  $\Delta I_{\rm BL}$  relationship between E/P and P/E modes extracted from 33 cells in 32 nm NAND flash memory strings. The strength of color of circular symbol shows the  $\Delta \ln(\tau_{\rm c}/\tau_{\rm e})$ , which is to subtract the  $\ln(\tau_{\rm c}/\tau_{\rm e})$  in P/E mode from that in E/P mode. The dashed line represents the point where the  $\Delta I_{\rm BL}$ s in E/P mode and P/E mode are the same.

Fig. 3.7. Measured  $\Delta I_{\rm BL}$  due to RTN in the time domain when a read cell is in (a)E/P mode and (b) P/E mode, respectively. The inset of Fig. 3.7 (b) shows the magnified  $I_{\rm BL}$  versus time.

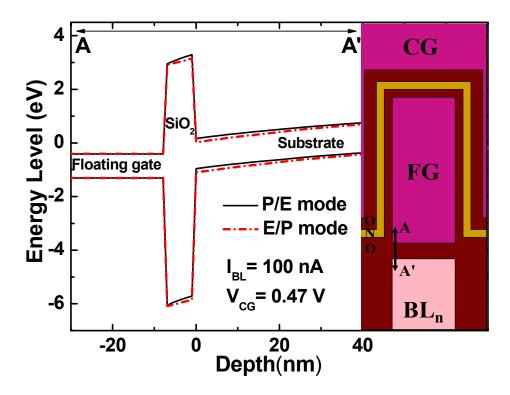

In order to explain this more detail, we prepare the energy band diagram of a read cell cut along A-A' (closer to BL<sub>n-1</sub>) in the inset of Fig. 3.8 when the read cell is in E/P and P/E modes as shown in Fig. 3.8. Here,  $V_{\rm BL}$  of the read cell is 0.5 V and  $I_{\rm BL}$  is adjusted to have 100 nA by controlling  $V_{\rm CG}$  ( $V_{\rm CG}$ =0.47 V) in both cases. In Fig. 3.8, the conduction and valence bands of the read cell in E/P

mode are more bended than those in P/E mode due to the increased electric field from the floating-gate of erased adjacent cell (BL<sub>n-1</sub> cell). Thus, the electric field from the floating-gate of adjacent BL cell has an direct influence on the difference between the trap energy level  $(E_T)$  and the Fermi level  $(E_F)$ , which leads to the change of  $\ln(\tau_c/\tau_e)$ . In this cell,  $E_T$  is quite close to  $E_F$  in E/P mode ( $E_{\rm T}$  -  $E_{\rm F}$   $\approx$ 31 meV), but higher than  $E_{\rm F}$  in P/E mode ( $E_{\rm T}$  -  $E_{\rm F}$   $\approx$ 156 meV). This change of  $\ln(\tau_c/\tau_e)$  due to the state of adjacent BL cells can lead to the significant error in NAND flash memory strings. Before shipping out NAND flash memories, failure tests, which is to check program or erase operation, charge loss, the distribution of  $V_{\rm th}$ , and etc should be done in the security block which stores the error correction code (ECC). In the case of Fig. 3.7, the capture event occurs much less frequently in P/E mode, which means that it is hard to detect the failed cell in the security block during the failure tests. From these results, it can be understood that the state of adjacent BL cells affects  $\Delta I_{\rm BL}$  and  $\ln(\tau_{\rm c}/\tau_{\rm e})$  in a cell at the same time. We can also roughly estimate  $z_T$  by using not only the behavior of  $\Delta I_{\rm BL}$  but also the behavior of  $\ln(\tau_{\rm c}/\tau_{\rm e})$ . When we correct the failed cells, it is needed to consider both  $\Delta I_{\rm BL}$  and  $\ln(\tau_{\rm c}/\tau_{\rm e})$  of the RTN, which are affected by the states of adjacent BL cells.

Fig. 3.8. Energy band diagram of a read cell cut along A-A' in the inset when the read cell is in E/P mode and P/E mode. The dash-dot line represents the diagram in E/P mode. The inset shows the simulation structure.

#### 3.5 3-D trap position in tunneling oxide

As mentioned in the section 3.4, the state of adjacent BL cells affects  $\Delta I_{\rm BL}$  due to RTN, which can be a key fingerprint to extract  $z_{\rm T}$ . When the adjacent cells are programmed or erased,  $J_{\rm e}$  distribution is changed along the z direction of the

read cell by bit-line interference. When a single electron is trapped at 1 Å from the channel surface,  $J_e$  under the trapped electron is changed dramatically. Due to the variation of  $J_e$  distribution with the states of adjacent cells, the  $\Delta I_{\rm BL}$  due to RTN in the read cell is affected at  $I_{\rm BL}$ . Here, the changes of  $\Delta I_{\rm BL}$  with the state of adjacent cells,  $x_{\rm T}$ , and  $z_{\rm T}$  are shown in Fig. 3.4. As shown in Fig. 3.3 and 3.4, a trapped electron inside the tunnel oxide existing above higher  $J_e$  region gives the larger  $\Delta I_{\rm BL}$ . For example, when a trapped electron is located near both edges of the channel width in E/P mode, the  $\Delta I_{\rm BL}$  for  $z_{\rm T}$ 0 nm is the larger than that near  $z_{\rm T}$ 32 nm due to asymmetric  $J_e$  distribution as shown by solid inverse triangles in Fig. 3.2. Comparing the result of Fig.3.4 with Fig. 3.9, the  $z_{\rm T}$  in this example can be roughly extracted (~8 nm).

By using the proposal equation as mentioned in the chapter 2 and the effect of adjacent bit-line interference, 3-D trap position can be extracted in NAND flash memory strings as shown in Fig. 3.10.

Fig. 3.9. (a) Measured  $\Delta I_{\rm BL}$  of a read cell with four different modes of the state of adjacent BL cells in time domain and (b) distribution of  $\Delta I_{\rm BL}$  extracted from the results of Fig. 3.9 (a).

Fig. 3.10. Distribution of extracted  $x_T$ ,  $y_T$  and  $z_T$  of traps in the tunneling oxide of (a) 32 nm and (b) 26 nm NAND flash memories (big dots). Small dots represent projected trap position on each plane (ex:  $y_T$ - $z_T$ )

## Chapter 4

# A new read method suppressing random telegraph noise

#### 4.1 Introduction

As mentioned in the chapter 2 and 3, Random telegraph noise (RTN) caused by electron capture/ emission at traps has been an issue as the device cell size scales down. The current fluctuation due to RTN can make serious problems, such as wide  $V_{\rm TH}$  distribution and device instability. Especially, tight control of  $V_{\rm TH}$  distribution of multi- level cell (MLC) NAND flash memory device is very important. There have been some reports to extract the position of trap generating RTN and to investigate current behavior with temperature (T) and gate bias [9], [23]. It is the best way to suppress completely the RTN so that we can reduce  $V_{\rm th}$  distribution greatly. However, there has been no report on a method to reduce or suppress RTN during read operation. In this work, we propose a new gate biasing scheme to read bit-line current ( $I_{\rm BL}$ ) during read

operation with extremely low probability of RTN, and investigate the RTN behavior for three different RTN cases.

#### 4.2 Device structure and measurement setup

The floating-gate NAND flash memory in this work was fabricated at a semiconductor company by applying 26 nm technology. The NAND flash memory string consists of sixty-four unit cells, two dummy cells, a drain select line (DSL) transistor and a source select line (SSL) transistor.

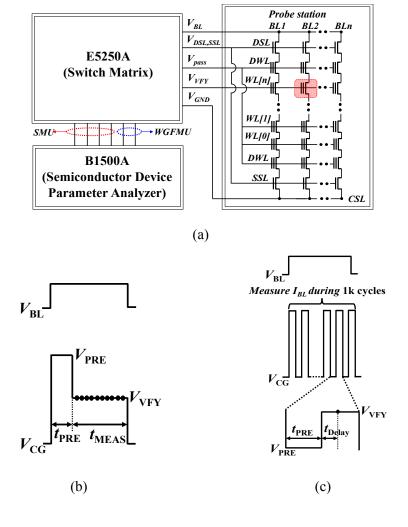

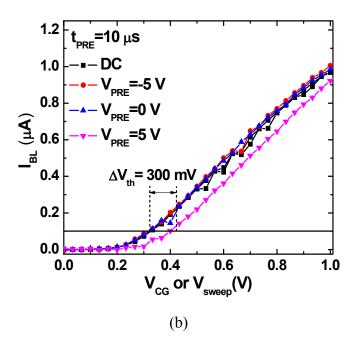

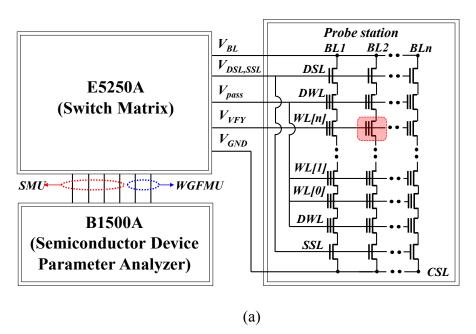

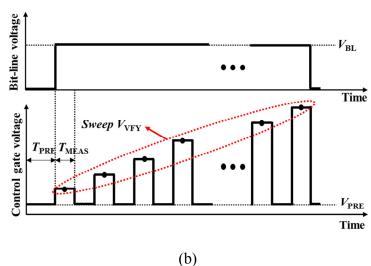

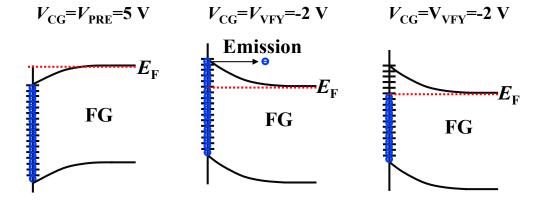

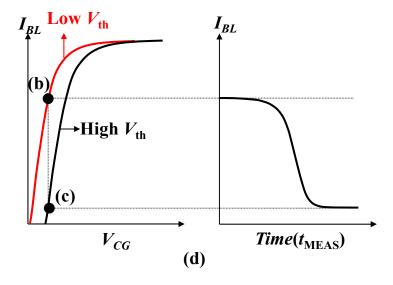

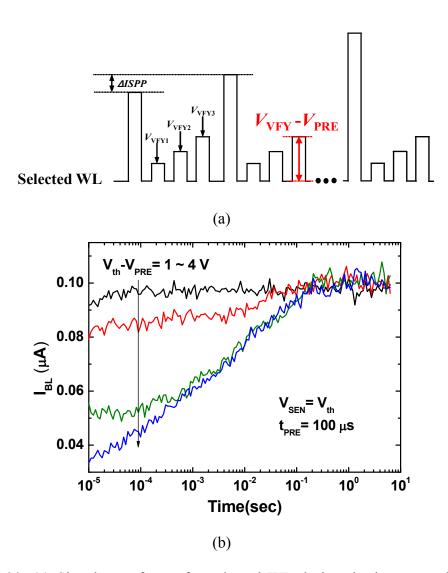

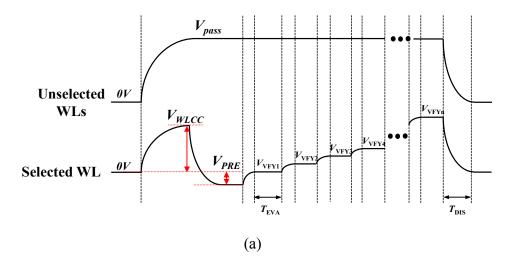

Since NAND flash memory strings actually are biased under dynamic signals during the short operation time ( $\sim \mu s$ ), it is appropriate to measure the electrical properties of trap in a short time. In order to observe the behavior of trap in a short time, the  $I_{BL}$  is set to be measured in  $\sim \mu s$  by using WGFMU modules that integrates arbitrary linear waveform generation capability with high-speed current and voltage measurement. The block diagram of pulsed I-V and fast transient  $I_{BL}$  measurement system is represented in Fig. 4.1 (a). To show the transient characteristic by adopting proposed reading method, the pulse waveform in Fig. 4.1 (b) is used. The  $V_{PRE}$  was applied to the control gate of a selected cell for  $t_{PRE}$  before read operation and then  $I_{BL}$  is measured at a  $V_{VFY}$  for  $t_{MEAS}$ .  $I_{BL}$  is measured by 1k times according to the method in Fig. 4.1 (c). A  $V_{read}$  is applied right after  $V_{PRE}$  is applied, and  $I_{BL}$  is sampled for  $1 \mu s$  after  $t_{delay}$ .

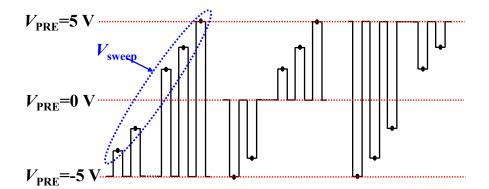

The  $I_{\rm BL}$  sampling is repeated by 1k times. Fig. 4.1 (d) shows the pulse waveform to measure pulsed I-V. The  $V_{\rm PRE}$  is applied to the control gate for  $t_{\rm PRE}$  before applying a sweep voltage ( $V_{\rm sweep}$ ). Then, the  $V_{\rm sweep}$  is applied and  $I_{\rm BL}$  is sampled. Here, we can control the  $V_{\rm PRE}$ , and use  $V_{\rm PRE}$ s of -5, 0 and 5V in this work as shown in Fig. 4.1 (d). Since read time is several  $\mu s$  in conventional NAND flash memory, B1530A module is used for measuring  $I_{\rm BL}$  and generating gate pulse in  $\mu s$  range.

Fig. 4.1. (a) Block diagram of the measurement system. The selected cell is represented by a red square. Pulse waveform of control gate bias voltage ( $V_{\rm CG}$ ) for (b) transient bit-line current ( $I_{\rm BL}$ ) measurement, (c) 1k times of  $I_{\rm BL}$  sampling at read bias ( $V_{\rm read}$ ) and (d) pulsed I-V measurement.

#### 4.3 Measurement results and discussion

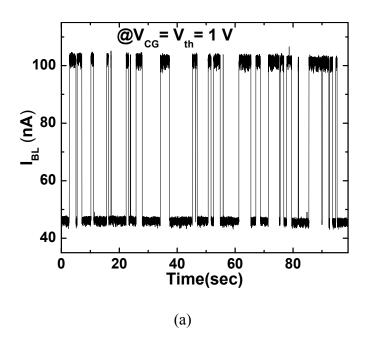

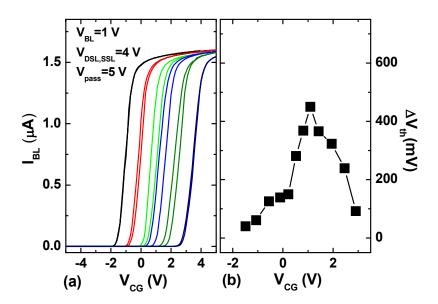

A cell with two level current fluctuation due to RTN shown in Fig. 2 (a) is measured at  $V_{\rm CG}=V_{\rm VFY}$ . In Fig. 2 (b), pulsed I-V curves show different  $V_{\rm th}s$  as  $V_{\rm PRE}$  changes due to hysteretic effect of RTN. Here,  $V_{\rm DSL,SSL}$ ,  $V_{\rm pass}$ , and  $V_{\rm BL}$  are 4 V, 5 V and 1 V, respectively.  $t_{\rm PRE}$  is 10  $\mu s$  and  $V_{\rm PRE}$  is changed to have -5 V, 0V, and 5 V. When  $V_{\rm PRE}$  is 5 V, the  $V_{\rm th}$  of a selected cell becomes higher compared to  $V_{\rm th}s$  of a selected cell when  $V_{\rm PRE}$  is -5 V or 0 V.

Fig. 4.2. (a) RTN waveform of  $I_{\rm BL}$  (b) DC and pulsed I-V curves with pre-bias voltage ( $V_{\rm PRE}$ ) (-5, 0 and 5 V).

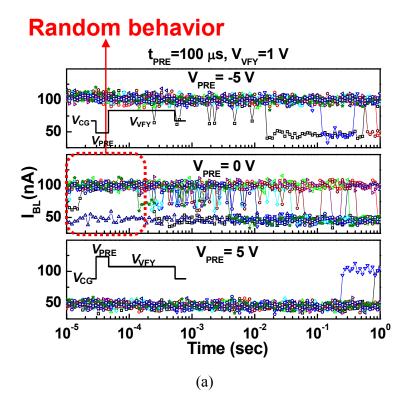

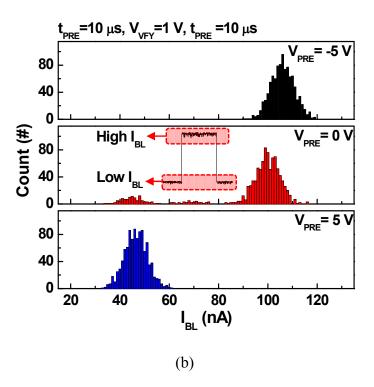

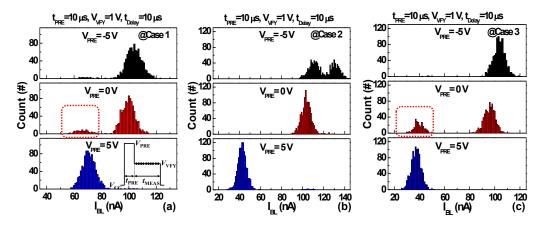

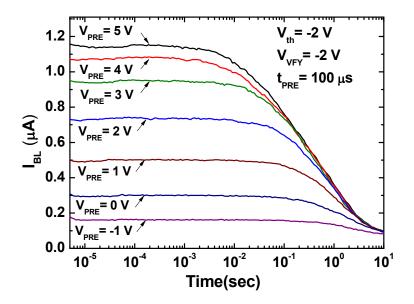

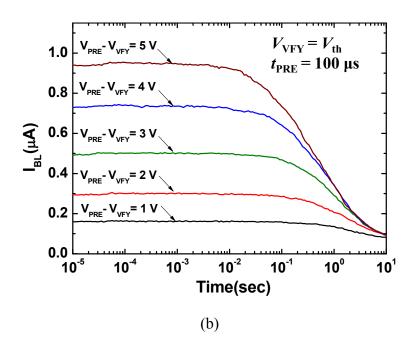

Fig. 4.3 (a) shows transient currents measured by 10 times at  $V_{\rm PRE}$ s of -5, 0 and 5V. The inset shows a pulse waveform showing  $V_{\rm PRE}$  and  $V_{\rm VFY}$  while the pulse is applied to the control gate. Here,  $t_{\rm PRE}$  and  $V_{\rm VFY}$  is 100  $\mu$ s and 1 V, respectively.  $V_{\rm DSL,SSL}$ ,  $V_{\rm pass}$ , and  $V_{\rm BL}$  are same conditions as mentioned in Fig. 4.2. Whereas the high or low level  $I_{\rm BL}$  appears randomly at a  $V_{\rm PRE}$  of 0 V, only high level and only low level  $I_{\rm BL}$  are observed at  $V_{\rm PRE}$ s of -5 and 5 V, respectively. Fig. 3 (b) shows histogram of 1k sampled  $I_{\rm BL}$ s at three  $V_{\rm PRE}$ s of -5, 0, and 5 V. Both  $t_{\rm PRE}$  and  $t_{\rm delay}$  are 10  $\mu$ s. At  $V_{\rm PRE}$ s of -5 and 5 V, only low or high level  $I_{\rm BL}$  distribution is observed. At a  $V_{\rm PRE}$  of 0 V, low and high level  $I_{\rm BL}$  distributions are observed although frequency count is different.

Fig. 3 (a) Transient  $I_{\rm BL}$  characteristics after  $V_{\rm CG}$  changes from  $V_{\rm PRE}$  to  $V_{\rm VFY}$ . (b) histogram of 1k sampled  $I_{\rm BL}$  with  $V_{\rm PRE}$  (-5, 0, 5 V). The inset shows the pulse waveform of  $V_{\rm CG}$ .

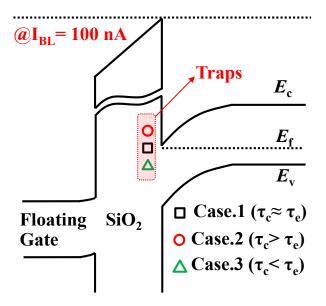

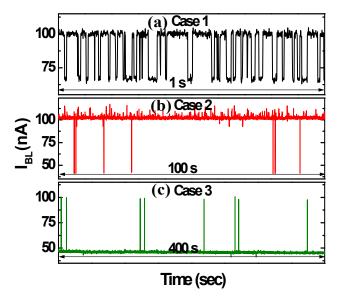

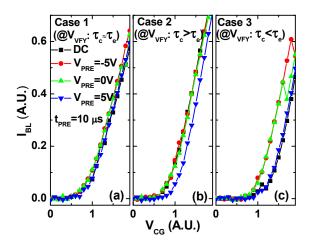

Proposed read method is applied in three cases related with the  $E_{\rm t}$  position relative to  $E_{\rm f}$  shown in Fig. 4.4. At a  $V_{\rm CG} = V_{\rm VFY}$ , cases 1, 2 and 3 represent  $E_{\rm T} \approx E_{\rm F}$ ,  $E_{\rm T} > E_{\rm F}$ , and  $E_{\rm T} < E_{\rm F}$ , respectively. Fig. 4.5 (a), (b) and (c) show the RTN waveforms measured in three different cells which represent cases 1, 2, and 3, respectively.

Fig. 4.4. Energy band diagram showing trap energy level ( $E_t$ ) in tunneling oxide as case 1, 2 and 3 at  $V_{CG}=V_{VFY}$ .

Fig. 4.5. RTN waveforms of  $I_{\rm BL}$  at  $V_{\rm CG} = V_{\rm VFY}$  in cases (a) 1, (b) 2 and (c) 3. In cases 1, 2 and 3.

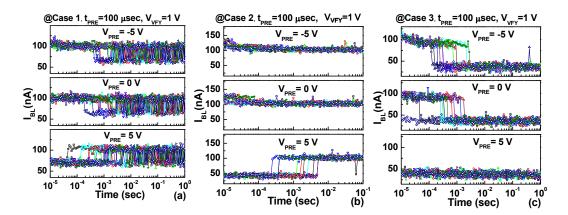

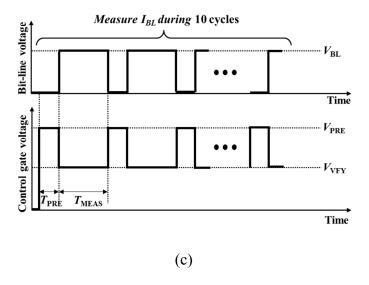

Fig. 4.6 shows the pulsed I-V curves in three cells which have different  $V_{th}$ s with the  $V_{PRE}$  in all cells. As the same result in Fig. 4.2, the hysteretic effect of RTN observed in all cases. Fig. 4.7 shows the transient  $I_{BL}$  characteristics with  $V_{PRE}$  in three cells. Here, transient  $I_{BL}$ s were measured by 10 times and for 100 ms at given a  $V_{PRE}$ .  $V_{PRE}$ s were applied to the control gate for 100  $\mu$ s. As a result of Fig. 4.7, random fluctuation of  $I_{BL}$  disappeared within the short time (~10  $\mu$ s). Fig. 4,8 show the histogram of 1k sampled  $I_{BL}$  with  $V_{PRE}$  (-5, 0, and 5 V) in cases (a) 1, (b) 2 and (c) 3. Here, both  $t_{delay}$  and  $t_{PRE}$  are 10  $\mu$ s. In three cases of Fig. 4.8, while only high  $I_{BL}$  distribution is observed at  $V_{PRE}$  = -5 V, only low  $V_{PRE}$  distribution is observed at 5 V. At a  $V_{PRE}$  of 0 V, high and low  $V_{PRE}$  are observed randomly. Applying sufficient high or low  $V_{PRE}$  before applying  $V_{VFY}$  can reduce the effect of RTN in three representative cases regardless of  $E_{T}$ .

Fig. 4.6. DC and pulsed I-V curves for cases 1, 2 and 3 with  $V_{PRE}$  (-5, 0 and 5 V).

Fig. 4.7. Transient  $I_{\rm BL}$  characteristics with  $V_{\rm PRE}$  (-5, 0, 5 V) in case (a) 1, (b) 2, and (c) 3. Here, transient  $I_{\rm BL}$ s were measured by 10 times and for 100 ms at given a  $V_{\rm PRE}$ .  $V_{\rm PRE}$ s were applied to the control gate for 100  $\mu$ s.

Fig. 4.8. Histogram of 1k sampled  $I_{BL}$  with  $V_{PRE}$  (-5, 0, and 5 V) in cases (a) 1, (b) 2 and (c) 3. Here, both  $t_{delay}$  and  $t_{PRE}$  are 10  $\mu$ s.

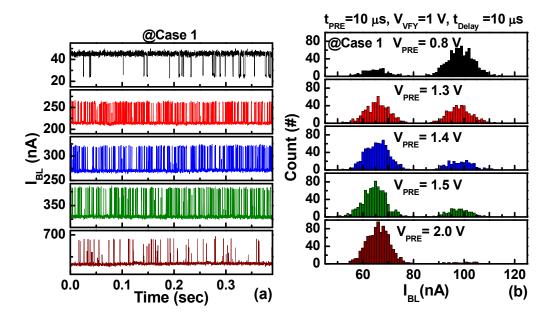

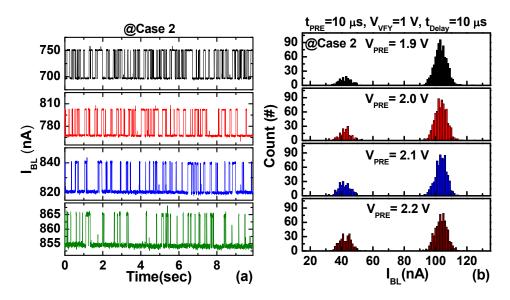

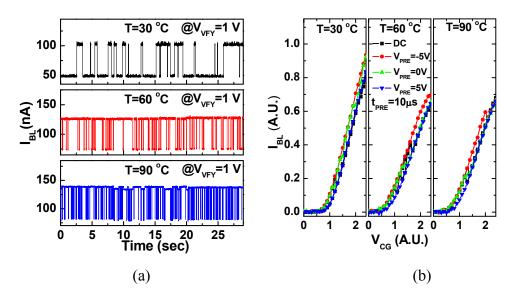

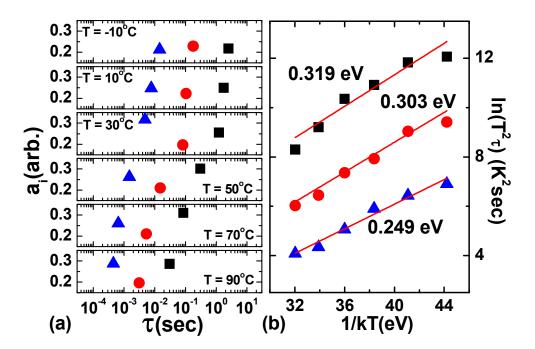

Figure (a) in Figs. 4.9-4.11 shows the dependency of  $\tau_c$  and  $\tau_e$  behavior on the  $V_{CG}$ . Here,  $V_{CG}$ s are controlled intentionally to change slightly  $E_T$  relative to  $E_F$ . Here, both  $t_{delay}$  and  $t_{PRE}$  are 10  $\mu$ s.  $V_{VFY}$  is 1 V. The  $\tau_c$  and  $\tau_e$  behavior in three (a)s of Figs. 4.9-4.11 show general DC characteristics of RTN with respect to  $V_{CG}$ . In three (b)s of Figs. 4.9-4.11, the frequency count of high or low  $I_{BL}$  changes as the  $V_{PRE}$  changes. At  $V_{PRE}$ s of Figs. 9-11,  $E_T$  is close to  $E_F$  in each case.

Fig. 4.9 (a) RTN waveforms of  $I_{BL}$  and (b) histogram of 1k sampled  $I_{BL}$  with  $V_{CG}$  (0.8, 1.3, 1.4, 1.5 and 2 V) in case 1.

Fig. 4.10 (a) RTN waveforms of  $I_{\rm BL}$  and (b) histogram of 1k sampled  $I_{\rm BL}$  with  $V_{\rm CG}$  (1.9, 2, 2.1 and 2.2 V) in case 2.

Fig. 4.11 (a) RTN waveforms of  $I_{\rm BL}$  and (b)  $I_{\rm BL}$  histogram of 1k sampled  $I_{\rm BL}$  with  $V_{\rm CG}$  (0.47, 0.52, 0.57 and 0.62 V) in case 3.

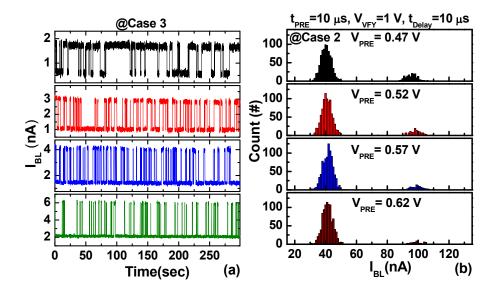

Fig. 4.12 (a), (b), and (c) compare  $\tau_c/\tau_e$  and frequency count ratio of high and low  $I_{\rm BL}$  as a parameter of  $V_{\rm PRE}$  in cases 1, 2, and 3, respectively. In case 1,  $\tau_c/\tau_e$  and the frequency count are similar. In case 2, the frequency count ratio is higher than  $\tau_c/\tau_e$ . In case 3,  $\tau_c/\tau_e$  is higher than frequency count ratio. This means that current fluctuation depends on not only  $V_{\rm PRE}$  but also  $V_{\rm VFY}$ .

Fig. 4.12  $\tau_c/\tau_e$  and frequency count ratio of high  $I_{\rm BL}$  and low  $I_{\rm BL}$  in cases (a) 1, (b) 2 and (c) 3.

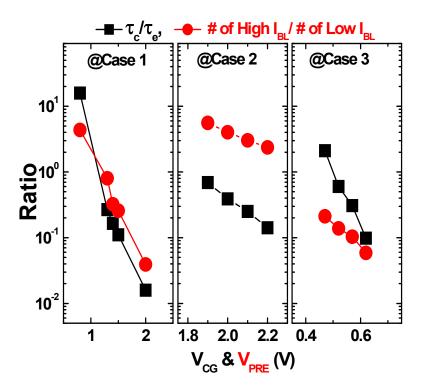

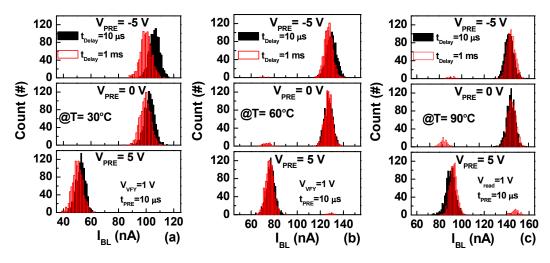

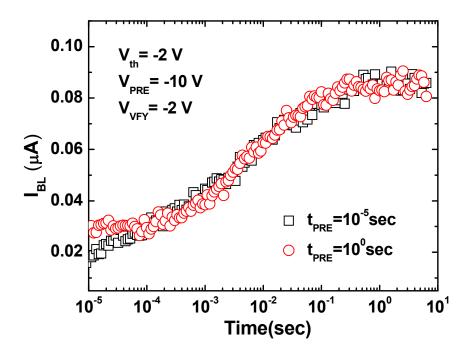

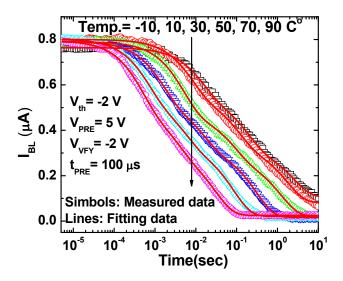

With increasing T,  $\tau_{\rm c}$  and  $\tau_{\rm e}$  becomes short at a  $V_{\rm VFY}$  as shown in Fig. 4.13 (a). Pulsed I-V curves plotted in Fig 4.13 (b) show different  $V_{\rm th}$ s with the  $V_{\rm PRE}$  at different Ts. Fig. 4.14 (a), (b), and (c) show histogram of 1k sampled  $I_{\rm BL}$  as parameters of  $V_{\rm PRE}$  and  $t_{\rm delay}$  at 30, 60, and 90 °C, respectively. Although  $\tau_{\rm c}/\tau_{\rm e}$  becomes short as T increases, the characteristic of high or low  $I_{\rm BL}$  distribution is not changed at the same  $V_{\rm PRE}$  compared to that at 300 K. When  $I_{\rm BL}$ s are sampled by 1k times after  $t_{\rm delay}$  of 1 ms, frequency count suppressed  $I_{\rm BL}$  level by a  $V_{\rm PRE}$  increases as T increases. From these results, by controlling the pre-bias in  $\sim$ µs range, it was confirmed that our method could suppress effectively the effect of RTN during read operation in NAND flash memory because  $I_{\rm BL}$  are sampled before changing the state of trap occupancy.

Fig. 4.13 (a) RTN waveforms of  $I_{\rm BL}$  at different temperatures (T) of 30, 60, and 90 °C, (b) DC and pulsed I-V characteristics as a parameter of  $V_{\rm PRE}$ .

Fig. 4.14 Histogram of 1k sampled  $I_{\rm BL}$  with  $V_{\rm PRE}$  as a parameter of and  $t_{\rm delay}$  at (a) 30, (b) 60, and (c) 90 °C.

### Chapter 5

# Hysteresis phenomena in floatinggate NAND flash memory

#### 5.1 Introduction

The continuous market needs for larger capacity of portable devices forces the floating-gate (FG) NAND flash memory to severely scale down its feature size. Furthermore, the multi-level-cell (MLC) operation becomes more common due to a lower cost per bit without scaling down. The aggressive reduction of the feature size of FG NAND flash memory cells and MLC operation lead to various problems such as cell-to-cell interference, reduction of on-cell string current, random telegraph noise, and etc [3], [24], [25]. Especially, Inter-poly dielectric (IPD) becomes the limitation of scaling down and MLC operation [26], because the reduced space between adjacent bit-line cells can no longer accommodate both IPD and the wrapped control-gate (CG) around FG which can increase the coupling ratio and minimize the FG interference. In order to solve this problem

while maintaining the cell performance, the shape of FG is changed to secure the sufficient geometrical area ratio between CG and FG, and the thickness of IPD should be reduced [13], [27], [28]. However, the geometry change of FG leads to the increased process complexity and cost per bit. And reduction of IPD thickness will inevitably cause the reliability issue such as the leakage current and data retention [28]. Therefore, high-k dielectric material, which will be able to increase the capacitance of IPD with a thick physical thickness, has been regarded as one candidate for solving these problems [29], [30]. However, highk materials have also a fatal problem due to the higher density of traps, which may increase the leakage current and degrade the retention characteristic due to trap-assisted tunneling. According to a previous paper, the threshold voltage shift  $(\Delta V_{\rm th})$  due to a trapped electron at the bottom oxide of IPD can be about 10 mV in 25 nm technology node, and the effect of trap in the IPD becomes more severe as scaling down [4]. Therefore, the reliability of IPD in flash memory becomes the one of the critical issue and has been widely studied in many groups [31]-[33]. It has been reported that the low-field leakage current of SiO<sub>2</sub>/Al<sub>x</sub>O<sub>1</sub>/SiO<sub>2</sub> (OAO) IPD at high temperature increases due to the abundant shallow traps of OAO IPD compared with those of the conventional SiO<sub>2</sub>/Si<sub>x</sub>N<sub>y</sub>/SiO<sub>2</sub> (ONO) IPD [32]. Furthermore, the counterclockwise or clockwise hysteresis phenomena in the high-k material which lead to the shift of threshold voltage  $(V_{th})$  were studied. The phenomena can be caused by the electron trapping or de-trapping from the

gate/substrate to the high-k stacks [34], or caused by the mobile charges in the high-k materials [35]. However, no paper has been systematically reported to investigate reliability problems and their cause in NAND flash memory having ONO stack as the IPD even if the ONO stack is still used as IPD in the industry.

In this paper, we observe the behavior of abnormal cell which has the counterclockwise hysteresis phenomena in floating-gate NAND flash memory strings having conventional ONO IPD. We also systematically identify the origin of the counterclockwise hysteresis phenomena by measuring the transient bit-line current ( $I_{\rm BL}$ ) characteristics. Furthermore, we investigate the transient  $I_{\rm BL}$  characteristics due to the hysteresis phenomena under various conditions such as temperature, pre-bias voltage ( $V_{\rm PRE}$ ), verifying bias voltage ( $V_{\rm VFY}$ ), and program/erase cycling.

#### 5.2 Device structure and measurement setup

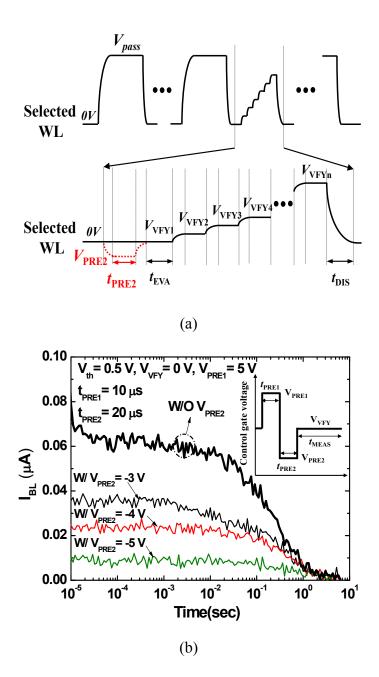

The floating-gate NAND flash memory in this work was fabricated by applying 48 and 26 nm technologies. A 48 nm NAND cell string consists of thirty-two unit cells, a drain select line (DSL) transistor and a source select line (SSL) transistor. A 26 nm NAND cell string consists of sixty-four unit cells, two dummy cells, a DSL transistor and a SSL transistor. Since NAND flash memory strings actually are biased under dynamic signals during the short operation time  $(\sim \mu s)$ , it is appropriate to measure the electrical properties of trap in a short time. In order to observe the behavior of trap in a short time, the  $I_{\rm BL}$  is set to be measured in ~us by using WGFMU modules that integrates arbitrary linear waveform generation capability with high-speed current and voltage measurement [36]. The block diagram of pulsed I-V and fast transient  $I_{\rm BL}$ measurement system is represented in Fig. 5.1 (a). To observe the pulsed *I-V* and transient characteristics of  $I_{\rm BL}$ , the biases are applied to the selected word-line (WL) and bit-line (BL) in the string by using the WGFMU modules. Fig. 5.1 (b) and (c) show the pulse waveform of  $V_{\rm BL}$  and  $V_{\rm CG}$  for pulsed I-V and fast transient  $I_{\rm BL}$  measurements, respectively. In the pulsed I-V measurement, the  $V_{\rm PRE}$  is applied to the CG for  $T_{\text{PRE}}$  before applying a verify voltage  $(V_{\text{VFY}})$ . Then, the  $V_{\rm VFY}$  is incrementally applied and  $I_{\rm BL}$  is sampled during the  $T_{\rm MEAS}$ . In the fast

transient  $I_{\rm BL}$  measurement, the  $V_{\rm PRE}$  and 0 V were applied to the CG and bit-line (BL) of the selected cell for  $T_{\rm PRE}$ , respectively, and then  $I_{\rm BL}$  is set to be measured at a  $V_{\rm VFY}$  and a  $V_{\rm BL}$  for  $T_{\rm MEAS}$ .  $I_{\rm BL}$  is repeatedly measured by 10 times for statistics since the characteristic of transient  $I_{\rm BL}$  is stochastic.

Fig. 5.1. (a) Block diagram of the measurement system. The selected cell is represented by a shaded box. The pulse waveform of  $V_{\rm BL}$  and  $V_{\rm CG}$  for (b) pulsed I-V and (c) fast transient  $I_{\rm BL}$  measurement.

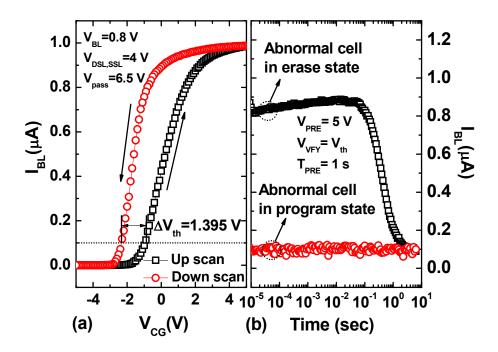

#### 5.3 Hysteresis phenomena in abnormal cells

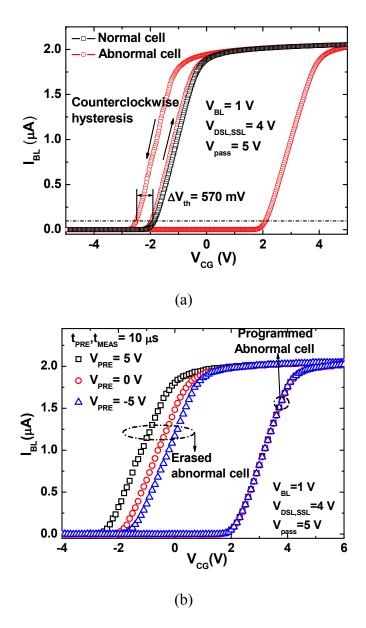

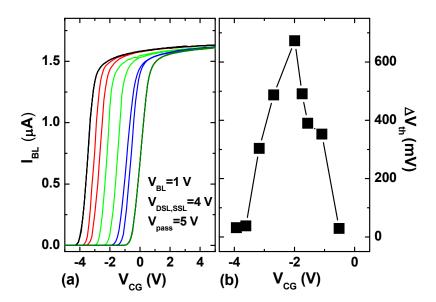

Fig.5.2 (a) shows the measured  $I_{\rm BL}$ - $V_{\rm CG}$  characteristics of 48nm NAND flash memory cell by using the DC measurement when a selected cell is erased or programmed. Here,  $V_{\rm DSL,SSL}$ ,  $V_{\rm pass}$ , and  $V_{\rm BL}$  are 4 V, 5 V and 1 V, respectively, when unselected cells are erased. The  $I_{\rm BL}$  of the selected cell is measured by using the up-scan reading where the  $V_{\rm CG}$  of the selected cell is changed from a negative to a positive bias direction and down-scan reading where the  $V_{\rm CG}$  of the selected cell is changed from a positive to a negative bias direction. As compared

with a normal cell in ease state, an abnormal cell in erase state has a counterclockwise hysteresis phenomenon that results in the large  $\Delta V_{th}$  (~570 mV) as shown in Fig. 5.2 (a). Note we can observe a clockwise hysteresis if electrons are trapped into the tunneling oxide [37]. When the abnormal cell is programmed, the counterclockwise hysteresis phenomenon disappears. In order to observe this phenomenon more clearly, we compare the  $I_{BL}$ - $V_{CG}$  characteristics of DC measurement with that of pulsed I-V measurement when the abnormal cell is erased or programmed. Here, the bias conditions for measurement are the same as those mentioned in Fig. 5.2(a), instead, the  $V_{\rm CG}$  of the selected cell is switched by WGFMU module as mentioned in Fig. 5.1(b) during the pulsed I-V measurement. Here,  $t_{PRE}$  is 10 µs and  $V_{PRE}$  is changed to have -5 V, 0V, and 5 V. When the abnormal cell is measured by using DC measurement,  $I_{\rm BL}$ - $V_{\rm CG}$ characteristics of the abnormal cell show the same results as that mentioned in Fig. 5.2(a). When the abnormal cell is measured by using pulsed I-Vmeasurement, the  $V_{\rm th}$  of the abnormal cell in erase state is changed by  $V_{\rm PRE}$  as shown in Fig. 5.2(b). With increasing  $V_{\rm PRE}$  from -5 V to 5 V, the  $V_{\rm th}$  is decreased from -3.458 V to -4.359 V. On the contrary, the  $V_{\rm th}$  of the abnormal cell in programmed state is constant with increasing  $V_{PRE}$ .

Fig. 5.2. (a) Measured  $I_{\rm BL}$ - $V_{\rm CG}$  characteristics of a 48nm NAND flash memory cell by using DC measurement when a selected cell is erased or programmed. (b) Measured  $I_{\rm BL}$ - $V_{\rm CG}$  characteristics of the 48nm NAND flash memory cell by using the pulsed I-V measurement when a selected cell is erased or programmed.

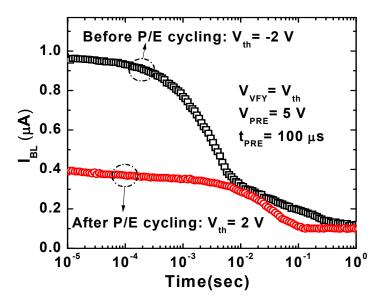

Fig. 5.3. Transient  $I_{\rm BL}$  characteristics of normal and abnormal cells in erased state. The inset shows the magnified  $I_{\rm BL}$  versus time.

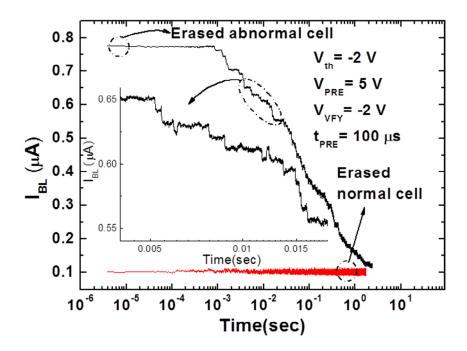

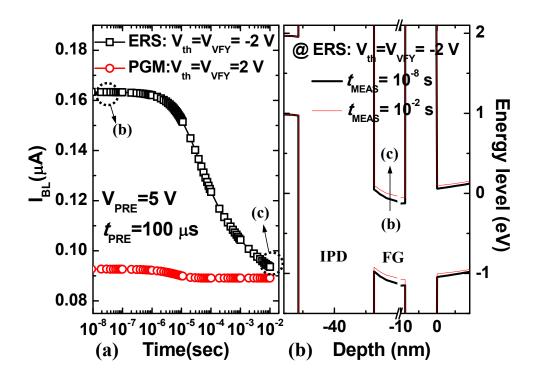

Fig. 5.3 shows the transient  $I_{\rm BL}$  characteristics of normal and abnormal cells in erase state. The inset of Fig. 5.3 shows the magnified  $I_{\rm BL}$  versus time. Here, the selected and unselected cells are erased to have a  $V_{\rm th}$  of -2 V.  $t_{\rm PRE}$  and  $V_{\rm PRE}$  are 100  $\mu$ s and 5 V, respectively.  $V_{\rm DSL,SSL}$ ,  $V_{\rm pass}$ , and  $V_{\rm BL}$  are 4 V, 5 V and 1 V, respectively. By comparing the transient  $I_{\rm BL}$  characteristics of normal cell with that of abnormal cell, the  $I_{\rm BL}$  of the abnormal cell discretely decreases such as the staircase during the  $t_{\rm MEAS}$  as shown in Fig. 5.3.

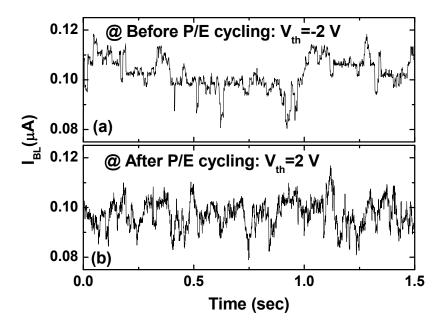

Fig. 5.4. Characteristics of  $I_{\rm BL}$  versus time with increasing  $V_{\rm CG}$  of abnormal cell when the abnormal cell is (a) erased or (b) programmed. The inset of Fig. 4 (a) shows the multi-level RTN amplitude distribution.

Fig. 5.4 shows the characteristics of  $I_{\rm BL}$  versus time with increasing  $V_{\rm CG}$  of abnormal cell when the abnormal cell is (a) erased or (b) programmed. Here,  $V_{\rm DSL,SSL}$ ,  $V_{\rm pass}$ , and  $V_{\rm BL}$  are 4 V, 5 V and 1 V, respectively. The inset of Fig. 5.4(a) is the distribution of  $I_{\rm BL}$  when  $I_{\rm BL}$  is nearly 0.6  $\mu$ A. As shown in Fig. 5.4, the multi-level random telegraph noise (RTN) is observed in the erased abnormal cell, but, disappeared in the programmed abnormal cell. Moreover, the fluctuation of  $I_{\rm BL}(\Delta I_{\rm BL})$  due to multi-level RTN is nearly constant as 0.01  $\mu$ A as shown in the inset of Fig. 5.4(a).

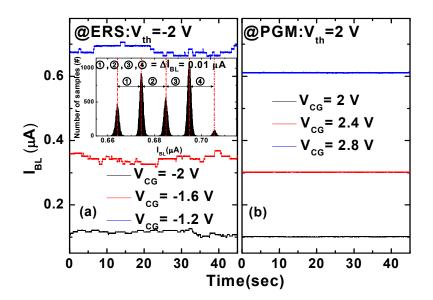

Fig. 5.5 (a) shows the erased  $V_{\rm th}$  as functions of erase voltage ( $V_{\rm ERS}$ ) and the erase time ( $t_{\rm ERS}$ ) when a selected cell is the normal cell or the abnormal cell. Fig. 5.5 (b) shows the erased  $V_{\rm th}$  of the abnormal cell as a function of erase voltage ( $V_{\rm ERS}$ ) when the erase time ( $t_{\rm ERS}$ ) is 10  $\mu$ s or 1 ms. Here, a selected cell is initially programmed to have a  $V_{\rm th}$  of 4 V and then erased by the single pulse of amplitude  $V_{\rm ERS}$  during  $t_{\rm ERS}$ . According to previous report [38], the degradation of erase efficiency occurs by the depletion effects in the poly-silicon FG due to the increase of fringing fields at the rounded FG and the reduction of the active dopant concentration in the small poly-silicon volume. From the results of Fig. 5.5, we can notice that the degradation of erase efficiency increases as decreasing  $t_{\rm ERS}$  when a selected cell is the abnormal cell, which implies that the deep depletion occurs in the poly-silicon FG.

Fig. 5.5 (a) Characteristics of erased  $V_{\rm th}$  as functions of erase voltage and erase time when a selected cell is the normal cell or the abnormal cell. (b) Erased  $V_{\rm th}$  of the abnormal cell as a function of erase voltage when the erase time is 10  $\mu$ s or 1 ms. Dashed lines show the ideal characteristics of erase speed.

## 5.4 Origin of hysteresis phenomenon in the abnormal cell

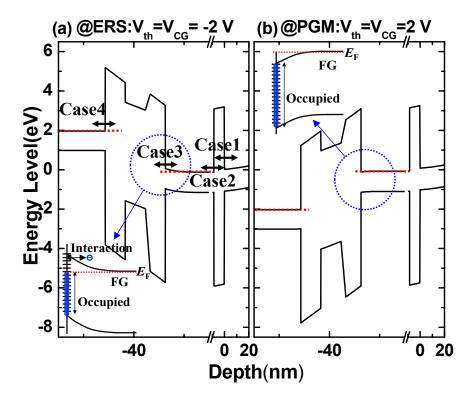

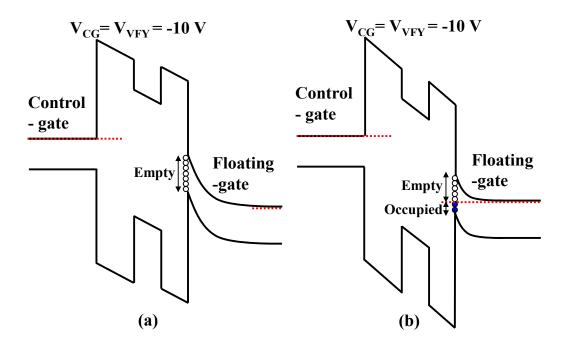

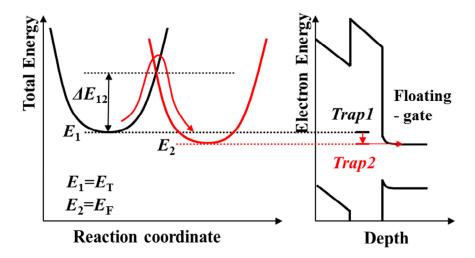

From the results as shown in above, we can assume that these phenomena are caused by the effect of trap in an abnormal cell. From now on, we discuss the origin of these hysteresis phenomena of the abnormal cell. From the results of Figs. 5.3 and 5.4, we can notice that a number of traps exist somewhere in the abnormal cell, which is responsible for the hysteresis phenomena. In order to define the position of traps in the abnormal cell, we consider the four different cases as shown in Fig. 5.6. Fig. 5.6 shows the simulation results of energy band diagram with  $V_{CG}$  of a selected cell when the selected cell is erased or programmed. For device simulation, the cell in the simulation has channel length and width of 48 nm, tunneling oxide thickness ( $t_{ox}$ ) of 7.9 nm, uniform channel doping of  $2\times10^{17}$  cm<sup>-3</sup>, and peak source/drain doping of  $1\times10^{19}$  cm<sup>-3</sup>. From the results of Fig. 5.5, we can notice that doping concentration of FG in the abnormal cell is lower than that of CG because the depletion occurs at the interface between the FG and the bottom oxide of IPD. So, the cell in the simulation has constant FG doping of 1×10<sup>19</sup> cm<sup>-3</sup> and constant CG doping of  $1 \times 10^{20} \text{ cm}^{-3}$ .

Fig. 5.6. Simulated energy band diagrams with  $V_{\rm CG}$  of a selected cell when the selected cell is (a) erased or (b) programmed. Insets of Fig.5.6 represent the schematic views of energy band diagrams between FG and bottom oxide with showing the occupancy of interface traps. Each of the small horizontal lines represents the interface trap.

According to previous papers [7]-[10], a trap which leads to various problems such as RTN and hysteretic effect is located in the tunneling oxide. So, we consider first assume that the traps responsible for the hysteresis are located

in the tunneling oxide and interacted with electrons in the channel (case1) or in the FG (case2). If traps are located in the tunneling oxide as mentioned in cases1 and 2, multi-level RTN is should be observed in not only the erased abnormal cell but also the programmed abnormal cell under the condition that  $I_{\rm BL}$  is adjusted to have the same level by controlling  $V_{\rm CG}$ , because the energy band banding of the tunneling oxide is the same whenever the selected cell is erased or programmed as shown in Fig. 5.6. However, the multi-level RTN is only observed in the abnormal cell in erased state and disappeared in the abnormal cell in programmed state as shown in Fig. 5.4. Furthermore,  $\Delta I_{\rm BL}$  due to multilevel RTN of cases1 and 2 cannot be constant due to the effect of random dopant fluctuations (RDF), line edge roughness (LER), and BL interference which can generate the percolation path in the channel [20], [22], [39]. However,  $\Delta I_{\rm BL}$  due to the multi-level RTN is nearly constant as 0.01 µA as mentioned in the inset of Fig. 5.4. According to the argument mentioned above, cases 1 and 2 can be ruled out.

Now, we assume that traps are located in the IPD and interact with electrons in the FG (case3) or in the CG (case4). In case3, traps, which interact with electrons in the FG, are located at the interface between the bottom oxide of IPD and FG. When the  $V_{\rm CG}$  of a selected cell in erased state is the same as the  $V_{\rm th}$  (=-2 V), the depletion occurs at the interface between the bottom oxide of IPD and FG due to low doping concentration. Electrons can interact with the interface