#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

### 공학박사학위논문

A Study on Ditherless CDR with Optimal Phase Detection

최적 위상 검출 회로를 이용한 클럭 및 데이터 복원 회로에 관한 연구

2014년 8월

서울대학교 대학원 전기·컴퓨터 공학부 박 명 재

### 공학박사학위논문

A Study on Ditherless CDR with Optimal Phase Detection

최적 위상 검출 회로를 이용한 클럭 및 데이터 복원 회로에 관한 연구

2014년 8월

서울대학교 대학원 전기·컴퓨터 공학부 박 명 재

## A Study on Ditherless CDR with Optimal Phase Detection

지도교수 김 재 하

이 논문을 공학박사 학위논문으로 제출함 2014년 6월

> 서울대학교 대학원 전기·컴퓨터 공학부 박 명 재

박명재의 공학박사 학위논문을 인준함 2014년 6월

| 위 원 | . 장 | 정  | 덕 | 균 | (인) |

|-----|-----|----|---|---|-----|

| 부위  | 원 장 | 김  | 재 | 하 | (인) |

| 위   | 원   | 김  | 수 | 환 | (인) |

| 위   | 원   | 0] | 강 | 윤 | (인) |

| 위   | 원   | 문  | 용 | 삼 | (인) |

#### Abstract

Bang-bang phase detectors are widely used for today's high-speed communication circuits such as phase-locked loops (PLLs), delay-locked loops (DLLs) and clockand-data recovery loops (CDRs) because it is simple, fast, accurate and amenable to digital implementations. However, its hard nonlinearity poses difficulties in design and analyses of the bang-bang controlled timing loops. Especially, dithering in bang-bang controlled CDRs sets conflicting requirements on the phase adjustment resolution as one tries to maximize the tracking bandwidth and minimize jitter. A fine phase step is helpful to minimize the dithering, but it requires circuits with finer resolution that consumes large power and area. In this background, this dissertation introduces an optimal phase detection technique that can minimize the effect of dithering without requiring fine phase resolution. A novel phase interval detector that looks for a phase interval enclosing the desired lock point is shown to find the optimal phase that minimizes the timing error without dithering. A digitally-controlled, phase-interpolating DLL-based CDR fabricated in 65nm CMOS demonstrates that it can achieve small area of  $0.026mm^2$  and low jitter of 41 mUIpp with a coarse phase adjustment step of 0.11UI, while dissipating only 8.4mW at 5Gbps. For the theoretic basis, various analysis techniques to understand bang-bang controlled timing loops are also presented. The proposed techniques are explained for both linearized loop and non-linear one, and applied to the evaluation of the proposed phase detection technique.

**Keywords**: Bang-bang control, dither, ditherless, clock-and-data recovery

Student Number: 2010-30218

## Contents

| $\mathbf{A}$ | bstr | act                                                                      | j  |

|--------------|------|--------------------------------------------------------------------------|----|

| $\mathbf{C}$ | onte | nts                                                                      | i  |

| Li           | st o | f Tables                                                                 | iv |

| Li           | st o | f Figures                                                                | v  |

| 1            | Int  | roduction                                                                | 1  |

|              | 1.1  | Motivations                                                              | 1  |

|              | 1.2  | Thesis Contribution and Organization                                     | 6  |

| 2            | Pse  | eudo-Linear Analysis of Bang-Bang Controlled Loops                       | 9  |

|              | 2.1  | Model of a Second-Order, Bang-Bang Controlled Timing Loop                | 9  |

|              | 2.2  | Necessary Condition for the Pseudo-Linear Analysis                       | 12 |

|              | 2.3  | Derivation of Necessity Condition for the Pseudo-Linear Analysis         | 17 |

|              | 2.4  | A Linearized Model of the Bang-Bang Phase Detector                       | 18 |

|              | 2.5  | Linearized Gain of a Bang-Bang Phase Detector for Jitter Transfer        |    |

|              |      | and Jitter Generation Analyses                                           | 21 |

|              | 2.6  | Jitter Transfer and Jitter Generation Analyses                           | 29 |

|              | 2.7  | Linearized Gains of a Bang-bang Phase Detector for Jitter Tolerance      |    |

|              |      | Analysis                                                                 | 34 |

|              | 2.8  | Jitter Tolerance Analysis                                                | 41 |

| 3            | No   | nlinear Analysis of Bang-Bang Controlled Loops                           | 48 |

|              | 3.1  | Transient Analysis of Bang-Bang Controlled Timing Loops                  | 48 |

|              | 3.2  | Phase-portrait Analysis of Bang-Bang Controlled Timing Loops             | 51 |

|              | 3.3  | Markov-chain Analysis of Bang-Bang Controlled Timing Loops $\ . \ . \ .$ | 53 |

|              | 3.4  | Analysis of Clock-and-Data Recovery Circuits                             | 57 |

|                         |       | 3.4.1   | Prediction of Bit-Error Rate                          |   | 57        |

|-------------------------|-------|---------|-------------------------------------------------------|---|-----------|

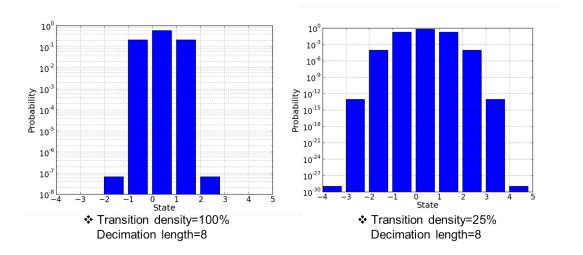

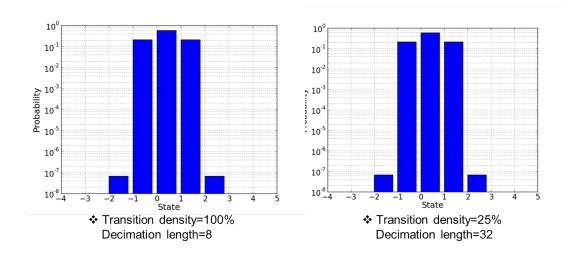

|                         |       | 3.4.2   | Effect of Transition Density                          |   | 58        |

|                         |       | 3.4.3   | Effect of Decimation                                  |   | 61        |

|                         |       | 3.4.4   | Analysis of Oversampling Phase Detectors              |   | 66        |

| 4                       | Des   | sign of | Ditherless Clock and Data Recovery Circuit            |   | <b>75</b> |

|                         | 4.1   | Optim   | nal Phase Detection                                   |   | 75        |

|                         | 4.2   | Propo   | sed Architecture                                      |   | 81        |

|                         | 4.3   | Analy   | sis of the CDR with Phase Interval Detection          |   | 84        |

|                         | 4.4   | Circui  | t Implementation                                      |   | 89        |

|                         |       | 4.4.1   | Sampling Receiver                                     |   | 89        |

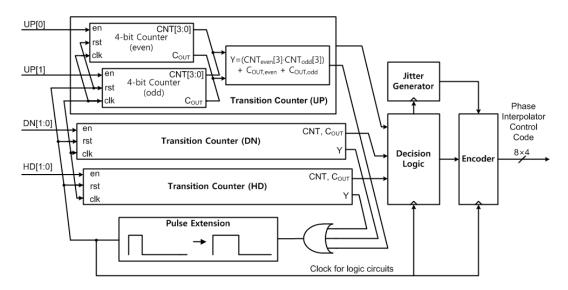

|                         |       | 4.4.2   | Phase Detector                                        |   | 91        |

|                         |       | 4.4.3   | Digital Loop Filter                                   |   | 95        |

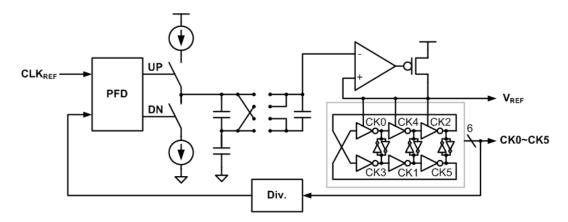

|                         |       | 4.4.4   | Phase Locked-Loop                                     |   | 98        |

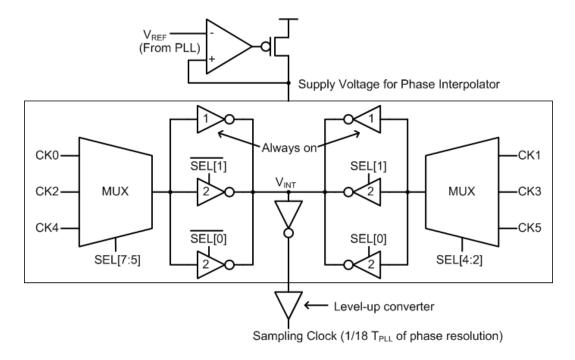

|                         |       | 4.4.5   | Phase Interpolator                                    |   | 99        |

|                         | 4.5   | Built-  | In Self-Test Circuit for Jitter Tolerance Measurement |   | 102       |

|                         | 4.6   | Measu   | rement Results                                        |   | 106       |

| 5                       | Cor   | nclusio | on                                                    | 1 | l14       |

| $\mathbf{R}^{\epsilon}$ | efere | ences   |                                                       | 1 | L16       |

| 국                       | 문 초   | 목       |                                                       | 1 | 121       |

## List of Tables

| 2.1 | Comparison of bang-bang controlled PLL/CDR analyses reported in |     |

|-----|-----------------------------------------------------------------|-----|

|     | literature                                                      | 22  |

| 4.1 | The Prototype Chip Performance Summary                          | 108 |

## List of Figures

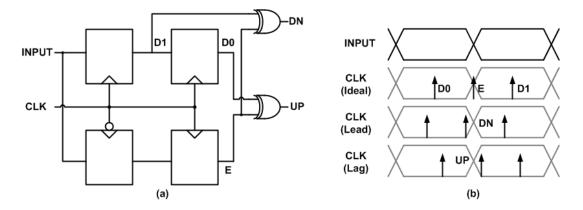

| 1.1 | (a) Circuit diagram of Alexander phase detector and (b) its timing       |    |

|-----|--------------------------------------------------------------------------|----|

|     | diagram for ideal/lead/lag cases                                         | 2  |

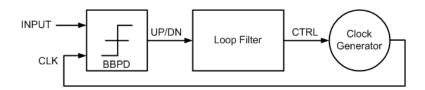

| 1.2 | Bang-bang controlled timing loop                                         | 4  |

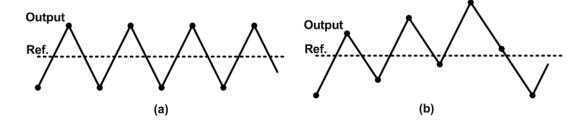

| 1.3 | Dithering behavior of (a) the systems with quantized selectable phases   |    |

|     | and (b) the systems with infinite resolution of phases                   | 5  |

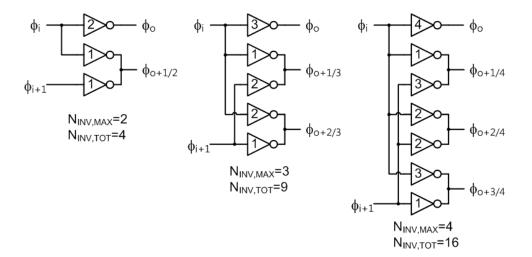

| 1.4 | Implementation of inverter-based phase interpolators with interpolat-    |    |

|     | ing ratios of $1/2$ , $1/3$ and $1/4$                                    | 6  |

| 2.1 | A discrete-time model of a second-order, bang-bang controlled PLL        |    |

|     | with normalized loop parameters                                          | 10 |

| 2.2 | General model of non-linear feedback system                              | 11 |

| 2.3 | (a) Describing function $N(A)$ vs. $A$ as a function of the input noise, |    |

|     | and (b) effective input-to-output transfer of a BBPD as a function of    |    |

|     | noise                                                                    | 13 |

| 2.4 | Nyquist plot of bang-bang CDR: (a) $G(s)$ with and without loop          |    |

|     | delay, (b) $G(s)$ with loop delay and $-1/N(a)$ without noise (inter-    |    |

|     | secting) and (c) $G(s)$ with loop delay and $-1/N(A)$ with noise (not    |    |

|     | intersecting)                                                            | 15 |

| 2.5 | A general model of BBPD                                                  | 19 |

| 2.6 | A model of (a) bang-bang PD and (b) CDR for the purpose of jitter        |    |

|     | transfer and jitter generation analyses                                  | 20 |

| 2.7 | Comparison of predicted quantization error power based on our model      |    |

|     | (solid line) and the model in [14] (star)                                | 23 |

| 2.8 | Comparison of the effective linear gains of a BBPD described by differ-  |    |

|     | ent models in the literature (normalized with respect to the bang-bang   |    |

|     | phase step $\phi_{bb}$ )                                                 | 25 |

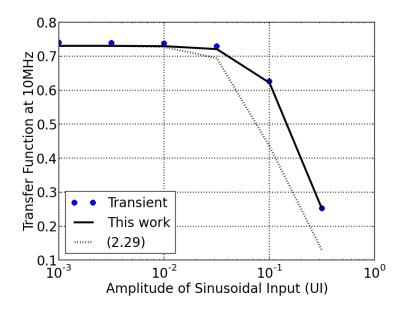

| 2.9  | Comparison of predicted transfer functions at 10MHz with various                                       |    |

|------|--------------------------------------------------------------------------------------------------------|----|

|      | amplitudes of sinusoidal input using transient simulation, proposed                                    |    |

|      | theory, and (2.29). $\phi_{bb}$ is 0.005UI, and $\alpha_T$ is 1.0                                      | 29 |

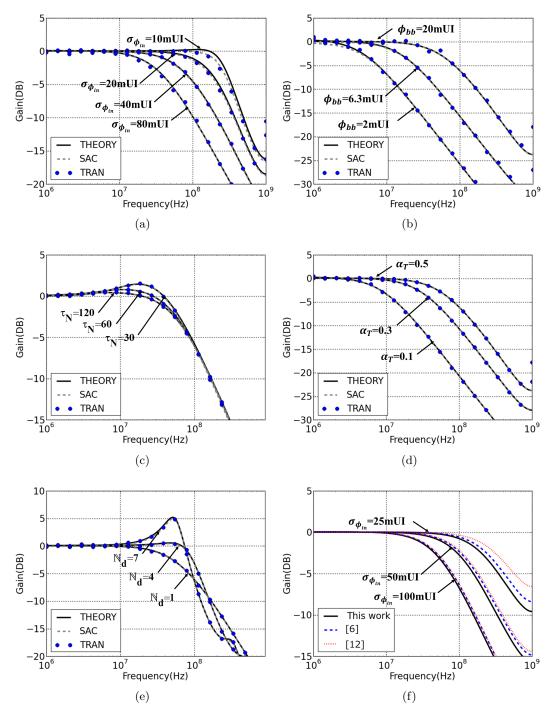

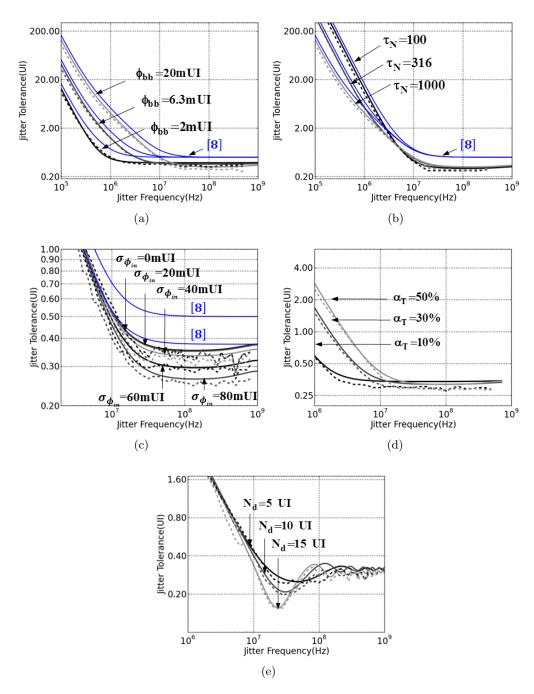

| 2.10 | Comparison of the jitter transfer functions with various (a) $\sigma_{\phi_{in}}$ , (b)                |    |

|      | $\phi_{bb}$ , (c) $\tau_N$ , (d) $\alpha_T$ , and (e) $N_d$ . (f) is the comparison with [6] when      |    |

|      | $\alpha_T = 1.0.$                                                                                      | 31 |

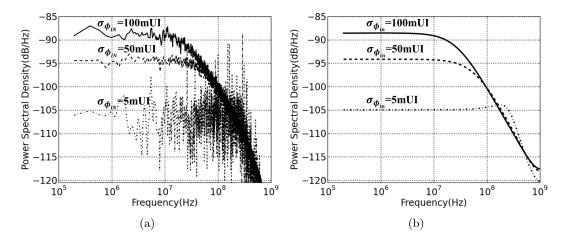

| 2.11 | Comparison of the output jitter PSDs (a) in time-accurate behavioral                                   |    |

|      | simulation and (b) the proposed linear model. Simulation parameters                                    |    |

|      | are same with those in Fig. 2.10                                                                       | 33 |

| 2.12 | A model of bang-bang CDR for the purpose of jitter tolerance (JTOL)                                    |    |

|      | analysis                                                                                               | 34 |

| 2.13 | The confluent hypergeometric functions                                                                 | 36 |

| 2.14 | The $K_{PD,S}$ versus $\sigma_{e,N}$ when the sum of $\sigma_{e,N}$ and $\sigma_{e,sin}$ is limited to |    |

|      | 10                                                                                                     | 38 |

| 2.15 | JTOL calculation procedure                                                                             | 38 |

| 2.16 | BER estimation in presence of sinusoidal and random components in                                      |    |

|      | the phase error                                                                                        | 40 |

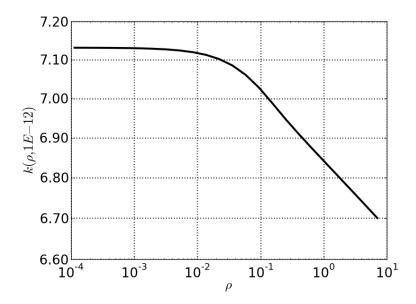

| 2.17 | $k(\rho, BER_{target})$ when $BER_{target}$ is $10^{-12}$                                              | 42 |

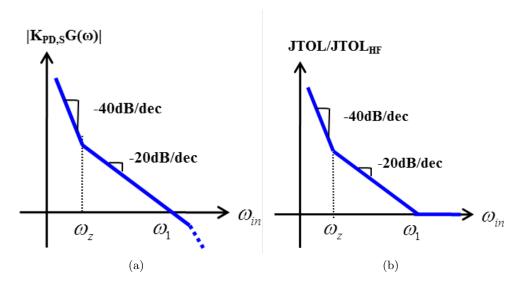

| 2.18 | (a) The linearized open-loop transfer function of a second-order BB-                                   |    |

|      | CDR and (b) its asymptotic JTOL curve showing the shift in slope                                       |    |

|      | at the zero frequency $(\omega_z)$ and the unity-gain frequency $(\omega_1)$                           | 44 |

| 2.19 | Comparison of the JTOL curves between the theoretical (solid) and                                      |    |

|      | simulation results (dashed) on BB-CDRs with various range of de-                                       |    |

|      | sign parameters: (a) bang-bang phase step $(\phi_{bb})$ , (b) normalized time                          |    |

|      | constant of loop filter $(\tau_N)$ , (c) input rms jiiter $(\sigma_{\phi_{in}})$ , (d) transition      |    |

|      | density $(\alpha_T)$ and (e) loop delay $(N_d)$                                                        | 47 |

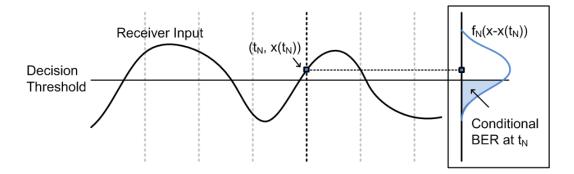

| 3.1  | An example of CBER calculation                                                                         | 50 |

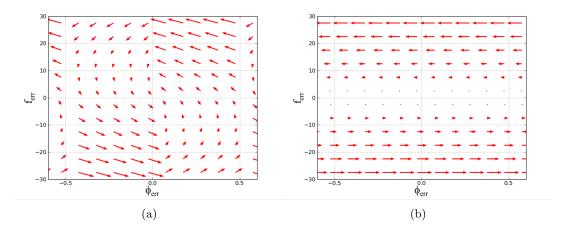

| 3.2  | Phase-portrait of bang-bang controlled timing loop when the transi-                                    |    |

|      | tion density is (a) 100% and (b) 0%                                                                    | 53 |

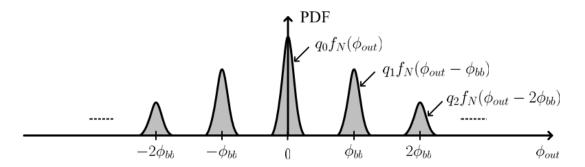

| 3.3  | Probability density function of bang-bang controlled loop's output                                     |    |

|      | phase                                                                                                  | 54 |

| 3.4  | Asymmetric stabilized phase distribution                                                | 54 |

|------|-----------------------------------------------------------------------------------------|----|

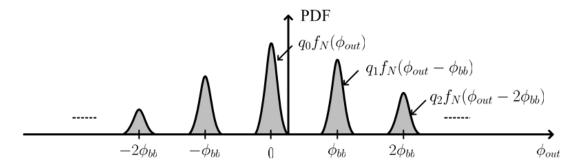

| 3.5  | Error probability of gaussian distributed random jitter $N(0, \sigma_N)$ ex-            |    |

|      | ceeding the threshold when majority voting algorithm with $N_{DEC}$ of                  |    |

|      | samples are performed. For the tie of votes, (a) does not decide it to                  |    |

|      | be an error while (b) does. $\dots$                                                     | 62 |

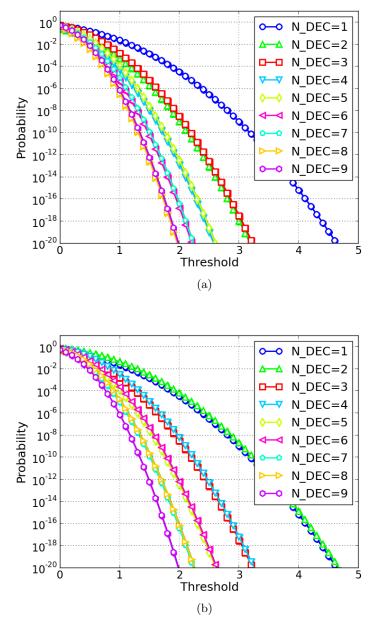

| 3.6  | (a) The error probabilities with majority voting with decimation for                    |    |

|      | $\sigma_N$ =0.1, 0.5 and 1.0 ( $\phi_{bb}$ ) and the ones without decimation that gives |    |

|      | the same results. (b) The simulated noise reduction ratio of majority                   |    |

|      | voting decimation                                                                       | 64 |

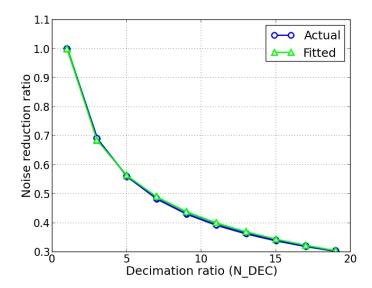

| 3.7  | The comparison between simulated noise reduction ratio and Eq. $(3.15)$ .               | 66 |

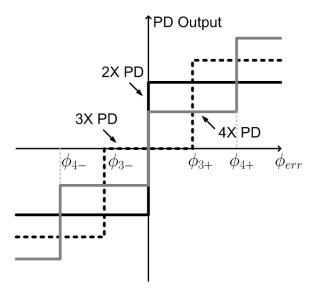

| 3.8  | Input-to-output relationships of oversampling phase detectors                           | 68 |

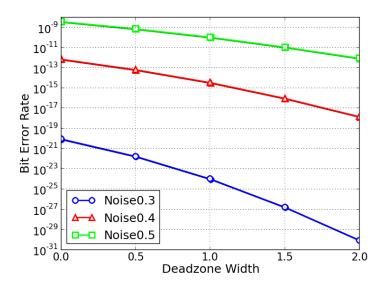

| 3.9  | The expected BER of the $3\times$ oversampling timing loop with various                 |    |

|      | width of deadzones                                                                      | 68 |

| 3.10 | Simulated (a) average of phase error and (b) expected BER of a bang-                    |    |

|      | bang controlled loop. Phase is normalized with the phase adjustment                     |    |

|      | step $(\phi_{bb})$                                                                      | 70 |

| 3.11 | Transient response of $3\times$ oversampling timing loop to sinuoidal input             |    |

|      | phase where $W_{DZ}$ =0, 1.0, and 2.0 ( $\phi_{bb}$ )                                   | 72 |

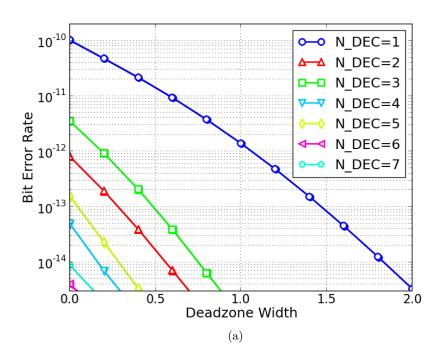

| 3.12 | BER with various deadzone widths and decimation depths. (a) as-                         |    |

|      | sumes $100\%$ of transition density while (b) is measred with various                   |    |

|      | $N_{EFF}$                                                                               | 74 |

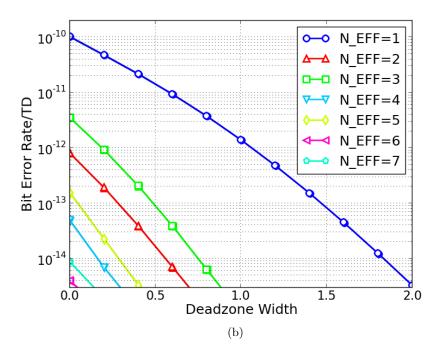

| 4.1  | Comparison of BBPD and optimal phase detection in (a) output phase                      |    |

|      | and (b) maximum phase error                                                             | 77 |

| 4.2  | Response of bang-bang controlled system without loop delay to sinu-                     |    |

|      | soidal input phase and its comparison with the optimal phase                            | 78 |

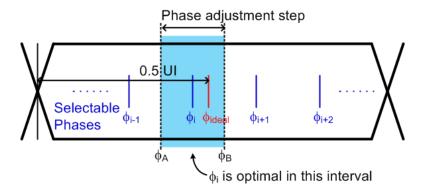

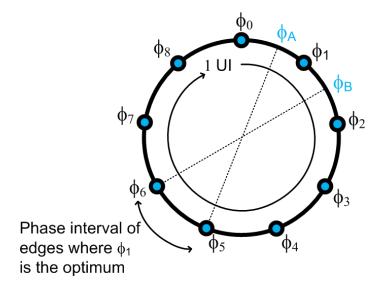

| 4.3  | Optimal phase selection with phase interval detection technique                         | 79 |

| 4.4  | Phase relationship of phase interval detection                                          | 80 |

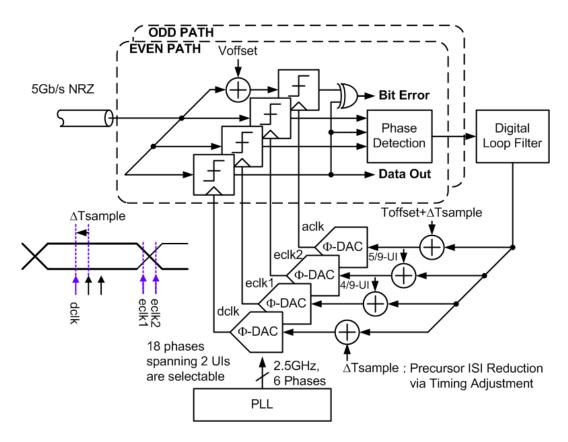

| 4.5  | Overall architecture of the prototype CDR with phase interval detec-                    |    |

|      | tor (PID)                                                                               | 82 |

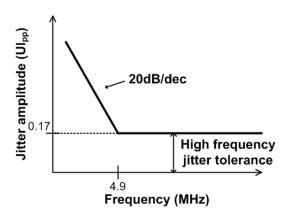

| 4.6  | Jitter tolerance requirements of USB 3.0                                                | 85 |

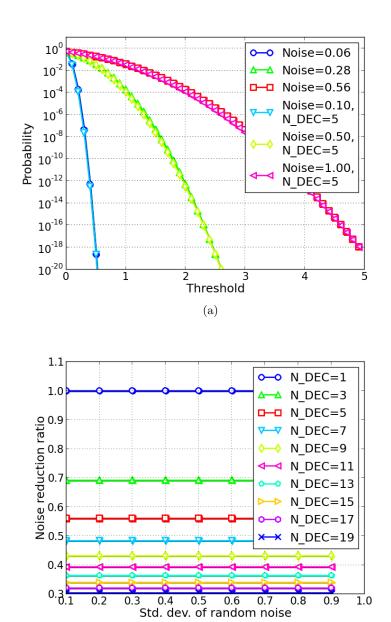

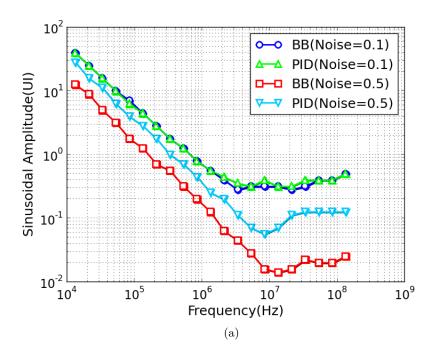

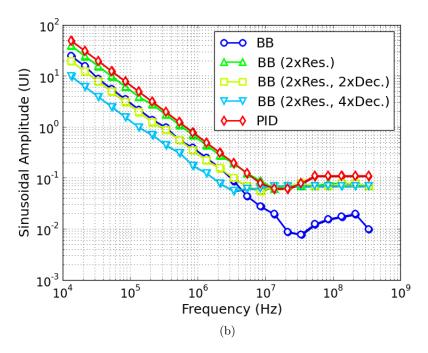

| 4.7  | Simulated jitter tolerance comparing BBPD and PID with (a) differ-      |     |

|------|-------------------------------------------------------------------------|-----|

|      | ent noise conditions, (b) various decimation lengths and phase reso-    |     |

|      | lutions. The 'Noise' in the figure represents the standard deviation of |     |

|      | the input jitter in $\phi_{bb}$ unit                                    | 87  |

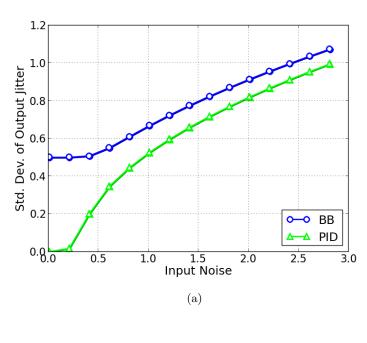

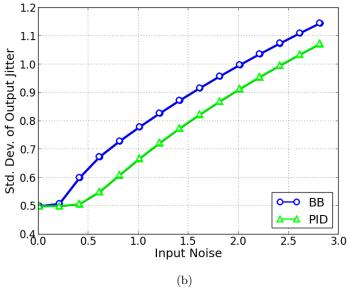

| 4.8  | Simulated output jitter vs. input jitter for BBPD and PID (a) when      |     |

|      | the ideal phase coincides with a selectable phase and (b) when the      |     |

|      | ideal phase is at the middle of two adjacent selectable phases. The     |     |

|      | phases are normalized with the phase adjustment step $(\phi_{bb})$      | 88  |

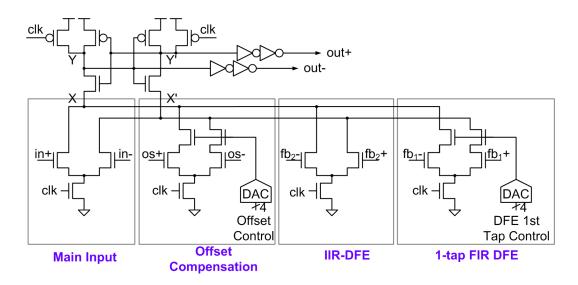

| 4.9  | The sampling receiver with signal summation and offset calibration      |     |

|      | capability                                                              | 89  |

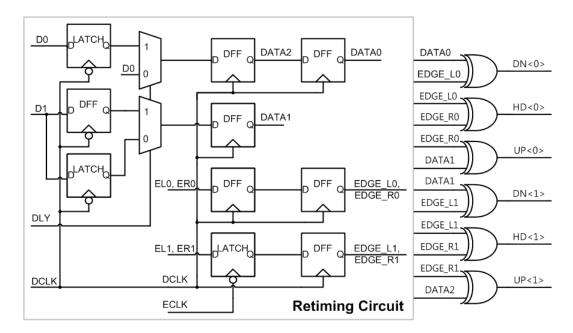

| 4.10 | A half-rate phase interval detector with retiming circuit               | 91  |

| 4.11 | Equalization technique applied to the prototype system                  | 93  |

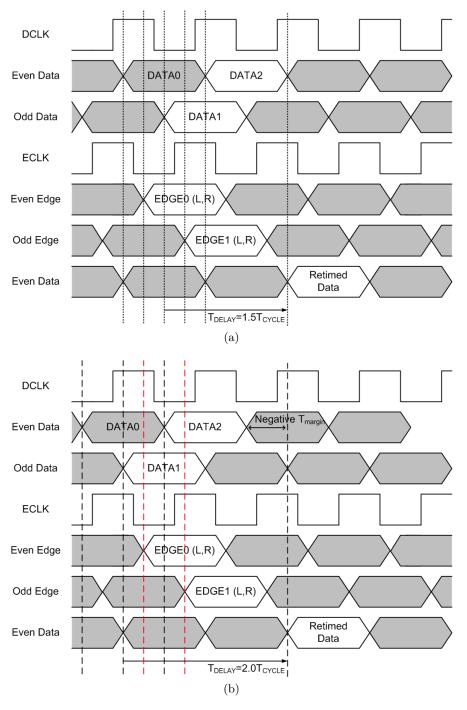

| 4.12 | Timing diagram of phase interval detector's operation when (a) dly=L    |     |

|      | and (b) dly=H                                                           | 94  |

| 4.13 | Block diagram of the digital loop filter                                | 95  |

| 4.14 | Jitter histogram of conventional CDR's output with transition density   |     |

|      | of 100% and 30%                                                         | 97  |

| 4.15 | Jitter histogram of proposed CDR's output with transition density of    |     |

|      | 90% and 30%                                                             | 98  |

| 4.16 | The 6-phase frequency synthesizing phase locked loop used for the       |     |

|      | prototype CDR                                                           | 98  |

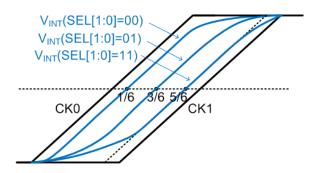

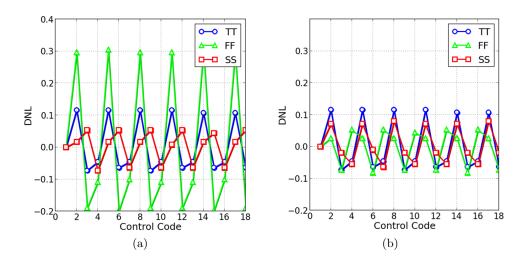

| 4.17 | 3x interpolating phase interpolator                                     | 100 |

| 4.18 | Timing diagram of phase interval interpolator's operation               | 101 |

| 4.19 | Process variation of interpolator's differential nonlinearity (DNL) (a) |     |

|      | without voltage regulation and (b) with regulation                      | 102 |

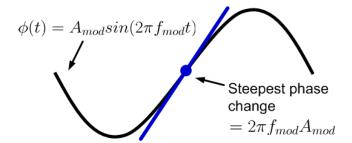

| 4.20 | An example of the sinusoidal jitter                                     | 104 |

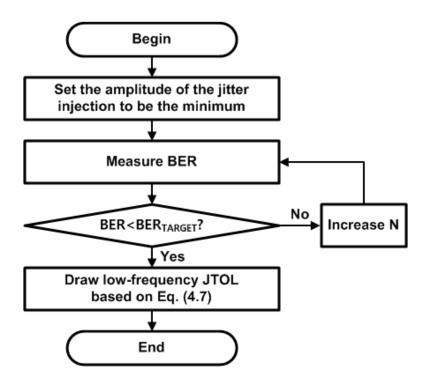

| 4.21 | Proposed procedure to measure the low-frequency JTOL                    | 105 |

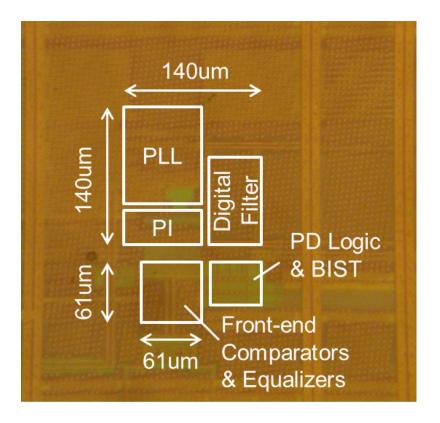

| 4.22 | The die photograph of the prototype CDR with equalizing receiver        |     |

|      | fabricated in 65nm CMOS                                                 | 107 |

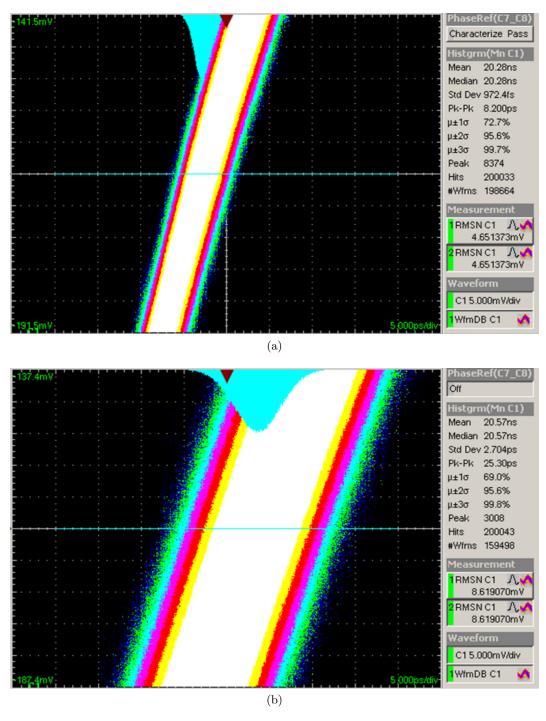

| 4.23 | Measured jitter of the recovered clock at 5Gbps in (a) meso-chronous    |     |

|      | configuration and (b) plesic-chronous configuration                     | 109 |

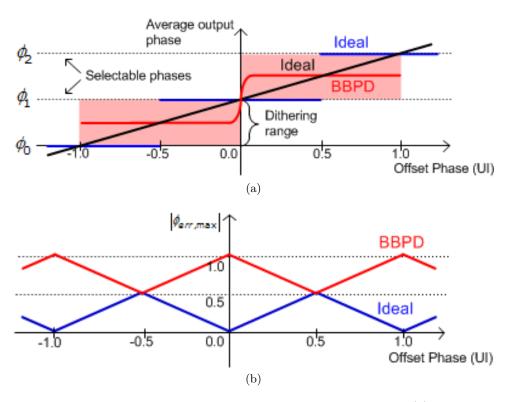

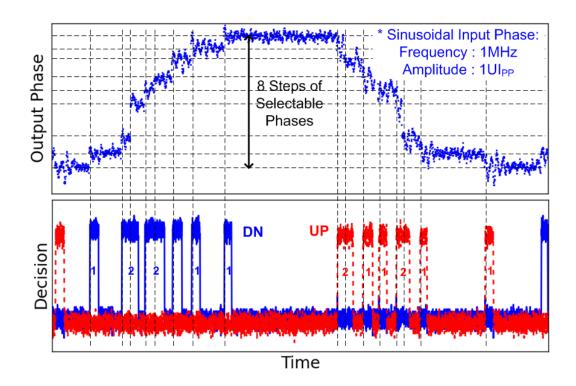

| 4.24 | Output phase and the decision of the loop when 1MHz, $1UI_{pp}$ of     |     |

|------|------------------------------------------------------------------------|-----|

|      | sinusoidal input phase is applied. The applied data pattern is $2^7-1$ |     |

|      | PRBS                                                                   | 110 |

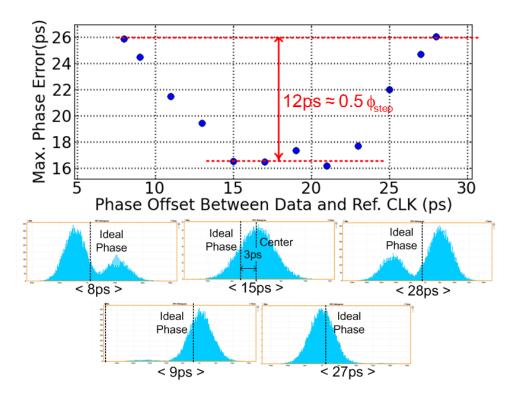

| 4.25 | Jitter histograms and the maximum phase error with various timing      |     |

|      | offsets between data and PLL reference clock                           | 111 |

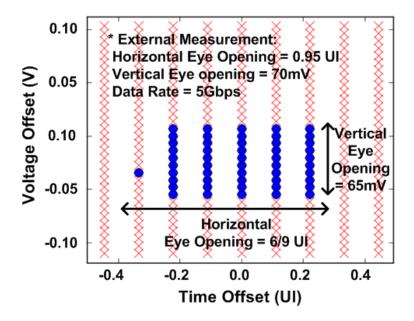

| 4.26 | Measured on-chip eye diagram                                           | 112 |

| 4.27 | Comparison of JTOLs measured with internal and external phase          |     |

|      | modulation                                                             | 119 |

## Chapter 1 Introduction

#### 1.1 Motivations

Many timing loops in today's high-speed communication circuits, such as phase/delay-locked loops (PLL/DLLs) and clock-and-data recovery loops (CDRs), use binary, also known as bang-bang phase detection since their circuit implementations are simple, fast, accurate and amenable to digital implementations. The BBPD compares the phases between the reference input and the feedback clock and tells only about the polarity of the phase error. As it does not measure the magnitude of the phase error, it is suitable for simple implementation and high-speed operation. In addition, it is accurate because most of them measures the phase error based upon the sampled inputs. This characteristic is important for the CDRs, as their purpose is to find the optimal sampling phase for the sampling receivers.

However, its hard nonlinearity poses some difficulties in design and analyses of the BBPD. First, traditional linear analysis including the concepts of loop bandwidth and phase margin cannot be applied directly. Secondly, the quantization noise generated from the BBPD affects the output clock jitter. Thirdly, its loop characteristic changes according to the amount of noise in the input stream. For example, it will be shown that the noise filtering bandwidth gets narrower when the input stream includes larger random noise. Lastly, the bang-bang controlled system does not converge to one stable point but wanders around there, which is called

Figure 1.1: (a) Circuit diagram of Alexander phase detector and (b) its timing diagram for ideal/lead/lag cases.

#### dithering.

As an example, the Alexander PD [1], the most well known implementation of BBPD is shown in Fig. 1.1. It is basically a 2x oversampling phase detector where two samples - data sample and edge sample - are made per one bit to measure the phase difference between the sampling clock and the center of the bit duration. The outputs of upper two flip-flops (D0 and D1) are data samples, whereas the final output of the lower branch (E) is the edge sample that contains the phase information. Assuming that the ideal data sampling point is the center of the bit duration, it detects the relative position of the bit boundary from the edge sampling clock. When the bit boundary is prior to the edge sampling clock, it means that the sampling clock is lagging and vice versa. For example, if D0 and E have different values, it means that the sampling phase leads, and UP signal is asserted. Likewise, when E and D1 have different values DN signal is asserted.

In response to the polarity of the phase error measured by BBPD, the bang-bang controlled loop can only make a fixed amount of adjustment, no matter how large or small the phase error is. A typical BB controlled loop consists of a BBPD, a

loop filter and a clock generator as shown in Fig. 1.2. If the transfer function of the loop filter is  $G_{LF}(s) = A_{prop} + A_{integral}/s$  and the gain of the clock generator is  $K_{clkgen}$ , the phase change of the sampling clock per each decision cannot be less than  $A_{integral}K_{clkgen}T_{ref}$  where  $T_{ref}$  is the interval between consecutive phase detections.

This gives rise to a range of phenomena that are unique to bang-bang controlled loops. For instance, even when the CDR clock phase is far from the desired position, the bang-bang CDR can advance its phase only in fixed steps and the phase transient exhibits a linear slewing behavior rather than an exponentially converging one. Simply put, bang-bang controlled loops can have a vastly different response to the input depending on its magnitude, which is not a phenomenon found in linear controlled loops.

One of the most important characteristic of bang-bang controlled loop is its dithering behavior. When the feedback phase is in proximity to the lock position, the loop keeps moving its phase by the same fixed amount every cycle and the phase displays an alternating phase which is called dithering. Assuming there is no frequency offset between the input bit stream and the sampling clock, the output phase alternates between two phases as shown in Fig. 1.3 (a). Dual-loop DLLs [2] or blind oversampling architectures [3] operating in synchronous or meso-chronous configuration fall in this category. In the aforementioned example, the dithering amount will be  $(A_{prop} + A_{integral})K_{clkgen}T_{ref}$  assuming less than one  $T_{ref}$  of loop delay. On the other hand, in a system that has small frequency difference between the transmitter and the receiver, the relative position of the reference phase drifts over time, and the loop must track the phase drift. For example, the average output phase of conventional charge-pump PLL-based CDRs [4] gradually decreases while

Figure 1.2: Bang-bang controlled timing loop.

alternating up and down as shown in Fig. 1.3 (b). Assuming that the control voltage of the VCO due to the integral path and proportional path are  $V_0$  and  $V_{prop}$ , respectively, the control voltage is  $V_0 + V_{prop}$  when the BBPD decides UP, while it is  $V_0$  when the BBPD decides DN. Therefore, the output phase decreases by

$$\Delta \phi = \frac{1}{K_{VCO}V_O} - \frac{1}{K_{VCO}(V_0 + V_{prop})}$$

(1.1)

per each alternation cycle of UP and DOWN where  $K_{VCO}$  is the gain of the VCO. The otput phase keeps decreasing until it crosses  $\phi_{REF} - \phi_{BB}$  and generates two consecutive UPs.

The effect of dithering increases when the system has a long loop delay between phase detection and output phase adjustment [5]. If the loop delay is  $N_d$  update cycles, it takes  $N_d$  cycles for the decision to be reflected to the output, which results in dithering with the magnitude of  $2(N_d + 1)$  cycles, and duration of  $4(N_d + 1)T_{ref}$ .

As the dithering is the dominant factor of deterministic jitter in most of bangbang controlled systems, careful analyses and design efforts are necessary to minimize its effect. For the CDRs, the increased deterministic jitter can cause the reduction of sampling timing margin, and hence the increased bit-error rate (BER). Considering that the bit error rate under gaussian random noise increases exponentially as the sampling margin decreases, securing the sampling timing margin is important for the CDRs, especially for the ones adopted in high-speed I/Os.

Figure 1.3: Dithering behavior of (a) the systems with quantized selectable phases and (b) the systems with infinite resolution of phases.

A fine phase step is helpful to minimize the dithering, but it requires circuits with finer resolution that consumes large power and area. Fig. 1.4 shows inverter-based phase interpolators with interpolating ratios of 1/2, 1/3 and 1/4. As the minimum achievable inverter size is limited, the area of the interpolator increases quadratically with the phase resolution. At the same time, the power consumption increases linearly assuming that only the inverters contributing the selected output are turned on, but it usually increases faster than linear because the parasitic capacitances of unused inverters contribute to the loading of the buffers. For example, the gate capacitances on  $\phi_i$  node increases from  $3C_{inv}$  to  $10C_{inv}$  while the interpolating ratio changes from 1/2 to 1/4. The tradeoff between the CDR's tracking bandwidth and dithering magnitude also hinders the use of fine phase resolution. As the bang-bang controlled loops tracks the input phase with a fixed amount per each update cycle, a fine phase resolution can cause slower tracking bandwidth.

With this background, this dissertation proposes a novel phase detection technique that can eliminate the dithering. The increased sampling timing margin attained from the proposed technique enables the system to adopt coarse phase resolution, and achieves small area and low-power operation. Moreover, various analysis techniques to predict the performance of the bang-bang controlled systems are pro-

Figure 1.4: Implementation of inverter-based phase interpolators with interpolating ratios of 1/2, 1/3 and 1/4.

posed and applied to the evaluation of the suggested phase detection technique.

#### 1.2 Thesis Contribution and Organization

This dissertation proposes a ditherless CDR and its analysis techniques that can be applied to wide range of bang-bang controlled timing circuits.

Previous efforts to analyze the behavior of bang-bang controlled loops can be largely classified into two categories: the ones that analyze the loop directly as a nonlinear system and the ones that model the system as an equivalent linear system. Without the presence of random noise, nonlinear behaviors such as the aforementioned dithering and slewing determine the majority of the loop's steady-state characteristics, including the clock jitter and loop's tracking bandwidth. Hence, in this case, the system is best modeled as a nonlinear one. On the other hand, with sufficient noise present in the system, a bang-bang controlled system can be modeled effectively as a linear one in a stochastic sense.

This dissertation presents analysis techniques applicable to bang-bang controlled CDRs for both linearized loop and non-linear one. Recently, various techniques were reported to analyze bang-bang controlled PLLs, but there was still no solution to predict the detailed shape of the JTOL curve of CDRs including the effect of additional random or deterministic jitter. On the contrary, the analysis techniques proposed in this dissertation can accurately predict the behavior of CDRs including various design parameters such as transition density, random noise, decimation and dead-zone width.

Chapter 2 describes an accurate, yet analytical method to predict the key characteristics of a bang-bang controlled timing loop: namely, the jitter transfer (JTRAN), jitter generation (JG), and jitter tolerance (JTOL). The analysis basically derives a linearized model of the system, where the bang-bang phase detector is modeled as a set of two linearized gain elements and an additive white noise source. This phase detector (PD) model is by far the most extensive one in literature, which can correctly estimate the effects of random jitter, transition density, and finite loop latency on the loop characteristics. The described pseudo-linear analysis assumes the presence of random jitter at the PD input and the minimum jitter necessary to keep the linear model valid is derived, based on a describing function analysis and Nyquist stability analysis. The presented analysis re-confirms the findings of prior theories and provides theoretical basis to the prior empirically-drawn equations, such as those for the quantization noise power and the gain reduction in presence of a finite loop delay.

Chapter 3 explains various analysis techniques to analyze the bang-bang controlled loop when it is not linearized. Especially, Markov-chain model analysis pre-

viously applied to the analysis of all-digital PLLs [6] are extended to include various design factors of CDRs such as loop delay, transition density, deadzone width and decimation. While explanation, it shows that the optimal deadzone width is a half of minimum phase resolution in the respect of low BER and high bandwidth, which gives the theoretic basis of the proposed phase interval detector.

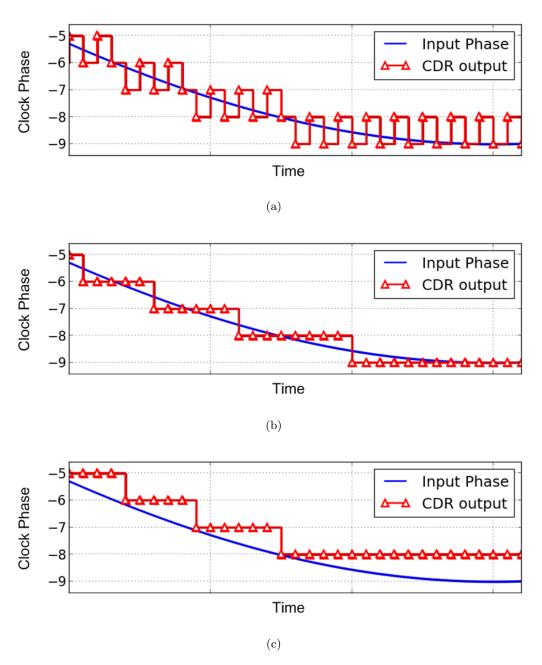

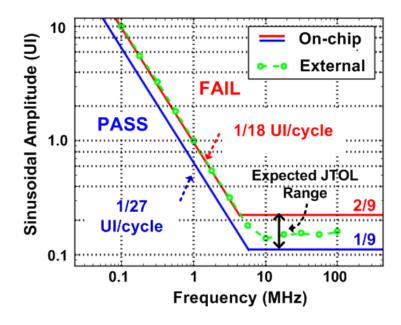

Based upon the aforementioned analyses, Chapter 4 introduces a novel phase interval detector that looks for a phase interval enclosing the desired lock point to find the optimal phase that minimizing the timing error without dithering. A digitally-controlled, phase-interpolating DLL-based CDR fabricated in 65nm CMOS demonstrates that it can achieve low jitter of 41- $mUI_{pp}$  with a coarse phase adjustment step of 0.11-UI, while dissipating only 8.4mW at 5Gbps. Measurement results verifies that the loop does not dither unless there are two sampling phases that give similar results. In addition, an on-chip measurement technique for characterizing the jitter tolerance (JTOL) of high-speed receivers is presented. The proposed technique emulates the SJ in the off-chip input data stream with a SJ in the on-chip recovered clock of the clock-and-data recovery loop (CDR), allowing an ordinary transmitter to be used as the input source.

## Chapter 2

## Pseudo-Linear Analysis of Bang-Bang Controlled Loops

BBPD's strongly nonlinear transfer characteristic hinders the use of long-established design insights and practices of linear PLL/DLLs. This chapter presents an analysis technique that derives the equivalent linear model of a bang-bang controlled timing loop so that its key characteristics, such as jitter generation (JG), jitter transfer (JTRAN) and jitter tolerance (JTOL), can be accurately predicted and the design trade-offs among those characteristics can be reasoned based on the familiar linear system theories.

### 2.1 Model of a Second-Order, Bang-Bang Controlled Timing Loop

Before delving into the proposed analyses, this section defines the analytical model of a second-order, bang-bang controlled loop and its associated design parameters.

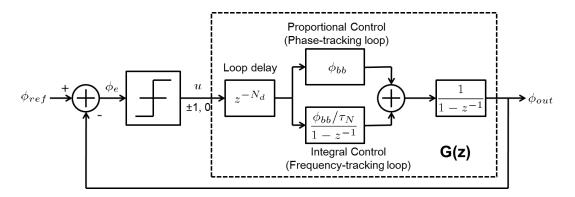

Fig. 2.1 shows the discrete-time model of the second-order, bang-bang controlled PLL whose loop filter is made of two control paths: a proportional control path that updates the VCO phase by  $\phi_{bb}$  (rad) and an integral control path that updates the VCO frequency by  $\phi_{bb}/(\tau_N T_{ref})$  (rad/s) upon the detection of the phase error polarity at each update cycle  $(T_{ref})$ . The loop filter can be implemented either as analog circuits (e.g., a charge pump followed by a series-RC filter) or as digital

Figure 2.1: A discrete-time model of a second-order, bang-bang controlled PLL with normalized loop parameters.

logic (e.g., a scaler, an accumulator and a summer). Higher-order control terms in the loop filter can be ignored for simplicity, unless the intra-cycle behavior is concerned [7].

We model the bang-bang phase detector (BBPD) as a slicer that provides the discrete output levels of +1, -1, and 0 each indicating that the output phase is 'late', 'early' or 'neutral (in case of no transition)', respectively according to the following equation:

$$u(t) = \begin{cases} sgn(\phi_e(t)) & \text{if there is transition} \\ 0 & \text{otherwise} \end{cases}$$

The VCO is basically modeled as a phase accumulator that accrues all the phase shifts requested by the loop filter in the past. The phase shift includes both the proportional phase shift  $\phi_{bb}$  and the phase shift resulting from the error in the integral control's frequency.

Note that we added a delay element  $z^{-(N_d+1)}$  in the loop filter, modeling the raw latency of  $N_d$  update cycles around the loop. The additional one cycle delay reflects the inherent delay of a discrete-time, sampled-data system. In other words, a

Figure 2.2: General model of non-linear feedback system.

discrete-time system cannot detect a change in a signal until it samples that change at the next cycle. It should be noted that including the loop delay in the PLL model is essential in describing the unique behavior of a bang-bang controlled PLL, such as dithering [5], slewing (i.e. slope overloading) [8] and pull-in force inversion [9].

Apart from the BBPD, which is modeled as the slicer, the rest of the system is linear. The discrete-time transfer function G(z), from the slicer output u to the output clock phase  $\phi_{out}$ , can be expressed as:

$$G(z) = \frac{\phi_{bb}}{\tau_N} \cdot \frac{1 + \tau_N (1 - z^{-1})}{(1 - z^{-1})^2} z^{-(N_d + 1)}$$

(2.1)

Often, it is more convenient to use a continuous-time version of G(z). An approximate continuous-time transfer function can be obtained by substituting  $e^{-sT_{ref}} \approx 1 - sT_{ref}$  for  $z^{-1}$ , assuming that the frequency of interest is much lower than the Nyquist frequency (i.e., one half of the BBPD update frequency),

$$G(s) = \frac{\phi_{bb}}{\tau_N T_{ref}^2} \frac{1 + \tau_N T_{ref} s}{s^2} e^{-sT_{ref}(N_d + 1)}$$

(2.2)

where  $T_{ref}$  is the update period of the loop.

The model presented here can be applied to a wide class of bang-bang controlled timing circuits other than the second-order PLL-based CDRs, including semi-digital dual-loop DLLs [2], blind oversampling CDRs [3] and phase-rotating PLLs [10]. Some timing circuits are first-order loops in nature without the integral control paths, in which case the integral time constant  $\tau_N$  in our model can be set to an infinite value.

# 2.2 Necessary Condition for the Pseudo-Linear Analysis

A bang-bang controlled system can be modeled as an equivalent linear system when sufficient noise is present in the system. This section derives the minimum noise necessary for our pseudo-linear analysis to be valid.

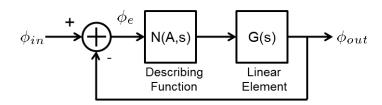

In a strict sense, dithering implies that the system is unstable and occurs when the feedback loop satisfies the following conditions: (1) large enough gain and (2) long enough delay. For instance, if we model the bang-bang controlled loop in Fig. 2.1(b) as a feedback loop as shown in Fig. 2.2, consisting of a linearized gain N(A) that corresponds to the nonlinear BBPD and G(s) that models the rest of the system, the closed-loop transfer function H(s) of the system from input to output can be written as:

$$H(s) = \frac{N(A) \cdot G(s)}{1 + N(A) \cdot G(s)}.$$

(2.3)

With G(s) including the loop delay component  $e^{-sT_{ref}(N_d+1)}$ , as in Eq. (2.2), this system may become unstable and exhibit limit-cycle behavior when the denominator  $1 + N(A) \cdot G(s)$  is equal to zero [11]. In other words, dithering can occur when there exist an amplitude A and a frequency  $s = j\omega$  that satisfy

$$G(s) = -\frac{1}{N(A)} \tag{2.4}$$

Figure 2.3: (a) Describing function N(A) vs. A as a function of the input noise, and (b) effective input-to-output transfer of a BBPD as a function of noise.

We denoted the linearized gain of the BBPD N(A) as a function of the input amplitude A. One way to derive the approximate linear gain of a nonlinear element as a function of the input signal amplitude A is the describing function analysis [11]. Assuming that the nonlinear BBPD receives a sinusoidal input with amplitude Aand the frequency  $\omega$ , the linearized gain is derived as the ratio between this input amplitude A and the amplitude of the corresponding frequency component in the output signal. One can predict the existence of limit cycles based on this describing function analysis. If there exist an amplitude A and a frequency s that satisfy (2.4), then the system is likely to have a limit-cycle behavior with the corresponding amplitude and frequency. In our case, the BBPD is memoryless and hence its linearized gain N(A) is a function of amplitude A only.

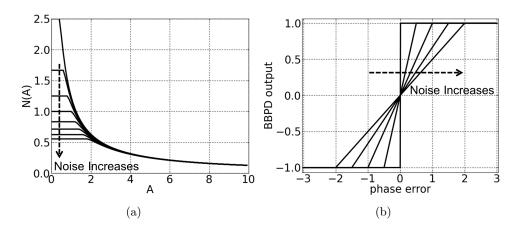

When there is no noise present at the input of the BBPD, the linearized gain

N(A) can be derived as in [11]:

$$N(A) = \frac{\frac{4}{\pi} \int_0^{\pi/2} 1 \cdot \sin(\omega t) d(\omega t)}{A}$$

$$= \frac{4}{\pi A}$$

(2.5)

The linearized gain N(A) starts from  $+\infty$  and decreases toward 0 as the input amplitude A increases, as shown in Fig. 2.3(a). The expression -1/N(A) will then change from 0 to  $-\infty$  as A changes from 0 to  $+\infty$ .

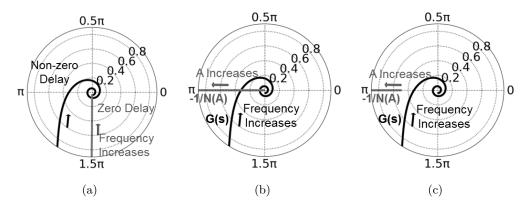

The existence of a solution to Eq. (2.4) can be visualized by plotting both sides of the equation on a Nyquist plot, as shown in Fig. 2.4. This plots the trajectories of G(s) and -1/N(A) on a complex plane with polar coordinates while sweeping the frequency  $s = j\omega$  and the amplitude A, respectively. As Fig. 2.4(a) shows, with a non-zero loop delay, the G(s) curve has a shape that intersects with the negative real axis. In this case, there exists a value of A that satisfies Eq. (2.4) because -1/N(A) spans the whole range of negative real values (Fig. 2.4(b)). In other words, the describing function analysis confirms that a bang-bang controlled loop can exhibit dithering behavior when the loop has a non-zero delay.

In contrast, when noise is present at the BBPD input, the noise effectively smoothes out the binary characteristic of the BBPD transfer function and lowers the linearized gain N(A), as plotted in Fig. 2.3(a). To illustrate this simply, let us assume that the input noise is uniformly distributed between  $-\Delta\phi_L$  and  $\Delta\phi_L$ . The effective input-to-output transfer function of the BBPD, calculated as the average output in the presence of noise from each given input, changes to the one shown in Fig. 2.3(b), which can be expressed as a convolution between the original BBPD transfer function and the noise PDF [12]. Intuitively speaking, for inputs smaller

Figure 2.4: Nyquist plot of bang-bang CDR: (a) G(s) with and without loop delay, (b) G(s) with loop delay and -1/N(a) without noise (intersecting) and (c) G(s) with loop delay and -1/N(A) with noise (not intersecting).

than the noise magnitude  $\Delta \phi_L$ , the probabilities of +1 and -1 outputs gradually change with the input amplitude, implying a linearized response. With this newly-formed linear region in the BBPD transfer function, the maximum linearized gain N(A) is at most  $1/\Delta \phi_L$ , even for the smallest A. It then follows that -1/N(A) will span a reduced range from  $-\Delta \phi_L$  to  $-\infty$ .

The above analysis illustrates that sufficient noise in the system can reduce the span of -1/N(A), as illustrated in Fig. 2.4(c), causing the system to not have a solution that satisfies Eq. (2.4) and, hence, to exhibit no dithering. In other words, the bang-bang controlled system is *sufficiently linearized* by the noise.

Note that a bang-bang controlled loop with a longer loop delay takes more noise to linearize. With the longer delay, the G(s) curve intersects with the negative real axis at the lower value (at the higher absolute value) and the larger noise  $(\Delta \phi_L)$  is required to avoid its crossing with -1/N(A). Without sufficient noise, the output phase will dither with the larger amplitude because the two curves intersect at the point that corresponds to the larger A. We will see later that the excessive loop

delay in a bang-bang controlled timing loop has many adverse effects on the overall performance metrics. It is desirable to keep the loop delay to the minimum possible via careful circuit and architecture designs.

From this analysis it follows that to suppress dithering in a bang-bang controlled loop, the noise in the system must be large enough so that the maximum effective BBPD gain  $K_{PD}$  becomes lower than a certain critical threshold  $K_{PD}^*$ . In the previous analysis,  $K_{PD}$  corresponds to the asymptotic value of N(A) as A approaches 0. The threshold  $K_{PD}^*$  is determined by the linear part of the feedback system G(s):

$$K_{PD}^* = -1/Re\{G(j\omega^*)\}$$

(2.6)

where  $\omega^*$  is the smallest  $\omega$  that satisfies  $\mathcal{I}m\{G(j\omega)\}=0$ . It is possible to derive the expression for  $K_{PD}^*$  in terms of the loop parameters using Eq. (2.2), and we can finally arrive at the necessary condition for the linearized system analysis:

$$K_{PD} < K_{PD}^* = \frac{\pi}{2} \frac{1}{\phi_{bb}(N_d + 1)}$$

(2.7)

The detailed derivation of the critical gain value  $K_{PD}^*$  is given in Section 2.3. This criterion confirms the previous results; namely that it takes the larger noise to linearize a bang-bang controlled loop when it has a larger gain  $(\phi_{bb})$  or a longer delay  $(N_d)$  [5]. It should be noted that Eq. (2.7) is the condition to avoid periodic dithering. The system may still exhibit non-periodic dithering even when  $K_{PD}$  is smaller than  $K_{PD}^*$ .

### 2.3 Derivation of Necessity Condition for the Pseudo-Linear Analysis

This section gives the validity of our pseudo-linear analysis within the suggested  $K_{PD}$  range explained in the previous section. By substituting  $s = j\omega$  and using the Euler's identity, (2.2) becomes

$$G(j\omega) = -\frac{\phi_{bb}}{\tau_N} \frac{1 + \tau_N T_{ref} j\omega}{T_{ref}^2 \omega^2} \{\cos(\omega T_{ref}(N_d + 1)) - j\sin(\omega T_{ref}(N_d + 1))\}.$$

$$(2.8)$$

Let us define the ratio between the time constant of loop filter and the loop delay  $\kappa$  as

$$\kappa = \frac{\tau}{t_{d,eff}} = \frac{\tau}{T_{ref}} / \frac{t_d + T_{ref}}{T_{ref}} = \tau_N / (N_d + 1). \tag{2.9}$$

Then the smallest  $\omega$  that satisfies  $Im\{G(j\omega)\}=0, \omega^*$ , is

$$Im(G(j\omega^*)) = \frac{-\phi_{bb}}{\tau_N T_{ref}^2 \omega^{*2}} \{ \tau_N T_{ref} \omega^* \cos(\omega^* T_{ref}(N_d + 1))$$

$$-\sin(\omega^* T_{ref}(N_d + 1)) \} = 0$$

$$\tau_N T_{ref} \omega^* = \tan(\omega^* T_{ref}(N_d + 1))$$

$$(2.10)$$

Inserting Eq. (2.9) into Eq. (2.10), we obtain

$$\kappa \omega^* T_{ref}(N_d + 1) = \tan(\omega^* T_{ref}(N_d + 1)). \tag{2.11}$$

Assuming  $\kappa >> 1$ , which is true in most systems,

$$\omega^* T_{ref}(N_d + 1) \approx \frac{\pi}{2}$$

$$\omega^* = \frac{\pi}{2} \frac{1}{T_{ref}(N_d + 1)}$$

(2.12)

Finally, by putting Eq. (2.12) into Eq. (2.6), we obtain

$$K_{PD}^* = \frac{1}{Re\{H(e^{j\omega^*T_{ref}})\}} = \frac{\pi}{2} \frac{1}{\phi_{bb}(N_d + 1)}.$$

(2.13)

# 2.4 A Linearized Model of the Bang-Bang Phase Detector

There have been many efforts to model the bang-bang phase detectors (BBPD) or equivalent one-bit quantizers as linear elements. These efforts were not limited to the context of PLLs and CDRs [6,8,12–14], but also included data converters [15]. The representative examples of such prior work are summarized in Tab 2.4. Some of the linear models do not include additive noise sources for modeling quantization noise [8,12] or do not model the influence of the input noise profile on the effective gain value [13]. It is noteworthy that recent studies have analyzed the effects of quantization noise in so-called, all-digital PLLs, but they may not be easily extended to CDRs because they either assume low noise conditions [16,17] or neglect the influence of the transition density [6,14]. In addition, the methods in prior work for deriving effective linear gain were either limited to a specific circuit implementation [8], or based on Markov-chain analysis which does not give a closed-form equation that can be applied to general problems [6,14,18]. This section presents a generally applicable linear model for a BBPD that includes all the effects of loop dynamics such as loop delay, quantization noise and transition density.

Let's assume that the phase error (i.e., the phase difference between the input data stream and the recovered clock) consists of two terms. One is the deterministic phase error term  $\phi_{e,X}(t)$  (e.g., deterministic ISI or sinusoidal jitter) and the other

Figure 2.5: A general model of BBPD.

is a zero-mean random error term  $\phi_{e,N}(t)$ . In expressions:

$$\phi_e(t) = \phi_{e,X}(t) + \phi_{e,N}(t)$$

(2.14)

The deterministic term  $\phi_{e,X}(t)$  is zero when analyzing the jitter transfer or jitter generation characteristics, assuming a fixed input phase. However,  $\phi_{e,X}(t)$  may take a sinusoidal waveform when analyzing the jitter tolerance.

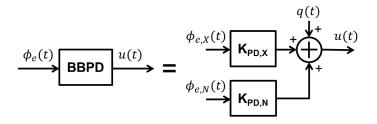

The key feature of our pseudo-linear analysis is that it assumes different gains for components  $\phi_{e,X}(t)$  and  $\phi_{e,N}(t)$ . Such a treatment was originally suggested by [15] for the purpose of analyzing the SNDR of delta-sigma ADCs. Fig. 2.5 illustrates our linearized model of a BBPD.  $K_{PD,X}$  and  $K_{PD,N}$  are linearized gains for the input components  $\phi_{e,X}(t)$  and  $\phi_{e,N}(t)$ , respectively, and an independent noise q(t) is added to the output to model the quantization effects of the BBPD. When sufficient noise is present in the system and the linearized analysis is valid, the random component  $\phi_{e,N}(t)$  is mainly the result of the input phase noise and is uncorrelated with the deterministic term  $\phi_{e,X}(t)$  [14].

The following discussion describes how to decompose the input of the BBPD  $\phi_e(t)$  into the two components  $\phi_{e,X}(t)$  and  $\phi_{e,N}(t)$ . Let us denote the nonlinear

Figure 2.6: A model of (a) bang-bang PD and (b) CDR for the purpose of jitter transfer and jitter generation analyses.

mapping of  $\phi_e(t)$  into the BBPD output u(t) as  $N(\phi_e(t))$ :

$$u(t) = N(\phi_e(t)) = N(\phi_{e,X}(t) + \phi_{e,N}(t)). \tag{2.15}$$

The instantaneous difference  $\phi_q(t)$  between u(t) and the output of linearized model  $K_{PD,X}\phi_{e,X}(t) + K_{PD,N}\phi_{e,N}(t)$  can be considered as the quantization noise. For the closest approximation of the BBPD's behavior, the linearized gains  $K_{PD,X}$  and  $K_{PD,N}$  should be set to minimize the power of this quantization noise [15]. The power of the quantization noise is then expressed as

$$\sigma_q^2 = E\{[u(t) - K_{PD,X}\phi_{e,X}(t) - K_{PD,N}\phi_{e,N}(t)]^2\},$$

(2.16)

and is minimized when

$$\frac{\partial \sigma_q^2}{\partial K_{PD,X}} = 2K_{PD,X}E\{\phi_{e,X}^2(t)\} - 2E\{\phi_{e,X}(t)u(t)\} = 0$$

$$\frac{\partial \sigma_q^2}{\partial K_{PD,N}} = 2K_{PD,N}E\{\phi_{e,N}^2(t)\} - 2E\{\phi_{e,N}(t)u(t)\} = 0$$

(2.17)

are satisfied. The equations then respectively yield:

$$K_{PD,X} = \frac{E\{\phi_{e,X}(t)u(t)\}}{E\{\phi_{e,X}^{2}(t)\}}$$

$$K_{PD,N} = \frac{E\{\phi_{e,N}(t)u(t)\}}{E\{\phi_{e,N}^{2}(t)\}}.$$

(2.18)

It is noteworthy that when Eq. (2.18) is satisfied, the random components of the input  $\phi_{e,N}(t)$  and the quantization noise q(t) become uncorrelated, because the expression

$$E\{\phi_{e,N}(t)q(t)\} = E\{\phi_{e,N}(t)u(t)\} - K_{PD,X}\{\phi_{e,N}(t)\phi_{e,X}(t)\}$$

$$- K_{PD,N}\{\phi_{e,N}^{2}(t)\}$$

(2.19)

is 0, given that  $\phi_{e,N}(t)$  is independent of  $\phi_{e,X}(t)$  and  $E\{\phi_{e,N}(t)u(t)\} = K_{PD,N}\{\phi_{e,N}^2(t)\}$  according to Eq. (2.17). This property will be leveraged in the later analyses in this chapter.

# 2.5 Linearized Gain of a Bang-Bang Phase Detector for Jitter Transfer and Jitter Generation Analyses

This section discusses the derivation of the linearized gain for the analyses of the jitter transfer (JTRAN) and jitter generation (JG) characteristics of a bang-bang controlled CDR, based on the mentioned linear model.

In the case of JTRAN and JG analyses, the input phase is assumed to be constant, implying that the deterministic component  $\phi_{e,X}(t)$  is a constant value, and it can be considered as 0 without a loss of generality. Fig. 2.6 shows the analytical model of the BBPD and the overall CDR. The effective linearized gain  $K_{PD}$  for the random input  $\phi_{e,N}(t)$ , which is equal to the phase error input  $\phi_{e}(t)$  in this case, can

Table 2.1: Comparison of bang-bang controlled  $\operatorname{PLL}/\operatorname{CDR}$  analyses reported in

| lit | era          | <b>†</b> 11 | ırρ |

|-----|--------------|-------------|-----|

| ш   | $c_{\rm L}a$ | ւսս         | пс  |

| Ref.            | Main Contributions               | Limitations                        |

|-----------------|----------------------------------|------------------------------------|

| Walker,         | Analysis of stability, tracking  | The linearized PD gain is fixed    |

| 2003 [13]       | performance and jitter genera-   | at unity with only the qualita-    |

|                 | tion property of a bang-bang     | tive explanation on the effects of |

|                 | CDR                              | random noise                       |

| Choi, Lee, 2003 | Derivation of the effective lin- | Neglects the quantization noise    |

| [4, 12]         | earized gain of a BBPD in the    | generated by the BBPD and the      |

|                 | presence of random noise         | loop dynamics                      |

| Dalt, 2006 [6]  | Derivation of the effective lin- | Neglects loop delay effects;       |

|                 | earized gain of a BBPD in con-   | based on Markov analysis which     |

|                 | sideration of the loop dynamical | is basically an inductive method   |

|                 | behavior                         |                                    |

| Chun, 2008 [18] | Extension of [6] that includes   | Results are derived on a case-     |

|                 | the loop delay effects           | by-case basis                      |

| Dalt, 2008 [14] | JTRAN and JG analysis based      | Neglects loop delay effects;       |

|                 | on the linearized model          | quantization noise is derived in   |

|                 |                                  | an inductive method                |

| Lee, 2004 [8]   | JTOL analysis based on non-      | Neglects the effects of random     |

|                 | linear behavior (slewing and     | noise and loop delay. $K_{PD}$ es- |

|                 | dithering)                       | timation is based on a specific    |

|                 |                                  | implementation.                    |

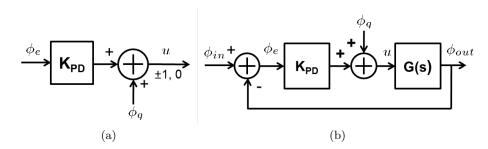

Figure 2.7: Comparison of predicted quantization error power based on our model (solid line) and the model in [14] (star)

be found by minimizing the power of the quantization error:

$$E[\phi_q^2] = E[(u(\phi_e) - K_{PD}\phi_e)^2]$$

(2.20)

yielding

$$K_{PD} = \frac{E[u(\phi_e)\phi_e]}{E[\phi_e^2]}.$$

(2.21)

Assuming that the phase error input  $\phi_e$  takes a Gaussian distribution, which is a reasonable assumption based on the central limit theorem and given that the recovered phase is the result of multiple integrations, the effective linearized gain of

the phase detector can be computed as

$$K_{PD} = \frac{\int_{-\infty}^{\infty} u(\phi_e)\phi_e f_e(\phi_e)d\phi_e}{E[\phi_e^2]}$$

$$= \frac{2\alpha_T \int_0^{\infty} \phi_e f_e(\phi_e)d\phi_e}{\sigma_e^2}$$

$$= \sqrt{\frac{2}{\pi}} \frac{\alpha_T}{\sigma_e}$$

(2.22)

where  $f_e(\phi_e)$  is the probability density function (PDF) of the phase error  $\phi_e$  and  $\alpha_T$  is the transition density of the input data stream which is same with the power of  $u(\phi_e)$  ranging from 0 to 1. Eq. (2.22) implies that the effective gain of a bangbang phase detector is inversely proportional to the standard deviation of the phase error and proportional to the transition density, which is consistent with the earlier findings in [6,12].

The power of the quantization error can be computed based on the binary characteristic of the PD's output. That is, since the phase detector output u(t) can take +1, -1, or 0, its power is simply equal to the transition density  $\alpha_T$ ;

$$E[u^{2}] = E[(K_{PD}\phi_{e} + \phi_{q})^{2}]$$

$$= K_{PD}^{2}E[\phi_{e}^{2}] + E[\phi_{q}^{2}] = \alpha_{T}.$$

(2.23)

Then, the variance of quantization error  $\sigma_q^2$  can be calculated as

$$\sigma_q^2 = \alpha_T - K_{PD}^2 \sigma_e^2 = \alpha_T - \frac{2}{\pi} \alpha_T^2 \tag{2.24}$$

where  $\sigma_e^2$  is the variance of the phase error  $\phi_e$ .

[14] asserted that the standard deviation of the input-referred quantization noise is approximately equal to three-fourths of the standard deviation of input jitter  $\sigma_{\phi_{in}}$

Figure 2.8: Comparison of the effective linear gains of a BBPD described by different models in the literature (normalized with respect to the bang-bang phase step  $\phi_{bb}$ ).

and the linearized gain of the BBPD takes an expression of

$$K_{PD} \approx \frac{1}{\sqrt{2\pi}\sigma_{\phi_{in}}} \left[1 + e^{-\frac{1}{2}\left(\frac{\phi_{bb}}{\sigma_{\phi_{in}}}\right)^2}\right]$$

(2.25)

when the transition density is 1.0. It follows that the output-referred quantization error for  $\alpha_T = 1.0$  can be expressed as

$$\sigma_q^2 = (\frac{3}{4}\sigma_{\phi_{in}})^2 K_{PD}^2$$

$$\approx \frac{9}{32\pi} [1 + e^{-\frac{1}{2}(\frac{\phi_{bb}}{\sigma_{\phi_{in}}})^2}]^2.$$

(2.26)

When  $\sigma_{\phi_{in}} \gg \phi_{bb}$ , its approximate value of  $\sigma_q^2$  becomes  $9/8\pi \approx 0.358$ . It is similar with the result based on (2.24),  $1 - 2/\pi \approx 0.363$ . As will be discussed in a later section, the simulation results for jitter generation characteristics confirm that our model in Eq. (2.24) is indeed accurate even with arbitrary transition density.

On the other hand, the variance of phase error  $\sigma_e^2$  can be calculated from the loop dynamical equations:

$$S_{\phi_e}(\omega) = S_{\phi_{in}}(\omega) \frac{1}{|1 + K_{PD}G(\omega)|^2}$$

$$+ S_{\phi_{VCO,N}}(\omega) \frac{1}{|1 + K_{PD}G(\omega)|^2}$$

$$+ S_{\phi_q}(\omega) \left| \frac{G(\omega)}{1 + K_{PD}G(\omega)} \right|^2$$

$$(2.27)$$

where  $S_{\phi_e}$ ,  $S_{\phi_{in}}$ ,  $S_{\phi_{VCO,N}}$  and  $S_{\phi_q}$  are the power spectral densities of the phase error, input random jitter, VCO's phase noise and BBPD's quantization error, respectively. Using Eq. (2.25) and given that the total noise power is equal to the PSD integrated across the entire frequency range, it follows that

$$\sigma_e^2 = \int_{-0.5}^{0.5} \frac{S_{\phi_{in}}(\omega) + S_{\phi_{VCO,N}}(\omega)}{|1 + K_{PD}G(\omega)|^2} d\omega + \int_{-0.5}^{0.5} (\alpha_T - \frac{2}{\pi}\alpha_T^2) |\frac{G(\omega)}{1 + K_{PD}G(\omega)}|^2 d\omega.$$

(2.28)

Eqs. (2.22) and (2.28) provide a basis for computing the effective linearized gain  $K_{PD}$  and the phase error power  $\sigma_e^2$  when the input phase noise PSD  $S_{\phi_{in}}(\omega)$ , the VCO phase noise PSD  $S_{\phi_{VCO,N}}(\omega)$  and the transition density  $\alpha_T$  are given. With the two variables and two equations, one can simultaneously solve them to find the solutions. For example, the solution can be found by finding the intersecting point of two equations graphically.

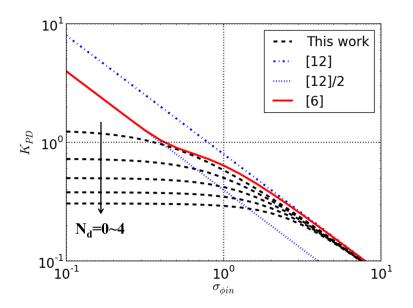

Fig. 2.8 compares the numerical values of the BBPD's linearized gain between the presented analysis and those in the literature [4, 6, 12, 14]. For instance, one alternate way of estimating the linearized gain is by computing the convolution between the BBPD's ideal input-to-output transfer function and the jitter PDF at the PD's input [4, 12]:

$$K_{PD} = \left. \frac{\partial E[u(t)]}{\partial \Delta \phi_{in}} \right|_{\phi_{in} = 0} = 2\alpha_T f(0)$$

(2.29)

where  $f(\phi_{in})$  denotes the jitter PDF. In case the input jitter takes a Gaussian distribution with a standard deviation of  $\sigma_{\phi_{in}}$ , the effective linearized gain can be expressed as:

$$K_{PD} = 2\alpha_T \left( \frac{1}{\sqrt{2\pi}\sigma_{\phi_{in}}} exp\left( -\frac{x^2}{2\sigma_{\phi_{in}}^2} \right) \right) \Big|_{x=0} = \sqrt{\frac{2}{\pi}} \frac{\alpha_T}{\sigma_{\phi_{in}}}$$

(2.30)

Fig. 2.8 shows that the gain values predicted by [12] agree with our values only for large enough input jitter conditions. It is because the derivation in [12] ignores the fact that the BBPD is within a feedback loop and therefore the input phase can move based on the BBPD's output. In other words, computing the convolution itself relies on the assumption that the input phase value and the input jitter are independent of each other; i.e. the input phase remains at a fixed value while the BBPD gives +1 or -1 outputs. This is true only when the feedback loop has low enough bandwidth, which corresponds to the case with large input jitter and hence low effective PD gain.

On the other hand, our predicted gain values agree better with those according to Eq. (2.25), which are derived based on a Markov-chain analysis that does take the feedback dynamics into account [6]. However, the discrepancies still exist for low jitter conditions, stemming from the different treatments of the quantization noise observed at the BBPD's output. While the BBPD model in [6] directly provides the discrete outputs of -1, 0, and +1, our linearized BBPD model expresses this discrete nature instead with an additive quantization noise of which power level is

derived as in Eq. (2.28). The presence of this quantization noise is the reason why our effective gain values do not keep increasing as the jitter decreases. Nonetheless, this discrepancy is irrelevant since at these low jitter conditions, the feedback loop is not sufficiently linearized and its behavior cannot be described accurately by the presented pseudo-linear analysis anyways.

It is noteworthy that the proposed expression for the effective linearized PD gain in Eq. (2.18) with two separate loops is valid over a wider range than the previously used expression in Eq. (2.29). First, Eq. (2.18) reduces to Eq. (2.29) for infinitesimally small sinusoidal perturbations, for which the detailed derivation is given in Appendix B. On the other hand, the proposed PD gain expression yields the more accurate predictions as the sinusoidal perturbation takes a finite, larger magnitude, as in the case of JTOL analysis. To illustrate this, Fig. 2.9 compares the pseudo transfer functions of a bangbang PLL measured using various amplitudes of the input sinusoidal jitter. The pseudo transfer gain at each frequency is measured by simulating the ratio between the input and output sinusoidal jitter amplitudes. For small input amplitudes, the transfer functions predicted by both the expressions Eq. (2.18) and Eq. (2.29) agree well with the simulated results. However, as the amplitude increases, the proposed PD gain expression Eq. (2.18) yields the better predictions.

In other words, the presented analysis derives the effective PD gain as the one that minimizes the quantization error considering the whole input distribution and therefore provides the better predictions. Especially, our derivation can also be applied to predicting the JTOL characteristics of the CDR without separately considering the case of slew-limiting as in [8,13] even when a large-amplitude sinusoidal

Figure 2.9: Comparison of predicted transfer functions at 10MHz with various amplitudes of sinusoidal input using transient simulation, proposed theory, and (2.29).  $\phi_{bb}$  is 0.005UI, and  $\alpha_T$  is 1.0.

jitter is applied to the BBPD's input. The application of the derived effective PD gain to the JTOL analysis will be described in later sections.

## 2.6 Jitter Transfer and Jitter Generation Analyses

This section applies the previously derived linearized gain of BBPD to the analyses of the CDR's jitter characteristics. The accuracy of the estimation is validated by comparing with the simulation results with various parameters including input noise and loop delay.

The power spectral density of the bang-bang CDR/PLL output phase noise can be derived once the linearized gain  $K_{PD}$  and the quantization noise power  $\sigma_q^2$  are computed for the pseudo-linear model in Fig. 2.6(b):

$$S_{\phi_{out}}(\omega) = S_{\phi_{in}}(\omega) \left| \frac{K_{PD}G(\omega)}{1 + K_{PD}G(\omega)} \right|^{2}$$

$$+ S_{\phi_{VCO,N}}(\omega) \frac{1}{|1 + K_{PD}G(\omega)|^{2}}$$

$$+ S_{\phi_{q}}(\omega) \left| \frac{G(\omega)}{1 + K_{PD}G(\omega)} \right|^{2}$$

$$(2.31)$$

where the first term on the right-hand side in Eq. (2.31) corresponds to the input phase noise transferred to the output, while the rest corresponds to the phase noise generated by the internal circuits. Especially, the last term is the contribution of the BBPD's quantization noise, which tends to be ignored by the majority of the prior work [4, 8, 12]. The main advantage of Eq. (2.31) is that it can help one to choose an optimal set of loop parameters that minimize the output phase noise, given the noise conditions at the input and the VCO.

To validate our pseudo-linear model, we compare its predicted results with those of behavioral simulations. Two kinds of behavioral simulation are performed for jitter transfer analysis: the stochastic AC (SAC) analysis outlined in [23] and the numerical model based on Fig. 2.1. The plurality of the results improves the fidelity of our validation.

Fig. 2.10 (a) plots the jitter transfer functions of CDRs for various noise conditions. Gaussian random jitter (RJ) with various standard deviation values (10mUI, 20mUI, 40mUI and 80mUI) is applied to the input while a transition density of 50%, a loop delay of one update cycle ( $N_d = 1$ ), and a  $\tau_N$  of 1000 are assumed. Default values are  $\phi_{bb} = 20mUI$ ,  $\tau_N = 1000$ ,  $\sigma_{\phi_{in}} = 50mUI$ ,  $\alpha_T = 0.5$ , and  $N_d = 1UI$ . Note that the predicted jitter transfer functions based on our theory match well with the simulation results from the stochastic AC analysis and the time-domain simulations.

Figure 2.10: Comparison of the jitter transfer functions with various (a)  $\sigma_{\phi_{in}}$ , (b)  $\phi_{bb}$ , (c)  $\tau_N$ , (d)  $\alpha_T$ , and (e)  $N_d$ . (f) is the comparison with [6] when  $\alpha_T = 1.0$ .

An exception is the case with 10mUI random jitter, in which case the CDR loop is not fully linearized. For comparisons, the predicted jitter transfer functions by other theory [6,12] are plotted in Fig. 2.10(f). As the theory in [6] is for the PLLs, the comparison is done with 100% of transition density. As expected [12] shows big difference comparing with other theories as it does not include the loop dynamics. The proposed theory shows good agreements with the theory in [6]. Its predicted bandwidth is slightly narrower but the difference is less than 5%. One may find a reason of the difference from the fact that Eq. (2.25) slightly overestimates the linearized gain as it limited the number of states for the simplicity [6].

Fig. 2.10(b), (c), (d) and (e) illustrate the effects of various parameters such as the bang-bang phase step  $\phi_{bb}$ , the normalized proportional-to-integral gain ratio  $\tau_N$ , the transition density of input data pattern  $\alpha_T$  and the loop delay  $N_d$  on the jitter transfer function. When the bang-bang phase step or input data transition density is big, the linearized gain of BBPD and the loop bandwidth increases. When  $\tau_N$  decreases, the zero frequency  $\omega_z$  shifts toward the higher frequency, reducing the phase margin and possibly resulting a peaking in the transfer function. The loop delay can cause similar peaking as it adds a phase shift to the open-loop transfer function.

The effective -3-dB bandwidth of a BB-PLL ( $\omega_{-3dB}$ ) can be calculated once the effective linearized gain for the BBPD is derived for the given noise/jitter condition. Since the other parts of the PLL are linear systems, the bandwidth computation is the same with that of a linear PLL. That is, the -3-dB bandwidth is the frequency when the closed-loop transfer function H(s) crosses the point -3dB below the DC

Figure 2.11: Comparison of the output jitter PSDs (a) in time-accurate behavioral simulation and (b) the proposed linear model. Simulation parameters are same with those in Fig. 2.10.

gain value (assumed 1).

$$\left| \frac{K_{PD}G(j\omega_{-3dB})}{1 + K_{PD}G(j\omega_{-3dB})} \right| = \frac{1}{\sqrt{2}}.$$

(2.32)

One complication in deriving the closed-form expression for  $\omega_{-3dB}$  is that the continoustime model G(s) in Eq. (2.2) bears the term  $e^{-sT_{ref}(N_d+1)}$  which models the effective loop latency. Since the phase shift caused by this loop latency can result in potential instability for linear PLLs as well as limit cycles for bang-bang PLLs, it must be minimized either by reducing the latency or the loop gain. In fact, if the phase shift at the bandwidth frequency  $\omega_{-3dB}T_{ref}(N_d+1)$  is sufficiently small, the exponential term can be approximated as 1, yielding a simple closed-form expression for  $\omega_{-3dB}$ :

$$\omega_{-3dB} = K_{PD}\phi_{bb}T_{ref} \tag{2.33}$$

This equation predicts the -3-dB bandwidth within 10% of error as long as the phase shift due to the loop latency  $\omega_{3dB}T_{ref}(N_d+1)$  is less than  $\pi/50$  radians.

Figure 2.12: A model of bang-bang CDR for the purpose of jitter tolerance (JTOL) analysis.

As with the jitter generation characteristics of the CDRs, the predicted power spectral densities (PSD) of the output jitter are compared against the results from time-accurate behavioral simulations [19]. Fig. 2.11(a) and (b) plot the simulated and predicted output jitter PSDs for various noise conditions for the transition density of 50%. Again, the theory and simulation results are in good agreement with the input random jitter's standard deviation values of 5  $mUI_{rms}$ , 50  $mUI_{rms}$  and 100  $mUI_{rms}$  event with non-100% transition density. Note that the simulated PSD for the 5- $mUI_{rms}$  input jitter shows spurs in multiple positions due to dithering (i.e., limit cycles) that cannot be modeled by any of the linearized models.

# 2.7 Linearized Gains of a Bang-bang Phase Detector for Jitter Tolerance Analysis

Along with the jitter transfer and jitter generation characteristics, the jitter tolerance (JTOL) is an important metric that describes the maximum tolerable amplitude of

the sinusoidal jitter which generates less than the target BER.

The work in [8] gave the asymptotes of the JTOL curves based on slewing, but it revealed a few limitations. First, it did not model the effects of random noise on the tracking behavior of the loop. Our proposed analysis suggests that the random noise can cause shift in the JTOL curve both in horizontal and vertical directions. Second, [8] did not model the effect of loop delays. Without a loop delay, the underpeaking found in some of the JTOL curves cannot be explained [20]

This section derives the parameters for our linearized BBPD model analysis, including the effective linearized gains and quantization noise. Once the parameters are derived, next subsection describes the estimation of JTOL curve including the high frequency JTOL. We find that there is a good agreement between the predicted JTOL characteristics and the simulated ones.

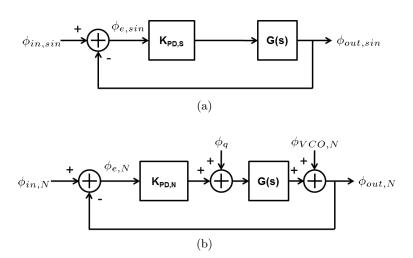

As mentioned, in the case of JTOL analysis, the BBPD receives a non-zero, time-varying deterministic input  $\phi_{e,X}(t)$ . Because the jitter tolerance measures the largest sinusoidal jitter that the CDR can tolerate with the specified BER target, it is likely that  $\phi_{e,X}(t)$  is a sinusoidal signal. This means that we will be fully utilizing the two-input linearized BBPD model in Fig. 2.5 with two different linearized gains  $K_{PD,X}$  and  $K_{PD,N}$ . Each linearized gain is determined based on Eq. (2.18), which makes the two inputs  $\phi_{e,X}(t)$  and  $\phi_{e,N}(t)$  uncorrelated with each other.

With proper selection of the two linearized gains that make the two inputs uncorrelated, we can analyze the CDR as two separate feedback loops: one with the deterministic input  $\phi_{in,sin}$  and the other with the random input  $\phi_{in,N}$ . This is illustrated in Fig. 2.12. Because the deterministic input is a sinusoidal one in this case, we use the suffix 'S' for the corresponding linearized gain  $(K_{PD,S})$ . Based on

Figure 2.13: The confluent hypergeometric functions

superposition principle, the overall output of the CDR is equal to the sum of the two loops' outputs.

According to Eq. (2.18), the linearized gains that minimize the quantization error are

$$K_{PD,S} = \frac{E\{\phi_{e,sin}(t)u(t)\}}{E\{\phi_{e,sin}^2\}}$$

$$= \frac{1}{\sigma_{e,sin}^2} \int_{-\infty}^{\infty} \int_{-\infty}^{\infty} \phi_{e,sin} N(\phi_{e,sin} + \phi_{e,N})$$

$$\cdot f_N(\phi_{e,N}) f_{sin}(\phi_{e,sin}) d\phi_{e,sin} d\phi_{e,N}$$

(2.34)

$$K_{PD,N} = \frac{E\{\phi_{e,N}(t)u(t)\}}{E\{\phi_{e,N}^2\}}$$

$$= \frac{1}{\sigma_{e,N}^2} \int_{-\infty}^{\infty} \int_{-\infty}^{\infty} \phi_{e,N} N(\phi_{e,sin} + \phi_{e,N})$$

$$\cdot f_N(\phi_{e,N}) f_{sin}(\phi_{e,sin}) d\phi_{e,sin} d\phi_{e,N}$$

(2.35)

where  $\phi_{e,sin}$  and  $\phi_{e,N}$  are the phase errors in the sinusoidal input tracking loop

and the random input tracking loop, respectively.  $\sigma_{e,sin}^2$  and  $\sigma_{e,N}^2$  denote their variances, and  $f_{sin}(\phi_{e,sin})$  and  $f_N(\phi_{e,N})$  are their probability density functions (PDFs), respectively. Assuming that the input phase during the JTOL test follows a sinusoidal trajectory with an additive Gaussian noise, PDFs  $f_{sin}(\phi_{e,sin})$  and  $f_N(\phi_{e,N})$  can be expressed as:

$$f_N(\phi_{e,N}) = \frac{2}{\sigma_{\phi_{e,N}}\sqrt{\pi}} e^{-\phi_{e,N}^2/2\sigma_{\phi_{e,N}}^2}$$

(2.36)

$$f_{sin}(\phi_{e,sin}) = \frac{1}{\pi \sqrt{(a_{in}^2 - \phi_{e,sin}^2)}}$$

(2.37)

where  $a_{in}$  is the amplitude of the sinusoidal jitter. The closed-form solutions to Eq. (2.36) and (2.37) are already given in [15]:

$$K_{PD,S} = \sqrt{\frac{2}{\pi}} (\frac{1}{\sigma_{e,N}}) M(0.5, 2, -\rho^2) \alpha_T$$

(2.38)

$$K_{PD,N} = \sqrt{\frac{2}{\pi}} (\frac{1}{\sigma_{e,N}}) M(0.5, 1, -\rho^2) \alpha_T$$

(2.39)

where  $\rho$  is the ratio between standard deviations  $\sigma_{e,sin}$  and  $\sigma_{e,N}$ , and M(a,b,z) is the confluent hypergeometric function defined as:

$$\rho = \frac{\sigma_{e,sin}}{\sigma_{e N}} \tag{2.40}$$

$$M(a, b, \rho) = \sum_{n=0}^{\infty} \frac{(a)_n \rho^n}{(b)_n n!}$$

(2.41)

where  $(a)_n = a(a+1)(a+2)\cdots(a+n-1)$ . It is a solution to Kummer's differential equation [21]:

$$z\frac{d^2w}{dz^2} + (b-z)\frac{dw}{dz} - aw = 0. {(2.42)}$$

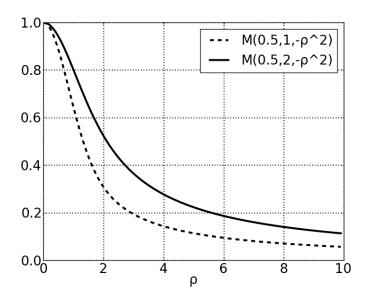

Fig. 2.13 plots the values of this  $M(a,b,-\rho^2)$  function for the two pairs of (a,b) used

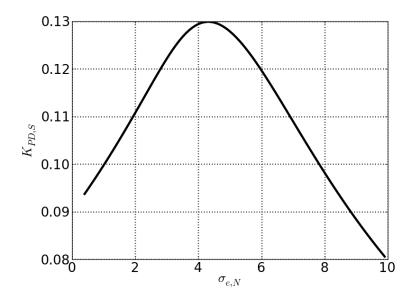

Figure 2.14: The  $K_{PD,S}$  versus  $\sigma_{e,N}$  when the sum of  $\sigma_{e,N}$  and  $\sigma_{e,sin}$  is limited to 10.

- 1. Find initial values for  $K_{PD,N}$  and  $\sigma_{e,N}$  assuming  $\rho = 0$  (i.e. random jitter only)

- 2. Derive initial values for  $K_{PD,N}$ ,  $\sigma_{e,sin}$  and  $\rho$ : use  $K_{PD,S} = K_{PD,N}$  and Eq. (2.43).

- 3. Perform the following iteration:

- a. Calculate  $K_{PD,S}$ ,  $K_{PD,N}$  and  $\sigma_q$  from  $\sigma_{e,sin}$ ,  $\sigma_{e,N}$  and  $\rho$  using Eqs. (2.38), (2.39), (2.46).

- b. Calculate  $\rho$ ,  $\sigma_{e,sin}$  and  $\sigma_{e,N}$  from  $K_{PD,S}$ ,  $K_{PD,N}$  and  $\sigma_{N}$  using Eqs. (2.40), (2.43) and (2.45)

- c. Repeat a-b until the solutions converge.

Figure 2.15: JTOL calculation procedure.

in Eqs. (2.38) and (2.39).

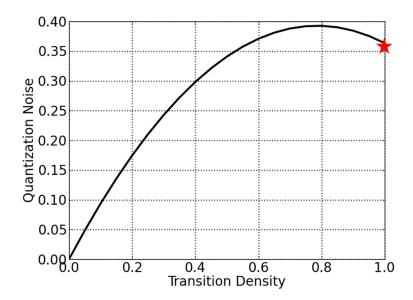

Fig. 2.13 shows that  $M(a, b, -\rho^2)$  is a decreasing function of  $\rho$ , which means it is also an increasing function of  $\sigma_{e,N}$ . It is interesting to note that the inversely proportional relationship between the PD gain and  $\sigma_{e,N}$  is weakened by  $M(a, b, -\rho^2)$ , but it is still a decreasing function of  $\sigma_{e,N}$  as  $1/\sigma_{e,N}$  decreases faster than the rate at

which  $M(a, b, -\rho^2)$  increases. However, when the sum of  $\sigma_{e,N}$  and  $\sigma_{e,sin}$  is limited, it is no longer a decreasing function of  $\sigma_{e,N}$ , as shown in Fig. 2.14. This relationship will be used for the explanation of the random noise's effect on JTOL in the next section.

With zero deterministic input (i.e.,  $\sigma_{e,sin} = 0$ ), Eqs. (2.38) and (2.39) reduce to Eq. (2.30). On the other hand, as the sinusoidal jitter increases, the sensitivity of the linearized gains with respect to the random noise diminishes. In this case, the phase error is dominated by the sinusoidal portion of the input phase and the random noise has relatively less influence on the linearized gains.

The standard deviation of the phase error in the sinusoidal input tracking loop  $\sigma_{e,sin}$  can be derived from the loop's transfer function, evaluated at the sinusoidal jitter frequency  $\omega$ :

$$\sigma_{e,sin} = \frac{\sigma_{in,sin}}{|1 + K_{PD,S}G(e^{j\omega T_{ref}})|}.$$

(2.43)

Because the phase error is also a sinusoidal signal, its amplitude  $a_{e,sin}$  can be calculated from its standard deviation:

$$\sigma_{e,sin}^2 = a_{e,sin}^2 / 2. (2.44)$$

The standard deviation of the phase error in the random input tracking loop  $\sigma_{e,N}^2$  must be calculated by integrating its output power spectral density (PSD) over the entire frequency:

$$\sigma_{e,N}^{2} = \int_{-0.5}^{0.5} \frac{S_{\phi_{in,N}}(\omega)}{|1 + K_{PD,N}G(\omega)|^{2}} d\omega$$

$$+ \int_{-0.5}^{0.5} \frac{S_{\phi_{vco,N}}(\omega)}{|1 + K_{PD,N}G(\omega)|^{2}} d\omega$$

$$+ \int_{-0.5}^{0.5} \sigma_{q}^{2} \left| \frac{-G(\omega)}{1 + K_{PD,N}G(\omega)} \right|^{2} d\omega.$$

(2.45)

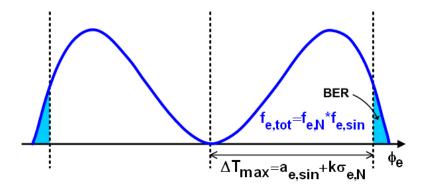

Figure 2.16: BER estimation in presence of sinusoidal and random components in the phase error.

And the quantization error power  $\sigma_q^2$  can be found by carrying out a similar analysis with Eq. (2.24):