Ph.D. DISSERTATION

# FLOATING-POINT SUPPORT FOR COARSE-GRAINED RECONFIGURABLE ARCHITECTURES

### 재구성형 연산 구조를 위한 부동소수점 지원

BY

MANHWEE JO

FEBRUARY 2014

DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE COLLEGE OF ENGINEERING SEOUL NATIONAL UNIVERSITY

Ph.D. DISSERTATION

# FLOATING-POINT SUPPORT FOR COARSE-GRAINED RECONFIGURABLE ARCHITECTURES

### 재구성형 연산 구조를 위한 부동소수점 지원

BY

MANHWEE JO

FEBRUARY 2014

DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE COLLEGE OF ENGINEERING SEOUL NATIONAL UNIVERSITY

## FLOATING-POINT SUPPORT FOR COARSE-GRAINED RECONFIGURABLE ARCHITECTURES

재구성형 연산 구조를 위한 부동소수점 지원

지도교수 최기 영

이 논문을 공학박사 학위논문으로 제출함

2013 년 11 월

서울대학교 대학원

전기 컴퓨터 공학부

#### 조 만 휘

조만휘의 공학박사 학위논문을 인준함 2013 년 12 월

| 위 원 장      | 채수익   | (인) |

|------------|-------|-----|

| 부위원장       | 최 기 영 | (인) |

| 위 원        | 백 윤 흥 | (인) |

| 위 원<br>위 원 | 이종은   | (인) |

| 위 원        | 김 윤 진 | (인) |

### Abstract

With a huge increase in demand for various kinds of compute-intensive applications in electronic systems, researchers have focused on coarse-grained reconfigurable architectures because of their advantages: high performance and flexibility. Besides, supporting floating-point operations on coarse-grained reconfigurable architecture becomes essential as the increase of demands on various floating-point inclusive applications such as multimedia processing, 3D graphics, augmented reality, or object recognition. This thesis presents FloRA, a coarse-grained reconfigurable architecture with floating-point support. Twodimensional array of integer processing elements in FloRA is configured at runtime to perform floating-point operations as well as integer operations. More specifically, each floating-point operation is performed by two integer processing elements, one for mantissa and the other for exponent. Fabricated using 130nm process, the total area overhead due to additional hardware for floating-point operations is about 7.4% compared to the previous architecture which does not support floating-point operations. The fabricated chip runs at 125MHz clock frequency and 1.2V power supply. Experiments show 11.6x speedup on average compared to ARM9 with a vector-floating-point unit for integer-only benchmark programs as well as programs containing floatingpoint operations. Compared with other similar approaches including XPP and Butter, the proposed architecture shows much higher performance for integer applications, while maintaining about half the performance of Butter for floating-point applications.

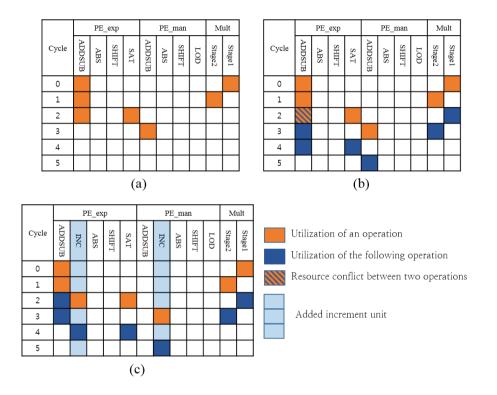

This thesis also proposes novel techniques to enhance utilization of integer units for high-throughput floating-point operations on CGRA. The approach to implementing floating-point operations on CGRA presented in this thesis enables floating-point functionality with less area overhead compared to the traditional approach of employing separate floating-point units (FPUs). However the total latency of a floating-point operation is larger than that of the traditional approach and the data dependency between split integer operations restricts further enhancement in terms of utilization of integer functional units in an operation. In order to overcome such inefficiency, two techniques are proposed in this thesis. One is overlapping two distinct floating-point operations, which increases the efficiency in terms of utilizations of integer functional units in the architecture. Free integer functional units in a floating-point operation can be used for another floating-point operation with this technique. The other is forwarding between two data-dependent floating-point operations, which decreases effective latency of the floating-point operations. The basic idea is to remove unnecessary calculations such as formatting which is normally done in between the two data-dependent floating-point operations. To implement the

overlapping or forwarding, FSMs and control paths in each PE are modified and temporal/communication registers are added. Light-weight sub-module such as increment units and registers for intermediate values are added for releasing resource conflict. Experiment is done with several arithmetic functions that are widely used in floating-point applications. The base architecture and the new architecture implementing the proposed technique are compared in terms of throughput and area overhead. The experimental result shows that the proposed technique increases the throughput by 33.9% on average with 20.9% of area overhead.

Keywords: Coarse-Grained Reconfigurable Architectures, floating-point num-

bers

Student Number: 2007-21094

## Contents

| Abstra  | ct     |                                          | i  |

|---------|--------|------------------------------------------|----|

| Conter  | its    |                                          | v  |

| List of | Figure | 5                                        | ix |

| List of | Tables |                                          | XV |

| Chapte  | er 1 I | NTRODUCTION                              | 1  |

| Chapte  | er 2 7 | ARGET ARCHITECTURE                       | 7  |

| 2.1     | Overa  | Il Architecture                          | 7  |

| 2.2     | Recor  | nfigurable Computing Module              | 8  |

| Chapte  | er 3 I | DEGISN OF FLOATING-POINT OPERATIONS      | 15 |

| 3.1     | Floati | ng-point Numbers                         | 15 |

|         | 3.1.1  | Representation of floating-point numbers | 15 |

|         | 3.1.2  | Floating-point operations                | 19 |

| 3.2    | FPU-PE Cluster                                           | 20 |

|--------|----------------------------------------------------------|----|

|        | 3.2.1 Construction of FPU-PE Cluster                     | 20 |

|        | 3.2.2 Construction of Array of FPU-PE Clusters           | 21 |

|        | 3.2.3 Comparing Different FPU-PE Clusters                | 23 |

| 3.3    | Implementation of Multi-Cycle Operations                 | 26 |

| 3.4    | Implementation of Floating-Point Operations              | 30 |

| 3.5    | Implementation of Floating-Point Operations Using Shared |    |

|        | Modules                                                  | 32 |

| Chapte | r 4 Chip Implementation                                  | 35 |

| 4.1    | Specification of Chip Implementation                     | 35 |

| 4.2    | Experimental Setup                                       | 38 |

| 4.3    | Experimantal Results                                     | 39 |

|        | 4.3.1 Performance Comparison                             | 39 |

|        | 4.3.2 Power Consumption Comparison                       | 42 |

| Chapte | r 5 Comparison with Other Architectures                  | 45 |

| 5.1    | Preparation for the comparison                           | 45 |

| 5.2    | Comparison with PACT XPP                                 | 47 |

| 5.3    | Comparison with Butter Architecture                      | 50 |

| 5.4    | Implication of the proposed architecture                 | 57 |

| Chapte | r 6 Enhancement Techniques                               | 63 |

| 6.1     | Introc | luction                                            | 63  |

|---------|--------|----------------------------------------------------|-----|

| 6.2     | Conve  | entional Approach                                  | 64  |

|         | 6.2.1  | Base Architecture                                  | 64  |

|         | 6.2.2  | Utilization of Floating-Point Operations           | 65  |

| 6.3     | Propo  | sed Enhancement Techniques                         | 66  |

|         | 6.3.1  | Overlapping Technique                              | 66  |

|         | 6.3.2  | Forwarding Technique                               | 71  |

| 6.4     | Exper  | iments                                             | 76  |

|         | 6.4.1  | Performance Comparison                             | 76  |

|         | 6.4.2  | Hardware Cost of the Proposed Techniques           | 77  |

|         | 6.4.3  | Utilization Enhancement by the Proposed Techniques | 80  |

| 6.5     | Comp   | parison with Other Architecture                    | 87  |

| Chapte  | r7 (   | Conclusion                                         | 93  |

| Bibliog | raphy  |                                                    | 95  |

| 국문초     | 록      |                                                    | 103 |

| 감사의     | 글      |                                                    | 105 |

# List of Figures

| Figure 2.1 | The overall structure of the target architecture            | 8  |

|------------|-------------------------------------------------------------|----|

| Figure 2.2 | The interconnection topology in PE array. Solid line means  |    |

|            | one-way bus interconnects from/to data memory while         |    |

|            | dotted line means peer-to-peer interconnects. Each dot-     |    |

|            | ted line is physically implemented as two one-way inter-    |    |

|            | connects.                                                   | 9  |

| Figure 2.3 | The inner-structure of PE and the shared modules in PE      |    |

|            | array                                                       | 11 |

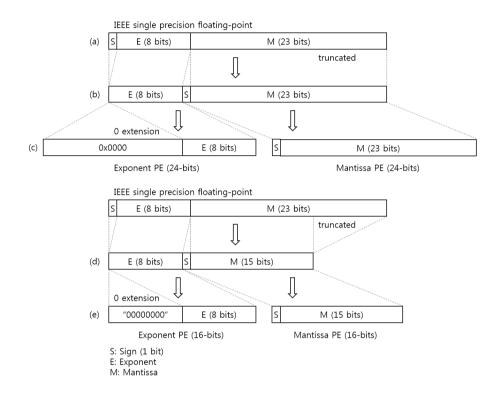

| Figure 3.1 | Floating-point formats: (a) 32-bit IEEE-754 simple pre-     |    |

|            | cision, (b) 32-bit format internally used in PE array which |    |

|            | has 24-bit data-path, (c) separation of a 32-bit floating-  |    |

|            | point value, (d) reduced 24-bit format internally used in   |    |

|            | PE array which has 16-bit data-path, and (e) separation     |    |

|            | of a 24-bit floating-point value.                           | 16 |

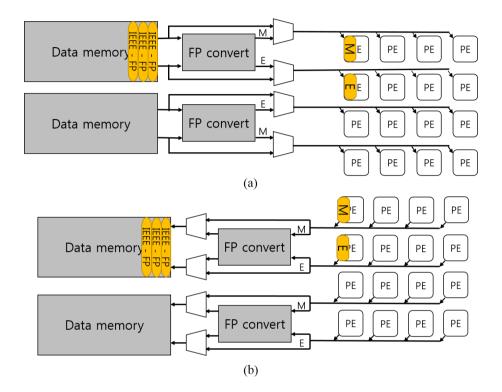

| Figure 3.2 | Floating-point format between PE array and the data mem-     |    |

|------------|--------------------------------------------------------------|----|

|            | ory. (a) shows the data-path from the data memory to the     |    |

|            | PE array, and (b) shows the data-path from the PE ar-        |    |

|            | ray to the data memory. Yellow tokens represent floating-    |    |

|            | point data                                                   | 18 |

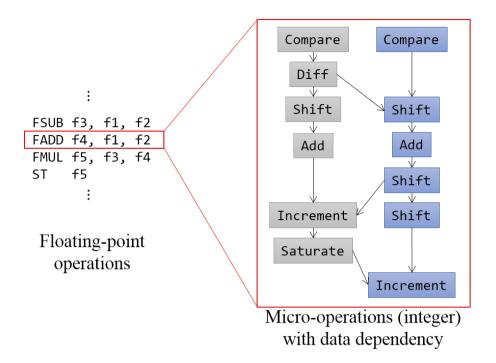

| Figure 3.3 | A floating-point addition operation boxed in the left side   |    |

|            | is split into several integer micro-operations with data de- |    |

|            | pendency                                                     | 19 |

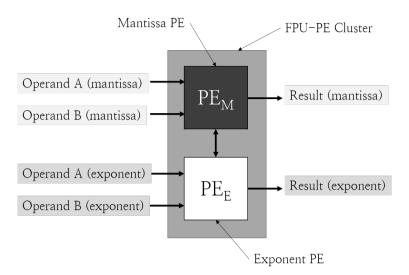

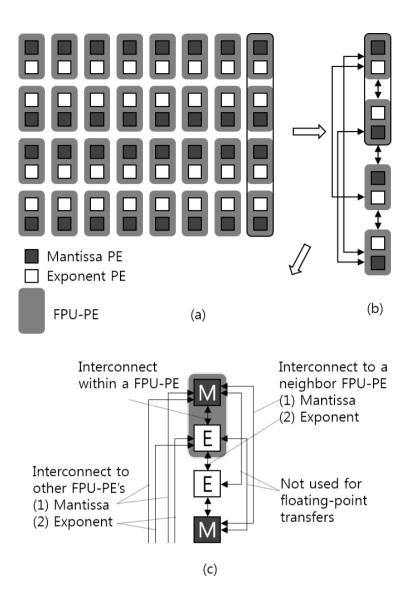

| Figure 3.4 | Overview of FPU-PE cluster.                                  | 21 |

| Figure 3.5 | Construction of FPU-PE cluster array: (a) locations of       |    |

|            | Mantissa PEs and Exponent PEs in PE array and con-           |    |

|            | structed FPU-PE array, (b) abstracted interconnection among  |    |

|            | RPU-PE clusters, and (c) interconnection of an FPU-PE        |    |

|            | cluster in detail                                            | 22 |

| Figure 3.6 | Normalized hardware area of the three different clustering   |    |

|            | cases                                                        | 25 |

| Figure 3.7 | Reconfiguration of a PE in the (a) base architecture, and    |    |

|            | (b) FSM-included architecture                                | 27 |

| Figure 3.8 | Behavior of floating-point addition for each cycle           | 31 |

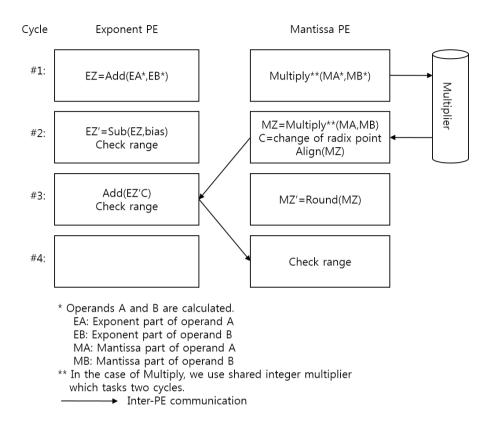

| Figure 3.9 | Behavior of floating-point multiplication for each cycle     | 33 |

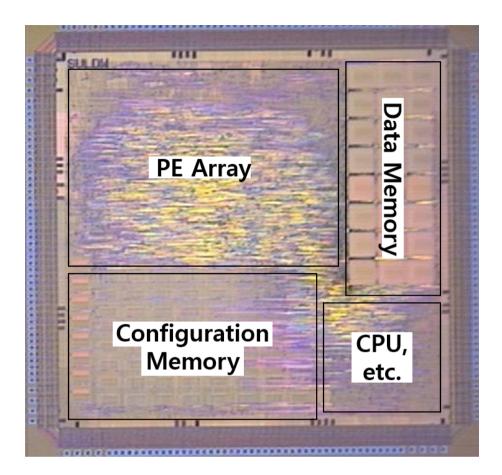

| Figure 4.1 | Micrograph of the fabricated chip.                           | 37 |

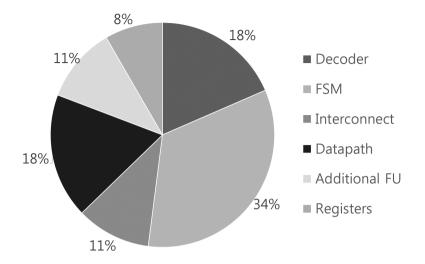

| Figure 4.2 | Area breakdown of the increased hardware                                                                                                                                                                                                       | 38 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

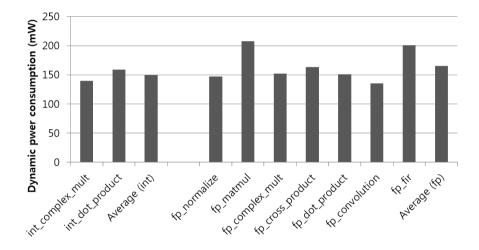

| Figure 4.3 | Dynamic power consumption of the benchmark kernels on the fabricated chip.                                                                                                                                                                     | 44 |

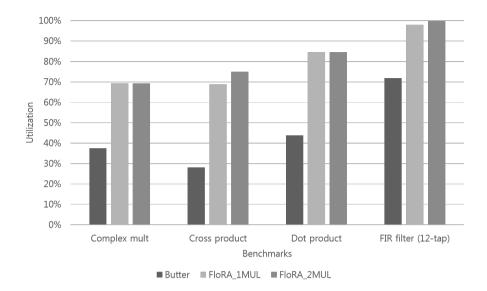

| Figure 5.1 | Comparison of the utilizations of the architectures for the floating-point kernels.                                                                                                                                                            | 55 |

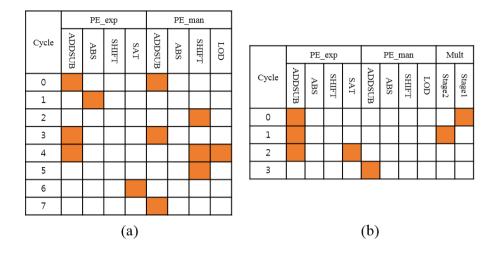

| Figure 6.1 | Utilization of integer functional units in an FPU-PE clus-<br>ter. (a) is for an FADD/FSUB operation, while (b) is for<br>FMUL operation. Colored box indicates that the func-<br>tional unit is utilized at the cycle                         | 66 |

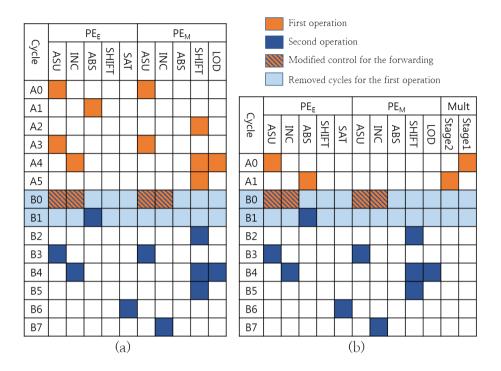

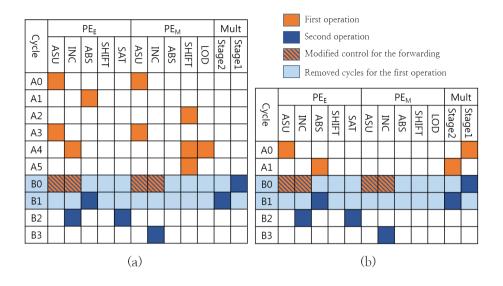

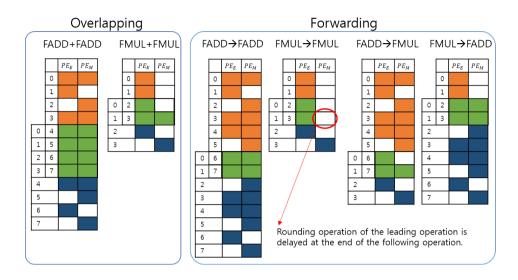

| Figure 6.2 | Utilization of integer functional units in an FPU-PE cluster<br>for a FADD operation: (a) for an operation, (b) for two<br>overlapped operations without additional functional unit,<br>(c) for two overlapped operations with functional unit | 69 |

| Figure 6.3 | Utilization of integer functional units in an FPU–PE cluster<br>for a FMUL operation: (a) for an operation, (b) for two<br>overlapped operations without additional functional unit,<br>(c) for two overlapped operations with functional unit | 70 |

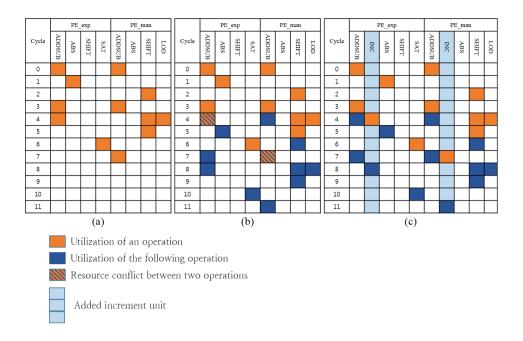

| Figure 6.4  | Utilization of integer functional units in an FPU-PE clus-   |    |

|-------------|--------------------------------------------------------------|----|

|             | ter in the case that the output of the leading operation is  |    |

|             | forwarded: (a) from FADD to FADD, and (b) from FMUL          |    |

|             | to FADD                                                      | 73 |

| Figure 6.5  | Utilization of integer functional units in an FPU-PE cluster |    |

|             | in the case that the output of the leading operation is for- |    |

|             | warded: (a) from FADD to FMUL, and (b) from FMUL             |    |

|             | to FMUL                                                      | 75 |

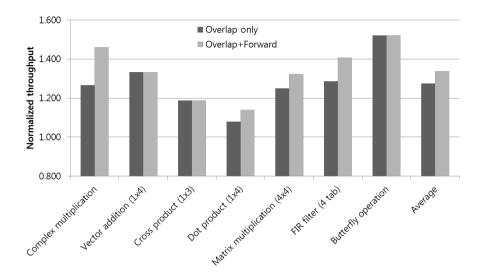

| Figure 6.6  | Normalized throughputs of the architectures where the        |    |

|             | enhancement technieuqs are applied compared to the base      |    |

|             | architecture                                                 | 77 |

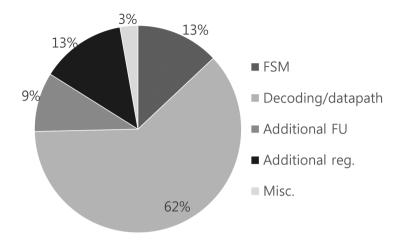

| Figure 6.7  | Area breakdown of the additional hardware for applying       |    |

|             | overlapping technique to the base architecture where any     |    |

|             | enhancement techniques are applied                           | 78 |

| Figure 6.8  | Area breakdown of the additional hardware for applying       |    |

|             | forwarding technique to the architecture where the over-     |    |

|             | lapping technique is applied                                 | 79 |

| Figure 6.9  | Utilizations of functional units of PEs during floating-     |    |

|             | point operations and their redefined utilizations            | 81 |

| Figure 6.10 | Utilizations of functional units of PEs where the enhance-   |    |

|             | ment techniques are applied                                  | 82 |

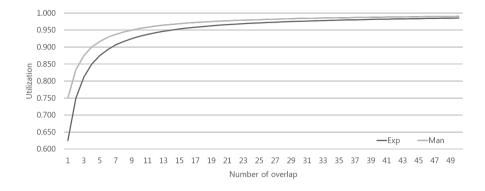

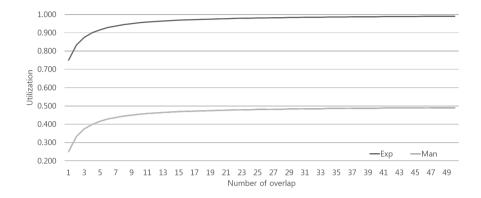

| Figure 6.11 | Utilization trends where FADD/FSUB are overlapped. "Exp"  |    |

|-------------|-----------------------------------------------------------|----|

|             | and ``Man" stand for the exponent PE and the mantissa PE, |    |

|             | respectively                                              | 83 |

|             |                                                           |    |

|             |                                                           |    |

| Figure 6.12 | Utilization trends where FMUL are overlapped. "Exp" and   |    |

|             | "Man" stand for the exponent PE and the mantissa PE,      |    |

|             | respectively                                              | 84 |

|             |                                                           |    |

| F' (12      |                                                           |    |

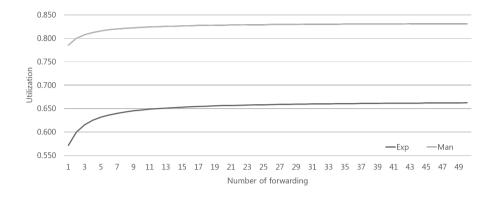

| Figure 6.13 | Utilization trends where FADD/FSUB are forwarded. "Exp"   |    |

|             | and "Man" stand for the exponent PE and the mantissa PE,  |    |

|             | respectively                                              | 85 |

|             |                                                           |    |

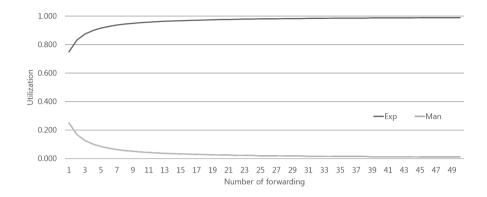

| Figure 6.14 | Utilization trends where FMUL are forwarded. "Exp" and    |    |

| 0           | "Man" stand for the exponent PE and the mantissa PE,      |    |

|             | respectively.                                             | 86 |

|             | respectively                                              | 00 |

|             |                                                           |    |

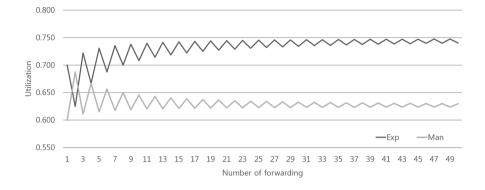

| Figure 6.15 | Utilization trends where FADD/FSUB and FMUL are for-      |    |

|             | warded alternately. "Exp" and "Man" stand for the expo-   |    |

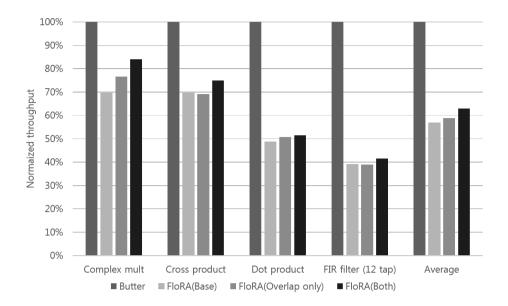

| Comparison of the normalized throughputs for floating-    |                                                                                                                                                                                                                                            |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| point benchmark kernels. FloRA(base) is the base archi-   |                                                                                                                                                                                                                                            |

| tecture, where the enhancement techniques are not ap-     |                                                                                                                                                                                                                                            |

| plied, FloRA(overlap_only) is the architecture implement- |                                                                                                                                                                                                                                            |

| ing the overlapping technique, and FloRA(Both) is the ar- |                                                                                                                                                                                                                                            |

| chitecture implementing both overlapping and forwarding   |                                                                                                                                                                                                                                            |

| techniques.                                               | 90                                                                                                                                                                                                                                         |

|                                                           | tecture, where the enhancement techniques are not ap-<br>plied, FloRA(overlap_only) is the architecture implement-<br>ing the overlapping technique, and FloRA(Both) is the ar-<br>chitecture implementing both overlapping and forwarding |

# List of Tables

| Table 3.1 | Comparison between different FPU-PE clusters               | 23 |

|-----------|------------------------------------------------------------|----|

| Table 3.2 | Properties of implemented floating-point operations        | 26 |

| Table 3.3 | Comparison of hardware cost per PE                         | 28 |

| Table 3.4 | Comparison of memory usages for 9/7tap wavelet transforms  | 29 |

| Table 4.1 | Performances of benchmark kernels accelerated by FloRA .   | 40 |

| Table 5.1 | Comparison of different FloRA implementations              | 46 |

| Table 5.2 | Comparison of hardware features of PACT XPP and FloRA      | 48 |

| Table 5.3 | Comparison of performances between PACT XPP and FloRA      |    |

|           | running 9/7 tap discrete wavelet transform                 | 49 |

| Table 5.4 | Comparison of hardware features of PEs in different archi- |    |

|           | tectures                                                   | 52 |

| Table 5.5 | Comparison of performance between Butter architecture      |    |

|           | and FloRA                                                  | 54 |

| Table 5.6 | Minimum ratio of the integer computation to the floating-   |    |

|-----------|-------------------------------------------------------------|----|

|           | point computation of applications which is better to be ex- |    |

|           | ecuted on FloRA                                             | 61 |

|           |                                                             |    |

| Table 6.1 | Utilization of PEs in a FPU-PE cluster                      | 67 |

| Table 6.2 | Clock frequencies of different versions of FloRA            | 88 |

| Table 6.3 | Minimum ratio of the integer computation to the floating-   |    |

|           | point computation of applications which is better to be ex- |    |

|           | ecuted on FloRA with enhancement techniques applied         | 91 |

### Chapter 1

### INTRODUCTION

Not many years ago, phones are used just for calling, but today they are used for playing audios/videos, surfing web, image processing, and enjoying games. Not only phones but also tablets have been gaining popularity rapidly and are now a part of our daily lives. However, as the functionality of such mobile devices becomes more diverse and complex, supporting them with limited resources is a big challenge. Multicores are not enough to meet the requirement of compute-intensive programs even though they are suitable for running several control-intensive problems simultaneously. ASICs can hardly support various programs since we cannot put tens or hundreds of them into a single chip. In addition to that, we have encountered another challenge. While conventional compute-intensive programs such as multimedia applications are based on integer calculation, new ones such as 3D graphics, augmented reality, object recognition, or face recognition require real number operations. Thus, efficient support for both fixed- and floating- point operations with limited resources is also important in future embedded systems.

With a huge increase of various high-performance multi-media applications running on a portable device, great attention to reconfigurable array architectures has been built up since such architectures can be a key to performance and flexibility [1, 2, 3, 4, 5, 6, 7, 8, 9, 10]. According to the granularity, we can classify such architectures into fine-grained reconfigurable array (FGRA) and coarse-grained reconfigurable array (CGRA). A representative example of FGRA is FPGA, which has an array of gates. On the other hand, CGRAs typically have an array of arithmetic and logic units (ALUs) or processing elements (PEs) so they can accelerate the execution of programs by parallel processing. In addition, they can run various applications by changing the functionality of hardware dynamically through the reconfiguration of the PEs and the interconnections between them. CGRAs have an advantage over FGRAs in that they can quickly adapt to a new application through dynamic reconfiguration. It is mainly due to the coarser granularity that renders less configuration overheads. CGRA has been proved to be one of viable solutions since it can provide performance and flexibility at the same time.

In spite of the advantages of CGRAs, most of the existing architectures are

limited to integer-based applications such as audio-visual data codec [2, 11], wireless communication [7], cryptography [8], and so on. Thus they are not able to meet the demands for floating-point-based applications effectively. Physics engines in 3-dimensional (3D) graphics are representative examples that cannot be handled efficiently by a conventional CGRA. There have been researches on implementing 3D rendering [12, 13] and ray tracing [14] with reconfigurable architectures. However, their approaches have limitations in generating high quality results due to the lack of floating-point computation.

Adding floating-point units (FPUs) to the integer-only reconfigurable architecture can be a solution to the above-mentioned problem. There have been several related researches on FPGAs. [15] introduces an FPGA including FPUs. [16] shows a design-space exploration for efficient implementation of floatingpoint operations on an FPGA by adding extra modules such as multipliers and FPUs or by modifying look-up tables (LUTs) for efficient binding. However, the area cost due to those approaches is significantly high, especially when multiple floating-point units are added. Moreover, the added units are not utilized at all when integer-based applications are running on the system. By the same token, the integer PEs will be useless when floating-point-based applications are running.

Another solution to the problem is reconfiguring existing units such that they can perform the floating-point operations [17, 18, 19, 20, 21, 22, 23].

[17] suggests a novel FPGA architecture and efficient implementation methods of floating-point operations on that architecture. However, implementing floating-point units using LUTs in FPGAs requires much more time to reconfigure the circuit than coarse-grained reconfigurable architecture. Thus it is hard to accelerate applications mixed with integer operations and floatingpoint operations. Coarse-grained reconfigurable architectures support reconfiguration with much less reconfiguration time (one cycle in our architecture). Thus the processing elements (PEs) in the architecture can be reconfigured to execute floating-point operations right after executing integer operations. The approaches in [18, 19, 20, 21] combine a pair of integer PEs to perform a floating-point operation. Since there are many PEs in an array, it is possible to perform multiple floating-point operations in parallel. For an efficient implementation of the floating-point operations, they use separate FSMs in addition to the configuration of the architecture. In this thesis, we present details of the chip implementation and experimental results of a coarse-grained reconfigurable architecture called FloRA (Floating-point-capable Reconfigurable Array), which supports floating-point operations as well as integer operations. Since the floating-point operations are performed with multiple integer PEs, the architecture does not have any separate floating-point units. This allows the architecture to have extended applicability with less hardware overhead.

There are other approaches to implementing floating-point operations ex-

ploiting the existing integer functional units in a CGRA. One of them is PACT XPP [24], a commercial coarse–grained reconfigurable architecture [23]. Their approach relies only on configurations of the existing architecture without any additional hardware support for floating–point operations and thus results in an inefficient implementation in terms of performance–to–area ratio. Another approach uses Butter architecture [25, 26, 27] where floating–point operations are implemented using its integer addition/subtraction units and multiplication units. Those architectures will be compared with our architecture in the later chapter.

Proposed approach of sharing integer functional units for floating-point operations has more latency than stand-alone floating-point units while the area overhead is much less. Besides, there could be utilization losses when floatingpoint operations are executed on PEs since each single functional unit in those PEs are not busy during the whole execution cycles. In order to overcome the implications above, two techniques are proposed in this thesis. One is overlapping two floating-point operations and the other is forwarding between the two floating-point operations which are data-dependent. The former enhances the utilization of the architecture while the latter increases the effective latency of the floating-point operations.

The organization of the thesis is as follows. Chapter 2 describes the template of the target CGRA in detail. Chapter 3 explains the design for floating-point

operations on the target architecture. Chapter 4 presents the characteristics of the fabricated chip of the target architecture and the experimental results obtained from chip test. Chapter 5 compares the target architecture with other architectures where similar floating-point implementation techniques are applied. Chapter 6 introduces the enhancement techniques for the implemented floating-point operations. Finally, Chapter 7 concludes.

### Chapter 2

## TARGET ARCHITECTURE

#### 2.1 Overall Architecture

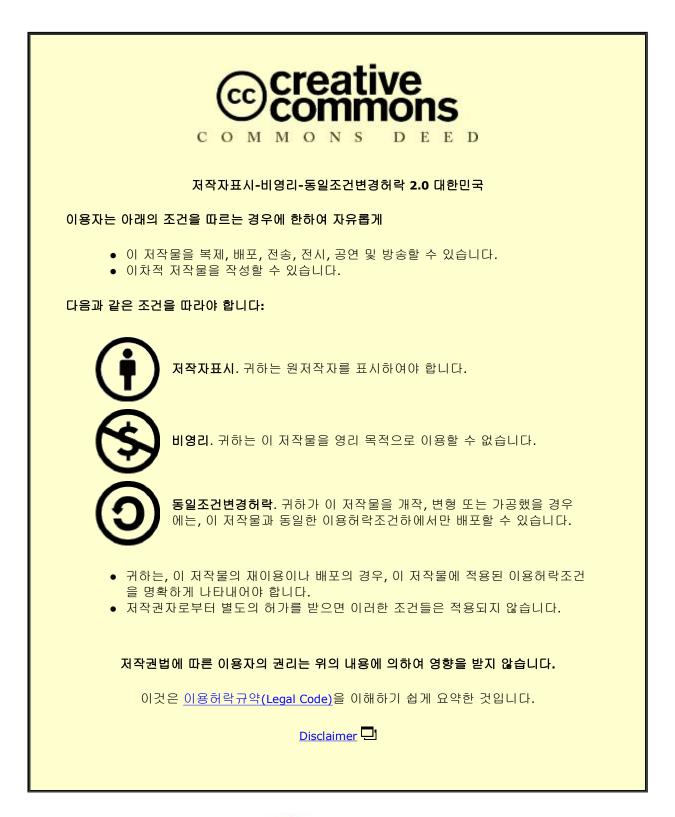

Figure 2.1 shows the overall architecture of FloRA. It consists of a RISC processor, a main external memory block, a DMA controller, and a reconfigurable computing module (RCM). All the components are connected through a data bus. Before executing an application on the architecture, the RISC processor initializes all other components in the architecture. It also controls them during the execution of the application. In addition, it executes control-intensive and irregular code blocks of the application while the RCM accelerates data-intensive and repetitive code blocks such as DSP kernels or matrix-vector calculations, which can be easily parallelized. The DMA controller is used for efficient communications between the RCM and the main memory.

Figure 2.1 The overall structure of the target architecture.

#### 2.2 Reconfigurable Computing Module

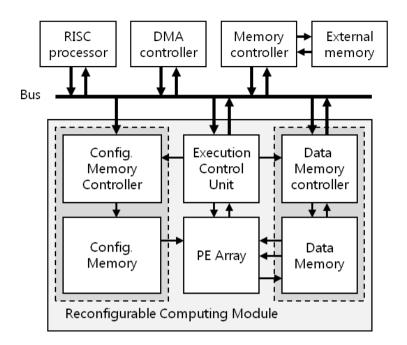

The RCM is in charge of accelerating data-intensive code blocks using an array of PEs. A PE is an ALU-like functional unit that can handle 16-bit integer values. The PE array is designed for accelerating data-intensive kernel code blocks by parallelizing independent operations in a code block on the array of PEs. As shown in Figure 2.2, each PE in the array has interconnections to its neighbor PEs (top, bottom, left, and right). Each PE also has interconnections to the PEs in two-hop distance in vertical and horizontal direction, and so on, so that it

Figure 2.2 The interconnection topology in PE array. Solid line means oneway bus interconnects from/to data memory while dotted line means peer-topeer interconnects. Each dotted line is physically implemented as two one-way interconnects.

can communicate directly with other PEs in a cycle via those interconnections without having to pass through neighbor PEs one-by-one along the paths. Such abundant interconnection resources make it easy to map data-flow graphs onto the array [28, 29].

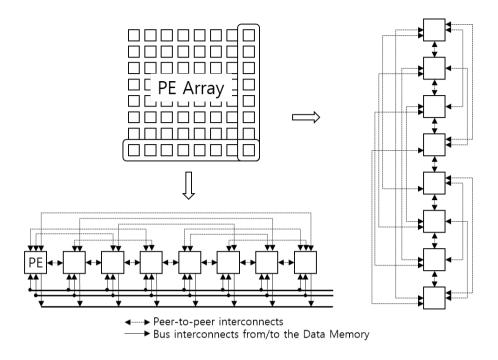

Each PE can perform arithmetic operations and logical operations including shift operations and compare and select operations. Thus a PE can be considered

as a small processor without instruction fetch unit and branch unit as shown in Figure 2.3. Some operations (critical operations) such as multiplication and division require functional units that require much larger area and delay than other operations. Each of the critical functional units such as multipliers and dividers is shared by a set of PEs. In the Figure 2.3, pipelined multipliers (blue boxes) are shared by a row of PEs. Because of the reason, the executions of those functional units by the PEs are scheduled ahead of time [6]. Since the critical functional units typically have longer delays, they are pipelined so that they do not degrade the overall system throughput. The number of critical functional units integrated into the array is much less than the number of PEs, thereby saving much area and power consumption at the cost of ignorable performance degradation. In case of division, it is a common practice to change divisions into shift operations for applications that are not very sensitive to accuracy. Thus the number of dividers can be further reduced compared to the number of multipliers.

The PEs are configured by configuration control unit (CCU) and a set of configuration memory elements (CEs). Configuration Memory in Figure 2.1 is basically an array of CEs. Each CE provides the configuration data to the corresponding PE or row of PEs depending on mapping strategies. The architecture supports two different mapping strategies: spatial mapping and temporal mapping. In the spatial mapping, every PE has its own configuration data fetched

Figure 2.3 The inner-structure of PE and the shared modules in PE array.

from its corresponding CE in order to implement the kernel's dataflow on the two-dimensional array of PEs. The data stream loaded from the data memory in the RCM flows along the array of PEs and the results are stored back to the data memory. In this strategy, if the dataflow is larger than the array size, it cannot be mapped onto the array. On the other hand, in the temporal mapping, the kernel's dataflow is implemented on a column of PEs. Every cycle, new configuration data fetched from the CEs change the configuration of the column according to the dataflow. In this strategy, only a column of PEs can run the entire dataflow, since the PEs can be reconfigured every cycle to perform any necessary operations in the dataflow. Therefore, any dataflow can be mapped onto the array regardless of the size (provided that the CEs can store

all the configuration data). Since there are multiple columns of PEs, multiple iterations of a kernel loop can be executed in parallel through loop pipelining. The configuration memory has a hybrid structure [30] in order to support both strategies.

CCU has a simple address generation mechanism for the configuration memory, called macro configuration. In this mechanism, macro configuration operations (MCOs) are used for address generation. Each MCO is 2-byte long and consists of start address, address count, etc. MCOs are stored in a memory block, called MCO table, in CCU. To execute RCM, CCU fetches MCOs from the MCO table and generates a sequence of addresses corresponding to each fetched MCO. The generated addresses are sent to the configuration memory one by one to load the configuration words onto the PE array. With this mechanism, frequently used chunks of configuration words can be reused just by duplicating MCOs, which saves a lot of configuration memory space.

The data memory in the RCM contains data to be processed in the PE array. There are two sets of data memory used to support double buffering for hiding communication overhead. Each set of data memory consists of three banks. By adjusting control registers, each bank of the data memory can be attached to one of three read/write data buses (shown in Figure 2.2) in the PE array. Two banks are used for input and the remaining one is used for output. All PEs in a column can access the data memory at the same time. But PEs in each row share the data buses so that only one PE can read/write data from/to memory through a bus at a time (since there are three buses, three PEs in a row can access the memory at a time).

# Chapter 3

# DEGISN OF FLOATING-POINT OPERATIONS

### 3.1 Floating-point Numbers

#### 3.1.1 Representation of floating-point numbers

Floating-point representation internally used in the PE array is different from the IEEE standard 754 [31]. In the single precision of the IEEE standard, the floating-point representation consists of 1-bit sign, 8-bit exponent, and 23-bit mantissa as shown in Figure 3.1(a). In the PE array, the floating-point format is rearranged (Figure 3.1(b)) and separated (Figure 3.1(c)) since a floating-point value is managed by a pair of PEs: one treats the signed mantissa part of the floating-point value, while the other treats the exponent part of the floatingpoint value.

Figure 3.1 Floating-point formats: (a) 32-bit IEEE-754 simple precision, (b) 32-bit format internally used in PE array which has 24-bit data-path, (c) separation of a 32-bit floating-point value, (d) reduced 24-bit format internally used in PE array which has 16-bit data-path, and (e) separation of a 24-bit floating-point value.

In the case that the bit-width of the data-path of each PE is less than 23 bits of mantissa part, the least significant bits are truncated. Figure 3.1(d) and (e) shows the representation of floating-point values used in the PE array which has 16-bit data-path. 8 bits of the mantissa part is truncated so that the reduced floating-point format has 24-bit in total: 1-bit sign, 8-bit exponent, and 15-bit mantissa, as shown in Figure 3.1(d). If the precision of 15-bit mantissa is good enough for the targeting situation, hardware cost of the architecture can be decreased easily by reducing the bit-width of the data-path. Reduced floating-point formats are often used for low-end embedded systems because they have larger dynamic ranges than integer formats in case that the precision is not important [32, 33].

We assume that floating-point values are stored in the data memory of the RCM confirming to the IEEE single precision standard. In other words, floating-point numbers are transformed where they are transferred between the data memory and the PE array. If we truncate 8 least significant bits of mantissa part while loading data from the data memory to the PE array. When we store the floating-point results back to the data memory, we attach zeroes for the 8 least significant bits of the mantissa part. Figure 3.2(a) shows the hardware structure of the format converter from the data memory to the PE array. IEEE-754 floating-point numbers (32-bits) are converted as the separated format used in the CGRA and transferred to the corresponding PEs. On the other hand, Figure

Figure 3.2 Floating-point format between PE array and the data memory. (a) shows the data-path from the data memory to the PE array, and (b) shows the data-path from the PE array to the data memory. Yellow tokens represent floating-point data.

Figure 3.3 A floating-point addition operation boxed in the left side is split into several integer micro-operations with data dependency.

3.2(b) shows the format conversion from the PE array to the data memory.

#### 3.1.2 Floating-point operations

A floating-point operation can be divided into several micro-operations each of which deals with a part of the whole floating-point operation. For example, a floating-point addition can be split into several micro-operations, as shown in Figure 3.3. Micro-operations have one or two fixed point values as its input, and outputs a fixed point value, in other words, they are integer operations each of which can be dealt by a PE in the PE array. Execution of floating-point operations on a PE array is similar to the emulation of floating-point operations in integer-only processors, except that the micro-operations from floating-point operations are scheduled by the configurations and they are executed in parallel.

### 3.2 FPU-PE Cluster

#### 3.2.1 Construction of FPU-PE Cluster

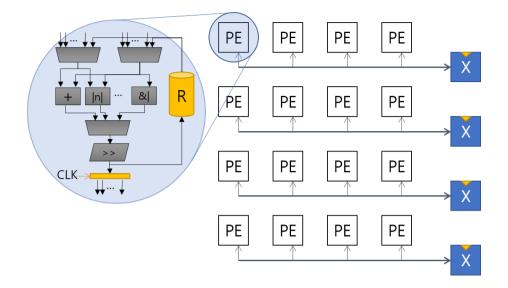

Each PE in the PE array has enough functionality to manipulate integer values. However it by itself cannot handle floating-point values efficiently. So, for a floating-point operation, we combine two PEs such that one PE takes charge of sign and mantissa parts of the floating-point operation, while the other PE takes charge of exponent part with remaining most significant bits set to zero as shown in Figure 3.1(c) or (e). The former is called mantissa PE and the latter is called exponent PE. Such a pair of PEs that co-operates to execute floatingpoint operations is called FPU-PE cluster (Figure 3.4).

To execute floating-point operations more efficiently, we add several submodules to each PE. Since the operations applied to the mantissa part and the exponent part are quite different, the sub-modules added to the mantissa PEs are different from those added to the exponent PEs, which makes the PE array heterogeneous. For instance, each mantissa PE has a leading-one detection

Figure 3.4 Overview of FPU-PE cluster.

module used for normalizing mantissa values, while each exponent PE has a saturation module used for limiting the exponent value not to exceed the value of infinity (0xFF in the single precision floating-point standard). If the architecture were designed with a homogeneous array of PEs, the hardware cost would be much higher without any performance gain.

#### 3.2.2 Construction of Array of FPU-PE Clusters

Figure 2.2 shows the interconnection topology of the PE array. The basic topology is mesh but some of 2-hop, 3-hop, and pair-wise interconnects are added. With these abundant interconnects, the PEs can efficiently transfer their output data to others, allowing easy mapping of applications onto the array. The

Figure 3.5 Construction of FPU–PE cluster array: (a) locations of Mantissa PEs and Exponent PEs in PE array and constructed FPU–PE array, (b) abstracted interconnection among RPU–PE clusters, and (c) interconnection of an FPU–PE cluster in detail.

| Clustering case     | Fixed              | Paring1                                        | Paring2              |

|---------------------|--------------------|------------------------------------------------|----------------------|

| Functionality of PE | Either M or E      | Either M or E                                  | Both                 |

| Clustering          | Fixed cluster      | Flexible                                       | Flexible             |

|                     |                    | $(1 \text{ PE}_M \text{ and } 1 \text{ PE}_E)$ | (2 PEs)              |

| Hardware overhead   | FSM / FU / control | FSM / FU / control                             | FSM / FU / control   |

|                     | for one of M or E  | for one of M or E,                             | for both of M and E, |

|                     |                    | pointer to the pair                            | pointer to the pair  |

| Configuration       | FP-operation only  | FP-operation                                   | FP-operation         |

|                     |                    | Pair selection                                 | Pair selection       |

Table 3.1 Comparison between different FPU-PE clusters

mantissa PE and the exponent PE of an FPU–PE are located side by side for frequent communications between them. Also the mantissa PEs and exponent PEs are properly placed in order to construct an array structure of FPU–PEs as shown in Figure 3.5. Thus we make best use of the array structure in case of floating–point operations as well as integer operations.

#### 3.2.3 Comparing Different FPU-PE Clusters

There are several ways to construct FPU–PE clusters. We can just fix the PEs to construct a FPU–PE cluster, or dynamically change the PEs in a FPU–PE cluster. A PE can deal with either mantissa part or exponent part, or a PE can deal with

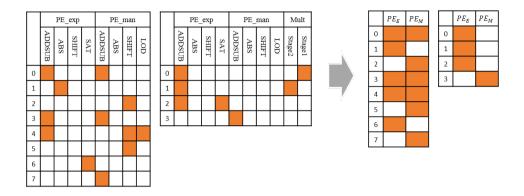

both of the parts. Table 3.1 shows the three candidates for construction of FPU-PE clusters. "Fixed" is the case that behavior of every PE is fixed so that a PE is either a mantissa PE or an exponent PE, and a pair of PEs constructing a FPU-PE cluster is also fixed. The additional hardware cost of each PE is for the FSM, additional functional units, and modified control/data paths. "Paring1" is the case that the behaviors of the PEs are fixed, but the cluster is flexible so that any pair of a mantissa PE and an exponent PE which are interconnected directly can construct FPU-PE cluster and calculate floating-point operations. In this case, additional hardware cost for the pointer to the pair PE in the same cluster is required compared to the "Fixed" case. "Pairing2" is the case that all the PE have functionality of both mantissa and exponent and any two PE can construct a FPU-PE cluster. According to the operations, PE's behavior is determined whether it manages mantissa part or exponent part. Multi-cycled floating-point operations implemented in the every clustering cases are using FSMs to control PEs during the execution cycles, instead of configuring with the configuration bits from the configuration memory, which will be explained and analyzed in detail in 3.3.

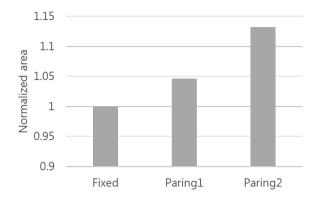

Figure 3.6 shows the normalized hardware area costs of the PE arrays of the three different clustering cases. Since the FPU-PE clusters are not fixed in the "Pairing1" and "Pairing2" cases, they requires additional configurations such as selecting the pair PEs for constructing FPU-PE clusters. It is implemented as

Figure 3.6 Normalized hardware area of the three different clustering cases.

an operation so that it may increase the number of operations of the kernels compared to the "Fixed" case. Compared to the "Fixed" case, "Paring1" requires 4.6% more and "Paring2" requires 13.2% more than the "Fixed" case, shown in the Figure 3.6.

Since "Paring1" and "Pairing2" allows more flexibility when constructing FPU–PE clusters, it is not effective floating–point conversion between the data memory and the PE array shown in Figure 3.2 limits their effects. Mantissa parts and exponent parts of floating–point numbers are sent to/received from certain PEs. Floating–point transfer in the FPU–PE cluster array shown in Figure 3.5 is efficient enough in that there are the same number of FPU–PE clusters in the PE array even though FPU–PE clusters are changed dynamically which are supported in "Pairing1" or "Pairing2" cases.

| Operations  | Input | Output | Latency  | Method             |

|-------------|-------|--------|----------|--------------------|

|             |       |        | (cycles) |                    |

| Add/sub     | float | float  | 6        | Internal ALU only  |

| Multiply    | float | float  | 4        | Shared multiplier  |

| Div         | float | float  | 7        | Shared divider     |

| Square root | float | float  | 7        | Shared square-root |

Table 3.2 Properties of implemented floating-point operations

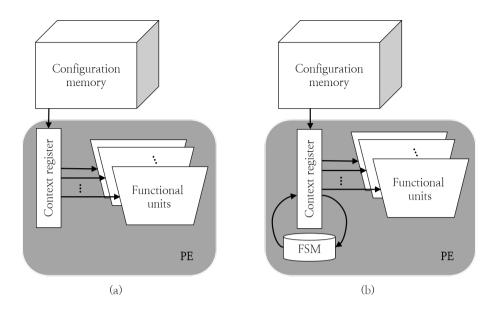

## 3.3 Implementation of Multi-Cycle Operations

Floating-point operations are much more complex than integer operations so that they are implemented as multi-cycle operations. To perform a floating-point operation, the pair of PEs in an FPU-PE co-operates for several cycles with its intermediate data stored in the local register files. Table 3.2 shows cycle counts of the floating-point operations implemented on each FPU-PE.

There are two different approaches to reconfiguring a PE for a multi-cycle operation. One is updating the PE's configuration every cycle with the code fetched from configuration memory until the operation is completed as shown in Figure 3.7(a), and the other is implementing a separate FSM in the PE to control the multi-cycle behavior of the PE as shown in Figure 3.7(b). The former does not require additional hardware like FSM, but it requires a lot of memory area

Figure 3.7 Reconfiguration of a PE in the (a) base architecture, and (b) FSM– included architecture.

for every-cycle configuration. It is also inevitable to consume more power for loading configuration words from the configuration memory. The latter requires implementation of FSM to control functional units in each PE, but it requires less memory space for the same functionality compared to the former. The both approaches accepts the fixed FPU-PE clustering.

Table 3.3 shows the hardware cost of the two different floating-point implementations. "FSM approach" indicates the case that the functional units in each PE are controlled by the corresponding FSM during floating-point executions, while "Config. memory approach" indicates that the functional units in

|                               | FSM approach | Config. memory approach |

|-------------------------------|--------------|-------------------------|

| Hardware cost per PE $(um^2)$ | 8820.2       | 6160.8 (69.8%)          |

Table 3.3 Comparison of hardware cost per PE

each PE are controlled by the configuration bits from the configuration memory during floating-point executions. The numbers are effective hardware area of a PE. This shows that "FSM approach" requires more hardware cost than "Config. memory approach" for the FSMs to control the functional units in the corresponding PEs.

We choose the former approach in spite of its hardware cost and complexity as shown in Table 3.3, due to the following reason. Each floating-point operation requires as many steps as the latency shown in Table 3.2. If the implementation of floating-point operations relies only on reconfigurations (without an FSM), then, at each step, it needs to fetch a new configuration for a proper operation corresponding to that step (note that, in the FSM approach, each floating-point operation requires only one configuration word which yields the control to the FSM). For an application kernel that uses floating-point operations frequently, the required configuration memory space will increase easily beyond our control. Moreover, accessing the configuration memory every cycle while floating-point operations are executed causes much more power con-

| Type of             | FSM approach | Config. memory approad |          |

|---------------------|--------------|------------------------|----------|

| config. memory      | Size(bytes)  | Size(bytes)            | Ratio(%) |

| Temporal config mem | 800          | 3264                   | 408      |

| Spatial config mem  | 1024         | 1024                   | 100      |

| MCO mem             | 44           | 44                     | 100      |

| Total               | 1868         | 4332                   | 232      |

Table 3.4 Comparison of memory usages for 9/7tap wavelet transforms

sumption compared to the case of using FSM. Table 3.4 shows memory usage of the two different approaches for a simple benchmark program of 9/7tap wavelet transform implemented with floating-point operations. Compared to the FSM approach, the approach of updating configuration memory every cycle requires about 2.3 times of memory space. For a larger application, it will require larger configuration memory space to exceed easily the existing local configuration memory space. Then the configuration words should be fetched from the external memory while the application is running. This implies that the requirement of large configuration memory space may bring about not only area overhead but also performance overhead.

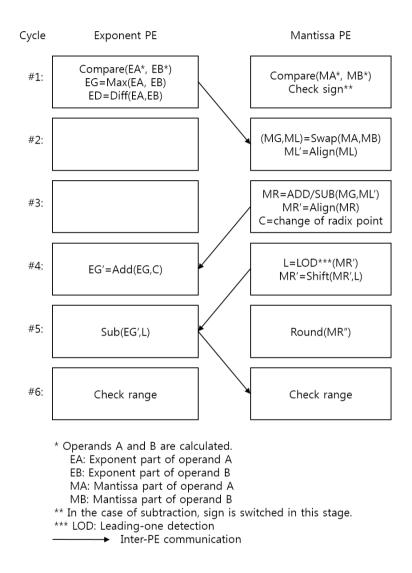

### 3.4 Implementation of Floating–Point Operations

Floating-point addition and subtraction share the same data-path. Subtraction can be implemented easily with the data-path for floating-point addition by toggling the sign of the subtrahend. Floating-point addition/subtraction takes six cycles in total by an FPU-PE. In the first cycle, the exponent PE in the FPU-PE compares the exponents of the two operands (at the same time, the mantissa PE also compares the absolute values of the mantissas in case the two exponents are same). It keeps the larger exponent value and sends the difference to the other PE so that the mantissa PE can align the radix points of the two mantissa values in the second cycle. In the third cycle, the mantissa PE performs addition/subtraction on the two operands depending on the sign difference of the two operands. In the fourth cycle, the mantissa PE obtains the position of leading-one in the addition/subtraction result in order to normalize it. In the next two cycles, the two PEs perform normalization by shifting the mantissa part and updating the exponent part accordingly and then check the range of the result. The behaviors of floating-point addition and subtraction are shown in Figure 3.8.

Figure 3.8 Behavior of floating-point addition for each cycle.

# 3.5 Implementation of Floating–Point Operations Using Shared Modules

Floating-point multiplication, division, and square-root operations are also implemented on the RCM. For those operations, separate shared integer functional modules (multipliers, dividers, and square-root units) are utilized for mantissa calculation. Each of the integer functional modules is shared by a set of PEs as mentioned in Section 2.2. For a floating-point operation on an FPU-PE, while the exponent PE calculates the exponent part, the mantissa PE sends two operands to the shared module and stalls until it receives the result back several cycles later when the shared module completes the calculation. Once the mantissa PE gets the intermediate result from the shared module, both the mantissa PE and exponent PE construct the final result and check its range and compensate it not to be out of range. The behavior of floating-point multiplication is shown in Figure 3.9.

Floating-point division and square-root operation are similar to multiplication. Floating-point division uses a mantissa PE and a shared divider in order to obtain the quotient of the mantissas. The exponent PE subtracts two exponents and then adds the bias number while mantissa PE waits for the result from the shared divider. Then the PEs follow the procedure of checking ranges of the result similarly to the floating-point multiplication shown in Figure 3.9. Since the division of the mantissa part takes more cycles than multiplication does, the

Figure 3.9 Behavior of floating-point multiplication for each cycle.

latency of the whole floating-point division operation is greater than that of the floating-point multiplication.

In case of floating-point square-root operation, one operand is given in an FPU-PE cluster. The exponent PE first checks to see whether the exponent part is odd or even. The flag is sent to the mantissa PE and the mantissa part is shifted by the flag in the mantissa PE. Then the mantissa PE sends the mantissa part to the integer square-root module, while the exponent PE divides the exponent

part by 2 (subtract bias rom the exponent part, shift right, and then add the bias). After the mantissa PE obtains the result from the shared square-root module, both PEs in the FPU-PE cluster check exception. Since the shared square-root module also takes long time, the total execution latency of the floating-point square-root operation is also long.

The properties of all the implemented operations are shown in Table 3.2. All the operations deal with 24-bit reduced precision floating-point values.

# Chapter 4

# Chip Implementation

## 4.1 Specification of Chip Implementation

Our architecture, which has been implemented to a chip, consists of an ARM7– compatible processor, a DMA controller, and an RCM, all of which are connected to an AHB bus. An AHB slave port and the processor's JTAG port are used as the chip's external interfaces. The RCM has an 8x8 array of PEs so that it can perform 64 integer operations or 32 floating–point operations at the same time. All PEs in each row of the array share a multiplier, all PEs in each of the 1st, 4th, 5th, and 8th rows share a divider, and all PEs in each of the 1st and 8th rows share a square–root unit. We have designed the architecture this way mainly because dividers and square–root modules occupy a quite larger area. Besides division and square–root operations are rarely used compared to multiplication. Integer functions such as DCT, FFT, FIR filters, which are frequently accelerated on the RCM, do not require division and square-root at all. And even floating-point functions rarely use square-root operations. Normalization, which is one of the most frequently used functions in 3D graphics, requires one square-root operation and three division operations among nine arithmetic operations in total. Since only the mantissa PE in an FPU-PE cluster uses a shared divider during floating-point division, having only one divider shared by two rows of PEs is enough to execute normalization.

The configuration memory size is 5632 bytes and data memory size is 6144 bytes. CCU has an MCO table of 128 bytes for the generation of configuration memory addresses. The chip has been fabricated using Dongbu HiTek 130nm CMOS technology. Figure 4.1 shows a chip photograph of the proposed architecture laid on 4.1 mm × 4.1 mm area. The equivalent gate count of the whole architecture implemented on the chip is 1338k. Compared to an integer–only design, the size of the RCM is increased by 7.4% due to the implementation of floating–point operation, while maintaining the clock frequency, compared to our previous RCM architecture where the proposed technique is not applied. 17% of the increment is from the addition of functional units such as leading–one detectors, saturators, while 34% is from the added FSM and decoder mod–ification, The rest of the increment is from other control– and data–paths like flag management for the pair PEs in an FPU–PE, flag registers, and so on. The

Figure 4.1 Micrograph of the fabricated chip.

proposed design, which we call FloRA, achieves maximum 6625M integer operations and 667.8M floating-point operations per second at 125 MHz operating frequency with 1.2V supply voltage.

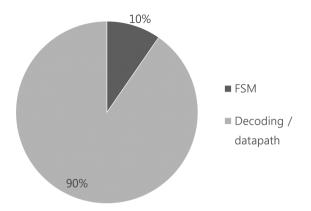

Breakdown of 7.4% of the increased hardware area cost is shown in Figure 4.2. The largest portion of the increment is from the FSM for control of multi-cycle operations. Additional modules such as saturation unit, leading-

Figure 4.2 Area breakdown of the increased hardware.

one detector and registers are not very large compared to the modification of decoder and data-paths in each PE. Impacts of additional interconnects is also not very much.

## 4.2 Experimental Setup

For the test of the fabricated chip, we have constructed the prototype board by connecting external memory blocks to the chip through the chip's external interfaces. The board has been designed as a daughter board mounted on top of an existing FPGA board. The AHB slave port – one of the external interfaces of the chip – has been connected to an external memory block via an AHB bridge module implemented on the FPGA. Besides, JTAG port for the RISC processor has been connected to a PC to control the processor. With this setup, we can download test programs and data into the external memory on the test board via a JTAG cable. We can also control the status of the processor and run/stop the execution of the processor. The FPGA board runs at 24MHz and the fabricated chip operates at 1.2V and the same clock speed as the board. Note that the maximum clock frequency of the chip is 125MHz.

Power consumption of the chip has been measured on the prototyping board. Power for the core in the chip has been supplied from a different power source from the FPGA board. By measuring the voltage and current of the separately supplied power source, we can obtain the power consumption of the chip.

### 4.3 Experimantal Results

#### 4.3.1 Performance Comparison

In this subsection, we present the evaluation result of the fabricated chip implementing our coarse-grained reconfigurable architecture having floating-point functionality. We have tested it with several integer and floating-point benchmark kernels as shown in Table 4.1. FloRA has been tested at 24MHz on the prototype board, but the performance has been calculated as if it were running at 125MHz, which is the maximum operating frequency of the fabricated chip. Also we have run the same kernels on the ARM7 platform and ARM9 platform

| 45.9       | 11.61        | 126.56       | 62.37M     | 26.1                 | 4.53M      | 99.8     | 0.99M                | 1204     | I     | Average                        |

|------------|--------------|--------------|------------|----------------------|------------|----------|----------------------|----------|-------|--------------------------------|

| 82.4       | 17.18        | 324.42       | 156.9M     | 43                   | 9.13M      | 23       | 0.48M                | 275      | float | FIR filter(4-tap) <sup>1</sup> |

| 33.4       | 1.88         | 42.05        | 2.1M       | 51                   | 1.12M      | 188      | 0.05M                | 2663     | float | Convolution (len:32)           |

| 34.0       | 9.53         | 84.97        | 41.7M      | 16                   | 4.38M      | 48       | 0.49M                | 271      | float | Dot product (1×4)              |

| 54.3       | 7.56         | 109.21       | 34.5M      | 21                   | 4.57M      | 46       | 0.32M                | 421      | float | Cross prod. $(1 \times 3)$     |

| 42.1       | 7.51         | 98.08        | 52.6M      | 11                   | 7.00M      | 30       | 0.54M                | 248      | float | Complex Mult.                  |

| 79.3       | 7.74         | 183.99       | 4.3M       | 53                   | 0.56M      | 378      | 0.02M                | 5691     | float | Mat. Mult. $(4 \times 4)$      |

| 35.3       | 14.14        | 228.28       | 25.6M      | 31                   | 1.81M      | 116      | 0.11M                | 1186     | float | Normalize $(1 \times 3)$       |

| 23.1       | 13.55        | 25.44        | 76.9M      | 5                    | 5.68M      | 37       | 3.02M                | 44       | int   | Dot product $(1 \times 4)$     |

| 29.2       | 25.40        | 42.62        | 166.7M     | 4                    | 6.56M      | 32       | 3.91M                | 34       | int   | Complex Mult.                  |

| (%)        | ARM9+VFP     | ARM7         | (iter/sec) |                      | (iter/sec) |          | (iter/sec)           |          |       |                                |

| PE array   | improv. over | improv. over | @125MHz    | (cycles)             | @210MHz    | (cycles) | @133MHz              | (cycles) |       |                                |

| Utiliz. of | Thruput      | Thruput      | Thruput    | Latency <sup>2</sup> | Thruput    | Latency  | Thruput              | Latency  |       | name                           |

|            |              | FloRA        |            |                      | ARM9+VFP   | ARN      | Software-only (ARM7) | Software | Туре  | Kernel                         |

Table 4.1 Performances of benchmark kernels accelerated by FloRA

<sup>1</sup> Integer complex multiplication, integer dot product, and floating-point matrix multiplication execute two iterations concurrently, and FIR filter processes eight samples concurrently within the given latencies.

$^2\,$  In case of FIR filter, the throughput is in samples/s.

with a vector-floating-point (VFP) unit for comparison. The ARM7 processor emulates a floating-point operation as a series of integer operations since there is no floating-point unit in the processor. All the codes running on the processors have been compiled with -O2. Third to fifth columns of Table 4.1 show the latencies obtained for the benchmark kernels running on each platform. Latencies of the benchmarks running on the ARM7 and ARM9 with a VFP unit are obtained by the ARM instruction-set simulator (AXD). Compared to software-only implementations on a processor (ARM7 at 133MHz), the FloRA implementations operating at 125MHz are 126.6 times faster on average. And compared to those on ARM9 processor with a VFP unit operating at 210MHz, the FloRA implementations are 11.6 times faster. By executing two iterations concurrently in the cases of integer complex multiplication, integer dot product, and floating-point matrix multiplication, 2X throughput improvement can be obtained. In the case of FIR filter, eight samples are processed at the same time on the PE array of FloRA, which has also been considered in the throughput calculation. The utilization in the table means the average ratio of number of active PEs over number of total PEs in the PE array within execution cycles. It is one of the main factors that affect the power consumption in FloRA.

#### 4.3.2 Power Consumption Comparison

For comparison of power consumption among different architectures, we measured the power consumption of the fabricated chip. The consumed power per clock frequency of the benchmarks running on the proposed architecture is 3.70mW/MHz on average. On the other hand, power consumption of ARM7 (ARM7TDMI-S in 130nm process whose maximum frequency is 100–133MHz) is 0.11mW/MHz [34], and that of ARM9 (ARM968E-S with VFP9 in 130nm process whose maximum frequency is 180-210MHz) is about 0.5mW/MHz [35, 36]. It has not been confirmed whether the power consumptions of both ARM7 and ARM9 architectures are obtained from macro-cells or chips. Even though the power consumption per unit frequency of the proposed architecture is higher than those of the two ARM architectures, the execution time of benchmark programs on the proposed architecture is much shorter than those on the other architectures. The energy consumption for the benchmark programs in the proposed architecture is 2.45% (7.57% for integer programs and 2.42% for floating-point programs) of that of ARM7, and 17.7% (24.0% for integer programs and 17.6% for floating-point programs) of that of ARM9 with VFP9. The results show that the proposed architecture is efficient than the software approach in terms of both performance and power consumption, and comparable with floating-point unit approach in terms of power consumption.

Figure 4.3 shows the dynamic power consumption of the benchmark ker-

nels on the fabricated chip. The numbers on the vertical axis represent dynamic power consumed by performing benchmark programs on the RCM. As can be seen in this figure, floating-point-based programs consume power comparable to the integer-based programs. When floating-point operations are executed, some PEs use multiple functional units simultaneously, but some other PEs do nothing but just wait while other PEs perform the calculations. Thus the power consumption of a floating-point operation is similar to that of integer operation. The overall power consumptions of applications depend on the utilization of the PEs rather than whether the application programs are based on floatingpoint operations or integer operations as shown in Figure 4.3. Two kernels, matrix multiplication and fir filter, consume much more power than other kernels, since they have much higher utilization of the PEs.

Figure 4.3 Dynamic power consumption of the benchmark kernels on the fabricated chip.

# Chapter 5

# Comparison with Other Architectures

### 5.1 Preparation for the comparison

The proposed architecture has 16bit-wide data-paths and does not support IEEE single precision floating-point standard, and thus it is not fair to compare the architecture with other architectures that support the IEEE standard. For a fair comparison, we have modified some features of FloRA. First, we have enlarged the bit-width of the data-paths of the PE array from 16 bits to 24 bits to support the IEEE single precision floating-point standard. We have removed modules for floating-point division and square-root, which are not supported in the other architectures to be compared. We have further optimized the design to reduce the critical path delay by placing shifter and ALU in parallel, which were serialized in the original design. It increases the cycle count

| Features    | FloRA Chip implementation | new FloRA implementation |

|-------------|---------------------------|--------------------------|

| FADD/FSUB   | 6 cycles                  | 8 cycles                 |

| FMUL        | 4 cycles                  | 5 cycles                 |

| FDIV        | 7 cycles                  | _                        |

| FSQRT       | 7 cycles                  | _                        |

| Clock freq. | 200 MHz (post-synthesis)  | 328 MHz (post-synthesis) |

Table 5.1 Comparison of different FloRA implementations

of floating-point addition and subtraction from 6 cycles to 8 cycles and that of floating-point multiplication from 4 cycles to 5 cycles. However, it increases the clock frequency significantly. Modified design is synthesized by Synopsys De-sign Compiler with TSMC 130nm library. The estimated clock frequency after logic synthesis of the 24-bit FloRA is 328 MHz while that of 16-bit architecture is 200MHz (125MHz after fabrication). Besides, area of 24-bit FloRA is a bit reduced compared to the 16-bit FloRA. It is because the integer division units, integer square-root units, and their corresponding control logic have been removed. The features of chip implementation of FloRA and the modified FloRA are summarized in the Table 5.1.

### 5.2 Comparison with PACT XPP

The approach in [23] also implements floating-point operations on PACT XPP, a commercial coarse-grained reconfigurable architecture. XPP has 2-dimensional array of integer ALUs – so called ALU-PAEs – and it accelerates various integer kernels with those ALUs. ALUs are connected with crossbar switches and registers. There are only integer ALUs in the architecture, it divides floating-point operations into several integer micro-operations each of which can be handled in the architecture. The approach to implement floating-point operations in XPP architecture is similar to our approach, but XPP architecture does not fix the ALUs to execute either mantissa part or exponent part.

In order to compare FloRA to the architecture, we have implemented the same benchmark kernel described in [23] for FloRA. There are two kinds of discrete wavelet transforms (DWTs) in [23]: reversible 5/3 tap DWT using fixed-point numbers and irreversible 9/7 tap DWT using floating-point numbers, and both are included in JPEG2000 standard. For our comparison the 9/7 tap DWT has been selected.

XPP64–A1, a commercial implementation of XPP architecture, is used for the comparison. It is also fabricated as a chip with 130nm technology [37]. It contains 64 ALU–PAEs (PAE: Processing Array Element), which is the same as the number of PEs in FloRA. However, the bit–width of ALU–PAE is 24 bits. Thus we can fairly compare it with FloRA with the bit–width of the data–paths

| Features                | XPP [37] | FloRA         |

|-------------------------|----------|---------------|

| CMOS process (nm)       | 130      | 130           |

| Data bit-width (# bits) | 24       | 24            |

| Clock frequency (MHz)   | 64       | $\sim 205^1$  |

| Area (mm <sup>2</sup> ) | 35.1     | $\sim 16.8^2$ |

Table 5.2 Comparison of hardware features of PACT XPP and FloRA

<sup>1</sup> Clock frequency is from estimation on the basis of the chip implementation of 16-bit FloRA.

<sup>2</sup> Area cost is from estimation on the basis of the chip implementation of 16-bit FloRA.

enlarged to 24 bits.

Table 5.2 shows the hardware features of both XPP architecture and FloRA with 24-bit data-path. The maximum clock frequency of the modified FloRA with 24-bit data-path was estimated with the information of FloRA with 16-bit data-path. The estimated maximum clock frequency after fabrication was 205MHz, which was much greater than 125MHz, the clock frequency of the 16-bit FloRA chip. Although the area has been reduced from that of 16-bit FloRA, the difference is not big compared to the whole chip size.

Table 5.3 compares the execution times of 9/7 tap DWT running on XPP and FloRA for various image sizes. Although FloRA takes more cycles for the

Table 5.3 Comparison of performances between PACT XPP and FloRA running 9/7 tap discrete wavelet transform

| Image     | XPP @64   | MHz [23]  | FloRA @205 MHz <sup>1</sup> |           |              |

|-----------|-----------|-----------|-----------------------------|-----------|--------------|

| size      | Cycles    | Time (ms) | Cycles                      | Time (ms) | Speed-up (X) |

| 256×256   | 398,000   | 6.200     | 709,536                     | 3.461     | 1.80         |

| 512×512   | 1,577,758 | 24.652    | 2,813,652                   | 13.725    | 1.80         |

| 1024×1024 | 6,296,340 | 98.380    | 11,164,680                  | 54.462    | 1.81         |

<sup>1</sup> Time and speed-up are calculated with clock frequency of 205MHz, which is of maximum frequency from the estimated 24-bit modified FloRA chip implementation. Since the modified 24-bit FloRA has only synthesis result, the clock frequency of the modified 24-bit FloRA has been estimated with the synthesis result and the fabrication information of 16-bitFloRA.

same sizes of image than XPP, the actual execution time is about 80% faster than XPP, since the clock frequency of FloRA is 3–4 times higher than that of XPP. Besides, XPP needs much larger area than FloRA as shown in Table 5.2. There are two reasons why the area of XPP is larger than that of FloRA. First, an ALU–PAE in XPP has three ALUs – one supporting all possible operations and the other two supporting simple operations, whereas a PE in FloRA has only one ALU. This allows XPP to execute the application with less number of clock cycles, but causes large area cost.

Secondly, each ALU-PAE has its own multiplier, which also allows XPP to execute the application with less number of clock cycles, but causes large area cost as well as lower clock frequency. In the chip implementation of XPP, there are only reconfigurable computing modules such as 64 ALU-PAEs and some Function-PAE, memory modules such as 16 RAM-PAEs (for storing data) and configuration cache memory blocks, JTAG debug interface and I/O interfaces, but not the whole architecture including large memory blocks [38]. It is the same as the case of FloRA chip implementation, which contains a RISC processor, RCM with local memory blocks, peripherals and interface for external memory. The fact that chip size of XPP is more than two times larger than that of FloRA shows the area efficiency of FloRA. If the number of PEs in the proposed architecture increases to fit the area of XPP chip implementation (from 16.8 mm2 to 35.1 mm2), the estimated speed-up of the proposed architecture can be up to 3.76 times of XPP architecture considering that the target application kernels are parallelizable according to the number of PEs.

# 5.3 Comparison with Butter Architecture

Butter [25] is a CGRA implemented in a similar way to ours for manipulating floating-point numbers. A floating-point unit in the Butter architecture is implemented using existing integer units in a PE. The mantissa part of a floatingpoint number is calculated by the integer units, while the remaining parts – exponent and sign parts – are treated by special modules added for floating-point operations.

Since the Butter architecture was implemented on an FPGA, we have also implemented FloRA targeting the same FPGA for a fair comparison. FloRA was synthesized by Altera Quartus II for Altera Stratix II EP2S180 FPGA chip, which was also used for implementing the Butter architecture in [25]. Since the Butter architecture can execute three floating–point operations: addition, subtraction, and multiplication, we have implemented FloRA that can execute floating–point addition, subtraction, and multiplication only, without dividers, square–root units, and corresponding control logic. Shared multipliers in FloRA were implemented with DSP blocks in FPGA. Bit–widths of the multipliers of both architectures are different, and the numbers of DSPs for constructing mul– tipliers are also different. For fair comparison, the number of DSPs is converted as the numbers of ALUTs, which will be explained later in this section.

Table 5.4 shows the area and the clock frequency of a PE in the three different architectures implemented on the FPGA: Butter architecture and two different instances of FloRA. FloRA\_1Mul in Table 6 has one column of integer multipliers, each of which is shared by one row of PEs. FloRA\_2Mul has two columns of integer multipliers; in other words, PEs in a row share two multipliers in FloRA\_2Mul. FloRA\_2Mul has better performance with more area cost by reducing resource conflicts, in general.

| Features of a     | PE       | Butter         | FloRA_1Mul <sup>1</sup> | FloRA_2Mul     |

|-------------------|----------|----------------|-------------------------|----------------|

| Comb. Area(ALUTs) | (a)Comb. | 1456           | 1430.33                 | 1487.66        |

|                   | (b)DSPs  | 1728 (12 DSPs) | 83.75 (1 DSPs)          | 167.5 (2 DSPs) |

| (a)+(b)           |          | 3184           | 1514.08                 | 1655.16        |

| Registers (Bits)  |          | 251            | 253                     | 253            |

| Frequency (MHz)   |          | 34             | 68.0                    | 62.1           |

Table 5.4 Comparison of hardware features of PEs in different architectures

<sup>1</sup> FloRA\_1Mul has one shared integer multiplier per row, while FloRA\_2Mul has two shared integer multipliers per row. The area of each PE is obtained by dividing the area of the entire PE array including shared modules by the number of PEs.

PEs in the Butter architecture use similar number of ALUTs but utilize much greater number of DSP blocks compared to the PEs in FloRA. For the purpose of comparison, we need to obtain the equivalent ALUT count for a DSP block, which depends on the bit-width of the module. The Butter architecture utilizes 12 DSP blocks per PE and among them eight DSP blocks are used to implement four 16x16 multipliers [26], each of which is made of 2 DSP blocks and is equivalent to 288 ALUTs.