Ph.D. Dissertation

### Bidirectional Error Correcting Codes and Interference Mitigation for Flash Memories

### 플래시 메모리를 위한 양방향 비대칭 오류 정정 부호 및 간섭 완화 기법

By

Myeongwoon Jeon

February 2014

Department of Electrical Engineering and Computer Science College of Engineering Seoul National University

### Abstract

Recently, NAND multi-level cell (MLC) flash memories are now widely used due to low cost and high capacity. However, when the number of cell levels increases, cell-to-cell interference (C2CI) which shifts threshold voltage may degrades the error rate in reading process. There are several approaches to alleviate the errors caused by the threshold voltage shift and we discuss error correcting codes and message encoding schemes.

First, we propose error correcting codes that are effective for multi-level cell flash memory and non-binary WOM (write once memory) codes. In particular, we focus on bidirectional error correction codes. The errors in MLC flash memories tend to be directional and limited-magnitude. Many related works focus on asymmetric errors, but bidirectional errors also occur because of the bidirectional interference and the adjustment of the hard-decision reference voltages. The code treats both upward and downward errors when the error magnitude in each direction differs. The maximum magnitudes of the upward error and downward error are  $l_u$  and  $l_d$ , respectively. One of proposed codes extends the technique of the distinct sum sets to the bidirectional error correction codes. The other code is bidirectional limited magnitude error correction codes based on modulo operation and uses non-binary conventional error correction performance than the conventional error correction codes when the code rate is equal. Furthermore, error correcting schemes for non-binary WOM codes are discussed. WOM codes is a coding scheme that allows information to be written in a memory cell multiple times without erasure, and conventional error correction codes cannot be directly applied to WOM codes. The advantages of the proposed methods are that these are practical and systematic codes, and the complexity of encoding and decoding processes are low. We also introduce effective error locating limited-magnitude parity check error correction codes for the MLC flash memory error with lower complexity.

Second, we introduce coding schemes to lower the generated interferences by cell to cell interference. It is known that C2CI is caused by the threshold voltage change of neighbor cells in writing operation. The amount of threshold voltage change is proportional to the magnitude. To minimize the generated interference, the average magnitude needs to be decreased. We propose two new C2CI reduction coding schemes that adjust the average magnitude to reduce C2CI. The proposed coding scheme deals with *q*-ary message codes, and generates fixed length codes. Message codewords are divided into several blocks, and are modified by modulo addition with proper values to minimize the average magnitude. We also propose low energy Huffman codes based on entropy coding when the frequency of symbols is not distributed uniformly. This scheme produces variable-length codes without redundancy. We modified Huffman codes to minimize average number of high bits ('1' bits). We show that proposed codes generate optimal codewords which have minimum high bits with minimum average codeword length.

Keywords: multi-level cell flash memory, error correction code, cell to cell interference,

WOM code, bidirectional error.

#### **Student number**: 2009-30210

## Contents

| Abstract                                                                         | i    |

|----------------------------------------------------------------------------------|------|

| Contents                                                                         | iv   |

| List of Figures                                                                  | vii  |

| List of Tables                                                                   | ix   |

| Chapter 1 Introduction                                                           | 1    |

| 1.1   Backgrounds                                                                | . 1  |

| 1.2 Scope and Organization                                                       | . 5  |

| Chapter 2 MLC Flash Memory Interference and Mitigation Techniques                |      |

| for Reliability                                                                  | 9    |

| 2.1 MLC flash memory and interference                                            | . 9  |

| 2.2 Signal processing based interference mitigation in MLC flash memories        | . 15 |

| 2.3 WOM codes                                                                    | . 22 |

| 2.4 Asymmetric limited-magitude error correction codes based on distinct sum set | . 27 |

| Chapte | er 3            | Error Correction Codes for Flash Memories                                | 29 |

|--------|-----------------|--------------------------------------------------------------------------|----|

| 3.1    | Introduction 29 |                                                                          |    |

| 3.2    | Bidi            | rectional error correction codes for non-binary WOM codes based on dis-  |    |

|        | tinc            | t sum sets                                                               | 30 |

|        | 3.2.1           | Bidirectional error correction codes based on distinct sum sets          | 30 |

|        | 3.2.2           | 2 Error correction coding schemes for WOM codes based on distinct        |    |

|        |                 | sum sets                                                                 | 41 |

| 3.3    | Bidi            | rectional error correction codes for WOM codes based on modulo operation | 44 |

|        | 3.3.1           | Bidirectional error correction codes based on modulo operation           | 44 |

|        | 3.3.2           | 2 Performance simulation of bidirectional error correction codes based   |    |

|        |                 | on modulo operation                                                      | 54 |

|        | 3.3.3           | B Error correction coding schemes for WOM codes based on modulo          |    |

|        |                 | operation                                                                | 58 |

| 3.4    | Perf            | formance of error correction coding schemes for WOM code                 | 61 |

| 3.5    | Erro            | or locating parity check codes for errors with limited magnitude         | 68 |

| 3.6    | Sun             | mary                                                                     | 77 |

| Chante | er 4            | On Interference Mitigating Codes for Multi-level Flash Mem-              |    |

| Chapt  |                 |                                                                          | -0 |

|        |                 | ories                                                                    | 79 |

| 4.1    | Intr            | oduction                                                                 | 79 |

| 4.2    | The             | modeling of generated interference in flash memory                       | 80 |

| 4.3    | Codin    | g schemes for interference mitigation                           | . 83  |

|--------|----------|-----------------------------------------------------------------|-------|

|        | 4.3.1    | Minimum energy coding                                           | . 83  |

|        | 4.3.2    | Module shift coding                                             | . 85  |

|        | 4.3.3    | Low energy Huffman code                                         | . 89  |

| 4.4    | Perfor   | rmance analysis of proposed coding schemes                      | . 91  |

|        | 4.4.1    | Performance analysis of ME codes                                | . 91  |

|        | 4.4.2    | Performance analysis of MS codes                                | . 93  |

|        | 4.4.3    | Performance of low-energy Huffman codes                         | . 97  |

|        | 4.4.4    | C2CI reduction performance                                      | . 99  |

| 4.5    | Summ     | ary                                                             | . 102 |

| Chapt  | er5C     | Conclusions                                                     | 105   |

| Appen  | dix A    |                                                                 | 109   |

| A.1    | Perfor   | rmance analysis of MS coding with $\eta$ =2 case in chap. 4.4.2 | . 109 |

| Biblio | graphy   |                                                                 | 113   |

| Abstra | act in K | Korean                                                          | 120   |

# **List of Figures**

| Figure 2.1  | Threshold voltage distribution of 4 level multi-level cell 10                     |    |  |

|-------------|-----------------------------------------------------------------------------------|----|--|

| Figure 2.2  | Cell to cell interference by the parasitic capacitances                           |    |  |

| Figure 2.3  | Interference model based on parasitic capacitances in a NAND flash array. 1       |    |  |

| Figure 2.4  | $V_T$ shift and bidirectional errors with adjusted $V_{read}$ 1                   |    |  |

| Figure 2.5  | Adaptive read voltage algorithm                                                   |    |  |

| Figure 2.6  | The careful cell compensation (CCC) method.                                       |    |  |

| Figure 2.7  | BER with respect to the two thresholds for the CCC algorithm                      | 20 |  |

| Figure 2.8  | BER performance of the CCC and the ARV algorithms                                 | 22 |  |

| Figure 2.9  | A WOM code that stores 3 bits in 2 cells writes [42]                              | 24 |  |

| Figure 2.10 | 0 The tiling used for an improved WOM code [42].                                  |    |  |

| Figure 3.1  | Various limited magnitude error types and $(l_u, l_d)$ bidirectional error        |    |  |

|             | channel                                                                           | 31 |  |

| Figure 3.2  | Systematic error correction codes structure for WOM code                          | 41 |  |

| Figure 3.3  | Adjustment of estimated error to be in the bound $(l_u = l_d \text{ is assumed})$ |    |  |

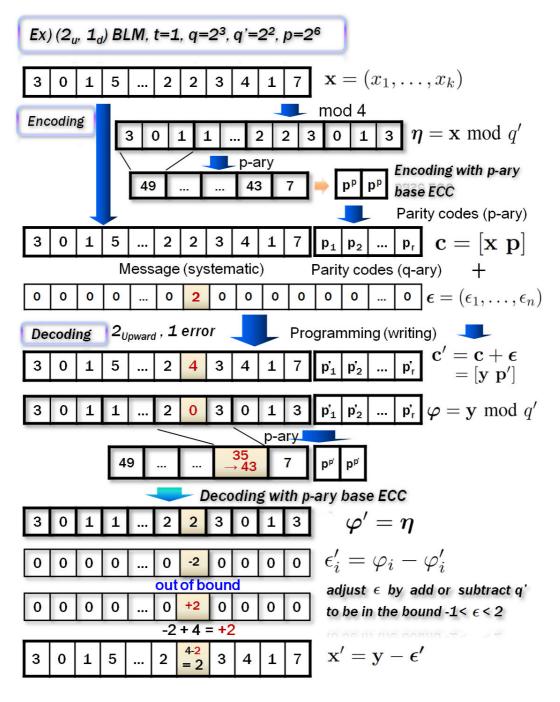

| Figure 3.4  | An example of BLM-ECC encoding and decoding                                       | 50 |  |

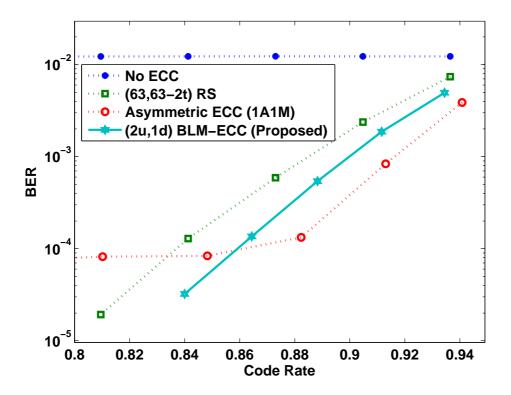

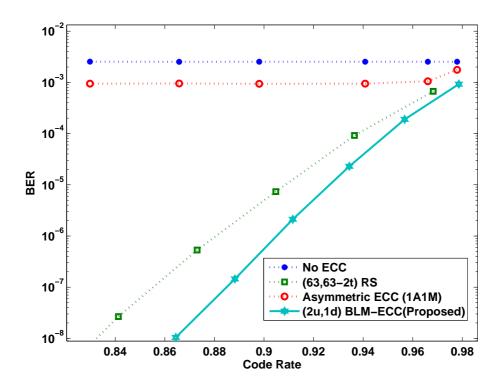

| Figure 3.5  | BER performance with original $V_{read}$ for an asymmetric channel        |     |  |

|-------------|---------------------------------------------------------------------------|-----|--|

| Figure 3.6  | BER performance with adjusted $V_{read}$ for a bidirectional channel      |     |  |

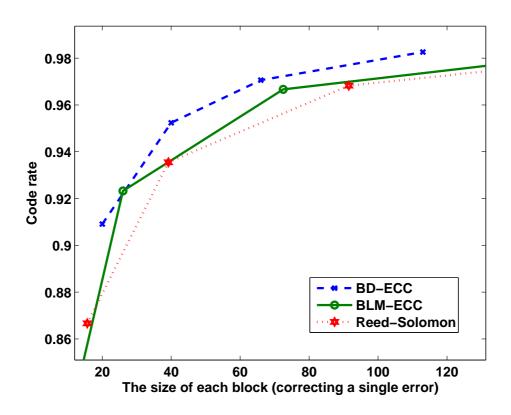

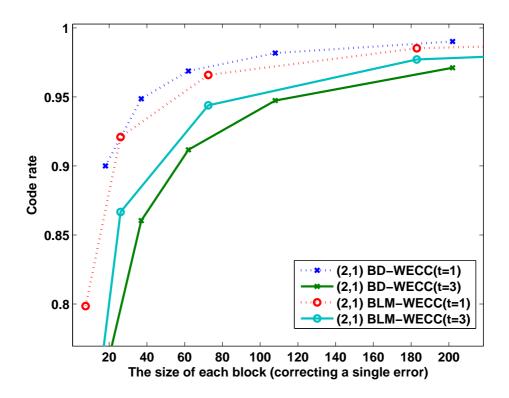

| Figure 3.7  | The code rate of proposed codes without WOM code schemes                  |     |  |

| Figure 3.8  | The code rate of two proposed codes for WOM codes with varying a          |     |  |

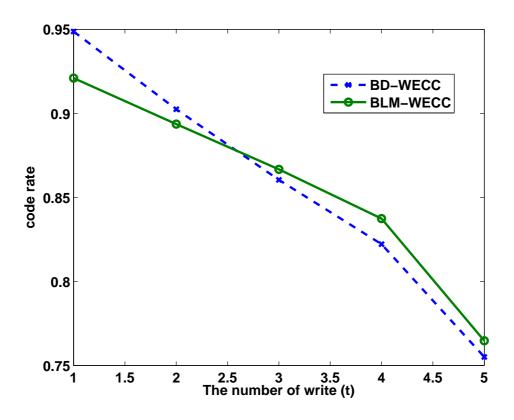

|             | block size                                                                | 64  |  |

| Figure 3.9  | The code rate of two proposed codes with varying $t$                      | 65  |  |

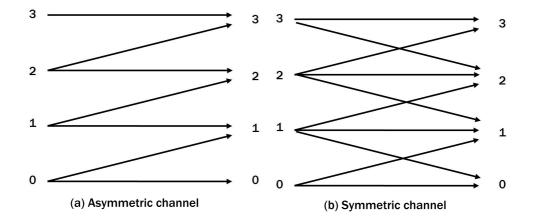

| Figure 3.10 | Asymmetric and symmetric limited-magnitude channel.                       | 68  |  |

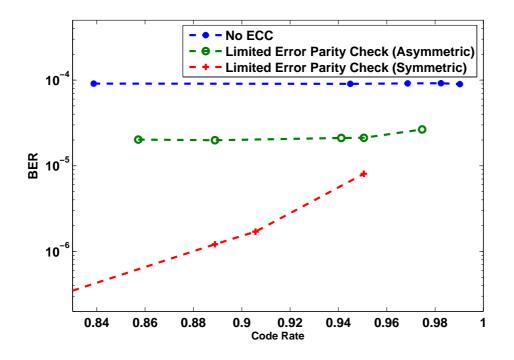

| Figure 3.11 | BER plot of the asymmetric and symmetric limited-magnitude error par-     |     |  |

|             | ity check codes.                                                          | 76  |  |

| Figure 4.1  | Interference model based on parasitic capacitances in a NAND flash array. | 81  |  |

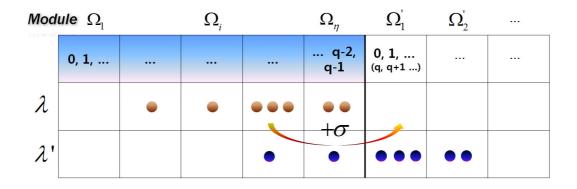

| Figure 4.2  | Module shift of MS coding                                                 | 87  |  |

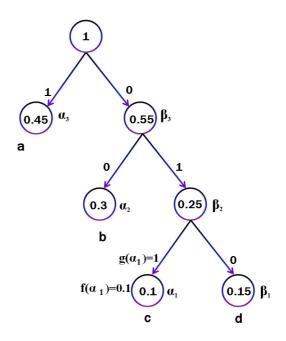

| Figure 4.3  | Low energy Huffman coding example                                         | 90  |  |

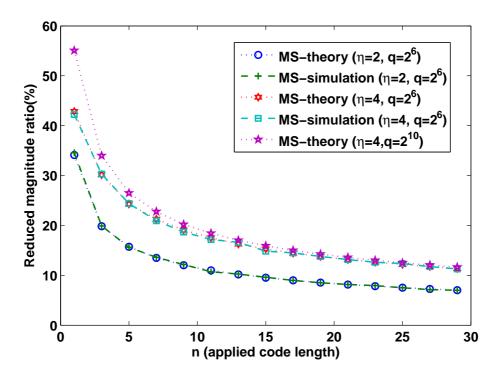

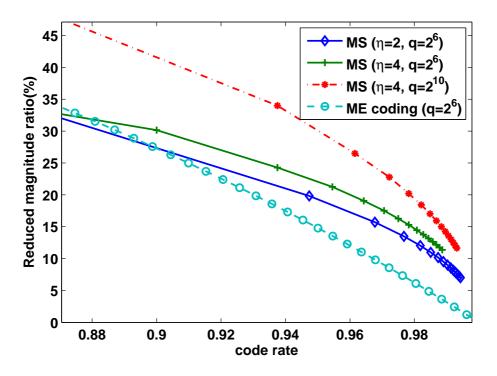

| Figure 4.4  | Reduced magnitude ratio of the module shift (MS) algorithms               | 96  |  |

| Figure 4.5  | Magnitude reduction ratio of encoded codeword                             | 97  |  |

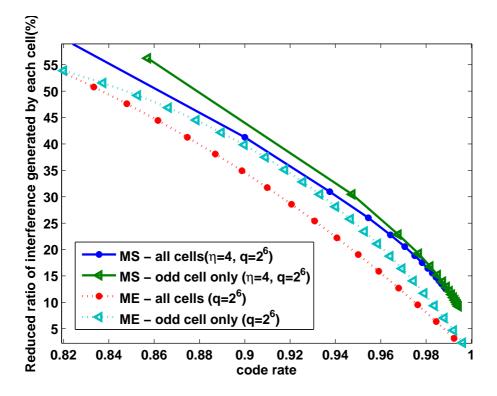

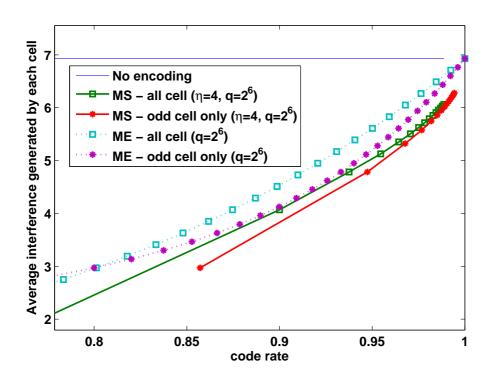

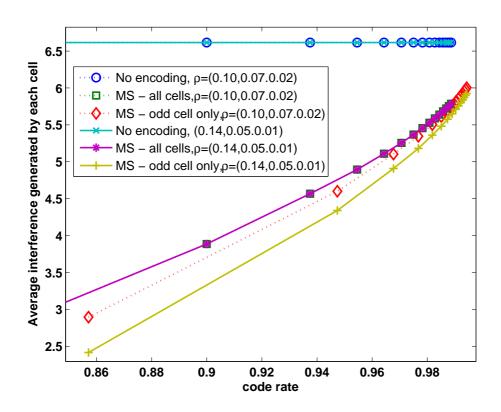

| Figure 4.6  | C2CI reduction ratio of the proposed algorithms                           | 101 |  |

| Figure 4.7  | C2CI reduction performance of the two algorithms                          | 102 |  |

| Figure 4.8  | C2CI reduction performance of the algorithms with the coupling coeffi-    |     |  |

|             | cient                                                                     | 103 |  |

## **List of Tables**

| Table 2.1 | 2-write binary WOM code example                                      | 23 |

|-----------|----------------------------------------------------------------------|----|

| Table 3.1 | Modification cases in generating minimum magnitude distinct sum sets | 34 |

| Table 3.2 | The parameters of $\Phi^m_{(l_u, l_d)}$                              | 35 |

| Table 3.3 | The parameters which proposed method generates the optimal set       | 36 |

| Table 3.4 | A comparison of two methods for symmetric error correction code      | 37 |

| Table 3.5 | The performance comparison of error correcting schemes for WOM codes | 67 |

| Table 4.1 | Magnitude reduction ratio of LE-H codes                              | 98 |

### Chapter 1

### Introduction

#### 1.1 Backgrounds

NAND flash memory has been used widely because of its non-volatility, portability and high capacity. Recently, multi-level cell (MLC) flash memories have been studied for improving memory capacity [1] [2]. Multi level cell flash memories use 4 or more levels, and store several bits in a single cell. High density storage of data can be obtained by using a high number of levels in a MLC flash memory cell. A cell of the NAND flash memory is a floating gate transistor, and its threshold voltage can be programmed by injecting certain amount of charges into the floating gate [3]. The threshold voltage ( $V_T$ ) is used to distinguish data levels in MLC memory. Several factors may change the distribution of the floating-gate threshold-voltage. These factors include cell-to-cell interference, cell leakage, temperature, program voltage ( $V_{pgm}$ ) disturbance, the pass voltage ( $V_{pass}$ ) applied to unselected word-lines, etc [4] [5]. One of the dominant factors is the cell-to-cell interference, which is caused by the  $V_T$  change of the neighbor cells in the programming (writing) operation. The cell-to-cell interference is approximately proportional to the voltage change of neighbor cells in the programming operation, but it is also affected by the structure of flash memories, the program order, and the number of levels (MLC) in a cell. Another problem related to degradation of the retention characteristics (a retention problem) also occurs with an increasing number of program/erasure cycles in the MLC flash memory.

There are several approaches to alleviate the errors caused by the threshold voltage shift such as the error correcting codes, signal processing methods and data encoding schemes. The conventional error correction codes can be inefficient for multi-level cell (MLC) flash memories because these codes are constructed for all possible error types where error magnitude and direction are random. Therefore, modified ECCs for MLC flash memories have been studied to increase efficiency. The  $V_T$  shift which is caused by the cell-to-cell interference is known to be upward (unidirectional). For these asymmetric interference factors, the error correction codes for the asymmetric channel can be useful. Asymmetric channels have been studied for several decades [6]. The topic was studied initially for a binary asymmetric channel (Z-channel). In a Z-channel, the input and the output are binary, and 1 can be changed to 0 with probability p, but 0 cannot be changed to 1. Recently, many error correction codes for asymmetric error with limited-magnitude error are discussed [7] [8] [9] [17]. Although the cell-to-cell interference which leads to upward errors is the dominant factor

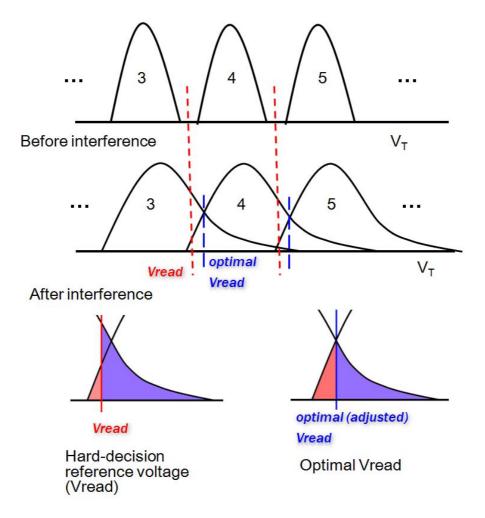

in MLC flash memories, there are also bidirectional (random-telegraph noise) and downward (retention noise) interference [11]. The hard-decision reference voltages  $(V_{read})$  for reading flash memory cells are determined based on the  $V_T$  distribution after the cell-to-cell interference, not before the cell-to-cell interference, which means the hard-decision reference voltages for reading is already near optimal. After adjusting  $V_{read}$  to be near optimal, the number of errors decreases, but the number of downward errors increases. Therefore, bidirectional errors should be considered in order to improve the BER performance. Even if the errors are bidirectional, the magnitude of the errors is still limited. The magnitudes of downward error and upward error can be different. The upward error magnitude can be larger than the downward magnitude in general since the dominant interference effect is still upward even if the optimal  $V_{read}$  is used. [16] proposed the systematic optimal codes for all symmetric errors of limited-magnitude, but it is not practical in that its code rate is too low. [10] introduced the symmetric limited error correction codes which can correct only one single error, so it is not practical for flash memories, either.

Another approach is to use interference cancellation algorithms or low interference memory structures. To mitigate the cell to cell interference, [11] proposes a page architecture including LSB and MSB program schemes. There are also other approaches based on signal processing techniques to compensate communication-channel inter-symbol interference [3] [20] [18]. The signal processing methods can be efficient because they do not require redundancy to improve the error rate. [20] proposes the post-compensation algo-

rithms. It is possible to estimate the amount of the  $V_T$  shift based on the neighbor cells' programming (writing) progress, and  $V_{read}$  is adapted accordingly.

The retention problem was also addressed by using the coding schemes. Much related research has been conducted, such as WOM (write once memory) code [29], floating code [30], and rank modulation code [31] [32]. WOM codes, which was introduced by Rivest and Shamir first [29], is a coding scheme that allows information to be written in a memory cell multiple times without erasure. The optical disc is an example of WOM, and present-day flash memory can be also considered as WOM. When erasure of each cell is required, the flash memory erases one whole page by constraint of the erasure process. Therefore, the modification of a cell message is inefficient, and it can be improved by WOM codes. The capacity bounds of WOM codes are discussed in [33], while [39] and [34] address two write WOM codes and non-binary WOM codes, respectively. Generally, WOM codes do not have error correction ability and conventional error correction codes cannot be directly applied to WOM codes. Although the original messages are WOM codes, the codes that are encoded by general error correction codes lose the WOM property, and are no longer WOM codes. Therefore, new error correction codes for WOM codes are required. Error-correcting WOMcodes were first studied in [37] for a single error in a binary case, while [36] proposed triple error correction codes for binary WOM codes. [38] discussed the generalization of errorcorrecting WOM-codes model for the non-binary case. However, the error correcting code is not systematic code and it requires large alphabet size (the number of levels in a cell).

#### **1.2 Scope and Organization**

In this dissertation, we discuss the error correction codes and encoding schemes for reliability of NAND multi-level cell flash memories.

At first, we introduce the discussions of error models in multi-level cell flash memory and provide an overview of the factors that contribute to the MLC interference and the cell to cell interference model in chapter 2. The signal processing methods are discussed to reduce the errors caused by the interference and related codes for reliability of flash memory are also introduced such as WOM codes and asymmetric error correction codes.

In chapter 3, we propose error correcting codes that are effective for non-binary WOM codes. In particular, we focus on bidirectional error correction codes. The code treats both upward and downward errors when the error magnitude in each direction differs. One of proposed codes extends the technique of the distinct sum sets [10] to the bidirectional error correction codes. The code uses the parity check matrix which is generated from the distinct sum sets and has low encoding and decoding complexity. The other code is bidirectional limited magnitude error correction codes based on modulo operation [8] [22] [35], and extends the technique of the asymmetric error correction codes [8] to the bidirectional error correction codes. The code uses conventional non-binary error correction codes as base error correction codes. Furthermore, error correcting schemes for non-binary WOM codes are discussed, and a parity splitting method is introduced as the WOM error correcting code schemes. The advantages of the proposed methods are that these are practical and systematic

codes, and their encoding and decoding processes have low complexity. Also we introduce effective error locating limited-magnitude parity check error correction codes for the MLC flash memory error with lower complexity [41].

In chapter 4, we discuss coding schemes to lower cell-to-cell interference (C2CI). In the flash memory process, the write (programming) operation is performed only after the erase operation, and the amount of threshold voltage change is proportional to the magnitude. Therefore, to minimize the generated interference, the average magnitude needs to be decreased. Conventional minimum energy (ME) coding is related to this problem [23], because the goal of the code is to reduce the average energy, and it can be used to generate less interference. However, ME coding causes significant redundancy for uniform symbol frequency, and it results in higher costs for flash storage devices. Therefore, we propose a new coding scheme to lower the magnitude and minimize redundancy. The proposed coding scheme deals with q-ary message codes, and generates fixed length codes. Message codewords are divided into several blocks, and are modified by modulo addition with some constant to minimize the average magnitude. We also propose low energy Huffman codes based on entropy coding when the frequency of symbols is not distributed uniformly. This scheme produces variable-length codes without redundancy. We modified Huffman codes to minimize average number of high bits ('1' bits). We show that proposed codes generate optimal codewords which have minimum high bits with minimum average codeword length.

Finally, a conclusion is given in chapter 5.

### Chapter 2

### MLC Flash Memory Interference and Mitigation Techniques for Reliability

In this chapter, an overview of the interfernece model in multi-level cell flash memory is provided. Signal processing methods and coding schemes such as WOM codes and asymmetric error correction codes for reliability of flash memory are also introduced.

#### 2.1 MLC flash memory and interference

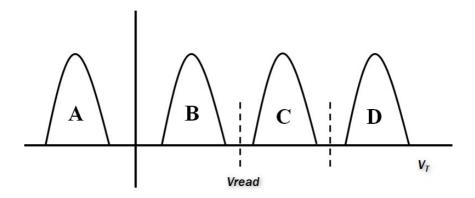

A cell of the NAND flash memory is a floating gate transistor, and its threshold voltage can be programmed by injecting certain amount of charges into the floating gate [3]. The threshold voltage  $(V_T)$  is used to distinguish data levels in MLC memory. Fig. 2.1 shows the  $V_T$  distribution of 4-level multi-level cell flash memory. Several factors may change the distribution of the floating-gate threshold-voltage. These factors include cell-to-cell interference, cell leakage, temperature, program voltage  $(V_{pgm})$  disturbance, the pass voltage

Figure 2.1 Threshold voltage distribution of 4 level multi-level cell

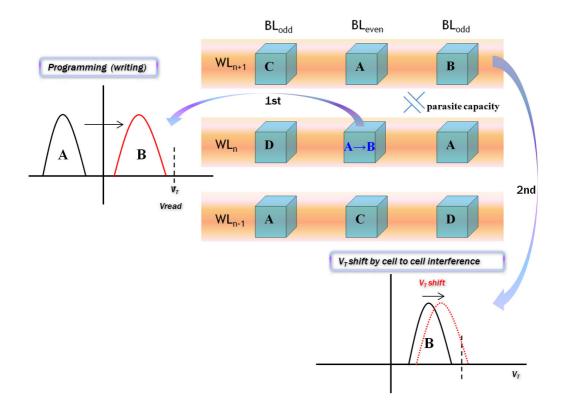

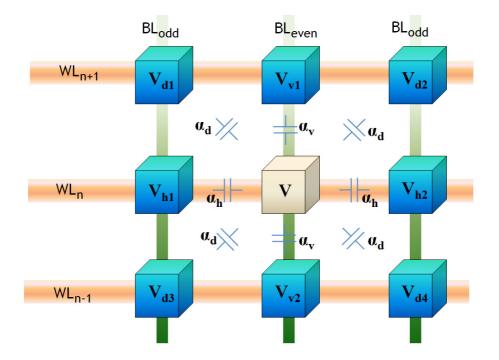

$(V_{pass})$  applied to unselected word-lines, etc [5]. One of the dominant factors is the cell-tocell interference, which is caused by the  $V_T$  change of the neighbor cells in the programming (writing) operation. If the data of neighbor cells change, the cell-to-cell coupling interference occurs and it is shown in Fig. 2.2. In this case, the  $V_T$  shift is known to be upward (unidirectional). The cell-to-cell interference is approximately proportional to the voltage change of neighbor cells in the programming operation, but it is also affected by the structure of flash memories, the program order, and the number of levels (MLC) in a cell. The quantitative interference can be estimated by measurements and simulations.

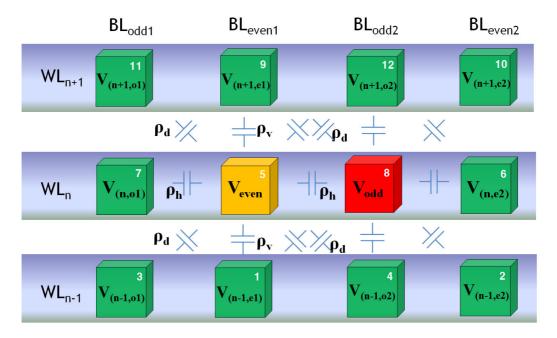

Fig. 2.3 shows an interference model based on the parasitic capacitance between neighbor cells [20] [18]. Suppose that  $V_h$ ,  $V_v$ , and  $V_d$  are the cell voltages of the horizontal, the vertical, and the diagonal neighbor cells, respectively.  $BL_{even}$  and  $BL_{odd}$  stand for the even and the odd bit lines, respectively, and  $WL_n$  stands for the *n*th word line.

Figure 2.2 Cell to cell interference by the parasitic capacitances

The interference in terms of threshold voltage shift  $(\Delta V_I)$  is given by

$$\Delta V_I = \alpha_h (\beta_{h1} \Delta V_{h1} + \beta_{h2} \Delta V_{h2}) + \alpha_v (\beta_{v1} \Delta V_{v1} + \beta_{v2} \Delta V_{v2}) + \alpha_d (\beta_{d1} \Delta V_{d1} + \beta_{d2} \Delta V_{d2} + \beta_{d3} \Delta V_{d3} + \beta_{d4} \Delta V_{d4})$$

(2.1)

where  $\alpha_h$ ,  $\alpha_v$ , and  $\alpha_d$  are the coupling coefficients for the horizontal, the vertical, and the diagonal neighbor cells, respectively. One cell can only be interfered by its neighbor cells which are programmed after this cell has been programmed.  $\beta_i$  has the binary value of '0' or '1', and it indicates whether the cell is interfered by the *i*th cell or not. If we assume that the

Figure 2.3 Interference model based on parasitic capacitances in a NAND flash array.

full-sequence programming strategy is being used, only after all the cells on one word line have been programmed can the next word line cells be programmed. By using an even/odd bit line structure, the cell-to-cell interference can be reduced. With the even/odd bit line structure, the even bit line cells are programmed first, and the odd bit line cells later [3]. For example, if we use a full-sequence programming strategy with the even/odd bit line structure, and the cell V (the red cell) belongs to an even bit line in Fig.1, the programming (writing) is performed in the order of  $WL_{n-1}(V_{v2}, V_{d3}, V_{d4})$ ,  $WL_n(V, V_{h1}, V_{h2})$ , and  $WL_{n+1}(V_{v1}, V_{d1}, V_{d2})$ . V is affected by the cell to cell interference caused by its 5 neighboring cells,  $V_{h1}, V_{h2}, V_{v1}, V_{d1}$ , and  $V_{d2}$ . More specifically,  $\beta_{d3}$ ,  $\beta_{v2}$ , and  $\beta_{d4}$  are 0's, and the others are 1's. With this programming strategy, the interference in terms of the threshold voltage shift of an even bit line cell is given by

$$\Delta V_I = \alpha_h (\Delta V_{h1} + \Delta V_{h2}) + \alpha_v (\Delta V_{v1})$$

$$+ \alpha_d (\Delta V_{d1} + \Delta V_{d2}).$$

(2.2)

If the cell V belongs to an odd bit line, the programming order is  $WL_{n-1}(V_{d3}, V_{d4}, V_{v2})$ ,  $WL_n(V_{h1}, V_{h2}, V)$ , and  $WL_{n+1}(V_{d1}, V_{d2}, V_{v1})$ . In this case,  $\Delta V$  is affected by its 3 neighboring cells,  $V_{d1}, V_{d2}$ , and  $V_{v1}$ . In other words,  $\beta_{h1}$ ,  $\beta_{h2}$ ,  $\beta_{d3}$ ,  $\beta_{v2}$ , and  $\beta_{d4}$  are 0's, and the others are 1's. The interference in terms of the threshold voltage shift of an odd bit line cell is given by

$$\Delta V_I = \alpha_v (\Delta V_{v1}) + \alpha_d (\Delta V_{d1} + \Delta V_{d2}).$$

(2.3)

A more realistic cell-to-cell interference model depends on the program order, page architecture, and the conventional LSB/MSB techniques [11].

For these asymmetric interference factors, the error correction codes for the asymmetric channel can be useful. Asymmetric channels have been studied for several decades [6]. The topic was studied initially for a binary asymmetric channel (Z-channel). In a Z-channel, the input and the output are binary, and 1 can be changed to 0 with probability p, but 0 cannot be changed to 1. Recently, many error correction codes for asymmetric error with limited-magnitude error are discussed [7] [8] [9]. Although the cell-to-cell interference which leads to upward errors is the dominant factor in MLC flash memories, there are also bidirec-

Figure 2.4  $V_T$  shift and bidirectional errors with adjusted  $V_{read}$ .

tional (random-telegraph noise) and downward (retention noise) interference [11]. The harddecision reference voltages for reading flash memory cells are determined based on the  $V_T$ distribution after the cell-to-cell interference, not before the cell-to-cell interference, which means the hard-decision reference voltages for reading is already near optimal. Fig. 2.4 illustrates the threshold voltage shift, and the adjusted  $V_{read}$ . After adjusting  $V_{read}$  to be near optimal, the number of errors decreases, but the number of downward errors increases. Therefore, bidirectional errors should be considered in order to improve the BER performance. Even if the errors are bidirectional, the magnitude of the errors is still limited. The magnitudes of downward error and upward error can be different. The upward error magnitude can be larger than the downward magnitude in general since the dominant interference effect is still upward even if the optimal  $V_{read}$  is used as in Fig. 2.4.

# **2.2** Signal processing based interference mitigation in MLC flash memories

The signal processing methods are discussed to reduce the errors caused by the interference in this subsection [20] [18]. If we know the exact cell to cell interference values caused by the voltage changes of neighbor cells, and the exact voltage of the current cell, the controller can cancel the interference, and make a less erroneous decision. To estimate the cell to cell interference, the data of the neighbor cells need to be read first. In other words, we need to read twice to estimate the interference. However, to know the exact voltage of a cell is difficult. Since a controller can only decide whether the cell (threshold) voltage is larger or less than the read voltage ( $V_{read}$ ), only a quantized version of the cell voltage instead of the precise cell voltage is available. This quantization is considered in proposing the following 2 signal processing based interference mitigation techniques.

At first, we discuss the adaptive read voltage (ARV) method. Most cells in flash memo-

ries are affected by the cell to cell interference.

$$V_T' = V_T + \Delta V_I + I_G \tag{2.4}$$

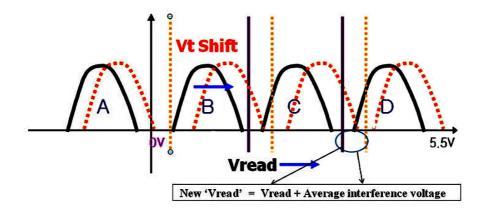

$V'_{T}$  is the threshold voltage,  $V_{T}$  is the original threshold voltage,  $\Delta V_{I}$  is cell to cell interference and  $I_{G}$  means the voltage shift by other interferences. Each cell has different interference due to different neighbor cell voltages, but we can apply the average value of the interference to every cell. Though it is not optimal, we can expect performance improvement. For example, if the average value of the cell to cell interference is  $\mathcal{E}(\Delta V_{I})$ , and  $V_{read} + \mathcal{E}(\Delta V_{I})$  as the read voltage instead of  $V_{read}$ , some (if not all) of the cells will be corrected especially when they have large inter-cell interference.  $\mathcal{E}(\Delta V_{I})$  can be treated as a constant if there are a large number of cells and the data values are random. Let  $\mathcal{D}(V_{read})$ be the data decision function. Each cell has q-level and  $V_{max}$  is maximum threshold voltage of the maximum level.

$$\mathcal{D}(V_{read}') = \mathcal{D}(V_{read} + \mathcal{E}(\Delta V_I)) \tag{2.5}$$

The interference in terms of the threshold voltage shift of an even bit line cell is given by  $\Delta V_{I} = \alpha_{h}(\Delta V_{h1} + \Delta V_{h2}) + \alpha_{v}(\Delta V_{v1}) + \alpha_{d}(\Delta V_{d1} + \Delta V_{d2}) \text{ and}$   $\mathcal{E}(\Delta V_{I}) = \mathcal{E}\left(\alpha_{h}(\Delta V_{h1} + \Delta V_{h2}) + \alpha_{v}(\Delta V_{v1}) + \alpha_{d}(\Delta V_{d1} + \Delta V_{d2})\right)$   $= \mathcal{E}(\Delta V)(2\alpha_{h} + \alpha_{v} + 2\alpha_{d})$   $= \frac{1 + 2 + \dots + q - 1}{q} \cdot \frac{V_{max}}{q - 1}(2\alpha_{h} + \alpha_{v} + 2\alpha_{d})$   $= \frac{V_{max}}{2}(2\alpha_{h} + \alpha_{v} + 2\alpha_{d}). \quad (2.6)$

Figure 2.5 Adaptive read voltage algorithm.

As for implementation, we can used fixed  $\mathcal{E}(\Delta V_I)$  for all cells, and the complexity of this method is minimal if the  $\mathcal{E}(\Delta V_I)$  value is pre-computed. Fig. 2.5 shows how the ARV algorithm works.

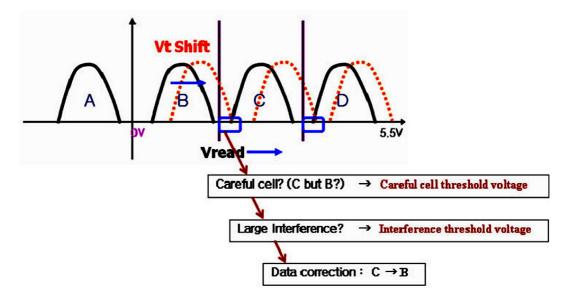

Next, we introduce *careful cell compensation (CCC)* method. This is a kind of the postcompensation algorithm. It is possible to estimate the amount of the  $V_T$  shift based on the neighbor cells' programming (writing) progress, and  $V_{read}$  is adapted accordingly. This algorithm consists of two steps. The first step is to check whether a cell has high possibility for large  $V_T$  shift, and the 2nd step is to check whether the inter-cell interference for those cells detected in the first step is large enough, and we correct those cells which pass the tests of the two steps. We define a 'careful cell' as the cell which is expected to be erroneous. The cell to cell coupling interference is always upward (unidirectional), and a cell affected by a large interference tend to have erroneous decisions. In other words, we classify a cell with the threshold voltage near the  $V_{read}$  as a 'careful cell'. The distance from the read voltages

Figure 2.6 The careful cell compensation (CCC) method.

is determined by the 'careful cell threshold'. To decide whether a cell is a careful cell, we read the cell twice with the read voltage of  $V_{read}$  and  $V_{read} + \tau_{cc}$  where  $\tau_{cc}$  is the careful cell threshold.  $\mathcal{E}(\Delta V_I)$  can be used as  $\tau_{cc}$ . If two decisions are are not equal, we declare that the cell is a *careful cell*. If a cell is declared as a careful cell, we estimate the interference for the cell. Since we already obtained the data of neighbor cells in the first step (careful cell decision), the cell to cell interference can be estimated from the neighborhood data. If the interference is large enough, the cell data is likely to be in error. The threshold to determine whether the interference is large enough is called *interference threshold voltage*. Let  $I_{th} =$  $\tau_{cc} + I'_G$  be interference threshold voltage and  $I'_G$  means estimated voltage shift by other interferences. If the interference exceeds the interference threshold,  $\Delta V_I > I_{th}$ , this cell is assumed to be in error, and is corrected by one downward level. An example is shown in Fig. 2.6. Assume that the data of the cell is detected as C with  $V_{read}$ . If it is decided as a careful cell and the estimated interference is larger than the interference threshold, the data is corrected to B. The careful cell threshold and the interference threshold can be determined analytically from the distribution model, but empirical values obtained from simulations may work better. In this algorithm, we need to read all the cells twice, and each reading operation causes delay. There is a trade-off between bit error rate and delay. The careful cell compensation algorithm (CCC) takes the following steps.

#### **Careful Cell Compensation (CCC) Algorithm**

- **1)** Read the cell data twice with  $V_{read}$  and  $V_{read} + \tau_{cc}$ .

- **1-1**) If two data values are not equal, then it is a careful cell and go to step 2.

- 2) Estimate the cell to cell interference using the neighbor data distribution of the cell.

- **2-1)** If the cell to cell interference  $\Delta V_I$  exceeds the interference threshold  $I_{th}$ , go to step 3.

- 3) Adjust the data value of the cell by one downward level.

We compare the performance of two proposed algorithms, the adaptive read voltage (ARV) algorithm, the careful cell compensation (CCC) algorithm algorithm. Bit error rate (BER) is used to measure the interference mitigation performance. In the comparison of the

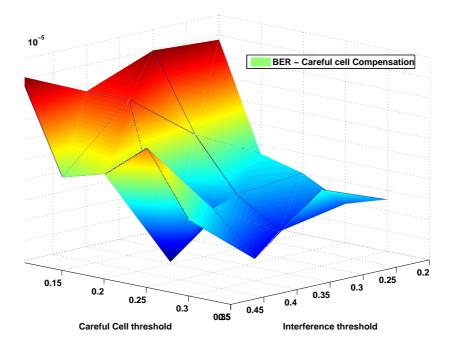

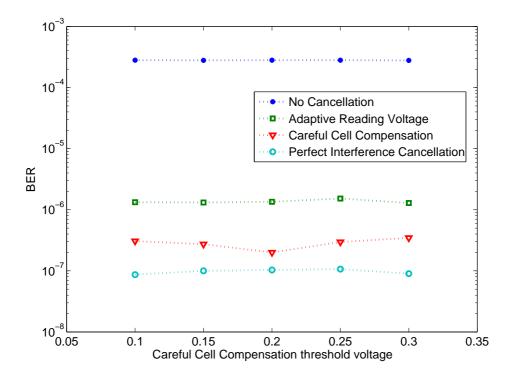

Figure 2.7 BER with respect to the two thresholds for the CCC algorithm.

ARV algorithm with the CCC algorithm, we use 4 levels with equal distribution model. The equal distribution model assumes that the every level has equal width. Before simulating the CCC algorithm, we find the careful cell threshold and the interference threshold numerically. We use an exhaustive search for the two thresholds to yield the best BER performance. In the simulation of the CCC algorithm, it is assumed that the ARV algorithm is combined with the CCC algorithm. It should be noted that we use either the no-interference case (the perfect case) or the case without interference cancellation as a benchmark. Fig. 2.7 is the 3D plot of the BER performance with respect to the careful cell threshold and the interference threshold. When the careful cell threshold voltage is 0.2V and the interference threshold

voltage is 0.4V, the best BER is achieved. To compare the BER performance of the CCC algorithm, we simulate with a fixed interference threshold of 0.4V, and the careful cell threshold is varied. In Fig. 2.8, the "perfect interference cancellation" means the case where cell to cell interference effects are removed. In this case, a threshold voltage  $V_T$  is adjusted by

$$V_T' - \Delta V_I = V_T + I_G. \tag{2.7}$$

It is observed that the BER performance of the careful cell compensation algorithm is between that of the ARV algorithm and that of the perfect interference cancellation. The CCC algorithm shows the best performance at the careful cell threshold of 0.2 V, and it is close to the no interference case.

In summary, to mitigate the interference, we propose two signal processing based algorithms: the adaptive read voltage (ARV) algorithm, the careful cell compensation (CCC) algorithm. It was shown by simulations that these algorithms are effective to reduce the effects of the interference. The ARV algorithm does not require extra data read, but its performance is not as good as the other one. The other algorithm CCC requires extra data read stages, but its performance is better than the ARV algorithm in general. If the cell data can be read only twice, the CCC algorithm appears to be promising.

Figure 2.8 BER performance of the CCC and the ARV algorithms.

#### 2.3 WOM codes

The longevity problem related with program/erasure cycle of flash memory has been addressed and much related codes are considered, such as WOM (write once memory) code [29], floating code [30], and rank modulation code [31]. WOM codes among them, which was introduced by Rivest and Shamir first [29], is a coding scheme that allows information to be written in a memory cell multiple times without erasure and the goal of designing WOM codes is to maximize the total amount of information written and to achieve high sum-rate [29]. In *t*-write WOM codes, the number of message data sets that can be written

#### without erasure is t. Table 2.1 introduces the example of 2-write binary WOM code [29].

| Data | $1^{st}$ write | $2^{st}$ write |

|------|----------------|----------------|

| 00   | 000            | 111            |

| 01   | 100            | 011            |

| 10   | 010            | 101            |

| 11   | 001            | 110            |

Table 2.1 2-write binary WOM code example

In the first write, 2-bit words are encoded using the  $1^{st}$  write codebook. For example, the first messages are 01, so 100 is written in the three cells, and the second messages are 11, then 110 is written. Therefore there are no  $1 \rightarrow 0$  cases, but only  $0 \rightarrow 1$ . If the second 2-bit word is the same as the first, there is no change to the written codeword. Non-binary WOM codes construction generates codes that have a large alphabet (q-ary). We define non-binary WOM codes construction based on [34].

**Definition 1.** The t-write non-binary q-ary WOM codes W is specified by t pairs of encoding and decoding maps  $\mathbb{E}_i$ ,  $\mathbb{D}_i$ , for  $1 \le i \le t$ .

$\mathbb{E}_1 : \{1, \cdots, M_1\} \to \{0, \cdots, q-1\}^n,$  $\mathcal{W}_i = \mathbb{E}_i(v_i, \mathcal{W}_{i-1}) \ge \mathcal{W}_{i-1}, (i \ge 2).$  $\mathbb{D}_1 : \{0, \cdots, q-1\}^n \to \{1, \cdots, M_i\},$  $\mathbb{D}_1(\mathbb{E}_1(v_1)) = v_1 \text{ and } \mathbb{D}_i(\mathbb{E}_i(v_i, \mathcal{W}_{i-1})) = v_i.$

$\mathbb{E}_i, \mathbb{D}_i$  are  $i_{th}$  encoding and decoding functions respectively, and  $v_i$  is the message.  $M_i$  is the alphabet size of  $i_{th}$  message  $v_i$ .

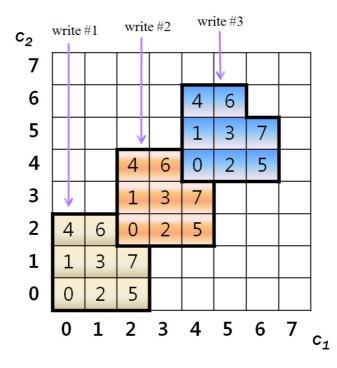

Figure 2.9 A WOM code that stores 3 bits in 2 cells writes [42].

We introduce a non-binary WOM code construction algorithm in [42]. [42] discusses the problem of 2 cell q-ary WOM codes which is addressed with a construction that uses lattice tilings. The resulting codes in [42] are shown to be within a small additive constant from the capacity. We assume that  $k_m$  input bits are written t times to n physical cells with q levels where the cell levels cannot decrease between writes in the WOM model. In an n = 2 code (2 cell q-ary WOM codes), the content of the memory is described by a pair  $(c_1, c_2) \in \{0, \dots, q-1\}^2$  of cell levels. By stacking 2-dimensional shapes along the main diagonal of the  $(c_1, c_2)$  plane, the code in Fig. 2.10 guarantees the re-writes. The rest of the plane outside the stack remains unused and better WOM code can be made by the

Figure 2.10 The tiling used for an improved WOM code [42].

construction to follow by utilizing the remaining cell states. To get more writes, we can take the following steps [42].

1) Tile the plane with the same basic shape from Fig. 2.9.

2) Specify update functions that traverse the tiling in a way that a certain number of writes is guaranteed for any sequence of input-value updates.

Then Fig. 2.10 is generated from Fig. 2.9 by the construction. The generated code guarantees four writes in the example.

Conventional correction codes cannot be directly applied to WOM codes, but error cor-

recting WOM codes have been conducted. [40] discusses the error correcting codes for flash coding. Flash coding schemes are related with WOM codes strongly and have been developed to maximize the number of writes before a block-erasure is needed. [40] proposes a new flash coding scheme based on error correction codes which minimize the frequency of block-erasures by using some controllable errors. The idea of the scheme is that cells whose levels are higher than others need not be increased and introduces errors which can be corrected within the error-correcting capability of the ECC. The code has also capable of additional errors or erasures. The encoding process of the idea is as follows. The encoding function is characterized by a integer  $0 \leq \varrho \leq \lfloor (d-1)/2 \rfloor$ .  $\varkappa = (\varkappa_1, \varkappa_2, \cdots, \varkappa_n)$ is the current cell-state vector and  $\vartheta = E_C(\mathbf{m}) = (\vartheta_1, \vartheta_2, \cdots, \vartheta_n)$  is the codeword in C corresponding to the message **m**.  $\mathcal{F}_0(\vartheta, \varkappa) = \{i : i = 1, 2, \cdots, n, \vartheta_i \neq (\varkappa_i)_2\}$ . For the reduced binary vector of the new cell-state vector to be equal to the codeword  $\vartheta = E_C(\mathbf{m})$ , all cells with indices in  $\mathcal{F}_0(\vartheta,\varkappa)$  increase the levels by 1. The scheme of [40] is not to increase the levels of those cells in which the levels are already the highest among all cells with indices in  $\mathcal{F}_0(\vartheta, \varkappa)$ . The paper introduce errors,  $\varrho$  which is the number of controllable errors (CE). By the error-correcting capability of the error-correcting code C, the decoder can recover the message correctly. For this purpose, Let  $\mathcal{F}(\vartheta,\varkappa) \subseteq \mathcal{F}_0(\vartheta,\varkappa)$  be a subset of size min  $\{|\mathcal{F}_0(\vartheta,\varkappa)|,\varrho\}$  such that for all  $i \in \mathcal{F}(\vartheta,\varkappa)$  and  $i' \in \mathcal{F}_0(\vartheta,\varkappa) \setminus \mathcal{F}(\vartheta,\varkappa)$ , we have  $\varkappa_i \geq \varkappa_{i'}$ .  $\mathcal{F}(\vartheta, \varkappa)$  includes indices of cells in which the levels are highest among all cells with indices belonging to  $\mathcal{F}_0(\vartheta, \varkappa)$ . The levels of cells with indices in  $\mathcal{F}(\vartheta, \varkappa)$  will

not be increased. [40] define  $t(q, \varrho)$  to be the number of guaranteed block-writes. Let d be the maximum Hamming distance between a pair of codewords in C. Then for  $d > 2\varrho$  and  $q \ge 2$ ,

$$t(q,\varrho) = 2\lfloor \frac{(q-2)\varrho}{d-2\varrho} + q - 1 \rfloor$$

(2.8)

From the (2.8), we notice that for [40] scheme to have more than q - 1 writes in the worst case.

## 2.4 Asymmetric limited-magitude error correction codes based on distinct sum set

The  $V_T$  shift which is caused by the cell-to-cell interference is known to be upward and the error correction codes for the asymmetric channel can be useful for these asymmetric interference factors. Recently, many error correction codes for asymmetric error with limited-magnitude error are discussed [7] [8] [9] [10].

[10] proposes error correction codes which correct single asymmetric limited magnitude errors, that is, *l*-asymmetric error correcting codes(*l*-AEC). The proposed codes achieve better performance than the ones given in [8] for the single error case, and it is based on distinct sum sets. For integer i, j, where  $i \leq j$ , we let  $[i, j] = \{i, i+1, i+2, \ldots, j\}$ . [10] defines that a  $B_{\lambda}[l](q)$  sequence of length m is a sequence of m distinct positive integers  $b_0, b_1, \ldots, b_{m-1}$  such that all sums  $\left(\sum_{j=1}^{\lambda} a_j b_{i_j}\right) \mod q$  are distinct, where  $0 \leq i_1 < i_2 < \cdots < i_{\lambda} \leq m-1$  and  $a_j \in [0, l]$ . This sequence or a set is also called distinct sum sequence or set in this dissertation. [10] discusses only  $\lambda = 1$  case. Based on B[l](q), the error correction codes can be constructed. Let **H** be the  $r \times n$  parity check matrix whose columns are all possible r length q-ary vectors whose first nonzero element belongs to B[l](q). Let C(B[l](q)) be the null space of  $\mathbf{H}^{\mathbf{T}}$ .

**Theorem 1.** If gcd(q, l!) = 1, C(B[l](q)) can correct a single asymmetric error limited magnitude l [10].

Proof and related discussions are shown in [10]. Let  $\mathbf{c} \in C$  and  $\boldsymbol{\epsilon}$  be a vector of errors with  $i_{th}$  component equal to nonzero integer and all other components equal to 0.

$$(\mathbf{c} + \boldsymbol{\epsilon})\mathbf{H}^{\mathbf{T}} = \mathbf{c}\mathbf{H}^{\mathbf{T}} + \boldsymbol{\epsilon}\mathbf{H}^{\mathbf{T}} = \boldsymbol{\epsilon}\mathbf{H}^{\mathbf{T}}$$

(2.9)

The syndromes  $\epsilon \mathbf{H}^{\mathbf{T}}$  are all distinct and the error can be corrected.

### Chapter 3

### **Error Correction Codes for Flash Memories**

#### 3.1 Introduction

The error increases with the number of levels in the cell [2] [4] and another problem related to degradation of the retention characteristics (a retention problem) also occurs with many cycles of program/erasure in MLC flash memories. Conventional error correcting codes have been used for solving reliability problems. Error correction codes for asymmetric or symmetric channels with limited-magnitude error were discussed in [7], [8], [16], and [10] for flash memories. There are also bidirectional error correcting codes can be meaning-ful for reliability of flash memory. Another issue is the retention problem and WOM codes, which was initially introduced by Rivest and Shamir [29], is a coding scheme that allows

information to be written in a memory cell multiple times without erasure. However, conventional error correction codes cannot be combined with WOM codes directly and new error correction codes for WOM codes are required.

In this chapter, error correcting codes that are suitable to practical flash memory devices and non-binary WOM codes are discussed. We deal with bidirectional error correction codes and these research are not conducted much as asymmetric errors and symmetric errors. One of proposed codes extends the technique of the distinct sum sets [10] to bidirectional error correction codes, and the other code is bidirectional limited magnitude error correction codes based on modulo operation [8] [22] [35]. The parity code constructions for systematic WOM codes are also discussed. The proposed codes have encoding and decoding process with low complexity, which is efficient for non-binary WOM codes. Furthermore, we discuss asymmetric and symmetric error locating limited-magnitude parity check error correction codes for the MLC flash memory error with lower complexity encoding [41].

# **3.2** Bidirectional error correction codes for non-binary WOM codes based on distinct sum sets

#### 3.2.1 Bidirectional error correction codes based on distinct sum sets

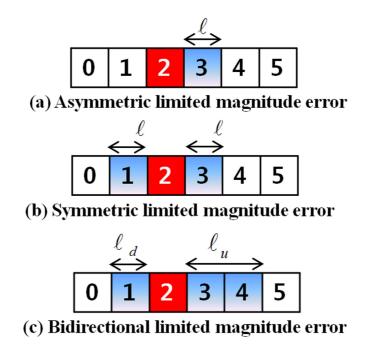

As described in the previous chapter, bidirectional error correction codes are efficient for practical systems. In the notation of  $(l_u, l_d)$ ,  $l_u$  and  $l_d$  represent the maximum upward error magnitude and the maximum downward error magnitude, respectively. Fig. 3.1 (a), (b),

and (c) illustrate the difference of various error types. The asymmetric limited magnitude errors of (a) are discussed in [8] [10], and the symmetric limited magnitude errors of (b) are considered in [16] [10]. However, little has been studied for the bidirectional limited magnitude errors of (c) [22] [35].

Figure 3.1 Various limited magnitude error types and  $(l_u, l_d)$  bidirectional error channel.

The bidirectional error correction codes which extend the technique of the limited magnitude error correction codes [10] to bidirectional error correction codes will be introduced. We define that a *bidirectional distinct sum set*  $\Phi_{\lambda}(l_u, l_d)$  of length m is a sequence of mdistinct positive integers  $\phi_0, \phi_1, \ldots, \phi_{m-1}$  such that all sums

$$\left(\sum_{j=1}^{\lambda} l_j \phi_{i_j}\right) \mod q \tag{3.1}$$

are distinct, where  $0 \le i_1 < i_2 < \cdots < i_\lambda \le m-1$  and  $-l_d \le l_j \le l_u$ .  $\lambda = 1$  case will be discussed at first.

**Definition 2.** When  $l_u$ ,  $l_d$  are given, we define a set

$$\Phi_{(l_u, l_d)} = \{1\} \cup \{\omega^i | max(l_u, l_d) < \omega^i \le \omega \cdot max(l_u, l_d), \\ \omega : prime, i: positive integer\},$$

(3.2)

and a sorting function  $\Omega(X, m) = \{x_k | x_1 < x_2 < \cdots < x_m, x_1, \cdots, x_m \text{ are } m \text{ smallest}$ elements in  $X, k = 1, \cdots, m\}$  for  $x_i \in X$  and  $|\Omega(X, m)| = m$ .

We then obtain a set of m elements, which is given by

$$\Phi^m_{(l_u, l_d)} = \Omega(\Phi_{(l_u, l_d)}, m) = \{\phi_1, \phi_2, \cdots, \phi_m\}$$

(3.3)

for  $\phi_1 < \phi_2 < \cdots < \phi_m$ .

The set  $\Phi^m_{(l_u, l_d)}$  is modified by the following conditions.

i) Let  $\tau_1$  and  $\tau_2$  be the two prime factors, which are not included in  $\Phi^m_{(l_u, l_d)}$  and less than  $max(l_u, l_d)$ . If there exist  $\tau_1^{\alpha} \tau_2^{\beta} < \phi_m$ ,  $\tau_1^{\alpha} \tau_2^{\beta}$  replaces  $\phi_m$  ( $\alpha, \beta$  : positive integers).

ii) When  $\tau^{\alpha} \in \Phi^{m}_{(l_{u},l_{d})}$  with prime  $\tau$  and  $\tau^{\alpha} max(l_{u},l_{d}) < \tau^{\beta} < \phi_{m}$ ,  $\tau^{\beta}$  replaces  $\phi_{m}$ .

iii) When  $\tau_1^{\alpha} \in \Phi_{(l_u,l_d)}^m$  with prime  $\tau_1$ , let  $\tau_2$  be the prime factor which is not included in  $\Phi_{(l_u,l_d)}^m$  and less than  $\max(l_u,l_d)$ . If  $\max(l_u,l_d) < \tau_1^{\beta}\tau_2^{\zeta} < \phi_m$  and  $\tau_1^{\beta}\max(l_u,l_d) < \tau_1^{\chi} < \phi_m$ ,  $\tau_1^{\beta}\tau_2^{\zeta}$  and  $\tau_1^{\chi}$  replace the  $\tau_1^{\alpha}$  and  $\phi_m$  ( $\alpha, \beta, \zeta, \chi$  : positive integers).

For example, when  $l_u = 7, l_d = 3, m = 6, \Phi_{(l_u, l_d)}^m = \{1, 8, 9, 11, 13, 17\}$  at first, and we get  $\phi_m$ =17. With case iii) of Definition 2, the prime factor 5 is not included in  $\Phi_{(l_u, l_d)}^m$ , and  $5 < \max(l_u, l_d)$ , so  $\tau_2 = 5$ .  $2^3 \in \Phi_{(l_u, l_d)}^m$  and  $\tau_1 = 2$ .  $\max(l_u, l_d) < 2 \cdot 5 < \phi_m$ and  $2\max(l_u, l_d) < 2^4 < 17$ . Then,  $2 \cdot 5 = 10$  and  $2^4 = 16$  replace 8 and 17. Finally,  $\Phi_{(l_u, l_d)}^m = \{1, 9, 10, 11, 13, 16\}.$

**Definition 3.** If  $\phi_m$  in distinct sum set  $\Phi^m_{(l_u, l_d)}$  which satisfies (3.1) is the minimum value, the set is defined as a minimum magnitude distinct sum set.

**Theorem 2.**  $\Phi_{(l_u,l_d)}^m = \{\phi_1, \phi_2, \cdots, \phi_m\}$  in Definition 2 are  $(l_u, l_d)$  distinct sum sets which satisfy (3.1) for all  $q \ge \phi_m(l_u + l_d) + 1$ .

*Proof.* Let  $1 \le v, w \le l_u$  or  $-l_d \le v, w \le -1$   $(v, w : integer, v \ne w), \phi_i, \phi_j \in \Phi^m$ ,  $\phi_i \ne \phi_j, 1 \le i, j \le m$ , and each of  $\phi_i$  and  $\phi_j$  has only one prime factor. Let us prove by contradiction. We assume that there exist  $v, w, \phi_i, \phi_j$  which satisfy  $v\phi_i = w\phi_j$ .  $v\phi_i = w\phi_j$ leads to  $\frac{v\phi_i}{w\phi_j} = 1$ .  $\phi_i$  and  $\phi_j$  are relatively prime, so  $|v| = \phi_j$  and  $|w| = \phi_i$ . According to the assumption in Definition 2,  $\phi_i$  or  $\phi_j > \max(l_u, l_d) > |v|, |w|$ , so  $|v| \ne \phi_j$  or  $|w| \ne \phi_i$ , which is a contradiction. Therefore  $v\phi_i \ne w\phi_j$ . Both  $v\phi_i, w\phi_j < \phi_m \max(l_u, l_d) < \phi_m(l_u + l_d) + 1$ ,  $v\phi_i \ne w\phi_j$  leads to  $v\phi_i \ne w\phi_j \mod q$  if  $q \ge \phi_m(l_u + l_d) + 1$ .

When  $\phi_i$  have two prime factor for the case i) of Definition 2,  $\tau_1^{\alpha} \tau_2^{\beta}$  will be the element.

$v\tau_1^{\alpha}\tau_2^{\beta} \neq w\phi_j$  for any j except i, because both prime factor  $\tau_1, \tau_2$  are not included in any  $\phi_i$ . For the case ii), if  $\phi_i$  and  $\phi_j$  have a common prime factor,  $\phi_i$  and  $\phi_j$  become  $\tau^{\alpha}$  and  $\tau^{\beta}$ . Because  $\tau^{\alpha}\max(l_u, l_d) < \tau^{\beta} < \phi_m$ ,  $|v|\tau^{\alpha} < |w|\tau^{\beta}$  and  $v\phi_i \neq w\phi_j$ . For the case iii), if  $\tau_1^{\beta}\tau_2^{\zeta}$  and  $\tau_1^{\chi}$  have a common prime factor  $\tau_1, \tau_1^{\beta}\max(l_u, l_d) < \tau_1^{\chi}$  leads to  $v\tau_1^{\beta}\tau_2^{\zeta} \neq w\tau_1^{\chi}$ . Let  $-l_d \leq v \leq -1, 1 \leq w \leq l_u$ .  $q - l_d\phi_m \leq (v\phi_i \mod q) < q$  and  $0 < w\phi_j \leq l_u\phi_m$ . Because  $\{0 < w\phi_j \leq l_u\phi_m < q - l_d\phi_m \leq v\phi_i < q\} \mod q, v\phi_i \neq w\phi_j \mod q$  is always valid.

**Remark 1.** It was shown by exhaustive computer search that  $\Phi_{(l_u, l_d)}$  given by Definition 2 is a minimum magnitude distinct sum set when  $m \leq 7$  and  $max(l_u, l_d) \leq 8$ .

| $\max(l_u, l_d)$ | m=3 | m=4 | m=5 | m=6 | m=7 |

|------------------|-----|-----|-----|-----|-----|

| 2                |     |     |     | ii  | ii  |

| 3                |     |     | iii |     |     |

| 4                | i   | i   |     |     |     |

| 5                | i   |     |     |     | iii |

| 6                |     |     |     |     | iii |

| 7                |     |     |     | iii | iii |

| 8                | i   | i   | i   |     |     |

Table 3.1 Modification cases in generating minimum magnitude distinct sum sets

As the parameters of  $\max(l_u, l_d)$ , *m* vary, the modification case of Definition 2 to generate the minimum magnitude distinct sum set is shown in Table 3.1. i,ii,iii represent the case i), case ii), and case iii) of Definition 2, respectively. The empty entries in Table II represent a case where minimum magnitude distinct sum sets are obtained by (3.2) and (3.3) only without any additional modification with the  $\max(l_u, l_d)$  and m.

Bidirectional error correction codes can be constructed by the  $\Phi_{(l_u,l_d)}^m$ . Let **H** be the  $r \times n$  parity check matrix, the columns of which are all possible r length q-ary vectors where the first nonzero element belongs to  $\Phi_{(l_u,l_d)}^m$ . If  $\mathcal{C}(\Phi_{(l_u,l_d)}^m)$  be the null space of  $\mathbf{H}^{\mathbf{T}}$ ,  $\mathcal{C}(\Phi_{(l_u,l_d)}^m)$  can correct a bidirectional error. If m and  $(l_u, l_d)$  are given and  $q \geq \tilde{q}$  in the

|              | $\widetilde{q}$ |     |     |     |     |

|--------------|-----------------|-----|-----|-----|-----|

| $(l_u, l_d)$ | m=2             | m=3 | m=4 | m=5 | m=6 |

| (1,0)        | 3               | 4   | 6   | 8   | 12  |

| (1,1)        | 5               | 7   | 11  | 15  | 23  |

| (2,0)        | 7               | 9   | 11  | 15  | 23  |

| (2,1)        | 10              | 13  | 16  | 22  | 34  |

| (2,2)        | 13              | 17  | 21  | 29  | 45  |

| (3,0)        | 13              | 16  | 22  | 28  | 34  |

| (3,1)        | 17              | 21  | 29  | 37  | 45  |

| (3,2)        | 21              | 26  | 36  | 46  | 56  |

| (3,3)        | 25              | 31  | 43  | 55  | 67  |

| (4,0)        | 21              | 25  | 29  | 37  | 45  |

| (4,1)        | 26              | 31  | 36  | 46  | 56  |

| (4,2)        | 31              | 37  | 43  | 55  | 67  |

| (4,3)        | 36              | 43  | 50  | 64  | 78  |

| (4,4)        | 41              | 49  | 57  | 73  | 89  |

Table 3.2 The parameters of  $\Phi^m_{(l_u, l_d)}$

Table 3.2,  $\Phi_{(l_u, l_d)}^m$  generated by Theorem 2 can correct a bidirectional error.

The set  $\Phi_{(l_u,l_d)}^m$  generated by Theorem 2 is optimal for special q and  $(l_u, l_d)$ . An optimal

set in this chapter means that m, the number of element in  $\Phi_{(l_u,l_d)}^m$  is maximized with given parameters q and  $(l_u, l_d)$ , and it can be obtained by an exhaustive search. If q equals to Table 3.3 The parameters which proposed method generates the optimal set

| $(l_u, l_d)$ | $\widetilde{q}$            |

|--------------|----------------------------|

| (2,0)        | 12                         |

| (2,1)        | 13, 14, 15, 17, 18, 19, 21 |

| (2,2)        | 20, 21, 24, 28             |

| (3,0)        | 16, 23                     |

| (3,1)        | 21, 22                     |

| (3,2)        | 26, 28, 29, 31, 36         |

| (4,0)        | 29                         |

| (4,1)        | 31, 33, 37, 39             |

| (4,2)        | 38                         |

| (4,3)        | 43, 51, 53, 54             |

$\tilde{q}$  in the Table 3.3, the proposed method generates the optimal set.  $\Phi_{(l_u,l_d)}^m$  generated by Theorem 2 can be used for the construction of symmetric error correction codes by setting  $l_u = l_d$ . [10] also proposed following method generating a *B*-set which can be used for the symmetric error. Note that

$$B = \{i(2l+1) + 1 | i \in [0, m-1]\}$$

(3.4)

is a B([-l, l])(q) set for q = 2p(l + 1) [10]. B[-l, l](q) is a sequence such that all sums are distinct in (3.1), where  $l_j \in [-l, l]$ . Our method for a symmetric error is compared to a method in [10] in Table 3.4. The proposed method can construct the symmetric error correction code for all  $q \ge \tilde{q}$ , while the method in [10] generate the symmetric code when only  $q = \tilde{q}$ . In addition to that, a lower  $\tilde{q}$  is more efficient clearly, and the proposed method

| Proposed |   | $	ilde{q}$ |       |       |       |

|----------|---|------------|-------|-------|-------|

|          | m | (1,1)      | (2,2) | (3,3) | (4,4) |

|          | 2 | 5          | 13    | 25    | 41    |

|          | 3 | 7          | 17    | 31    | 49    |

|          | 4 | 11         | 21    | 43    | 57    |

|          | 5 | 15         | 29    | 55    | 73    |

| [10]     | m | (1,1)      | (2,2) | (3,3) | (4,4) |

|          | 2 | 9          | 25    | 49    | 99    |

|          | 3 | 9          | 25    | 49    | 99    |

|          | 4 | 15         | 25    | 49    | 99    |

|          | 5 | 15         | 25    | 49    | 99    |

Table 3.4 A comparison of two methods for symmetric error correction code

produces lower  $\tilde{q}$  in most cases than the method in [10]. This shows the advantage of the proposed method.

There is discussion only of single error correction codes in [10], and bidirectional double error correction codes based on distinct sum sets can be considered. A new set  $\Psi = \{\psi_1, \psi_2, \dots, \psi_m\}$  is defined for double error correction.

**Remark 2.** For double error correction, there is a constraint that both  $(\alpha_x \psi_i + \alpha_y \psi_j \mod q)$ and  $(\alpha_z \psi_k \mod q)$  should be all distinct for any  $\psi_i, \psi_j, \psi_k \in \Psi, i \neq j \neq k$ , and  $-l_d \leq \alpha_x, \alpha_y, \alpha_z \leq l_u$  with integers  $i, j, k, \alpha_x, \alpha_y, \alpha_z$ , and  $l_u, l_d$ .

**Theorem 3.** If  $X = \{\omega^i | \omega : prime, i = 0, \dots, m - 1, \omega > max(l_u, l_d)\}$ , X is a  $\Psi$  set if  $q > (l_u + l_d)\omega^{m-2}(\omega + 1)$ .

*Proof.* At first, we prove  $\alpha_x \psi_i + \alpha_y \psi_j \neq \alpha_z \psi_k + \alpha_w \psi_o$  when all  $\alpha$  are positive integers  $(0 < \alpha \leq l_u < \omega)$  and  $k > o, i > j, i \neq j \neq k \neq o$ . The prime factor of  $\psi$  is  $\omega$ , and let  $\psi_i = \omega^i \in \Psi$ . If we assume  $\alpha_x \psi_i + \alpha_y \psi_j = \alpha_z \psi_k + \alpha_w \psi_o$ , then  $\alpha_x \omega^i + \alpha_y \omega^j = \alpha_z \omega^k + \alpha_w \omega^o$ , and  $\omega^j (\alpha_x \omega^{i-j} + \alpha_y) = \omega^o (\alpha_z \omega^{k-o} + \alpha_w)$ .  $\alpha_x \omega^{i-j} + \alpha_y < \alpha_x \omega^{i-j} + \omega \leq \alpha_x \omega^{i-j} + \omega^{i-j} = (\alpha_x + 1)\omega^{i-j} \leq \omega^{i-j+1}$ . Then  $\omega^i < \omega^j (\alpha_x \omega^{i-j} + \alpha_y) < \omega^{i+1}$  and  $\omega^k < \omega^o (\alpha_z \omega^{k-o} + \alpha_w) < \omega^{k+1}$ . Because  $\omega^j (\alpha_x \omega^{i-j} + \alpha_y) = \omega^o (\alpha_z \omega^{k-o} + \alpha_w)$ , *i* should be equal to *k*, which is a contradiction to the assumption of  $i \neq j \neq k \neq o$ , so we have

$\alpha_x \psi_i + \alpha_y \psi_j \neq \alpha_z \psi_k + \alpha_w \psi_o. \tag{3.5}$

Let us consider the case that all  $\alpha$  are negative integers. From (3.5),  $-\alpha_x\psi_i - \alpha_y\psi_j \neq -\alpha_z\psi_k - \alpha_w\psi_o$ . Let  $\tilde{\alpha}$  be  $-\alpha$ , then  $\tilde{\alpha_x}\psi_i + \tilde{\alpha_y}\psi_j \neq \tilde{\alpha_z}\psi_k + \tilde{\alpha_w}\psi_o$ , and the constraint is also valid in this case. In the case that two of four  $\alpha$  are negative and the others are positive,  $\alpha_x\psi_i - \alpha_w\psi_o \neq \alpha_z\psi_k - \alpha_y\psi_j$  from (3.5) and we have  $\alpha_x\psi_i + \tilde{\alpha_w}\psi_o \neq \alpha_z\psi_k + \tilde{\alpha_y}\psi_j$ . For the case that three  $\alpha$  are positive and the other is negative, we prove  $\alpha_x\omega^i + \alpha_y\omega^j \neq \alpha_z\omega^k + \tilde{\alpha_w}\omega^o$ . If we assume  $\alpha_x\omega^i + \alpha_y\omega^j = \alpha_z\omega^k + \tilde{\alpha_w}\omega^o$ ,  $\alpha_x\omega^i + \alpha_y\omega^j + \alpha_w\omega^o = \alpha_z\omega^k$ . k should be larger than i, j, o and assume i > j > o (the order can be changed). We get  $\alpha_z\omega^k - \alpha_x\omega^i - \alpha_y\omega^j = \alpha_w\omega^o$ . Dividing by  $\omega^o$ , we have  $\alpha_z\omega^{k-o} - \alpha_x\omega^{i-o} - \alpha_y\omega^{j-o} = \alpha_w$ , which is factorized to

$$\omega^{j-o}(\alpha_z \omega^{k-j} - \alpha_x \omega^{i-j} - \alpha_y) = \alpha_w, \tag{3.6}$$

and  $\omega^{j-o}(\omega^{i-j}(\alpha_z\omega^{k-i}-\alpha_x)-\alpha_y) = \alpha_w$ .  $\alpha_z\omega^{k-i} \ge \omega > \alpha_x$ , so  $\alpha_z\omega^{k-i}-\alpha_x \ge 1$  and  $\omega^{i-j}(\alpha_z\omega^{k-i}-\alpha_x)-\alpha_y \ge 1$ . Consequently,  $\omega^{j-o}(\alpha_z\omega^{k-j}-\alpha_x\omega^{i-j}-\alpha_y) > \alpha_w$  which is contradictory to (3.6). Therefore,  $\alpha_x\psi_i + \alpha_y\psi_j \ne \alpha_z\psi_k + \tilde{\alpha_w}\psi_o$ .

Next, we prove  $\alpha_x \psi_i + \alpha_y \psi_j \neq \alpha_z \psi_k$  ( $0 < \alpha \le l_u < \omega$ ). Let us assume that  $\alpha_x \psi_i + \alpha_y \psi_j = \alpha_z \psi_k$ , k > i > j > 0,  $i \neq j \neq k$ , and  $\alpha_x \omega^i + \alpha_y \omega^j = \alpha_z \omega^k$ . Dividing by  $\omega^j$ , we have  $\alpha_z \omega^{k-j} - \alpha_x \omega^{i-j} + = \alpha_y$ , which is factorized to

$$\omega^{i-j}(\alpha_z \omega^{k-i} - \alpha_x) = \alpha_y. \tag{3.7}$$

Because  $\omega^{i-j} \geq \omega$  and  $\alpha_z \omega^{k-i} \geq \omega > \alpha_x$ , we have  $\alpha_z \omega^{k-i} - \alpha_x \geq 1$ . It leads to  $\omega^{i-j}(\alpha_z \omega^{k-i} - \alpha_x) \geq \omega > \alpha_y$ , we then have  $\omega^{i-j}(\alpha_z \omega^{k-i} - \alpha_x) \neq \alpha_y$ , which is contradictory to (3.7). Thus, we conclude that

$$\alpha_x \psi_i + \alpha_y \psi_j \neq \alpha_z \psi_k. \tag{3.8}$$

In the case that two of three  $\alpha$  are negative and the other is positive,  $\alpha_x \psi_i + \alpha_y \psi_j \neq \alpha_z \psi_k$ from 3.8 and  $\alpha_x \psi_i \neq \alpha_z \psi_k - \alpha_y \psi_j$ . Then we have  $\alpha_x \psi_i \neq \alpha_z \psi_k + \tilde{\alpha_y} \psi_j$ . Because  $\max(\alpha_x \psi_i + \alpha_y \psi_j) < l_u \omega^{m-1} + l \omega^{m-2} = l_u \omega^{m-2} (\omega + 1)$  and  $\min(\alpha_x \psi_i + \alpha_y \psi_j) > -l_d \omega^{m-1} - l_d \omega^{m-2} = -l_d \omega^{m-2} (\omega + 1)$ , we have  $(\alpha_x \psi_i + \alpha_y \psi_j \neq \alpha_z \psi_k + \alpha_w \psi_o) \mod q$  when  $q > (l_u + l_d) \omega^{m-2} (\omega + 1)$ .

The construction of  $\mathbf{H}$  for single error correction is shown in [10], but it is not possible for double error correction, and it needs to consider new parity check matrix construction

$$\mathbf{H} = \begin{bmatrix} \omega & \cdots & \omega & \omega^2 & \cdots & \omega^2 & \omega^3 & \cdots & \omega^m \\ 1 & \cdots & k & k+1 & \cdots & k(k+1) & k^2+k+1 & \cdots & k(k^{m-1}+\dots+1) \end{bmatrix} (3.11)$$

for double error correction codes. Let us consider the case where the length of parity is r = 2. For  $l_1$  and  $l_2$  which are the magnitudes of double errors, we have

$$\mathbf{H} \cdot (\mathbf{c} + \mathbf{e})^{\mathbf{T}} = \mathbf{H} \cdot \mathbf{e}^{\mathbf{T}}$$

$$= \begin{bmatrix} \cdots & \psi_{j} & \psi_{j} & \cdots & \psi_{k} & \psi_{k} & \cdots \\ \cdots & \iota_{j1} & \iota_{j2} & \cdots & \iota_{k1} & \iota_{k2} & \cdots \end{bmatrix} \begin{bmatrix} \vdots \\ l_{1} \\ \vdots \\ l_{2} \\ \vdots \end{bmatrix},$$

where  $0 \leq l_1, l_2 \leq l, \psi \in \Psi$ , and  $\iota$  is an integer. For all distinct syndromes,

$$l_1\iota_{j1} + l_2\iota_{k2} \neq l_1\iota_{j2} + l_2\iota_{k1} \tag{3.9}$$

$$l_1(\iota_{j1} - \iota_{j2}) \neq l_2(\iota_{k1} - \iota_{k2}), \tag{3.10}$$

where  $\iota_{ji}$  is an integer element of a *distinct distance set*. If  $l_1 = \pm 1$  and  $l_2 = \pm 1$ , we have  $\iota_{j1} - \iota_{j2} \neq \pm (\iota_{k1} - \iota_{k2})$ . For instance, let  $|\Psi| = m$ ,  $l_1 = \pm 1$ ,  $l_2 = \pm 1$ ,  $q > \max(2\omega^{m-1}(\omega + 1), k^m + k^{m-1} + \dots + k^2 + k)$ , it is possible to construct a parity check matrix of  $2 \times km$ for double error correction based on distinct sum set, which is given in (3.11).

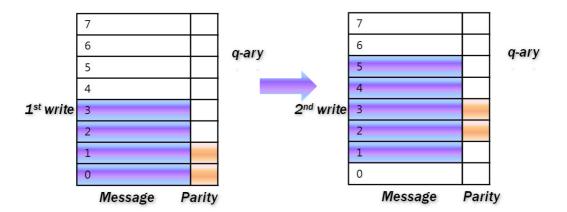

## **3.2.2** Error correction coding schemes for WOM codes based on distinct sum sets

WOM codes do not have error correction ability generally and conventional error correction codes cannot be applied directly to the WOM codes. Although the original messages are WOM codes, the codes that are encoded by general error correction codes lose the WOM property, and are no longer WOM codes. Even if systematic error correction codes are used to keep the property of WOM codes, the parity code part does not guarantee *t*-write WOM. Therefore, we proposed new methods for error correction codes for WOM codes based on distinct sets. To construct the codes, a parity splitting method is introduced.

Figure 3.2 Systematic error correction codes structure for WOM code.

Let  $\mathcal{C}(\Phi)$  be the null space of  $\mathbf{H}^{\mathbf{T}}$  and  $\mathbf{c} \in \mathcal{C}(\Phi)$ .  $\mathbf{c}$  is systematic code, and can be divided by a WOM message part  $\mathcal{W}$  and a parity part  $\mathcal{P} = [p_1 \ p_2 \ \cdots \ p_r]$ . Because  $\mathcal{P}$  is not WOM code, it should be converted  $\hat{\mathcal{P}}$  which satisfies the constraint of WOM code. If  $\mathbb{E}_i^p$ ,  $\mathbb{D}_i^p$  are WOM encoding and decoding function for parity parts,  $\hat{\mathcal{P}}_i = \mathbb{E}_i^p(\mathcal{P}_i, \hat{\mathcal{P}}_{i-1}) \geq \hat{\mathcal{P}}_{i-1}$  should be valid. Furthermore, if there is u errors within  $(l_u, l_d)$  in  $\hat{\mathcal{P}}_i$ ,  $\mathcal{P}_i$  obtained by  $\mathbb{D}_i^p(\hat{\mathcal{P}}_i)$  should have u or less errors within  $(l_u, l_d)$ . A simple example of  $\mathbb{E}_i^p$  can be introduced for a single error. The parity codes  $\mathcal{P}$  can be converted to a sum of s symbols with lower alphabet size,  $p_i = p_i^1 + p_i^2 + \dots + p_i^s$ .  $\Lambda(p_i^k)$  represents the alphabet size of  $p_i^k$ . The parameters s and  $\Lambda(p_i)$ of each cell should be determined with  $\Lambda(p_i) \leq \Lambda(p_i^1) + \dots + \Lambda(p_i^s)$ . If an  $(l_u, l_d)$  error occurs at the  $j_{th}$  parity symbol,  $p_i - l_d \leq p_i^1 + p_i^2 + \dots + (p_i^j + l) + \dots + p_i^s = p_i + l \leq p_i + l_u$ , and an error can be corrected by  $(l_u, l_d)$  bidirectional error correction codes. Let us assume  $\Lambda(p_1) = \dots = \Lambda(p_s) = \mu$ .

**Remark 3.**  $s \geq \lceil \frac{q}{\lfloor q/t \rfloor} \rceil$ , if  $\Lambda(p_1) = \cdots = \Lambda(p_s) = \mu$ .

$\mu t \leq q$  leads to  $\mu \leq \lfloor \frac{q}{t} \rfloor$ . Because  $s\mu$  represents the total alphabet size of  $\mu$ -ary s symbol, and  $s\mu$  should be larger than q, so  $s \geq \lceil \frac{q}{\lfloor q/t \rfloor} \rceil$ . Fig.3.2 shows the example of systematic error correction codes for non-binary WOM codes. The original message does not lose its WOM property due to the systematic codes, and the parity code part can guarantee t-write WOM. This method can only be used for single error correction.

The encoding and the decoding algorithms of the proposed codes based on distinct sum sets are described as follows.

Bidirectional distinct sum set-based non-binary WOM error correction codes (BD-WECC)

#### Encoding

Input : the  $i_{th}$  message codeword  $c_i, i = 1, \cdots, t$ .

Output :  $[\mathcal{W}_i \hat{\mathcal{P}}_i], i = 1, \cdots, t.$

$W_i$ : the  $i_{th}$  encoded WOM codeword of  $c_i$  message

$\hat{\mathcal{P}'}_i$ : the  $i_{th}$  parity code for WOM codeword

(Initialization) i = 1.

- **1)** Generate the parity check matrix **H** based on distinct-set  $\Phi_{(l_u, l_d)}^m$

- 2) Obtain non-binary WOM codes using encoding maps.

If

$$i = 1$$

,  $\mathcal{W}_1 = \mathbb{E}_1(c_1)$ .

or  $i \ge 2$ ,  $\mathcal{W}_i = \mathbb{E}_i(c_i, \mathcal{W}_{i-1})$

- **3**) Generate codes which is null space of  $\mathbf{H}^{\mathbf{T}}$  based on proposed bidirectional codes using  $\Phi^m_{(l_n,l_d)}$  and obtain r length parity codes  $\mathcal{P}_i$ .

- **4)** Encode r length parity codes into rs length WOM parity codes by  $\hat{\mathcal{P}}_i = \mathbb{E}_i^p(\mathcal{P}_i, \hat{\mathcal{P}}_{i-1})$ .

- **5)** Systematic encoded codewords  $[W_i \hat{\mathcal{P}}]$  are written to the q-ary memory cell.

- **6)** If i = t, go to step 7, else  $i \leftarrow i + 1$  and go to step 1.

- 7) *Erase the cells,*  $i \leftarrow 1$  *and go to step 1.*

#### Decoding

(Initialization) Received codeword  $[\mathcal{W}'_i \hat{\mathcal{P}}'_i] = [\mathcal{W}_i \hat{\mathcal{P}}] + \epsilon$ , where  $\epsilon = (\epsilon_1, \dots, \epsilon_n)$  is the error vector with each integer component within  $(l_u, l_d)$ ,

- **1)** Obtain the decoded parity codes by  $\mathcal{P}'_i = \mathbb{D}^p_i(\hat{\mathcal{P}}'_i)$ .

- **2)** Generate the syndrome by  $\mathbf{H} \cdot [\mathcal{W}'_i \mathcal{P}'_i]$ .

- **3**) *Estimate*  $\epsilon'$ , *the location and the magnitude of an error by syndrome.*

- 4) The corrected WOM encoded message  $W_i$  is obtained by  $W_i = W'_i \epsilon'$ .

- **5)** The original message is decoded by  $c_i = \mathbb{D}_i(\mathcal{W}_i)$

# **3.3** Bidirectional error correction codes for WOM codes based on modulo operation

#### 3.3.1 Bidirectional error correction codes based on modulo operation

We introduce t bidirectional  $(l_u, l_d)$  limited-magnitude error correction codes, which can reduce errors more effectively. The proposed code is systematic, and can correct t bidirectional errors with upward and downward magnitude of  $l_u$  and  $l_d$ , respectively. We call the codes the 'bidirectional limited magnitude error correction code based on modulo operation(BLM-ECC)'. Bidirectional limited-magnitude error correction codes [22] [35] extend the technique of the asymmetric error correction codes [8] to the bidirectional error correction codes. For example in  $(2_u, 1_d)$  channel, if cell data is '2' in a 6-ary cell, an error within  $-1 \le \epsilon \le 2$  can be added to the data value of '2', so the cell data can be  $1 \le 2 + \epsilon \le 4$ . The threshold voltage  $(V_T)$  of the cell is not integer, but it is assumed that the cell data and the error values are integer. Since we do not know the exact threshold voltage or the interference voltage by memory reading operation, only the integer decision after hard-decision is possible. Therefore, the cell data of 2 in the  $(2_u, 1_d)$  channel can be changed to 1, 2, 3, or 4 with an error.  $t - (l_u, l_d)$  BLM-ECC can correct the codeword with t errors of  $(l_u, l_d)$  magnitude. The code construction is as follows [35] [8]. Let  $\Omega$  be a q'-ary code and  $q' = l_u + l_d + 1$ . The q-ary code C (q > q') is defined as

$$\mathcal{C} = \{ \mathbf{c} = (c_1, ..., c_n) \mid \mathbf{c} \mod (l_u + l_d + 1) \in \Omega \}$$

(3.12)

C correct t bidirectional  $(l_u, l_d)$  limited-magnitude errors if  $\Omega$  corrects t symmetric errors. The process of encoding and decoding of the proposed codes is described as follows.

Let  $\mathbf{x} = \{x_1, \dots, x_k\}$  be a q-ary message codeword, and q-ary multi-level cell memory is assumed to be used. We get the q'-ary remainder of the q-ary message  $\mathbf{x}$  by modular q' operation  $(q' = l_u + l_d + 1, q' < q)$ . The q'-ary remainder codes are called *base codes*. In order to encode by the *base codes*, conventional p-ary t symmetric error correction codes are used, which is called *base error correction codes*. With  $\mathbf{x} \mod q'$  codeword, the p-ary parity codes can be obtained using base error correction codes. A p-ary parity codeword needs to be converted to a q-ary codeword  $\mathbf{p} = \{p_1, \dots, p_r\}$  in order to be stored in a qary memory cell. The systematic encoded codeword is then  $\mathbf{c} = [\mathbf{x} \mathbf{p}] = \{c_1, c_2, \dots, c_n\}$  and n = k + r. 'Systematic' means that the original message part and the parity part are separated in the encoded codeword. The code rate is defined by k/n. For every k symbols of useful information, the code generates total n symbols of data, of which n - k are parity codes. Since q > q', the base code size is smaller than that the original message, and the parity code size can be also reduced. Therefore, the code rate of the BLM-ECC is larger than that of conventional error correction code, and this is the key advantage of the proposed code.

However, the above encoding method can cause the error count mismatch problem. The problem means one erratic cell usually causes two or more errors. There are two kinds of the problem, one is a *message correction problem* when p < q',  $l \ge 2$ , and the other is a *parity code writing problem* when p < q,  $l \ge 2$ . Let us discuss the message correction problem first. One error in a q-ary cell can cause two or more errors in a p-ary message codeword if p < q'. For example, in a  $(2_u, 1_d)$  memory channel, let us assume that q = 8, q' = 4, and p = 2 (binary) are the parameters for the base error correction codes. Note that  $a_b$  means b-ary a value for convenience. A message code  $1_8$  is  $1_4$  and  $01_2$ . If l = 2 error occurs in the q-ary cell,  $1_8$  is changed to  $3_8$  which is  $3_4$  and  $10_2$  when the gray code (000, 001, 011, 010, 110, ...) is used. Two bits are different between  $01_2$  and  $10_2$ , and one cell error in the message cannot be corrected by t = 1 binary base error correction codes in this example. If  $p \ge q'$ , we can avoid the problem although p < q.

Next, let us describe the parity code writing problem when  $p < q, l \ge 2$ . The proposed