#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

Disclaimer 🖃

#### Ph.D. DISSERTATION

## High-Performance LDPC Decoding for Error Correction of NAND Flash Memory

낸드플래시 메모리 오류정정을 위한 고성능 LDPC 복호방법 연구

BY

JONGHONG KIM

**AUGUST 2013**

DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE COLLEGE OF ENGINEERING SEOUL NATIONAL UNIVERSITY

## High-Performance LDPC Decoding for Error Correction of NAND Flash Memory

낸드플래시 메모리 오류정정을 위한 고성능 LDPC 복호방법 연구

지도교수 성원용 이 논문을 공학박사 학위논문으로 제출함 2013년 8월

> 서울대학교 대학원 전기·컴퓨터 공학부 김 종 홍

김종홍의 공학박사 학위논문을 인준함 2013년 8월

| 위 원 | 장:  | 노  | 종 | 선 |  |

|-----|-----|----|---|---|--|

| 부위원 | 년장: | 성  | 원 | 용 |  |

| 위   | 원 : | 채  | 수 | 익 |  |

| 위   | 원 : | ०] | 정 | 우 |  |

| 위   | 원:  | 조  | 준 | 호 |  |

#### **Abstract**

High-performance error correction for NAND flash memory is greatly needed because the raw bit error rate increases as the semiconductor geometry shrinks for high density. Soft-decision error correction, such as low-density parity-check (LDPC) codes, offers high performance but their implementation complexity hinders wide adoption to consumer products. This dissertation proposes two high-performance message-passing schedules and a low-complexity decoding algorithm for LDPC codes. In particular, an efficient decoder architecture for finite geometry (FG) LDPC codes is proposed, and the energy consumption of soft-decision decoding for NAND flash memory is analyzed.

The first part of this dissertation is devoted to improving the informed dynamic scheduling (IDS) algorithms. We analyze the behavior of the residual belief propagation (RBP), which is the fastest IDS algorithm, and develop an improved RBP (iRBP) by avoiding the concentration of message updates at a particular node. We also study the syndrome-based mixed scheduling of the iRBP and the node-wise scheduling (NS). The proposed mixed scheduling outperforms all other scheduling methods tested in this work.

The next part of this dissertation is to develop a conditional variable node update scheme for the *a posteriori* probability (APP) algorithm. The developed algorithm is robust to decoding failures and can reduce the dynamic power consumption by lowering switching activities in the LDPC decoder. To implement the developed al-

gorithm, we propose a memory-efficient pipelined parallel architecture for LDPC

decoding. The architecture employs FG-LDPC codes that not only show fast conver-

gence speed and good error-floor performance but also perform well with iterative

decoding algorithms, which is especially suitable for data storage devices. We also

developed a rate-0.96 (68254, 65536) Euclidean geometry LDPC code and imple-

mented the proposed architecture in 0.13- $\mu$ m CMOS technology.

This dissertation also covers low-energy error correction of NAND flash mem-

ory through soft-decision decoding. The soft-decision-based error correction algo-

rithms show high performance, but they demand an increased number of flash mem-

ory sensing operations and consume more energy for memory access. We examine

the energy consumption of a NAND flash memory system equipping an LDPC code-

based soft-decision error correction circuit. The sum of energy consumed at NAND

flash memory and the LDPC decoder is minimized. In addition, the chip size and en-

ergy consumption of the decoder were compared with those of two Bose-Chaudhuri-

Hocquenghem (BCH) decoding circuits showing the comparable error performance

and the throughput. We also propose an LDPC decoder-assisted precision selection

method that needs virtually no overhead. This dissertation is intended to develop

high-performance and low-power error correction circuits for NAND flash memory

by studying improved decoding and scheduling algorithms, VLSI architecture, and a

read precision selection method.

Keywords: Dynamic scheduling, low-density parity-check (LDPC) codes, NAND

flash memory, soft-decision error correction, soft-decision sensing operation

**Student Number** : 2009-30185

ii

### **Contents**

| Al | ostrac  | ct                                                  |     |  |  | i   |

|----|---------|-----------------------------------------------------|-----|--|--|-----|

| Co | onten   | nts                                                 |     |  |  | iii |

| Li | st of l | Figures                                             |     |  |  | vi  |

| Li | st of ' | Tables                                              |     |  |  | ix  |

| 1  | Intr    | roduction                                           |     |  |  | 1   |

|    | 1.1     | NAND Flash Memory                                   |     |  |  | 1   |

|    | 1.2     | LDPC Codes                                          |     |  |  | 4   |

|    | 1.3     | Outline of the Dissertation                         |     |  |  | 6   |

| 2  | LDI     | PC Decoding and Scheduling Algorithms               |     |  |  | 8   |

|    | 2.1     | Introduction                                        |     |  |  | 8   |

|    | 2.2     | Decoding Algorithms for LDPC Codes                  |     |  |  | 10  |

|    |         | 2.2.1 Belief Propagation Algorithm                  |     |  |  | 10  |

|    |         | 2.2.2 Simplified Belief Propagation Algorithms      |     |  |  | 12  |

|    | 2.3     | Message-Passing Schedules for Decoding of LDPC Code | s . |  |  | 15  |

|   |      | 2.3.1   | Static Schedules                                           | 15     |

|---|------|---------|------------------------------------------------------------|--------|

|   |      | 2.3.2   | Dynamic Schedules                                          | 17     |

| 3 | Imp  | roved D | ynamic Scheduling Algorithms for Decoding of LDPC Codes    | 22     |

|   | 3.1  | Introdu | action                                                     | 22     |

|   | 3.2  | Improv  | ved Residual Belief Propagation Algorithm                  | 23     |

|   | 3.3  | Syndro  | ome-Based Mixed Scheduling of iRBP and NS                  | 26     |

|   | 3.4  | Compl   | exity Analysis and Simulation Results                      | 28     |

|   |      | 3.4.1   | Complexity Analysis                                        | 28     |

|   |      | 3.4.2   | Simulation Results                                         | 29     |

|   | 3.5  | Conclu  | nding Remarks                                              | 33     |

| 4 | A Pi | pelined | Parallel Architecture for Decoding of Finite-Geometry LDPC | !<br>• |

|   | Cod  | es      |                                                            | 36     |

|   | 4.1  | Introdu | action                                                     | 36     |

|   | 4.2  | Finite- | Geometry LDPC Codes and Conditional Variable Node Up-      |        |

|   |      | date A  | lgorithm                                                   | 38     |

|   |      | 4.2.1   | Finite-Geometry LDPC codes                                 | 38     |

|   |      | 4.2.2   | Conditional Variable Node Update Algorithm for Fixed-Point |        |

|   |      |         | Normalized APP-Based Algorithm                             | 40     |

|   | 4.3  | Decod   | er Architecture                                            | 46     |

|   |      | 4.3.1   | Baseline Sequential Architecture                           | 46     |

|   |      | 4.3.2   | Pipelined-Parallel Architecture                            | 54     |

|   |      | 4.3.3   | Memory Capacity Reduction                                  | 57     |

|   | 4.4  | Impler  | mentation Results                                          | 60     |

|   | 4.5  | Conclu  | uding Remarks                                              | 64     |

| 5  | Low    | -Energ   | y Error Correction of NAND Flash Memory through Sof      | t-  |

|----|--------|----------|----------------------------------------------------------|-----|

|    | Dec    | ision De | ecoding                                                  | 66  |

|    | 5.1    | Introdu  | uction                                                   | 66  |

|    | 5.2    | Energy   | y Consumption of Read Operations in NAND Flash Memory .  | 67  |

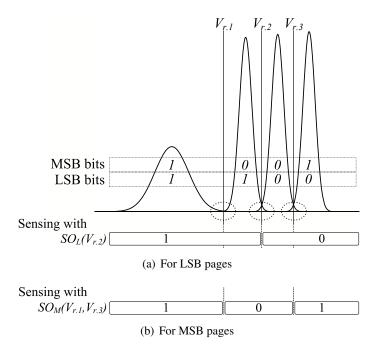

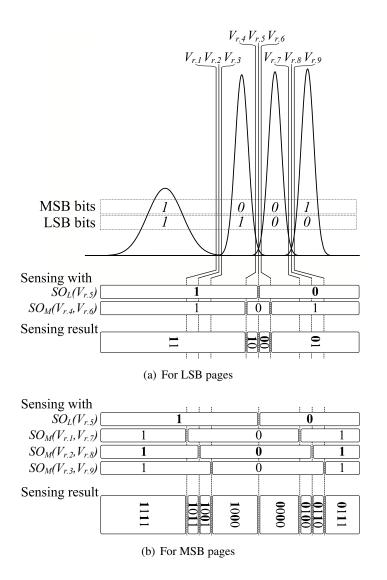

|    |        | 5.2.1    | Voltage Sensing Scheme for Soft-Decision Data Output     | 67  |

|    |        | 5.2.2    | LSB and MSB Concurrent Access Scheme for Low-Energy      |     |

|    |        |          | Soft-Decision Data Output                                | 72  |

|    |        | 5.2.3    | Energy Consumption of Read Operations in NAND Flash      |     |

|    |        |          | Memory                                                   | 73  |

|    | 5.3    | The Po   | erformance of Soft-Decision Error Correction over a NAND |     |

|    |        | Flash l  | Memory Channel                                           | 76  |

|    | 5.4    | Hardw    | vare Performance of the (68254, 65536) LDPC Decoder      | 81  |

|    |        | 5.4.1    | Energy Consumption of the LDPC Decoder                   | 81  |

|    |        | 5.4.2    | Performance Comparison of the LDPC Decoder and Two       |     |

|    |        |          | BCH Decoders                                             | 83  |

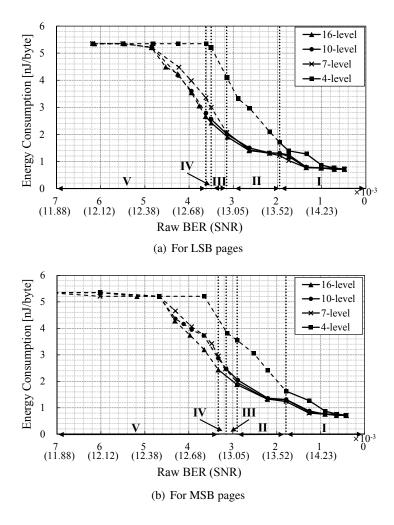

|    | 5.5    | Low-E    | Energy Error Correction Scheme for NAND Flash Memory     | 87  |

|    |        | 5.5.1    | Optimum Precision for Low-Energy Decoding                | 87  |

|    |        | 5.5.2    | Iteration Count-Based Precision Selection                | 90  |

|    | 5.6    | Conclu   | uding Remarks                                            | 91  |

| 6  | Con    | clusion  |                                                          | 94  |

| Bi | bliog  | raphy    |                                                          | 96  |

| Al | ostrac | et in Ko | rean                                                     | 110 |

## **List of Figures**

| 1.1 | Two bit-line structures of NAND flash memory                          | 3  |

|-----|-----------------------------------------------------------------------|----|

| 2.1 | A (2, 3)-regular (12, 5) RS-LDPC code                                 | 9  |

| 3.1 | Cumulative number of the continuous updates for the rate-1/2 1944-    |    |

|     | bit LDPC code                                                         | 25 |

| 3.2 | FER performance of the rate-1/3 1920-bit LDPC code                    | 31 |

| 3.3 | FER performance of the rate-1/2 1944-bit LDPC code for a $E_b/N_0$ of |    |

|     | 1.75 dB                                                               | 32 |

| 3.4 | FER performance of the rate-3/4 1944-bit LDPC code, where $E_b/N_0$   |    |

|     | is fixed to 3.10 dB                                                   | 33 |

| 3.5 | FER performance of the rate-1/3 1920-bit LDPC code with the max-      |    |

|     | imum iteration number of 50                                           | 34 |

| 3.6 | FER performance of the rate-1/2 1944-bit LDPC code for the maxi-      |    |

|     | mum iteration number of 10                                            | 34 |

| 3.7 | FER performance of the rate-3/4 1944-bit LDPC code over AWGN          |    |

|     | channel where the maximum iteration number is set to 15               | 35 |

| 3.8  | FER performance of the rate-1/2 1944-bit LDPC code for the maxi-         |    |

|------|--------------------------------------------------------------------------|----|

|      | mum iteration number of 50                                               | 35 |

| 4.1  | Parity-check matrices                                                    | 39 |

| 4.2  | Codeword structure of the (68254, 65536) shortened EG-LDPC code          |    |

|      | and its mapping method                                                   | 40 |

| 4.3  | Number of bit errors of the two LDPC codes with the normalized           |    |

|      | APP-based algorithm for 20 undecodable blocks                            | 41 |

| 4.4  | (Dashed line) Frame- and (solid line) bit-error performance of the       |    |

|      | (68254, 65536) shortened EG-LDPC code with the serial-C schedule         | 44 |

| 4.5  | Baseline architecture of the proposed LDPC decoder                       | 48 |

| 4.6  | Structure of a node processing unit                                      | 50 |

| 4.7  | Structure of a modified node processing unit                             | 50 |

| 4.8  | Saturation rate of a posteriori LLRs and bit transition probabilities at |    |

|      | the SNR of 5.5 dB                                                        | 51 |

| 4.9  | Critical path splitting through pipelining                               | 55 |

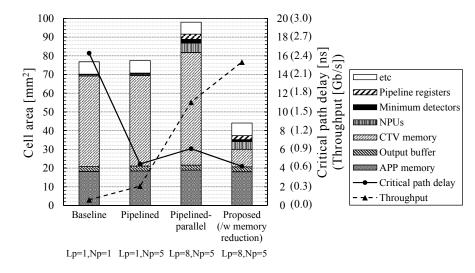

| 4.10 | Comparison of the cell area, the critical path delay, and the minimum    |    |

|      | decoding throughput of the four decoders that were synthesized in        |    |

|      | $0.13$ - $\mu$ m CMOS technology                                         | 55 |

| 4.11 | Organization of CTV memory and its connection to NPUs                    | 59 |

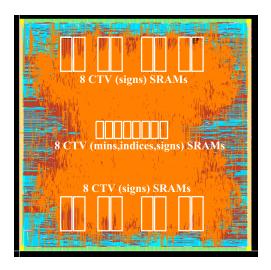

| 4.12 | Layout of the proposed LDPC decoder                                      | 63 |

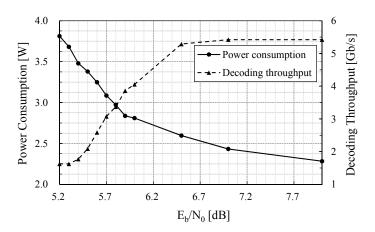

| 4.13 | Average power consumption and throughput of the decoder                  | 63 |

| 5.1  | Threshold voltage distributions and voltage sensing schemes of 2-bit     |    |

|      | MLC NAND flash memory                                                    | 68 |

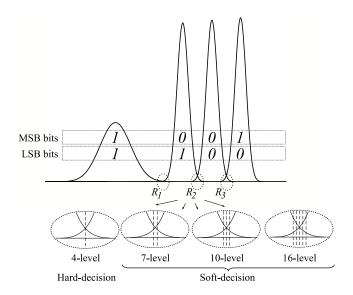

| 5.2  | Voltage sensing scheme of 4-level signal quantization                    | 69 |

| 5.3  | Voltage sensing scheme of 10-level signal quantization           | 71 |

|------|------------------------------------------------------------------|----|

| 5.4  | NAND flash memory with internal soft-decision data composition . | 73 |

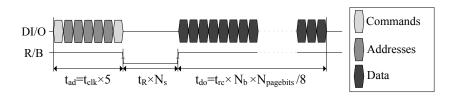

| 5.5  | Timing diagram of read page mode                                 | 73 |

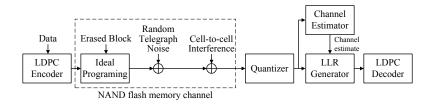

| 5.6  | MLC NAND flash memory channel model                              | 77 |

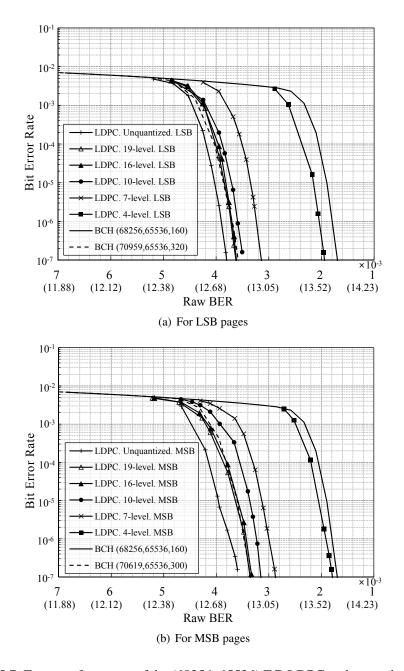

| 5.7  | Error-performance of the (68254, 65536) EG-LDPC code over the    |    |

|      | NAND flash memory channel                                        | 79 |

| 5.8  | The energy consumption of the (68254, 65536) LDPC decoder (65-   |    |

|      | nm VLSI) over NAND flash memory channel                          | 82 |

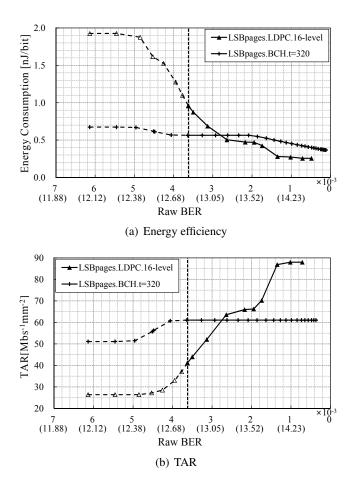

| 5.9  | Energy efficiency and TAR of the (68245, 65536) LDPC and (70959, |    |

|      | 65536, 320) BCH decoders for LSB pages                           | 85 |

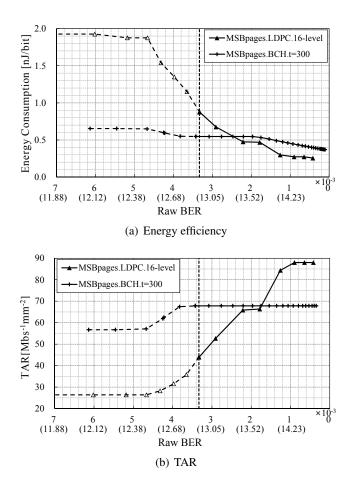

| 5.10 | Energy efficiency and TAR of the (68245, 65536) LDPC and (70619, |    |

|      | 65536, 300) BCH decoders for MSB pages                           | 86 |

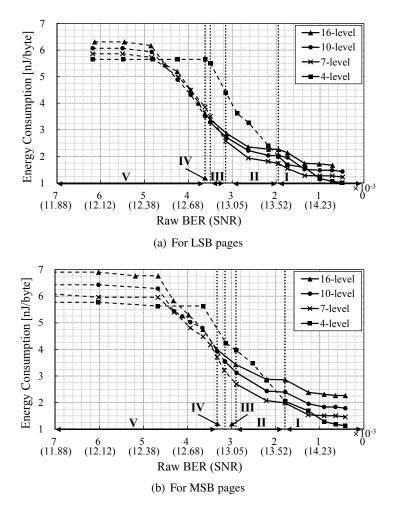

| 5.11 | The total energy consumption                                     | 88 |

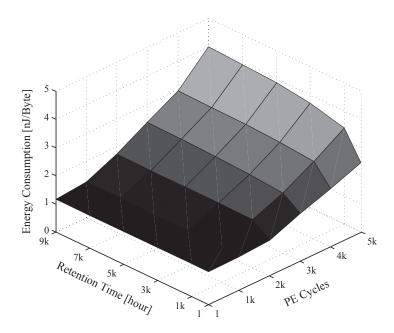

| 5.12 | The total energy consumption for MSB pages with the number of PE |    |

|      | cycles and retention time                                        | 89 |

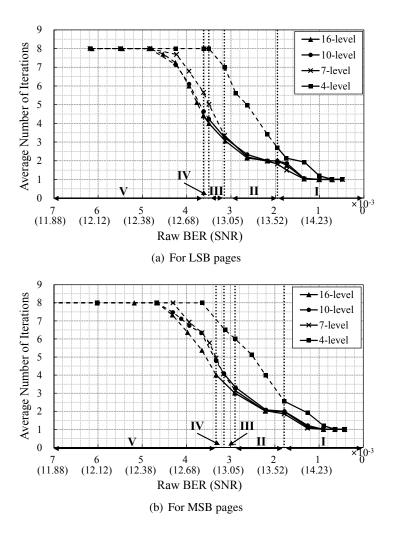

| 5.13 | Average number of decoding iterations of the (68254, 65536) LDPC |    |

|      | dagadar                                                          | 02 |

## **List of Tables**

| 1.1 | The features of 34-nm 2-bit MLC NAND flash memory                   | 3  |

|-----|---------------------------------------------------------------------|----|

| 3.1 | Computational complexity of schedules                               | 30 |

| 4.1 | Comparison of power consumption (in W)                              | 53 |

| 4.2 | Implementation results                                              | 61 |

| 5.1 | The number of sensing and data output (DO) operations for hard- and |    |

|     | soft-decision sensing with conventional NAND flash memory           | 70 |

| 5.2 | The voltage, current, and timing parameters of 2-bit MLC NAND       |    |

|     | flash memory                                                        | 75 |

| 5.3 | The energy consumption of a read operation for LSB and MSB pages    | 76 |

| 5.4 | The operating regions according to memory signal quantization       | 80 |

| 5.5 | The parallel factors of the two BCH decoders                        | 84 |

#### Chapter 1

#### Introduction

#### 1.1 NAND Flash Memory

NAND flash memory is widely used in many mobile devices, such as cellular phones, digital cameras, and smart-pads because of high capacity, fast access speed, and low power consumption. In particular, solid-state drives (SSDs) for notebook computers become popular as the density of NAND flash memory increases rapidly.

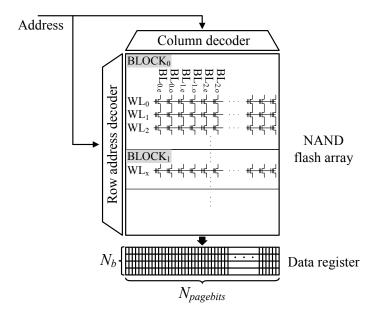

A NAND flash memory device contains thousands of cell blocks that can independently be erased. Each cell block consists of rows and columns of cells. The cells in the same row and those in the same column are controlled by the same word-line (WL) and the same bit-line (BL), respectively. Each flash memory cell is a floating gate NMOS transistor in which the gate stores charges to control the threshold voltage of the transistor. Because of the process variation, program inaccuracy, charge leakage, and noise, the threshold voltage of NAND flash memory has a Gaussian-like distribution, which can cause bit errors when reading the cell. Hence, traditionally,

NAND flash memory systems equip error correction circuits that employ Hamming, Bose-Chaudhuri-Hocquenghem (BCH), or Reed-Solomon (RS) codes [1, 2, 3, 4, 5].

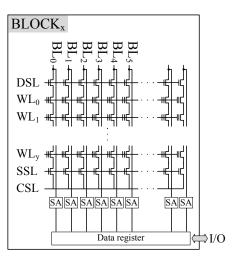

Conventional NAND flash memory devices adopt either all-BL or even/odd-BL structure. Figure 1.1(a) shows the all-BL structure in which all the cells in the same WL can be read or programmed simultaneously, where DSL, SSL, and CSL denote drain-select, source-select, and common-source lines, respectively. Because the unit of read and write operations is called a *page*, the number of BLs in the all-BL structure equals to the number of bits in a page. Note that the typical page size of the current generation of NAND flash memory is 64 kbits (8 kbytes) besides the parity data. The even/odd-BL structure is illustrated in Fig. 1.1(b) in which the cells in even BLs and those in odd BLs are independently selected, thus the same peripherals can be shared by two adjacent BLs, and two pages are mapped to an WL. Although the even/odd-BL structure reduces the overhead of peripheral circuits by sharing data latches and sense amplifiers (SAs), this one incurs larger cell-to-cell interference (CCI) when compared to the all-BL structure.

Today's NAND flash memory adopts the multi-level cell (MLC) technology that stores more than one bit per memory cell to increase the density. The organization of a 128-Gbit NAND flash memory device with 2-bit MLC technology is shown in Table 1.1 [6]. Note that in 2-bit MLC NAND flash memory, two and four pages are mapped to an WL in the all-BL and the even/odd-BL structures, respectively.

The MLC technology, however, reduces the gap between adjacent threshold voltage levels, which significantly increases the bit error rate (BER). Moreover, as the feature size of NAND flash memory shrinks, the number of electrons in the floating gate of a transistor also decreases, and as a result, the memory is very prone to charge loss caused by long data retention [7]. The CCI also increasingly deteriorates

(a) All-bit-line structure

(b) Even/odd-bit-line structure

Figure 1.1: Two bit-line structures of NAND flash memory

Table 1.1: The features of 34-nm 2-bit MLC NAND flash memory

| Capacity    | 128 Gbits         |

|-------------|-------------------|

| MLC tech.   | 2 bits/cell       |

| Device size | 8,192 blocks      |

| Block size  | 256 pages         |

| Page size   | 8,192 + 448 bytes |

the reliability of information stored at the floating gates [8, 9]. It is also well known that SSD applications usually demand high program-and-erase cycles, which greatly affects the reliability of NAND flash memory [10].

NAND flash memory devices have a spare region at each page to store parity bits for error correction. Traditionally, Hamming and BCH codes have been widely used for NAND flash memory error correction. However, as the process technology scales down continuously, more advanced error-correcting codes are needed to keep NAND flash memory reliable. Soft-decision error-correcting methods can increase

the error-correcting performance because the reliability of stored information can also be utilized. In this dissertation, we consider LDPC codes as error correction of NAND flash memory because of their excellent error-correcting capability and highly parallelizable decoding scheme.

#### 1.2 LDPC Codes

LDPC codes [11, 12] have received great attention in recent years because of their capacity-approaching performance and fully parallelizable decoding algorithms. In particular, LDPC codes have successfully been applied to many communication systems such as DVB-S2 [13], IEEE 802.3an [14], IEEE 802.11n [15], and IEEE 802.16e [16].

The performance of LDPC decoding can be improved by employing the serial message passing schedule [17, 18, 19, 20, 21]. The serial schedule uses the renewed messages immediately for updating their neighboring nodes and, as a result, shows better error performance than the conventional flooding-based ones. In addition, the informed dynamic scheduling (IDS) algorithms not only increase the convergence of the decoding but also significantly improve the error performance by removing trapping set errors [22, 23] when compared to the static scheduling algorithms such as the serial and the flooding schedules. Although it takes more operations to decode a codeword due to the nature of the IDS algorithms, it can be used for future applications where error performance is critical. Meanwhile, in order to further improve the error performance, mixed scheduling of IDS algorithms has been intensively studied in the past few years [23, 24, 25, 26]. In this dissertation, we propose an improved IDS algorithm to increase the convergence speed. We also propose a mixed IDS strategy

that adopts a different approach to improve the error performance of the algorithm compared to the adaptive mixed scheduling algorithms [23, 24, 25, 26].

With the advances in semiconductor technology, there have been many works to implement LDPC decoders in VLSI. The early stage of the study featured fully parallel LDPC decoders with the belief propagation (BP) algorithm [27, 28]. However, in order to reduce the implementation cost, most high-throughput LDPC decoders [29, 30, 31] usually employ partially parallel architectures with the min-sum (MS) algorithm, an approximate BP algorithm [32, 33]. Moreover, since LDPC codes were chosen in many communication standards, multi-rate LDPC decoders have been extensively studied [34, 35, 36]. Nevertheless, only little work has been conducted on the implementation of LDPC decoders with a large code length [37, 38, 39].

LDPC codes have been considered for error correction of NAND flash memory [40, 41, 42] because of severe performance degradation of recent NAND flash memory devices. The threshold voltage signal of high-density NAND flash memory contains a large amount of noise because of aggressive scaling down of memory cells, CCI, program-and-erase (PE) cycling, data retention, and MLC technology. Hard-decision error correction algorithms, such as BCH or RS, are no more sufficient for high-density NAND flash memory. In NAND flash memory, the read and write operations are performed by the unit of a page that has been recently increased to 8 kB. In addition, the empirical performance of LDPC codes converges to its expected behavior as the code length increases [43]. Therefore, LDPC codes with fairly large code lengths need to be studied for the application to NAND flash memory. Soft-decision decoding of LDPC codes shows much better error correcting performance than hard-decision decoding, however it demands multiple memory sensing operations. Multiple sensing operations and delivering soft-decision data obviously

increase the energy consumption of NAND flash memory. In this dissertation, we implement a high-rate LDPC decoding circuit for NAND flash memory and analyze the energy consumption of a NAND flash memory system with soft-decision LDPC decoding.

#### 1.3 Outline of the Dissertation

This dissertation is organized as follows. Chapter 2 describes the background of LDPC codes, decoding algorithms, and message-passing schedules. In Chapter 3, two improved dynamic scheduling algorithms are proposed. The improved residual BP (RBP) algorithm that increases the convergence of the conventional RBP algorithm is proposed in Section 3.2, and mixed scheduling of two IDS algorithms is developed and presented in Section 3.3. Chapter 4 proposes a pipelined parallel architecture for decoding of finite geometry (FG) LDPC codes. The conditional variable node update algorithm that makes the conventional normalized a posteriori probability (APP) algorithm resilient to decoding failure is proposed in Section 4.2. The proposed decoder architecture and optimization strategies are described in Section 4.3. Section 4.4 provides the implementation results. Chapter 5 analyzes the energy consumption for read operation of NAND flash memory with soft-decision error correction. The performance of LDPC decoding for NAND flash memory is presented in Section 5.3. The energy consumption for NAND flash memory access and that of the LDPC decoder implemented in Chapter 4 are examined in Section 5.2 and Section 5.4, respectively. Section 5.5 optimizes the total energy consumption for accessing NAND flash memory with soft-decision error correction and proposes an LDPC decoder-assisted precision selection method. Finally, Chapter 6 concludes this dissertation.

The material in this dissertation was presented in [44, 45, 46, 47, 48].

#### **Chapter 2**

## LDPC Decoding and Scheduling Algorithms

#### 2.1 Introduction

LDPC codes are linear codes with parity-check matrices having few non-zero elements, which allows low decoding complexity, and show good error performance when decoded with soft-decision information. A  $(d_v, d_c)$ -regular (N, K) LDPC code is defined by an  $M \times N$  parity-check matrix H with the column weight  $d_v$  and the row weight  $d_c$ , where N and K denote the code length and the number of information bits, respectively, and  $M \ge N - K$ . Note that  $d_v$  and  $d_c$  are also referred to as the degree of a variable node and that of a check node, respectively. If H is full rank, M = N - K. Each column of the parity-check matrix corresponds to a codeword bit, and each row of the matrix represents a parity-check constraint that defines a code; i.e.,  $\sum_{n \in \mathbb{N}(m)} \bigoplus c_n = 0$  for m-th row, where  $\bigoplus$  denotes the exclusive OR (XOR) operation. The number of parity bits, N - K, of an LDPC code corresponds to the rank of

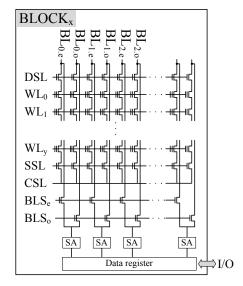

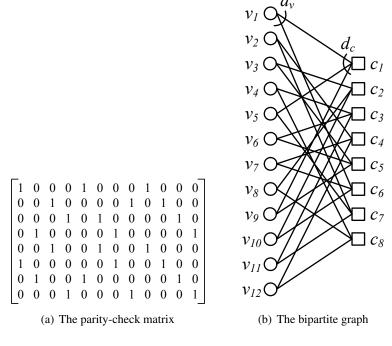

Figure 2.1: A (2, 3)-regular (12, 5) RS-LDPC code

the parity-check matrix of the code.

The LDPC code can be represented by a bipartite graph that has N variable nodes and M check nodes as well as edges. Each variable node corresponds to a codeword bit, or equivalently a column of the parity-check matrix, and each check node corresponds to a parity-check constraint, or equivalently a row of the matrix. Since there is an edge between the n-th variable node and the m-the check node if and only if  $H_{m,n} = 1$ , every variable (check) node is connected to  $d_v$  check ( $d_c$  variable) nodes. Note that for irregular LDPC codes,  $d_v$  or  $d_c$  are not constant. Figure 2.1 shows the parity-check matrix of a (2, 3)-regular (12, 5) RS-LDPC code and the corresponding bipartite graph. Every variable node has  $d_v$  (= 2) neighboring check nodes and every check node are connected to  $d_c$  (= 3) variable nodes. Since the parity-check matrix

contains one redundant row,  $M \neq N - K$ .

In the bipartite graph, each edge has a variable-to-check (VTC) and a check-to-variable (CTV) messages that can be represented as either probabilities or log-likelihood ratios (LLRs). However, in practice, it is more convenient to use LLRs [11, 12]. Each node receives messages from neighboring nodes, updates the outgoing messages, and propagates the messages back to its neighboring nodes. The message update rules for variable and check nodes are given by decoding algorithms, whereas the order of message updates is determined by scheduling algorithms. Therefore, decoding of LDPC codes can be configured in many ways according to decoding and scheduling algorithms. In the following section, decoding and scheduling algorithms are introduced.

#### 2.2 Decoding Algorithms for LDPC Codes

This section contains a brief review of decoding algorithms for LDPC codes. The belief propagation (BP) algorithm that provides the best error performance is described in Section 2.2.1, and simplified BP algorithms that approximate the variable and check node update operations are explained in Section 2.2.2.

#### 2.2.1 Belief Propagation Algorithm

The probabilistic decoding was devised by Gallager [11, 12] and later generalized by Tanner [49] and Wiberg [32], whereas the BP algorithm, also known as the sumproduct algorithm [50], was first proposed by Pearl [51]. However, it turned out that the probabilistic decoding is a special version of the BP algorithm [52, 53, 50].

In order to describe the BP decoding algorithm, the following notations are first

introduced. Let  $c = \{c_1, c_2, \dots, c_N\}$ ,  $x = \{x_1, x_2, \dots, x_N\}$ , and  $y = \{y_1, y_2, \dots, y_N\}$  be an N-bit cordword, the transmitted bipolar sequence, and the corresponding received word, respectively, where  $c_n \in \{0, 1\}$  and  $x_n \in \{\pm 1\}$ . Let  $I_n$  be the channel LLR of the n-th received symbol, and let  $Z_n$  be the a posteriori LLR of the n-th variable node. Let  $L_{mn}$  denote a CTV message sent from the check node m to the variable node n. Similarly, let  $Z_{nm}$  be a VTC message sent from the variable node n to the check node m. Define N(m) and M(n) as the set of variable nodes connected to the check node m and that of check nodes connected to the variable node n, respectively. Then, the variable and check node update rules are given by

$$Z_{nm} = I_n + \sum_{m' \in \mathcal{M}(n) \setminus m} L_{m'n}$$

(2.1)

and

$$L_{mn} = \prod_{n' \in \mathcal{N}(m) \setminus n} \operatorname{sign}(Z_{n'm}) \times 2 \tanh^{-1} \left( \prod_{n' \in \mathcal{N}(m) \setminus n} \tanh\left(\frac{|Z_{n'm}|}{2}\right) \right), \tag{2.2}$$

respectively, and the a posteriori LLR is computed by

$$Z_n = I_n + \sum_{m \in \mathcal{M}(n)} L_{mn}. \tag{2.3}$$

For a binary-input memoryless channel, the channel LLR is given by

$$I_n = \ln \frac{p(c_n = 0|y_n)}{p(c_n = 1|y_n)}.$$

(2.4)

If a codeword *c* is transmitted over an additive white Gaussian noise (AWGN) channel

with zero mean and variance  $\sigma^2$ ,

$$I_n = \ln \frac{p(c_n = 0|y_n)}{p(c_n = 1|y_n)} = \begin{cases} -2y_n/\sigma^2, & x_n = 2c_n - 1\\ 2y_n/\sigma^2, & x_n = (-1)^{c_n}. \end{cases}$$

(2.5)

Note that the channel LLR is also called the intrinsic information, whereas the VTC and CTV messages are also referred to as the extrinsic information. Note also that the check node update rule of Gallager's probabilistic decoding is

$$L_{mn} = \prod_{n' \in \mathcal{N}(m) \setminus n} \operatorname{sign}(Z_{n'm}) \times f\left(\sum_{n' \in \mathcal{N}(m) \setminus n} f(|Z_{n'm}|)\right), \tag{2.6}$$

where  $f(x) = \ln(e^x + 1) / (e^x - 1)$ .

#### 2.2.2 Simplified Belief Propagation Algorithms

The variable and check node update rules of the BP decoding can be simplified using the *a posteriori* probability (APP) [33] and the min-sum (MS) algorithms [32], respectively. These simplified algorithms show degraded error performance when compared to the BP decoding but greatly reduce the implementation complexity, especially for LDPC codes with high node degrees. The Max-Log-MAP algorithm presented in [54] and the max-product algorithm [55] are equivalent to the MS algorithm, where the performance of the Max-Log-MAP and max-product algorithms were evaluated using the density evolution [43]. In addition, the reduced-complexity decoding algorithms based on the forward-backward algorithm [50] that operates in the LLR domain was proposed [56] and later elaborated [57] in which piecewise linear approximation of the check node update operation was also proposed.

Two modified versions of the MS algorithm improve the error performance using a normalization factor [58] or a single correction term [56, 59]. The MS algorithm with a normalization factor is called the normalized MS (NMS) algorithm, whereas that with a single correction term is referred to as the offset MS decoding (OMS) [60]. The modified MS algorithms incur only negligible degradation in error performance when compared to the BP algorithm. The normalized APP-based algorithm that combines the APP and NMS algorithms was also proposed to improve the error performance of the APP algorithm [61]. After that, the MS algorithms has been extensively studied in the last decade, which includes the  $\lambda$ -min algorithm [62], the MS with conditional correction [63], the MS with the degree-matched approximation [64], the adaptive OMS [65], the two-dimensional NMS [66], the transformed MS [67], the self-corrected MS [68], and the MS with two normalization factors [69].

The asymptotic performance of the modified MS algorithms were analyzed using DE in [59, 60, 70, 71], and the quantization effects of fixed-point arithmetic in the algorithms were studied in [63, 70, 72, 73, 74, 75].

In the following, the MS and its modified versions are described.

#### 2.2.2.1 Min-Sum Algorithms

The MS algorithm and its two modified versions, the NMS and OMS algorithms, approximate the check node update rule of the BP decoding, while preserving the variable node update rule. In the MS algorithm, the core operation of the check node

update rule can be approximated as [76]

$$L(U \oplus V) = \log \frac{1 + e^{L(U) + L(V)}}{e^{L(U)} + e^{L(V)}}$$

$$= \operatorname{sign}(L(U)) \operatorname{sign}(L(V)) \cdot \min(|L(U)|, |L(V)|) + s(L(U), L(V))$$

$$\approx \operatorname{sign}(L(U)) \operatorname{sign}(L(V)) \cdot \min(|L(U)|, |L(V)|), \qquad (2.7)$$

where U and V are statistically independent random variables, and the term  $s(L(U),L(V)) = \log\left(1+e^{-|L(U)+L(V)|}\right) - \log\left(1+e^{-|L(U)-L(V)|}\right)$  is the correction factor [57]. Then, Eq. (2.2) can be written as

$$L_{mn} = \prod_{n' \in \mathcal{N}(m) \setminus n} \operatorname{sign}(Z_{n'm}) \cdot \min_{n' \in \mathcal{N}(m) \setminus n} |Z_{n'm}|.$$

(2.8)

The correction factor in Eq. (2.7) can be approximated to a fixed number  $\beta > 0$ , then the check node operation Eq. (2.2) becomes

$$L_{mn} = \prod_{n' \in \mathcal{N}(m) \setminus n} \operatorname{sign}(Z_{n'm}) \cdot \max\left(\min_{n' \in \mathcal{N}(m) \setminus n} |Z_{n'm}| - \beta, 0\right), \tag{2.9}$$

which corresponds to the check node update rule of the OMS algorithm. In the NMS algorithm, a scaling factor  $\beta < 1$  is introduced to reduce the overestimated CTV messages in the MS algorithm, that is to say  $|L(U \oplus V)| \leq \min(|L(U)|, |L(V)|)$  [72]. The check node update rule of the NMS algorithm is given by

$$L_{mn} = \prod_{n' \in \mathcal{N}(m) \setminus n} \operatorname{sign}(Z_{n'm}) \cdot \min_{n' \in \mathcal{N}(m) \setminus n} |Z_{n'm}| \cdot \alpha.$$

(2.10)

#### 2.2.2.2 APP Algorithm

The APP algorithm simplifies the variable node operation by substituting the extrinsic outgoing messages from a variable node with the *a posteriori* LLR of the corresponding variable node [33], namely  $Z_{nm} = Z_n \ \forall n, m \in \mathcal{M}(n)$ , while maintaining the same check node update rule of the BP decoding. The APP algorithm not only reduces the computational complexity of the variable node operation but also saves the memory that stores the extrinsic information  $Z_{nm}$ . However, the correlation among the extrinsic outgoing messages significantly degrades the error performance compared to the BP and MS decoding algorithms [33, 72].

#### 2.3 Message-Passing Schedules for Decoding of LDPC Codes

This section describes the scheduling algorithms that determine the order of message updates for decoding of LDPC codes. The scheduling algorithms are categorized into static and dynamic schedules; the former updates messages in a predetermined order, whereas the latter dynamically updates messages based on a specific metric such as the reliabilities or residuals of the messages propagated. Depending on the scheduling algorithm employed, LDPC decoding shows different performance and complexity characteristics. We start with the static scheduling algorithms that include flooding and the serial schedule.

#### 2.3.1 Static Schedules

Flooding is the most well-known message-passing schedule that first updates all check nodes with VTC messages and then updates all variable nodes with intrinsic information and the CTV messages in every iteration, which is also known as the

two-phase message-passing algorithm. The BP decoding with the flooding schedule is formally described in Algorithm 1.

#### Algorithm 1 The BP decoding with flooding schedule

k = k + 1

Go to line 3;

18:

19:

20: **end if**

```

1: Initialize k = 0

2: Initialize all Z_{nm}^{(-1)} = I_n

3: for m = 1 to M do

for every n \in \mathcal{N}(m) do

5:

L_{mn}^{(k)} = \prod_{n' \in \mathcal{N}(m) \setminus n} \operatorname{sign}\left(Z_{n'm}^{(k-1)}\right) \times 2 \tanh^{-1}\left(\prod_{n' \in \mathcal{N}(m) \setminus n} \tanh\left(\frac{\left|Z_{n'm}^{(k-1)}\right|}{2}\right)\right)

end for

6:

7: end for

8: for n = 1 to N do

for every m \in \mathcal{M}(n) do

Z_{nm}^{(k)} = I_n + \sum_{m' \in \mathcal{M}(n) \setminus m} L_{m'n}^{(k)}

Z_n^{(k)} = I_n + \sum_{m \in \mathcal{M}(n)} L_{mn}^{(k)}

10:

11:

end for

12:

14: Decide a hard-decision vector \hat{\mathbf{w}} = \{\hat{w}_1, \dots, \hat{w}_N\} based on

\hat{w}_n = \begin{cases} 0, & \text{if } Z_n^{(k)} \ge 0\\ 1, & \text{otherwise} \end{cases}

15: if H\hat{\mathbf{w}}^T = 0 or the maximum iteration number is reached then

Output the hard-decision \hat{w}

16:

17: else

```

Another well-known static scheduling algorithm is the serial-C schedule [17] in which a check node is updated with its neighboring variable nodes first, and then the newly updated check node messages are immediately used to partially update the

variable nodes. The layered [18] and turbo decoding [19] algorithms are equivalent to the serial-C schedule. The serial-V schedule is a dual algorithm to the serial-C one, hence a variable node is updated first, and then the neighboring check nodes are updated. The shuffled iterative decoding [20] and the lazy scheduling [21] are equivalent to the serial-V schedule.

The serial schedule is advantageous in convergence speed and hardware implementation. Both the serial-C and serial-V schedules converge almost twice faster than the conventional flooding and save the memory for storing the VTC messages,  $Z_{nm}$ 's, because the VTC messages can be recovered from the APP and CTV messages, namely  $Z_{nm} = Z_n - L_{mn}$ . The BP decoding with the serial-C and that with the serial-V schedule are formally described in Algorithm 2 and 3, respectively, where  $P_m$  denotes the *check product* of the *m*-th check node and  $\Delta L_{mn}^{(k)} = L_{mn}^{(k)} - L_{mn}^{(k-1)}$ . Note that the BP decoding with the serial-V schedule needs additional memory for M check products.

#### 2.3.2 Dynamic Schedules

This subsection introduces the dynamic scheduling algorithms based on *residuals*, which is called the informed dynamic scheduling (IDS) strategies. The IDS of the BP decoding was first proposed under the name of the residual BP (RBP) algorithm by Elidan *et al.* [77]. Then, Vila Casado *et al.* applied the algorithm to decoding of LDPC codes and also introduced the node-wise scheduling (NS) to relieve the problem caused by the greediness of the RBP [22, 23]. Since then, variants of IDS have been investigated [24, 25, 26, 78, 79, 80].

The RBP is an IDS scheme that schedules message updates according to the *residual* that is defined as the norm of the difference between the messages before and after an update [77]. Since all of the messages are represented as one-dimensional vari-

#### Algorithm 2 The BP decoding with the serial-C schedule

```

1: Initialize k = 0

2: Initialize all Z_n = I_n

3: Initialize all L_{mn}^{(-1)} = 0

4: for m = 1 to M do

for every n \in \mathcal{N}(m) do Z_{nm}^{(k-1)} = Z_n - L_{mn}^{(k-1)}

6:

7:

for every n \in \mathcal{N}(m) do

8:

L_{mn}^{(k)} = \prod_{n' \in \mathcal{N}(m) \backslash n} \operatorname{sign}\left(Z_{n'm}^{(k-1)}\right) \times 2 \tanh^{-1}\left(\prod_{n' \in \mathcal{N}(m) \backslash n} \tanh\left(\frac{\left|Z_{n'm}^{(k-1)}\right|}{2}\right)\right)

end for

10:

for every n \in \mathcal{N}(m) do Z_n = Z_{nm}^{(k-1)} + L_{mn}^{(k)}

11:

12:

13:

14: end for

15: Decide a hard-decision vector \hat{\mathbf{w}} = \{\hat{w}_1, \dots, \hat{w}_N\} based on

```

$$\hat{w}_n = \begin{cases} 0, & \text{if } Z_n \ge 0\\ 1, & \text{otherwise} \end{cases}$$

16: **if**  $\mathbf{H}\hat{\mathbf{w}}^T = 0$  or the maximum iteration number is reached **then**

- 17: Output the hard-decision  $\hat{w}$

- 18: **else**

- 19: k = k + 1

- 20: Go to line 4;

- 21: **end if**

#### Algorithm 3 The BP decoding with the serial-V schedule

- 1: Initialize k = 02: Initialize all  $Z_n^{(-1)} = I_n$

- 3: Initialize all  $P_m = \prod_{n \in \mathcal{N}(m)} \tanh\left(\frac{Z_n^{(-1)}}{2}\right)$

- 4: **for** n = 1 to N,  $\forall m \in \mathcal{M}(n)$  **do**5:  $Z_{nm}^{(k-1)} = Z_{n}^{(k-1)} L_{mn}^{(k-1)}$ 6:  $L_{mn}^{(k)} = 2 \tanh^{-1} \left( P_{m} / \tanh \left( \frac{Z_{nm}^{(k-1)}}{2} \right) \right)$ 7:  $Z_{n}^{(k)} = Z_{n}^{(k-1)} + \sum_{m \in \mathcal{M}(n)} \Delta L_{mn}^{(k)}$ 8:  $Z_{nm}^{(k)} = Z_{n}^{(k)} L_{mn}^{(k)}$ 9:  $P_{m} \leftarrow \tanh \left( \frac{L_{mn}^{(k)}}{2} \right) \cdot \tanh \left( \frac{Z_{nm}^{(k)}}{2} \right)$

- 10: **end for**

- 11: Decide a hard-decision vector  $\hat{\mathbf{w}} = \{\hat{w}_1, \dots, \hat{w}_N\}$  based on

$$\hat{w}_n = \begin{cases} 0, & \text{if } Z_n^{(k)} \ge 0 \\ 1, & \text{otherwise} \end{cases}$$

- 12: **if**  $\mathbf{H}\hat{\mathbf{w}}^T = 0$  or the maximum iteration number is reached **then**

- Output the hard-decision  $\hat{w}$ 13:

- 14: **else**

- 15: k = k + 1

- Go to line 4;

- 17: **end if**

ables in the LLR-BP decoding of LDPC codes, the residual is the absolute value of the difference of LLR values [22]. In particular, the RBP decoding presented in [22] and [23] considers only CTV messages when computing the residuals. Thus, the residual of the message  $L_{mn}$  propagated from the m-th check node to the n-th variable node is expressed as

$$r(L_{mn}) = \left| L_{mn}^{(k+1)} - L_{mn}^{(k)} \right|,$$

(2.11)

where  $L_{mn}^{(k+1)}$  is computed based on the VTC messages,  $Z_{nm}^{(k)}$ 's. As the BP converges, all of the residuals become zero. Therefore, giving the priority of update to the message that has the largest residual can accelerate the decoding convergence [22]. The RBP is formally described in Algorithm 4, where the decoder checks the stopping rule when the number of message updates reaches the number of edges in the bipartite graph of an LDPC code [22, 23].

```

Algorithm 4 The residual BP

```

```

1: Initialize all Z_{nm} = I_n

```

- 2: Initialize all  $L_{mn} = 0$

- 3: Compute all  $r(L_{mn})$

- 4: Find  $m, n = \underset{\substack{\forall m', 1 \leq m' \leq M \\ n' \in \mathbb{N}(m')}}{\arg \max} r(L_{m'n'})$

- 5: Generate and propagate  $L_{mn}$

- 6: Set  $r(L_{mn}) = 0$

- 7: **for** every  $m' \in \mathcal{M}(n) \setminus m$  **do**

- 8: Generate and propagate  $Z_{nm'}$

- 9: **for** every  $n' \in \mathcal{N}(m') \setminus n$  **do**

- 10: Compute  $r(L_{m'n'})$

- 11: end for

- 12: end for

- 13: **if** Stopping rule is not satisfied **then**

- 14: Go to line 4;

- 15: **end if**

#### **Algorithm 5** The BP decoding with the node-wise scheduling

```

1: Initialize all Z_{nm} = I_n

2: Initialize all L_{mn} = 0

3: Compute all r(L_{mn})

4: Find m = \arg \max r(L_{m'n'})

\forall m', 1 \leq m' \leq M

n' \in \mathcal{N}(m')

5: for every n \in \mathcal{N}(m) do

Generate and propagate L_{mn}

Set r(L_{mn}) = 0

7:

for every m' \in \mathcal{M}(n) \setminus m do

8:

Generate and propagate Z_{nm'}

9:

10:

for every n' \in \mathcal{N}(m') \setminus n do

Compute r(L_{m'n'})

11:

end for

12:

end for

13:

14: end for

15: if Stopping rule is not satisfied then

Go to line 4:

17: end if

```

The RBP shows the fastest convergence speed, thus exhibiting substantially better performance than the BP decoding with the flooding or serial schedules when the number of iterations is small. However, the RBP shows worse error performance for a large number of iterations due to the greediness of the RBP [22, 23]. In order to alleviate the negative effects caused by the greediness, Vila Casado *et al.* proposed the NS algorithm that propagates and generates  $L_{mn'}$ ,  $\forall n' \in \mathcal{N}(m)$  such that  $L_{mn}$  has the largest residual  $r^*$  [22, 23]. The NS algorithm is described in Algorithm 5.

The NS not only shows faster convergence speed than the BP with the flooding and serial schedules but also achieves better performance than the RBP and the BP decoding with static schedules when the number of iterations is large. This is because the NS can correct trapping set errors.

#### **Chapter 3**

# Improved Dynamic Scheduling Algorithms for Decoding of LDPC Codes

#### 3.1 Introduction

Since the length of an LDPC code is finite and the number of decoding iterations is limited, practical LDPC codes can hardly achieve the asymptotic performance predicted by density evolution [43]. In order to improve the error performance of LDPC codes, several researchers have studied message passing schedules rather than decoding algorithms themselves [17, 18, 19, 20, 21, 81, 82, 83, 84, 85]. Recently, Vila Casado *et al.* have proposed the informed dynamic scheduling (IDS) that determines the order of message passing based on the differences of messages generated in the previous and current updates, which is different from the static scheduling schemes, such as flooding or layered decoding, that update messages in a predetermined order,

as discussed in Chapter 2 [22, 23].

In particular, in order to improve the error performance of IDS, three mixed scheduling methods were proposed in [23, 24, 25]. The two-staged IDS algorithm [24] combines the residual belief propagation (RBP) and the node-wise scheduling (NS), whereas both the adaptive layered BP (LBP)/NS [23] and the adaptive mixed scheduling [25] are the combination of the LBP and the NS. Note that the LBP is equivalent to the serial-C schedule.

In this Chapter, we propose an improved RBP (iRBP) that accelerates the convergence speed of the RBP and also study a syndrome-based mixed scheduling of the iRBP and the NS. While the mixed scheduling strategies proposed in [23, 24, 25] consist of two stages in which the number of decoding iterations of the first stage is fixed [23] or adaptively determined [23, 24, 25], the proposed mixed scheduling performs either the iRBP or the NS according to the syndrome of the check node that propagates the message.

The rest of this Chapter is organized as follows. Section 3.2 explains the IDS of the BP algorithm and proposes the iRBP. Section 3.3 presents the syndrome-based mixed scheduling of the iRBP and the NS. The complexity analysis and the simulation results are provided in Section 3.4, and concluding remarks are given in Section 3.5.

#### 3.2 Improved Residual Belief Propagation Algorithm

The RBP decoding can be considered a greedy algorithm because it finds and updates the message that has the largest residual at every message update. In the RBP decoding, however, different outgoing check-to-variable (CTV) messages from the same check node can be selected and updated continuously within several message updates. For ease of description, we designate the check node that contains the CTV message with the largest residual as the selected check (SC). The output value of a check node is mainly determined by the minimum magnitude among the input messages to the check node as shown in Eq. (2.7). Thus, if two minimum magnitudes among the input to a check node are close, the outgoing messages from the check node have similar magnitudes. This can be more clearly explained by the min-sum approximation of the BP decoding whose check node operation is given by Eq. (2.8). When the incoming variable-to-check (VTC) messages to the SC satisfy the above condition, the residuals of outgoing messages from the SC can be similar in magnitude, which results in continuous updates of different CTV messages from the same SC within several message updates. As stated in [22] and [23], the RBP tends to give a high priority of update to the message propagated to the less reliable variable node. In particular, for check nodes that had not been updated up to the previous message update, the RBP always propagates the message to the least reliable variable node.<sup>1</sup> Then, due to the continuous update, the variable nodes with relatively higher reliability as well as those with lower ones are renewed.

The iRBP is proposed to avoid updating variable nodes with high reliability, which is implemented by forcing the residuals of the SC to zeros. In other words, assuming that the CTV message  $L_{mn}$  has the largest residual  $r(L_{mn}) = r^*$ , the proposed iRBP sets the residuals of all CTV messages  $r(L_{mn'})$  to zeros as shown in line 19 of Algorithm 6, where  $n' \in \mathcal{N}(m)$ , while the RBP sets the residual of the tar-

<sup>&</sup>lt;sup>1</sup>For the check nodes that had been updated at least once before the current message update, some residuals of the outgoing messages from the check node have been set to zeros unless they are updated by other check nodes. In this case, only the CTV messages having non-zero residuals are the candidates for the current message update.

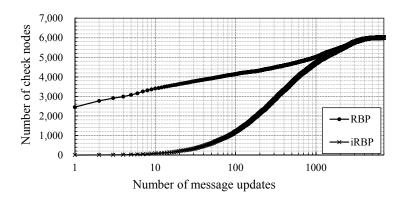

Figure 3.1: Cumulative number of the continuous updates for the rate-1/2 1944-bit LDPC code

get message  $r(L_{mn})$  to zero after the propagation of the message  $L_{mn}$ . The proposed iRBP corresponds to line 18 to 25 of Algorithm 6.

Figure 3.1 illustrates an example of the cumulative number of continuous updates for the rate-1/2 1944-bit LDPC code defined in IEEE 802.11n standard [15]. The x-axis represents the number of message updates between continuous updates of CTV messages from the same SC, and it is plotted in log scale. The simulation was carried out for 6,966 message updates, which corresponds to one decoding iteration. For example, the value of 2,452 at the message update 1 for the RBP decoding represents that 2,452 check nodes are once again chosen as SCs right after their previous message updates, while the value of 2,771 at x = 2 indicates that 2,771 check nodes are selected again after one or two message updates, which includes the value of 2,452 at x = 1. Compared to the RBP decoding, the proposed iRBP shows a very small number of continuous updates within several message updates, which leads to the fastest convergence speed among various decoding schedules as demonstrated in Section 3.4. Note that the extreme case of the continuous update is the NS decoding that updates all CTV messages from an SC, thus resulting in slow decoding conver-

### 3.3 Syndrome-Based Mixed Scheduling of iRBP and NS

When the RBP propagates the message  $L_{mn}$  having  $r^*$  from an unsatisfied check node m to a correct variable node n with low reliability, the sign of the variable node can be flipped because the propagated message tries to correct the variable node, which incurs an additional bit error [22, 23]. To solve this problem, we propose a mixed scheduling strategy that performs either the iRBP or the NS according to the syndrome. The proposed algorithm is different from the two-staged adaptive scheduling strategies that switch from the first to the second stage after a given number of iterations as introduced in [23, 24, 25]. The syndrome  $s_m$  of the m-th check node is defined as the modulo-2 sum of the hard-decision bits of the variable nodes connected to the m-th check node [86]. A check node is said to be satisfied if the syndrome of the check node is zero; otherwise, it is unsatisfied. The proposed mixed scheduling does not require much overhead because it uses the syndromes that are computed for the stopping rule check in the previous iteration rather than those that are generated in each message update. Thus, the mixed scheduling only needs an additional N-bit memory.

The proposed mixed strategy is performed as follows. In the first iteration, the decoder performs the iRBP to improve the convergence of the decoding. In the subsequent iterations, the decoder performs either the iRBP or the NS according to the syndrome. If an SC is unsatisfied, the decoder runs the NS to alleviate the negative effects caused by the greediness of the RBP, thereby improving the error-correcting performance. However, if an SC is satisfied, the decoder performs the iRBP because

### Algorithm 6 Syndrome-based mixed scheduling

```

1: Initialize all k = 0

2: Initialize all Z_{nm} = I_n

3: Initialize all L_{mn} = 0

4: Compute all r(L_{mn})

5: Find m, n = \arg \max r(L_{m'n'})

6: if (k > 0) AND (s_m = 1) then

for every n \in \mathcal{N}(m) do

7:

Generate and propagate L_{mn}

8:

9:

Set r(L_{mn}) = 0

for every m' \in \mathcal{M}(n) \setminus m do

10:

Generate and propagate Z_{nm'}

11:

for every n' \in \mathcal{N}(m') \setminus n do

12:

Compute r(L_{m'n'})

13:

14:

end for

end for

15:

end for

16:

17: else

Generate and propagate L_{mn}

18:

19:

Set r(L_{mn'}) = 0 \ \forall n' \in \mathcal{N}(m)

20:

for every m' \in \mathcal{M}(n) \setminus m do

Generate and propagate Z_{nm'}

21:

for every n'' \in \mathcal{N}(m') \setminus n do

22:

Compute r(L_{m'n''})

23:

end for

24:

end for

25:

26: end if

27: if Stopping rule is not satisfied then

k++

28:

29:

Go to line 4;

30: end if

```

the message propagated from a satisfied check node is less likely to generate a bit error than that from an unsatisfied one. The proposed mixed scheduling is formally described in Algorithm 6.

### 3.4 Complexity Analysis and Simulation Results

### 3.4.1 Complexity Analysis

This subsection analyzes the computational complexity of the proposed iRBP and syndrome-based mixed schedules as well as the conventional static schedules (the flooding the LBP) and two IDS strategies (the RBP and the NS). Let E be the number of edges in the bipartite graph of an LDPC code. Then, the flooding schedule updates E VTC and E CTV messages in every iteration as described in Section 2.3.1. In the LBP schedule, an iteration consists of E CTV and E CTV messages. Therefore, the LBP schedule also updates E VTC and E CTV messages in every iteration.

In IDS schedules, an iteration is defined as E CTV message updates [22, 23]. Therefore, the stopping rule is checked when the number of CTV message updates reaches the number of edges in the graph, E. In the RBP decoding, a CTV message and  $d_v - 1$  VTC messages are generated and propagated in each *message update*, where  $(d_v - 1)(d_c - 1)$  residuals are also computed. Therefore, the RBP decoding updates  $E(d_v - 1)$  VTC and E CTV messages and computes  $E(d_v - 1)(d_c - 1)$  residuals in every iteration.

The NS decoding generates and propagates  $d_c$  CTV and  $d_c(d_v-1)$  VTC messages and computes  $d_c(d_v-1)(d_c-1)$  residuals in each message update. Thus, an iteration consists of  $E/d_c=M$  message updates in the NS decoding. Consequently, the NS

decoding updates  $M \cdot d_c(d_v - 1) = E(d_v - 1)$  VTC and  $M \cdot d_c = E$  CTV messages and computes  $M \cdot d_c(d_v - 1)(d_c - 1) = E(d_v - 1)(d_c - 1)$  residuals, which is the same to that of the RBP decoding.

In the RBP and NS schedules, the residuals of the propagated CTV messages from an SC are set to zeros. Hence, both schedules require E set-to-zero operations, i.e.,  $r(\cdot)=0$  operation. When compared to the RBP decoding, the proposed iRBP needs  $d_c$  set-to-zero operations in each message update, thus resulting in  $E \cdot d_c$  set-to-zero operations per iteration. Note that the number of message updates and that of residual computations are the same to those of the RBP decoding.

Because the proposed mixed scheduling is based on the syndrome of an SC, the number of set-to-zero operations as well as that of the message updates depends on the ratio of satisfied, or unsatisfied, check nodes. Denoting the ratio of satisfied check nodes in each iteration as  $\rho_l$ , the mixed scheduling performs  $\rho_l$  iRBP and  $1-\rho_l$  NS decoding operations. Hence, the number of residual computations as well as that of message updates is the same to that of the iRBP or NS decoding, while the number of set-to-zero operations is computed as  $(\rho_l(d_c-1)+1)E$ , which is the sum of  $\rho_l \cdot E \cdot d_c$ , for the iRBP, and  $(1-\rho_l)E$ , for the NS. Note that the number of set-to-zero operations for the mixed scheduling is smaller than or equal to that for the iRBP because  $\rho_l \leq 1$ .

The complexities of the above schedules are summarized in Table 3.1.

#### **3.4.2** Simulation Results

In this subsection, we present the performance of the proposed iRBP and the syndromebased mixed scheduling over the AWGN channel. The floating-point BP algorithm was employed, and the frame error rate (FER) performance was measured until at

Table 3.1: Computational complexity of schedules

| Schedules | VTC updates | CTV updates | Residual computations | $r(\cdot) = 0$ operations |

|-----------|-------------|-------------|-----------------------|---------------------------|

| Flooding  | E           | E           | =                     | -                         |

| LBP       | E           | E           | -                     | -                         |

| RBP       | $E(d_v-1)$  | E           | $E(d_v-1)(d_c-1)$     | E                         |

| NS        | $E(d_v-1)$  | E           | $E(d_v-1)(d_c-1)$     | E                         |

| iRBP      | $E(d_v-1)$  | E           | $E(d_v-1)(d_c-1)$     | $E \cdot d_c$             |

| Mixed     | $E(d_v-1)$  | E           | $E(d_v-1)(d_c-1)$     | $(\rho_l(d_c-1)+1)E$      |

least 100 frame errors were observed. The decoder checks the stopping rule when the number of message updates reaches the number of edges in the bipartite graph of an LDPC code [22, 23].

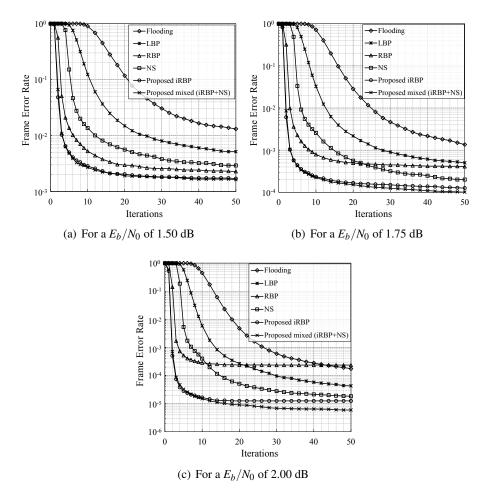

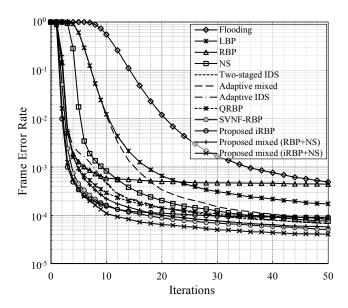

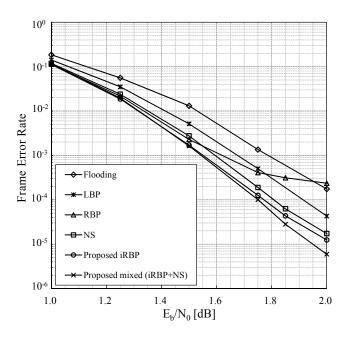

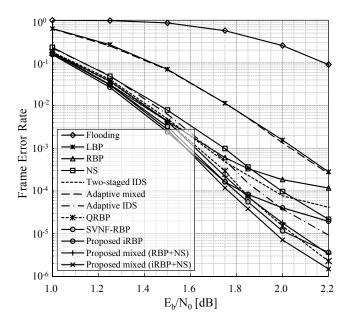

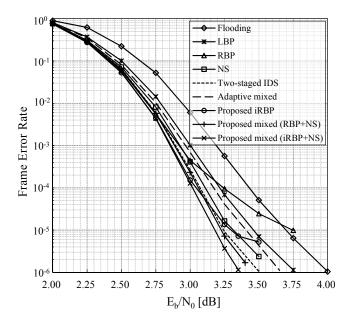

Figures 3.2, 3.3, and 3.4 show the FER performance of the rate-1/3 1920-bit [87], the rate-1/2 1944-bit [15], and the rate-3/4 1944-bit LDPC codes [15], respectively, with the flooding, the LBP, the RBP, the NS, the two-staged IDS [24], the adaptive mixed scheduling [25], the proposed iRBP, and the syndrome-based mixed schedule. The FER performance of the adaptive IDS [26], the quota-based RBP (QRBP) [80], and the silent-variable-node-free RBP (SVNF-RBP) [80] are also plotted in Fig. 3.3. The signal to noise ratios (SNRs) were set to  $E_b/N_0 = 1.75 \, \mathrm{dB}$  for Fig. 3.3 and  $E_b/N_0 = 3.10 \, \mathrm{dB}$  for Fig. 3.4. In order to validate the proposed syndrome-based mixed strategy, we also consider the mixed scheduling of the RBP and the NS as well as that of the iRBP and the NS in Fig. 3.3 and Fig. 3.4.

The proposed iRBP exhibits the fastest convergence speed among all of the scheduling schemes and converges about two times faster than the RBP decoding. Moreover, the proposed iRBP performs consistently better than the RBP decoding in terms of FER. This is because avoiding the continuous update not only improves the convergence speed at the early stage of decoding but also removes trapping sets and thereby

Figure 3.2: FER performance of the rate-1/3 1920-bit LDPC code

improves the error performance.

Furthermore, the proposed syndrome-based mixed scheduling of the iRBP and the NS outperforms all other scheduling schemes because the proposed method exploits not only the iRBP for fast convergence but also the iRBP and the NS for removing trapping sets. The performance gap between the proposed syndrome-based mixed scheduling and other schedules is more pronounced at high SNR as shown in

Figure 3.3: FER performance of the rate-1/2 1944-bit LDPC code for a  $E_b/N_0$  of 1.75 dB

Fig. 3.2. We note that the proposed syndrome-based mixed scheduling also performs well when combined with the RBP, especially when compared with the two-staged IDS studied in [24], which is also a mixed strategy of the RBP and the NS.

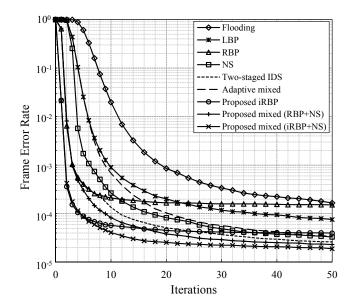

Figures 3.5, 3.6, and 3.7 show the FER performance of the rate-1/3 1920-bit, the rate-1/2 1944-bit, and the rate-3/4 1944-bit LDPC codes, respectively, where the maximum iterations are set to 50 for Fig. 3.5, 10 for Fig. 3.6, and 15 for Fig. 3.7. The rate-1/2 1944-bit LDPC code was also simulated with the maximum iteration of 50 as shown in Fig. 3.8. From these figures we can find that the proposed syndrome-based mixed scheduling of the iRBP and the NS shows the best error performance when compared with the other scheduling schemes. In particular, the proposed mixed strategy suffers less from the error floor behavior.

Figure 3.4: FER performance of the rate-3/4 1944-bit LDPC code, where  $E_b/N_0$  is fixed to 3.10 dB

### 3.5 Concluding Remarks

In this chapter, we propose an improved residual belief propagation (iRBP) and a syndrome-based mixed scheduling scheme combining the iRBP and the node-wise scheduling (NS). The proposed iRBP forces the residuals of a *selected check* (SC) to zeros, which prevents updating reliable variable nodes and thus improves the convergence speed of the RBP by approximately two times. The proposed mixed scheduling performs either the iRBP or the NS based on the syndrome of the SC. Simulation results show that the proposed mixed-scheduling yields significant performance improvement when compared to all other scheduling schemes.

Figure 3.5: FER performance of the rate-1/3 1920-bit LDPC code with the maximum iteration number of  $50\,$

Figure 3.6: FER performance of the rate-1/2 1944-bit LDPC code for the maximum iteration number of  $10\,$

Figure 3.7: FER performance of the rate-3/4 1944-bit LDPC code over AWGN channel, where the maximum iteration number is set to 15

Figure 3.8: FER performance of the rate-1/2 1944-bit LDPC code for the maximum iteration number of 50

### **Chapter 4**

## A Pipelined Parallel Architecture for Decoding of Finite-Geometry LDPC Codes

### 4.1 Introduction

High-throughput LDPC decoders for NAND flash memory controllers need to be implemented in hardware. As hardware implementation of LDPC decoders is directly affected by decoding and scheduling algorithms as well as hardware architectures, low-complexity algorithms with fast convergence speed and their hardware implementation have been extensively studied in the literature [27, 29, 30, 31, 35, 88]. The early studies for the hardware implementation featured fully parallel LDPC decoders with the belief propagation (BP) algorithm [27, 28]. However, since fully parallel decoders demand very complex interconnection networks, most high-throughput LDPC decoders usually employ partially parallel architectures with the min-sum (MS) al-

gorithm or its variants and a serial scheduling algorithm [29, 30, 31, 88] to lower the interconnection complexity and increase the decoding throughput. Although the performance of LDPC codes converges to the thresholds predicted by the density evolution (DE) [43] as the code length increases, only little work has been devoted to the implementation of LDPC decoders with a large code length [37, 38, 39].

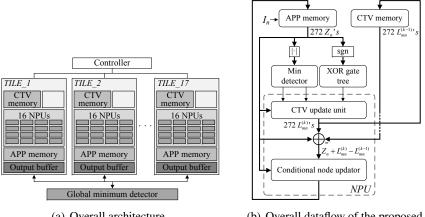

In this chapter, a pipelined parallel architecture with the serial-C schedule is proposed for finite geometry (FG) LDPC codes. The decoding hardware employs the normalized *a posteriori* probability (APP) based algorithm that not only shows good error-correcting performance for FG-LDPC codes but also simplifies both the variable and check node operations. A conditional variable node update scheme is proposed to make the normalized APP-based algorithm resilient to decoding failure as well as to reduce circuit switching activities in the node processing units. In order to increase the decoding throughput while minimizing the chip area, the decoder adopts pipelined parallel architecture and employs three memory size reduction techniques, which are optimizing the word-length of extrinsic information, compressing the extrinsic information, and approximating the second minimum magnitudes. The implementation results are given for a (69615, 66897) Euclidean geometry (EG) LDPC code.

The remainder of this chapter is organized as follows. Section 4.2 introduces the property of FG-LDPC codes and the proposed serial schedule of normalized APP-based algorithm with conditional node update. In Section 4.3, the decoder architecture and optimization strategies are presented. The implementation results are provided in Section 4.4. Section 4.5 concludes this chapter.

# **4.2** Finite-Geometry LDPC Codes and Conditional Variable Node Update Algorithm

### **4.2.1** Finite-Geometry LDPC codes

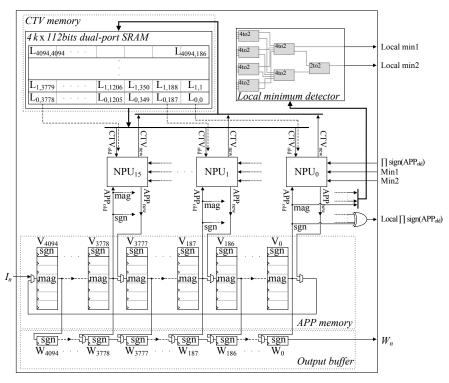

FG-LDPC codes are constructed based on Euclidean and projective geometries over finite fields. FG-LDPC codes have large minimum distances and perform well with iterative decoding algorithms [86]. They show fast convergence speed [86] and have no harmful trapping sets with the size smaller than their minimum weights, thus resulting in good error-floor performance [89]. It is reported that (1024, 781) EG-LDPC code has the error-floor below the bit error rate (BER) of  $10^{-23}$  [90]. Moreover, the parity-check matrices of FG-LDPC codes contain redundant rows that give additional improvement in error performance [86, 72]. FG-LDPC codes have either cyclic or quasi-cyclic (QC) structure for their parity-check matrices, which allows efficient encoder implementation. The encoder can be implemented with linear feedback shift registers. However, since the row and column weights,  $d_c$  and  $d_v$ , respectively, are quite large when compared to other classes of LDPC codes, it is very challenging to implement a high-throughput FG-LDPC decoder.

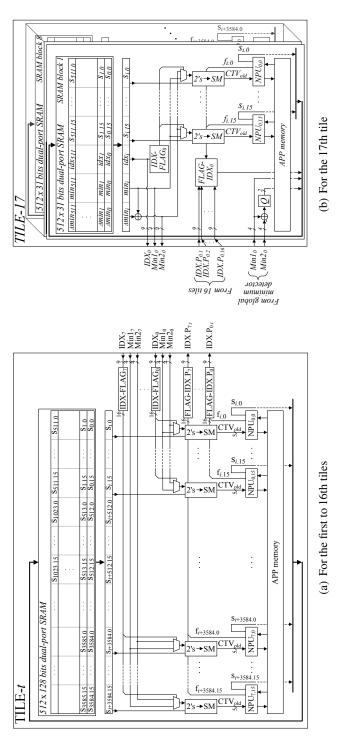

Figure 4.1 shows the parity-check matrices of a rate-0.77 (1057, 813) projective geometry (PG) LDPC code and a rate-0.96 (69615, 66897) EG-LDPC code. The (1057, 813) PG-LDPC code has the cyclic parity-check matrix with  $d_v = d_c =$  33. The parity-check matrix of the (69615, 66897) EG-LDPC code consists of 17 sub-matrices, and each sub-matrix is a cyclically right-shifted 4,095 × 4,095 matrix with the row and column weights of 16. As a result, the parity-check matrix has a 4,095 × 69,615 structure with the row weight  $d_c$  of 272 and the column weight  $d_v$  of

(b) A rate-0.96 (69615, 66897) EG-LDPC code

Figure 4.1: Parity-check matrices

16.

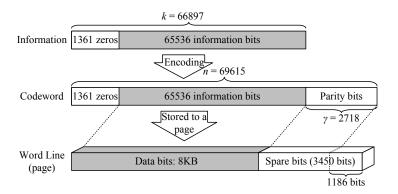

A shortened EG-LDPC code is considered for the application to NAND flash memory as follows. Since the number of information bits contained in the (69615, 66897) EG-LDPC code is different from the page size of NAND flash memory devices, which is typically 8 kbytes, the (68254, 65536) shortened EG-LDPC code is constructed by removing 1,361 (= 66,897 - 65,536) data bits from the original EG-LDPC code as shown in Fig. 4.2, where the parameter  $\gamma$  represents the number of parity bits of the EG-LDPC code. In this work, we assume that a flash memory page consists of 8 kbytes of user data and 3,450 bits (5 %) of spare data. Among the spare bits, 2,718 bits are used for error correction and the remaining 732 bits are reserved for other purposes such as cell-to-cell interference (CCI) cancellation and the operation of flash translation layer. Implementing this shortening process is straightforward both for encoding and decoding. At the encoding process, 1,361 zeros are inserted in the information part of the (69615, 66897) EG-LDPC code. At the decoding process, this zero-filled bit positions are regarded to have zero received values with a large

Figure 4.2: Codeword structure of the (68254, 65536) shortened EG-LDPC code and its mapping method

reliability.

## 4.2.2 Conditional Variable Node Update Algorithm for Fixed-Point Normalized APP-Based Algorithm

Hardware-based implementation of FG-LDPC codes is considered very difficult because of their large row and column weights that demand a complex interconnection network. Also, when the code length is very large as shown in Fig. 4.1(b), a large memory size is required for the implementation. Thus, it is very needed to lower the implementation complexity of the codes, especially for high-throughput decoding with parallel architecture. For a reduced complexity implementation, the normalized APP-based algorithm [61], which performs well with FG-LDPC codes [72], is employed. This algorithm simplifies the variable node operations by substituting the extrinsic messages from a variable node with the *a posteriori* log-likelihood ratio (LLR) of the corresponding variable node [61].

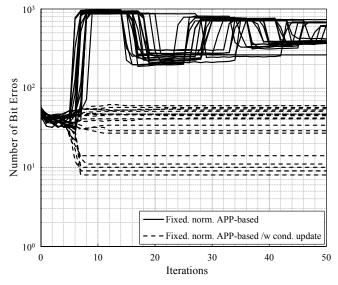

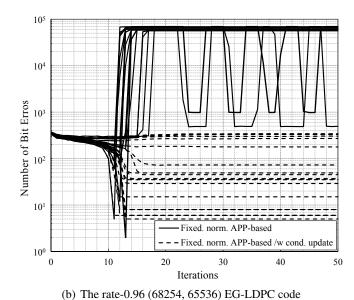

The normalized APP-based algorithm, however, causes a large number of bit errors for undecodable blocks. Figure 4.3 shows the number of bit errors of the (1057,

(a) The rate-0.77 (1057, 813) PG-LDPC code

Figure 4.3: Number of bit errors of the two LDPC codes with the normalized APP-based algorithm for 20 undecodable blocks

813) PG-LDPC code and the (68254, 65536) EG-LDPC code for 20 undecodable blocks, where  $E_b/N_0$  is set to 3.5 dB and 5.5 dB, respectively. As shown in Fig. 4.3, the APP-based decoding reduces the number of bit errors at the early stage but, rather, increases it as the iteration proceeds. This is caused by the correlation among propagated messages, which continues to increase the reliabilities (magnitudes) of uncorrected variable nodes and saturates some of them. The unstopped reliability increase of the uncorrected variable nodes also affects the correct ones and eventually leads to a large number of bit errors after several iterations. In order to solve this problem, we develop a conditional variable node update algorithm for the fixed-point normalized APP-based decoding. The proposed conditional node update algorithm finishes updating a variable node as soon as the reliability of the corresponding a posteriori LLR reaches the maximum fixed-point value. As a result, the proposed algorithm can prevent the reliability decrease of correct variable nodes that is caused by unstopped reliability increase of uncorrected variable nodes. Figure 4.3 shows the number of bit errors as the iteration proceeds for several decoding failed blocks, and it illustrates the effect of the conditional update.

Along with the reduced complexity decoding algorithm, the serial-C schedule that can halve the number of decoding iterations when compared to the conventional flooding schedule is applied to achieve a high throughput [17]. As discussed in Section 2.3, the serial schedule converges almost twice faster than the conventional flooding schedule.

The algorithm operates as follows. Consider a regular (N, K) LDPC code defined by an  $M \times N$  parity-check matrix H with the row weight  $d_c$  and the column weight  $d_v$ . Let  $\alpha$  be a normalization factor. Then, the serial schedule of the normalized APP-based algorithm with conditional node update is described in Algorithm 7.

### Algorithm 7 Serial schedule of normalized APP-based algorithm with conditional node update

- 1: Initialize k = 02: Initialize all  $L_{mn}^{(-1)} = 0$

- 3: Initialize all  $Z_n = I_n$

- 4: **for** m = 1 to M **do**

- **for** every  $n \in \mathcal{N}(m)$  **do**

6:

$$L_{mn}^{(k)} = \prod_{n' \in \mathcal{N}(m) \setminus n} \operatorname{sign}(Z_{n'}) \cdot \min_{n' \in \mathcal{N}(m) \setminus n} |Z_{n'}| \cdot \alpha \tag{4.1}$$

- end for 7:

- **for** every  $n \in \mathcal{N}(m)$  **do** 8:

$$Z_n = \begin{cases} Z_n, & \text{if } |Z_n| = 2^{q-1} - 1\\ Z_n + L_{mn}^{(k)} - L_{mn}^{(k-1)}, & \text{otherwise} \end{cases}$$

(4.2)

- end for 10:

- 11: **end for**

- 12: Decide a hard-decision vector  $\hat{\mathbf{w}} = \{\hat{w}_1, \dots, \hat{w}_N\}$  based on

$$\hat{w}_n = \begin{cases} 0, & \text{if } Z_n^{(k)} \ge 0\\ 1, & \text{otherwise} \end{cases}$$

- 13: **if**  $H\hat{\mathbf{w}}^T = 0$  or the maximum iteration number is reached **then**

- Output the hard-decision  $\hat{w}$ 14:

- 15: **else**

- 16: k = k + 1

- 17: Go to line 4;

- 18: **end if**

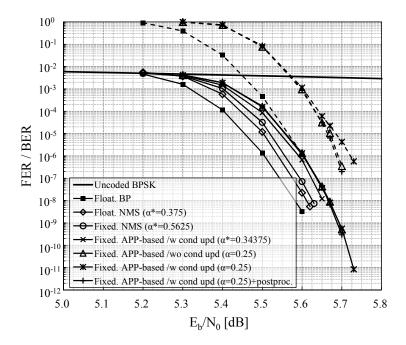

Figure 4.4: (Dashed line) Frame- and (solid line) bit-error performance of the (68254, 65536) shortened EG-LDPC code with the serial-C schedule

Figure 4.4 shows the error performance of the (68254, 65536) shortened EG-LDPC code with various decoding algorithms over the additive white Gaussian noise (AWGN) channel, which include floating-point BP, floating-point normalized MS (NMS), fixed-point NMS, and fixed-point normalized APP-based algorithm with and without conditional node update. The serial-C schedule is employed, and the maximum iteration number is set to eight. The normalization factors of the floating-point NMS, fixed-point NMS, and fixed-point APP-based algorithms are set to 0.375, 0.5625, and 0.34375, respectively, which yield the best error performance. The performances of the fixed-point normalized APP-based algorithms with the normalization factor of 0.25, which leads to simple hardware, are also shown. All of the fixed-point simulations employ the word-length, q, of seven, which includes one bit for

the sign, four bits for the integer, and two bits for the fractional part [91]. The BP algorithm shows the best error-correcting performance, and the gap between the BP and the floating-point NMS algorithms is about  $0.033 \, dB$  at the BER of  $10^{-7}$ . However, because of the quantization noise, the fixed-point NMS decoding shows slight performance degradation of 0.052 dB compared to the BP algorithm. The fixed-point normalized APP-based algorithms with and without conditional node update show good error performance that is close to the NMS decoding, when the normalization factors of 0.34375 or 0.25 are used. Note that the error performance degradation due to the conditional node update in the normalized APP algorithm is less than 0.01 dB at the frame error rate (FER) of  $10^{-4}$ . This is because the variable node cannot be corrected under the conditional node update scheme when an incorrect variable node is saturated to the maximum fixed-point value,  $\pm 2^{q-1} - 1$ . However, in high signal-tonoise ratio (SNR) region, only a small number of variable nodes remain unchanged and the FER increase is very minor. When the SNR is 5.7 dB, 92 % of erroneous frames contain only one uncorrected bit error in each frame. Thus, if needed, we can remove these remaining bit errors by applying the LDPC decoding without the conditional node update again on the decoded data output (consult the "+" marked curves in Fig. 4.4, where one decoding iteration without the conditional node update is applied after finishing seven decoding iterations with the conditional update).

The proposed conditional variable node update algorithm can be compared with the reduced computational complexity algorithms proposed in [92] and [93]. Both papers have proposed similar algorithms that stop updating reliable variable nodes using a pre-defined [92] or a dynamic thresholds [93]. Although their complexity reduction was reported to be up to 60 % and 35 % in [92] and [93], respectively, some error performance degradation was observed due to erroneously identified variable

nodes. Furthermore, these algorithms require extensive simulations to determine the optimum threshold, and their error performance and computational complexity reduction are very sensitive to the threshold. In contrast to those methods, the proposed conditional node update does not require a precise threshold, and the error performance degradation is almost negligible.

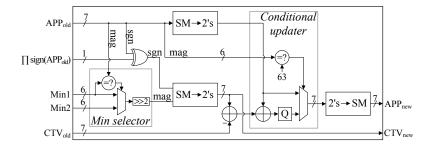

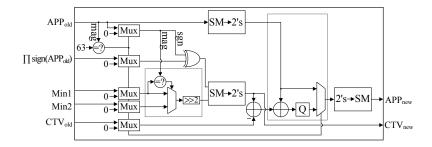

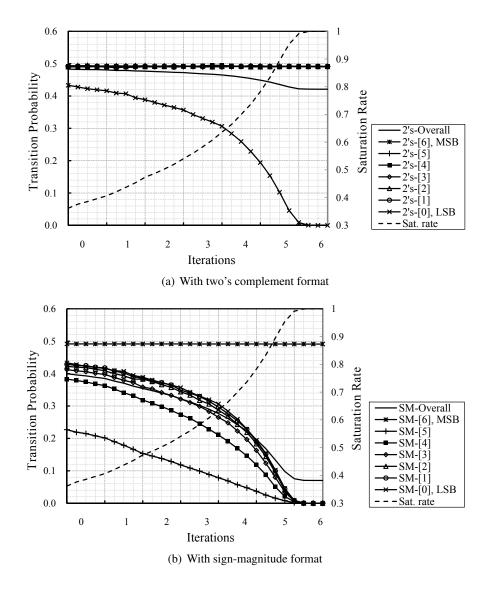

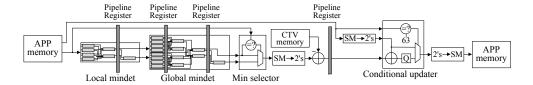

### 4.3 Decoder Architecture