#### 저작자표시-비영리-동일조건변경허락 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

- 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

- 이차적 저작물을 작성할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

동일조건변경허락. 귀하가 이 저작물을 개작, 변형 또는 가공했을 경우 에는, 이 저작물과 동일한 이용허락조건하에서만 배포할 수 있습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

Disclaimer

### Ph.D. DISSERTATION

# Efficient Predication Techniques on Coarse-Grained Reconfigurable Architectures

재구성형 구조에서의 효율적인 조건실행 기법

BY

Kyuseung Han

AUGUST 2013

DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

### Ph.D. DISSERTATION

# Efficient Predication Techniques on Coarse-Grained Reconfigurable Architectures

재구성형 구조에서의 효율적인 조건실행 기법

BY

Kyuseung Han

AUGUST 2013

DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

# Efficient Predication Techniques on Coarse-Grained Reconfigurable Architectures

재구성형 구조에서의 효율적인 조건실행 기법

지도교수 최 기 영 이 논문을 공학박사 학위논문으로 제출함 2013 년 5 월

> 서울대학교 대학원 전기 컴퓨터 공학부 한 규 승

한규승의 공학박사 학위논문을 인준함 2013 년 6 월

| 위 원 장                 | 채 수 익 |

|-----------------------|-------|

| 부위원장                  | 최 기 영 |

| 위 원                   | 백 윤 흥 |

| 위<br>위<br>원<br>위<br>위 | 이 종 은 |

| 위 원                   | 김 윤 진 |

## Abstract

Coarse-Grained Reconfigurable Architecture (CGRA) is one of viable solutions in embedded systems to accelerate data-intensive applications. It typically consists of an array of processing elements (PEs) and a centralized controller, which can provide high performance, flexibility, and low power. Parallel array processing reduces execution time of applications, reconfigurability of PEs allows changing its functionality, and simplified control structure with static scheduling for instruction fetching and data communication minimizes power consumption.

However, as applications become complex so that data-intensive parts are having control flows in them, CGRAs face a challenge for its effectiveness. Since the entire PEs are controlled by a centralized unit, it is impossible to execute programs having control divergence among PEs. To overcome the problem, we can adopt the technique called predicated execution, which is the unique solution known so far, but conventional predication techniques have a negative impact on both performance and power consumption due to longer instruction words and unnecessary instruction-fetching/decoding/nullifying steps.

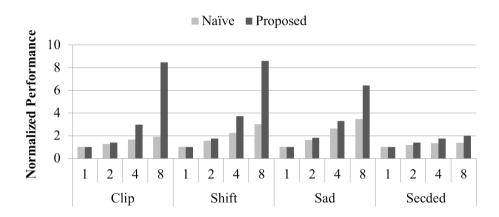

Thus, this thesis reveals performance and power issues in predicated execution when a CGRA executes both data- and control-intensive applications, which have not been well-addressed yet. Then it proposes high-performance and low-power predication mechanisms. Experiments conducted through gate-level simulation show that the proposed mechanism improves energy-delay product by 11.9%, 14.7%, and 23.8% compared to three conventional techniques. In addition, this thesis also reveals mapping issues when mapping applications

on CGRAs using the proposed predication. A power-saving mode introduced

into PEs prohibits multiple conditionals from being parallelized if conventional

mapping algorithms are used. Thus, this thesis proposes the framework to re-

lease this problem by mapping conditionals to different PEs. Experiments show

that mapping results from the proposed approach lead to 2.21 times higher

performance than those of the naïve approach.

$\textbf{Keywords} : \operatorname{CGRA}, \operatorname{reconfigurable}, \operatorname{predication}, \operatorname{predicated} \operatorname{execution}, \operatorname{low} \operatorname{power},$

high performance

Student Number: 2008-21002

ii

# Contents

| Abstra | ct     |                                              | i         |

|--------|--------|----------------------------------------------|-----------|

| Chapte | er 1 I | ntroduction                                  | 1         |

| Chapte | er 2 E | Background and Related Work                  | 5         |

| 2.1    | Coarse | e-Grained Reconfigurable Architecture        | 5         |

|        | 2.1.1  | Introduction                                 | 5         |

|        | 2.1.2  | Target Domain                                | 6         |

|        | 2.1.3  | Comparison with Other Architectures          | 6         |

|        | 2.1.4  | Application Mapping                          | 8         |

|        | 2.1.5  | Target CGRA                                  | 8         |

| 2.2    | Predic | cated Execution Technique                    | 11        |

|        | 2.2.1  | Introduction                                 | 11        |

|        | 2.2.2  | Classification                               | 12        |

|        | 2.2.3  | Different Roles in ILP and DLP processors    | 13        |

|        | 2.2.4  | Predication Support on CGRAs                 | 14        |

| Chapte | er 3 ( | Conventional Predicated Execution Techniques | <b>15</b> |

| 3.1    | Partia | l Predication (Partial)                      | 16        |

| 3.2    | Condi  | ition-Based Full Predication (CONDFULL)                                                                | 18 |

|--------|--------|--------------------------------------------------------------------------------------------------------|----|

| Chapte | er 4 S | State-Based Full Predication                                                                           | 23 |

| 4.1    | Previo | ous Approach (PseudoBranch)                                                                            | 24 |

| 4.2    | Count  | ter-Based Approach (STATEFULL)                                                                         | 25 |

| 4.3    | Dual-  | Issue-Single-Execution (DISE)                                                                          | 28 |

| 4.4    | Hybri  | d Predication                                                                                          | 32 |

|        | 4.4.1  | Motivation                                                                                             | 32 |

|        | 4.4.2  | StateFull+Partial                                                                                      | 34 |

|        | 4.4.3  | STATEFULL+PARTIAL+DISE                                                                                 | 35 |

| Chapte | er 5 l | Evaluation                                                                                             | 39 |

| 5.1    | Imple  | mentation                                                                                              | 39 |

|        | 5.1.1  | Conventional Techniques                                                                                | 39 |

|        | 5.1.2  | Proposed Techniques                                                                                    | 40 |

| 5.2    | Exper  | rimental Setup                                                                                         | 43 |

| 5.3    | Exper  | rimental Results                                                                                       | 46 |

|        | 5.3.1  | Effect of Predication Mechanism on Power Consumption                                                   |    |

|        |        | of a PE                                                                                                | 47 |

|        | 5.3.2  | Quantitative Definitions of $\mathit{short}\text{-}\mathit{if}$ and $\mathit{long}\text{-}\mathit{if}$ | 48 |

|        | 5.3.3  | Compilation Strategy in StateFull+Partial                                                              | 48 |

|        | 5.3.4  | Conventional Techniques (PARTIAL, CONDFULL, and PSEU-                                                  |    |

|        |        | DOBRANCH) vs. Proposed StateFull Technique                                                             | 49 |

|        | 5.3.5  | Proposed Hybrid Predication Techniques                                                                 | 53 |

|        | 5.3.6  | Putting Together                                                                                       | 54 |

|        | 5.3.7  | Speedup of Applications                                                                                | 57 |

| Chapte | er 6 I | Mapping Framework                                                                                      | 61 |

| 6.1    | Motivation     |                                   |    |  |

|--------|----------------|-----------------------------------|----|--|

| 6.2    | Propo          | sed Approach                      | 63 |  |

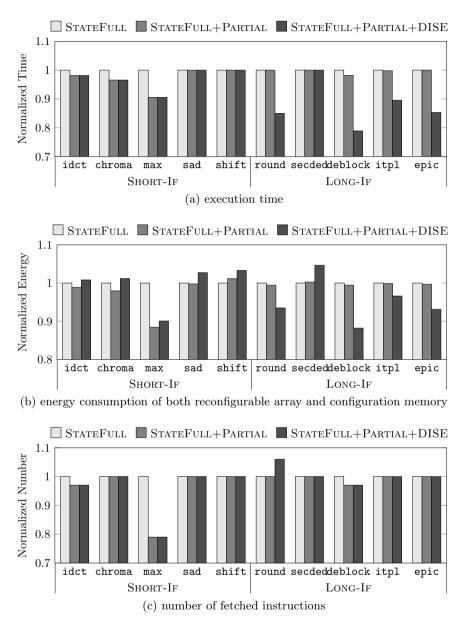

|        | 6.2.1          | Overall Flow                      | 63 |  |

|        | 6.2.2          | From IR to CDFG                   | 64 |  |

|        | 6.2.3          | Separation                        | 65 |  |

|        | 6.2.4          | CDFG Mapping                      | 68 |  |

| 6.3    | Imple          | mentation                         | 69 |  |

| 6.4    | Exper          | iments                            | 69 |  |

|        | 6.4.1          | Experimental Setup                | 69 |  |

|        | 6.4.2          | Verification of Mapping Framework | 70 |  |

|        | 6.4.3          | Quality of Mapping Results        | 70 |  |

| Chapte | er 7 (         | Conclusion                        | 73 |  |

| 7.1    | Summ           | nary                              | 73 |  |

| 7.2    | Applie         | cable Scope and Future Work       | 75 |  |

| Appen  | $\mathbf{dix}$ |                                   | 77 |  |

| 국문초-   | 록              |                                   | 93 |  |

| 감사의    | 글              |                                   | 95 |  |

# List of Figures

| Figure 1.1 | Application profiling results                               | 2  |

|------------|-------------------------------------------------------------|----|

| Figure 2.1 | The target architecture FloRA                               | 10 |

| Figure 2.2 | Architecture for loop pipelining technique for FloRA        | 11 |

| Figure 3.1 | An example C code and its branch equivalent                 | 16 |

| Figure 3.2 | Partial predication (PARTIAL)                               | 17 |

| Figure 3.3 | Condition-based full predication (CONDFULL)                 | 19 |

| Figure 3.4 | An example program that naïve conversion to COND-           |    |

|            | Full produces incorrect assembly code due to its $nested$ - |    |

|            | if structure                                                | 20 |

| Figure 4.1 | Instruction-based wake-up for state-based full predica-     |    |

|            | tion (PseudoBranch)                                         | 24 |

| Figure 4.2 | Counter-based wake-up for state-based full predication      |    |

|            | (StateFull)                                                 | 26 |

| Figure 4.3 | The concept of the DISE technique                           | 28 |

| Figure 4.4 | Dual-Issue-Single-Execution (DISE)                          | 30 |

| Figure 4.5 | Additional nop instructions inserted for DISE to balance       |    |

|------------|----------------------------------------------------------------|----|

|            | the lengths of if- and else-paths                              | 32 |

| Figure 4.6 | An example program that PARTIAL executes with better           |    |

|            | performance than StateFull                                     | 34 |

| Figure 4.7 | A solution to eliminate the need for nop instructions          | 36 |

| Figure 4.8 | Applying DISE and STATEFULL together into $\textit{nested-if}$ |    |

|            | structures for better performance                              | 38 |

| Figure 5.1 | Modification of architecture to support DISE                   | 41 |

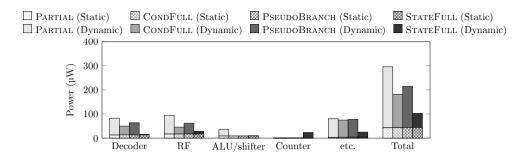

| Figure 5.2 | Power consumption of a PE on an unnecessary path.              |    |

|            | Here $etc.$ includes power consumption of state registers      |    |

|            | and wires                                                      | 48 |

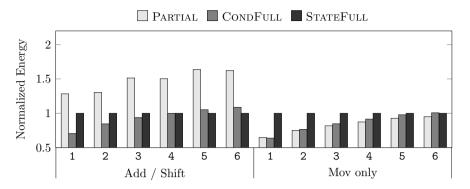

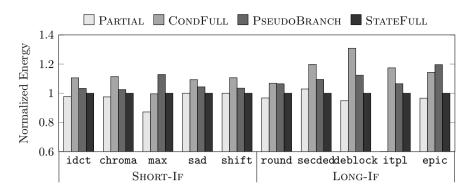

| Figure 5.3 | Energy normalized to that of StateFull                         | 49 |

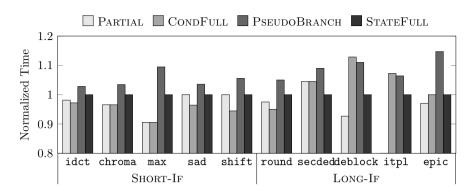

| Figure 5.4 | Execution time normalized to that of StateFull                 | 50 |

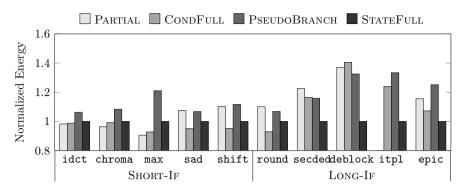

| Figure 5.5 | Energy consumption of reconfigurable array normalized          |    |

|            | to that of StateFull                                           | 51 |

| Figure 5.6 | Energy consumption of configuration memory normal-             |    |

|            | ized to that of StateFull                                      | 52 |

| Figure 5.7 | Number of fetched instructions normalized to that of           |    |

|            | STATEFULL                                                      | 52 |

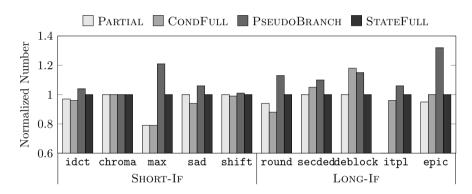

| Figure 5.8 | Comparison among StateFull and hybrid approaches.              | 55 |

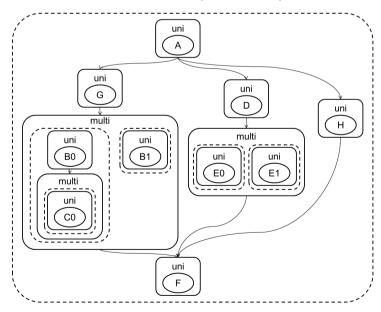

| Figure 6.1 | The mapping framework on StateFull-based CGRAs                 | 63 |

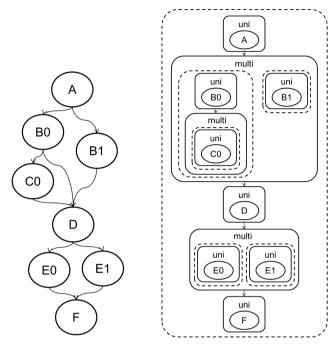

| Figure 6.2 | Conversion process from IR to CDFG                             | 66 |

| Figure 6.3 | Comparison of mapping results on performance                   | 71 |

# List of Tables

| Table 4.1 | Characteristics of Predicated Execution Techniques | 33 |

|-----------|----------------------------------------------------|----|

| Table 5.1 | The Detailed Information of the Applications       | 46 |

| Table 5.2 | Improvements of StateFull+Partial                  | 56 |

| Table 5.3 | Improvements of StateFull+Partial+DISE             | 57 |

| Table 5.4 | Execution time of JPEG decoder (cycle)             | 58 |

| Table 5.5 | Execution time of H.264 decoder (cycle)            | 59 |

## Chapter 1

## Introduction

A Coarse-Grained Reconfigurable Architecture (CGRA) is an array of Processing Elements (PEs) which can be reconfigured to perform word-level operations. It is a viable solution for embedded systems since it can meet performance, flexibility, and low power consumption at the same time. Parallel execution on abundant PEs reduces the execution time of applications, and reconfigurability of PEs enables to change its functionality according to applications. To simplify the control of PEs, the schedule of configuration (or instruction) fetching and data communication are statically decided at compile time and the single controller orchestrates all. This feature makes CGRAs have the scalability on the number of PEs despite of the use of a single controller and also gives the efficiency on power consumption. Due to these benefits, there have been many researches proposing various kinds of CGRAs [1–10] and surveys on them [11,12].

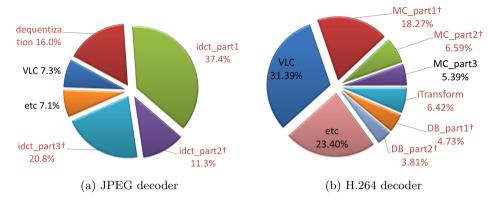

Figure 1.1: Application profiling results.

However, CGRAs face a challenge for its effectiveness as applications become complex so that data-intensive parts are having control flows in them. Figure 1.1 shows profiling results when two representative multimedia applications are running on a single ARM 9 processor<sup>1</sup>. Pieces with red labels are data-intensive parts and the dagger symbol ( $\dagger$ ) indicates that the corresponding part has if structures. We can observe from the figure that lots of data-intensive parts consuming big portions of the total execution time have control flows in them.

Although accelerating both data- and control- ntensive parts is becoming an important issue, conventional CGRAs are not suitable to handle them. Since they have a single controller for the simplified control structure, it is impossible to execute programs having control divergence among PEs. The only way to overcome this architectural limitation is known as the technique called predicated execution [14]. However, conventional predications can threaten the competitiveness of CGRAs since it causes serious overhead in both performance and power consumption.

<sup>&</sup>lt;sup>1</sup>We measured the execution time using ARM Developer Suite 1.2 [13].

Thus, in this thesis, we reveal performance and power issues of predicated execution and propose a novel mechanism to overcome drawbacks of the conventional techniques. The main contributions of the thesis include the following.

- We investigate power consumption related with predicated execution techniques for the first time not only in the domain of CGRAs, but in all domains related to predicated execution. Most of the previous research on predicated execution has concentrated only on performance improvement and design automation through architecture-level [15, 16] and/or compiler-level [17, 18] modifications, but no one has considered power consumption.

- We propose a low-power predication mechanism to mitigate power consumption overhead of predicated execution. Conventional full predication techniques require both additional instruction bits for instruction encoding and unnecessary decoding of instructions, which incur extra power consumption in configuration memory and processing elements, respectively. It reaches 32.0% on average over the main target applications (H.264 video CODEC).

- We propose a predication mechanism to accelerate execution of control flows. Conventional predication techniques have focused on "correct execution" of control flows, and thus have negative or no impact on performance. On the contrary, our approach not only correctly executes control flows, but also accelerates their execution through a technique called DISE (Dual-Issue-Single-Execution). Experiments show that DISE accelerates the main target applications by 15.1% on average.

• We also reveal mapping issues when using the proposed predication. A power-saving mode introduced into processing elements prohibits multiple conditionals from being parallelized if conventional mapping algorithms are used. Thus, we propose the framework to map conditionals separately. Experiments show that mapping results from the proposed approach lead to 2.21 times higher performance than those of the naïve approach.

## Chapter 2

## Background and Related Work

### 2.1 Coarse-Grained Reconfigurable Architecture

#### 2.1.1 Introduction

As the size of semiconductor reaches physical limits but the amount of computation required in an application increases, it becomes more and more difficult to satisfy the performance requirement of an embedded system with just software running on a processor. Therefore, many embedded systems or System-On-Chips (SoCs) are equipped with one or more dedicated hardware IPs. Such hardware IPs may provide sufficient performance but lack flexibility, and so they should be redesigned from the scratch even when the required functionality changes slightly. Moreover, since hardware can hardly be fixed after fabrication, it needs much more time and effort put into the verification of the design before fabrication. Even further, considering that it is a trend to support various multimedia applications such as music or video codec in a cellular phone or

a portable multimedia player, developing an IP for each application takes too much cost and development time.

One way to solve such a problem is to use a CGRA, which provides hardware-like performance through an array processing as well as software-like flexibility through reconfigurability. Instead of developing a new IP for a new application, to implement an application on a CGRA, one can just reconfigure the existing CGRA such that the CGRA provides the necessary functionality of the application. Due to these benefits, there have been many researches proposing various kinds of CGRAs [1–10] and surveys on them [11, 12].

#### 2.1.2 Target Domain

CGRAs target both Instruction-Level Parallelism (ILP) and Data-Level Parallelism (DLP), but rely more on DLP to utilize abundant PEs since the amount of ILP is generally limited [19, 20]. Thread-Level Parallelism (TLP) is hardly supported due to the simplified control structure although there are some attempts [21, 22]. Thus, many works [3, 6, 23–25] have showed that CGRAs are suitable for multimedia applications, which are the traditional DLP applications. In addition, [26–28] have argued that CGRAs can support multiple domains, which include not only multimedia but also 3D graphics, and [29–31] have proved that the target domains can be extended to wireless communication system.

#### 2.1.3 Comparison with Other Architectures

Compared to Very Long Instruction Word (VLIW) processors [32], CGRAs have much simpler control structures. This makes it hard to support dynamic behaviors like stalls, which requires interactions among PEs or between PEs

and the controller. On the other hand, CGRAs have scalability and can have tens or hundreds of PEs while VLIWs generally have less than ten PEs due to complexity of such logics.

SIMD is well known to be effective and is used popularly [33,34], but [35] recently reported the utilization problem in conventional SIMD architectures. They found that the amount of DLP is quite varying according to applications so PEs are wasted when applications do not have as much DLP as the number of PEs. In such cases, CGRAs can exploit ILP on the unused ones, resulting in better utilization. Instead, CGRAs have more complex hardware and mapping process than those of SIMD.

There is another kind of reconfigure architecture, which is Field-Programmable Gate Array (FPGA) [36,37]. FPGAs have bit-level reconfigurability rather than word-level one, which makes hardware much more optimized for specific applications. However, making configuration is much more complex and also takes longer in order to assign bit-level functionality to reconfigurable logics, and the area/power efficiency can be lower in cases where the applications consist mostly of word-level operations and so bit-level reconfigurability is neglected.

Many-core systems and CGRAs are similar in that both have many PEs. However, PEs of CGRAs are much simpler ones since they do not have autonomy and receive orders from a single shared controller. Thus, CGRAs have efficiency in exploiting ILP and DLP while many-core systems are suitable for TLP.

#### 2.1.4 Application Mapping

To run applications on CGRAs, it is needed to generate configuration of CGRAs corresponding to the required functionality. The process of generating the configuration is called application mapping or just mapping in short. Since it is neither possible nor beneficial to execute the entire application on CGRAs, only data-intensive parts called kernels that have large parallelism are mapped to CGRAs. Most of the kernels are a loop where iterations have no dependency between them and thus can be executed in parallel or have some dependency but can be pipelined with short initiation interval. The functionality of a kernel is generally expressed as a CDFG (control data flow graph) and the kernel mapping is a process of generating configuration of CGRAs such that the PEs perform the operations in the CDFG while communication through the interconnections of PEs handles the data dependency among the operations.

Mapping of applications onto CGRAs have been researched actively. Some researched mapping methodology for better quality of solution or faster running time [38–45], and some want to integrate new issues on mapping process [16, 44, 46, 47].

### 2.1.5 Target CGRA

The target architecture is a CGRA called FloRA [9,48]. It mainly targets the embedded system applications having ILP and DLP, which include multimedia applications such as video CODEC (MPEG4, H.264) and 3D graphics. It has been implemented on a chip and its functionality and performance have already been verified [48].

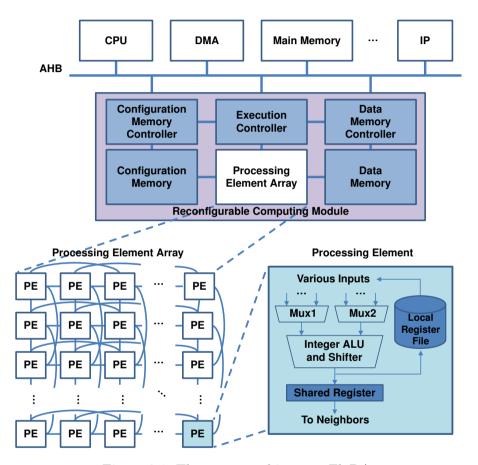

The overall architecture is shown in Figure 2.1. It consists of four main

components: the PE array, configuration memory, data memory, and controllers. The PE array has 8×8 PEs, each of which is comprised of an integer ALU, a shifter, and a local register file and can be dynamically reconfigured every cycle if needed. The configuration memory contains configuration information (or instructions) used by the PE array, which defines not only the operation of each PE but also the interconnection among the PEs. Currently, the bit-width of the information used by one PE for each cycle is 20 bits and configuration memory can hold at most 3072 entries. The data memory stores the input output data used/generated by the PE array. It is accessible from the outside of the reconfigurable computing module through the bus, which enables host processors to provide data for the CGRA. The execution controller manages macro instructions which generate signals that control the execution of the CGRA at a macro level. A macro instruction controls issuing instructions (in the form of a configuration stream that specifies the start address and the end address in the configuration memory) and fetching/storing data from/into the data memory.

FloRA has three distinguished features compared to other CGRAs. First one is efficient resource sharing [9]. Multipliers and dividers are area-critical, but are used less frequently than ALUs. Thus, it is quite wasteful that each PE has its own such resources. To tackle this problem, [9] proposed the way that several PEs share area-critical resources.

Second, FloRA has the loop pipelining technique depicted in Figure 2.2 [49]. In this technique, configuration information is pipelined through the PEs in the same row, instead of being directly fetched from the configuration memory for each PE. It contributes to reducing the amount of configuration information,

Figure 2.1: The target architecture FloRA.

Figure 2.2: Architecture for loop pipelining technique for FloRA.

and thus saves power consumption in accessing the configuration memory. Also, it simplifies the programming model for shared area-critical resources by allowing each PE in the same row to use the shared resources in a round-robin manner.

Lastly, FloRA can perform floating-point operations by combining two integer PEs. If separate floating point units are integrated to architectures, they are useless when integer operations are performed. On the other hand, when floating point units are used, integer functional units will be wasted. Thus, this approach can save area significantly by utilizing integer functional units for floating point operations.

### 2.2 Predicated Execution Technique

#### 2.2.1 Introduction

The existence of control flow in programs limits parallelism in two ways [50]. First, instructions having control dependences cannot be executed until they are released even though data dependences are released. Second, multiple conditionals have to be serialized due to lack of resources that are needed to handle

control flow. Processors targeting fine-grained parallelism like ILP and DLP generally execute single thread at a time, and thus, lack branch handling units, program counters, and instruction memory ports, preventing several control flows from being handled concurrently.

To overcome this limitation and exploit more parallelism, predicated (or guarded) execution technique [14] or predication in short is adopted by processors [15, 18, 50–54]. It is a technique to converts control flows to data flows by modifying both architectures and compilers. It handles control flows by fetching all instructions but selectively executing them, rather than branching. A predicate indicates whether an instruction is executed or not, and predication mechanism denotes the way of determining a predicate. An instruction that can be nullified by a predication mechanism is called a predicated instruction.

#### 2.2.2 Classification

[50] classified predication techniques into partial and full predication and compared their effects on performance in the domain of ILP, not of DLP. Its notion of full predication is limited to a narrow sense in that they consider only condition-based full predication. We extend their classification by introducing state-based full predication [54].

There have been several works related to the state-based full predication. [52] revealed that state-based full predication can virtually implement full predication only at the cost of partial predication. [51] emphasized that state-based full predication can handle *nested-if* structures, whereas condition-based full predication cannot.

#### 2.2.3 Different Roles in ILP and DLP processors

Predication improves the performance of ILP processors directly and indirectly. Increasing parallelism by removing control dependences is a direct way, which is stated in Section 2.2.1. However, when an *if* structure is long, applying predication to it takes longer time than branching since predicated instructions always take cycles even if they are not executed actually. If predication is optionally given, however, speedup of programs is guaranteed by simply not using predication when it gives worse results than branching. The side effect of predication is related to branch prediction. It can remove hard-to-predict branches which cause frequent branch miss [55] and help increase the success ratio of branch prediction. The removal of branches may make it hard to predict remaining branches as branch predictors cannot use correlation information anymore, but the problem can be solved by predicate prediction [56].

On DLP processors including CGRAs, predication is a much more critical issue. If a loop body has control flows but an architecture does not support predication, the loop cannot be parallelized and each iteration should be executed sequentially. The following code shows an example of such programs.

```

for (i = 0; i < 8; i++)

{

if (c[i] == 1)

x[i] = 0;

else

x[i] = 1;

}</pre>

```

Each loop iteration requires different instruction flows, but each PE cannot select its own flow since multiple PEs are controlled by a single control unit. This problem, called *control divergence*, prevents programs requiring different control

for each PE from being parallelized. Thus, in order to exploit DLP on such loops, it is essential to adopt predication into architectures [16, 18, 51–54, 57].

#### 2.2.4 Predication Support on CGRAs

Partial predication is used for CGRAs in [57–59]. [57] showed how to implement partial predication efficiently, and [58] maximized performance by using partial predication in a speculative way. [59] presented automatic mapping framework proposed in [58]. On the other hand, [16] proposed an automatic way to accelerate control-intensive kernels by using condition-based full predication.

However, they all tried to use conventional predications instead of inventing a better predication, and [16] and [59] showed that only minimal efforts are needed for automatic mapping of control flows using conventional predications. By adopting *if*-conversion (e.g., [60]), control dependency can be converted to data dependency. As a result, conventional mapping algorithms do not need to handle control flow explicitly, but only need to consider data dependency as usual.

## Chapter 3

# Conventional Predicated Execution Techniques

Through this and next sections, we present detailed comparison of three existing predication techniques and two proposed ones. We discuss performance using 3-address form ISA, which can be extended to a general case. We also discuss power analysis for fetching/decoding/executing instructions in such a way that it can be adopted in other processing units, not restricted to the domain of CGRAs. The characteristics of CGRAs can affect pros and cons of each predication technique in some cases, but we explicitly separate such parts from ISA- or machine- independent parts.

To explain the mechanism of each predication technique, we use an example of C program shown in Figure 3.1a throughout this section. We assume that the code represents a part of a loop body and the variables c[i], x, and y are stored in registers R0, R1, and R2, respectively. Also, we consider several types of if

```

if (c[i] == 1)

cmp R0 #1

1

2

b neq ELSE

3

x = x+1;

IF:

add R1 R1 #1

3

add R2 R2 #1

у

= y+1;

}

b uc END

5

5

6

else

6

7

7

ELSE: sub R1 R1 #1

x = x-1;

sub R2 R1 #1

9

y = y-1;

9

10

END:

(a) C code

(b) branch

```

Figure 3.1: An example C code and its branch equivalent.

structures; *if-only* structures, *if-else* structures, and *nested-if* structures. Since each predication shows different characteristics according to these types, we will use *if-else* structure to show the basic mechanism and add the explanation for other types.

### 3.1 Partial Predication (PARTIAL)

Predication is classically divided into two categories, partial and full, according to the range of predicated instruction [50]. Partial predication (PARTIAL) simply adds a number of special predicated instructions such as conditional mov to ISA (Instruction Set Architecture), whereas full predication makes all instructions predicated using more architectural modification.

To emulate predication effects for normal instructions using some special ones, Partial first executes instructions for every control path and commits results from only one path selected according to the condition using the special predicated instructions, which is called a *transformation* process. For example, line 3 in Figure 3.1a is converted to two instructions as shown in Figure 3.2: one for storing the result of a normal addition to a temporary register R3 (line

|   | Aggamble, Codo | RO == 0   |      | RO == 1       |      |

|---|----------------|-----------|------|---------------|------|

|   | Assembly Code  | Executed? | Flag | Executed?     | Flag |

| 1 | add R3 R1 #1   | Yes       |      | Yes           |      |

| 2 | add R4 R2 #1   | Yes       |      | Yes           |      |

| 3 | sub R5 R1 #1   | Yes       |      | Yes           |      |

| 4 | sub R6 R2 #1   | Yes       |      | Yes           |      |

| 5 | cmp R0 #1      | Yes       | lt   | Yes           | eq   |

| 6 | cmov eq R1 R3  | No        | lt   | Yes           | eq   |

| 7 | cmov eq R2 R4  | No        | lt   | Yes           | eq   |

| 8 | cmov neq R1 R5 | Yes       | lt   | $\mathbf{No}$ | eq   |

| 9 | cmov neq R2 R6 | Yes       | lt   | No            | eq   |

Figure 3.2: Partial predication (PARTIAL).

1) and the other for committing it if the eq flag (in the status register) is set (line 6).

The main advantage of Partial is minimal architectural support which is to add a few instructions to an ISA as stated before. Since an ISA usually has spare encoding space so that the designer can add new instructions, this approach does not need many changes in the hardware structure. On the other hand, it has lower performance than other predication mechanisms since the transformation inserts predicated instructions additionally and increases register pressure [50].

The increased register pressure could threaten potential speedup achievable through CGRAs. Originally CGRAs do not have many registers since they are typically targeted for data-intensive kernels<sup>2</sup>, where the live ranges of most variables are relatively short and not much overlapped with each other. Also, the high cost of registers in terms of area and power consumption hinders the number of registers from being increased. Consequently, it drives the user to

<sup>&</sup>lt;sup>2</sup>CGRAs and SIMD processors may be targeted to accelerate the control-intensive part of programs as well as the data-intensive part, but they generally have two separate hardware modules, one for each part [7,34,61,62].

rely on software-level approaches, which generally degrade performance.

Register spill is the most popular and intuitive way to solve the problem, but it is not appropriate for CGRAs since a limited number of load-store units and a single, centralized control unit act as a bottleneck to spill registers. For example, the target CGRA requires at least 12 cycles to read the spilled data back. Instead, we can allocate more PEs to provide more registers per loop body. For example, if a loop body has 12 variables and each PE has only eight registers, executing it on only a single PE would spill four variables, whereas mapping the loop body into two PEs completely eliminates the need for spilling. However, it could still have lower performance compared to other approaches since the PEs may be underutilized, or it may make it impossible to map bigger applications. In the experiments, average 1.75 more registers are required per PE, and one example (itpl) cannot be accelerated by the CGRA since it has 16 divergent paths.

In addition, Partial could incur additional overhead in energy consumption because it executes even  $unnecessary\ paths$  whose results will not be taken. This makes the execution units including ALUs and register files consume up to 2.88 times (1/(1-0.653)) energy compared to other predication techniques that do not execute instructions on unnecessary paths, which is shown in Section 5.3.1. The power gap becomes even larger if Partial is used for switch statements having multiple paths that need not be executed.

### 3.2 Condition-Based Full Predication (CONDFULL)

Unlike partial predication, full predication makes all instructions predicated.

Condition-based full predication (CondFull) is a type of full predication that

|   | Aggamble Code |             |    |    | la. | RO == 0       |      | RO == 1   |      |

|---|---------------|-------------|----|----|-----|---------------|------|-----------|------|

|   | Assembly Code |             |    |    |     | Executed?     | Flag | Executed? | Flag |

| 1 | uc            | cmp         | RO | #1 |     | Yes           |      | Yes       |      |

| 2 | eq            | ${\tt add}$ | R1 | R1 | #1  | $\mathbf{No}$ | lt   | Yes       | eq   |

| 3 | eq            | ${\tt add}$ | R2 | R2 | #1  | $\mathbf{No}$ | lt   | Yes       | eq   |

| 4 | neq           | sub         | R1 | R1 | #1  | Yes           | lt   | No        | eq   |

| 5 | neq           | sub         | R2 | R2 | #1  | Yes           | lt   | No        | eq   |

Figure 3.3: Condition-based full predication (CONDFULL).

introduces an additional field called *condition operand* in all instructions. This condition operand is compared to the flag in each PE and the result determines whether the corresponding instruction should be executed or not. In other words, each instruction is annotated by its own activating condition. For example, condition operands uc, eq, and neq in Figure 3.3 denote that the corresponding instruction is executed unconditionally, only if the eq flag is set, and only if the neq flag is set, respectively.

Compared to Partial, Condfull does not have overhead in performance or energy consumption since it does not require the transformation process [50]. However, there are several reasons that make Condfull increase the overall energy consumption. First, Condfull requires additional instruction bits used for condition operands. It affects both dynamic and static energy since it increases the capacity of the configuration memory. This could eventually lead to an increase in energy consumption even when the architecture executes normal programs that do not use the predication effect. In addition, although it eliminates the need for executing instructions on unnecessary paths (refer to Partial), it still needs to decode the instructions to check the condition operands in them.

| C Code      | a == 0    |   | Assembly Code | RO == 0        |

|-------------|-----------|---|---------------|----------------|

| C Code      | Executed? |   | Assembly Cou  | Executed? Flag |

| if (a == 1) | Yes       | 1 | uc cmp RO #1  | Yes            |

| if (b == 1) | No        | 2 | eq cmp R1 #1  | l No lt        |

| x = 0;      | No        | 3 | eq mov R2 #0  | No lt          |

| else        |           | 4 |               |                |

| x = 1;      | No        | 5 | neq mov R2 #1 | Yes lt         |

(a) naïve conversion

| C Codo                | a == 0                                      |   |     | Assembly Code |      | RO == 0 |    |    |     |    |

|-----------------------|---------------------------------------------|---|-----|---------------|------|---------|----|----|-----|----|

| C Code                | C Code ———————————————————————————————————— |   |     | Executed?     | Flag |         |    |    |     |    |

| if (a == 1 && b == 1) | Yes                                         | 1 | uc  | teste         | q    | R3      | RO | #1 | Yes |    |

|                       |                                             | 2 | uc  | teste         | q    | R4      | R1 | #1 | Yes |    |

|                       |                                             | 3 | uc  | and           | R4   | R3      | R4 |    | Yes |    |

|                       |                                             | 4 | uc  | cmp           | R4   | #1      |    |    | Yes | lt |

| x = 0;                | No                                          | 5 | eq  | mov           | R2   | #0      |    |    | No  | lt |

| if (a == 1 && b != 1) | Yes                                         | 6 | uc  | testn         | ıeq  | R4      | R1 | #1 | Yes | lt |

|                       |                                             | 7 | uc  | and           | R4   | R3      | R4 |    | Yes | lt |

|                       |                                             | 8 | uc  | cmp           | R4   | #0      |    |    | Yes | lt |

| x = 1;                | No                                          | 9 | neq | mov           | R2   | #1      |    |    | No  | lt |

(b) flattened

Figure 3.4: An example program that naïve conversion to CONDFULL produces incorrect assembly code due to its *nested-if* structure.

Also, Condfull has another limitation in handling *nested-if* structures. Since the mechanism is based on condition operands, it can express only one control flow at a time. In other words, the flag that controls the execution of a predicated instruction is determined only by the most recent comparison instruction, and that makes Condfull hard to handle *nested-if* structures. As an example, Figure 3.4a shows a program that is executed incorrectly with naïve conversion to Condfull. Assuming that variables a, b, and x are stored in the registers R0, R1, and R2, respectively, the assembly code generates incorrect results when the value of a (i.e., R0) is zero.

To overcome this limitation, CONDFULL uses a *flattening* technique in soft-

ware level, in which nested-if structures are converted into non-nested ones during architecture-specific optimization in the backend process. For example, the code in Figure 3.4a could be converted to the one in Figure 3.4b. However, this flattening technique could incur performance overhead as can be seen in the figure. This is mainly because it needs to recalculate flags for each combination. Moreover, it makes register pressure higher due to the need for extra temporary registers used to keep intermediate values for calculating flags (see R3 and R4 in the figure). For example, the deblock application has an if structure nested four times, so flattening causes about 13% overhead compared to the proposed predication technique that can support nested structures.

## Chapter 4

## **State-Based Full Predication**

State-based full predication is yet another type of full predication proposed in [54]. It uses a shared state to make instructions predicated instead of adding a condition operand to each instruction. In this mechanism, only a few special instructions are added to manage this shared state, thereby minimizing changes to the architecture. Nevertheless, since the state affects the entire set of instructions, state-based full predication virtually obtains the effect of full predication without any modification of normal instructions. To achieve this, an 1-bit state register is added to each PE, which indicates either awake or sleep state. PEs execute instructions normally in AWAKE state, whereas they nullify every instruction in SLEEP state. Therefore, by controlling the state of each PE using a special instruction, either the if-path or else-path can be executed selectively.

| <b>A</b> aa | ombly Codo  | R     | RO == 0 |      |       | RO == 1  |      |  |

|-------------|-------------|-------|---------|------|-------|----------|------|--|

| Ass         | embly Code  | State | Tag     | Flag | State | Tag      | Flag |  |

| cmp         | RO #1       | AWAKE |         |      | AWAKE |          |      |  |

| sleep       | neq END_IF  | AWAKE |         | lt   | AWAKE |          | eq   |  |

| add         | R1 R1 #1    | SLEEP | END_IF  | lt   | AWAKE |          | eq   |  |

| add         | R2 R2 #1    | SLEEP | END_IF  | lt   | AWAKE |          | eq   |  |

| sleep       | uc END_ELSE | SLEEP | END_IF  | lt   | AWAKE |          | eq   |  |

| awake       | END_IF      | SLEEP | END_IF  | lt   | SLEEP | END_ELSE | eq   |  |

| sub         | R1 R1 #1    | AWAKE |         | lt   | SLEEP | END_ELSE | eq   |  |

| sub         | R2 R2 #1    | AWAKE |         | lt   | SLEEP | END_ELSE | eq   |  |

| awake       | END_ELSE    | AWAKE |         | lt   | SLEEP | END_ELSE | eq   |  |

Figure 4.1: Instruction-based wake-up for state-based full predication (PSEUDOBRANCH).

## 4.1 Previous Approach (PSEUDOBRANCH)

To control the state of each PE, [51] proposed to use *sleep* and *awake* instructions (PSEUDOBRANCH). It associates each sleep instruction with a tag in order to support *nested-if* structures without flattening them. Each PE has a *tag register* to store the tag of the most recently executed sleep instruction. When a sleep instruction is invoked, the PE checks the status flag and enters into SLEEP state with saving a tag to the register if the flag value satisfies the condition. Once the PE enters into SLEEP state, it wakes up only when an awake instruction with the same tag is invoked.

Figure 4.1 shows an example of using PSEUDOBRANCH. "sleep neq END\_IF" in the line 2 denotes a sleep instruction that changes the state of the PE to SLEEP state and saves tag as END\_IF if the neq flag is set. Awake instructions in the line 6 and 9 have tags as an operand. It can be seen that in the case of RO == 1 the awake instruction in line 6 has no effect since the tag of the PE does not match to the one in the awake instruction.

PSEUDOBRANCH can support *nested-if* structures compared to conventional predications, but it has performance overhead in non-*nested* structures since it requires two additional instructions per *if* structure. In addition, it will consume as much power as CONDFULL since it needs to decode every instruction even in SLEEP state to check for an awake instruction.

## 4.2 Counter-Based Approach (STATEFULL)

We propose a novel state-based full predication, which uses per-PE counters and a sleep instruction for state transition (STATEFULL). The sleep instruction changes the state of a PE from AWAKE state to SLEEP state, which has two operands: condition and offset. When a PE enters SLEEP state, the per-PE counter is initialized to the value of the offset operand so that the PE returns to AWAKE state after skipping as many instructions as specified in the offset operand (i.e., sleep period). The sleep instructions have similar semantics to branch instructions, except that PEs simply ignore (neither decode nor execute) the instructions during SLEEP state instead of jumping to a new address by modifying the program counter.

Figure 4.2 shows the mechanism of STATEFULL. "csleep neq 3" is a sleep instruction that makes the PE sleep during the next three instructions if the neq flag is set. For example, if R0 is not 1, the sleep instruction in line 2 is activated (see State column) to put the PE into SLEEP state and keep it in that state until the counter becomes zero. During the sleep period, the counter keeps track of the number of instructions to be skipped including the current instruction.

There can be some issues related to multicycle operations or stalls. First,

|   | A             | F     | RO == 0 |      | RO == 1 |         |      |

|---|---------------|-------|---------|------|---------|---------|------|

|   | Assembly Code | State | Counter | Flag | State   | Counter | Flag |

| 1 | cmp RO #1     | AWAKE |         |      | AWAKE   |         |      |

| 2 | csleep neq 3  | AWAKE |         | lt   | AWAKE   |         | eq   |

| 3 | add R1 R1 #1  | SLEEP | 3       | lt   | AWAKE   |         | eq   |

| 4 | add R2 R2 #1  | SLEEP | 2       | lt   | AWAKE   |         | eq   |

| 5 | csleep uc 2   | SLEEP | 1       | lt   | AWAKE   |         | eq   |

| 6 | sub R1 R1 #1  | AWAKE |         | lt   | SLEEP   | 2       | eq   |

| 7 | sub R2 R2 #1  | AWAKE |         | lt   | SLEEP   | 1       | eq   |

Figure 4.2: Counter-based wake-up for state-based full predication (StateFull).

we assume that no operations require varying number of cycles (e.g., data-dependent operation cycles) since such operations can be hardly supported by CGRAs or other parallel architectures having a single controller and passive PEs. It is almost impossible for the controller to adjust the execution of PEs considering the status of all PEs. Second, fixed-multicycle operations cause no problem in the proposed approach since they are converted to the consecution of several single-cycle operations in the scheduling phase due to exactly the same reason as the first one. Thus, a PE does not need to consider multicycle operations at all. Lastly, the architecture can be stalled dynamically due to runtime conditions. For example, ADRES architecture [7] should be stalled if data read operations cause bank conflicts. In such situations, however, we can simply solve the problem by stalling the counters, too.

Statefull improves performance over Pseudobranch, since it does not require awake instructions which cause performance overhead. On the other hand, since it still needs to insert special sleep instructions to control the states of PEs, it could incur performance overhead compared to Condfull for programs that do not have any *nested-if* structure. This performance overhead

can be relatively large for *short-if* statements (*short-if* means the body of the *if* structure is short; refer to Section 5.3.2 for the definition). However, STATEFULL provides better performance than CONDFULL for programs having *nested-if* structures, since it naturally can handle them without flattening. In STATEFULL, nesting of *if* structures does not further increase the register pressure nor the number of instructions.

Moreover, Statefull contributes to reducing power consumption of PEs compared to Condfull. A major source of the reduction is that a PE knows a priori whether the next instruction will be executed or not before decoding the instruction. This is possible since the predicate is determined solely by the state register thereby completely eliminating the need for decoding the next instruction. Thus, when the PE is in SLEEP state, it does not need to do anything but just counts down until it wakes up. We exploit this observation by activating only some small logic circuits for counters and blocking unnecessary switching in registers and combinational circuits, including instruction registers and decoders. This can lead to a huge reduction in dynamic power consumption if it is implemented through clock-gating techniques. Note that it is impossible for Condfull since the PEs recognizes the predicate only after the instruction has been decoded and the corresponding condition has been evaluated. As a result, the proposed approach reduces power by 43.4% compared to Condfull (refer to Section 5.3.1).

In addition, it could reduce the power consumption of configuration memory as well. Considering the fact that STATEFULL does not require adding any additional field to the instructions, it uses smaller configuration memory compared to that for CONDFULL. Thus it reduces the power consumption of the

Figure 4.3: The concept of the DISE technique.

configuration memory as well.

## 4.3 Dual-Issue-Single-Execution (DISE)

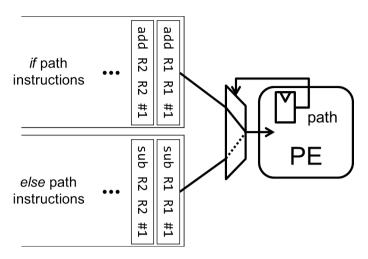

We propose another novel approach called *Dual-Issue-Single-Execution* (DISE) to accelerate execution of control flows. Figure 4.3 summarizes this concept. Considering that only one path (branch) is taken for each *if-else* construct, it is possible to issue instructions from both paths at the same time and let the PE execute only one path depending on the predicate. There is an internal 1-bit state register called *path register* for each PE to keep track of the path that the PE is currently executing.

The value of the path register is toggled by a predicated instruction named changepath. To provide enough instruction bandwidth, the PE fetches two instructions at each cycle, one for *true-path* and the other for *false-path*. Between them, the PE selects true-path instruction for execution if the value of the path register is TRUE, and selects the false-path one, otherwise.

If the true-path is longer than the false-path, then the false-path should be filled up with dummy nop instructions, and vice versa. Adding the dummy nop instructions is done during compile time and thus increases the code size thereby taking more configuration memory space. In case of normal code that has no control flow in it<sup>3</sup>, all the original instructions are put into the true-path (path register is set to TRUE) and the false-path is filled up with nop instructions. In this mechanism, however, DISE could waste lots of configuration memory space due to the increased code size. For example, the round application in the experiments has an if-else structure that takes 16.7% of the entire execution time. It means that nop instructions should be inserted into the false-path for the normal code part, which takes 83.3%, so the dynamic energy on configuration memory will be increased by 83.3% due to more instruction fetches.

To avoid this problem, we handle the two code parts differently by introducing two instruction-fetch modes. Normal code is fetched in the *normal mode*, where only one instruction is fetched and assigned to the true-path, and if-else code is fetched in the *DISE mode*, where two instructions are fetched (refer to Section 5.1.2 for the implementation detail).

Figure 4.4 shows an example of DISE. "changepath neq" flips the value of the path register if the specified flag is asserted. In the case of R0 == 0, the path register, which is initially set to TRUE to fetch normal code, is changed to FALSE by the changepath instruction in line 2 since the given predicate is true. After that, three instructions from the false-path are executed instead of

$<sup>^3</sup>$ Hereafter, we call the portions of the program corresponding to if-else paths as *if-else code* and all others as *normal code*.

|   | Assembl              | y Code        | RO == | 0    | RO == | = 1  |

|---|----------------------|---------------|-------|------|-------|------|

|   | True-path False-path |               | Path  | Flag | Path  | Flag |

| 1 | cmp RO #1            |               | TRUE  |      | TRUE  |      |

| 2 | changepath neq       |               | TRUE  | lt   | TRUE  | eq   |

| 3 | add R1 R1 #1         | sub R1 R1 #1  | FALSE | lt   | TRUE  | eq   |

| 4 | add R2 R2 #1         | sub R2 R2 #1  | FALSE | lt   | TRUE  | eq   |

| 5 | nop                  | changepath uc | FALSE | lt   | TRUE  | eq   |

Figure 4.4: Dual-Issue-Single-Execution (DISE).

true-path instructions until another changepath instruction in the false-path is invoked to return to the true-path, indicating the termination of *if-else code*.

The major objective of DISE is to accelerate the execution of control flows. The previous approaches focus mainly on "correct execution" of control flows and their execution time is proportional to the total number of instructions in the if-else code. However, since DISE issues two instructions—one from the true-path and the other from the false-path—at every cycle, its execution time depends on the number of instructions in the longest side between if- and else-paths. This can be achieved without any additional functional unit, but with minimal modification in the memory structure, causing only 2% area overhead [53]. DISE is also preferable in terms of performance to the existing technique that uses more PEs to accelerate the execution of control flows by executing if- and else-paths at the same time and then selecting the right result [58]. Although their technique may reduce the latency of one iteration, it does not improve the throughput when the target application has enough parallelism.

As mentioned in Section 4.2, STATEFULL reduces dynamic power consumption by not decoding instructions during sleep periods. Similarly, DISE reduces

dynamic power consumption since only instructions in either of the two paths are decoded. Note that dual-issuing does not increase the number of fetched instructions. Although it issues twice as many instructions as other predication techniques for each cycle, the total number of fetched instructions over the entire execution remains almost the same (ignoring the extra instructions for DISE, which take typically a very small portion), which is the sum of the lengths of if- and else-paths. Hence, DISE consumes almost the same dynamic energy as that of STATEFULL except the overhead to the circuits added to support dual-issuing and doubled port width of configuration memory. Fortunately, we develop several techniques to keep the overhead very low (2.4% power overhead in the reconfigurable array and configuration memory) as detailed in Section 5.3.6. Moreover, DISE could eventually reduce energy consumption even with the additional circuit overhead through clock/power gating during the slack period obtained by performance improvement.

However, it could be inefficient in the case that the lengths of if- and elsepaths are unbalanced. The technique requires balancing the lengths of the two paths, and thus extra nop instructions are inserted for unbalanced if-else paths as depicted in Figure 4.5. This incurs increase in code size, and eventually leads to larger dynamic energy consumption in the configuration memory. This problem should be addressed carefully since real programs may have a considerable number of unbalanced *if-else* structures or even *if-only* structures making DISE inefficient.

Besides, DISE has a limitation in applying it to *nested-if* structures. This is because the mechanism uses path registers to choose the right instructions to be executed, which can handle only one control flow at a time. Therefore, this

| C Code         |   | Assembly Code              |  |  |  |  |  |

|----------------|---|----------------------------|--|--|--|--|--|

|                |   | True-path False-path       |  |  |  |  |  |

| if (x[i] == 1) | 1 | cmp RO #1                  |  |  |  |  |  |

| {              | 2 | changepath neq             |  |  |  |  |  |

| a = a + 1;     | 3 | add R1 R1 #1 sub R1 R1 #1  |  |  |  |  |  |

| b = b + 1;     | 4 | add R2 R2 #1 nop           |  |  |  |  |  |

| c = c + 1;     | 5 | add R3 R3 #1 nop           |  |  |  |  |  |

| d = d + 1;     | 6 | add R4 R4 #1 changepath uc |  |  |  |  |  |

| }              | 7 |                            |  |  |  |  |  |

| else           | 8 |                            |  |  |  |  |  |

| a = a - 1;     | 9 |                            |  |  |  |  |  |

Figure 4.5: Additional nop instructions inserted for DISE to balance the lengths of if- and else-paths.

mechanism also requires flattening the *nested-if* structures as in CondFull, and thus would cause performance degradation. However, its effect is smaller than that in CondFull since it has the capability of accelerating the execution of control flows thereby compensating the negative effect of flattening.

## 4.4 Hybrid Predication

#### 4.4.1 Motivation

Each predication has pros and cons. Condfull shows relatively good performance in both short-if and long-if structures, but it incurs notable overhead in energy consumption and requires significant modification of the existing ISA. As an alternative, Statefull could be chosen since it does have significantly lower energy consumption while maintaining or even improving the performance over Condfull. However, it performs poorly in the case of short-if structures, which could be a serious problem since short-if structures take a considerable portion of control flows in real programs. Other predication techniques such as Partial and DISE are not appropriate to be used solely since their charac-

Table 4.1: Characteristics of Predicated Execution Techniques

|                                | ISA     | Config.   |          | Performance | )         | Energ    | y Consun | ption     |

|--------------------------------|---------|-----------|----------|-------------|-----------|----------|----------|-----------|

|                                | 15A     | Mem.      | Short-if | Long-if     | Nested-if | Short-if | Long-if  | Nested-if |

| Partial                        | +insts  | Identical | Moderate | Slow        | Slow      | Moderate | High     | High      |

| CondFull                       | width ↑ | Bigger    | Fast     | Fast        | Slow      | Moderate | High     | High      |

| STATEFULL                      | +insts  | Identical | Slow     | Moderate    | Fast      | High     | Low      | Low       |

| DISE                           | + insts | Identical | Moderate | Very Fast   | Moderate  | Moderate | Low      | Moderate  |

| STATEFULL+PARTIAL              | +insts  | Identical | Moderate | Moderate    | Fast      | Moderate | Low      | Low       |

| ${\tt STATEFULL+PARTIAL+DISE}$ | + insts | Identical | Moderate | Very Fast   | Very Fast | Moderate | Low      | Low       |

teristics are rather specialized to specific kinds of programs (*short-if* structures for Partial and balanced *if-else* structures for DISE). The first four rows of Table 4.1 summarize the characteristics of predication techniques introduced in the previous section.

Therefore, we propose to combine StateFull with Partial and/or DISE. The key idea behind this is to compensate the weakness of StateFull by adopting other predication techniques, and so, to bring synergistic effects in terms of both performance and energy consumption as shown in the last two rows of Table 4.1. Also they could be easily integrated into the architecture without interfering with each other as they are implemented as special instructions rather than modifying the entire ISA. Note that combining CondFull with Partial is not beneficial since Partial does not provide any benefit over CondFull. Hybridizing CondFull with DISE is not beneficial either since neither DISE nor CondFull can execute nested-if structures efficiently. Lastly, the combination of CondFull and StateFull is inefficient in terms of power consumption as both provide similar benefits from full predication itself and CondFull causes lots of overhead in configuration memory.

| C Code                         | StateFull                                             | Partial                                   |  |  |  |

|--------------------------------|-------------------------------------------------------|-------------------------------------------|--|--|--|

| if (x[i] > 255)<br>x[i] = 255; | mov R1 #255<br>cmp R0 R1<br>csleep leq 1<br>mov R0 R1 | mov R1 #255<br>cmp R0 R1<br>cmov gt R0 R1 |  |  |  |

Figure 4.6: An example program that Partial executes with better performance than StateFull.

#### 4.4.2 STATEFULL+PARTIAL

STATEFULL inserts sleep instructions into the code to control *if* structures, which incurs overhead in energy consumption as well as performance. For *long-if* structures, reduction in energy consumption on unnecessary paths is usually large enough for compensating the overhead of sleep/awake instructions. However, this overhead could eventually lead to an increase in total energy consumption in the case of *short-if* structures, in which energy reduction on unnecessary paths is small.

To mitigate this overhead, we propose to incorporate Partial into State-Full to cover *short-if* structures with very low overhead in performance and energy consumption. This is based on the observation that mov-only *if* structures are common for *short-if* structures, for example, 79.4% of *short-if* structures in three examples (idct, chroma, and max) are composed of only mov operations, and Partial can handle mov-only *if* structures without performance overhead by just replacing mov instructions with conditional mov instructions, as shown in Figure 4.6.

However, Partial is not always preferred against Statefull in handling short-if structures, especially when they contain instructions other than mov instructions. This is because the transformation of short-if structures contain-

ing non-mov instructions could degrade performance and consume more energy due to unnecessary execution of instructions, as explained in Section 3.1. This is the reason why we decide to use Partial only for mov-only *short-if* structures in a software manner. This strategy is investigated through experiments in Section 5.3.3.

This approach is not ISA specific. Almost all ISAs have mov instructions and adding a conditional mov instruction into an ISA is a representative implementation of partial predication [50]. Thus, mov instructions can be easily transformed to conditional mov instructions added to general ISAs. Note that the strategy may have to be changed if a different type of partial predication is implemented (e.g., partial predication based on select instructions [50]).

#### 4.4.3 STATEFULL+PARTIAL+DISE

We propose to combine DISE with STATEFULL to further improve performance and energy efficiency. This is remarkably beneficial because DISE can effectively accelerate simple *if-else* structures while STATEFULL efficiently covers the case of *nested-if* structures. STATEFULL is very effective even for *if-only* structures (as well as *nested-if* structures), which are not efficiently handled by DISE. Using DISE for unbalanced *if-else* structures has a problem of increased code size because the extra nop instructions are inserted to balance the true- and false-path. This eventually leads to the increase in dynamic power consumption due to the extra instruction fetches.

To solve this problem, we propose a hardware-level solution to handle unbalanced *if-else* structures in a power-efficient way. The solution is adding a predicated instruction that has the capability of changing the state of a PE

|   | Assem           | Assembly Code         |       |         | RO == 0         |      |  |  |  |

|---|-----------------|-----------------------|-------|---------|-----------------|------|--|--|--|

|   | True-path       | False-path            | State | Counter | Path            | Flag |  |  |  |

| 1 | cmp RO #1       |                       | AWAKE |         | TRUE            |      |  |  |  |

| 2 | changepath neq  |                       | AWAKE |         | TRUE            | lt   |  |  |  |

| 3 | add R1 R1 #1 su | ıb R1 R1 #1           | AWAKE |         | FALSE           | lt   |  |  |  |

| 4 | add R2 R2 #1 ch | nangepath_csleep uc 2 | AWAKE |         | FALSE           | lt   |  |  |  |

| 5 | add R3 R3 #1    |                       | SLEEP | 2       | $\mathbf{TRUE}$ | lt   |  |  |  |

| 6 | add R4 R4 #1    |                       | SLEEP | 1       | TRUE            | lt   |  |  |  |

Figure 4.7: A solution to eliminate the need for nop instructions. This is the result when the solution is applied to the example code shown in Figure 4.5.

to SLEEP state and, at the same time, alternating between true-path and false-path. This special instruction, changepath\_csleep, eliminates the need for extra nop instructions completely thereby reducing the size of code so dynamic power consumption as well. Figure 4.7 shows an example of using the special instruction. Instead of filling the false-path (which is shorter than the true-path) with nop instructions, a changepath\_csleep instruction is inserted right after the termination of the false-path. Note that changing the path right after the termination of the false-path may not work correctly since it would result in executing the remaining instructions in the true-path. For example, changing the path right after the sub instruction in Figure 4.7 would make the PE execute two add instructions, which leads to incorrect execution of the program. That is why it sleeps for two cycles before changing the path.

Basically, in *nested-if* structures, DISE can be applied to either the outermost or innermost *if-else* structures and the rest should be covered by STATE-FULL. However, such structures can be handled even more efficiently when DISE and STATEFULL are applied together. Figure 4.8 shows such an example. Figure 4.8a shows the C code and Figure 4.8b shows the case of applying DISE

to the outermost *if-else* structure while Figure 4.8c shows the case of applying it to the innermost one. Figure 4.8d shows how DISE can be applied several times to further improve the performance by moving multiple code blocks to the false-path side. Note that in all three cases, converting STATEFULL to DISE improves the performance but maintains the same number of instructions as that of the STATEFULL-only case; applying DISE just requires the change of the predicated instruction type (csleep to changepath) but does not require additional instructions. Therefore, we can accelerate nested structures effectively by selecting the one giving the maximum performance among the candidates<sup>4</sup>.

Consequently, these software- and hardware-level techniques help DISE to overcome its weakness. Moreover, we could further improve the technique by putting Partial together with it to cover the weakness of StateFull on short-if structures as discussed in the previous section. Therefore, we use the technique StateFull+Partial+DISE, as a universal solution to predicated execution in terms of both performance and power.

<sup>&</sup>lt;sup>4</sup>Identifying the best candidate efficiently remains to be a problem to be solved. In the experiments, we tried all combinations of else code blocks to be moved and chose the one with highest performance among the feasible (no overlap in the false-path) combinations.

| C Code         |    | StateFull     |

|----------------|----|---------------|

| if (x[i] == 1) | 1  | cmp R0 #1     |

| {              | 2  | csleep neq 10 |

| d = 0          | 3  | mov R5 #0     |

| if (y[i] == 1) | 4  | cmp R1 #1     |

| {              | 5  | csleep neq 4  |

| a = 0;         | 6  | mov R2 #0     |

| b = 0;         | 7  | mov R3 #0     |

| c = 0;         | 8  | mov R4 #0     |

| }              | 9  | csleep uc 2   |

| else           | 10 | mov R2 #1     |

| a = 1;         | 11 | mov R3 #1     |

| b = 1;         | 12 | csleep uc 1   |

| }              | 13 | mov R5 #1     |

| else           | 14 |               |

| d = 1;         | 15 |               |

| True-path      | False-path             |

|----------------|------------------------|

| cmp R0 #1      |                        |

| changepath neq |                        |

| mov R5 #0      | mov R5 #1              |

| cmp R1 #1      | changepath_csleep uc 7 |

| csleep neq 4   |                        |

| mov R2 #0      |                        |

| mov R3 #0      |                        |

| mov R4 #0      |                        |

| csleep uc 2    |                        |

| mov R2 #1      |                        |

| mov R3 #1      |                        |

(b) applying DISE into the outermost *if-else* structure

(a) example

|    | True-path      | False-path    |   |       |

|----|----------------|---------------|---|-------|

| 1  | cmp R0 #1      | <u> </u>      |   | 7     |

| 2  | csleep neq 7   |               | 1 | cmp   |

| 3  | mov R5 #0      |               | 2 | char  |

| 4  | cmp R1 #1      |               | 3 | mov   |

| 5  | changepath neq |               | 4 | cmp   |

| 6  | mov R2 #0      | mov R2 #1     | 5 | char  |

| 7  | mov R3 #0      | mov R3 #1     | 6 | mov   |

| 8  | mov R4 #0      | changepath uc | 7 | mov   |

| 9  | csleep uc 1    |               | 8 | mov   |

| 10 | mov R5 #1      |               |   |       |

|    |                |               | ( | d) an |

| True-path      | False-path             |  |  |  |

|----------------|------------------------|--|--|--|

| cmp R0 #1      |                        |  |  |  |

| changepath neq |                        |  |  |  |

| mov R5 #0      | mov R5 #1              |  |  |  |

| cmp R1 #1      | changepath_csleep uc 4 |  |  |  |

| changepath neq |                        |  |  |  |

| mov R2 #0      | mov R2 #1              |  |  |  |

| mov R3 #0      | mov R3 #1              |  |  |  |

| mov R4 #0      | changepath uc          |  |  |  |

(d) applying DISE into both  $\emph{if-else}$  structures

Figure 4.8: Applying DISE and State Full together into nested-if structures for better performance.

<sup>(</sup>c) applying DISE into the innermost  $\it if\text{-}else$  structure

## Chapter 5

## **Evaluation**

## 5.1 Implementation

#### 5.1.1 Conventional Techniques

#### Partial Predication (PARTIAL)

We added a *conditional mov* (cmov) instruction to the ISA for Partial. Instead of the cmov instruction, a select instruction could have been implemented for the purpose of Partial. However, it was impossible to integrate the select instruction into the target architecture because it had four operands, whereas the ISA allowed only three-address form.

#### Condition-Based Full Predication (CONDFULL)

For the implementation of CONDFULL, we appended a 3-bit condition operand to each instruction and implemented a mechanism to nullify instructions on unnecessary paths by generating signals to disable writes into the registers and latches (disabling writes into the latches keeps the functional units from unnecessary switching). Due to this, the length of each instruction was increased from 20 bits to 23 bits and the capacity of the configuration memory was increased from  $7.5 \, \text{KB} \ (=3072 \times 20 \, \text{bits})$  to  $8.625 \, \text{KB} \ (=3072 \times 23 \, \text{bits})$ .

#### Another State-Based Full Predication (PSEUDOBRANCH)

We tried to implement PSEUDOBRANCH as proposed in [51]. We added sleep/awake instructions to the ISA, and added an 1-bit state register (representing either AWAKE or SLEEP state) and a 5-bit tag register to each PE. However, as explained in Section 4.1 and Section 4.2, PSEUDOBRANCH cannot save power with extra logic.

#### 5.1.2 Proposed Techniques

#### State-Based Full Predication (STATEFULL)

We added a csleep instruction to the ISA. To keep track of information on sleep states, we added an 1-bit state register (representing either AWAKE or SLEEP state) and an 8-bit sleep period counter (in short, sleep counter) for each PE. This sleep counter was implemented by extending the existing 3-bit counter, which had been originally introduced to support multicycle operations such as multiplication. The counter could be shared like this since the existing counter would have not been used otherwise during SLEEP state. The 1-bit state register is used for gating clock signals of all registers (except the sleep counter) to prevent unnecessary bit changes during SLEEP state, thereby reducing dynamic power consumption dramatically.

Since we use an 8-bit sleep counter, it limits the maximum sleep period to 256 instructions. However, it is sufficient for the target applications having DLP as they do not have extremely *long-if* structures in most cases. In the ten

Figure 5.1: Modification of architecture to support DISE.

applications, the longest *if* structure consists of 143 instructions. Note that this does not imply that the target architecture cannot execute longer *if* structures. Rather, such *long-if* structures can be handled by applying software-level techniques such as splitting a long sleep period into multiple, short sleep periods having at most 256 instructions.

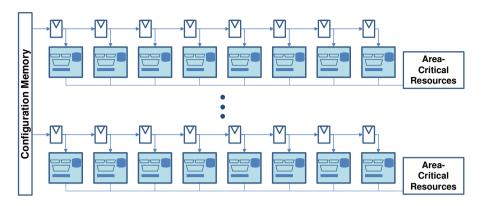

#### Dual-Issue-Single-Execution (DISE)

The implementation of the DISE technique requires adding one more memory bank and datapath to fetch one more instruction. The actual implementation can be varying according to the baseline architectures since they have their own ways of configuration, but Figure 5.1 shows how it is combined with the feature shown in Figure 2.2. The instruction registers, which pipeline instructions through the PEs in the same row, were doubled and the configuration memory was divided into two banks (thus having the same capacity, 1536 entries for each bank). We also added a changepath instruction to the ISA and incorporated an 1-bit path register and a two-to-one 20-bit multiplexer into each PE to select the instructions to be executed.