#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

#### 공학박사 학위논문

# High quality GaP and InP growth on Si (001) substrates by MOCVD

MOCVD를 이용한 실리콘(001) 기판 위에 고품위 GaP 및 InP 성장에 대한 연구

2015년 2월

서울대학교 대학원

재료공학부

이 상 문

#### **Abstract**

# High quality GaP and InP growth on Si (001) substrates by MOCVD

Lee Sangmoon

Department of Materials Science and Engineering

College of Engineering

Seoul National University

High-quality epitaxial growth of III-V on silicon substrates has been of great interest for many years due to because of the potential for monolithic integration of III-V based devices with Si metal-oxide semiconductor (MOS) integrated circuits and high performance and low power logic devices. Particularly, integration of III-V on Si can open up opportunities for new functionalities and multiple integration platforms, such as terahertz electronics, optoelectronics, integrating logic and communication platforms on the same Si wafer.

In this dissertation, the epitaxial growth of InP layers on Si (001) substrates by selective area growth (SAG) has been studied in order to explore the potential applications as mentioned before. High quality InP layers were grown using a thin GaP buffer layer in SiN<sub>x</sub> trenches on Si (001) substrates. There are three main challenges for growth of high quality epitaxial layers.

The first challenge is the high defect density in the epitaxial layers due to the large lattice mismatch between InP and the Si substrates. The second is the large difference in thermal expansion coefficient between InP and the Si substrates or  $SiN_x$  mask in SAG. Last one is the generation of polar/non-polar interfaces between InP and Si substrates. The main focus of this work is to understand the defect formation mechanism as well as to develop solutions for defect reduction and to grow InP layers having extremely flat top surface for CMOS applications without CMP process.

A thin GaP buffer layer is used as the intermediate layer between the InP and the Si substrates to alleviate the large lattice mismatch and to facilitate the InP nucleation. We find the optimized growth condition of GaP layers on exact Si (001) substrate through a multi-step MOCVD process to achieve such high quality GaP/Si (001) template substrates by planar method. We have investigated the generation process of low defects in GaP layers grown on Si substrates by FME. It was found that there were optimized growth conditions as growth temperature, V/III ratio and growth rate. RMS roughness is 2.8 nm from the optimized growth conditions. InP epilayers were grown on Si substrates using buffer layers of GaP. AFM, SEM and TEM examination results showed that GaP is a proper material as a buffer layer, and that its optimum thickness is about 3~5nm. TEM observation showed that the inserted InGaAs strained layers were very helpful to reduce the surface roughness and defect reduction. It also confirmed that GaP acted as a buffer to

alleviate the lattice mismatch between InP and Si. The best AFM roughness

obtained from inserted InGaAs strained layers was 2.1nm for 5 x 5  $\mu$ m<sup>2</sup>.

Next, we also propose a new scheme of SiN<sub>x</sub> mask for SAG process to

grow InP layers with high quality and flat top surface by applying to mask

with etched Si surfaces and rounded top shape SiN<sub>x</sub>. The extremely flat InP

top surface is obtained by the optimized SiN<sub>x</sub> mask for SAG.

In last part, we investigated SAG of InP layers on patterned Si substrates

with InP/GaP buffer layers at various growth temperatures ranging from

500 °C to 650 °C. In order to grow high quality InP, a thin GaP buffer layer

was grown on stepped sidewall surfaces of etched Si. The different growth

temperature resulted in different top surfaces. The high quality InP layer with

smooth surface can be attributed to the dislocation necking effect together

with the formation of void. Finally we demonstrated the formation of

InGaAs/InP heterostructures using the suggested InP templates, which can be

used in applications of electronic devices.

Keywords: Indium phosphide, Gallium phosphide, Selective Area Growth

(SAG), Metalorganic chemical vapor deposition (MOCVD), defect

necking, Anti-phase boundary (APB), Surface morphology

**Student Number: 2011-30192**

V

# Contents

| Abs  | stract | t        |                                                     | I   |

|------|--------|----------|-----------------------------------------------------|-----|

| Cor  | ntent  | S        |                                                     | V   |

| List | t of T | ables    |                                                     | IX  |

| List | t of F | igures . |                                                     | X   |

|      |        |          |                                                     |     |

| Ch   | apt    | er 1.    | Introduction                                        | 1   |

|      | 1.1    | Mot      | ivation                                             | 3   |

|      | 1.2    | Si a     | nd III-V material properties                        | 7   |

|      | 1.3    | The      | sis organization                                    | 11  |

|      | 1.4    | Refe     | erences                                             | 13  |

|      |        |          |                                                     |     |

| Ch   | apt    | ter 2.   | Growth and characterization of InP on Si            | 15  |

|      | 2.1    | Cha      | nllenges of InP growth on Si                        | 16  |

|      |        | 2.1.1    | Lattice mismatch                                    | 16  |

|      |        | 2.1.2    | Thermal mismatch                                    | 18  |

|      |        | 2.1.3    | Defects Associated to Polar on Non-Polar Epitaxy    | 19  |

|      | 2.2    | Met      | alorganic Chemical Vapor Deposition (MOCVD) system  | 30  |

|      |        | 2.2.1    | Overview                                            | 30  |

|      |        | 2.2.2    | MOCVD system                                        | 32  |

|      |        | 2.2.3    | Source Molecules                                    | 33  |

|      |        | 2.2.4    | Principle of MOCVD                                  | 36  |

|      | 2.3    | Cha      | racterizations                                      | 44  |

|      |        | 2.3.1    | Nomarski DIC microscope                             | 44  |

|      |        | 2.3.2    | Field emission scanning electron microscopy (FE-SEM | )45 |

|      |        | 2.3.3    | Transmission electron microscopy (TEM)              | 45  |

|         |     | 2.3.4   | Atomic force microscopy (AFM)                           | 46      |

|---------|-----|---------|---------------------------------------------------------|---------|

|         |     | 2.3.5   | High resolution X-ray diffractometry (HR-XRD)           | 46      |

|         | 2.4 | Ref     | erences                                                 | 47      |

|         |     |         |                                                         |         |

| Cha     | apt | ter 3 ( | GaP blanket growth on Si (001) substrate                | es52    |

|         | 3.1 | Intr    | oduction                                                | 53      |

|         | 3.2 | Exp     | perimental details                                      | 58      |

|         | 3.3 | Res     | sults and discussions                                   | 59      |

|         |     | 3.3.1   | Optimization of LT GaP layers on Si                     | 60      |

|         |     | 3.3.2   | Optimization of HT GaP layers on Si                     | 72      |

|         | 3.4 | Sun     | nmary                                                   | 78      |

|         | 3.5 | Ref     | erences                                                 | 79      |

| <b></b> | ·P· |         | Heteroepitaxial InP growth on Si(001)a (001) substrates |         |

|         | 4.1 | Intr    | oduction                                                |         |

|         | 4.2 |         | perimental details                                      |         |

|         | 4.3 | Res     | sults and discussions                                   | 86      |

|         |     | 4.3.1   | Heteroepitaxial InP growth on Si(001) and               | Ge(001) |

|         |     |         | substrates                                              | 86      |

|         |     | 4.3.2   | Optimization of InP growth on Si using GaP buffer.      | 99      |

|         | 4.4 | Sun     | nmary                                                   | 101     |

|         | 4.5 | refe    | erences                                                 | 102     |

|         |     |         |                                                         |         |

| Ch      | m   | tor 5 G | SAG of high quality InP on Si substrate (               | ucina a |

| CII     | apı | ICI 3 N |                                                         | O       |

|         |     |         | GaP thin buffer layer                                   | 105     |

| 5.1     | Intr    | oduction                                   | 106            |

|---------|---------|--------------------------------------------|----------------|

| 5.2     | Exp     | perimental details                         | 108            |

| 5.3     | Res     | ults and discussion                        | 110            |

|         | 5.3.1   | Effects on growth temperature on surface i | norphology 110 |

|         | 5.3.2   | Defect formation mechanisms                | 121            |

| 5.4     | Sun     | nmary                                      | 129            |

| 5.5     | Ref     | erences                                    | 131            |

|         |         |                                            |                |

| Chapt   | ter 6 ( | Conclusions                                | 134            |

| 국문 .    | 초록.     |                                            | 138            |

| List of | publ    | ication                                    | 142            |

| 감사의     | 의 글.    |                                            | 146            |

# **List of Tables**

| and III-V semiconductors | Table 1-1. Physical properties of common group IV |

|--------------------------|---------------------------------------------------|

| 8                        | [5]                                               |

| of various metal-organic | Table 2-1. Thermal pyrolysis (or decomposition)   |

| 35                       | (MO) and gas sources                              |

# **List of Figures**

| Figure 1-1  | Microprocessor performance increase due to scaling [9]                |

|-------------|-----------------------------------------------------------------------|

| Figure 1-2  | Active and standby power density trends plotted from industry data    |

|             | The extrapolations indicate a cross over below 20nm gate length       |

|             | [10]4                                                                 |

| Figure 1-3  | The chain of communication systems versus the length of the           |

|             | interconnection and the business volume of the corresponding          |

|             | technology. (Source: Intel)                                           |

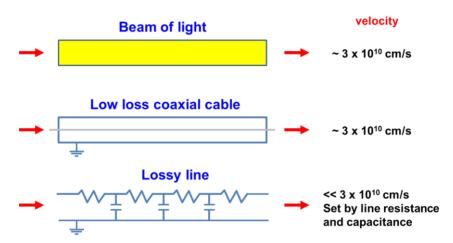

| Figure 1-4. | Illustration of types of optical and electrical propagation and their |

|             | velocities [11]6                                                      |

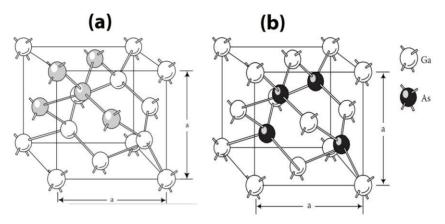

| Figure 1-5. | Primitive cells of diamond (a) and zincblende (b) crystals. The       |

|             | two identical sublattices in the diamond crystal structure are        |

|             | shifted toward each other along the diagonal direction. The           |

|             | zincblende crystal structure has two sublattices composed of          |

|             | different elements                                                    |

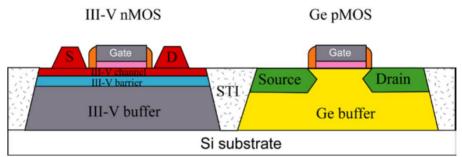

| Figure 1-6. | Example of heterointegration of Ge and III-V MOS transistors on       |

|             | a Si substrate. Different device structures can be made on the        |

|             | strain-relaxed III-V and Ge buffer layers. On the left, a quantum-    |

|             | well device architecture is shown and the III-V barrier layer is      |

|             | inserted to block the source-to-drain leakage current. On the right   |

|             | shown is Ge channel strain engineering by embedded source and         |

|             | drain                                                                 |

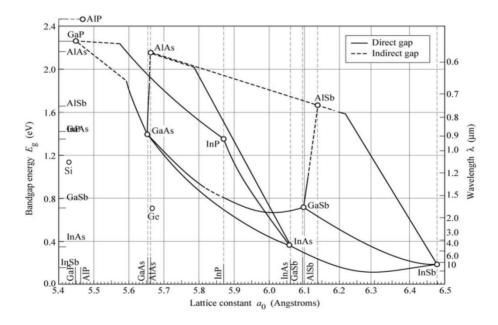

| Figure 2-1  | Band gap energy and lattice constant of various III-V and IV          |

|             | semiconductors at room temperature [3]                                |

| Figure 2-2  | Schematic diagram of anti-phase domains boundaries in InAs            |

|             | formed by a single-atom step on the silicon substrate surface.        |

|             | Figure modified according to reference [11]22                         |

| Figure 2-3 Schematic diagram of anti-phase domains boundaries in InAs              |

|------------------------------------------------------------------------------------|

| formed by a single-atom step on the silicon substrate surface.                     |

| Figure modified according to reference [11]                                        |

| Figure 2-4 Self-annihilation anti-phase domains on $[011]$ plane in a $(001)$ zinc |

| blende semiconductor by the close proximity of bonding of two                      |

| APD faces. Figure modified according to reference [9]                              |

| Figure 2-5 HR-TEM image of stacking faults defects found in InP/GaP/Si             |

| system                                                                             |

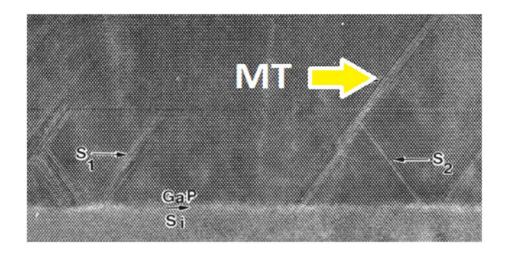

| Figure 2-6 HRTEM image of micro twin and stacking faults defects (S1,S2) in        |

| GaP/Si system. Figure modified according to reference [24] 29                      |

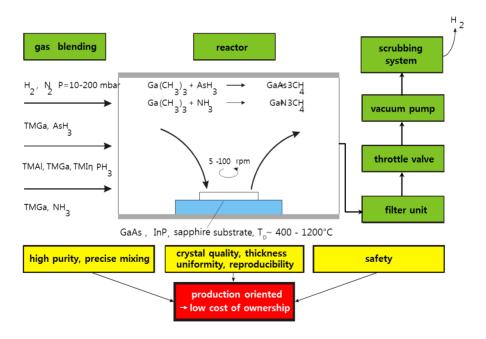

| Figure 2-7 Schematic illustration of the MOCVD system [Aixtron]31                  |

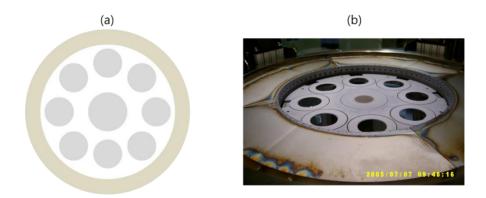

| Figure 2-8 (a) Layout of the AIX 2400 G3 susceptor in the $8\times3$ inch. (b)     |

| Photo of the reactor chamber of the AIX 2400 G3 in the 8×3 inch                    |

| configuration                                                                      |

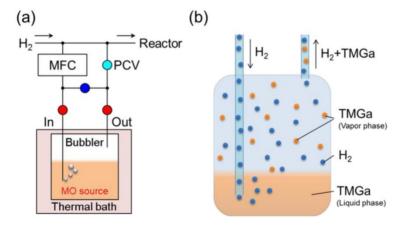

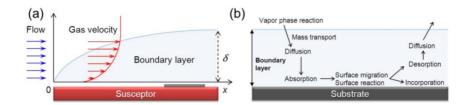

| Figure 2-9 (a) Schematic illustration of the line for metal-organic (MO)           |

| source provided by bubblers                                                        |

| Figure 2-10 (a) Schematic illustration of the flow into the reactor, gas velocity  |

| decreasing near the susceptor surface, and boundary (stagnant)                     |

| layer. The $\delta$ represents the thickness of boundary layer. The gas            |

| flow feeds from left side ( $x < 0$ , upper stream of the reactor) to              |

| right side ( $x > 0$ , downstream of the reactor) of this figure. The              |

| black rectangle lied on the susceptor represents the growth                        |

| substrate. The vertical axis represents the direction, which is                    |

| perpendicular to the surface of the susceptor or to the growth                     |

| surface of the substrate. (b) Schematic illustration of the some                   |

| kinds of mechanisms involved in the MOCVD process 38                               |

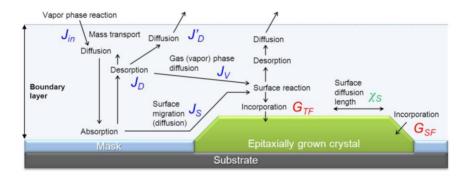

| Figure 2-11 Schematic illustration of the some kinds of mechanisms involved        |

| in the selective-area (SA) MOVPE process40                                         |

|                                                                                    |

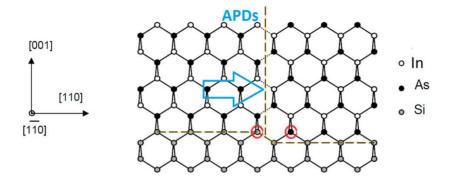

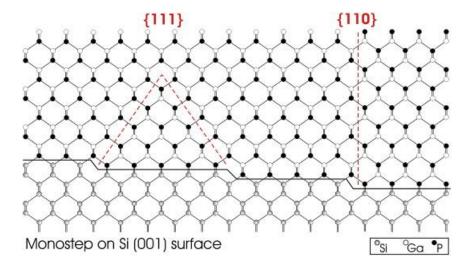

| Figure 3-1. Sketch of the APB formation in the {111} and {110} lattice planes                                          |

|------------------------------------------------------------------------------------------------------------------------|

| of the GaP zinc-blende structure due to the presence of mono-                                                          |

| layer steps on the Si surface                                                                                          |

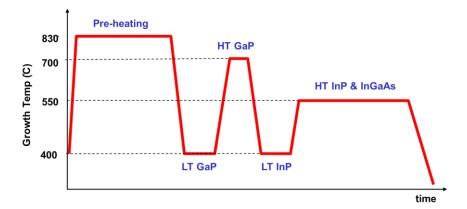

| Figure 3-2 Growth sequence of InP/GaP epilayers on Si substrates 59                                                    |

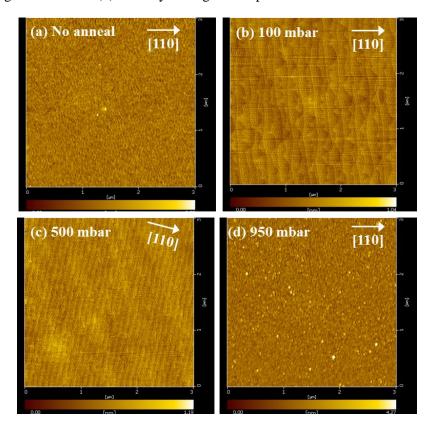

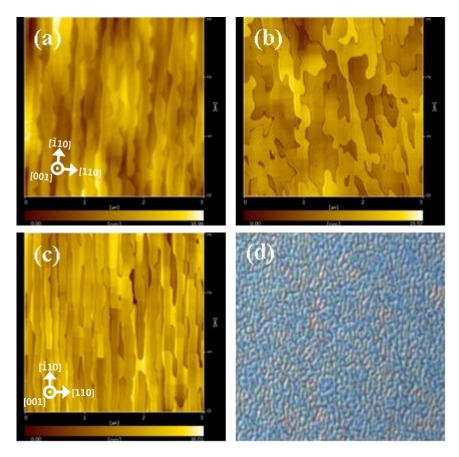

| Figure 3-3 AFM images of the surface of bare Si substrates after annealed at                                           |

| $830^{\circ}\mathrm{C}$ for 30min in different reactor pressures of H2 ambient. (a)                                    |

| no annealing (b) 100 mbar (c) 500 mbar (d) 950 mbar61                                                                  |

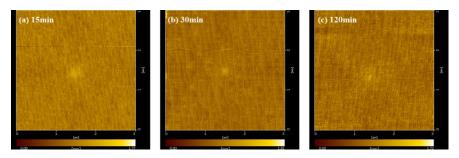

| Figure 3-4 AFM images of the surface of bare Si substrates after annealed at                                           |

| $830^\circ\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$                                    |

| of H2 ambient. (a) 15min (b) 30min (c) 120min                                                                          |

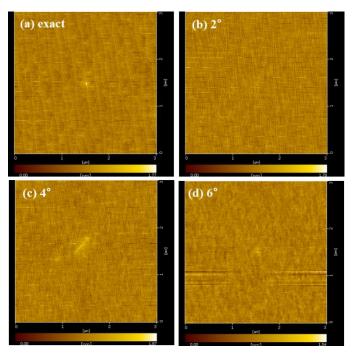

| Figure 3-5 AFM images of the surface of bare Si substrates after annealed at                                           |

| $830^\circ\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$                                    |

| using different substrate orientations. (a) exact (b) 2° off (c) 4°                                                    |

| off (d) 6° off toward [110] direction respectively                                                                     |

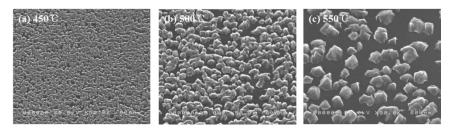

| Figure 3-6 SEM micrographs of LT-GaP layers grown at different growth                                                  |

| temperature after annealed at at $830^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

| reactor pressure. (a) 450 $^{\circ}$ C (b) 500 $^{\circ}$ C (c) 550 $^{\circ}$ C respectively.                         |

| 65                                                                                                                     |

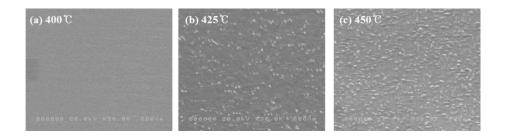

| Figure 3-7 SEM images of LT-GaP layers grown at different growth                                                       |

| temperature after annealed at at $830^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

| reactor pressure, (a) 400 $^{\circ}$ C (b) 425 $^{\circ}$ C (c) 450 $^{\circ}$ C                                       |

| respectively 65                                                                                                        |

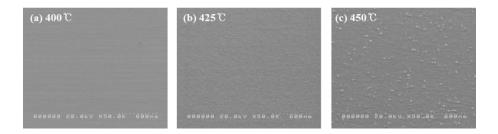

| Figure 3-8 SEM images of LT-GaP layers grown at different growth                                                       |

| temperature after annealed at at 830°C for 30min in 100 mbar                                                           |

| reactor pressure. (a) 400 $^{\circ}$ C (b) 425 $^{\circ}$ C (c) 450 $^{\circ}$ C                                       |

| respectively                                                                                                           |

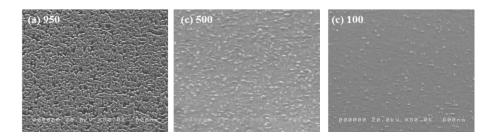

| Figure 3-9 SEM images of LT-GaP layers grown at 450 °C after annealed at                                               |

| 1 15010 5 5 5 5 5 11 minges of 11 our rayors grown at 750 0 arror amounted at                                          |

| $830^{\circ}\mathrm{C}$ for 30min in different reactor pressure, (a) 950 (b) 500 (c)                                                      |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 100 mbar respectively67                                                                                                                   |  |  |  |  |  |

| Figure 3-10 RMS roughness as LT-GaP growth temperature for different H2                                                                   |  |  |  |  |  |

| annealing reactor pressure (a) 100 mbar marked as a solid square                                                                          |  |  |  |  |  |

| (b) 500 mbar marked as a solid circle                                                                                                     |  |  |  |  |  |

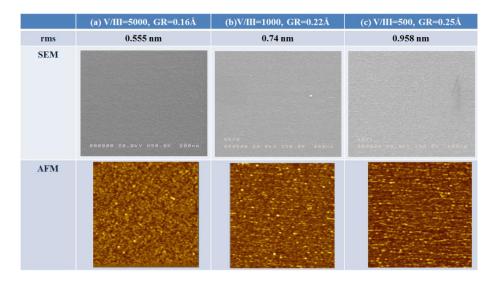

| Figure 3-11 SEM and AFM images of LT-GaP layers grown at different $V/III$                                                                |  |  |  |  |  |

| ratio and growth rate of (a) V/III=5000, growth rate=0.16 $\mbox{\normalfont\AA}$ (b)                                                     |  |  |  |  |  |

| V/III=1000, growth rate=0.22Å, (c) $V/III=500$ , growth                                                                                   |  |  |  |  |  |

| rate=0.25Å respectively. All of samples are grown at 425 $^{\circ}\mathrm{C}$                                                             |  |  |  |  |  |

| after annealed at $830^{\circ}\mathrm{C}$ for $30\mathrm{min}$ in $150~\mathrm{mbar}$ reactor                                             |  |  |  |  |  |

| pressure                                                                                                                                  |  |  |  |  |  |

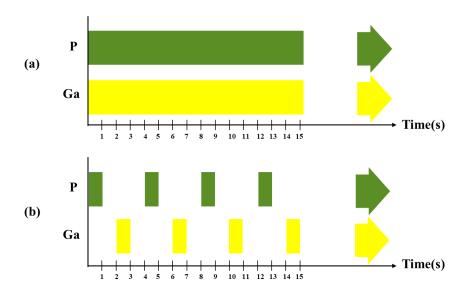

| Figure 3-12 Schemetic depiction of the time dependences of the metal organic                                                              |  |  |  |  |  |

| precursor injection during continuous (a) or flow rated modulated                                                                         |  |  |  |  |  |

| (b) epitaxy. The nucleation was either started by P for both                                                                              |  |  |  |  |  |

| cases                                                                                                                                     |  |  |  |  |  |

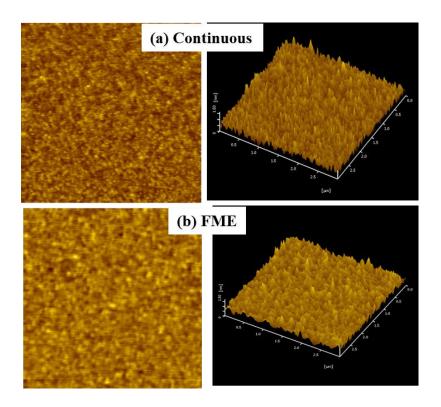

| Figure 3-13 AFM images of LT-GaP layers grown at 400 $^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$   |  |  |  |  |  |

| at $830^{\circ}\mathrm{C}$ for 30min in 100 mbar reactor pressure using different                                                         |  |  |  |  |  |

| growth mode, (a) continuous nucleation, (b) FME respectively.                                                                             |  |  |  |  |  |

| RMS roughness of each sample is same as 0.17nm71                                                                                          |  |  |  |  |  |

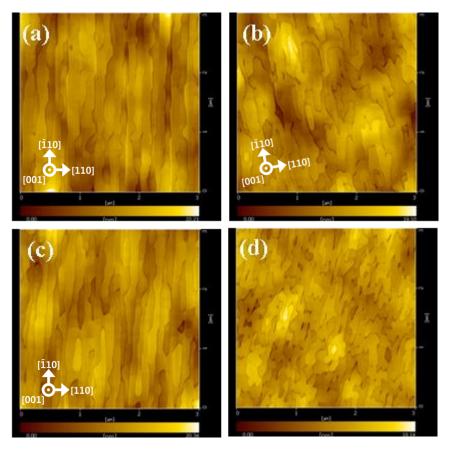

| Figure 3-14 AFM images of GaP bulk layers grown at different growth                                                                       |  |  |  |  |  |

| temperature (a) $500^{\circ}\mathrm{C}$ , (b)525 $^{\circ}\mathrm{C}$ , (c) 550 $^{\circ}\mathrm{C}$ , (d) 650 $^{\circ}\mathrm{C}$ , (e) |  |  |  |  |  |

| 700 $^{\circ}$ C, (f) 800 $^{\circ}$ C respectively. LT-GaP nucleation layers of all                                                      |  |  |  |  |  |

| samples are grown at 400 $^{\circ}\mathrm{C}$ and have 3nm-thickness. RMS                                                                 |  |  |  |  |  |

| roughness is (a) 10.9nm, (b) 10.8nm, (c) 18.9nm, (d) 4.3nm, (e)                                                                           |  |  |  |  |  |

| 2.94nm, (f) 3.44nm respectively                                                                                                           |  |  |  |  |  |

| Figure 3-15 AFM images of GaP bulk layers grown at 700 $^\circ\mathrm{C}$ with different                                                  |  |  |  |  |  |

| V/III ratio (a) 5000 (b) 1000, (c) 500, (d) 100 respectively. LT-                                                                         |  |  |  |  |  |

|              | GaP nucleation layers of all samples are grown at 400 $^\circ\!\!\mathbb{C}$ and                               |

|--------------|----------------------------------------------------------------------------------------------------------------|

|              | have 3nm-thickness. RMS roughness is (a) 2.9nm, (b) 2.1nm, (c)                                                 |

|              | 2.0nm, (d) very hazy respectively and last sample (d) is measured                                              |

|              | by Normalski optical microscopy due to very hazy surface.                                                      |

|              | 75                                                                                                             |

| Figure 3-16  | AFM images of GaP bulk layers grown at 700 $^\circ\mathrm{C}$ with different                                   |

|              | V/III ratio (a) 500 (b) 250, (c) 100 respectively. Sample (d) is                                               |

|              | grown at sample temperature with $V/III = 100$ and 2 times growth                                              |

|              | rate than that of sample (c). LT-GaP nucleation layers of all                                                  |

|              | samples are grown at 400 $^\circ\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$      |

|              | roughness is (a) 3.5nm, (b) 2.7nm, (c) 2.5nm, (d) 2.1nm                                                        |

|              | respectively76                                                                                                 |

| Figure 3-17. | GaP bulk layers grown at $700^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

|              | at 400 $^{\circ}\text{Chaving 3nm-thickness after annealed at at 830 ^{\circ}\text{C} for$                     |

|              | 30min in 100 mbar reactor pressure using different growth                                                      |

|              | mode77                                                                                                         |

|              |                                                                                                                |

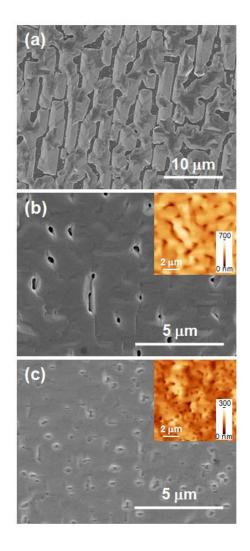

| Figure 4-1 1 | x 1 μm <sup>2</sup> AFM images of InP layers grown on vicinal Si(001) at (a)                                   |

|              | 450 and (b) 400 °C for 10 min                                                                                  |

| Figure 4-2   | Plan-view SEM images of two-step InP layer grown on vicinal                                                    |

|              | Si(001). The growth temperatures of second layer were (a) 650,                                                 |

|              | (b) 600 and (c) 550 $^{\circ}\text{C}$ . The insets of (b) and (c) are AFM images                              |

|              | of corresponding samples. The RMS roughnesses of (b) and (c)                                                   |

|              | are 68.0 and 32.5 nm, respectively                                                                             |

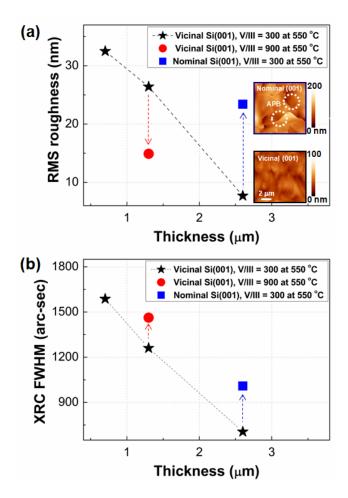

| Figure 4-3   | (a) Plots of RMS roughness and (b) XRC FWHM of InP layers                                                      |

|              | depending on growth conditions. The insets of (a) are $10 \times 10$                                           |

|              | $\mu\text{m}^2$ AFM images of InP layers of 2.6 $\mu\text{m}$ grown on nominal and                             |

|              | vicinal Si(001) with the RMS roughnesses of 23.4 and 7.7 nm.                                                   |

| respectively90                                                                 |

|--------------------------------------------------------------------------------|

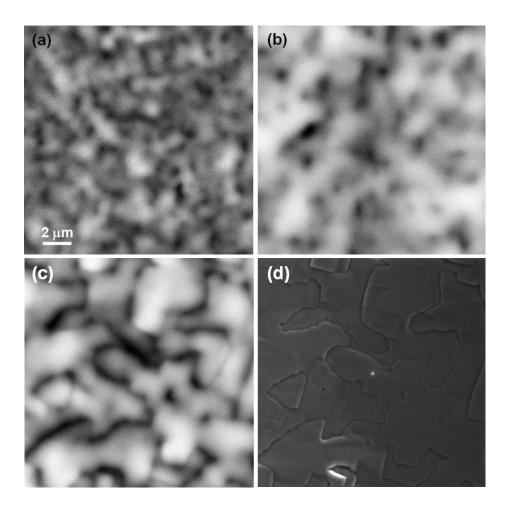

| Figure 4-4 CL images of InP layers on (a), (b) vicinal and (c) nominal Si(001) |

| substrates at 80 k. The thickness of InP layers are (a) 1.3 and (b),           |

| (c) 2.6 µm. (d) Plan-view SEM image corresponding to (c) 92                    |

| Figure 4-5 10 x 10   m2 AFM images of 1.3   m-thick InP layer grown on         |

| vicinal (a) Si(001) and (b) Ge(001) substrates. RMS roughnesses                |

| are (a) 26.4 and (b) 7.8 nm                                                    |

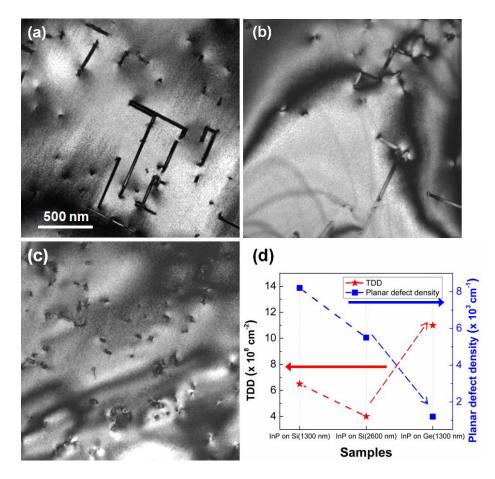

| Figure 4-6 Plan-view TEM images of InP layer grown on vicinal (a), (b)         |

| Si(001) and (c) Ge(001) substrates. Thicknesses of InP layers are              |

| (a), (c) 1.3 and (b) 2.6 m. (d) the plot of TDD and planar                     |

| defect density of InP layer grown on vicinal Si(001) and Ge(001)               |

| substrates                                                                     |

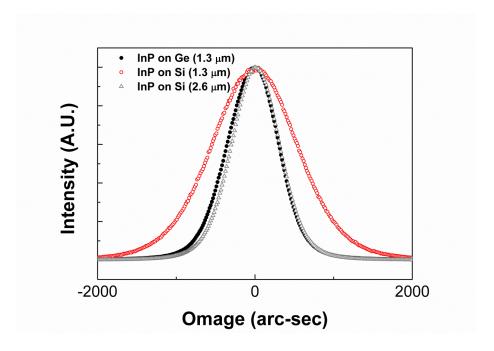

| Figure 4-7 $$ XRD rocking curves of InP layers grown on vicinal Si(001) and    |

| Ge(001) substrates                                                             |

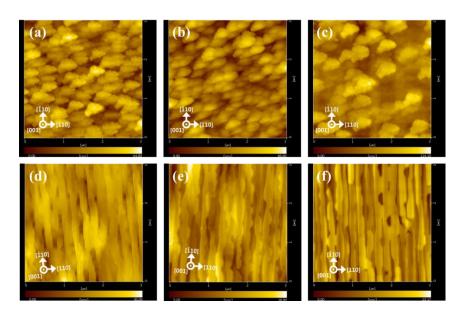

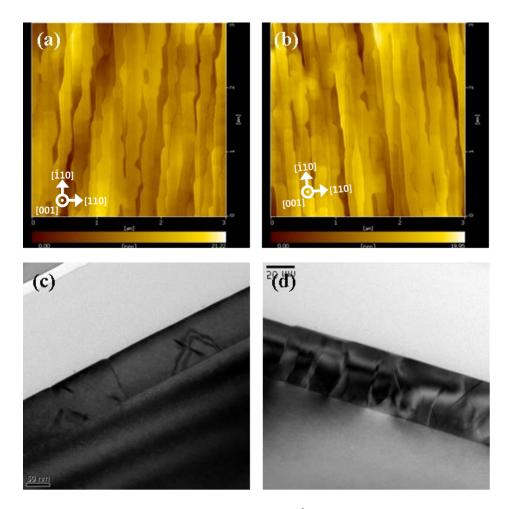

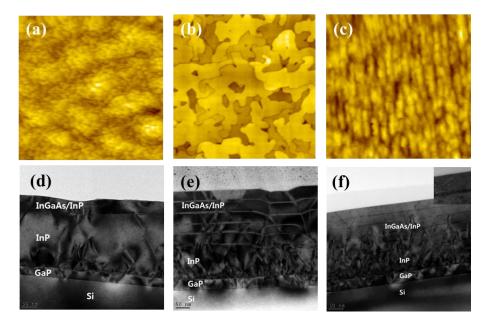

| Figure 4-8 AFM images of InP top layers from (a) to (c) and bright field       |

| (g=(001)) cross-sectional TEM micrograph are from (d) to (f)                   |

| with different growth condition and buffer structure. All samples              |

| have the same GaP buffer growth conditions and RMS roughness                   |

| is (a) 9.4nm, (b) 5.5nm, (c) 2.1nm respectively                                |

|                                                                                |

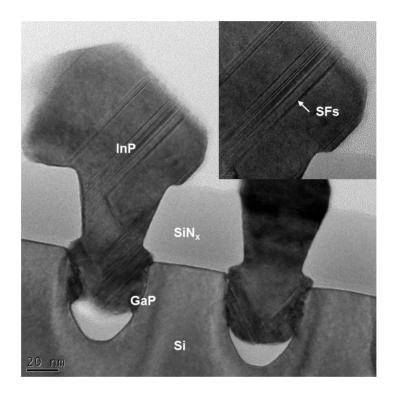

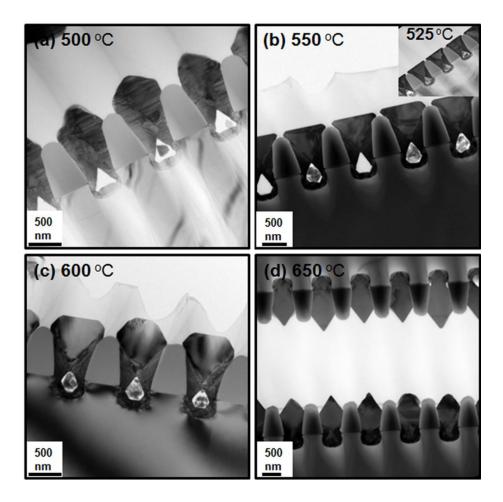

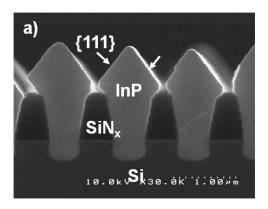

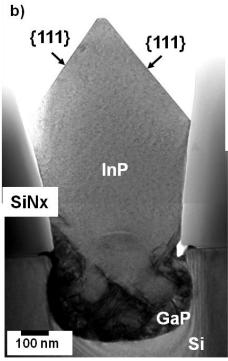

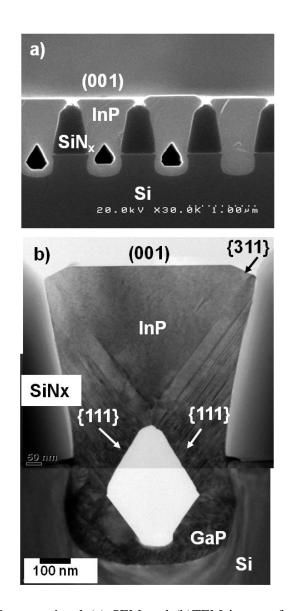

| Figure 5-1 Cross-sectional TEM images of InP layers grown on patterned Si      |

| (001) substrate at various growth temperatures ranging from (a)                |

| 500 °C to (d) 650 °C with increment of 50 °C                                   |

| Figure 5-2 Cross-sectional (a) SEM and (b) TEM images of epitaxially grown     |

| InP layer on a patterned Si (001) wafer with SiNx mask. HT InP                 |

| layer is grown at 650 °C                                                       |

| Figure 5-3 Cross-sectional (a) SEM and (b)TEM image of HT InP layer            |

| grown on a patterned Si (001) wafer with SiNx mask. HT InP                     |

| layer is grown at 550 °C                                                  |

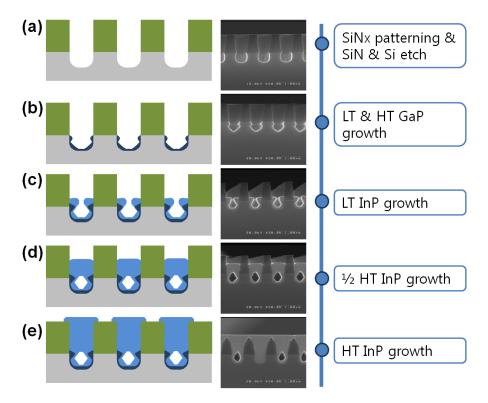

|---------------------------------------------------------------------------|

| Figure 5-4 Evolution of growth behavior of InP layer from the (a) $SiNx$  |

| patterning to (e) the HT InP growth                                       |

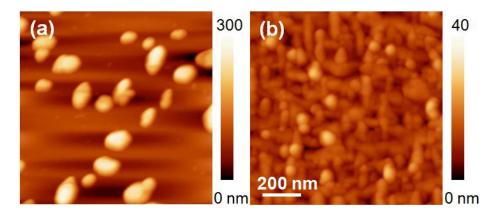

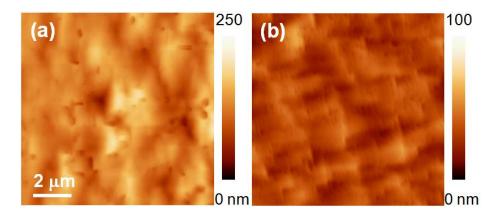

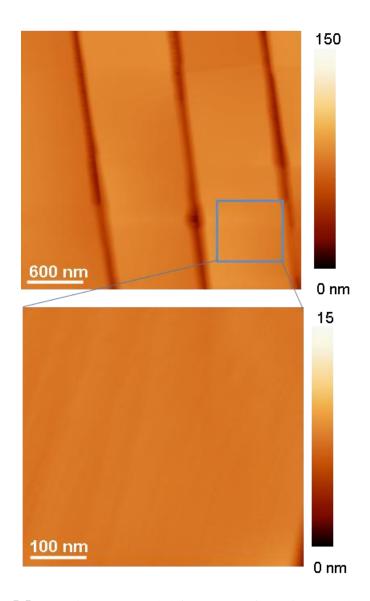

| Figure 5-5 AFM images recorded from the surface of HT InP layer grown at  |

| 550 oC. The lower figure shows the magnified image of the flat            |

| top region                                                                |

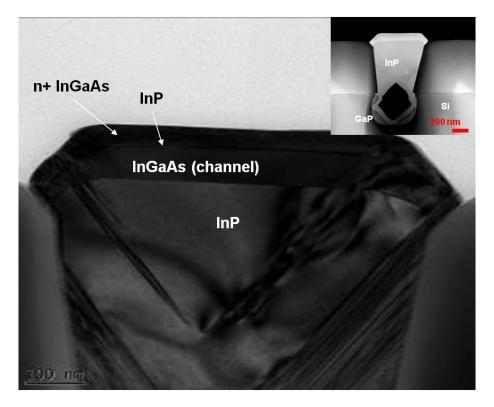

| Figure 5- 6. Cross sectional TEM image of InGaAs grown on HT InP template |

| grown at 550 oC. The inset shows the STEM image of the same               |

| structure                                                                 |

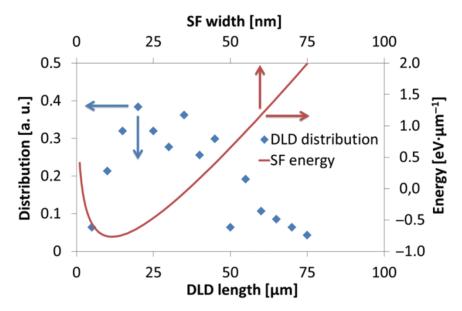

| Figure 5-7. Normalized distribution of DLDs with respect to DLD width     |

| extracted from sample K with layer thickness of $100\mu\text{m}$ . The    |

| crystal energy/unit length of SF with respect to SF width is              |

| included for comparison. The arrows indicate on which scale the           |

| data is plotted on [21]                                                   |

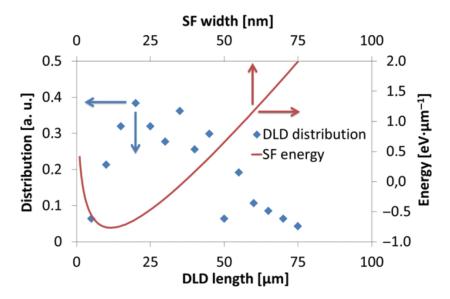

| Figure 5-8. Normalized distribution of DLDs with respect to DLD width     |

| extracted from sample K with layer thickness of $100\mu\mathrm{m}$ . The  |

| crystal energy/unit length of SF with respect to SF width is              |

| included for comparison. The arrows indicate on which scale the           |

| data is plotted on [21]                                                   |

### **Chapter 1**

#### Introduction

Silicon is the basic material of electronics. About 95% of all semiconductor devices are manufactured using silicon substrates. As a carrier, the Si substrate is undoubtedly advantageous due to its small mass, good thermal conductivity, low cost, maximum wafer diameter, and wide prevalence. In addition, Si channel based complementary metal oxide semiconductor (CMOS) microelectronics industry has moved into a new era of nanoelectronics driven by the well-known Moor's scaling law [1,2]. The fast scaling has been slowed down in the past few years as the physical gate lengths of CMOS devices approach about 20 nm [1]. Further shrinking the dimensions does not give any performance benefit but bring up great challenges in device fabrication.

As an alternative to the Si-channel devices, high mobility materials have been widely considered and triggered extensive research interest over the past decade in order to further boost the device performance [3,4]. The high hole mobility of Ge makes it a good candidate for pMOS devices while III-V compound semiconductor materials generally have higher electron mobility [5]. The combination of Ge and III-V materials provides a promising approach to making high performance non-Si channel CMOS devices. However, the mechanical and thermal properties of both Ge and III-V materials make them incompatible with the mainstream Si processing technologies [6]. Furthermore, Ge and III-V materials are much more expensive with limited availability compared to Si. Therefore, the benefit of

Ge and III-V materials has to be accomplished by epitaxial growth on Si, which allows a thin layer instead of bulk substrates for device fabrication by using the Si processing platform. To manufacture non-Si CMOS devices, selective area growth (SAG) of Ge and III-V materials on Si proves to be one of the best solutions. In SAG, epitaxial growth only occurs on the dedicated device areas while the deposition on oxide or nitride surfaces is prevented [7]. Therefore, different materials can be integrated on a single Si substrate by using SAG. However, there are many challenges in SAG of Ge and III-V materials in order to make device quality epitaxial layers on Si substrates.

This dissertation describes our contributions on monolithic integration of InP on Si for the CMOS technologies and optical detection technologies. This introductory chapter begins with a brief background and discussion of the motivation of this work. The limitations of scaling of conventional Si bulk MOSFETs and electrical wires are summarized. Finally, the organization of the dissertation is presented.

#### 1.1. Motivation

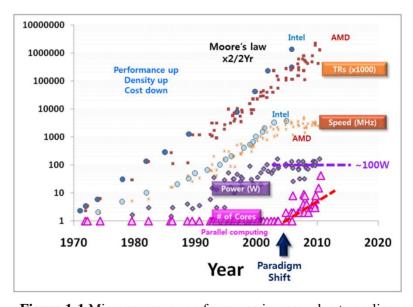

The Silicon Metal-Oxide-Semiconductor Field Effect Transistor has been the workhorse of the semiconductor industry for the last three to four decade. Device scaling has improved both packing density and transistor performance, resulting in increase in cost per function, which propelled the success of semiconductor industry. Figure 1-1 depicts the exponential increase in microprocessor performance represented by millions of instructions per second, over technology generations. Even though the physical dimensions have been continually shrinking by a factor of 2-3 in accordance with Moore's Law [8], the fundamental architecture and materials of the device has remained the same. However, as we further shrink the device dimension, transistor with conventional structure and material is reaching its fundamental scaling limit.

Figure 1-1 Microprocessor performance increase due to scaling

[Source: Intel & AMD]

Without change in transistor geometry and introduction of novel materials, exponential decrease in device dimensions cannot continues further, as beyond the 22nm node fundamental as well as practical constraints will limit the maximum performance achievable by these scaled transistors.

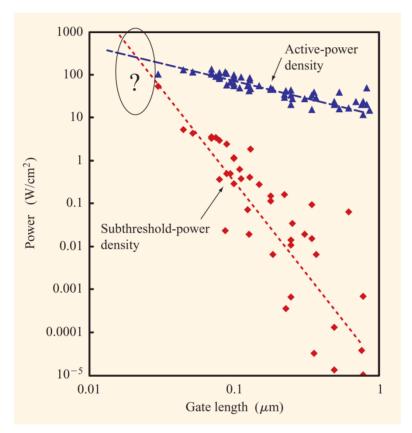

**Figure 1-2** Active and standby power density trends plotted from industry data. The extrapolations indicate a cross over below 20nm gate length [10]

Increased performance has come at a cost of increased off state power in transistors. Figure 1-2 depicts the evolution of power density as the devices are scaled traditionally. The static power has increased more rapidly compared with the linear increase in the active power dissipation. Around the

gate length of 20 nm, static power would approach the active power, and even surpass it, as we continue the scaling. Hence, beyond gate length of 20nm, it is questionable if the traditional scaling techniques would be effective. The major reason for this rapid increase in static power is the subthreshold leakage. With decreasing channel length, gate bias cannot form effective potential barrier between the source and the drain when the transistor is turned off, which blocks the current flow. This results in the increased static leakage current, and increases the static power dissipation. Management and suppression of static power is one of the major challenges to continued gate length reduction for higher performance.

Once the scaling of conventional bulk MOSFETs starts slowing down, the insertion of performance boosters, like novel materials and non-classical device structures, will be necessary to continue to improve performance.

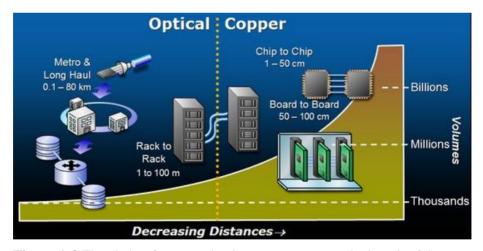

**Figure 1-3** The chain of communication systems versus the length of the interconnection and the business volume of the corresponding technology.

(Source: Intel)

On the other hand, while individual logic elements have become significantly smaller and faster, computational speed is limited by the communication between different parts of digital systems. This bottle neck is identified as one of the grand challenges in the progress of integrated electronics.

**Figure 1-4.** Illustration of types of optical and electrical propagation and their velocities [11]

Since the introduction of low-loss silica fibers for optical communications, optics has been dominating the long haul communications and it has consistently made its way down to short distance (Figure 1-3). There are several benefits for replacing conventional electrical cables with optics. Signals in both optical and electrical links are carried by electromagnetic waves. Information in typical electrical wires such as coaxial cables propagates almost at the velocity of light similar to that in optical links as illustrated in Figure 1-4. However, with increased modulation frequencies, the traditional electrical wires are becoming increasingly resistive and the signals moves at a slower rate due to dissipative wave propagation.

An excellent review of the potential benefits offered by optical interconnections is presented in [11] based on the fundamental physical differences of the higher frequency, shorter wavelength and larger photon energy of optics compared to electrical interconnections. Optics has negligible propagation loss from large bandwidth signals because the carrier frequency of light is very high compared to any practical modulation frequency. On the other hand, electrical interconnects suffer from significant signal distortion and frequency dependent cross-talk at high modulation frequencies. Owing to the short optical pulses, optics provide increased time precision over electrical interconnects, and this leads to the ability to transmit multi-channels down a single optical link thanks to wavelength division multiplexing. Furthermore, for optics, it is relatively easy to guide optical wave. The transmitted signal can be confined into the material boundaries of the guiding medium owing to the small waveguide of the optical signals. Additionally, due to the quantum nature of the physical processes, optics does not suffer from the impedance mismatching problem, which is quite challenging for electronics. While electronic devices have high impedance and low capacitance, the communication between such devices rely on low impedance and high capacitance transmission lines. In electronics, line drivers are used to match the impedance, which increase power dissipation and chip area at high operation frequencies. On the other hand, for the optics, the classical field or voltage is irrelevant.

#### 1.2. Si and III-V material properties

The high carrier mobility of Ge and III-V materials make them attractive in fabricating future CMOS devices. Meanwhile, there are many drawbacks associated with these materials. The most striking one is that these materials

do not have a stable and high-quality native oxide that can act as a natural surface passivation layer. This is the reason Si has become the dominant material in CMOS industry despite the first transistor being made on Ge substrates at Bell Labs in 1947 [12]. The lack of high-quality native oxides requires additional efforts in developing other surface passivation dielectrics [13-16]. One of successful passivation layers for Ge pMOS is a few monolayer (ML) thick Si cap layer which mimics the Si substrate and gives high-quality SiO2 passivation layer [15]. In contrast, III-V passivation is much more complicated and less successful even though a great deal of efforts have been dedicated to this field [14,17].

Table 1-1. Physical properties of common group IV and III-V semiconductors [5].

|                                              |                          | Si     | Ge     | GaP    | InP    | GaAs   | InAs   | GaSb   | InSb    |

|----------------------------------------------|--------------------------|--------|--------|--------|--------|--------|--------|--------|---------|

| Electron mobility (cm <sup>2</sup> /Vs) 300K |                          | 1450   | 3800   | 160    | 5400   | 9000   | 330000 | 7620   | 77000   |

| Electron effective mass(/m <sub>o</sub> ) 4K | $\mathbf{m}_{\parallel}$ | 0.19   | 0.0823 | 0.21   | 0.808  | 0.0662 | 0.23   | 0.039  | 0.01359 |

| Electron effective mass(/m <sub>0</sub> ) 4K | mı                       | 0.916  | 1.59   | 7.25   |        |        |        |        |         |

| Hole mobility (cm <sup>2</sup> /Vs) 300K     |                          | 370    | 1800   | 135    | 190    | 400    | 450    | 680    | 850     |

| TI-1606                                      | $m_{hh}$                 | 0.537  | 0.0438 | 0.67   | 0.455  | 0.34   | 0.57   | 0.3    | 0.032   |

| Hole effective mass (/m <sub>0</sub> ) 4K    | $m_{lh}$                 | 0.153  | 0.284  | 0.17   | 0.121  | 0.094  | 0.35   | 0.042  | 0.016   |

| Band gap (eV) (300K)                         |                          | 1.1242 | 0.664  | 2.272  | 1.344  | 1.424  | 0.354  | 0.75   | 0.18    |

| Band gap (eV) (0K)                           |                          | 1.17   | 0.785  | 2.35   | 1.4236 | 1.519  | 0.418  | 0.822  | 0.2352  |

| Lattice constant nm (300K)                   |                          | 0.5431 | 0.5658 | 0.5451 | 0.5869 | 0.5654 | 0.6058 | 0.6096 | 0.6479  |

| Melting point (K)                            |                          | 1687   | 1210   | 1749   | 1327   | 1511   | 1221   | 991    | 800     |

| Debye T (K)                                  |                          | 636    | 374    | 445    | 321    | 344    | 247    | 266    | 203     |

| Thermal conductivity (W/cmK) 300K            |                          | 1.56   | 0.4    | 0.77   | 0.7    | 0.455  | 0.3    | 0.4    | 0.4     |

| Thermal expansion coefficient (ppm) 300K     |                          | 2.92   | 5.9    | 4.65   | 4.75   | 6      | 4.52   | 7.75   | 5.37    |

| Density (g/cm <sup>3</sup> ) 300K            |                          | 2.329  | 5.3234 | 4.138  | 4.81   | 5.3161 | 5.66   | 7.75   | 5.7747  |

The second challenge of using Ge and III-V materials for CMOS device fabrication is the process and cost issue. Due to the mechanical properties and thermal expansion issues (see Table 1-1), large scale wafer substrates are not commercially available. The largest Ge substrates available is 200 mm and the mainstream III-V wafer size is 100 mm while 300 mm Si wafers are routinely used in the state-of-the-art Si fabs. Small wafer substrates do not allow cost-effective high volume production. Thirdly, these wafers are not

compatible with the Si processing equipments. The higher densities and poor mechanical properties of Ge and III-V materials make them much more fragile than Si. Fourthly, Ge and III-V materials are less abundant than Si, resulting in prohibitive wafer costs.

**Figure 1-5.** The fcc crystal structures of different semiconductors: (a) The diamond crystal structure. All atoms are of the same type (e.g., Si). (b) The zinc blende crystal structure. The white and black atoms belong to the two different sublattices (e.g., Ga and As) [20].

From the above-mentioned issues, it is technologically and economically challenging to use Ge and III-V bulk substrates for device fabrication. Fortunately, all these challenges except the surface passiviation can be addressed by heteroepitaxial growth on Si substrates. Si has the diamond crystal structure as Si (Figure 1-5a). III-arsenides and III-phosphides have zincblende crystal structure which has the same atomic stacking as diamond except that the cations and anions are stacked alternately (Figure 1-5b). The same crystal structure makes it possible to grow Ge or III-V compounds on Si substrates epitaxially. Generally, thin (typically <1µm) layers are grown on Si substrates and the devices can be made on the epitaxial layers. These thin

layers overcome the high substrate cost and the processing equipment incompatibility. Furthermore, when SAG is performed, both Ge and III-V materials can be grown on one Si substrate in a way that both pMOS and nMOS can be made adjacent to each other to give CMOS function. SAG allows us to use Si wafers with standard shallow trench isolation (STI) that gives good lateral electrical isolation. An integration scheme is shown in Figure 1-6 [3, 18]. The nMOS III-V channel is grown on top of a strain-relaxed buffer layer that has the same lattice constant as the bulk material. The pMOS device is made on a strain-relaxed Ge buffer layer. To ultimately boost the device performance, source and drain engineering can be employed [18]. There are other options in the details of device structure design such as high electron mobility transistors (HEMT) [19]. Therefore, device quality strain-relaxed Ge and III-V buffer layers provide a platform for the subsequent device engineering.

**Figure 1-6.** Example of heterointegration of Ge and III-V MOS transistors on a Si substrate. Different device structures can be made on the strain-relaxed III-V and Ge buffer layers. On the left, a quantum-well device architecture is shown and the III-V barrier layer is inserted to block the source-to-drain leakage current. On the right shown is Ge channel strain engineering by embedded source and drain [37].

#### 1.3. Thesis organization

This thesis is organized as following. Chapter 2 deals with the growth and characterization and chapter 3 is GaP and InP blanket growth on Si (001) substrates, chapter 4 and 5 are about InP SAG epitaxial growth. The conclusions and future work are summarized in chapter 6.

Chapter 2 starts with a short introduction to the growth and characterization of InP on Si substrates, including the MOCVD system and principle. Then the characterizations of III-V on Si substrates are briefly discussed followed.

Chapter 3 discusses GaP blanket growth on Si (001) substrates that have been developed within the frame of this PhD work by optimization of several growth parameters. One approach for growing GaP on Si (001) substrates is to use the high V/III ratio and the low growth.

In chapter 4, InP layers were grown on Si(001) and Ge(001) substrates by using metalorganic chemical vapor deposition (MOCVD). Two-step InP growth on Si(001) was optimized by controlling growth conditions such as growth temperature, V/III ratio and thickness. Finally, high quality InP top layers using a thin GaP buffer layer and inserted In<sub>0.6</sub>Ga<sub>0.4</sub>As strained layers on Si (001) substrates.

In chapter 5, we investigated SAG of InP layers on patterned Si substrates with InP/GaP buffer layers at various growth temperatures ranging from 500 °C to 650 °C. In order to grow high quality InP, a thin GaP buffer layer was grown on stepped sidewall surfaces of etched Si. The different growth temperature resulted in different top surfaces. The high quality InP layer with smooth surface can be attributed to the dislocation necking effect together with the formation of void. Finally we demonstrated the formation of InGaAs/InP heterostructures using the suggested InP templates, which can be

used in applications of electronic devices.

In the end, the summary of this PhD work and future work are given in chapter 6. High-quality InP virtual substrates are obtained in  $SiN_x$  trenches, which enables the integration III-V MOSFET devices and optoelectronic devices on standard Si (001) substrates. The remaining interest in further exploring this subject is given as the future work.

#### 1.4. References

- [1] http://www.itrs.net.

- [2] http://www.intel.com/technology/mooreslaw/.

- [3]M. Heyns, M. Meuris, and M. Caymax, ECS Trans. 3 (7), 511 (2006).

- [4] E. Fitzgerald, M. Bulsara, Y. Bai, C. Cheng, W. K. Liu, D. Lubyshev, J. M. Fastenau, Y. Wu, M. Urtega, W. Ha, J. Bergman, B. Brar, C. Drazek, N. Daval, F. Leterte, W. E. Hoke, J. R. LaRoche, K. J. Herrick, and T. E. Kazior, *ECS Trans.* **16** (**10**), 1015 (2008).

- [5] O. Madelung, Semiconductors: Data Handbook (Springer, 2004).

- [6] M. Heyns, C. Adelmann, G. Brammertz, D. Brunco, M. Caymax, B. De Jaeger, A. Delabie, G. Eneman, M. Houssa, D. Lin, K. Martens, C. Merckling, M. Meuris, J. Mittard, J. Penaud, G. Pourtois, M. Scarrozza, E. Simoen, S. Sioncke, and W. E. Wang, *10th Int. Conf. Ult. Integ. of Si*, 83 (2009).

- [7] D. J. Dumin, J. Cryst. Growth, **8**, 33 (1971).

- [8] Z. M. Sze and N. K. K., Physics of Semiconductor Devices, 3rd ed. (John Wiley & Sons, Inc., New Jersey, 2007).

- [9] G. E. Moore, "No exponential is forever: but "forever" can be delayed! [semiconductor industry]", in Digest of Technical Papers IEEE *International Solid-State Circuits Conference*, pp. 20-23 (2003).

- [10] E. J. Nowak, "Maintaining the benefits of CMOS scaling when scaling bogs down", in *IBM Journal of Research and Development*, **46**(2/3), pp. 169-180 (2002).

- [11] D. A. B. Miller, "Physical reasons for optical interconnection," *Int. J. Optoelectron.* **11**, 155-168 (1997).

- [12] C.-T. Sah, Fundamentals of Solide State Electronics (World Scientific Publishing Co. Pte. Ltd., Singapore, 1991).

- [13] M. Kobayashi, T. Irisawa, B. M. Kope, Y. Sun, K. Saraswat, H. S. P.

- Wong, P. Pianetta, and Y. Nishi, Symp. VLSI Techn., 76 (2009).

- [14] J. Kwo and M. Hong, *J. Cryst. Growth* **311**, 1944 (2009).

- [15] J. Mitard, B. De Jaeger, F. E. Leys, G. Hellings, K. Martens, G. Eneman, D. P. Brunco, R. Loo, J. C. Lin, D. Shamiryan, T. Vandeweyer, G. Winderickx, E. Vrancken, C. H. Yu, K. De Meyer, M. Caymax, L. Pantisano, M. Meuris, and M. M. Heyns, *IEDM*, **873** (2008).

- [16] J. Mitard, C. Shea, B. De Jaeger, A. Pristera, G. Wang, M. Houssa, G. Eneman, G. Hellings, W. E. Wang, J. C. Lin, F. E. Leys, R. Loo, G. Windericks, E. Vrancken, A. Stesmans, K. De Meyer, M. Caymax, M. Pantisano, M. Meuris, and M. Heyns, in 2009 Symp. on *VLSI Tech.*, Kyoto, Japan, 2009.

- [17] M. W. Hong, J. R. Kwo, P. C. Tsai, Y. C. Chang, M. L. Huang, C. P. Chen, and T. D. Lin, *J. J. Appl. Phys.* **46**, 3167 (2007).

- [18] R. Loo, G. Wang, L. Souriau, J. C. Lin, S. Takeuchi, G. Brammertz, and M. Caymax, *J. Electrochem. Soc.* **157**, H13 (2010).

- [19] A. Kasamatsu, K. Kasai, K. Hikosaka, T. Matsui, and T. Mimura, *Appl. Surf. Sci.* **224**, 382 (2004).

- [20] J. E. Ayers: Heteroepitaxy of semiconductors: theory, growth, and characterization, CRC Press Taylor & Francis Group, (2007)

# **Chapter 2**

Growth and characterization of InP on Si

#### 2.1. Challenges of InP growth on Si

Though InP has its advantages over Si, it has some drawbacks, for example, high cost and mechanical weakness compared with Si. Furthermore, today's industry is much concentrated in Si technology. So, to exploit advantages of InP on Si-based platform, monolithic integration of InP on Si is needed, and InP growth technology on Si would be a starting point to the monolithic integration. However, the lattice mismatch between InP and Si causes much problem in growing InP on Si.

#### 2.1.1. Lattice mismatch

If a material, for example, Si is to be grown on the same material (homoepitaxy), since lattice constants of the starting material and the epi material are same, high quality layers can be achieved, without incurring significant defects like threading dislocations. In Fig. 2-1, shown against the background of the lattice constant dependences of the band gaps of the group IV semiconductor materials (Si and Ge) and III-V compounds are the crystallographic transition pathways from silicon to InP, on the latter of which GaAs or Ge type heterosystems can be grown by known techniques, and then various devices can be created on their bases. Even if the two materials are different (hetero-epitaxy), if they have the same lattice constant, equally high quality epi-layers can be achieved. Growth of In<sub>0.53</sub>Ga<sub>0.47</sub>As on InP and In<sub>0.52</sub>Al<sub>0.48</sub>As on InP are examples for hetero-epitaxial growth with same lattice constants.

Difficulties rise if the lattice constants for the substrate and the epi material are different. If the mismatch is only a few percent and the layer is thin, the epitaxial layer grows with a lattice constant in compliance along the surface plan as its lattice constant adapts to the seed crystal. Such a layer is called pseudomorphic because it is not lattice-matched to the substrate without incurring strain. However, if the epitaxial layer exceeds a critical thickness (t<sub>c</sub>), which depends on the lattice mismatch, the strain energy leads to formation of defects called misfit dislocation. In our research, we want to grow high quality indium phosphide layers on silicon. However, indium phosphide's lattice constant is 5.868 Å whereas silicon's is 5.4307 Å [1]. Thus the percent difference is 8.052%.

**Figure 2-1** Band gap energy and lattice constant of various III-V and IV semiconductors at room temperature [3].

If the mismatch is considerable and relatively thick epi-layer is needed, additional epitaxial growth techniques are needed. As one starts to grow InP on Si, the new InP layer will conform to the lattice spacing of the Si substrate. The InP layer is now compressively strained as the lattice is reduced. So below a certain thickness, one can grow defect-free compressively strained InP on Si. This thickness has been shown to be around several nm. As one continues to grow thicker layers, it is energetically favorable to relieve the strain by forming dislocations at the InP/Si interface. In addition, the islanding can occur as an additional means of reducing the elastic strain energy of the film [2]. This leads to rough surfaces unsuitable for device applications.

#### 2.1.2. Thermal mismatch

Growth of InP on Si or III-V in general, takes place at high temperature typically around 600°C which demands a wide temperature range of cooling to room temperature. As a consequence the lattice constants of InP and Si are subjected to change differently due to the difference in the thermal expansion of the two materials. The thermal expansion coefficient difference induces significant strain in the layer, bending of the substrate and incase of tensile stress cracks in the epitaxial layer. The thermal strain induced by the thermal expansion coefficient difference is given by [4],

$$\varepsilon = \int_{T_0}^{T_g} (\alpha_s - \alpha_l) dT$$

(2.1)

where  $T_0$  is the reference temperature which is normally room temperature (300K),  $T_0$  is growth temperature and  $\alpha_s$  and  $\alpha_l$  are thermal expansion coefficients of substrate and layer, respectively. The thermal expansion coefficients of  $I_0$ ,  $I_$

#### 2.1.3. Defects Associated to Polar on Non-Polar Epitaxy

An unavoidable issue of III-V/Si heteroepitaxy is the integration of polar and non-polar heterointerface. However, a complete understanding of polar on nonpolar epitaxy is a critical challenge for successful III-V semiconductor compound integration. Silicon, being made up of a single atomic species, forming purely covalent chemical bonds with zero net dipole moments, is a non-polar crystalline material. On the other hand, III-V like InAs, made up of both In and As atoms whose ionic bonds possess a significant net dipole moment, is a so-called polar crystalline material; the interface between two such materials presents a number of challenges that must be taken into account. It was proposed that if the first III-V atomic plane adjacent to the silicon bulk substrate were a perfect atomic plane, a large electrical charge would be induced [7]. To neutralize the interface charge, rearrangement of

atoms may result, creating an environment of III-V island formations. Growing at low temperature with a layer by-layer growth mode, referred to as migration enhanced epitaxy (MEE), was used to address this issue. This growth technique proved indispensable for previous successful GaAs/Ge work [8]. The polar/non-polar charge neutrality dilemma is nearly impossible to monitor except by observation of possible post-epitaxy effects, such as the formation of interfacial planar defects such as: antiphase domain boundaries (APBs), stacking faults (SFs) and microtwin (MT) defects. The goal of this work, therefore, is the suppression of these heterointerface-driven defects through the proper surface preparation of the Si substrates and optimization of the growth and nucleation conditions of the III-V heteroepitaxial layers.

#### 2.1.3.1. Autodoping by interdiffusion

Additional di-culties may arise when atomic species are interchanged at IIIV/Si interfaces. Interdiusion of atoms across a hetero-interface is possible, when enough atoms are thermally excited to a mobilize limit within the crystals for atomic exchange mechanism [9]. However, if the III-V/Si interface consists of III-Si or V-Si bonds, then electrical neutrality is lost and the interface becomes polarized. Therefore, inter-diffusion between III-V/Si can lead to an effect known as autodoping, due to the fact that group-III and group-V materials are common p-type and n-type dopants of silicon, respectively. On the other hand, silicon species are amphoteric in the zinc blende crystal structure through their preference for the group-III sites. They can act as an n-type dopant for the III-V material. Inter-diffusion by itself presents the additional complication of unwanted autodoping across the interface. Autodoping tends to produce undesired doping proles, which can

hinder devices performance. So keeping the diffusion at the interface to minimum is a priority. In practice, interface polarity is likely compensated during growth by the presence of charged point defects and dislocation cores as well as some atomic exchange a cross the interface [12]. Previous work in the GaAs/Ge or GaP/Si systems indicated that a multi-stage growth approach involving initial low-temperature MEE GaAs growth mode, prior to a conventional high-temperature heteroepitaxial MBE growth mode, su-ciently suppressed autodoping between the two materials [8]. A similar approach was examined for the GaP/Si system and will be discussed in the experimental part of the growth in this thesis work.

#### 2.1.3.2. Antiphase domain boundary

A number of planar crystal defects are encountered in III-V semiconductor heteroepitaxy on silicon, as it was discussed before. The far greater concern during III-V/Si heteroepitaxy is the possibility of antiphase disorder formation. Antiphase (domain) boundaries (APBs) are one type of the planar defects that will be introduced through the growth of compound semiconductor materials on an elemental crystal, such as the case of InAs/Si, can result in the formation of crystalline subdomains referred to as anti-phase domains and anti-phase domain boundaries (APBs) also known as, inversion domains boundaries (IDBs) [10].

**Figure 2-2** Schematic diagram of anti-phase domains boundaries in InAs formed by a single-atom step on the silicon substrate surface. Figure modified according to reference [11].

There are a few theoretical reasons for their formation. During growth initiation of a compound material, two crystal domains can form independently of one another, each the result of different nucleation species like in In vs. As; the planes at which the domains of reversed polarity meet, referred to as APBs, possess In-In and/or As-As bonds instead of proper In-As bonds, as in the case of GaP/Si system [12].

**Figure 2-3** Schematic diagram of anti-phase domains boundaries in InAs formed by a single-atom step on the silicon substrate surface. Figure modified according to reference [11]

In another case, APDs can be formed if the elemental crystal (i.e. silicon) has single atomic steps on its surface as shown in Fig. 2.2. A surface variation such as an atomic-level step on the Si substrate can cause the III-V layer above this step to rotate its orientation, and thus lead to the formation of a propagating boundary layer between two distinct III-V domains [13].

Due to the lower symmetry of the polar semiconductor, it can grow with one of two (nonequivalent) crystal orientations on the nonpolar substrate. The boundaries between regions having these two orientations will also result in the formation of inverted domain boundaries. The nature of the chemical bonding across the APBs causes them to be electrically active, which directly relates to the degradation in material quality. Experiments involving time resolved photoluminescence of GaAs/Ge system demonstrated a large decrease in minority carrier lifetime with a large increase in interface recombination rates in the samples containing the APD defects versus those without [10]. Generally, APDs are expected to introduce states within the energy gap and give rise to non-radiative recombination. They therefore degrade the e-ciencies of LEDs and cause excess leakage in p-n junctions. Avoiding the APDs defect is tricky and demands control of the substrate surface structure prior to III-V growth, but it has been accomplished in systems like GaAs/Ge [8, 14]. Early research into direct III-V/Si MBE integration focused on high indexed Si substrates with a surface atomic structure providing bonding sites for alternating group-III and V-atoms, creating an electrically neutral interface to help preventing the formation of APDs [15]. However, many other authors have investigated surface preparations recipes, and reported many nucleation conditions which can minimize or eliminate the formation of APDs for many III-V/IV systems like GaAs/Si, GaP/Si and GaAs/Ge [10,12,16]. Another method has been provided efficient APDs suppression [17], utilizes silicon substrates whose surfaces are polished such that the surface atomic plane is intentionally misoriented a few degrees toward an orthogonal [110] direction away from the (001) surface in order to induce a double atomic step reconstruction (DASR) as schematically shown in Fig. 2.2. In contrast to the irregular single steps of nominally on-axis (001) Si surface, deliberately mis-orienting the substrate toward [110] direction introduces a regular array of single steps running the [110] direction. These regular arrays of single steps line up in a manner of proper atomic positions, with planar atomic growth occurring in the (001) direction, as illustrated in Fig.2.2. However, as the off-cut angle is increased, the density of steps increases and the average terrace width w decreases according to Eq. 2.2. Where h is the height of the step.

$$w = h \tan^{-1}(\emptyset)$$

At high temperatures and under ultra-high vacuum conditions, off-cut (001) surfaces are known to transform from their initial single-stepped two-domains configuration to a lower energy single-domain configuration of double steps reconstruction [18-19]. Double steps surfaces preserve sublattice orientation between neighboring terraces, thereby facilitating APDs-free III-V epitaxial growth on silicon substrates. In the event that single-stepped two-domains surface is not achieved, substrate o-cut may also serve to limit the extent of APDs in zinc-blende crystal structures by self-annihilation as a

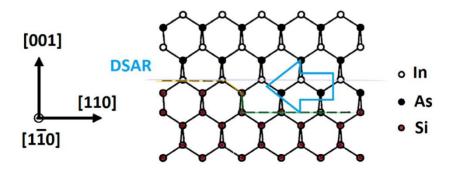

**Figure 2-4** Self-annihilation anti-phase domains on [011] plane in a (001) zinc blende semiconductor by the close proximity of bonding of two APD faces. Figure modified according to reference [9].

Here, APDs annihilation occurs at the line of intersection of the two APD planes, which lies along a [110] direction parallel to the interface [20]. Annihilation reactions can also occur between APDs on [011] planes [9], which can meet along a [010] direction, as shown in Fig. 2-4. The high single density afforded by substrate misorientation decreases the spacing between neighboring APDs, hence increasing the probability that neighboring APDs will find one another and form small close domains. Many reports of single

domain GaAs/Si and GaAs/Ge in the literature actually refer to initial two domain III-V growth, followed by rapid annihilation of APDs near the interface, leaving a single dominant domain [21-23]. In the limit of vicinal (001) substrates, however, the spacing between adjacent APDs is thought to be quite large such that self-annihilation near the interface of single-domain becomes less likely [17].

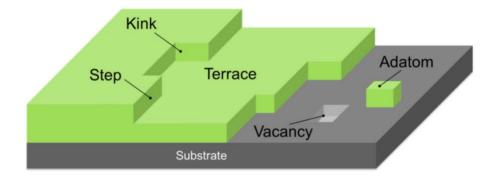

#### 2.1.3.3. Stacking Faults

Stacking faults (SFs) are produced when the regular arrangements of layer atoms are disturbed. A perfect crystal can be considered a stack of atomic layers occurring in a particular sequence. The stacking of the zinc blende structure of III-V semiconductor in the [111] direction can be described as ABCABC. A stacking fault can occur with an extra plane of atoms inserted into the stacking sequence, as in ABCBABC, a B layer is inserted. This is called an extrinsic stacking fault.

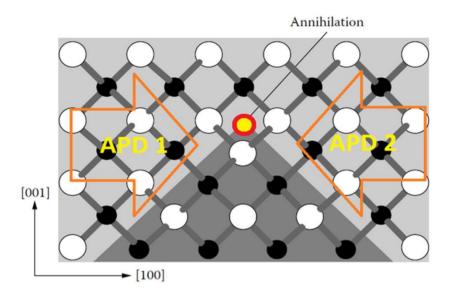

Another possible type of stacking fault involves the removal of one plane, as in ABCBC, an A layer is removed and is called an intrinsic stacking fault [10]. Stacking faults are planar defects that are bounded on either side by partial dislocations. Fig. 2-5 shows a high resolution transmission electron microscopy image of SFs defects and SF loops found in InAs QDs embedded in Si matrix system, grown in our MOCVD system. It was also reported for GaP/Si system that initial planar nucleation of GaP/Si is difficult to control, often creating many small faceted GaP islands. Coalescence of these GaP islands often results in the formation of SFs, which then propagate throughout the entire GaP layer [24]. Later reports indicated that SFs could

be suppressed by forcing a 2D growth mode for the first few layers of GaP using migration enhanced epitaxy (MEE) for the nucleation process on Si substrate. Thus, it is essential to carefully monitor polar/non-polar of III-V/Si interface and ensure a low density of SFs.

**Figure 2-5** HR-TEM image of stacking faults defects found in InP/GaP/Si system.

#### **2.1.3.4.** Micro twins

Another type of planar defect resulting from a change in the stacking sequence is the micro twins (MTs). In diamond and zinc blende crystals,

twinning occurs almost exclusively on [111] planes. Using the stacking notation used in the last section (Sec. 2.1.3.3), a twin boundary in a diamond or zinc blende crystal may be denoted as ABCABACBA. There is a change in crystal orientation at the twinning plane. Here the normal crystal and its twin share a single plane of atoms (the twinning plane or composition plane) and there is reflection symmetry about the twinning plane as shown in Fig.2-6. In other words, the MTs defect occurs when the stacking faults sequence is disturbed in such a way as to create a mirror image of itself, as in ABCABCCBAACBA [10]. Twinning involves a change in long-range order of the crystal; it therefore cannot result from the simple insertion or removal of an atomic plane, as in the case of the stacking fault. Therefore, twins cannot be created by the glide of dislocations. Instead, twinning occurs during crystal growth, either bulk growth or heteroepitaxy.

Finding ways to reduce the density of dislocations at a given mismatch strain level is an important goal for successful strained-layer heteroepitaxy. As mentioned before, dislocations and defects can act as non-radiative recombination centers in optoelectronic devices, because the localized midbandgap energy levels in the dislocations cores will act as highly efficient trap states for injected minority carriers [26].

A great volume of research activities has already been dedicated to the various barriers to III-V integration on silicon. Nevertheless, it has yet to be shown the quality of III-V on Si material can offer reliability and performance demanded optoelectronic and other device applications. In this research work, a new approach for III-V on silicon heterepitaxy based on self-assembled and localized growth of nanostructures like quantum dots and dashes will be investigated. The idea is to minimize the above mentioned problems of the formation of dislocations during the growth of relaxation

layers. However, the materials integration processes were conducted by the means of the epitaxial growth of III-V quantum dots and dashes on silicon substrates via MOCVD technique, using the most challenging materials integration approach, by limiting the III-V material to the active region.

**Figure 2-6** HRTEM image of micro twin and stacking faults defects (S1,S2) in GaP/Si system. Figure modified according to reference [24].

# **2.2.** Metalorganic Chemical Vapor Deposition (MOCVD) system

#### 2.2.1. Overview

Epitaxial growth is defined as a precise oriented growth of a single crystal material upon the surface of a single crystal substrate. Growth of a layer with the same kind of atoms as are in the substrate is called homoepitaxy, and growth with a different kind of atoms is called heteroepitaxy. The growth of epitaxial films can be done by a number of methods including liquid phase epitaxy (LPE), molecular beam epitaxy (MBE), vapor-phase epitaxy (VPE), hydride vapor-phase epitaxy (HVPE), and metal-organic vapor-phase epitaxy (MOVPE) or metal-organic chemical vapor deposition (MOCVD). Such methods for the epitaxial growth are important and are used to produce high quality single crystal layers with low defect density and complex heterostructures for electrical and optical applications. In particular, MOVPE is one of the leading techniques for the production of III-V materials for electric and photonic devices. In this technique, III and V metal–organic (MO) and hydride molecules are used for growing III–V compound semiconductors. These source molecules are provided to growth substrate with purified hydrogen or nitrogen gas and diffuse near the surface of the growth substrate. These molecules are thermally decomposed and then chemically react near the surface of growing substrate. Atoms are incorporated at certain positions on the surface in relationship to the underlying crystal structure. For instance,

trimethylgallium (TMGa), Ga(CH<sub>3</sub>)<sub>3</sub>, and arsine, AsH<sub>3</sub>, are introduced above a heated GaAs substrate, an epitaxial film of GaAs can grow according to the following reaction,

$$Ga(CH_3)_3(g) + AsH_3(g) \rightarrow GaAs(s) + 3CH_4$$

(2-3)

where (g) and (s) represent "gas" and "solid" phase, respectively.

The major attraction of MOCVD relative to the other techniques is that the MOCVD is suitable for mass production. Moreover, this single growth technique can be used to produce virtually all of the III–V materials and structures required for the cutting edge of electronic and photonic devices including AlGaInP for red or yellow light–emitting diodes (LEDs), III–V nitrides for blue LEDs, and III–V highest efficiency tandem solar cells.

Figure 2-7 Schematic illustration of the MOCVD system [from Aixtron].

#### 2.2.2. MOCVD system

This section explains the MOCVD system used in this work. Figure 2-7 shows the schematic illustration of the MOCVD system. The essential components are the gas delivery system, the reactor and temperature controller, and the low pressure pumping system. All growth in this work was carried out with a horizontal low–pressure MOCVD system.

First, we describe about gas delivery system. Palladium diffused purified hydrogen (H2) is used as a carrier gas. The carrier gas transport the source gases flowing over the heated susceptor and substrate to the exhaust as shown in Figure 2-7. The vapor—phase source molecules are fed to the reactor in separate lines for metal—organic (MO) source and gas source. The MO sources are provided from bubblers and gas sources are provided from gas cylinders.

**Figure 2-8** (a) Layout of the AIX 2400 G3 susceptor in the 8×3 inch. (b) Photo of the reactor chamber of the AIX 2400 G3 in the 8×3 inch configuration.

Fig. 2-8 shows a schematic of the susceptor of the AIX 2400 G3 in the 8×2 inch (a) and a corresponding photo of the reactor chamber (b). The gases enter the reactor chamber through the central inlet in the reactor lid (not visible in the photo) and stream radially outward across the deposition zone. The susceptor is heated by RF induction heating from below and rotates at rotation frequencies of typically 10 rpm. In addition the wafer discs are rotating utilizing AIXTRON's patented Gas Foil Rotation technique. This double rotation insures highest uniformities.

#### 2.2.3. Source Molecules

The MO source materials for group–III are trimethylgallium (TMGa), trimethylindium (TMIn), trimethylaluminum (TMAl). PH<sub>3</sub> and AsH<sub>3</sub> are used for the gas source materials for group–V. Silane (SiH4, gas) and diethylzinc (DEZn, MO) are used for n–type and p–type doping, respectively.

**Figure 2-9** (a) Schematic illustration of the line for metal—organic (MO) source provided by bubblers [37].

The MO sources are provided in the bubblers, which are kept at a certain temperature by the thermal bath to control and maintain the partial pressure of material supply as shown in Figure 2-9(a). The carrier gas is led through the liquid or solid source material in the bubbler. As a result, the carrier gas contained MO sources with saturated vapor pressure, which is controlled by the temperature of the bubbler, is provided to the reactor (Figure 2-9(b)).

The partial pressure of each MO sources fed to the reactor is determined by the carrier gas flow through the bubbler which is controlled by mass–flow controllers (MFCs). Pressure controller keeps a fixed pressure in the bubbler, and then, mixture of H<sub>2</sub> and MO down to the reactor pressure. The vapor pressure of a MO sources is a critical parameter used to control the precise concentration of MO sources entering the reactor, and subsequently the rate of deposition in the MOVPE process. Hence, an accurate evaluation of the vapor pressures of the MO sources is essential to the MOVPE process. The vapor pressure equation in linear logarithmic form,

$$log10PMO = B - A/T \tag{2-4}$$

has been found to be the most acceptable form for representing the vapor pressure of MO sources ( $P_{MO}$  (Torr)) in MOVPE, where T (K) is the absolute temperature of MO sources (or thermal bath) and A and B are the gas constant for each MO sources.

#### 2.2.4. Thermal decomposition of Source Molecules

Supplied metal-organic (MO) and gas sources are thermally decomposed by the heated temperature of susceptor near the surface of substrate. The decomposition behavior is dependent on the kinds of source material, and this factor is also important for the crystal growth. The thermal pyrolysis (or decomposition) of MO and gas sources has been studied [27-34]. Typically these studies monitor, optically or through mass spectrometry, the decrease in the concentration of a particular reactant as it passes through a SiO2 reactor. The temperature ranges for thermal pyrolysis for various MO and gas sources are summarized in Table 2–1.

**Table 2-1.** Thermal pyrolysis (or decomposition) of various metal-organic (MO) and gas sources [37].

|                  | Carrier gas<br>& Experimental condition | Pyrolysis range (°C) |           |

|------------------|-----------------------------------------|----------------------|-----------|

|                  |                                         | start                | completed |

| TMGa             | $H_2$                                   | 370                  | 470       |

| TMGa             | $H_2$                                   | 400                  | 580       |

| TMGa             | $N_2$                                   | 450                  | 570       |

| TMIn             | $H_2$                                   | ~ 250                | ~ 340     |

| TMIn             | $H_2$                                   | ~ 300                | ~ 340     |

| TMIn             | $N_2$                                   | ~ 340                | ~ 430     |

| $AsH_3$          | $H_2$                                   | 650                  | 750       |

| $AsH_3$          | $H_2$                                   | ~ 470                | ~ 640     |