# A Tool for Fast Mismatch Analysis of Analog Circuits

## R. Rodríguez-Macías, F.V. Fernández, A. Rodríguez-Vázquez, and J.L. Huertas

Dept. of Analog Circuit Design. Centro Nacional de Microelectrónica. Edificio CICA, Avda. Reina Mercedes s/n, 41012-Sevilla, Spain.

### ABSTRACT

A tool is presented that evaluates statistical deviations in performance characteristics of analog circuits, starting from statistical deviations in the technological parameters of MOS transistors. Performance is demonstrated via the analysis of a Miller OTA in two different configurations and a linearized CMOS transconductor. The CPU time is reduced by a factor of 25 to 90 with respect to conventional Monte Carlo simulation, while maintaining similar accuracy in the computations.

#### I. Introduction

The performance of analog cells may be severely deteriorated due to random fluctuations in the electrical parameters of their components: transistors, resistors and capacitors. Crucial features like offset, commonmode rejection ratio (CMRR), power-supply rejection ratio (PSRR), etc., are critically dependent on random-induced mismatches, and require careful design (equivalently sizing) to guarantee that specifications remain within tolerable margins for the largest possible number of circuit samples. However, due to the difficulties encountered in the modeling and evaluation of random fluctuations, this problem is usually handled by simply imposing conservative constraints in the design parameter space; e.g. the transistor area in a differential amplifier must be larger than say,  $100 \,\mu m^2$ . This leads to underexploitation of the performance potentials of the technologies. The optimization of the design procedure of analog cells under random fluctuations of the transistor parameters encompasses two different kinds of problems:

a) *Statistical modeling*, essentially the capture of statistical features of the components into parameterized models.

b) *Statistical simulation*, or the evaluation of the statistical features of the circuit performance induced by random variations of the electrical parameters.

The statistical modeling of MOS components has been covered by different authors in recent years [1-4]. Our contribution focuses not on the statistical modeling, but rather on statistical simulation. For modeling we rely on the proposal by Pelgrom [1] and more specifically, its further refinement as proposed in [2]. Such a model provides the variances of the electrical parameters of MOS devices as a function of their geometry and distances and covers correlations among electrical parameters.

According to [2] variances of the electrical parameters of a given device can be evaluated from its layout as

$$\sigma^2 (\Delta P) = \frac{A_p}{2WL} + S_p^2 D^2$$

(1)

where D denotes the distance from the device to a common reference point (the coordinate center); WL, its area; and  $A_p$  and  $S_p$  are fitting constants, different for each technological parameter subject to variation.

Let us focus on statistical simulation. Most analog designers use Monte Carlo analysis for this purpose. However, for large analog cells described at the electrical level this is very costly in CPU time. This precludes its usage inside iterative analog design procedures [5,6] and motivates looking for more efficient solutions [7,8,9]. Especially significant is the technique proposed by [9], based on a two-step linearization of the circuit performance. Precise results are obtained using the Monte Carlo method with that linearization. However, it assumes that circuit performances do not change significantly. Thus, the examples presented have no node with voltage standard deviation larger than 0.1V.

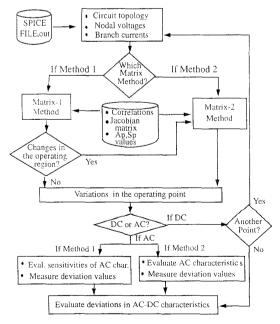

Our contribution aims to use matrix methods to perform statistical analysis of analog integrated circuits starting from correlated electrical model parameters. These have been calculated according to the modeling technique in [4]. In particular, two different matrix techniques have been developed and included in a computer tool whose flowchart is shown in Fig.1. Some significant features of the proposed method are:

1) Statistical features of branch currents and node voltages of any circuit can be evaluated, allowing easy extension to any electrical, DC or AC, performance.

2) Results adequately fit those obtained with Monte Carlo analysis using an electrical simulator.

3) Analysis time is minimized so that the method can be included in an optimization-based design system.

### II. Matrix-1 Technique

Variations in the transistor electrical parameters of a

given circuit induce changes in its node voltages and branch currents which can be calculated analytically. For a single transistor:

$$\sum_{k} \frac{\partial I}{\partial p_{k}} \Delta p_{k} + \frac{\partial I}{\partial V_{G}} \Delta V_{G} + \frac{\partial I}{\partial V_{D}} \Delta V_{D} + \frac{\partial I}{\partial V_{S}} \Delta V_{S} + \frac{\partial I}{\partial V_{B}} \Delta V_{B} = (2)$$

$$= \Delta I$$

where  $p_k$  represents the *k*-th electrical model parameter.

Equation (2) is more conveniently written as,

$$\frac{\partial I}{\partial V_G} \Delta V_G + \frac{\partial I}{\partial V_D} \Delta V_D + \frac{\partial I}{\partial V_S} \Delta V_S + \frac{\partial I}{\partial V_B} \Delta V_B - \Delta I =$$

$$= -\sum_k \frac{\partial I}{\partial p_k} \Delta p_k$$

(3)

For a given circuit containing N transistors, and assuming that M node voltage variations and N-M branch current variations are chosen as unknowns, the following linear equation system can be formulated:

A

$$\Delta \mathbf{x} = \mathbf{b} \tag{4}$$

where

$$\Delta \mathbf{x}_{j} = \begin{cases} \Delta V_{j} & \text{if } j \leq M \\ \Delta I_{j-M} & \text{if } j > M \end{cases} \mathbf{b}_{i} = -\sum_{k} \frac{\partial I_{i}}{\partial p_{k}} \Delta p_{k}$$

$$a_{ij} = \begin{cases} \frac{\partial I_{i}}{\partial V_{D}} \delta_{Dj} + \frac{\partial I_{i}}{\partial V_{G}} \delta_{Gj} + \frac{\partial I_{i}}{\partial V_{B}} \delta_{Bj} + \frac{\partial I_{i}}{\partial V_{S}} \delta_{Sj} & \text{if } j \leq M \end{cases}$$

(5)

$$-1 & \text{if } j > M \\ 0 & \text{otherwise} \end{cases}$$

where  $\delta_{xi}$  (x=D,G,S,B) is 1 if voltage V<sub>x</sub> and voltage V<sub>i</sub> correspond to the same physical node, or contrarily 0.

Cramer's rule is used to solve (4) and enables introducing correlations between transistors in the calculation. Hence, the *j*-th unknown is given by:

$$\Delta x_{j} = (A_{1j}b_{1} + A_{2j}b_{2} + \dots + A_{Nj}b_{N})\frac{1}{|4|}$$

(6)

where the coefficients  $A_{ij}$  are the cofactors of the elements in the *j*-th column.

Since we aim to determine variance, (6) must be multiplied by itself and integrated over the entire range of  $p_k$  parameters. Then, the variance results:

$$\sigma_{\Delta x_{j}}^{2} = \frac{1}{|A|^{2}} \sum_{k=1}^{N} \sum_{l=1}^{N} A_{kj} A_{lj} \rho_{b_{k} b_{j}} \sigma_{b_{k}} \sigma_{b_{j}} \sigma_{b_{j}}$$

(7)

where  $\sigma_b$  is given by:

$$\sigma_{b_{2}} = \sqrt{\sum_{r} \sum_{s} \frac{\partial I_{k} \, \partial I_{k}}{\partial p_{r} \partial p_{s}} \rho_{p,p_{s}} \sigma_{p_{r}} \sigma_{p_{r}}} \tag{8}$$

· . p

and the correlation between two entries of vector **b**:

$$\rho_{b_k b_l} = \begin{cases} 1 & , if \quad k = l \\ \frac{Dist_{M_k} Dist_{M_l} \sum_r \sum_s \frac{\partial I_k \partial I_l}{\partial p_r \partial p_s} \rho_{p_r p_s} S p_r S p_s}{\sigma_{b_k} \sigma_{b_l}}, & otherwise \end{cases}$$

$Dist_{Mk}$  and  $Dist_{Ml}$  represent distances to the coordinate center. The mean values are assumed equal to the nominal values.

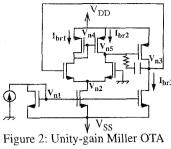

The OTA Miller in Fig.2, configured as an unitygain buffer, illustrates the performance of this method.

Table 1 shows the deviations in node voltages and branch currents obtained by Monte Carlo simulations (50 simulation instances) and those obtained by the Matrix-1 technique. As shown, the Matrix-1 technique reduces the CPU time by a factor of 90, without significant deviations in the analysis results as compared with those obtained by Monte Carlo simulations. The BSIM model was used considering variations of 16 parameters (and their correlations). Correlations of the electrical parameters in HSPICE simulations were calculated using the Principal Component Analysis technique [2].

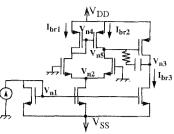

However, the Matrix-1 method does not consider eventual excursions of the transistor operating points through different operating regions (i.e. ohmic, saturation, etc.) and thus, may obtain inaccurate results for circuits containing nodes which swing over wide voltage intervals. For example, consider the open loop OTA Miller of Fig.3. Table 2 shows the branch currents and node voltages obtained by Monte Carlo analysis and the Matrix-1 technique. Since the circuit is in open loop, the voltage V<sub>n3</sub> changes over a wide range, taking transistors  $M_6$  and  $M_7$  out of their nominal operating regions and hence, introducing important analysis errors.

## III. Monte Carlo analysis on the system matrix: Matrix-2 Technique

The Matrix-2 technique solves these problems by performing a Monte-Carlo analysis on vector b. Parameters are generated according to their distribution. A nonlinear system is solved using the Newton-Raphson method and sensitivities are updated at each iteration.

Let us define a function  $F_i$  for each transistor:

$$_{i} \equiv I_{i} - I_{i} (V, p_{i})$$

$i = 1, 2, ..., N$  (10)

Circuit analysis consists in determining the voltages and currents which annul all  $F_i$ . A Monte Carlo simulation consists in solving the system for a large number of vectors of electrical parameters  $p_i$ .

The time is reduced considerably by using the system solution at the nominal point as an initial solution of the Newton-Raphson method. The function  $F_i$  at the nominal point is:

$$F_{ni} \equiv I_{ni} - I_{ni} (\mathbf{V}_n, \mathbf{p}_{ni})$$

$i = 1, 2, ..., N$  (11)

For another vector of electrical parameters  $p_i$ transistor currents can be approximated as:

$$I_{i} = I_{i}(\mathbf{V}, \mathbf{p}_{i}) = I_{i}(\mathbf{V}, \mathbf{p}_{ni}) + \sum \frac{\partial I_{i}}{\partial p_{ik}} \Big|_{\mathbf{x}_{n}} \Delta p_{ik}$$

(12)

where the derivative is evaluated at the nominal point. Its corresponding function  $F_i$  is then:

$$F_{i} \equiv I_{i} - I_{i} \left( \mathbf{V}, \mathbf{p}_{ni} \right) - \sum_{k} \frac{\partial I_{i}}{\partial p_{ik}} \bigg|_{\mathbf{x}_{n}} \Delta p_{ik}$$

(13)

Let us define a function  $G_i$  as the difference of  $F_i$  at the nominal point and  $F_i$  for another set of parameters  $p_i$ :

$$G_{i} \equiv F_{i} - F_{ni} =$$

$$= I_{i} - I_{ni} - I_{i} \left( \mathbf{V}, \mathbf{p}_{ni} \right) + I_{ni} \left( \mathbf{V}_{n}, \mathbf{p}_{ni} \right) - \sum_{k} \frac{\partial I_{i}}{\partial p_{ik}} \Big|_{\mathbf{x}_{k}} \Delta p_{ik}$$

(14)

Expanding  $G_i$  in Taylor series (first order) and making it equal zero to apply the Newton-Raphson method:

$$G_i(X_o + \delta X) = G_i(X_o) + \sum_j \frac{\partial}{\partial x_j} G_i(X) \Big|_{X_o} \delta x_j = 0$$

(15)

Applying (15) to (14) and reordering terms obtains in matrix notation. 7

. \_

$$\mathbf{A} \begin{bmatrix} \boldsymbol{\delta} & (\Delta \mathbf{x}) \end{bmatrix} = \\ = \left[ -\sum_{k} \frac{\partial I_{i}}{\partial p_{ik}} \right]_{x_{n}} \Delta p_{k} + I_{i} \left( \mathbf{V}_{n} + \Delta \mathbf{V}, \mathbf{p}_{ni} \right) - I_{ni} \left( \mathbf{V}_{n}, \mathbf{p}_{ni} \right) - \Delta I_{i} \right]$$

(16)

where A is defined as in (5) and  $\Delta x$  is the vector of unknown variations in voltages and currents.

In every iteration of the Newton-Raphson method the equation system is solved by LU decomposition and  $\Delta x$  is updated summing the solution  $\delta(\Delta x)$  to it. The iterative procedure continues until convergence.

Performing Monte Carlo analysis on the system matrix is more costly in CPU time than the Matrix-1 technique, but allows more accurate evaluation of variations, as shown in the OTA Miller results in Table 2. Moreover, a precise shape of the distribution is obtained.

# IV. Statistical features of DC Characteristics

Interesting DC characteristics are functions of node voltages and branch currents at one or more operating points. As their relationships are known, their statistical features are easily obtained starting from the voltage and current deviations at the operating points needed for their evaluation. The variation in a DC performance  $Y_i$  is expressed as:

$$Y_{i} = Y_{i} (\Delta x_{11}, ..., \Delta x_{1N}, ..., \Delta x_{M1}, ..., \Delta x_{MN})$$

(17)

where  $\Delta x_{ik}$  is the increase in the *k*-th unknown at the *j*-th operating point. Performances are usually determined by only one unknown; so, (17) is simplified to:

$$Y_i = Y_i (\Delta x_{r1}, \dots, \Delta x_{rN}) \tag{18}$$

Method-1 calculates performance sensitivities with respect to vector  $\Delta X$ , and the variance in then given by:

$$\sigma^{2} (\Delta P_{i}) = \sum_{k} \left( \frac{\partial P_{i}}{\partial x_{r}} \right|_{k} \right)^{2} \sigma_{\Delta - x_{r}i}^{2} + 2 \sum_{k} \sum_{l} \frac{\partial P_{i}}{\partial x_{r}} \left|_{k} \cdot \frac{\partial P_{i}}{\partial x_{r}} \right|_{l} \cdot \overline{\Delta x_{rk} \cdot \Delta x_{rl}}$$

(19)

where

$$\overline{\Delta x_{rk} \cdot \Delta x_{rl}} = \sum_{j} \sum_{m} A_{jr} A_{mr} \rho_{b_{jk} b_{ml}} \sigma_{b_{jk}} \sigma_{b_{ml}}$$

(20)

and  $\rho_{h}$ is defined similarly to (9).

If Method-2 is used, calculations are reduced to using conventional statistical estimators.

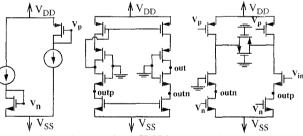

Table 3 shows experimental results for the linearized transconductor in Fig.4. The specifications considered are slope, linearity, input offset, and output offset. Methods 1 and 2 give similar results (except mean values which are assumed equal to the nominal ones in Method-1), because no node experiments large excursions. Speed with respect to Monte Carlo analysis is increased by a factor of around 25 with Method-2 and a factor of 80 using Method-1.

#### V. References

- M.J.M. Pelgrom, A.C.J. Duinmaijer, and A.P.G. Welbers: "Matching Properties of MOS Transistors", *IEEE J. of Solid-State Circuits*, Vol. 24, pp. 1433-1440, Oct. 1989. C. Michael and M. Ismail: "Statistical Modeling of Device [1]

- [2] C. Furchaer and M. Ismail: "Statistical Modeling of Device Mismatch for Analog MOS Integrated Circuits", *IEEE J. of Solid-State Circuits*, Vol. 27, pp.154-166, Feb. 1992.

J. Shyu, G.C. Temes, and K. Yao: "Random Error Effects in Matched MOS Capacitors and Current Sources", *IEEE J. of Solid-State Circuits*, Vol. 10, and Current Sources, *IEEE J. of*

- [3] Solid-State Circuits, Vol. 19, pp. 948-955, Dec. 1984.

- K. Lakshmikumar, R.A. Hadaway, and M.A. Copeland: "Characterization and Modeling of Mismatch in MOS Transistors for Precision Analog Design". *IEEE J. of Solid-State Circuits*, Vol.21, pp. 1057-1066, Dec. 1986. [4]

- F. Medeiro, F.V. Fernández, R. Domínquez and A. Rodríguez-Vázquez: "A Statistical Optimization-Based Approach for [5] Automated Sizing of Analog Cells", *Proc. ICCAD*, 1994. P. Maulik, R. Carley and D. Allstot: "Sizing of Cell-Level

- [6] Analog Circuits Using Constrained Optimization Techniques", *IEEE J. Solid-State Circuits*, Vol. 28, pp.233-241, March 1993. H. Su, C. Michael and M. Ismail: "Statistical Constrained

- [7] Optimization of Analog MOS Circuits Using Empirical Performance Models", *Proc. ISCAS*, Vol.1, pp.133-136, 1994.

- J. Oehm and K. Schumacher: "Quality Assurance and Upgrade of Analog Characteristics by Fast Mismatch Analysis option in Network Analysis Environment", *IEEE J. of Solid-State* [8] Circuits, Vol. 28, pp.865-871, July 1993.

- Z. Wang and S. W. Director: "An Efficient Yield Optimization [9] Method Using a Two Step Linear Approximation of Circuit Performance", *Proc. EDAC*, pp. 567-571, Feb. 1994

Figure 1: Flow diagram of the tool

Figure 3: Open-loop Miller OTA

| Node<br>voltages                     | MonteCarlo<br>(50 samples) | Matrix-1<br>technique | Node<br>voltages<br>& branch | Monte Carlo analysis<br>(50 samples) |         | Matrix-1 Matrix-2 technique (50 samples) |        |         |

|--------------------------------------|----------------------------|-----------------------|------------------------------|--------------------------------------|---------|------------------------------------------|--------|---------|

| & branch<br>currents                 | std dev                    | std dev               | currents                     | mean                                 | std dev | std dev                                  | mean   | std dev |

| V <sub>nI</sub>                      | 5.29mV                     | 4.39mV                | V <sub>ni</sub>              | -3.89V                               | 5.29mV  | 4.39mv                                   | -3.89V | 4.95mV  |

| V <sub>n2</sub>                      | 6.24mV                     | 5.26mV                | V <sub>n2</sub>              | -1.27V                               | 3.5mV   | 2.72mv                                   | -1.27V | 3.21mV  |

| V <sub>n3</sub>                      | 4.94mV                     | 3.15mV                | V <sub>n3</sub>              | -3.04V                               | 3.11V   | 0.4V                                     | -3.13V | 3.18V   |

| V <sub>n4</sub>                      | 4.23mV                     | 3.40mV                | V <sub>n4</sub>              | 4.11V                                | 4.39mV  | 3.34mV                                   | 4.11V  | 3.86mV  |

| V <sub>n4</sub>                      | 7.94mV                     | 7.43mV                | V <sub>n5</sub>              | 4.17V                                | 0.31V   | 0.2V                                     | 3.91V  | 0.33V   |

| I <sub>br1</sub>                     | 0.22µA                     | 0.22µA                | I <sub>br1</sub>             | 7.27µA                               | 0.27μΑ  | 0.27µA                                   | 7.14µA | 0.27µA  |

|                                      | 0.23µA                     | 0.22µA                | I <sub>br2</sub>             | 7.24µA                               | 0.29μΑ  | 0.27µA                                   | 7.28µA | 0.29µA  |

| I <sub>br2</sub><br>I <sub>br3</sub> | 1.28µA                     | 1.18μΑ                | I <sub>br3</sub>             | 27.28µA                              | 33.9µA  | 35.7µA                                   | 32.2µA | 35.2µA  |

| CPU time                             | 90s                        | 1.0s                  | CPU time                     | 50s                                  |         | 0.8s                                     | 2.0s   |         |

Table 1: Comparative results for Fig.2.

Table 2: Comparative results for the circuit in Fig.3

Figure 4: Linearized CMOS transconductor

| - <b>1</b> 0 - <b>1</b>         | М          | onte-Carlo         | New Tool                    |                    |  |

|---------------------------------|------------|--------------------|-----------------------------|--------------------|--|

| Specifications                  | mean value | standard deviation | mean value                  | standard deviation |  |

| Slope (V <sub>in</sub> =0)      | 5.5 μA/V   | 0.21µA/V           | 5.4µA/V                     | 0.21µA/V           |  |

| Output offset                   | -0.1nA     | 0.5uA              | -0.1nA                      | 0.5µA              |  |

| Input offset                    | -0.4mV     | 0.1V               | -0.35mV                     | 0.07V              |  |

| Linearity: V   I(V)=0.9*I(-2.5) | -1.1V      | 20mV               | -1.1V                       | 21mV               |  |

| CPU time                        |            | 800s               | Matrix-1 10s / Matrix-2 30s |                    |  |

Table 3: Comparative results for the circuit in Fig.4 using Monte Carlo simulation and the new tool